https://theses.gla.ac.uk/

# Theses Digitisation:

https://www.gla.ac.uk/myglasgow/research/enlighten/theses/digitisation/

This is a digitised version of the original print thesis.

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

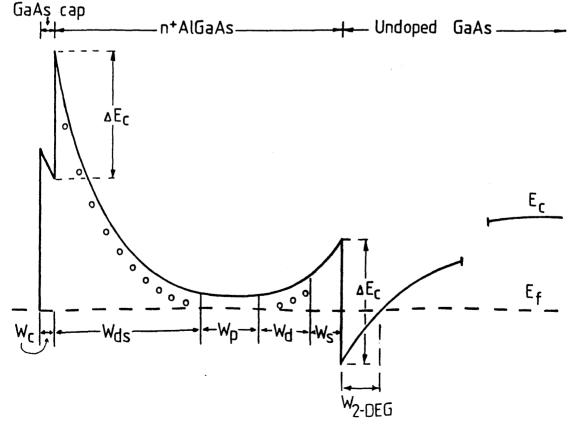

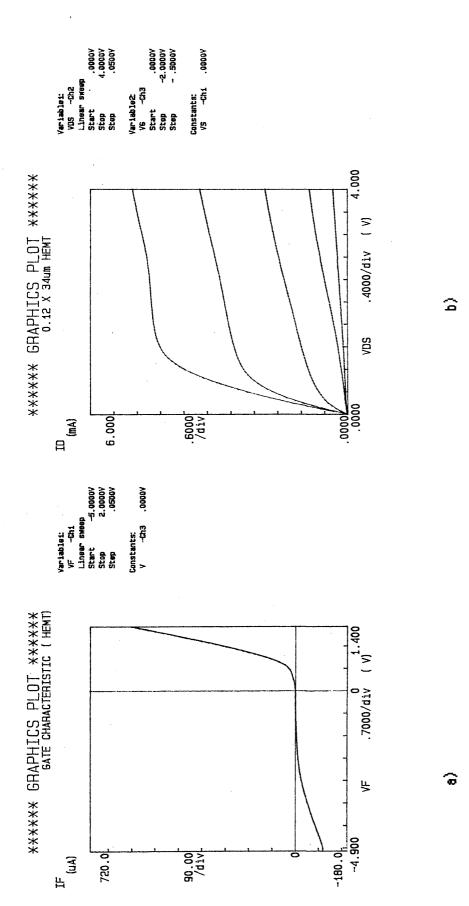

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses

<a href="https://theses.gla.ac.uk/">https://theses.gla.ac.uk/</a>

research-enlighten@glasgow.ac.uk

## THE FABRICATION OF VERY SHORT GATE-LENGTH

## GaAs FIELD EFFECT TRANSISTOR DEVICES

A thesis submitted to

the Faculty of Engineering of the

University of Glasgow for the degree

Doctor of Philosophy

by William Patrick

December 1985

ProQuest Number: 10991728

### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10991728

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC.

789 East Eisenhower Parkway

P.O. Box 1346

Ann Arbor, MI 48106 – 1346

#### **ACKNOWLEDGEMENTS**

I wish to express my thanks to Professor J. Lamb for the use of laboratory and computing facilities for the duration of this project and also to my supervisor Professor C.D.W. Wilkinson, Dr S.P. Beaumont and Dr W.S Mackie for their invaluable advice and encouragement throughout this project.

I would also to express my appreciation to the Science and Engineering Research Council and Plessey (Caswell) Ltd for their financial support. Also the staff at Caswell who provided valuable assistance during my visits to Caswell as well as guidance in the design and testing of devices. These include C. Oxley, I Davies, D. Bramley, B. Wilson, J. Sparrow and many more.

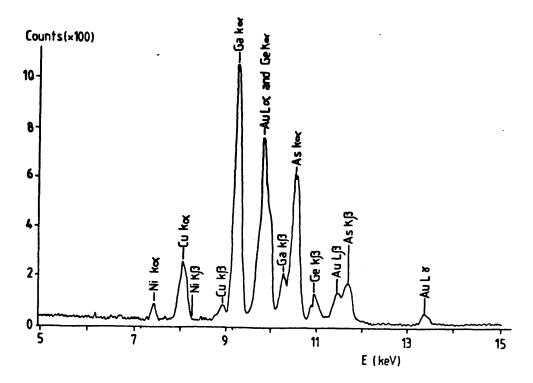

I am grateful to Dr J. Chapman of the Natural Philosophy Department for his advice and assistance throughout the x-ray analysis work and to Dr. M. Drummond for his invaluable help in this work.

Thanks are also due to all the technical staff who provided assistance throughout this work. In particular, J. Crichton, A. Stark, D. Gourlay, J. Clark, G. Boyle, L. Hobbs, K. Piechowiak and H Anderson. Also the computing staff especially A MacKinnon for providing enough disc space for my many pattern files.

I would also like to express my appreciation to all my fellow research students past and present for making my stay in the Department a memorable experience. Also for the many useful discussions which were had over a cup of K.Y. Lee tea.

Finally I would like to thank my family and friends for their support during my years of study and most of all my wife, Jane, for her incessant encouragement and understanding over the past three years.

## CONTENTS

| CHAPTER         | 0 GENERAL INTRODUCTION                             | 1  |

|-----------------|----------------------------------------------------|----|

| 0.1             | INTRODUCTION                                       | 1  |

| 0.2             | PROJECT OUTLINE                                    | 2  |

| CHAPTER         | 1 E-BEAM PROCESSING                                | 5  |

| 1.1             | INTRODUCTION                                       | 5  |

| 1.2             | EXPOSURE SYSTEM                                    | 5  |

| 1.3             | DESIGN and SHAPES                                  | 6  |

| 1.4             | PATTERN REPLICATION                                | 7  |

| 1.4.1           | Resist                                             | 7  |

| 1.4.2           | Choice of Casting Solvent                          | 9  |

| <b>CHAPTE</b> R | 2 OHMIC CONTACTS                                   | 12 |

| 2.1             | INTRODUCTION                                       | 12 |

| 2.1.2           | Chapter Outline                                    | 14 |

| 2.2             | TRANSMISSION LINE MODEL                            | 14 |

| 2.2.1           | Introduction                                       | 14 |

| 2.2.2           | TLM Test Structure                                 | 15 |

| 2.2.3           | Fabrication                                        | 16 |

| 2.3             | ANNEALING                                          | 17 |

| 2.4             | Auge CONTACT                                       | 18 |

| 2.4.1           | Thin Epi-Layer v Bulk Substrate                    | 18 |

| 2.4.2           | Results                                            | 19 |

| 2.4.3           | First TLM Measurements                             | 20 |

| 2.4.4           | Specific Contact Resistance v Anneal Temperature   | 21 |

| 2.4.5           | Specific Contact Resistance v Anneal Time          | 22 |

| 2.5             | AuGe/Ni/Au CONTACTS                                | 23 |

| 2.5.1           | Low Temperature Annealing                          | 23 |

| 2.5.2           | Test Structure                                     | 24 |

| 2.5.3           | Varying The Ni Concentration                       | 24 |

| 2.5.4           | Optimum AuGe Thickness                             | 25 |

| 2.5.5           | Varying The Ni Concentration on Optimum AuGe Layer | 27 |

| 2.6             | DISCUSSION                                         | 27 |

| 2A              | Appendix Contact Analysis Using the TLM              | 29         |

|-----------------|------------------------------------------------------|------------|

|                 | TLM Test Pattern for Contact Analysis                | 31         |

|                 | Modification to the TLM                              | 33         |

| <b>CHAPTE</b> R | 3 AUGER AND ENERGY DISPERSIVE X-RAY MICROANALYSIS OF |            |

| CIFICIEN        | ANNEALED CHAIC CONTACTS                              | 36         |

|                 |                                                      | 50         |

| 3.1             | INTRODUCTION                                         | 36         |

| 3.2             | AUGER ANALYSIS OF CONTACTS TO SOLID SUBSTRATES       | 36         |

| 3.2.1           | Introduction                                         | 36         |

| 3.2.2           | Sample Description                                   | 37         |

| 3.2.3           | Results                                              | 38         |

| 3.2.4           | Discussion                                           | <b>4</b> 0 |

| 3.3             | ENERGY DISPERSIVE X-RAY ANALYSIS OF CONTACTS TO      |            |

|                 | THIN GaAs MEMBRANES                                  | <b>4</b> 2 |

| 3.3.1           | Introduction                                         | 42         |

| 3.3.2           | Sample Preparation                                   | 42         |

| 3.3.3           | Energy Dispersive X-Ray Microanalysis                | <b>4</b> 3 |

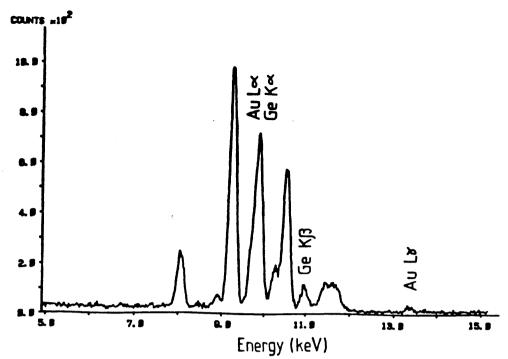

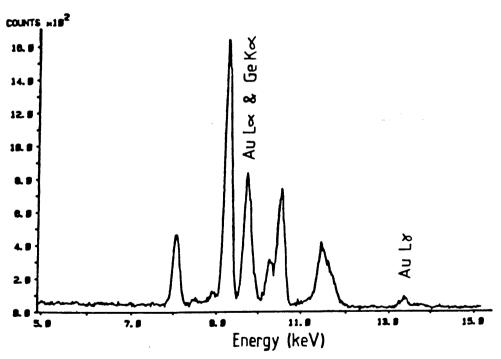

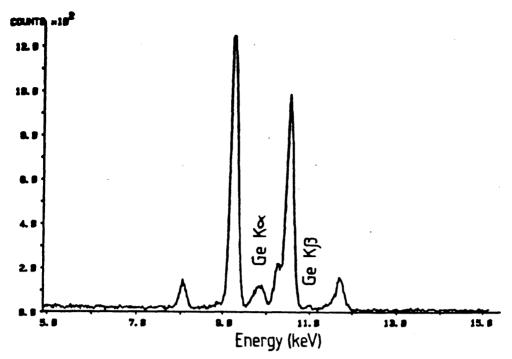

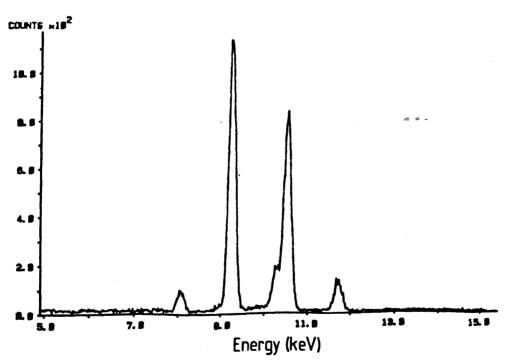

| 3.3.4           | Characteristic X-ray Spectrum                        | 44         |

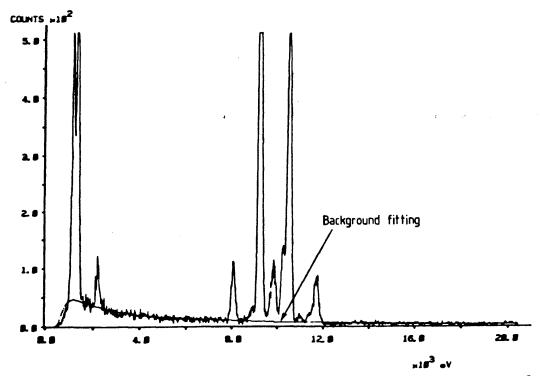

| 3.3.5           | Spectrum Analysis                                    | 45         |

| 3.3.6           | Experimental Results                                 | 46         |

| 3.3.7           | Unannealed Sample                                    | 47         |

| 3.3.8           | 300 <sup>O</sup> C Annealed Sample                   | 47         |

| 3.3.9           | 400 <sup>O</sup> C Annealed Sample                   | 48         |

| 3.3.10          | Quantitative Analysis                                | 49         |

| 3.4             | Summary                                              | 51         |

|                 |                                                      |            |

| CHAPTER         | 4 Gaas METAL SEMICONDUCTOR FIELD EFFECT TRANSISTORS  | 54         |

| 4.1             | INTRODUCTION                                         | 54         |

| 4.1.1           | Structure of a GaAs MESFET                           | 54         |

| 4.1.2           | Device Operation                                     | <b>5</b> 5 |

| 4.2             | MESFET FABRICATION                                   | 57         |

| 4.2.1           | General Description                                  | 57         |

| 4.2.2           | Alignment Techniques                                 | 58         |

| 4.2.2.1         | Alignment Test                                       | 58         |

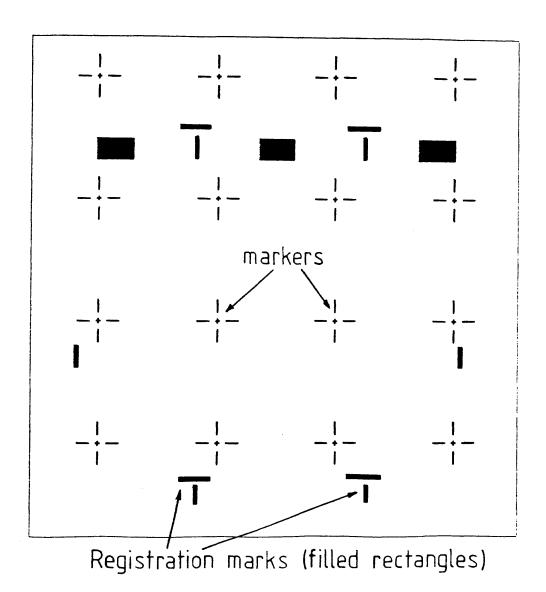

|                 | Coarse Alignment                                     | 58         |

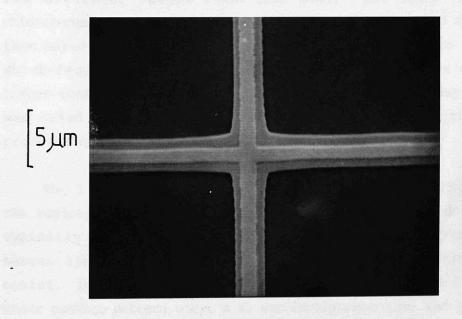

|                 | Fine Alignment                                       | 59         |

|                 | Results                                              | 59         |

| 4.2.3           | MESFET Fabrication Outline                           | 60         |

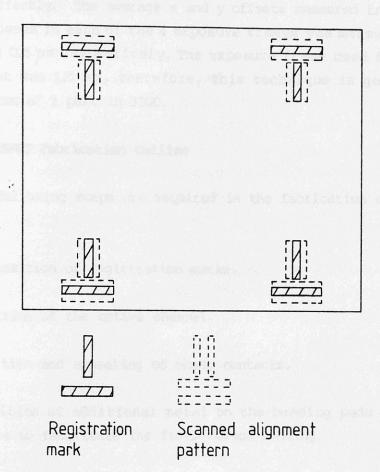

| 4.2.4   | Registration Marks                               | 61         |  |  |

|---------|--------------------------------------------------|------------|--|--|

| 4.2.5   | Isolation Level                                  | 62         |  |  |

| 4.2.5.1 | Mesa Isolation                                   | 63         |  |  |

| 4.2.5.2 | Boron Isolation                                  | 64         |  |  |

| 4.2.6   | Ohmic Contact Level                              | <b>6</b> 5 |  |  |

| 4.2.7   | Bonding Pad Level                                | 66         |  |  |

| 4.2.8   | Gate Level                                       | 67         |  |  |

| 4.2.8.1 | Gate Resist                                      | 67         |  |  |

| 4.2.8.2 | Gate Alignment                                   | <b>6</b> 8 |  |  |

| 4.2.8.3 | Gate Metallisation                               | 69         |  |  |

| 4.2.8.4 | Gate Recessing                                   | 70         |  |  |

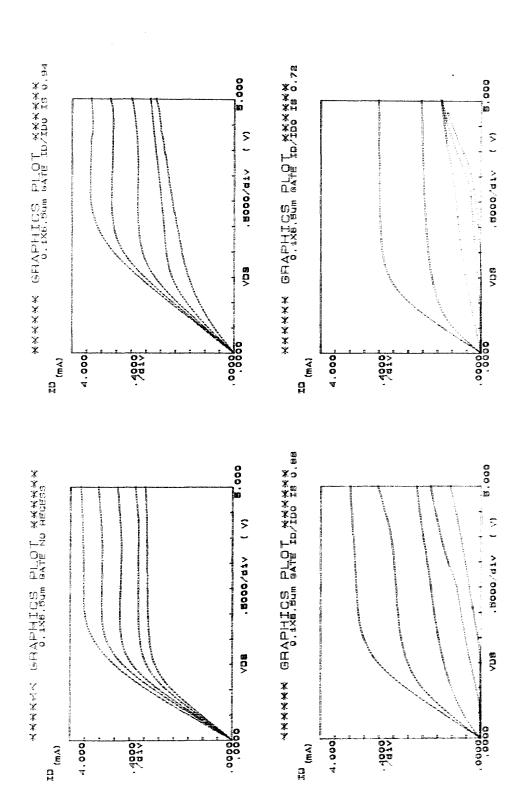

| 4.3     | DC OUTPUT CHARACTERISTICS                        | 71         |  |  |

| 4.3.1   | Material                                         | 71         |  |  |

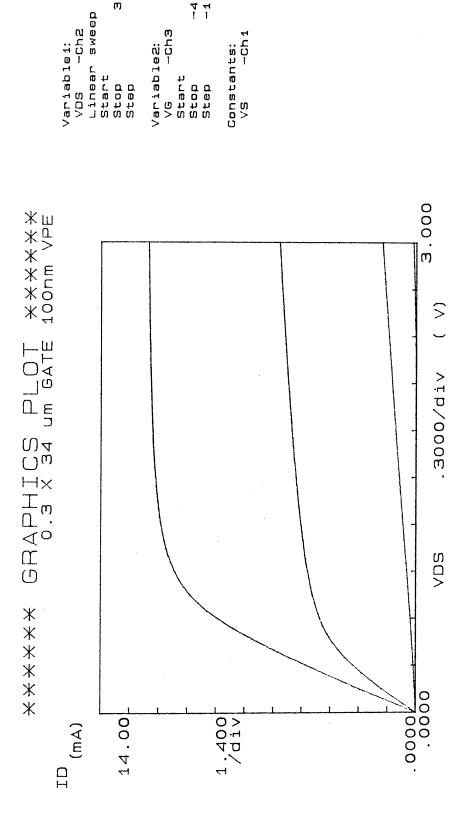

| 4.3.2   | Devices on 85 nm VPE Grown Layer                 | 71         |  |  |

| 4.3.2.1 | Monte Carlo Simulation                           | 73         |  |  |

| 4.3.2.2 | Variation of Transconductance with Gate Length   | 74         |  |  |

| 4.3.3   | Devices on 100 nm VPE Grown Layer                | 75         |  |  |

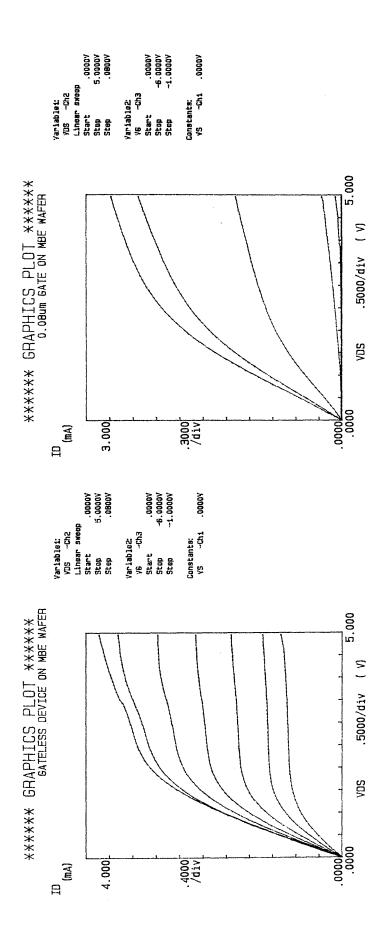

| 4.3.4   | Devices on 50 nm MBE Grown Layer                 | 76         |  |  |

| 4.3.4.1 | Backgating                                       | 76         |  |  |

| 4.3.4.2 | "Gateless FEI"                                   | 76         |  |  |

| 4.3.4.3 | MESFETs With Gates                               | <b>7</b> 7 |  |  |

| 4.3.5   | Devices on MCCVD Wafer (AlGaAs Buffer Layer)     | 78         |  |  |

| 4.3.6   | Summary of dc Measurements                       | 79         |  |  |

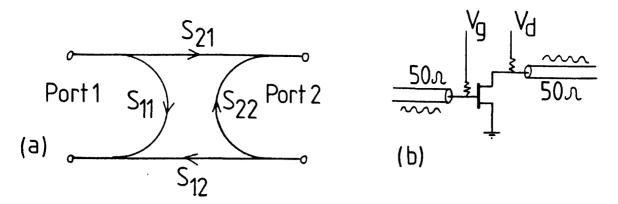

| 4.4     | AC MEASUREMENTS                                  | 79         |  |  |

| 4.4.1   | Results                                          | 81         |  |  |

| 4.4.2   | Summary of ac Results                            | 82         |  |  |

| CHAPTER | 5 ION IMPLANTATION MASKING TECHNIQUES AND DEVICE |            |  |  |

|         | INTERCONNECTIONS                                 | 87         |  |  |

| 5.1     | INTRODUCTION                                     | 87         |  |  |

| 5.2     | ION IMPLANTATION FOR DEVICE ISOLATION            | 87         |  |  |

| 5.2.1   | Introduction                                     | 87         |  |  |

| 5.2.2   | Masking Difficulties                             | <b>8</b> 8 |  |  |

| 5.2.3   | Development of Masking Technique                 | 89         |  |  |

| 5.3     | PROTON ISOLATION                                 | 89         |  |  |

| 5.3.1   | Original Proton Implantation Mask                | 89         |  |  |

| 5.3.2   | Gold Mask With Arsenic Trisulphide Parting Layer |            |  |  |

| 5.4     | BORON IMPLANTATION                               | 92         |  |  |

| 5.4.1   | Introduction                                     | 92         |  |  |

| 5.4.2      | Metal on Polymer Ion Implantation Masks                                  | 93         |

|------------|--------------------------------------------------------------------------|------------|

| 5.4.3      | Modified MOP Mask                                                        | 93         |

| 5.4.4      | Characterisation of Polyimide as a Negative Electron                     |            |

|            | Resist                                                                   | 93         |

| 5.4.5      | Modified MOP Mask Fabrication Process                                    | 95         |

| 5.4.6      | Chemically Produced MOP Mask v Plasma Etched                             | 96         |

| 5.4.7      | Discussion                                                               | 97         |

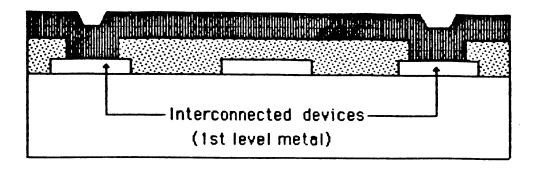

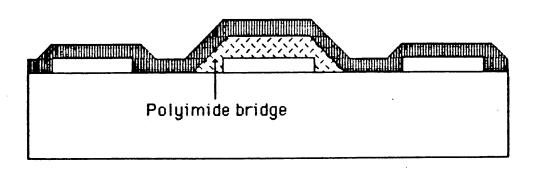

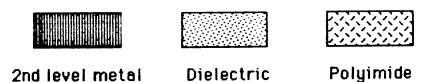

| 5.5        | CIRCUIT CROSSOVERS USING POLYIMIDE BRIDGES                               | <b>9</b> 8 |

| 5.5.1      | Introduction                                                             | 98         |

| 5.5.2      | Interconnecting Techniques                                               | 98         |

| 5.5.3      | Fabrication of Crossovers                                                | <b>9</b> 9 |

| 5.5.4      | Test Circuit                                                             | 99         |

| 5.5.5      | Results                                                                  | 100        |

| 5.6        | DISCUSSION                                                               | 101        |

|            |                                                                          |            |

| CHAPTER    | 6 DEVICES ON THIIN GAAS SUBSTRATES                                       | 103        |

| <i>c</i> 1 | TANIESCOLICEITOL                                                         | 100        |

| 6.1        | INTRODUCTION CHAPTED CHELTNE                                             | 103        |

| 6.3        | CHAPTER OUTLINE  PACE TO EDOME ALTCHMENT ON CILICON NUTRITION MARRIES    | 104        |

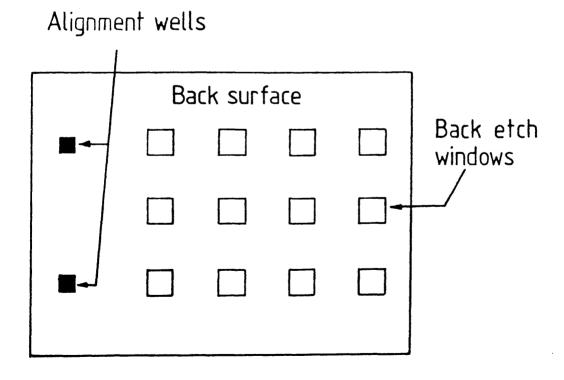

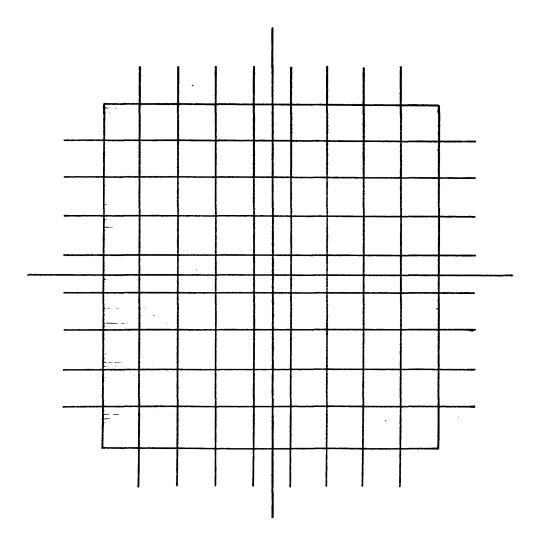

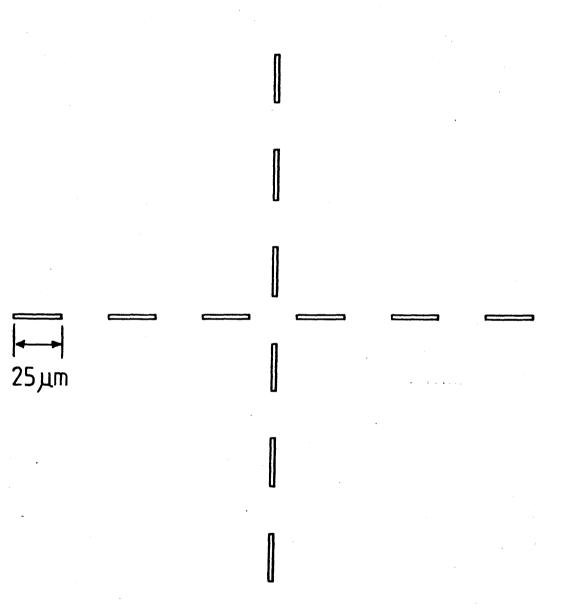

| 6.3.1      | BACK TO FRONT ALIGNMENT ON SILICON NITRIDE WAFERS Alignment Test Pattern | 105<br>105 |

| 6.3.2      | Resist Coating                                                           | 105        |

| 6.3.3      | Silicon Nitride Etch                                                     | 105        |

| 6.3.4      |                                                                          | 106        |

| 6.3.5      |                                                                          | 107        |

| 6.3.6      | Alignment                                                                | 107        |

| 6.3.7      | Results                                                                  | 108        |

|            | BACK TO FRONT ALIGNMENT ON GAAS WAFERS                                   | 109        |

| 6.4.1      |                                                                          | 109        |

| 6.4.2      |                                                                          | 110        |

| 6.4.3      | -                                                                        | 110        |

| 6.4.4      | Alignmnet                                                                | 111        |

| 6.4.5      | Results                                                                  | 111        |

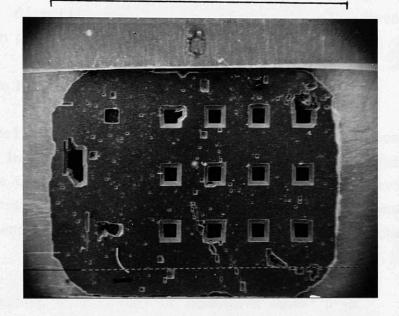

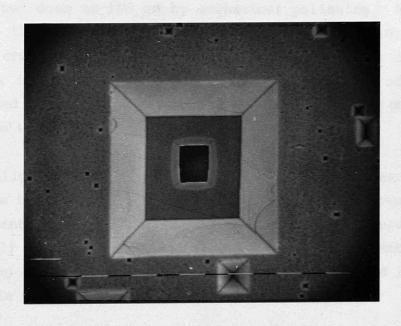

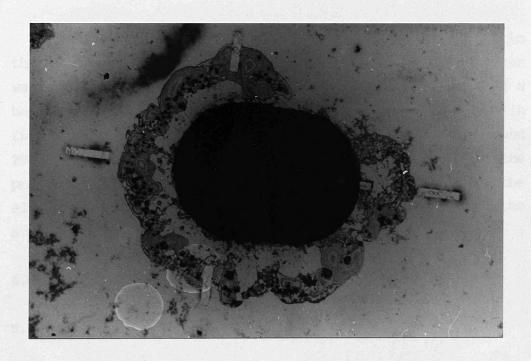

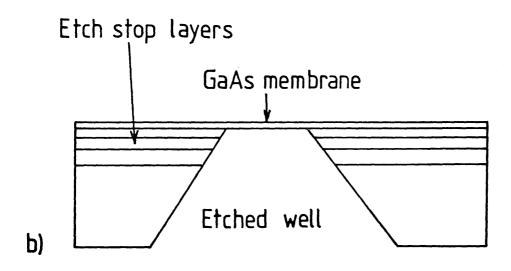

| 6.5        | GaAs MEMBRANE FABRICATION                                                | 111        |

| 6.5.1      | Introduction                                                             | 111        |

| 6.5.2      | Material                                                                 | 112        |

| 6.5.3      | Crystal Orientation                                                      | 113        |

| 6.5.4      | Masking System                                                           | 113        |

| 6.5.5      | Etching                                                                  | 114        |

| 6.5.6      | Membrane Fabrication                                                     | 114        |

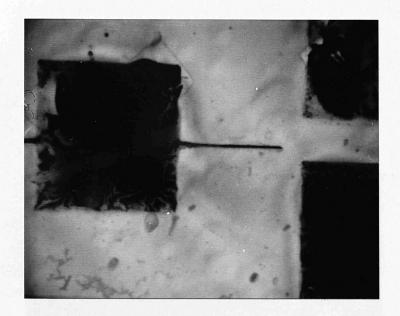

| 6.5.7   | Yield                                             | 117 |

|---------|---------------------------------------------------|-----|

| 6.6     | LITHOGRAPHY ON GaAs MEMBRANES                     | 117 |

| 6.6.1   | Introduction                                      | 117 |

| 6.6.2   | Ohmic Contact Metallisation                       | 118 |

| 6.6.3   | Contact Annealing                                 | 119 |

| 6.6.4   | Gate Patterning                                   | 120 |

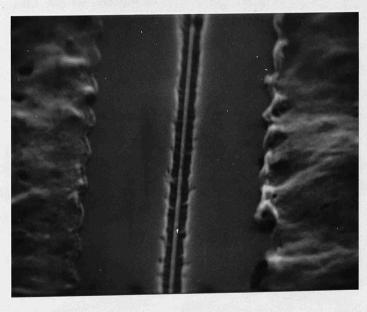

| 6.7     | CRACKS AROUND MEMBRANES                           | 121 |

| 6.8     | DEVICE FABRICATION                                | 122 |

| 6.8.1   | Process Outline                                   | 122 |

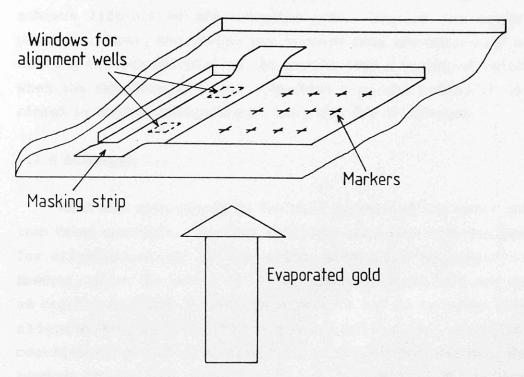

| 6.8.2   | Markers                                           | 123 |

| 6.8.3   | Metal on Polymer Mask                             | 123 |

| 6.8.4   | Coarse Contact Pattern                            | 123 |

| 6.8.5   | Back to Front alignment                           | 124 |

| 6.8.6   | Etching The Back Etched Wells                     | 124 |

| 6.8.7   | Annealing                                         | 125 |

| 6.8.8   | Testing                                           | 125 |

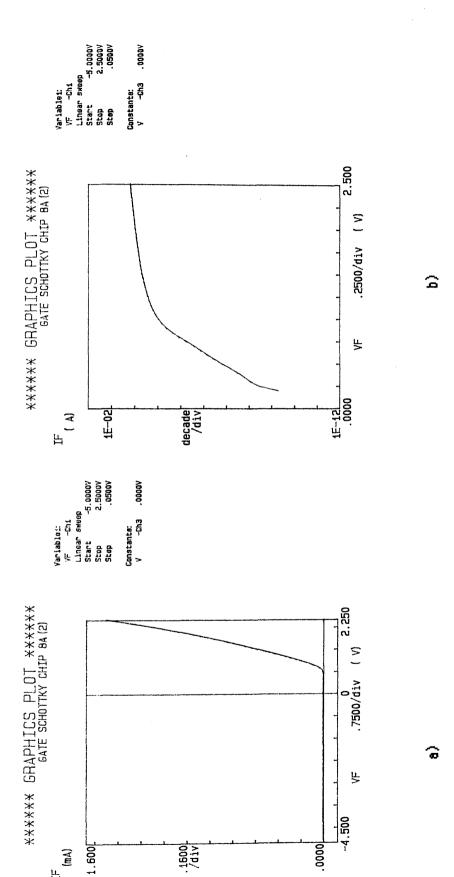

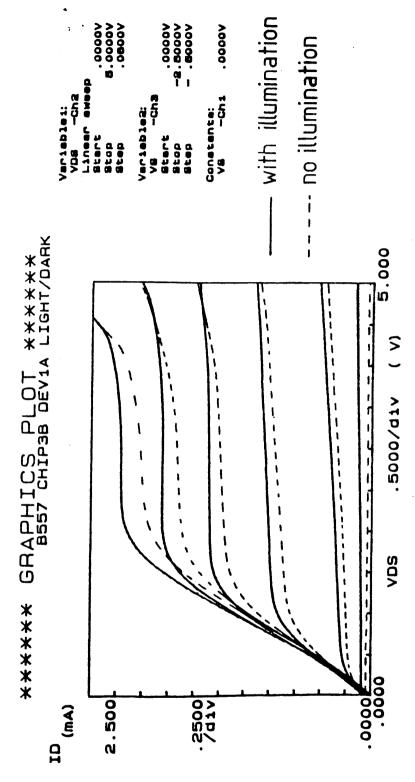

| 6.9     | FUTURE OF MEMBRANE DEVICES                        | 127 |

| CHAPTER | 7 HIGH ELECTRON MOBILITY FIELD EFFECT TRANSISTORS | 129 |

| 7.1     | INTRODUCTION                                      | 129 |

| 7.1.1   | Introduction to HEMTs                             | 129 |

| 7.1.2   | Design Considerations                             | 130 |

| 7.2     | HEMT FABRICATION                                  | 131 |

| 7.2.1   | Design of HEMT Structure                          | 131 |

| 7.2.2   | Material Growth                                   | 131 |

| 7.2.3   | Fabriaction                                       | 132 |

| 7.3     | HEMT CHARACTERISTICS                              | 132 |

| 7.4     | DISCUSSION                                        | 133 |

| CHAPTE  | R 8 CONCLUSIONS                                   | 137 |

The object of the work described in this thesis was to fabricate GaAs Metal-Semiconductor Field Effect Transistors with gate lengths comparable with the smallest structures fabricated previously in this Department using electron beam lithography. It was envisaged that MESFETs would be fabricated on both solid substrates and on thin active membranes of GaAs. It was then hoped to transfer the technology developed for the fabrication of MESFETs to the fabrication of High Electron Mobility Transistors (HEMTs).

A substantial part of the work was devoted to the development of a low temperature contact technology which could be used for the formation of ohmic contacts to GaAs. The low temperature was thought to be necessary to prevent undesired diffusion of the contact material during annealing, particularly on devices with closely spaced drain-source contacts. It was found that by varying the contact composition, a reduction in optimum annealing temperature of over 100 oc could be achieved without a reduction in specific contact resistance.

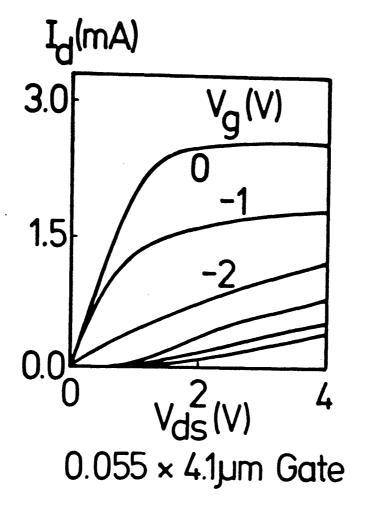

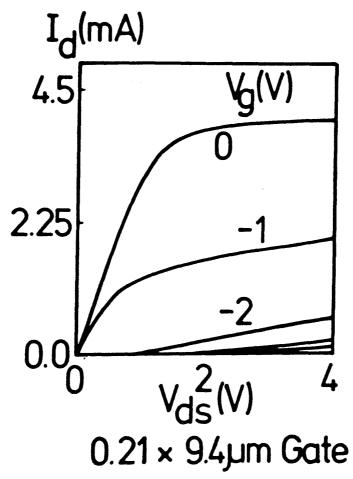

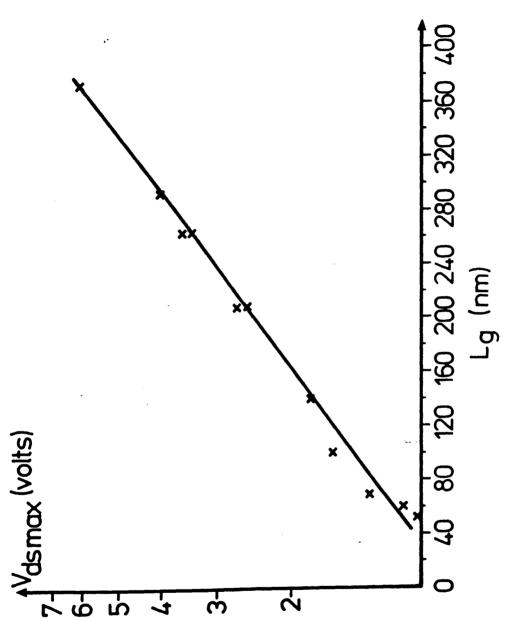

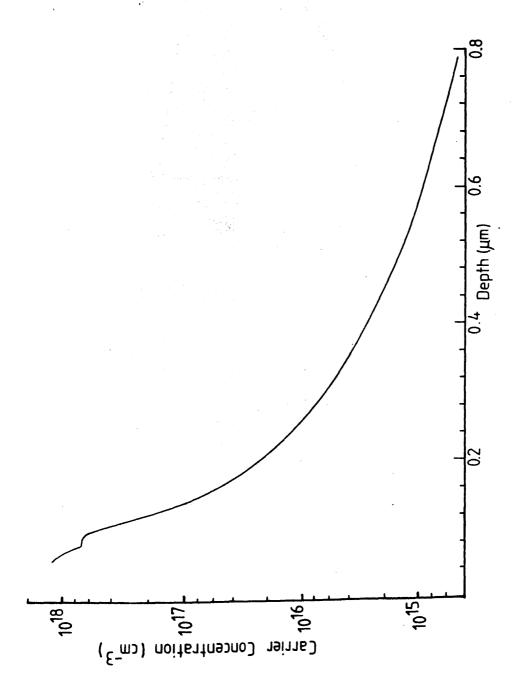

The MESFETs were designed to conform to a geometrical layout suggested by Plessey (Caswell) which would allow them to be bonded for rf testing. With this design, MESFETs with gate lengths down to 0.055 µm were fabricated and tested both at dc and at high frequency. Devices were fabricated on several different substrates and were optimised for maximum dc transconductance. The devices worked well at dc exhibiting transconductance values as high as had been reported for similar device structures, but the ac measurements (s-parameters) were disappointingly poor.

A new isolation technique was also developed - isolation using a boron ion implant - to replace mesa isolation. As this was only fully developed towards the end of the project only a specimen number of devices were fabricated using the technique. However, the process has subsequently been adopted by other workers in the electron-beam lithography group and has been shown to work satisfactorily.

With the development of the boron isolation technique it was possible to consider fabricating FET type devices on thin GaAs membranes (<100 nm). Various new processing methods combined with those already available, were used to produce a device with ohmic contacts on an area of active GaAs membrane, which was isolated from the rest of the wafer. Unfortunately, the material parameters were not suitable for continuation of this work, but, since the conclusion of this project, another worker has shown that devices may yet be made on a GaAs membrane.

Finally high electron mobility transistors were studied. A design for such a device was compiled and the material grown in this Department. Devices were fabricated and tested at dc where errors originating with the initial design became obvious. It was however, established from these results, that the devices operated in good agreement with theoretical predictions.

### 0.1 Introduction

Photolithography is by far the most important tool in the semiconductor industry for defining the features which form solid state electronic circuits. The advancement in expertise in this field has, so far, enabled the industry to fabricate circuits of progressively increased complexity by the reduction of device dimensions. Unfortunately, the minimum feature size which can be defined optically is determined by the wavelength of the illuminating radiation. This sets a resolution limit for photolithography at approximately 0.3 µm (deep ultraviolet radiation). Future circuit requirements may demand smaller feature sizes, tending towards the sub 0.1 um or nanometer scale, in which case alternative lithographic techniques will have to be X-ray and ion beam lithography are possible alternatives but, to date, the highest resolution has been obtained using electron beam lithography (EBL) where 10 nm linewidths have been demonstrated [0.1,0.2]. Currently the principal use of EBL systems is in the fabrication of reticle masks for use in optical lithography. More importantly, from a research point of view, the mask can be disposed of completely and patterns can be exposed directly (Direct Write) onto wafers coated in electron sensitive resist. The Direct Write system is particularly useful for research applications because of the ease of which pattern information, stored in computer memory, can be modified as needs demand. The main disadvantage of direct write EBL systems is that the sequential manner in which the pattern is scanned imposes limitations on sample throughput. It is therefore unlikely that the technique will be adopted for mass production purposes.

The electron beam lithography group in this Department was set up about seven years ago to study the limitations of electron beam lithography as a tool for fabricating extremely small features, less than O.1 µm in size. Much of the early work consisted of writing metallic gratings on thin, electron transparent substrates; initially carbon [0.3,0.4] but more recently on silicon nitride [0.5] and GaAs membranes [0.1,0.6].

The ultimate linewidth and pitch resolution obtained on these thin substrates (silicon nitride) was 10 nm and 40 nm respectively [0.1]. More recently the emphasis has been on transferring the lithographic technology to the fabrication of devices which might exhibit interesting characteristics because of their small dimensions. In particular Mackie [0.1] developed the techniques for fabricating very short gate-length GaAs MESFETs and Binnie [0.7] studied the fabrication of small geometry silicon MOSFETs.

#### 0.2 Project Outline

The aim of the work done for this thesis was to develop the techniques for fabricating very short gate-length GaAs MESFETs and to attempt to fabricate a MESFET device on a thin active It has been predicted that devices with layer of GaAs. dimensions of the order a few tens of nanometers would have different characteristics from similar devices with larger dimensions [0.8,0.9]. In simple terms, the carriers in an extremely small device would have a reasonable chance of being transfered ballistically between contacts; without experiencing any scattering events in the substrate. If this happens, the electrons would not reach an equilibrium velocity meaning that classical device physics no longer apply. Using high resolution electron beam lithography it was envisaged that MESFETs with gate lengths down to 50 nm, or less, could be fabricated on solid substrates. This dimension is still too large to expect truly ballistic effects but it was hoped that novel device characteristics would be observed because of the very smallness of the device. The reason for attempting to fabricate devices on a thin GaAs membranes was to take advantage of the very high resolution pattern definition capabilities previously demonstrated in this Department [0.1,0.3-6]. It would then be possible to fabricate transistors with a gate length of the order of 10 nm and drain-source spacing about an order of magnitude higher.

The work was divided into the following main sections:-

(1) The development of a low temperature annealing process for

forming ohmic contacts to GaAs. It was envisioned that the low temperature annual would enable closely spaced contacts to be formed without interdiffusion of the contact material between contacts.

- (2) Qualitative analysis of the annealed contacts using x-ray microanalysis to study the lateral diffusion of contacts on a thin GaAs membrane and Auger analysis to examine contacts formed on solid substrates.

- (3) Processing and testing of GaAs MESFETs fabricated on a number of different substrates. The MESFETs were optimised for maximum dc transconductance. When tested at dc the output characteristics were good even down to a gate-length of 55 nm. Unfortunately, the ac (s-parameter) measurements taken from a selection of these devices were unsatisfactory.

- (4) Development of an isolation technique to replace the conventional mesa isolation method. A novel ion implantation process (metal on polymer mask) was developed using a positive on negative two layer resist system.

- (5) Fabrication of devices on thin active GaAs membranes isolated using boron implantation. Although no working transistors were produced the results obtained indicated that the fabrication of such a device is still a distinct possibility.

- (6) A brief study of High Electron Mobility Transistors (HEMTs) was made, from the material design through to the manufacture and testing of devices.

A short description of the lithographic processes used throughout this work is given in the following chapter. The ohmic contact processing and analysis are described in chapters 2 and 3. Chapter 4 is devoted to the fabrication of GaAs MESFETs on solid substrates. Included in this chapter is the dc characterisation of devices fabricated on different substrates as well as s-parameter measurements (up to 18 GHz) of a selection of these devices. A novel ion implantation masking technique is described in chapter 5. Chapter 6 deals with the processes

required in the fabrication of MESFET devices on thin GaAs membranes. The design, fabrication and testing of HEMT devices is given in Chapter 7. Finally, some overall conclusions and suggestions for future work are given in chapter 8.

#### Chapter O References

- [O.1] WS Mackie, PhD Thesis, University of Glasgow (1984).

- [0.2] HG Craighead, RE Howard, LD Jackel, PM Manckiewitch, "10-nm Linewidth Electron-Beam Lithography on GaAs," Appl. Phys. Lett 43 p38 (1983).

- [O.3] SP Beaumont, T Tamamura, CDW Wilkinson, "Two Layer Resist System for Efficient Lift-Off in Very High Resolution Lithography," Proc. Microcircuit 80, Amsterdam, (1980)

- [O.4] SP Beaumont, PG Bower, T Tamamura, CDW Wilkinson, "Sub-20-nm-wide Metal Lines by Electron Beam Exposure of thin Poly(methylmethacrylate) films and Lift-Off," App. Phys. Lett. 38 p436-438 (1981).

- [O.5] SP Beaumont, B Singh, CDW Wilkinson, "Very High resolution Lithography-Thin Films or Solid Substrate?" Proc. 10th International Conf. on Electron and Ion Beam science and Technology, montreal, Canada (1982).

- [O.6] WS Mackie, SP Beaumont, CDW Wilkinson, JS Roberts, "High Resolution Lithography on Active Semiconductor Membranes," Ref. O.5.

- [0.7] CE Binnie, PhD Thesis, University of Glasgow (1985).

- [O.8] MS Shur, LF Eastman, "Ballistic Transport in Semiconductors at Low-temperatures for Low-Power, High Speed Logic," IEEE Trans. Elect. Dev. ED-26, 1677-1683 (1979).

- [O.9] LF Eastman, R Stall, D Woodward, N Dandekar, CEC Wood, M Shur, K Board, "Ballistic Motion in GaAs at Room Temperature," El. Lett. 16, p524-525 (1980).

#### 1.1 Itroduction

Much has already been written about electron-beam litographic processing in the theses of Mackie [1.1], Binnie [1.2] and Rishton [1.3]. Therefore a detailed review of all the processing steps used in this work will not be presented here. However, for completeness, a brief description of the main processes is given in the following sections. A recently published article by Mackie and Beaumont provides a good overview of nanometer lithographic techniques [1.4].

#### 1.2 Exposure System

The machine used in this project was a Philips PSEM 500 scanning electron microscope which was modified for lithography. The main modifications were:-

- (a) The addition of a beam blanking system to prevent undesired exposure of the sample. When this feature is selected, control of the electron beam is switched from the internal raster scan generator to an external digital scan generator. Both the beam blanking and scan generator are controlled by a microcomputer. This was originally a KIM microprocesser with only a temporary memory which meant that pattern data had to be transfered from the GEC 4180 mainframe computer at every exposure session. The KIM has now been replaced with an Ithaca microcomputer which has the facility for storing all the pattern data on disc.

- (b) A transmission detector was fitted in the specimen chamber for the exposure and examination of thin substrate specimens.

The Philips machine has a range of electron spot sizes from 8 nm up to 1 µm and an accelerating voltage which is continuously variable from 1.5 to 50 kV. The spot size selected for exposure purposes depended mainly on the frame size and area of the feature to be exposed but the accelerating voltage was invariably set at 50 kV for maximum resolution.

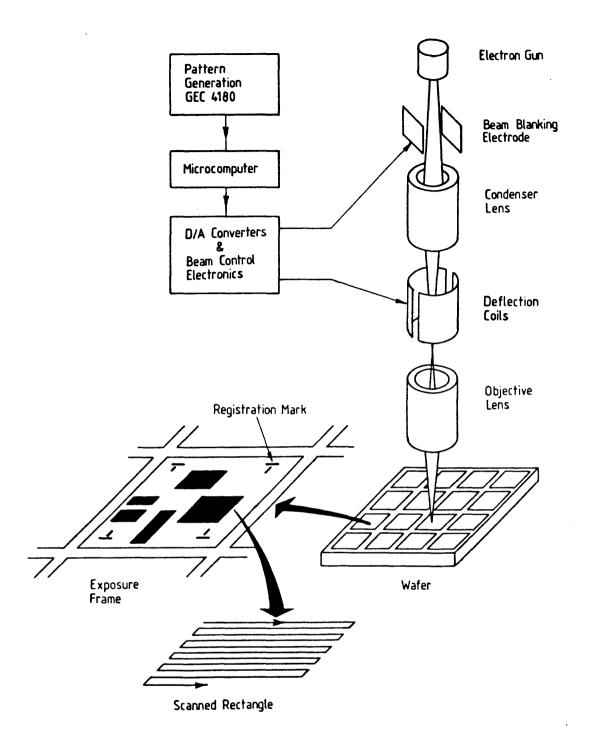

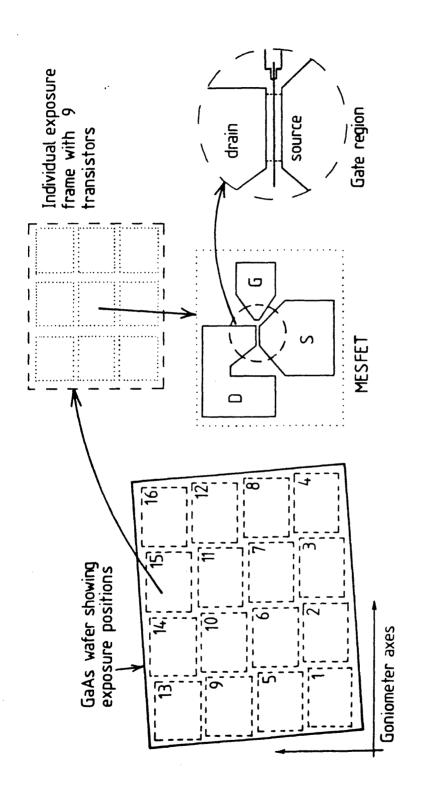

A schematic representation of the scanning electron-beam exposure system is shown in fig. 1.1. Each pattern file is generated on a GEC 4180 computer, using an interactive pattern editor (DESIGN) developed by Mackie [1.1]. The files are transfered to the microcomputer where they are stored on disc. A program (EBSS) is run on the microcomputer which sends pattern data sequentially to the scan generator which, in turn, generates the reversing raster scan that defines each rectangle. When the beam is scanned over the electron sensitive resist, the structure of the resist is modified in such a manner that either the exposed or the unexposed resist can be selectively removed in a suitable developer. The patterned resist layer can then be used as a stencil to transfer a metallic pattern onto the wafer or it can be used as a mask for etching.

#### 1.3 DESIGN and SHAPES

DESIGN is the interactive pattern editor used for pattern development and is run on a GEC 4180 computer. Since describing DESIGN in his thesis, Mackie has modified the program to cater for multi-level pattern editing which has proved to be most useful in the design of complete mask sets for device manufacture. The basic concepts of the program however, are the same as described in ref. [1.1]. The data file generated using DESIGN contains the coordinates of the opposite corners of each rectangle in the pattern as well as the appropriate exposure information for each section of the pattern.

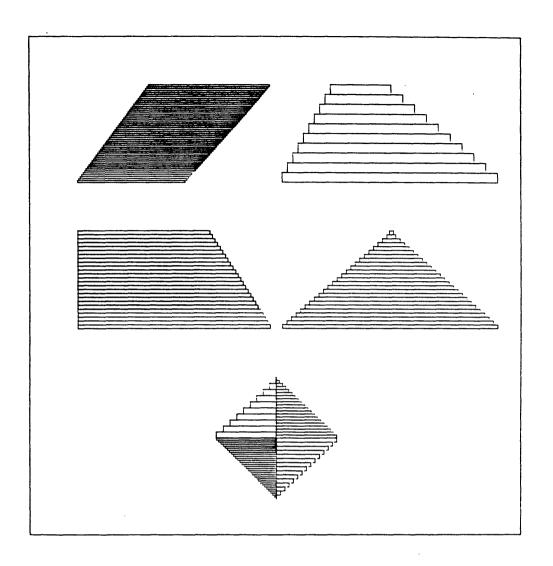

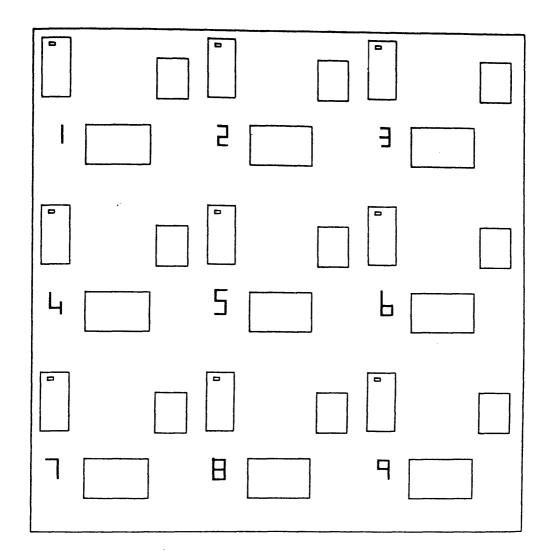

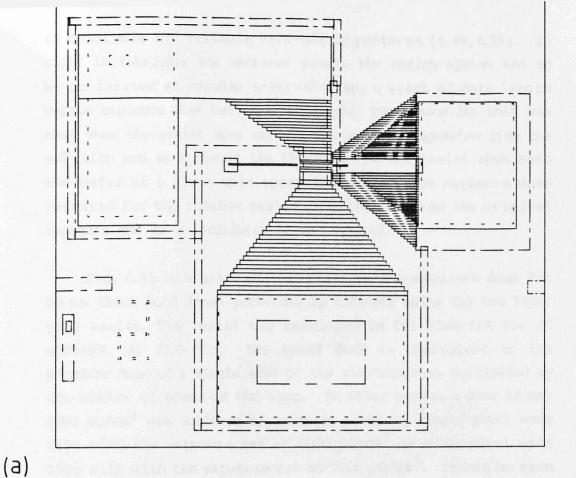

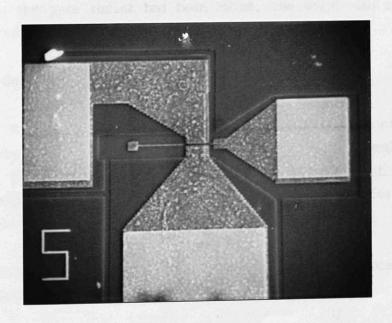

SHAPES is a simple program which was written for this thesis to generate triangular or trapezoidal patterns made up of a series of narrow rectangles. Although this program is not incorporated into DESIGN, the output of SHAPES is in a form which can be used directly in DESIGN for final pattern editing. Using SHAPES, it is assumed that two sides of the figure are parallel to the x-axis. However, by reducing one of the parallel sides to a point, it is possible to generate triangular patterns (fig. 1.2.). The y coordinates of the top and bottom sides of each pattern, the x coordinates of all of the corners (defined clockwise from the bottom left hand corner) and the number of rectangles per figure are specified for each separate pattern. The diamond shape shown

Fig.1.1 Schematic illustration of the electron-beam exposure system used throughout this project.

Fig. 1.2 Examples of the patterns which can be generated using the program "SHAPES".

in fig.1.2 was made up of four individual parts and each part was made up with a different number of rectangles. The choice of the number of rectangles per figure depends on how smooth the edges of the final exposed pattern needs to be. Clearly the more rectangles specified per figure the less apparent it will become that the pattern is, in fact, made up of a group of individual rectangles. It should be noted that the maximum number of rectangles which can be stored in a DESIGN file is 1000 so this has to be taken into consideration when creating a pattern using SHAPES. In this work the main pattern which utilised this program was the ohmic contact pattern of the GaAs MESFETs (Sect. 4.2.6) which contained 950 rectangles.

## 1.4 Pattern Replication

#### 1.4.1 Resist

There are two types of resist; positive resist where the areas of resist exposed by the electron beam are subsequently dissolved in a developer and negative resist where it is the unexposed resist which is dissolved. Negative resist (in this case polyimide) was only used as part of a novel process for fabricating metal on polymer ion implantation masks and circuit crossover points. This is described in full in chapter 5 and so requires no further mention here. The bulk of the work was carried out using Poly (Methyl MethAcrylate) (PMMA) positive resist. When PMMA is illuminated by an electron beam the molecular structure of the exposed area of the resist is modified by the beam. Put simply, the long molecular chains are severed principally by the secondary electrons generated in the resist from inelastic scattering of the primary beam electrons [1.3,1.5,1.6]. The modified resist areas can be selectively dissolved in a suitable solvent such as Methyl IsoButyl Ketone (MIBK). Conventially, the developer solution consists of part MIBK and part Iso Propyl Alcohol (IPA) the latter of which dissolves neither the exposed or unexposed resist. The ratio of MIBK to IPA essentially determines the sensitivity, contrast and edge definition of the resist [1.4].

The main pattern replication techniques employed in the work

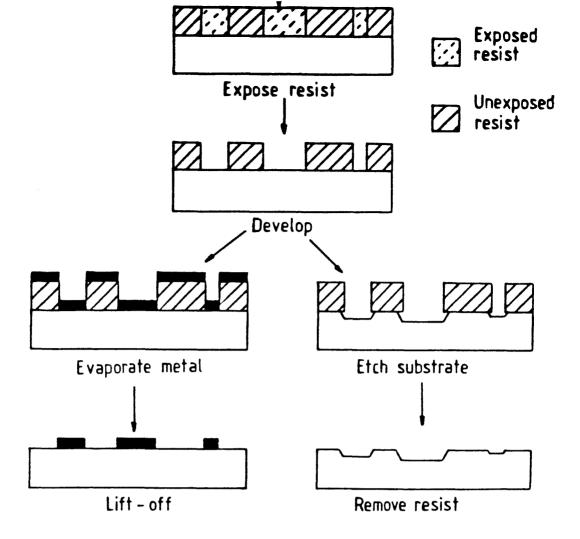

Fig. 1.3 Illustration showing the lift-off and etching techniques used in this work.

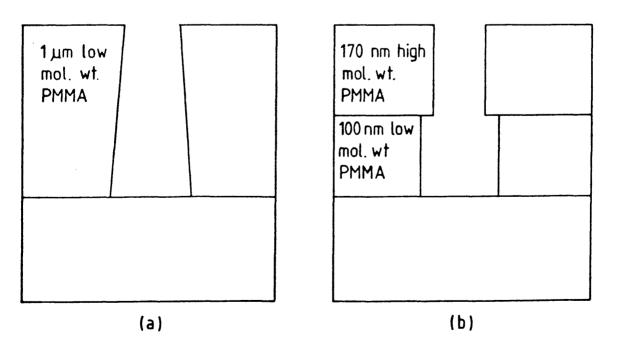

Fig.1.4 Developed profiles of the two main resists used for pattern definition. (a) Low resolution resist for all lift-off and etching steps other than those associated with gate definition. (b) Two layer, high resolution resist for defining very short gates.

of this thesis were lift off and etching. These processes are illustrated in fig 1.3. The lift-off process uses a patterned PMMA film as a stencil for transfering a metallic pattern to the specimen surface. After processing the resist, a metallic layer is deposited over the entire surface of the wafer (thermal evaporation was used throughout this project). The unwanted metal is then removed by dissolving the remaining PMMA in acetone, leaving the desired metal pattern on the wafer. Patterned resist films were also used as masks for etching the substrate material below the resist. Care had to be taken in the preparation of an etch mask to ensure good adhesion between the resist and substrate (Sect. 1.4.2).

Two resist sytems were used extensively throughout this project:-

- (a) A thick (1  $\mu$ m), single layer of low molecular weight PMMA (185 OCO) and

- (b) A high resolution two layer resist consisting of a 170 nm layer of high molecular weight PMMA (350 000) on 100 nm of low molecular weight PMMA (185 000).

Resist (a) was used for defining thick metallic patterns (low resolution) by lift-off. The profile of this resist after development is shown in fig. 1.4 a). The undercut profile is a consequence of the divergence of the electron-beam as it passes through the resist film (due to elastic and inelastic scattering events). Fortunately, this profile is ideal for lift-off because the metal evaporated over the resist is completely separated from the metal on the specimen surface. This allows easy access of the solvent to the remaining resist and facilitates good, clean lift-off of the unwanted metal [1.1,1.2.1.4].

Resist (a) was also used successfully as a wet etch mask for various applications. This resist was chosen because of the small amount of pinhole defects associated with the thick resist and for its resistance to the etch solutions, provided it was properly prepared (see following section).

Resist (b) was used only for the definition of the very narrow lines used in the formation of Schottky gates on GaAs MESFETs. When developed, the two layer resist also exhibits a desireable undercut profile (fig. 1.4b)) which improves the reliability and quality of the lifted-off lines. The undercut, in this case, arises because the lower layer of resist is more sensitive than the upper layer. Thus, when the resist is developed, more material is dissolved from the bottom layer, leaving the undercut profile shown in the figure [1.1,1.2,1.4,1.7].

## 1.4.2 Choice of Casting Solvent

The PMMA, as received from the manufacturers, was in powder form and had to be dissolved in a suitable solvent before it could be spin coated onto wafers for processing. There were essentially four readily available solvents which could be used; MIBK, chlorobenzene, xylene and trichloroethylene. A short experiment was carried out to see if the casting solvent in any way affected the adhesion of the resist to a substrate. First of all, solutions of PMMA dissolved in each of the solvents were made up and characteristic plots of resist thickness (after baking) versus spin speed were obtained. Then, selecting spin speeds for each solution that would produce resist layers of similar thickness (200 nm), several clean GaAs wafers were coated with resist and baked for either 2 hours or overnight (12 h) at 180°C. An arbitary pattern was then exposed in the resist and developed in 1:1 MIBK: IPA. Next, each wafer was immersed in a 10 % ammonia solution, chosen because previous experimental evidence had shown that PMMA (dissolved in xylene) had low resistance to ammonia containing solutions. After 1 minute in ammonia, the wafers were rinsed in deionised water, blown dry, and observed under an optical microscope. In the table 1.1 below the percentage of the PMMA mask remaining on each sample, after being subjected to the ammonia solution, is shown.

CASTING SOLVENT BAKE TIME PERCENTAGE OF RESIST FILM REMAINING

| MIBK              | 2  | HOURS | 100 %       |

|-------------------|----|-------|-------------|

|                   | 12 | •     | 100 %       |

| Chlorobenzene     | 2  | n     | 6O %        |

|                   | 12 | •     | 100 %       |

| Xylene            | 2  | **    | O %         |

|                   | 12 | n     | 50 <b>%</b> |

| Trichloroethylene | 2  | n     | 0 %         |

|                   | 12 | 11    | O %         |

|                   |    |       |             |

TABLE 1.1

The obvious choice of casting solvent for PMMA is MIBK which adhered perfectly to the substrate in this experiment even with just a two hour bake. However, MIBK was not selected because the time taken to dissolve the large amounts of MIBK required to produce a PMMA layer of similar thickness to resist (a) above, was excessive. Consequently chlorobenzene was chosen as the casting solvent for the PMMA layers required for device processing. The 1 µm layer was obtained by dissolving 15 % PMMA by weight in the solvent and spin coating the solution onto GaAs wafers at 5000 rpm. When the resist was to be used as an etch mask it was always baked overnight beforehand. Similarly, the lower layer of the two layer resist (b) was obtained by spinning 4 % PMMA dissolved in chlorobenzene at 6000 rpm. Unfortunately, because the dissolution rate of PMMA in chlorobenzene is very high, this solvent could not be used as the casting solvent for the upper layer of the two layer system. This would have resulted in partial dissolution of the previously applied film as soon as the second solution was applied. Xylene, which is a relatively slow dissolver of PMMA, was therefore chosen as the casting solvent for the second layer resist.

## Chapter 1 References

- [1.1] WS Mackie, PhD Thesis, University of Glasgow (1984).

- [1.2] CE Binnie, PhD Thesis, University of Glasgow (1985).

- [1.3] SA Rishton, PhD Thesis, University of Glasgow (1984).

- [1.4] WS Mackie, SP Beaumont, "Materials and Processes for Nanometer Lithography," Solid State Tech. Aug 1985, pl17-123.

- [1.5] AN Broers, "Resolution Limits of PMMA Resist for Exposure with 50 kV Electrons," J. Electrochem Soc. 128 pl66-170 (1981).

- [1.6] GR Brewer, "Electron-Beam Technology in Microelectronic Fabrication," Academic Press, New York, (1980).

- [1.7] CE Binnie, SP Beaumont, CDW Wilkinson, JC White, "The Fabrication of Very Short Gate Length N-Channel MOSFETs by Direct Write Electron Beam Lithography," Proc Microcircuit 82, Grenoble, France (1982).

#### 2.1 Introduction

In the fabrication of semiconductor devices good ohmic contacts need to be formed to transfer current into or out of each device. An ohmic contact is defined as a metal to semiconductor contact that has negligible contact resistance compared with the bulk or spreading resistance of the semiconductor. A good ohmic contact should supply the required current to a device with a voltage drop at the metal semiconductor interface that is sufficiently small compared with the drop across the active region of the device [2.1]. The specific contact resistance,  $\rho_{\rm C}$ , is an important figure of merit for the contacts and is defined as [2.2].

$$\mathcal{O}_{C} = \frac{V_{C}}{J_{C}} = \frac{\text{Voltage drop across the interface}}{\text{The interfacial current density}}$$

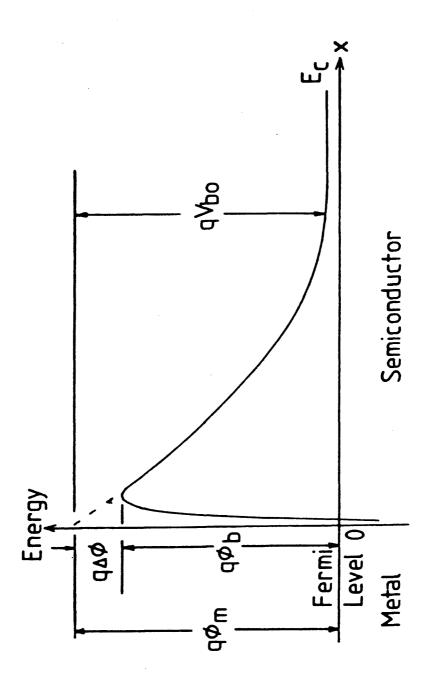

The energy band diagram of a metal-semiconductor barrier under equilibrium conditions is shown in fig. 2.1  $\not\!\! D_m$  is the work function of the metal,  $\not\!\! D_b$  is the barrier height,  $\Delta \not\!\! D_b$  is the barrier lowering due to image force and  $V_{bO}$  is the built in potential.

There are two main current transport mechanisms associated with metal semiconductor barriers. These are thermionic emission of carriers over the metal-semiconductor barriers and tunneling through the space charge region at the metal-semiconductor interface. For contacts to low doped semiconductors ( $<10^{17}$  /cm³), the thermionic emission dominates and lower contact resistances can be obtained using lower barrier heights [2.2]. On highly doped material on the other hand the tunneling process dominates since the width of the potential barrier decreases with increased doping. The best conditions for low resistivity metal-semiconductor contact formation is therefore a high doping concentration, a low barrier height or both. However on GaAs, since the barrier height is essentially independent of the metal used (approximately 0.8 eV) [2.1,2.3], it is necessary to use highly doped semiconductor contact layers for the fabrication of

Fig. 2.1 Energy band diagram for a metal-semiconductor contact.

contacts with low resistivities. A paper by Pruniaux [2.4] claims that heating the substrate during contact evaporation will reduce the barrier height. However, since the temperatures required (>150  $^{\rm O}$ C) are greater than the glass transition temperature of PMMA (100  $^{\rm O}$ C), this method is not practical for use when lift-off is used for pattern definition.

The doping level of the GaAs epi-layers used for MESFET fabrication (Chap. 4) was typically  $10^{18}$  /cm<sup>3</sup>; about ten times lower than the doping level required for the potential barrier at the metal-semiconductor interface to appear almost transparent to carrier flow [2.2]. Higher doped material could not be used in MESFET fabrication because, although the ohmic contacts would improve, the Schottky characteristics of the gate, an important element in the devices, would deteriorate. Therefore, the commonly used AuGe/Ni/Au contact system was adopted for producing contacts to GaAs. When these contacts are annealed, complex metallurgical reactions take place and a degenerately doped semiconductor layer is formed beneath the contact. Many attempts have been made to describe these complex reactions; the work of Ogawa [2.5] gives a detailed analysis of annealed contacts.

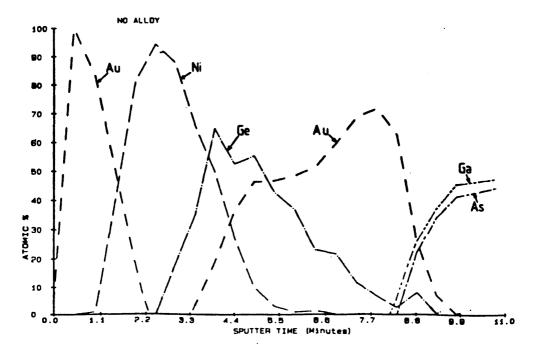

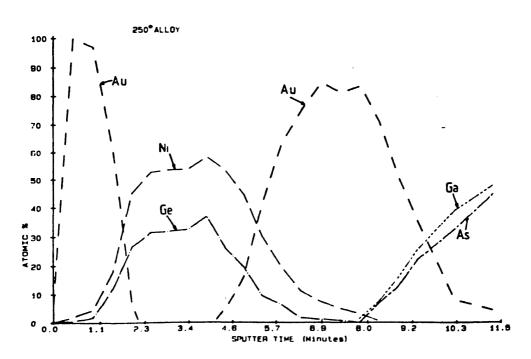

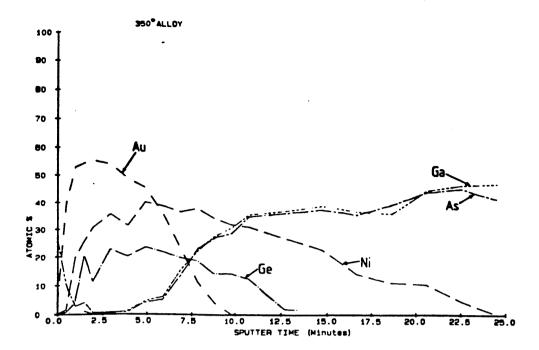

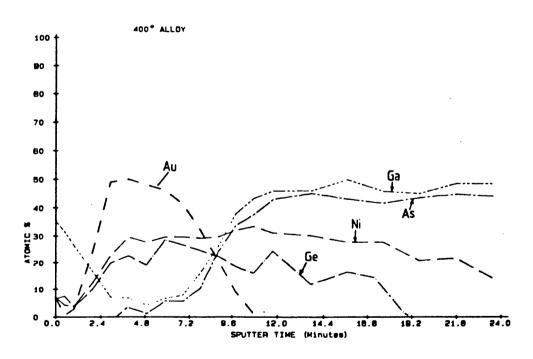

Essentially the description given by Ogawa for annealed contacts is as follows. At 300 °C Ge diffuses towards the contact surface and is trapped in the Ni layer. Some of the Ni diffuses inward. At the metal-semiconductor interface GaAs is decomposed partly through the reaction between Ni and GaAs but mainly through the reaction of Au with GaAs where Ni plays the role of a catalyst. At higher temperature (400 °C) the Ge which was trapped at the surface diffuses inwards and is partly captured by NiAs. The rest of the Ge is considered to be doped into the GaAs.

In the work described here, specific contact resistances around  $10^{-5}$  ohm.cm<sup>2</sup> were obtained on material originally doped with silicon to  $10^{18}$  /cm<sup>3</sup>. Theoretically  $\rho_{\rm C}$  on this material should have been about  $10^3$  ohm.cm<sup>2</sup> assuming a barrier height of 0.8 eV [2.2,2.6]. The doping level required to reduce  $\rho_{\rm C}$  to  $10^{-5}$  ohm.cm<sup>2</sup> is around  $3.10^{19}$  /cm<sup>3</sup> for the same barrier height. Therefore, during the annealing of the AuGe/Ni/Au contacts the

doping of the semiconductor layer below the contact must have been increased by more than an order of magnitude.

## 2.1.2 Chapter Outline

In this chapter the experimental work done on the fabrication of ohmic contacts to n<sup>+</sup> GaAs is described. In particular, the development of a low temperature annealing process for contacts to thin epi-layers (<100nm) will be given. Low temperature annealing was desireable, particularly in devices with small source-drain gaps, to ensure that the lateral diffusion of the contact material during annealing does not adversly affect the GaAs in the vicinity of the gate. It was thought that if the annealing temperature could be reduced from the standard temperature for AuGe/Ni/Au of 420 °C to less than 300 °C (below the eutectic temperature of AuGe 365 °C), then the diffusion of the contact material during annealing would be significantly reduced.

Before describing the low temperature annealing process for contacts to thin n+ GaAs epi-layers a description of the transmission line model used in the analysis of contact parameters will be given. Then the initial experiments on AuGe contacts to epitaxial and bulk n<sup>+</sup> substrates, including the effects of anneal temperature and time, are described. Finally the optimisation of AuGe/Ni/Au contacts for low temperature annealing will be described. The following chapter contains the analysis of contacts on solid substrates using Auger Analysis and of contacts on thin substrates using Energy Dispersive X-ray microanalysis.

## 2.2 Transmission Line Model

## 2.2.1 Introduction

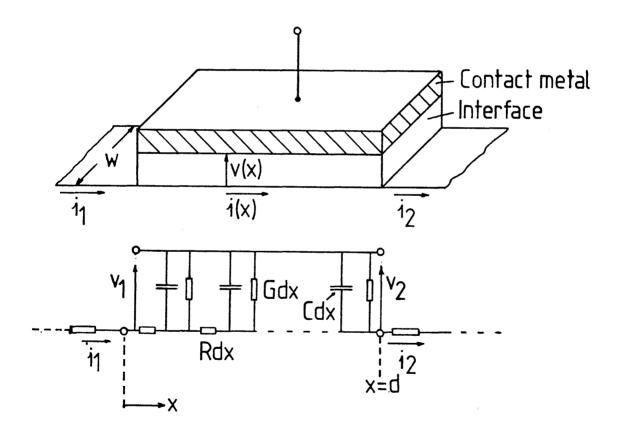

The tool used in the analysis of planar ohmic contacts is the transmission line model (TLM) developed by Murrmann and Widmann [2.7] and independently by Berger [2.8]. In this model the contacts are modelled as a distributed circuit analogous to that of a transmission line. A detailed description of the TLM is given in appendix 2A.

In the original model, the sheet resistance of the semiconductor directly below the contact is assumed to be the same as the semiconductor layer outside the contact region. This assumption is not however realistic for the contacts studied here as it is likely that the diffusion depth of the annealed Au/Ge/Ni contacts will be greater than the n+ GaAs epi-layer thicknesses (<100 nm) [2.5]. Hence, it is reasonable to assume that the metallurgical reactions that take place during contact annealing will significantly change the sheet resistance of the semiconductor below the contact [2.6,2.9]. Therefore the modified TLM model described by Kellner [2.9] and Reeves and Harrison [2.10] was used in the analysis of all the contacts made to thin epi-layers. In this model, the difference in sheet resistance of the semiconductor layer outside the contact (R<sub>sh</sub>) and that underneath the contact  $(R_{sk})$  is taken into account. should be noted that the resulting values of specific contact resistance obtained using the modified TLM were often more than an order of magnitude greater than those evaluated using the standard models of Berger and Murrmann and Widmann. consistent with the observations made by both Kellner and Reeves and Harrison.

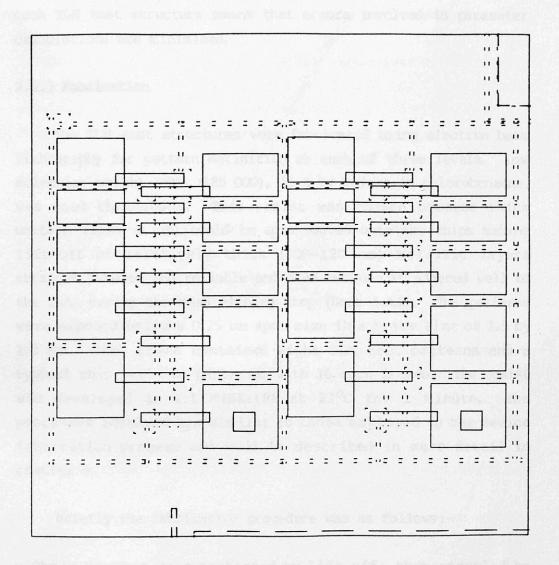

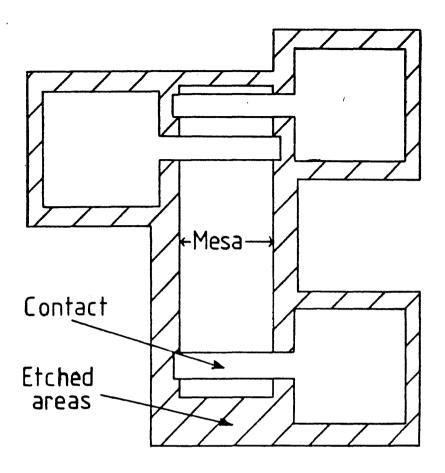

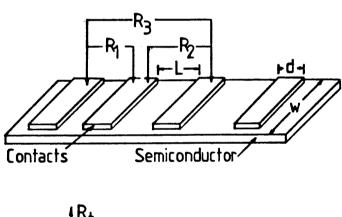

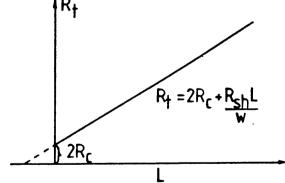

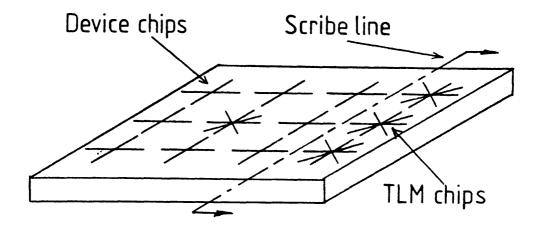

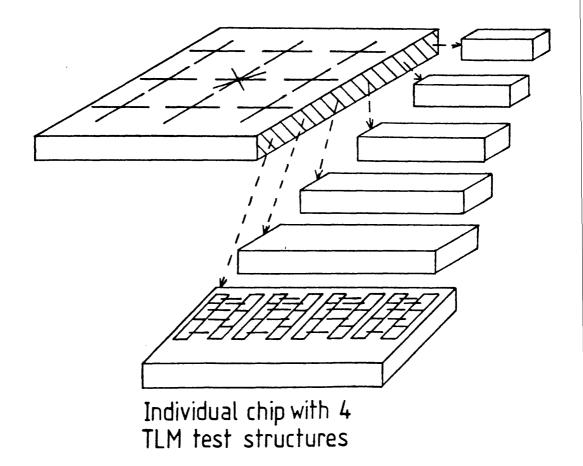

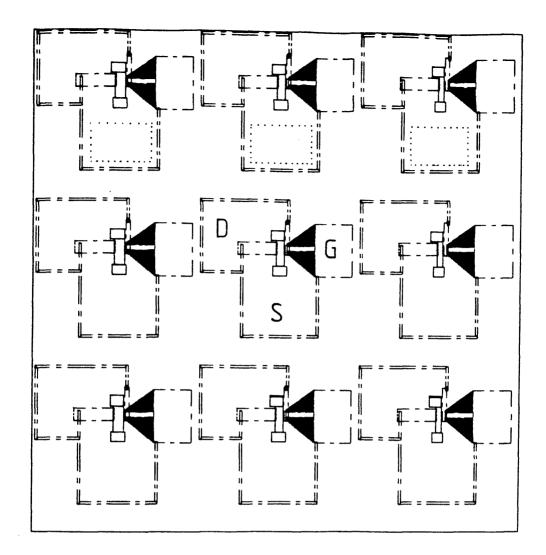

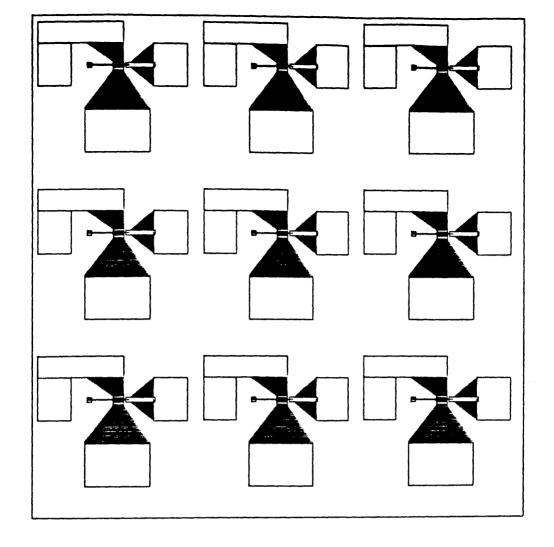

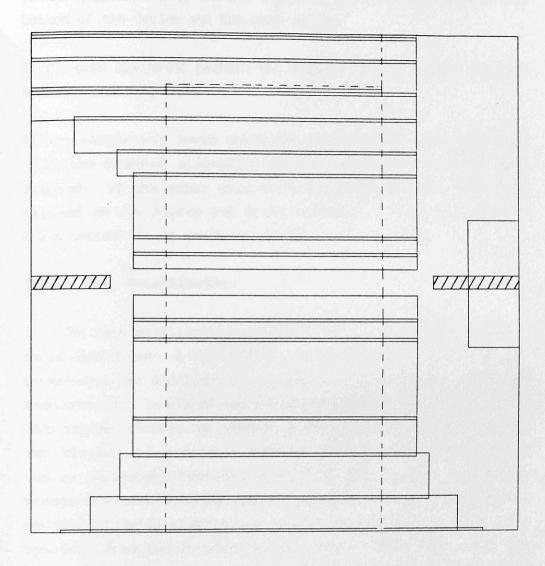

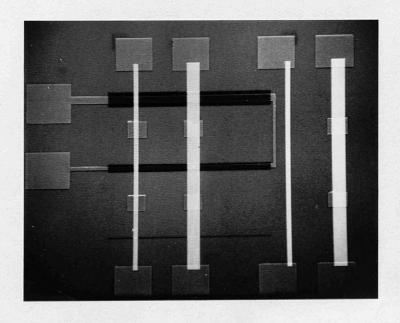

### 2.2.2 TLM Test Structure

The final version of the transmission test structure consisted of a set of ten identical contact stripes patterned over 14 or 20µm wide mesas of n<sup>+</sup> GaAs (fig 2.2). These contacts extended from the mesa to larger pads approximately 100 µm square which were used for probing. The distance between the contacts (L) varied in increments of about 4 µm from 2 µm up to 38 µm. From the measured resistance values between contacts (R<sub>T</sub>) a graph of R<sub>T</sub> v L with 9 data points could be plotted. Also from the test pattern up to 8 values of the so called contact "end resistance" (R<sub>e</sub>) [2.8-10] could be determined from groups of three contacts. R<sub>e</sub> is defined as the potential at the end of a contact divided by the current flowing into that contact (see

==== Mesa Isolation Channels

Ohmic Contact Metallisation Pattern

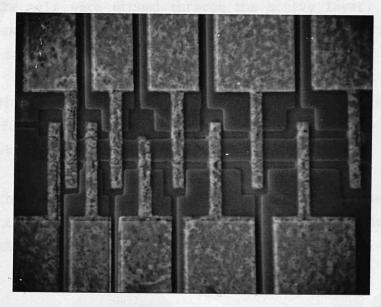

Fig. 2.2 (a) Mesa isolation and contact patterns for TLM test chips and (b) an SEM micrograph of a completed test structure.

App. 2A). The relatively large number of measurements taken from each TLM test structure means that errors involved in parameter calculations are minimised.

#### 2.2.3 Fabrication

The TLM test structures were fabricated using electron beam lithography for pattern definition at each of three levels. molecular weight PMMA (185 000), 15 % by weight in chlorobenzene. was used throughout. This resist was chosen because thick uniform films (1 µm) could be spin coated onto the chips making lift-off of relatively thick (100-120 nm) metallic layers straight forward and reliable and also because it adhered well to the GaAs during the mesa etching step (Sect 1.4.2). were exposed using a 0.25 um spot size in a frame size of 1.5 by 1.2 mm. Each frame contained eight TLM test patterns and a typical chip would be patterned with 16 such frames. The resist was developed in 1:1 MIBK:IPA at 23°C for 1 minute. processes involved are similar to those employed in the device fabrication process and will be described in more detail in chapter 4.

Briefly the fabrication procedure was as follows:-

- Ohmic markers were patterned by lift-off, then annealed to produce low resistivity probing pads to be used in the mesa isolation step.

- Channels were etched through the active layer, using a resist mask, to isolate probing pads and to define the mesas between contacts.

- The ohmic contacts were defined using lift-off. The GaAs wafers were scribed and broken up into chips containing 4 TLM test structures 2 wide and 2 narrow mesas.

- The chips were individually annealed and the measurements for contact analysis made using an HP 4145A semiconductor parameter analyser and probing system.

Some of the earlier work on ohmic contacts was done on less refined TLM structures consisiting of only 5 or even 3 contacts. However, all of the results for the final analysis of low temperature contacts to thin GaAs epi-layers were obtained from structures with 10 contacts per mesa and the final result obtained from each annealed chip was the averaged values obtained from the 4 test structures on that chip.

## 2.3 Annealing

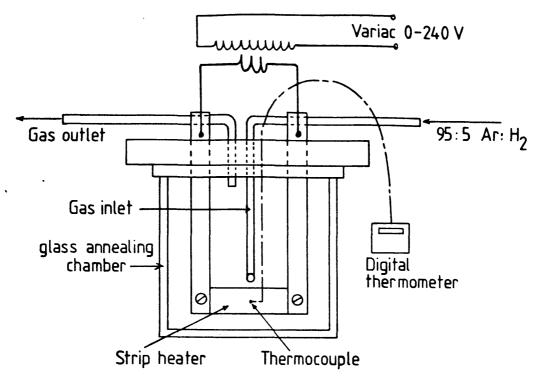

All of the samples were annealed on a strip heater in a reducing atmosphere of 95:5 Ar:H<sub>2</sub>. Figure 2.3 is a schematic of the annealing furnace. Before annealing the chamber was flushed out for at least 2 minutes with the reducing gas. During annealing however, the gas flow was reduced, but not cut-off altogether, so that a positive Ar:H<sub>2</sub> pressure was maintained in the chamber. This pressure was crudely monitored by observing the gas outlet through a bubbler. Annealing was carried out when the water level in the outlet tube was about 2 cm below the level of the water in the flask. The reduction in gas flow was essential to maintain a uniform temperature during the annealing.

The temperature of the strip heater, which consisted of a 2 cm wide strip of either iron or tungsten, was manually controlled using a variac to alter the current through the strip. A thermocouple, connected to a digital thermometer was used to measure the temperature of the strip. The samples, which were typically only 0.5 mm square were placed as close to the thermocouple as possible during the anneal as the temperature variation over the strip, particularly if it had been used for several weeks, was significant. If larger samples (e.g. 5 mm device chips) were being annealed the thermocouple was sometimes placed on the surface of the chip itself if a suitable position, such as a faulty exposure site, could be found.

When several samples were to be annealed at different temperatures it was often convenient to calibrate the temperature of the strip heater to the variac setting before annealing the samples. This was not a one-off procedure as the calibration varied from day to day depending on the metal and dimensions of

Fig. 2.3 Schematic representation of the furnace used for annealing ohmic contacts to GaAs.

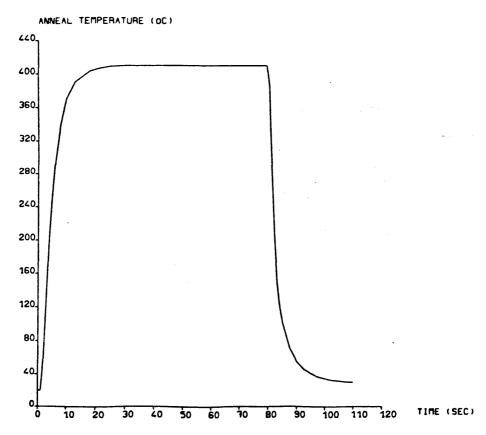

Fig. 2.4 Graph of temperature versus time for a typical 1 minute anneal cycle. The temperature rise and fall times are about 20 and 30 seconds respectively.

the strip heater as well as the positioning of the thermocouple and gas inlet pipe.

The annealing furnace has a very rapid temperature response cycle. The plot in figure 2.4 shows a typical temperature versus time curve obtained by connecting the thermocouple output to a chart recorder during a 60 second anneal. It can be seen that fast temperature rise and fall times (20 and 30 seconds respectively) could be achieved. This high heating and cooling rate is thought to be important in the production of contacts of low resistivity [2.5,2.11,2.12]. The temperature fluctuation at the peak annealing temperature could be held to +/- 5 °C without any difficulty when the gas flow was reduced as described above.

#### 2.4 AuGe Contacts

#### 2.4.1 Thin Epi-layer v Bulk Substrate

It was found early on in the work on ohmic contacts that the fabrication of ohmic contacts to very thin ( < 100nm) n<sup>+</sup> GaAs epi-layers was significantly different to the fabrication of contacts to bulk GaAs substrates with similar doping levels. Initially arrays of gold germanium dots (12 % Ge by weight) 100nm thick were patterned on various substrates using photolithography and lift-off. The substrates were:-

- a) 50nm MOCVD grown n<sup>+</sup> GaAs (1.5.10<sup>18</sup> /cm<sup>3</sup>) on an AlGaAs heterostructure similar to those described in chapter 6 for membrane fabrication (grown at Sheffield University).

- b) 80 nm n<sup>+</sup> GaAs  $(2.3.10^{18} / \text{cm}^3)$  as above.

- c) Bulk  $n^+$  GaAs  $(10^{18} / cm^3)$ .

After the AuGe dots were defined the samples were scribed then broken into smaller chips, each containing several dots. The chips were then annealed at temperatures in the range 200 to  $400^{\circ}$ C and for durations of 0 to 18 minutes. The 0 minute anneal means that the time spent at the annealing temperature was as short as possible. In other words the sample was heated up to

annealing temperature then the current to the heater was immediately cut off.

The AuGe dots were probed and the I/V characteristics observed on a curve tracer. At this stage the contact was considered ohmic if, when a voltage was applied between two dots, the resulting I/V curve had linear characteristics in the voltage range -5 to +5 V. No attempts were made in these early experiments to analyse the contacts using TLM test srutuctures.

#### 2.4.2 Results

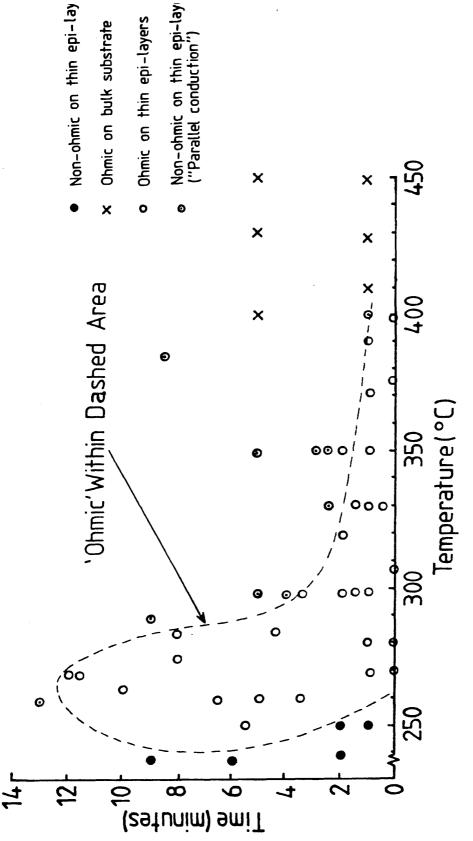

The graph in figure 2.5 shows which anneal temperatures and times produced ohmic contacts to the various substrates. There is a distinct area on this graph within which all of the contacts on the epitaxial material exhibited linear I/V characteristics. This "ohmic" region extends right down to temperatures as low as 250°C. It was interesting to observe that if the annealing times were too long the contacts no longer produced linear curves. For example at 320°C a 1 minute anneal produced ohmic contacts to the epitaxial GaAs wafers whereas a 3 minute anneal did not. The curves obtained with longer anneal times were generally linear at the origin but there was a point of inflection at about 2 volts.

It was not understood at the time of this experiment why ohmic contacts could be obtained with a 1 minute anneal but not with a 3 minute anneal. On reflection however, it seems likely that as most of the measurements were made on GaAs/AlGaAs heterostructures, the contact material had penetrated through the active layer and into the underlying AlGaAs layer. It is therefore possibile that there was some parallel conduction through the AlGaAs layer which would lead to the inflections observed in the I/V characteristics [2.13,2.14] which resulted in the contacts being labelled non-ohmic.

This initial test did show that ohmic contacts could be formed to thin GaAs epi-layers at temperartures a lot lower than the 420 to 450  $^{\rm O}$ C required for contact formation to bulk n<sup>+</sup> material.

temperatures which could be used to form ohmic contacts to thin n GaAs layers. In this case "ohmic" is defined as linear I∕V Fig 2.5 Graph showing the range of anneal times and anneal characteristics.

#### 2.4.3 First TIM Measurements

The first transmission line model test patterns were fabricated on 200 nm thick GaAs epi-layers (n=1.5  $\times$  10<sup>18</sup> /cm<sup>3</sup>) with a nominally undoped buffer layer between the active layer and the semi-insulating substrate. The material was grown using vapour phase epitaxy (VPE) at Plessey (Caswell). The test pattern consisted of three identical 18  $\mu$ m wide contacts patterned over a 75  $\mu$ m wide mesa of active material (Fig. 2.6). The distances between the contacts were 15 and 150  $\mu$ m. In this original structure, the active layer below the probing pads was removed during the mesa isolation step. The test structures were fabricated in a similar way to the ultimate TLM structure summarised in section 2.3.

The initial experiments involving the TLM were to determine how the specific contact resistance of AuGe contacts varied with anneal temperature and anneal time. Test structures were fabricated with AuGe contacts 120 nm thick. It should be noted that in the early experiments no special cleaning of the GaAs surface was carried out before contact metallisation and that no nickel was used to improve the contact resistivity [2.15].

Individual TLM test structures were annealed in the furnace described in section 2.3. After annealing the resistances between contacts were computed from the slope of the I/V curves. The contact end resistance  $R_{\rm e}$  which is an essential parameter in the modified TLM was determined by both of the methods described in appendix 2A. The first of these methods was to measure the resistance between contacts 1 and 2, 2 and 3 and 1 and 3 ( $R_{\rm l}$ ,  $R_{\rm l}$  and  $R_{\rm l}$  respectively) then compute  $R_{\rm l}$  from the equation

$$R_e = 0.5 (R_1 + R_2 - R_3).$$

The second method was to pass a current between contacts 1 and 2 and measure the voltage drop between contacts 2 and 3. The value of  $R_{\rm e}$  was then determined by dividing the measured voltage by the input current.

Fig 2.6 Initial TLM structure consisting of a 75  $\mu m$  wide mesa with 18  $\mu m$  contact stripes separated by 15 and 150  $\mu m$  .

The sheet resistance of the semiconductor layer outside the contacts (R<sub>sh</sub>) and the contact resistance (R<sub>c</sub>) were determined directly from the measured resistance values and the physical dimensions of the test structure. Then, using the modified transmission line model [2.9,2.10], the specific contact resistance (A) and the sheet resistance of the semiconductor layer directly below the contact  $(R_{sk})$  were computable using the determined values of  $R_e$ ,  $R_c$  and  $R_{\rm sh}$ . A program (RESCAL) was written to determine all the contact parameters from measured In this simplified test pattern only the measured resistance between contacts, the  ${\rm R}_{\!_{\rm P}}$  value and the spacing between contacts were input to the program. With the more complex test structure described in Sect. 2.2.2, a graph of resistance between contacts v contact separation was first of all plotted. Then, after fitting the best curve to this data, two reference points could be taken from the curve and input to RESCAL along with an average value of R<sub>e</sub> determined from up to eight measurements per sample.

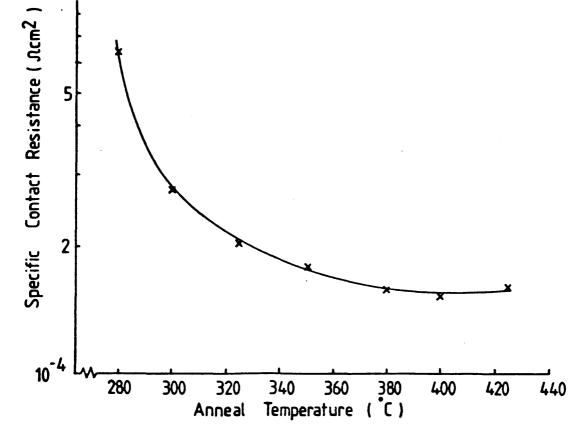

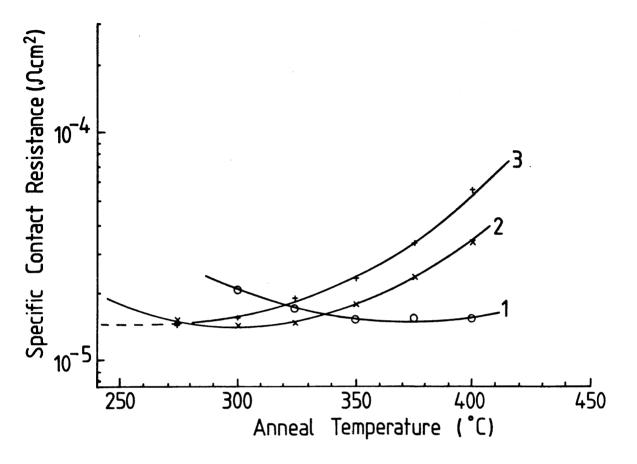

# 2.4.4 Specific Contact Resistance v Anneal Temperature

Table 2.1 contains the measured and computed results from samples annealed at different temperatures (60 seconds). The  $\rm R_{\rm e}$  values were determined using both of the methods described above. It can be seen that the sheet resistance of the semiconductor layer outside the contact  $\rm (R_{\rm sh})$  is constant over the entire temperature range studied. The sheet resistance under the contact  $\rm (R_{\rm sk})$  does however vary with the anneal temperature. Broadly speaking, the lower the value of specific contact resistance obtained  $(\rho_{\rm c})$ , the lower the value of  $\rm R_{\rm sk}$ . The fluctuations in  $\rm R_{\rm sk}$  are due to errors in the measured value of  $\rm R_{\rm e}$ . This is the main reason why the simple test structure of this experiment, where only one  $\rm R_{\rm e}$  measurement can be made, was subsequently replaced by the complex test structure (Sect. 2.2.2) where up to 8 measurements of  $\rm R_{\rm e}$  can be made.

In this experiment the lower values of  $\rho_{\rm C}$  (10<sup>-4</sup> ohm.cm<sup>2</sup>) were obtained at higher annealing temperatures (Fig. 2.7). The reduction in sheet resistance below the contact is caused by the reactions which take place during annealing. It is likely that

Table 2.1

| T           | R <sub>1</sub> | R <sub>2</sub> | R <sub>3</sub> | Re    | R <sub>sh</sub> | R <sub>C</sub> | Pc  | R <sub>sk</sub> |

|-------------|----------------|----------------|----------------|-------|-----------------|----------------|-----|-----------------|

| 280         | 140            | 380            | 430            | 45.0  | 133             | 56.6           | 6.6 | 101.0           |

|             |                |                |                | *42.0 |                 |                | 6.3 | 129.0           |

| 300         | 65             | 285            | 314            | 18.0  | 122             | 20.3           | 2.5 | 19.4            |

|             |                |                |                | *16.0 |                 |                | 2.3 | 37.2            |

| 325         | 64             | 280            | 314            | 14.5  | 120             | 20.0           | 2.2 | 48.5            |

|             |                |                |                | *11.0 | į               |                | 1.9 | 83.8            |

| 350         | 50             | 280            | 307            | 11.5  | 128             | 12.2           | 1.6 | 6.0             |

|             |                |                |                | *11.5 |                 |                | 1.6 | 6.0             |

| 380         | 50             | 282            | 312            | 10.0  | 129             | 12.1           | 1.4 | 18.2            |

|             |                |                |                | * 9.5 |                 |                | 1.4 | 22.7            |

| <b>40</b> 0 | 46             | 265            | 291            | 10.0  | 121             | 10.8           | 1.4 | 7.0             |

|             |                |                |                | * 9.5 |                 |                | 1.3 | 11.4            |

| 425         | 50             | 270            | 300            | 10.0  | 122             | 12.8           | 1.5 | 24.2            |

|             |                |                |                | *10.0 |                 |                | 1.5 | 24.2            |

T is in  $^{\rm O}$ C,  ${\rm R_1,\,R_2,\,R_3,\,R_e}$  and  ${\rm R_c}$  are in ohms  ${\rm R_{sh}}$  and  ${\rm R_{sk}}$  are in ohms/square  ${\rm P_c}$  is in ohm.cm $^2$  xl0 $^{-4}$  \* indicates  ${\rm R_e}$  measured using V/I method.

$(e_{1}, V_{1}, V_{2}) = (e_{2}, e_{3}, e_{$

at higher temperatures more Ge will have diffused from the contact into the underlying semiconductor increasing the doping level by more than an order of magnitude [2.9,2.10], hence, the reduction in sheet resistance.

This lowering in sheet resistance below the contact illustrates why the standard TLM model gives lower values for the specific contact resistance than the modified TLM. In order to get contact resistances of the order of  $10^{-5}$  ohm.cm<sup>2</sup> the GaAs doping level should be around  $5.10^{19}$  /cm<sup>3</sup> [2.6]. In the case of contacts to thin epi-layers, as already discussed, it is likely that the whole of the semiconductor layer will be modified during contact annealing (lower sheet resistance). If the layer below the contact is not assumed to be modified, then, in order to satisfy the measurements made on the TLM test structure, the calculated values of specific contact resistance would appear to be smaller than they actually were.

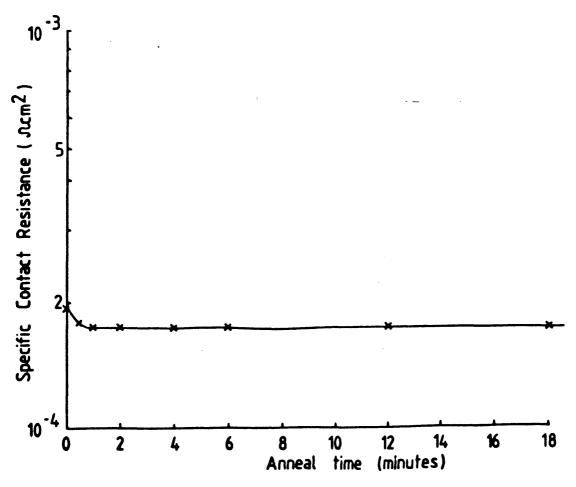

# 2.4.5 Specific Contact Resistance v Anneal Time

A second experiment was carried out to find out how the specific contact resistance of the AuGe contacts varied with anneal time. A set of TLM samples, fabricated in the same way as those in the previous test, were annealed for different times at  $350\,^{\circ}\text{C}$ . The graph of fig. 2.8 shows that  $\rho_{\text{C}}$  is in fact more or less constant for anneal times from O (instantaneous anneal) up to 18 minutes. The inflections observed in the I/V curves of the samples fabricated on GaAs/AlGaAs heterostructures with longer anneal times were not present in this test on 200nm n<sup>+</sup> epi layers on undoped buffers. This confirmed that the inflections observed previously were due to parallel conduction through the AlGaAs layer and not to a deterioration in the contact quality.

In all subsequent experiments the anneal time was chosen to be 1 minute since there was no obvious advantage in annealing the samples for any longer. 1 minute was selected in preference to say 15 seconds to allow the completion of the reactions which take place during annealing. It was speculated by Ogawa [6.5] that contacts formed at low temperature would deteriorate with time because the reactions would be incomplete. However, the

Fig 2.7 Specific contact resistance versus annealing temperature for AuGe contacts to 200 nm  $10^{18}$  GaAs. The anneal time was 60 seconds for each sample.

Fig 2.8 Specific contact resistance versus anneal time for AuGe contacts annealed at 350 °C.

results of this experiment indicate that the reactions are completed in a few seconds since there is no improvement in resistivity when longer anneal times are used. In later work on AuGe contacts with Ni and Au capping layers, low temperature contacts annealed for 1 minute were remeasured some 8 weeks after they were first tested and it was found that there had been no deterioration of the contacts in this time.

# 2.5 AuGe/Ni/Au Contacts

The minimum values of specific contact resistance (10<sup>-4</sup> ohm.cm<sup>2</sup>) obtained in these initial experiments was high compared with other reported values on similarly doped material measured using the modified TLM [2.9,2.10]. To improve the resistivity a nickel layer was incorporated into the contacts since the nickel improves wetting and enhances the solubility of the GaAs. Nickel does have the disadvantage that it is a fast diffuser and a compensating acceptor [2.15,2.16]. A gold capping layer typically 20 nm thick was also added to reduce the sheet resistance of the metal contact.

It was also found that cleaning the GaAs immediately before the contact metallisation improved the resistivity of the contacts. A 60 second clean in 5 % ammonia solution prior to metal evaporation reduced  $\rho_{\rm C}$  by about a factor of five and also improved the adhesion of the contacts to the GaAs. It is believed that the ammonia solution etches away any surface oxide, thus improving the contact resistance.

#### 2.5.1 Low Temperature Annealing

The initial results from contacts including nickel showed that low resistivity contacts could be formed with annealing temperatures in the range 300 - 320  $^{\rm O}{\rm C}$  (Sect. 2.5.3). Further experiments were therefore carried out to see if the composition of the AuGe/Ni/(Au) contacts could be optimised for low temperature annealing (Sect. 2.5.4,5). Ultimately contacts with  $\rho_{\rm C}$  around 10<sup>-5</sup> ohm.cm<sup>2</sup> were obtained with an anneal temperature of 300  $^{\rm O}{\rm C}$ .

#### 2.5.2 Test Structures

Experiments were carried out to study what effect the nickel concentration had in AuGe/Ni/Au contacts to thin GaAs epi-layers and to determine if a suitable composition could be found for low temperature annealing. The TLM structures described in Sect. 2.2.2 (fig 2.2), consisting of 10 contacts on mesas 14 and 20 µm wide, were fabricated on material consisting of an 85nm n<sup>+</sup> GaAs (n=10<sup>18</sup>/cm<sup>3</sup>) active layer and a 1 µm nominally undoped buffer layer grown by VPE on a semi-insulating substrate. Initially a 4 X 5.2 mm chip was patterned with 9 exposures, each containing 8 TLM patterns. The frame size for each exposure was 1.2 X 1.5 mm. When the chip was completely processed, including mesa isolation and ohmic metallisation, the chip was scribed and broken into 1 X 0.5 mm samples, each with 4 test structures, for individual annealing.

Immediately before loading the samples into the vacuum system for contact metallisation, the GaAs surface was cleaned by immersing the samples in 5 % ammonia solution. The samples were then rinsed in de-ionised water and thoroughly blown dry in a stream of nitrogen.

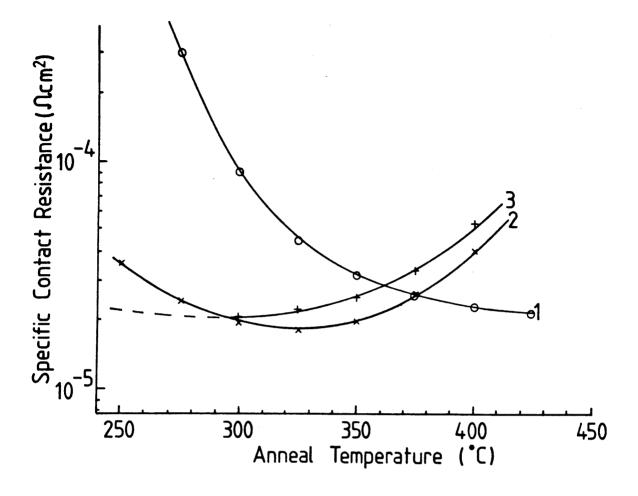

#### 2.5.3 Varying The Nickel Concentration

The first test was to determine what effect the nickel concentration in the composite metal contacts had on the annealed contacts. TLM structures were fabricated which were metallised with 92nm AuGe / X nm Ni / 20 nm Au, where X (the nickel thicknesses) were 12, 25 and 35 nm. The percentages of nickel to AuGe by weight were 6.4, 12.3 and 17.5 % respectively. A standard composition for annealing contacts at high temperatures consists of 100 nm AuGe (88:12) with approximately 5 % Ni by weight and an Au capping layer to reduce the sheet resistance of the contact metal [2.15]. The samples were annealed at temperatures in the range 250 - 425 °C. To limit the number of variables, and since the alloying process was shown to be almost independent of annealing time (sect 2.4.5), all the samples were annealed for 1 minute. After annealing resistance values were measured from the test chips and the average value of specific

contact resistance computed from the 4 test patterns on each of the samples.

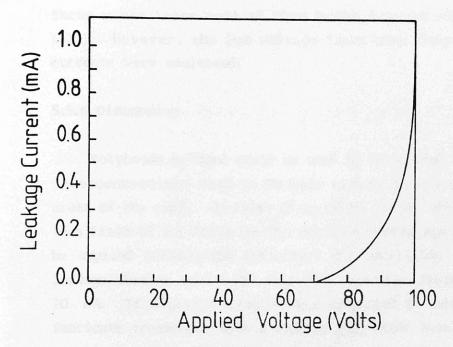

Fig. 2.9 contains a graph of specific contact resistance versus anneal temperature for contacts with each of the three nickel concentrations. Curve 1 was plotted for contacts containing 6.4 % Ni (Ni to AuGe by weight) and shows a minimum value of  $2.10^{-5}$  ohm.cm<sup>2</sup> when the annealing temperature was  $420^{\circ}$ C. This is a standard temperature for contact formation to bulk GaAs [2.15] which is reasonable since the composition of the contacts of curve 1 was close to the standard.

Curve 2 however (12.3 % Ni), shows a minimum in specific contact resistance, similar in value to the minimum of curve 1 (2.10<sup>-5</sup> ohm.cm<sup>2</sup>) at an annealing temperature of 320 °C. Specific contact resistances in the order of 2.10<sup>-5</sup> ohm.cm<sup>2</sup> were also obtained from some of the contacts containing 17.5 % Ni (curve 3) annealed at temperatures as low as 250 °C. Unfortunately, the number of low resistivity contacts formed at these very low temperatures was less than the number of contacts with extremely high resistivities.

The curves in fig. 2.9 show that the annealing temperature of AuGe/Ni/Au contacts can be reduced by over  $100^{\circ}\text{C}$  by increasing the proportion of nickel in the composition. The specific contact resistances obtained in the contacts with a high proportion of nickel annealed at  $300 - 320^{\circ}\text{C}$  were as low as were achieved using a contact of standard composition annealed at  $420^{\circ}\text{C}$ . However, when the anneal temperatures are too low (250- $300^{\circ}\text{C}$ ), low resistivity contacts cannot be made reliably even if the nickel concentration is increased further. Therefore, an annealing temperature of  $300 - 320^{\circ}\text{C}$  was considered to be the lowest practical temperature for contact formation.

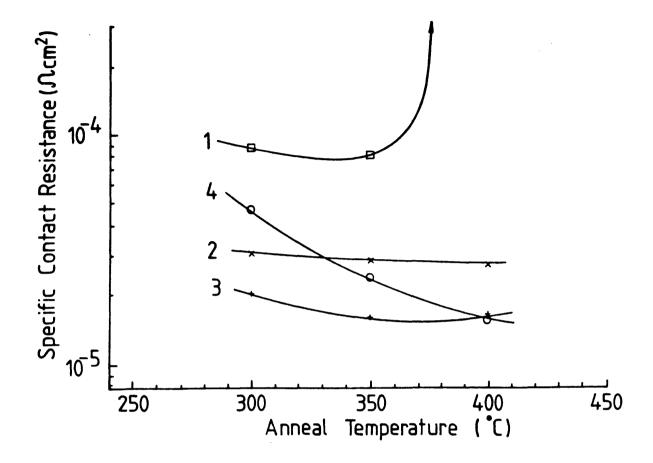

#### 2.5.4 Optimum AuGe Thickness

A second set of experiments was carried out to find out if there is an optimum AuGe thickness which would give low resistivity contacts when annealed at low temperatures. TLM test structures were fabricated on the same material as the previous

Fig 2.9 Specific contact resistance versus anneal temperature for contacts with the following compositions:-

Curve 1 92 nm AuCe (88:12), 12 nm Ni (6.4% by weight), 20 nm Au.

Curve 2 " " 25 nm Ni 12.3% " " " "

Curve 3 " " 35 nm Ni 17.5% " " "

test chips. Four different AuGe thicknesses were used in the metallisation of the contacts: 30, 63 75 and 85 nm. To complete the metallisation, a nickel layer equivalent to 10 % of the AuGe thickness (4.5 % weight) and a gold capping layer 20 nm thick were evaporated. Annealing was once again carried out on individual 0.5 x 1 mm chips containing 4 TLM patterns.

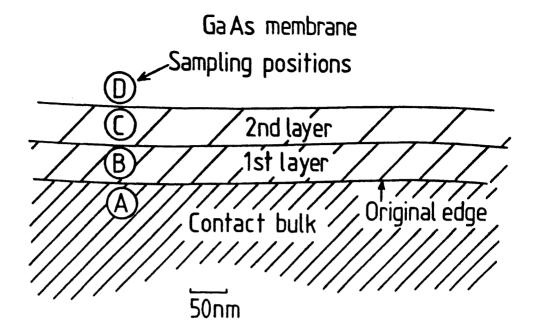

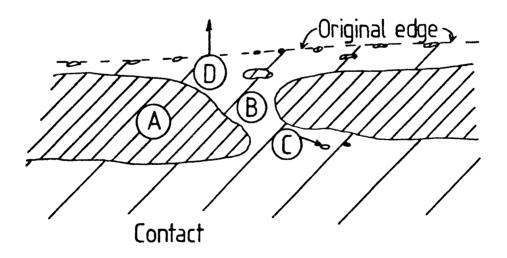

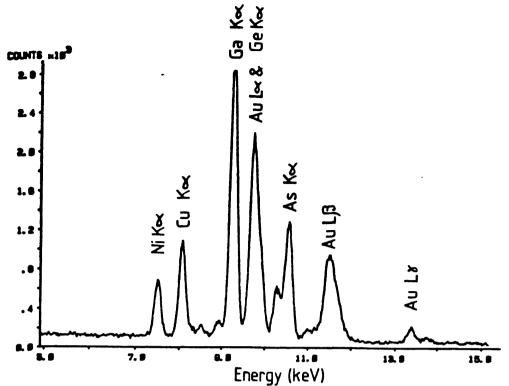

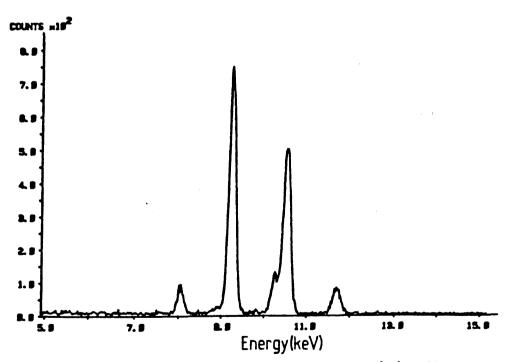

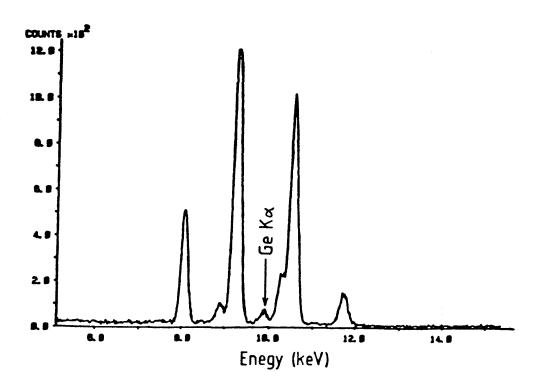

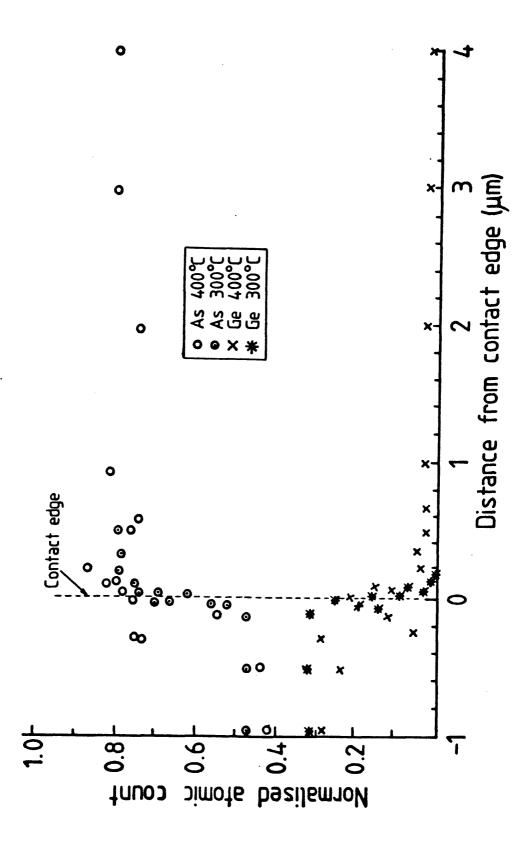

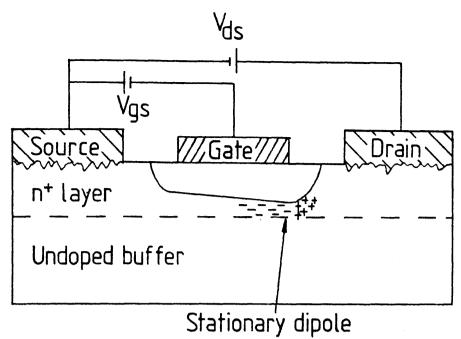

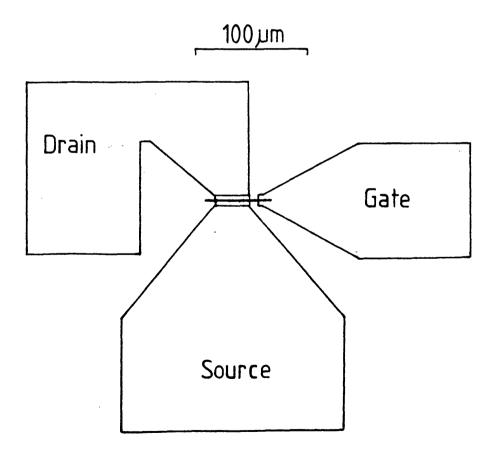

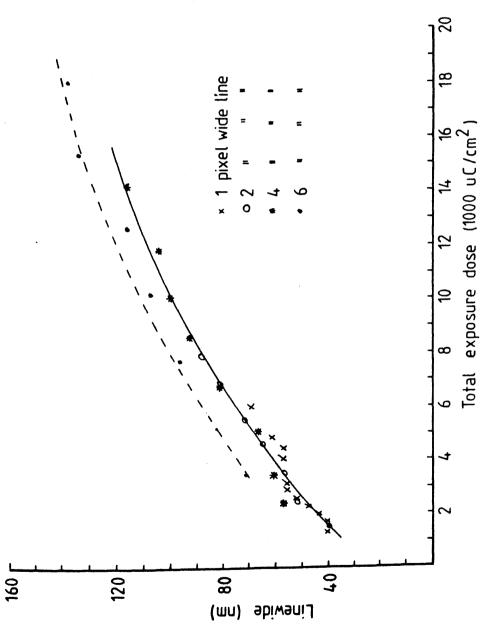

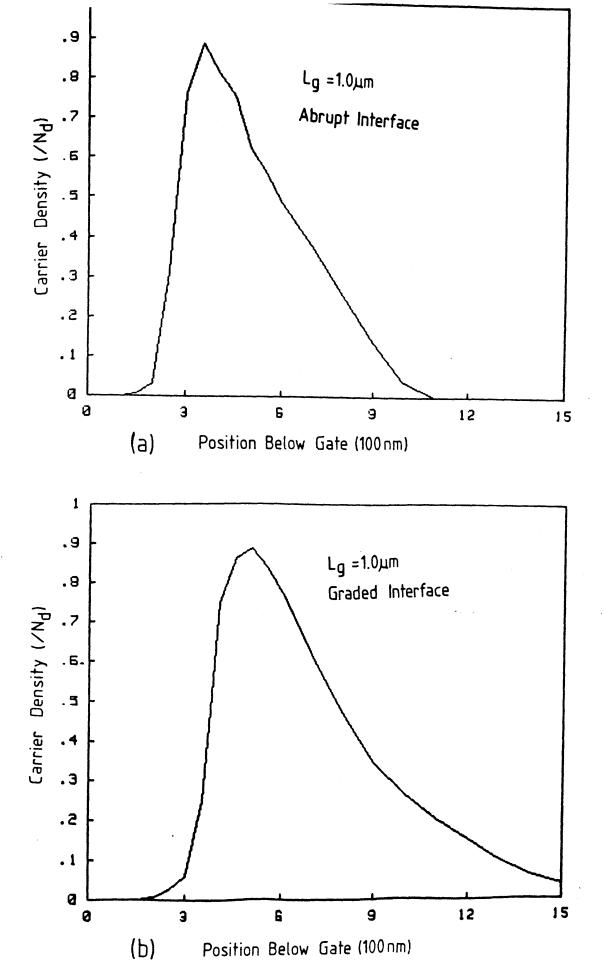

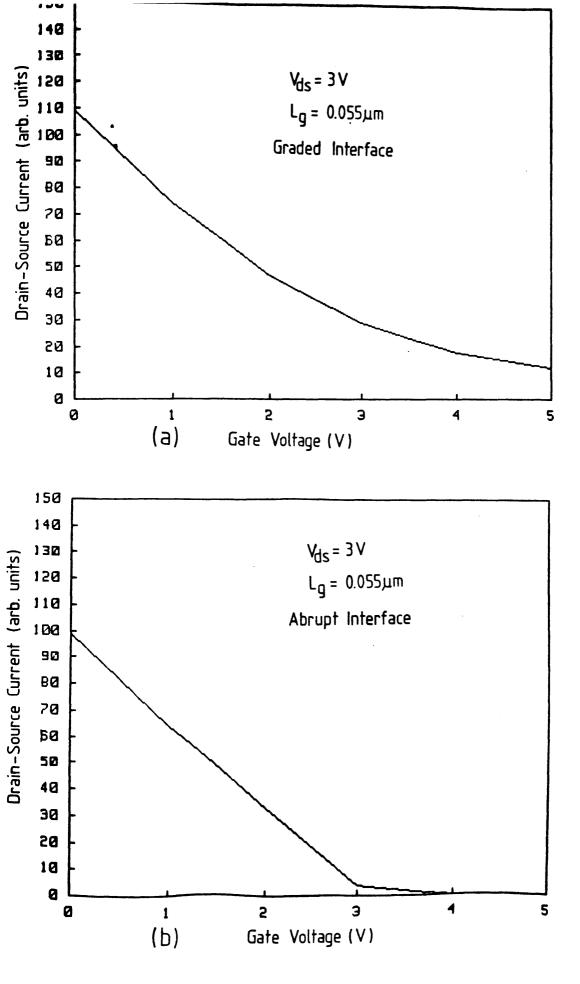

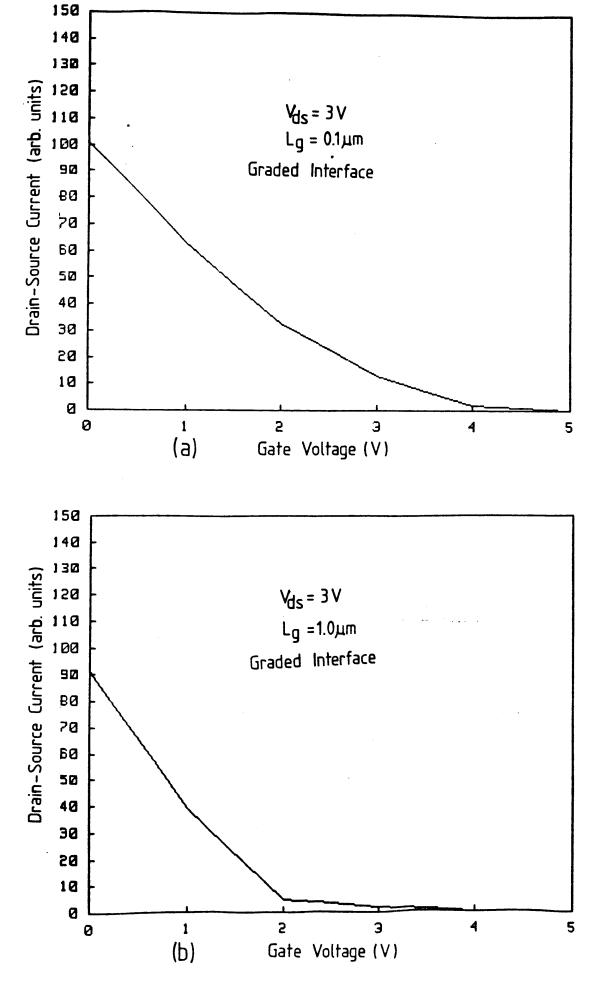

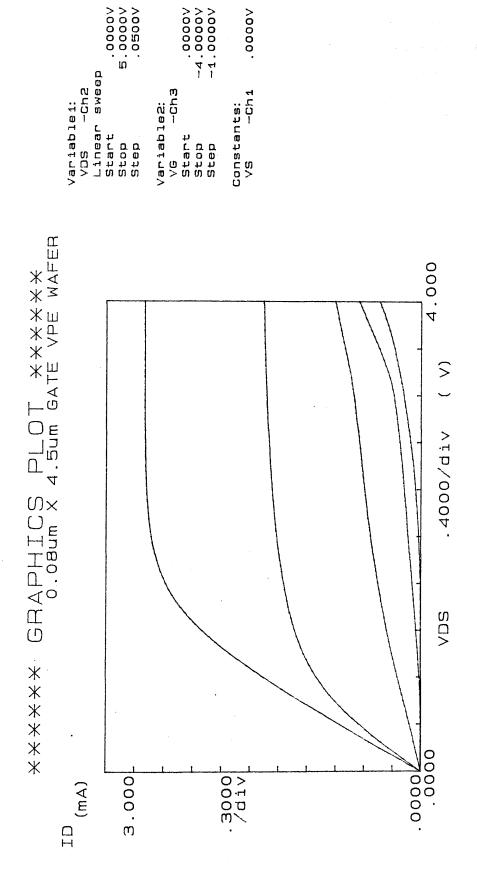

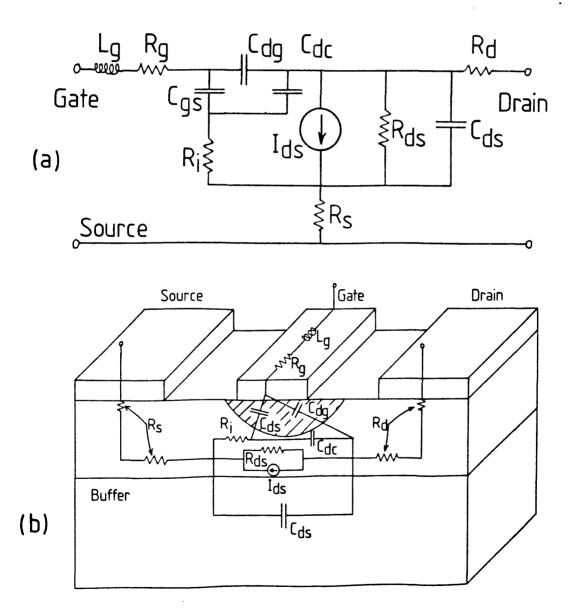

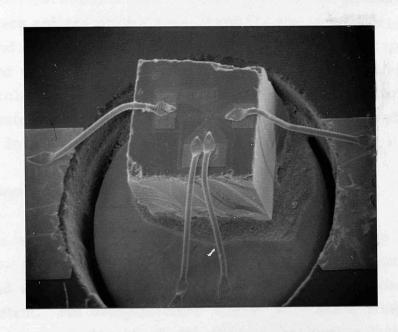

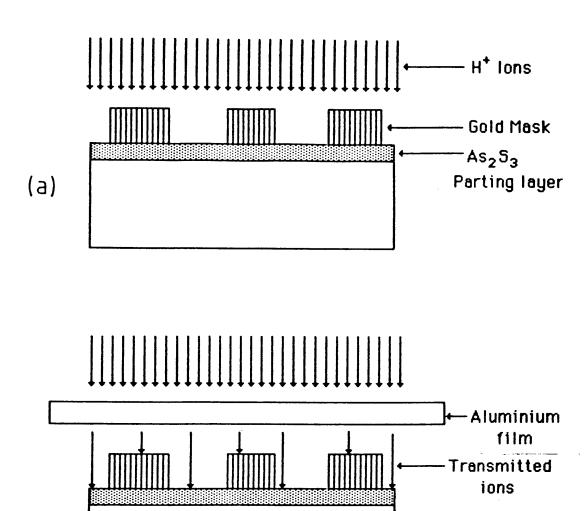

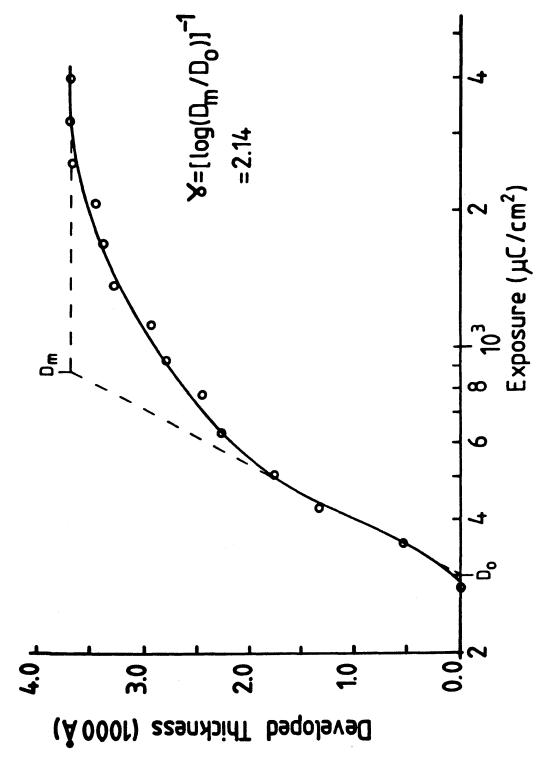

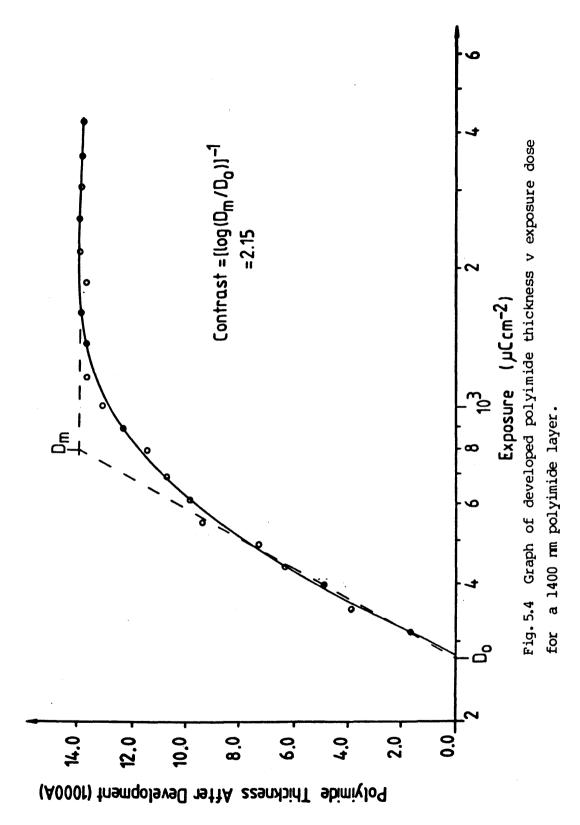

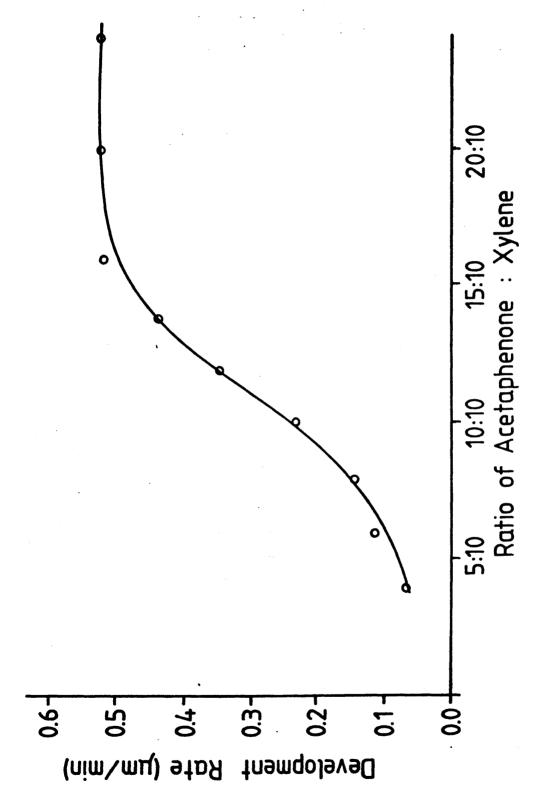

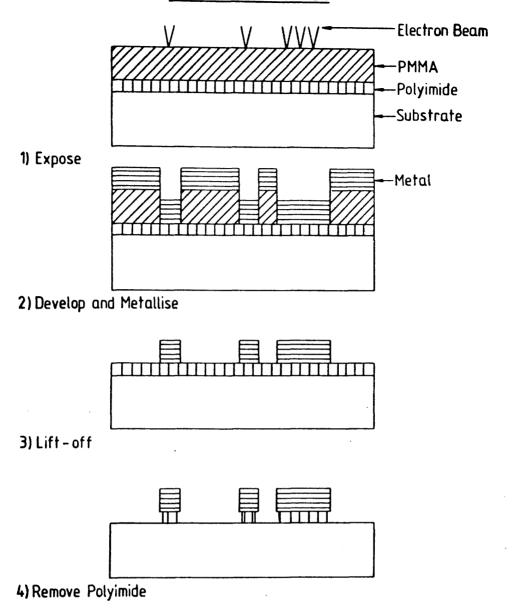

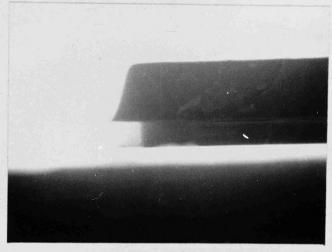

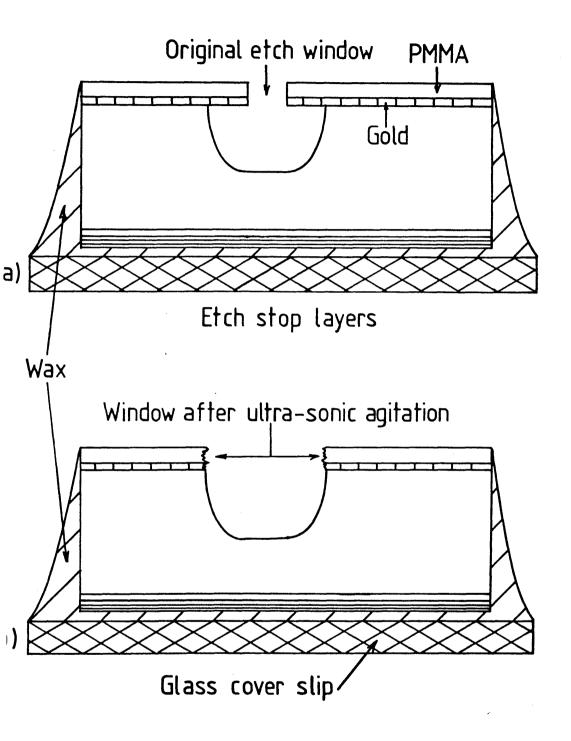

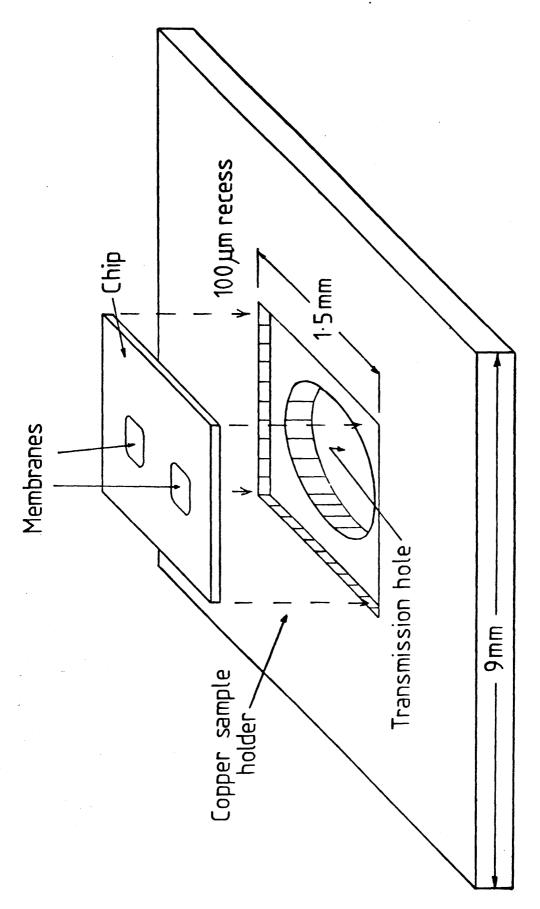

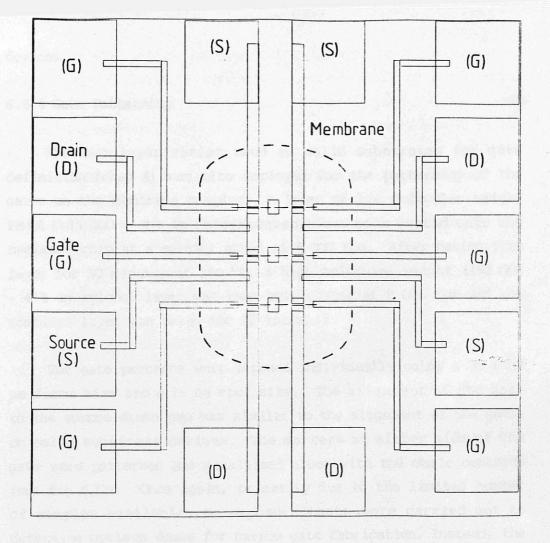

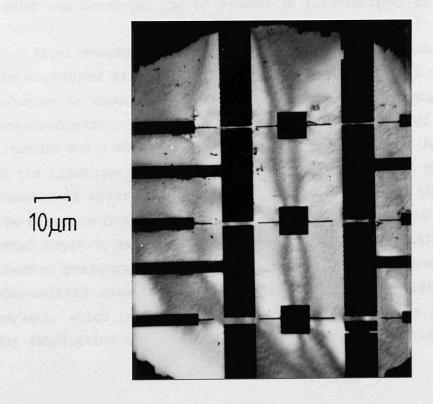

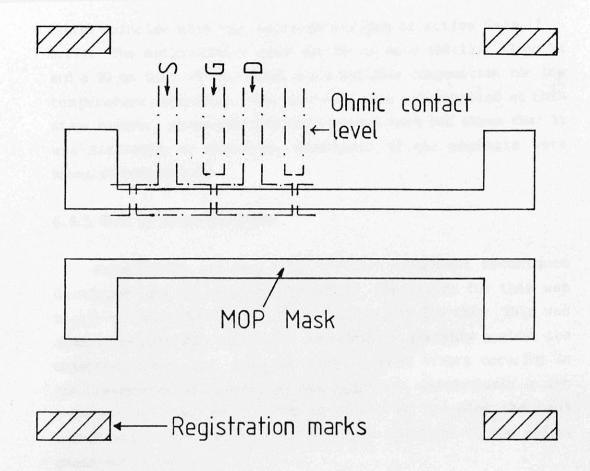

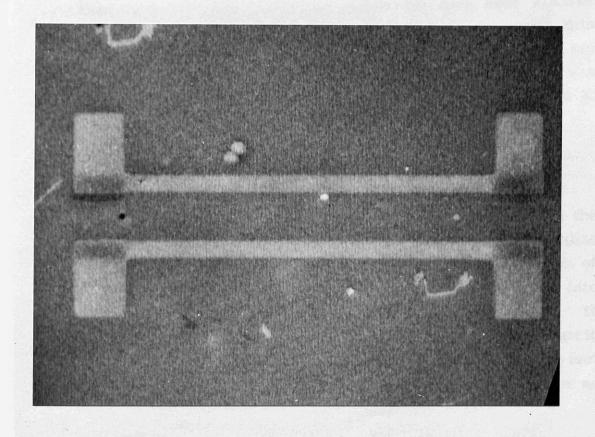

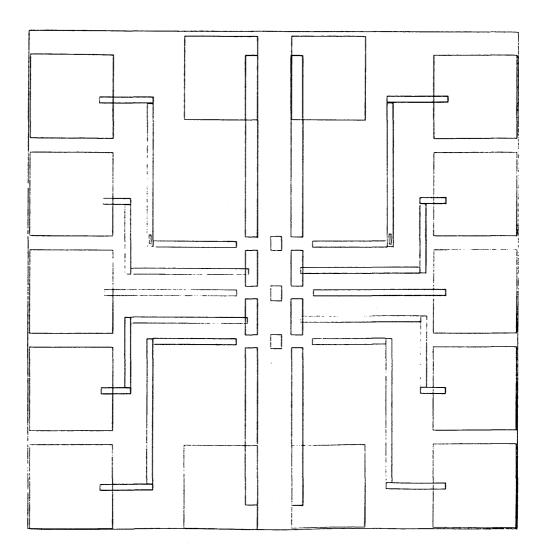

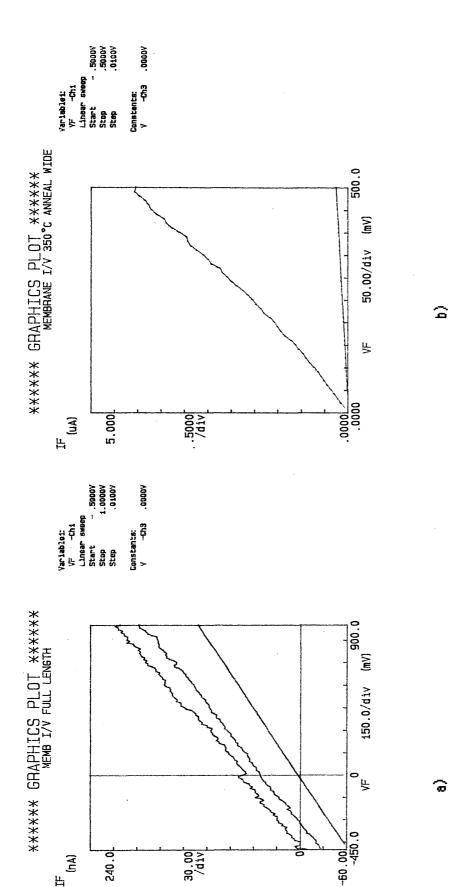

The graph of fig. 2.10 shows the specific contact resistances obtained from each of these samples annealed at temperatures from 300 to 400 °C. From this graph it can be seen that curve 3 with 75 nm of AuGe has the lowest specific contact resistance (minimum 1.4 X 10<sup>-5</sup> ohm.cm<sup>2</sup>) over the temperature range studied. The minimum value of specific contact resistance was not significantly lower than any previously obtained values. Extrapolation of curve 4 (85 nm) suggests that this composition may produce lower contact resistances when annealed at temperature greater than 400 °C. Nevertheless, the optimum AuGe thickness for low temperature annealing of ohmic contacts to thin n<sup>+</sup> GaAs epi-layers was taken to be 75 nm.