Kriama, Abdulbast (2011) 3D complex shaped- dissolvable multi level micro/nano mould fabrication. PhD thesis.

http://theses.gla.ac.uk/2405/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# 3D complex shaped- dissolvable multi level micro/nano mould fabrication

Abdulbast Kriama

Thesis submitted to the School of Engineering, University of Glasgow,

for the degree of Doctor of Philosophy

University of Glasgow

November 2010

### Acknowledgements

First and foremost I would like to thank the almighty God (ALLAH) for giving me the knowledge, strength and patience to complete this work. May His blessings continue to shower on Prophet Mohammad (peace be upon him). I pray that He continues the same the rest of my life.

I would like to show my sincere appreciation to my advisor, Dr. Graham Green, for his support, encouragement and guidance throughout this work. His knowledgeable insights, outstanding perception and friendly personality showed me not only how to be an engineer, but how to be a man. The experience of working under his supervision in his research group will have profound impact on my future career development. This dissertation work would not have been possible without his continuous support and enthusiasm for applied research. My special thanks go to Dr Phil Dobson for his helping to complete this work

My special gratitude goes to my sponsor the Libyan Embassy in London and the Higher Education Ministry of Libya for giving me the opportunity and the scholarship for my studies. I would also like to acknowledge the funding provided by the School of Engineering, University of Glasgow, in support of conferences attendance.

I wish to thank the wonderful people in the IWNC for their unlimited technical support. Thanks to everyone who helped me in completing this work especially my friends Adel Saad and Ihsan Irthiea.

I sincerely thank my parents and my children: Abdelrahman, Afra, Mohamed and my little Howraa for their unending support, encouragement, patience for more than four years living abroad.

Finally, I want to express my sincere gratitude to my wife, Hanan for her longtime support and unconditional love! She always makes me smile even facing the greatest difficulty.

#### **Abstract**

There is growing interest in the development of fabrication techniques to cost effectively mass-produce high-resolution (micro/nano) 3D structures in a range of materials. Biomedical applications are particularly significant.

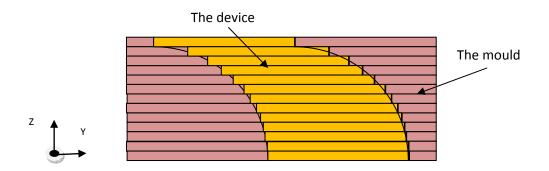

This work demonstrates a novel technique to simultaneously fabricate a sacrificial mould having the inverse shape of the desired device structure and also create the desired device structure using electroplating deposition techniques. The mould is constructed of many thin layers using a photoresist material that is dissolvable and sensitive to UV light. At the same time the device is created in the emerging mould layers using Gold electroplating deposition technique. Choosing to fabricate the mould and the 3D structures in multiple thin layers allows the use of UV light and permits the potential cost-effective realization of 3D curved surfaces, the accuracy and geometric details of which are related to the number of layers used.

In this work I present a novel idea to improve the LIGA process when using many masks to deposit multi thin layer over each other. Moreover, this technique can be utilized to produce a curved surface in the vertical direction with any diameter. Practically, a 2 µm thickness of layer is applied in the proposed technique. However, a layer of 0.5 µm or less can be deposited. An example is provided to explain the novel fabrication process and to outline the resulting design and fabrication constraints. With this technique, any structure could be made and any material used.

The work employs conventional techniques to produce a 3D complex shape. By using conventional techniques with multi layers to produce a 3D structure, many problems are expected to occur during the process. Those problems were mentioned by many researchers in general but have not been addressed correctly. Most researchers have covered those problems by leaving the conventional and using a new technique they invented to produce the required product. However, in my work I have addressed those problems for the first time and I offered a new and effective technique to improve the MEMS technology and make this technology cheaper. This was achieved by using a research methodology requiring a rigorous review of existing processes, as outlined above, then by proposing a concept design for an improved process. This novel proposed process was then tested and validated by a series of experiments involving the manufacture of demo-devices. The conclusion is that this new process has the potential to be developed into a commercially implementable process.

3D complex shaped- dissolvable multi level micro/nano mould fabrication

**Declaration**

This thesis contains no material which has been accepted for the award of any other

degree or diploma, except where due reference is made in the text of the thesis. To

the best of my knowledge, this thesis contains no material previously published or

written by another person, except where due reference is made in the text of the

thesis.

Abdulbast Kriama

Glasgow, 28/02/2011

VI

### Contents

| Acknowledgements                            | II  |

|---------------------------------------------|-----|

| Abstract                                    | IV  |

| Declaration                                 | VI  |

| List of Figures                             | XI  |

| List of table                               | XIV |

| List of Acronyms                            | XV  |

| Chapter 1                                   | 1   |

| Introduction                                | 1   |

| 1.1. Definition of MEMS                     | 2   |

| 1.2. MEMS Application                       | 3   |

| 1.3. Motivation                             | 5   |

| 1.4 Objectives                              | 7   |

| 1.2. Research Program                       | 9   |

| 1.3 Structure of the Thesis                 | 10  |

| Chapter 2                                   | 12  |

| Literature review                           | 12  |

| 2.1. History of the MEMS                    |     |

| 2.1.1. General Historical Overview          | 14  |

| 2.2. Review of MEMS fabrication process     | 23  |

| 2.2.1. General description                  | 23  |

| 2.2.2. Depositing thin film                 | 27  |

| 2.2.3. Electrodeposition                    | 30  |

| 2.2.4. Photolithography                     | 33  |

| 2.2.5. Etching processes                    | 41  |

| 2.2.6. Bulk Micromachining                  | 46  |

| 2.2.7. Surface Micromachining               | 47  |

| 2.2.8. Mould Micromachining                 | 50  |

| 2.3. Comparative study of previous research | 59  |

| 2.3.1. Using UV light instead of X Ray      | 59  |

| 2.3.2. Utilizing three layers               | 61  |

| 2.3.3. Using dry photo resist               | 64  |

|    | 2.3.4. Effect of soft bake process                                     | 67    |

|----|------------------------------------------------------------------------|-------|

|    | 2.3.5. Using sacrificial metallic mould                                | 68    |

|    | 2.3.6. Utilization of a hybrid process                                 | 70    |

|    | 2.3.7. Study of conventional resist and compared with polyimide resist | 73    |

|    | 2.3.8. Other techniques to produce 3D structure                        | 74    |

|    | 2.4. Conclusion                                                        | 80    |

| Ch | apter 3                                                                | 82    |

| Co | ncept design of process                                                | 82    |

|    | 3.1. Introduction                                                      | 83    |

|    | 3.2. Objective                                                         | 84    |

|    | 3.3. Steps of the method                                               | 87    |

|    | 3.3.1. Preparing the photo resist                                      | 88    |

|    | 3.3.2. Exposing the photo resist using UV light                        | 88    |

|    | 3.3.3. Developing the resist                                           | 89    |

|    | 3.3.4. Depositing the desired material in the mould                    | 90    |

|    | 3.3.5. Cleaning process                                                | 91    |

|    | 3.4. Conclusion                                                        | 93    |

| Ch | apter 4                                                                | 94    |

| Fa | brications and Experiments                                             | 94    |

|    | 4.1. Introduction                                                      | 95    |

|    | 4.2. The first level                                                   | 99    |

|    | 4.2.1. Electroplating                                                  | . 101 |

|    | 4.3. The second level                                                  | . 105 |

|    | 4.4. Third and subsequent levels                                       | . 107 |

|    | 4.5. Cleaning process                                                  | . 107 |

|    | 4.6. Conclusion                                                        | . 111 |

| Ch | apter 5                                                                | . 113 |

| Re | sults and Discussion                                                   | . 113 |

|    | 5.1. Introduction                                                      | . 114 |

|    | 5.2. Problems in the first level                                       | . 117 |

|    | 5.3 Electroplating process                                             | . 125 |

|    | 5.4. Droblems in the second level                                      | 120   |

| 5.5. Problems in the third level                                                                                           | 136       |

|----------------------------------------------------------------------------------------------------------------------------|-----------|

| 5.6. Results of investigation                                                                                              | 142       |

| 5.7. Conclusion                                                                                                            | 147       |

| Chapter 6                                                                                                                  | 148       |

| Conclusions and future work                                                                                                | 148       |

| Conclusions                                                                                                                | 149       |

| Future work                                                                                                                | 153       |

| References                                                                                                                 | 154       |

| Appendix                                                                                                                   | 162       |

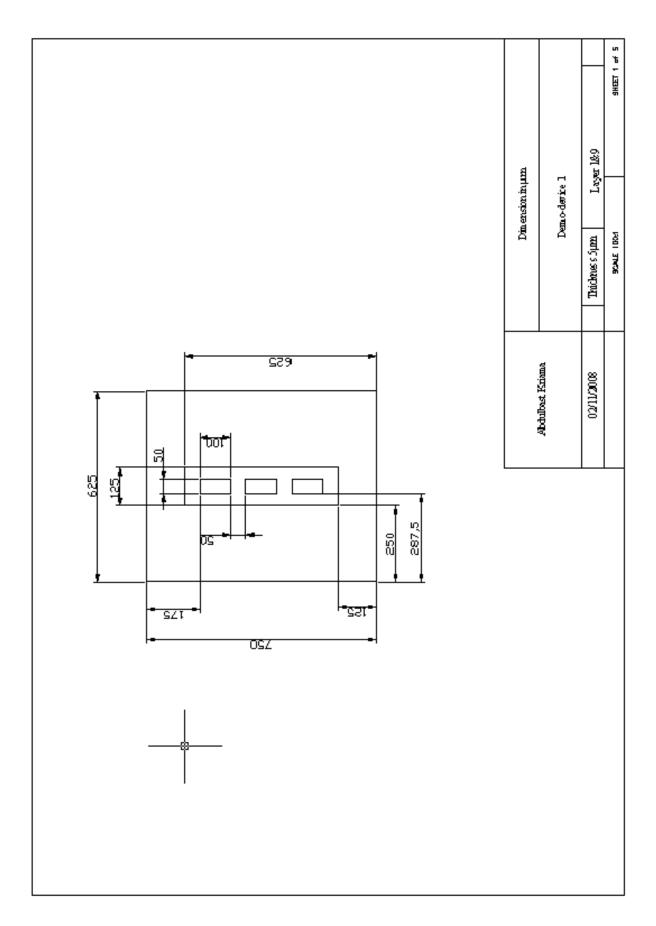

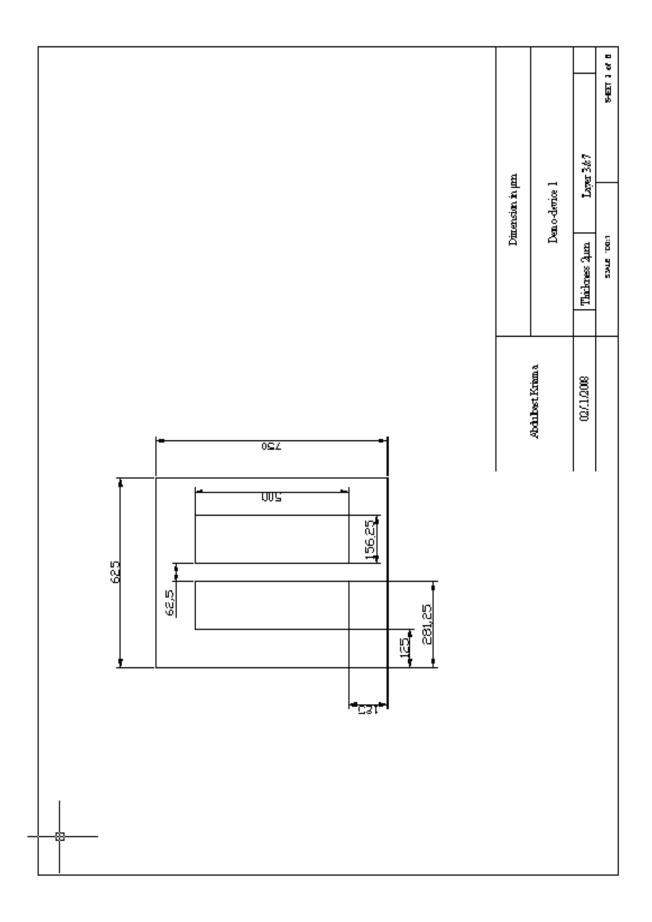

| A.1                                                                                                                        | 164       |

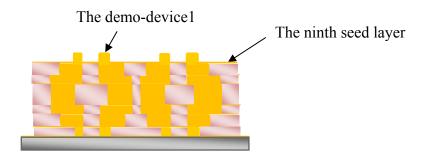

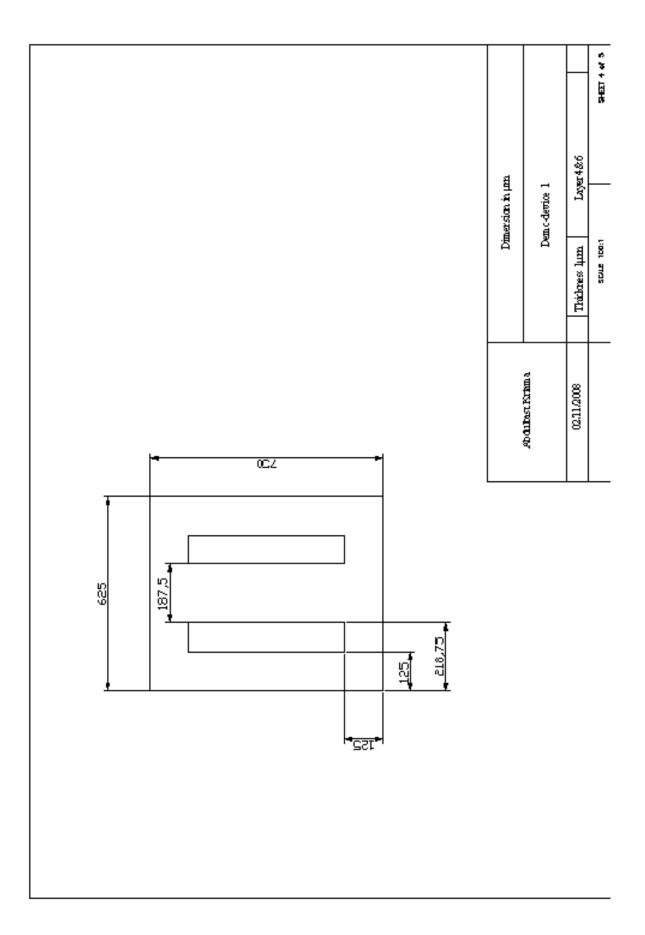

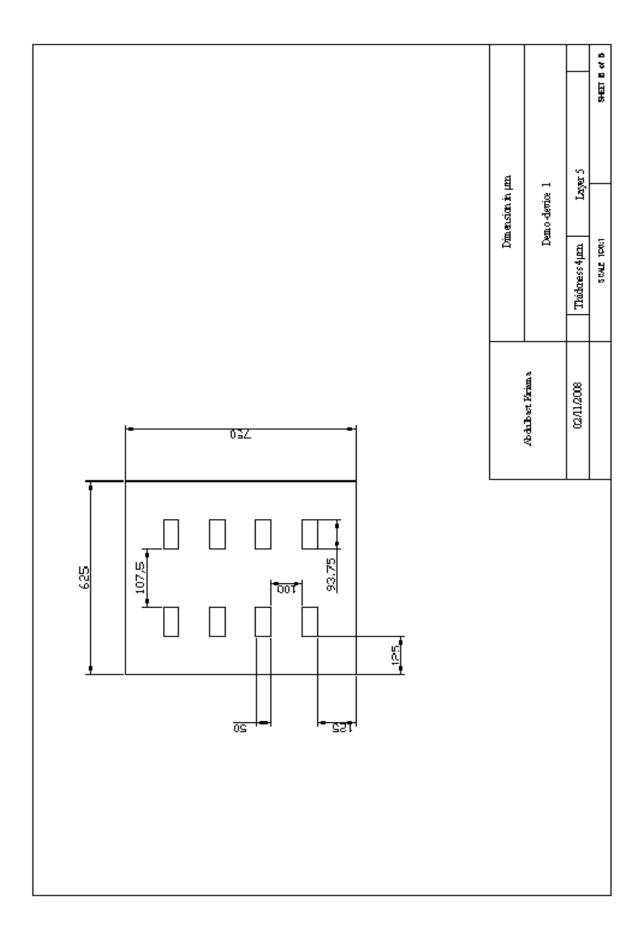

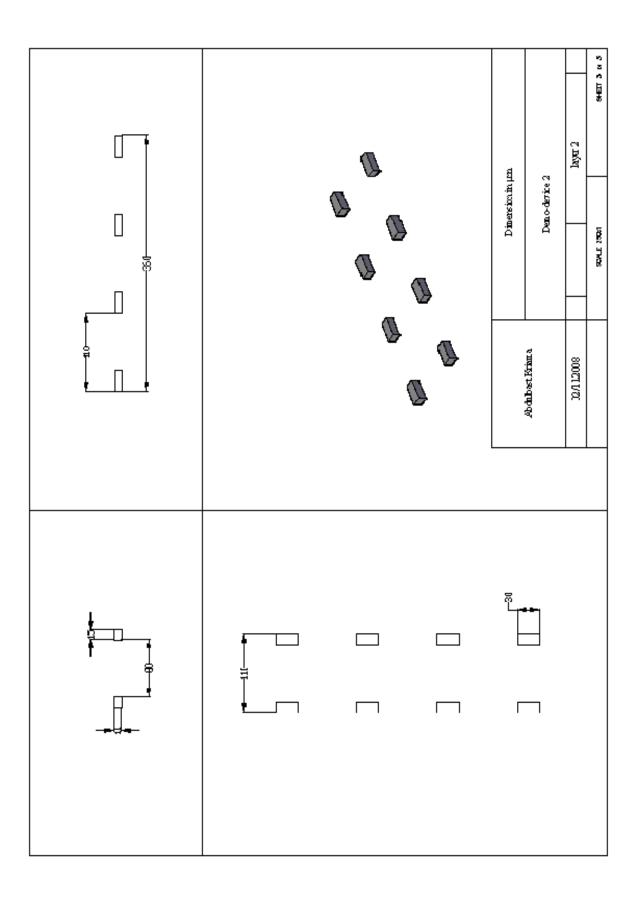

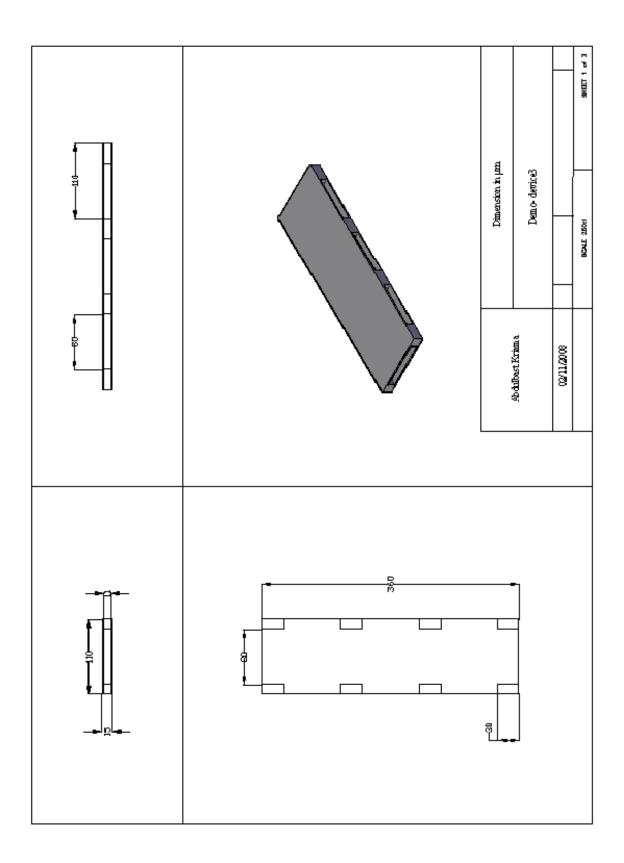

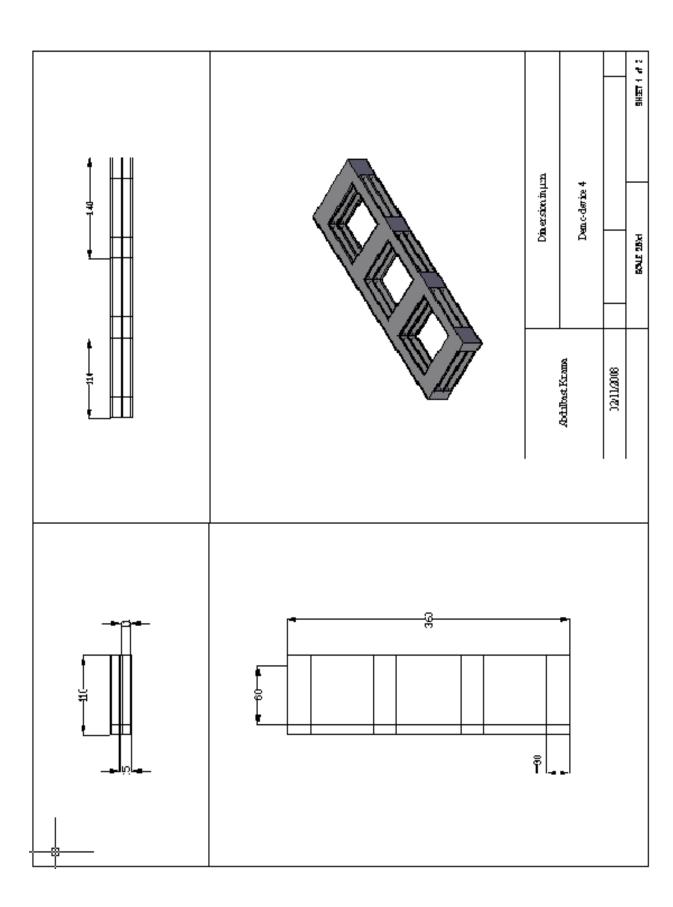

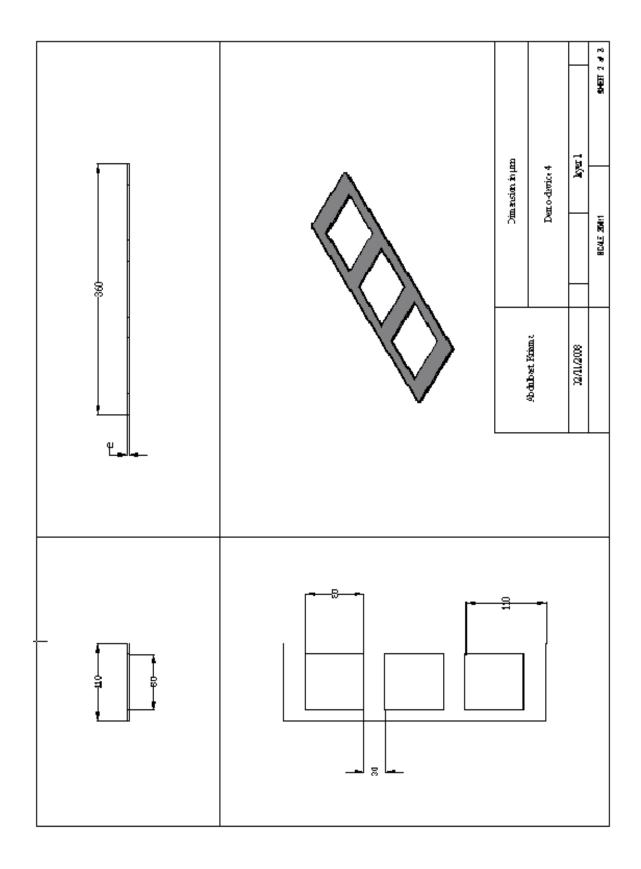

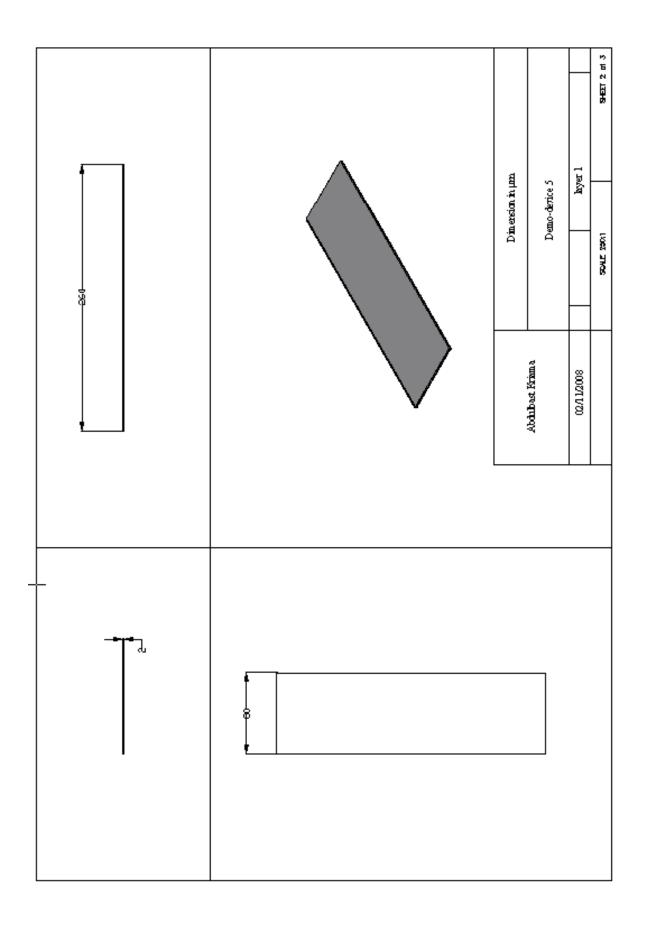

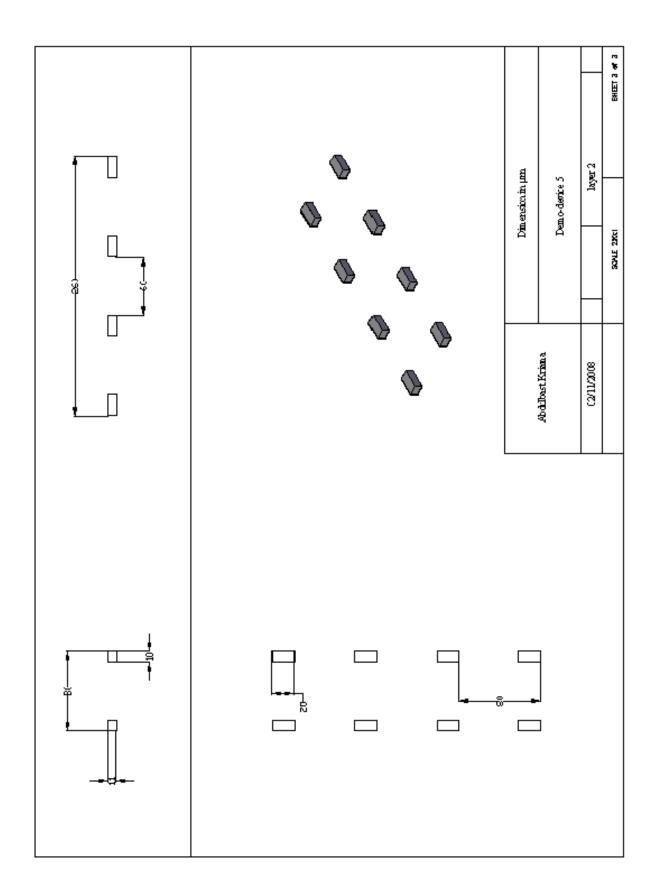

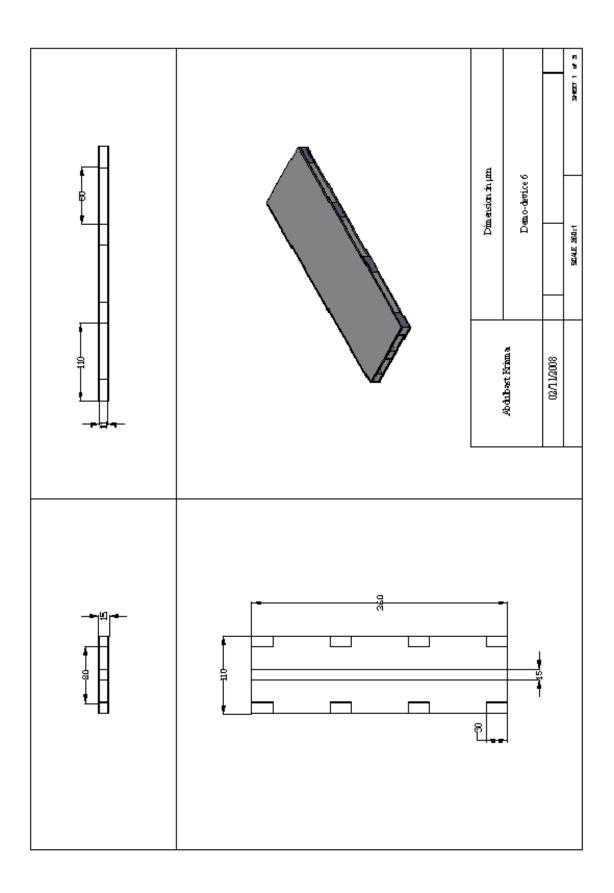

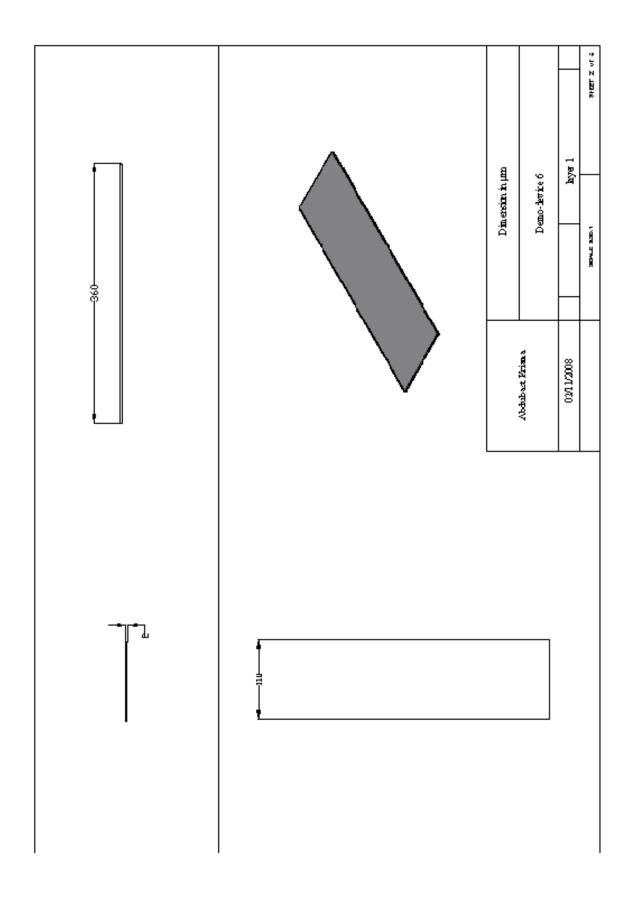

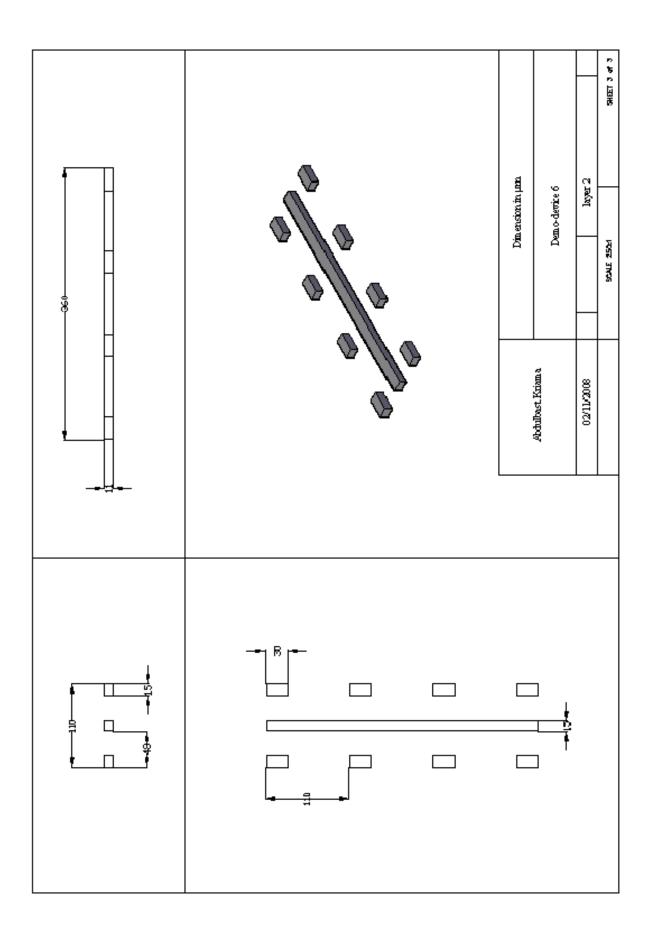

| Drawing of the demo-device1                                                                                                | 164       |

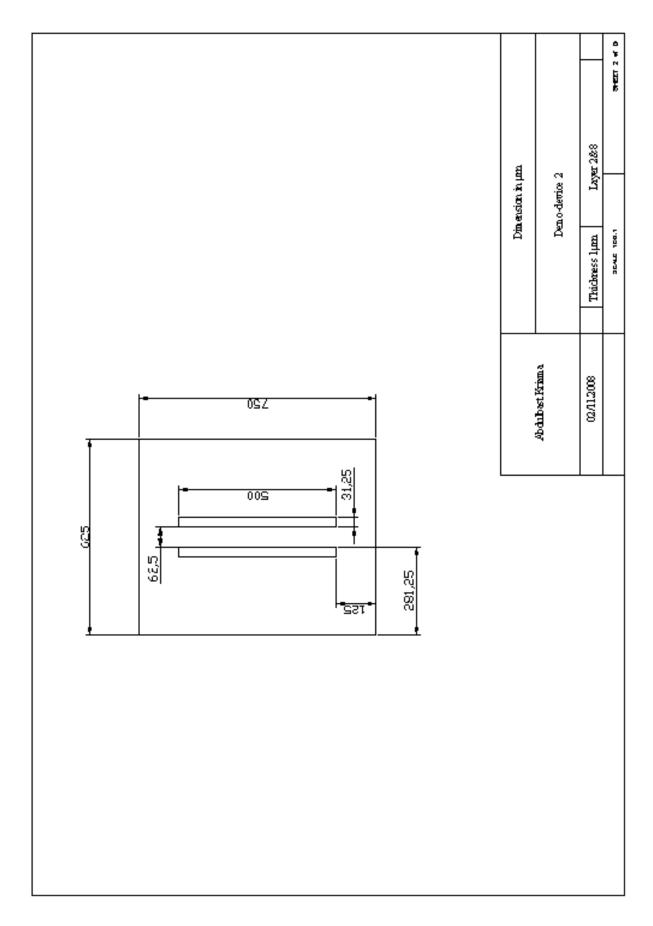

| A1.1                                                                                                                       | 170       |

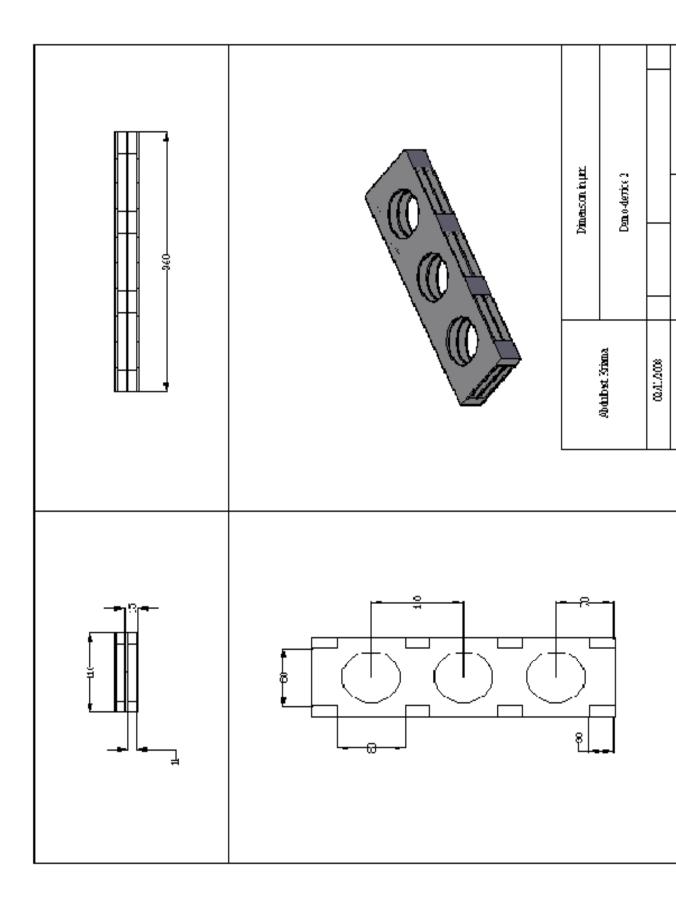

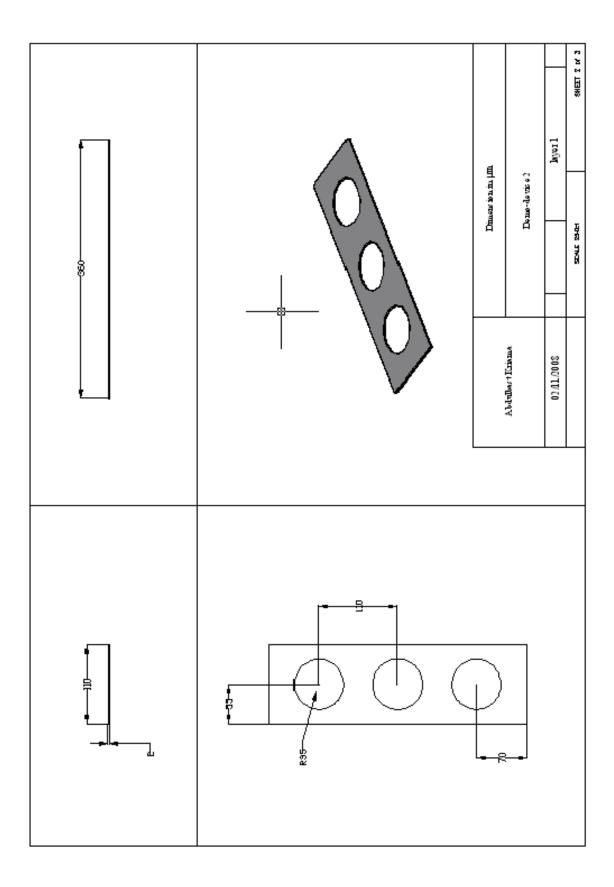

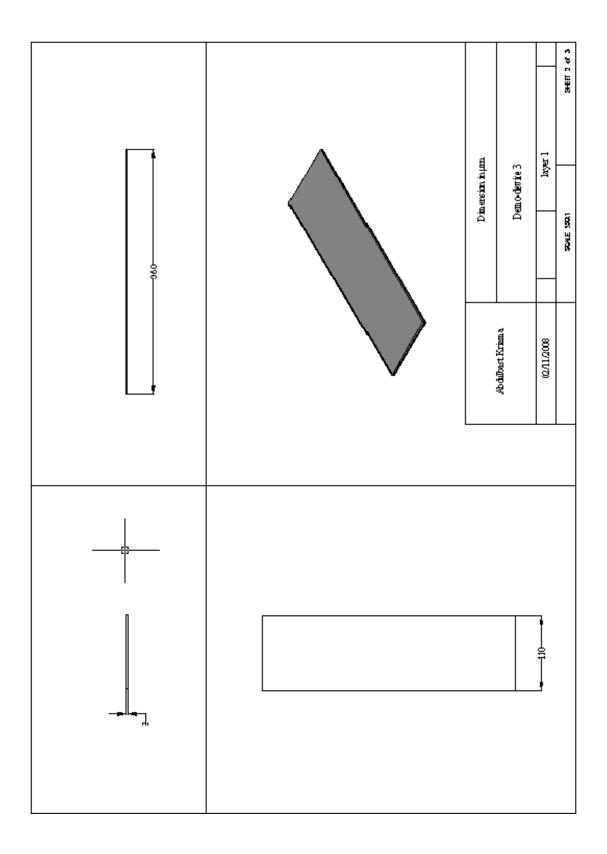

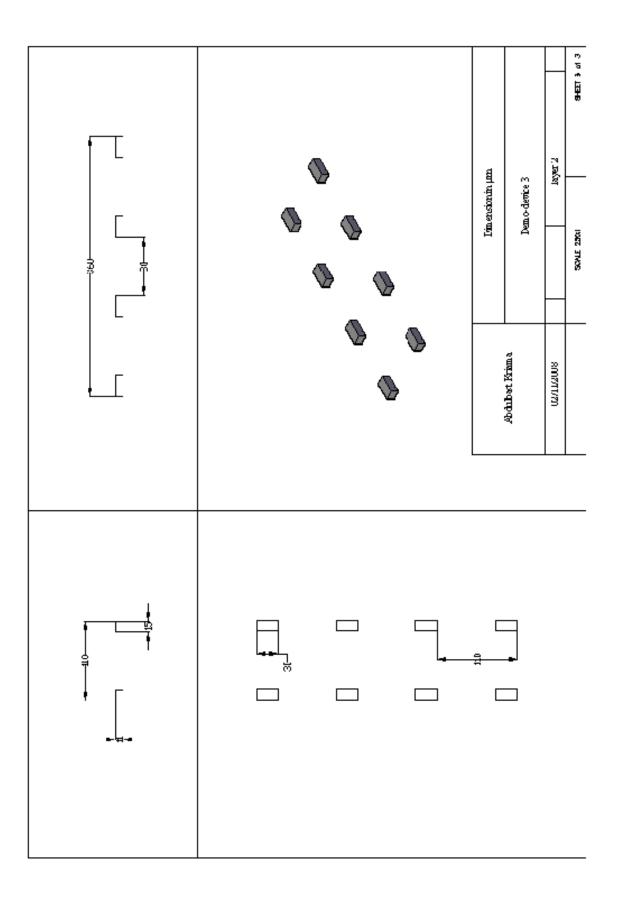

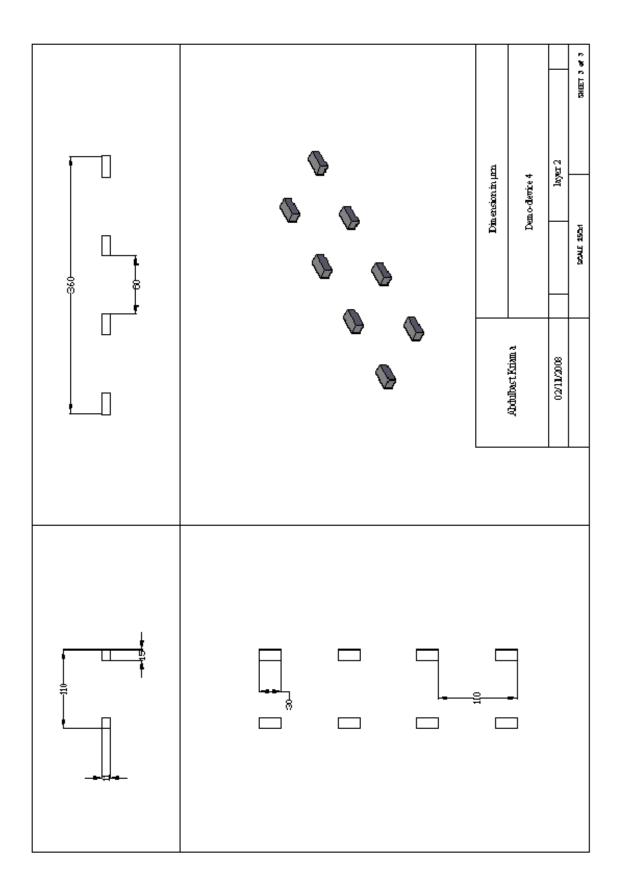

| Drawing of the demo-device2                                                                                                | 170       |

| A.2                                                                                                                        | 186       |

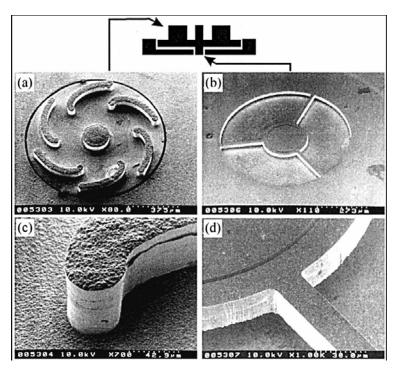

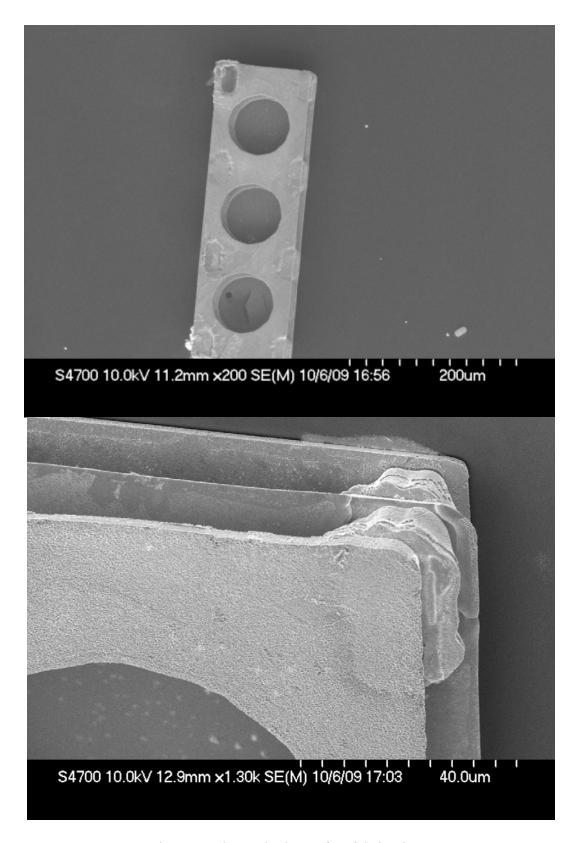

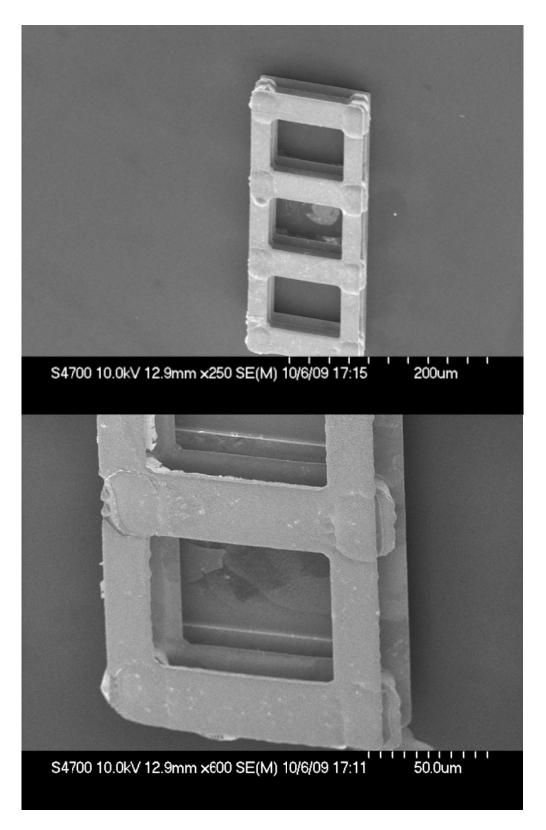

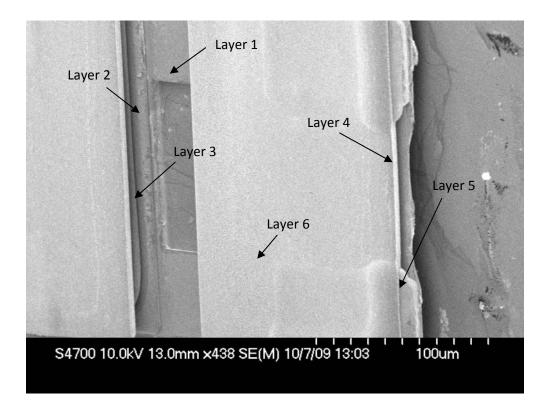

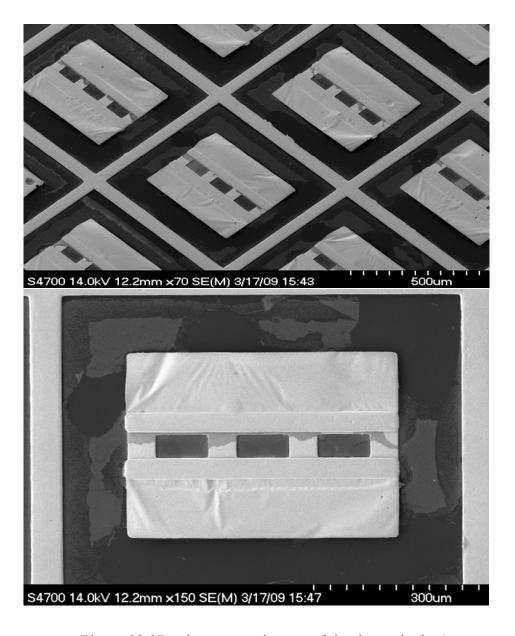

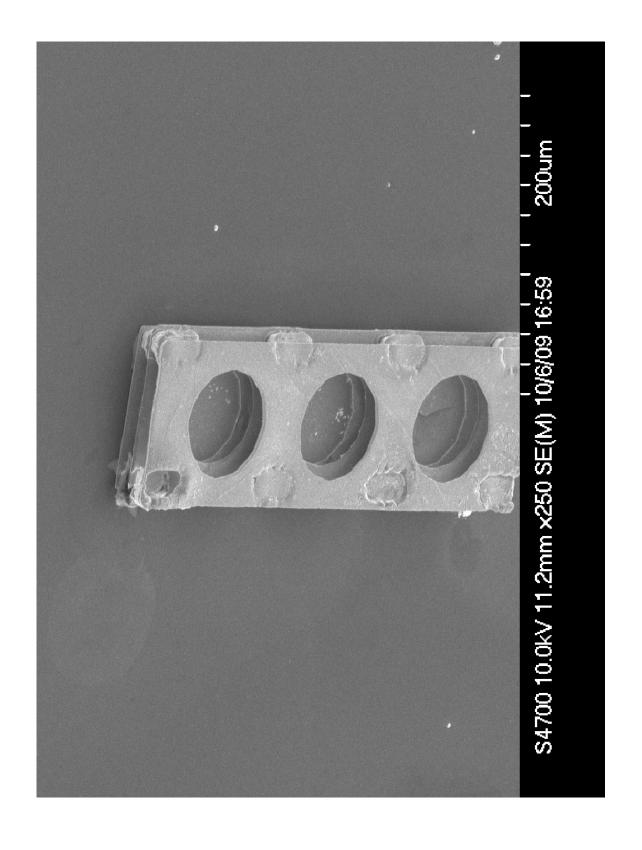

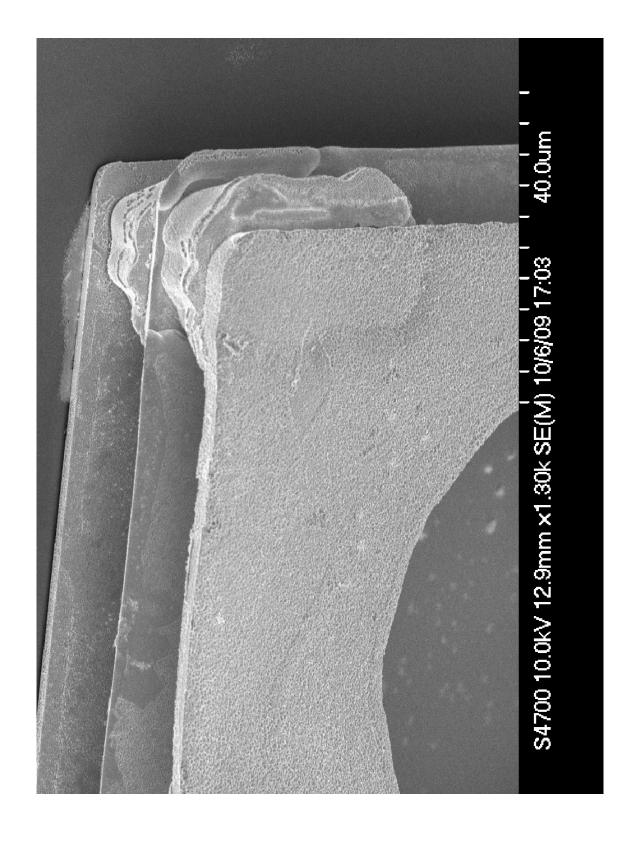

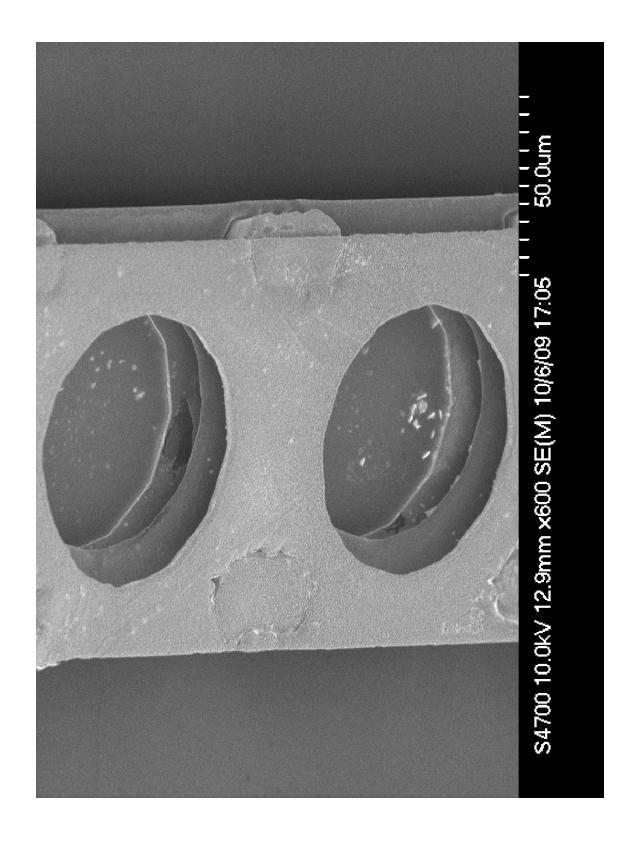

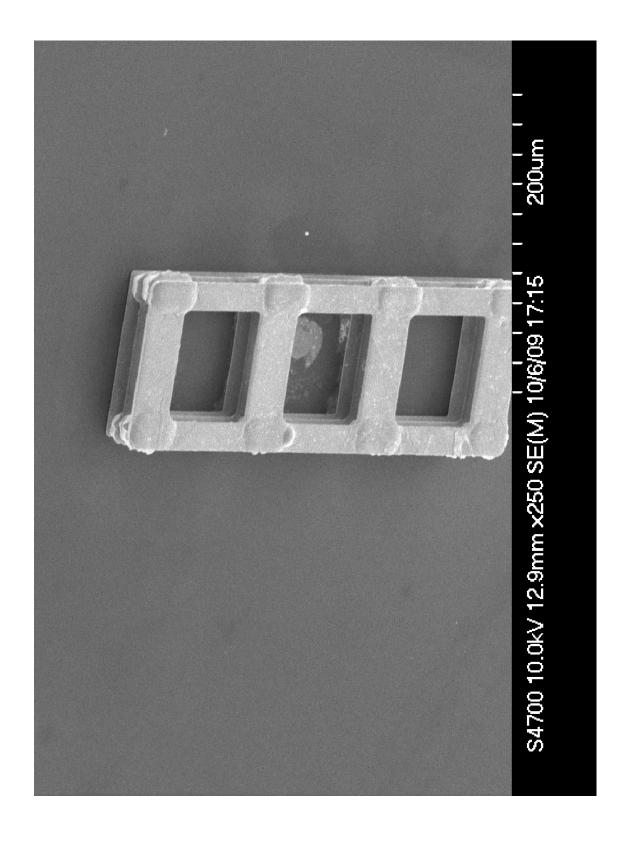

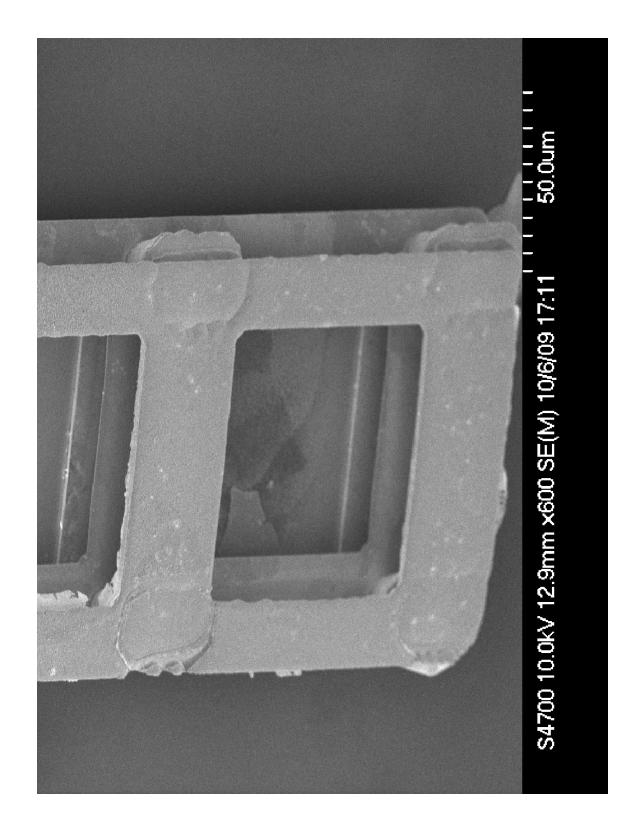

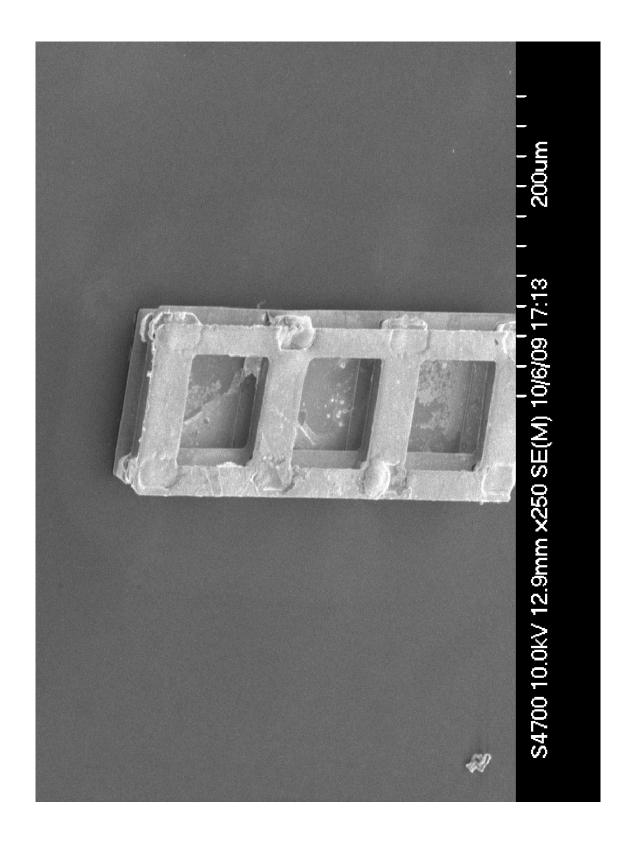

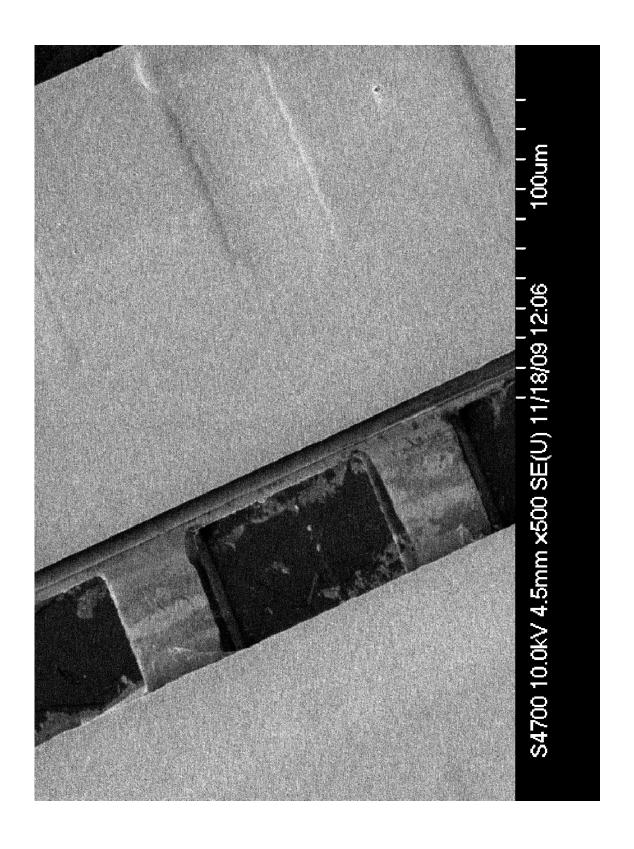

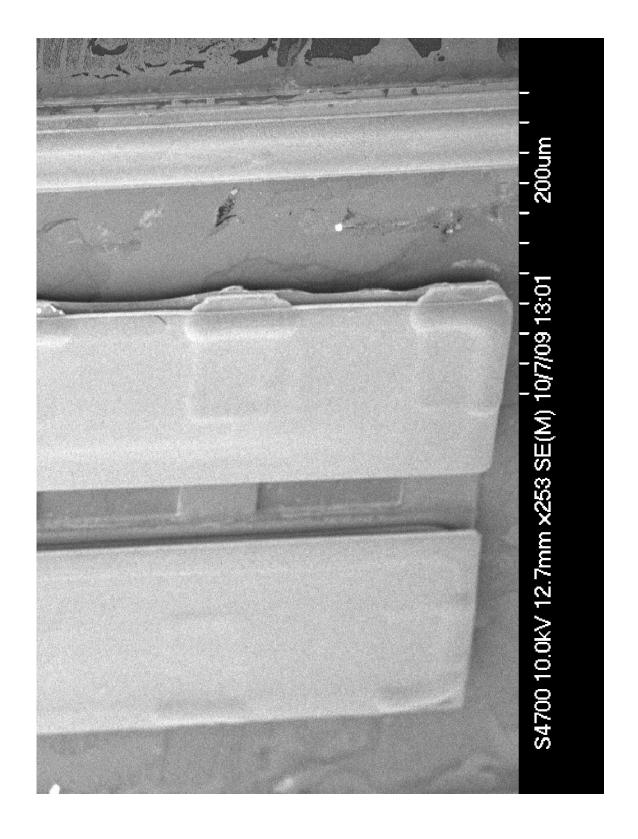

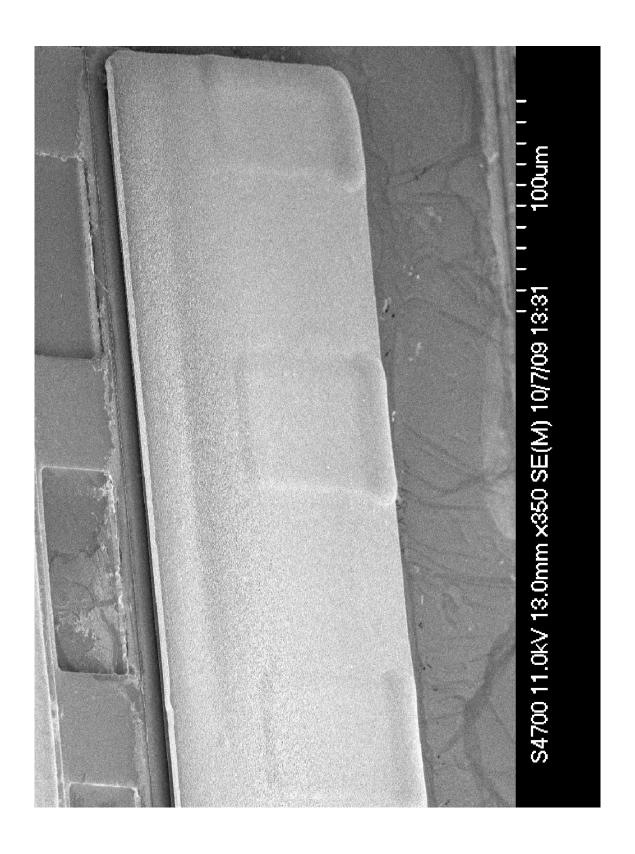

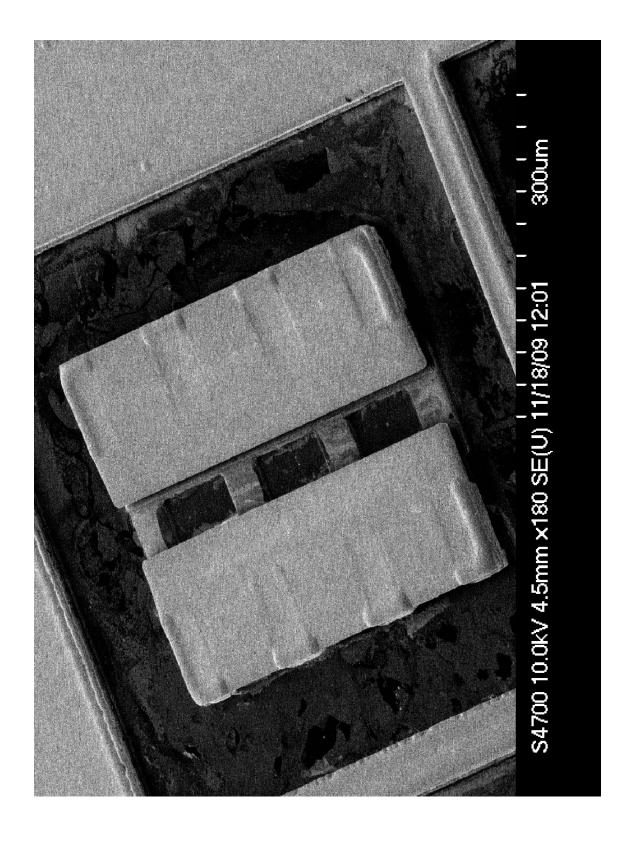

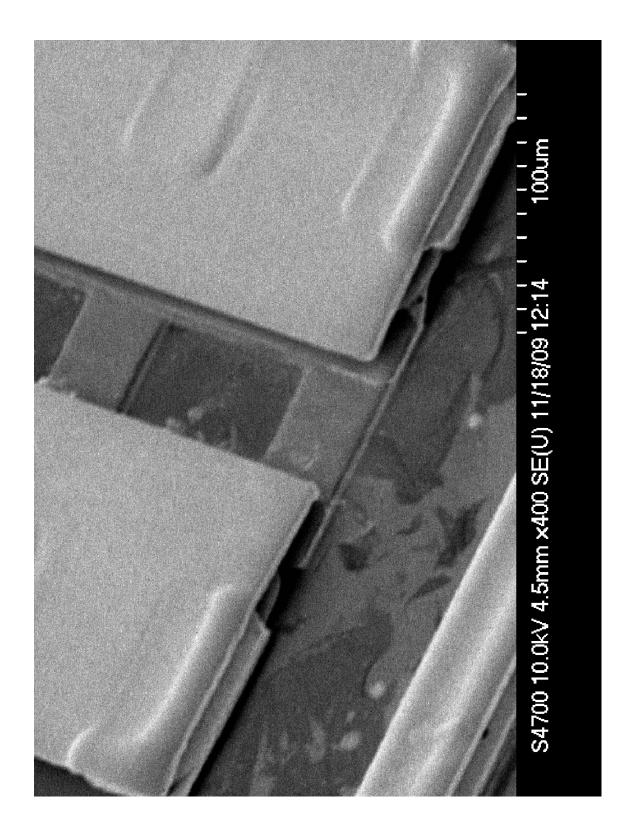

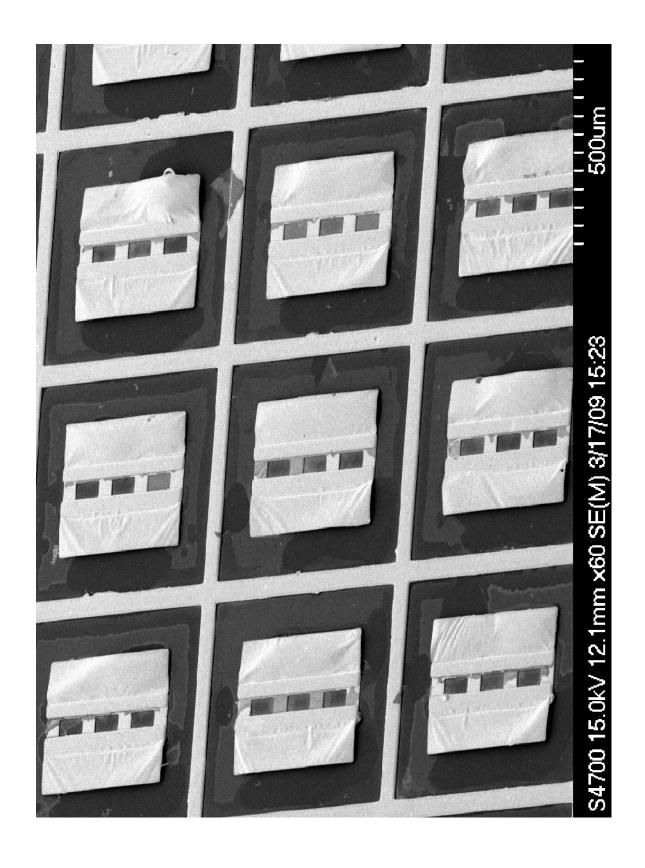

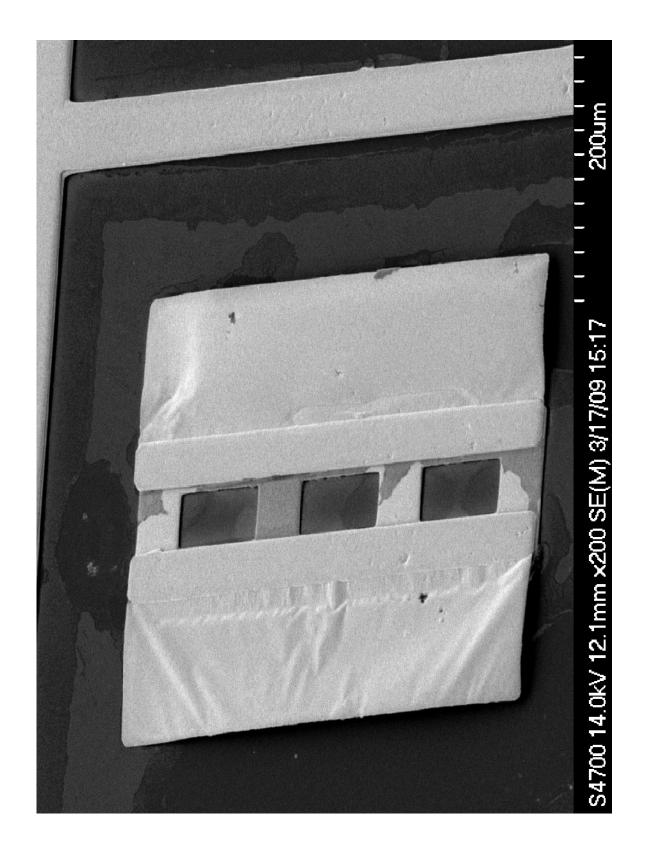

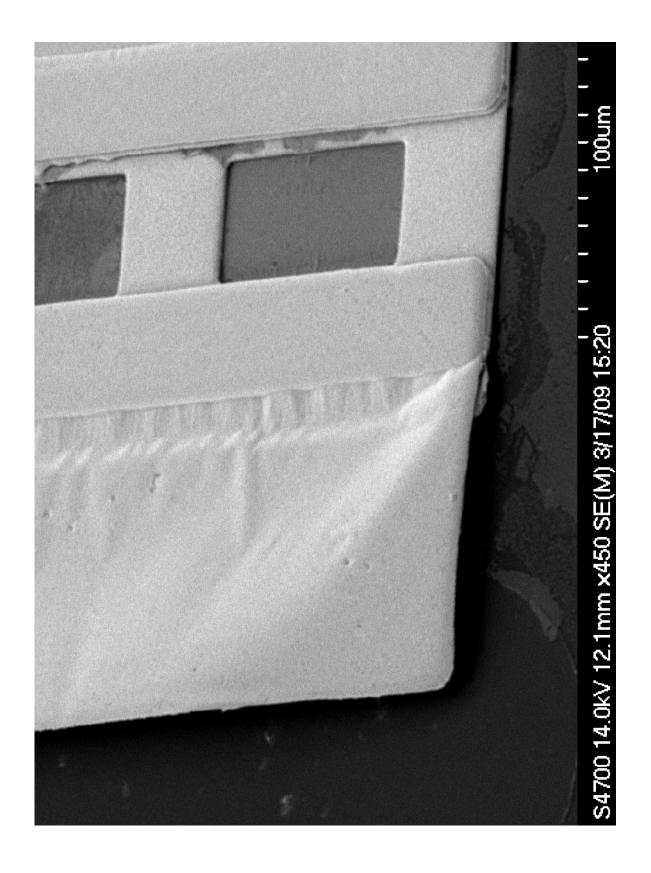

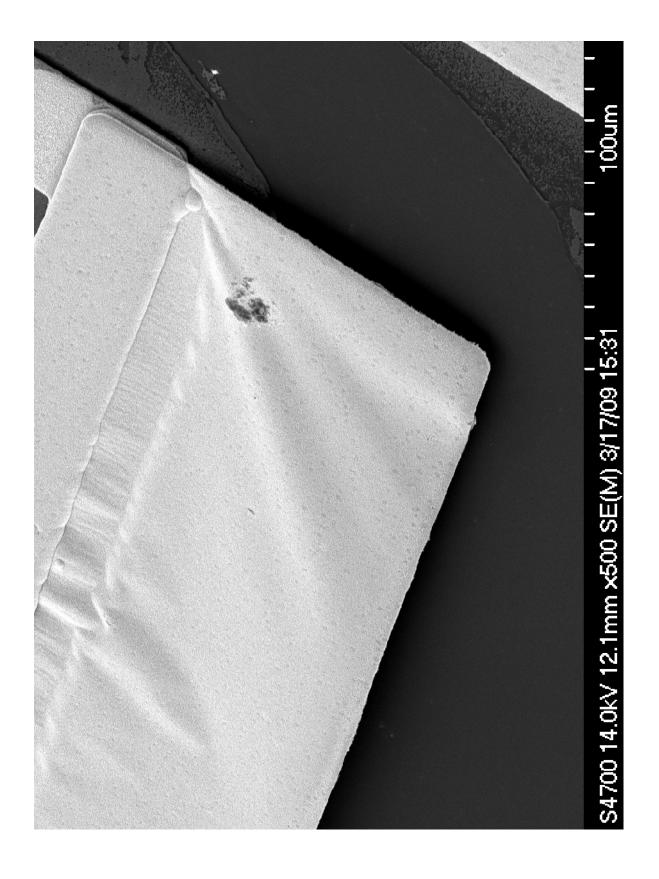

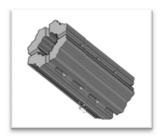

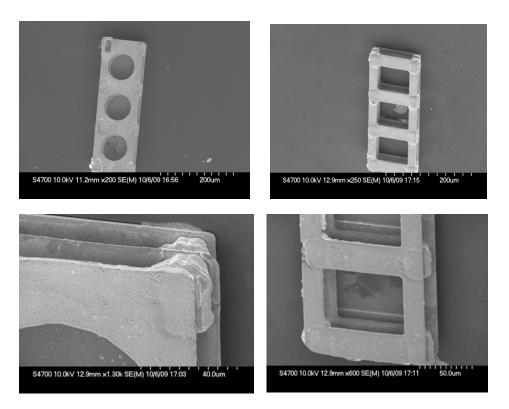

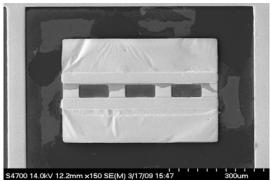

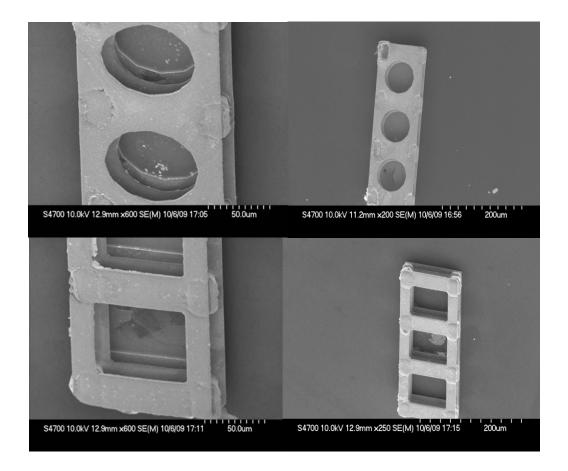

| Some pictures of the demo-device2, which were built with 5 layers, have been tak using Scanning Electron Microscopy (SEM). | •         |

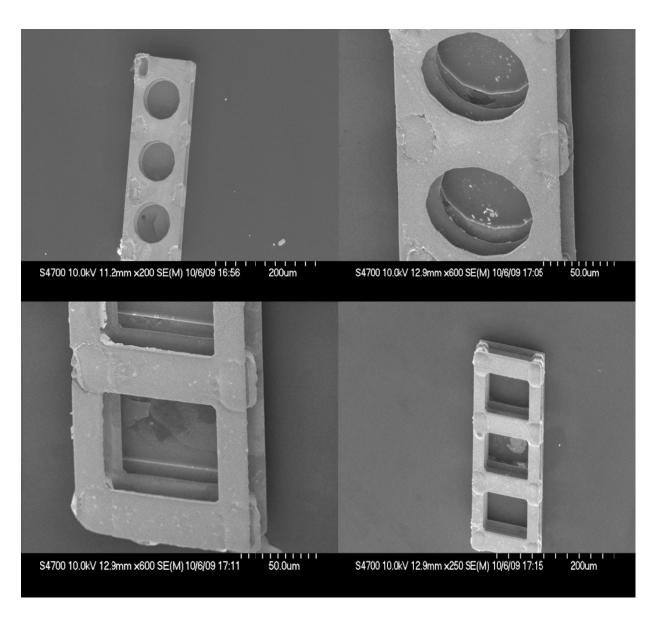

| A.3                                                                                                                        | 194       |

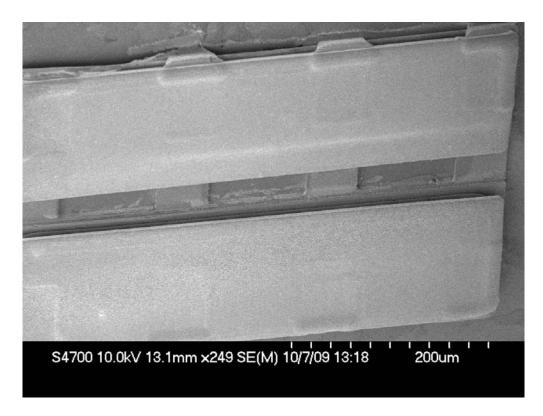

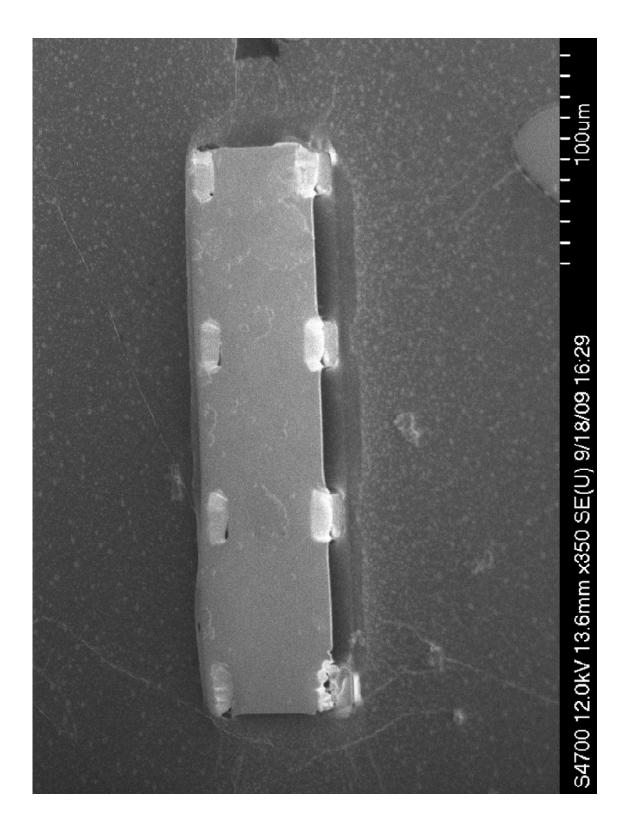

| Some pictures of the demo-devices1, which were built with 9 layers, have been ta using Scanning Electron Microscopy (SEM). | •         |

| A.4                                                                                                                        |           |

| Pictures of removing the SU8 and not solving                                                                               | 200       |

| A.5                                                                                                                        | 203       |

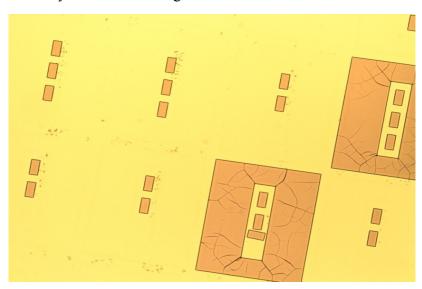

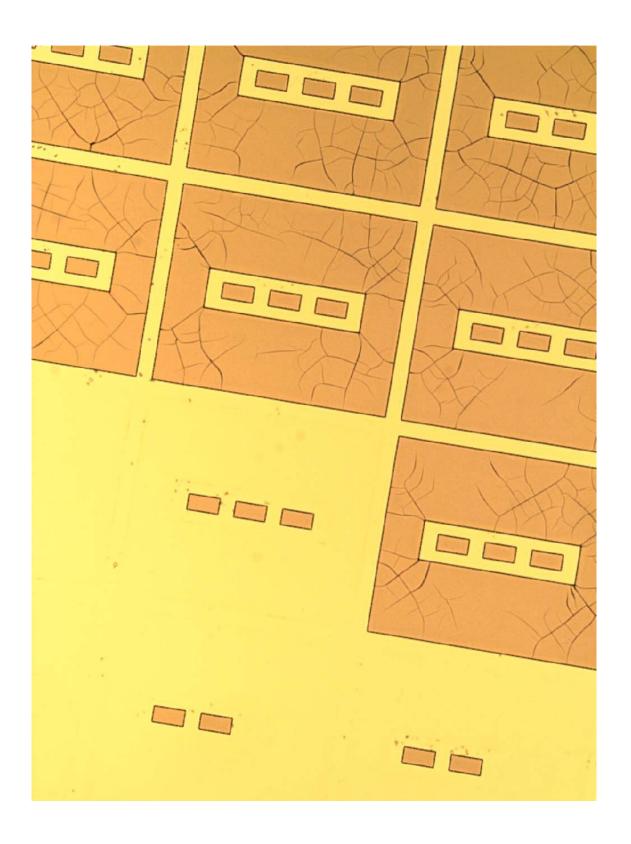

| The surface of the photoresist after the development and before electroplating pr                                          | ocess 203 |

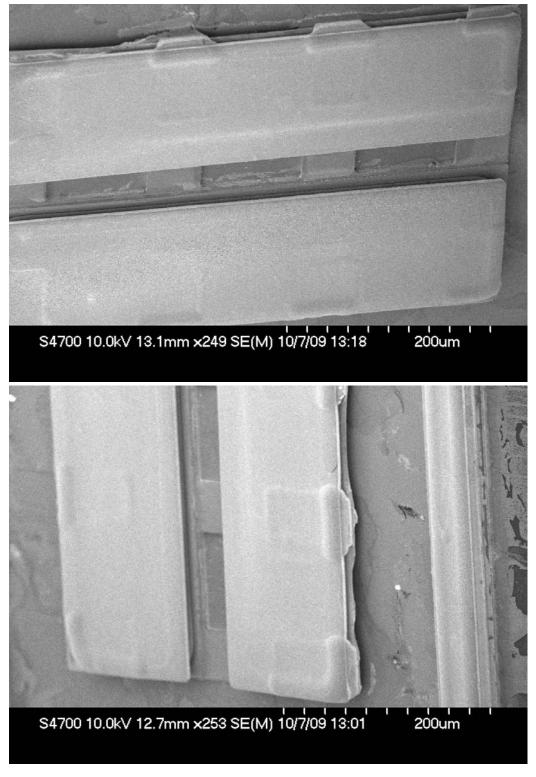

| A.6                                                                                                                        | 208       |

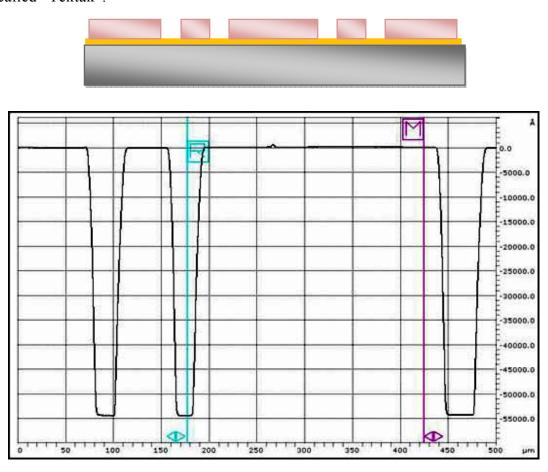

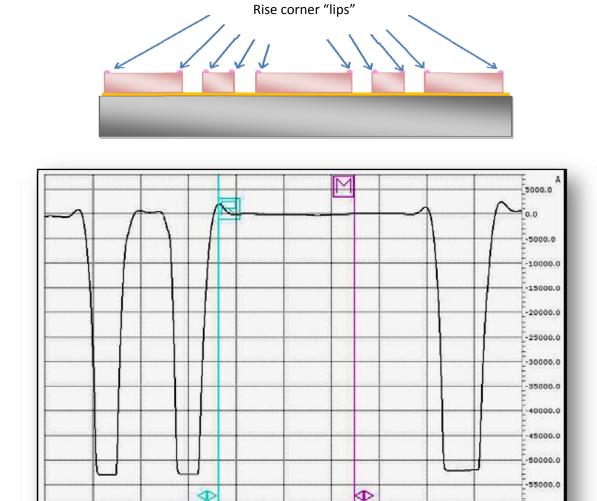

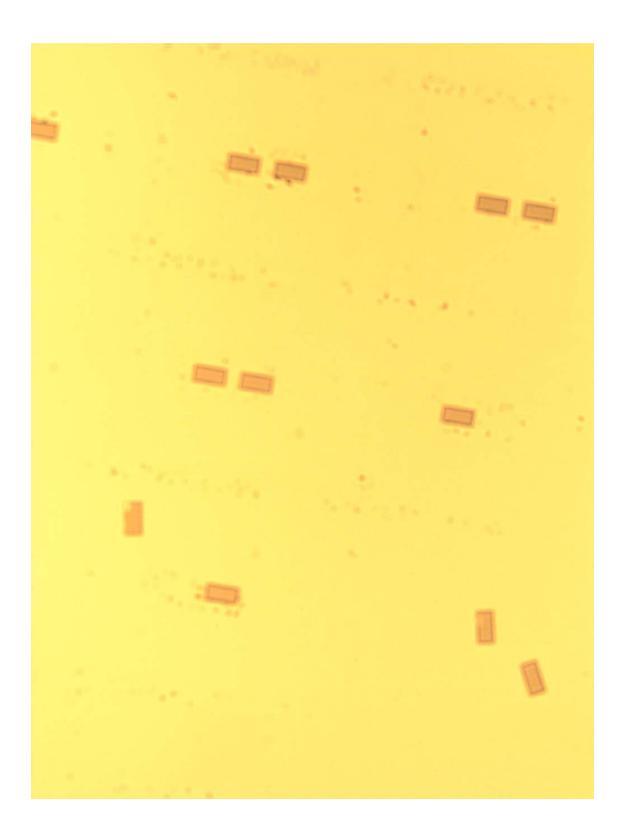

| The surface of the photoresist after the electroplating process and appearing of lip                                       | os 208    |

| A.7                                                                                                                        | 210       |

| Scheme of the treated photoresist surface                                                                                  | 210       |

| A.8                                                                                                                        | 212       |

| Appearing of bubbles in the second level                                                                                   | 212       |

| A.9                                                                                                                        | 217       |

| Appearing of bubbles under the second level                                                                                | 217       |

| A.10                                                                                                                       | 220       |

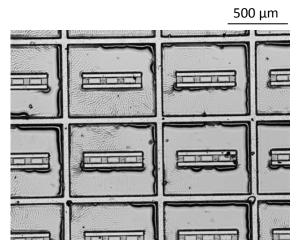

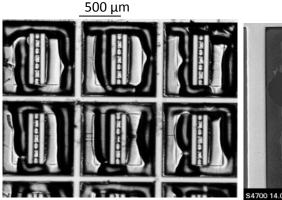

| Some nictures of wrinkled surface in the photoresist                                                                       | 220       |

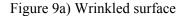

| A.11                                                                                     | 224 |

|------------------------------------------------------------------------------------------|-----|

| Some pictures of wrinkled surfaces in the demo-devices, which were built with 3 layers,  |     |

| have been taken by using Scanning Electron Microscopy (SEM)                              | 224 |

| A.12                                                                                     | 232 |

| Paper which we participated in a conference in Barcelona in Spain in 2008                | 232 |

| A.13                                                                                     | 237 |

| Submission of the work to Proceedings of the Institution of Mechanical Engineers, Part E | 3,  |

| and Journal of Engineering Manufacture in June 2010                                      | 237 |

# **List of Figures**

| Figure 1 the Intel 4004 Microprocessor, Busicom calculator <sup>[16]</sup>                     |    |

|------------------------------------------------------------------------------------------------|----|

| Figure 2 the process of multi layer using seed layers <sup>[28]</sup>                          | 18 |

| Figure 3 hot Embossing <sup>[32]</sup>                                                         |    |

| Figure 4 glancing Angle Deposition <sup>[35]</sup>                                             | 21 |

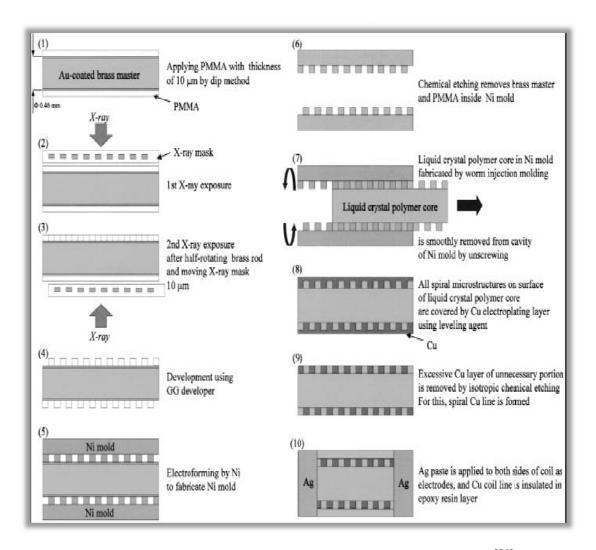

| Figure 5 spiral microcoil using a 3D-LIGA process <sup>[38]</sup>                              | 22 |

| Figure 6 the light passes through the mask                                                     | 24 |

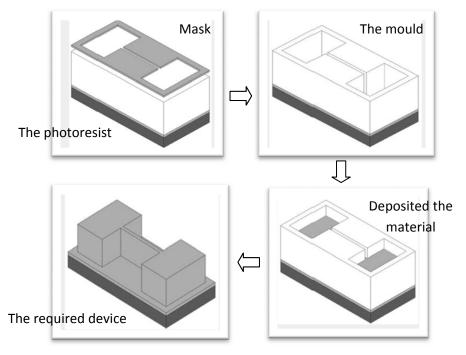

| Figure 7 transfer the 2D configuration                                                         | 25 |

| Figure 8 Deposited material                                                                    | 25 |

| Figure 9 process of the electroplating                                                         | 30 |

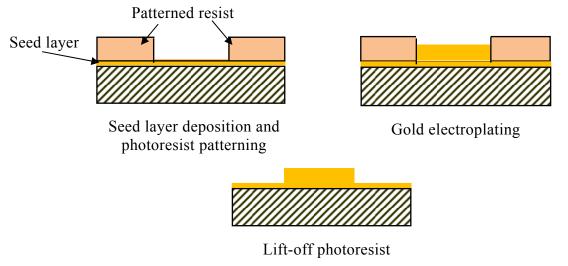

| Figure 10 the electroplating process to depositing gold                                        | 32 |

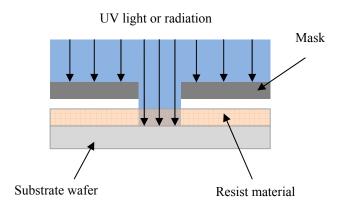

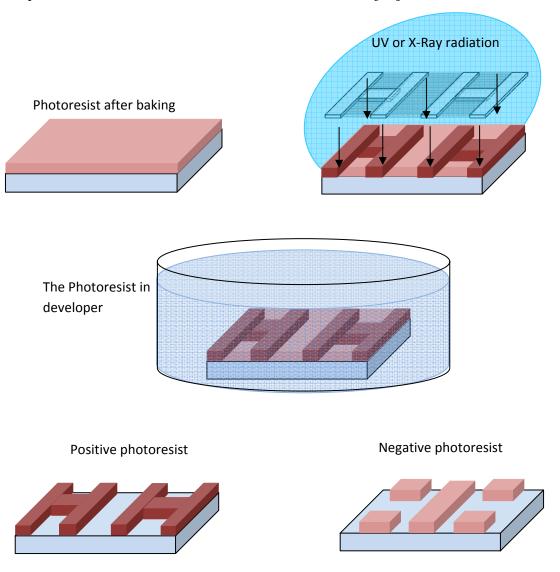

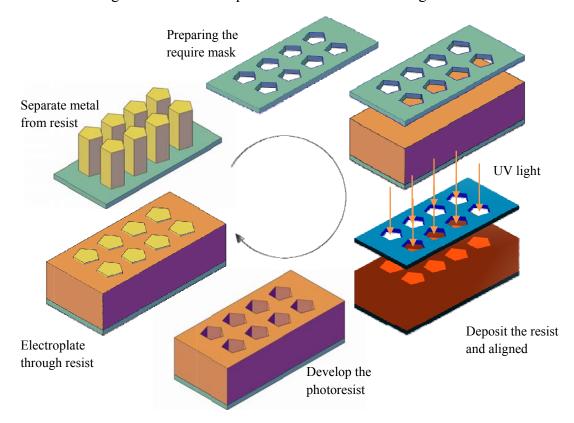

| Figure 11 the Photolithography processes                                                       | 34 |

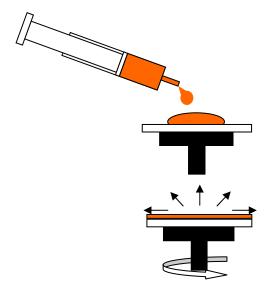

| Figure 12 spin coating process                                                                 | 35 |

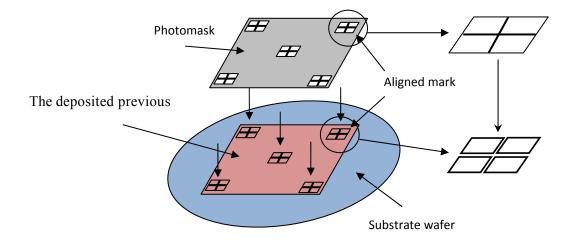

| Figure 13 Photomask                                                                            | 38 |

| Figure 14 the aligned process                                                                  | 38 |

| Figure 15 Positive and Negative resist                                                         | 39 |

| Figure 16 isotropic etching                                                                    | 44 |

| Figure 17 anisotropic etching                                                                  | 44 |

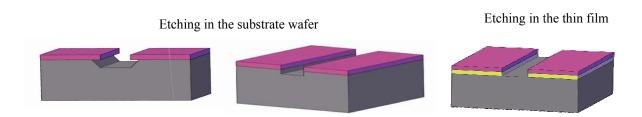

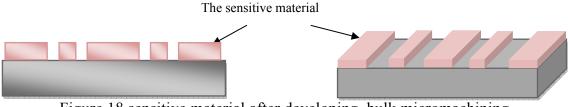

| Figure 18 sensitive material after developing, bulk micromachining                             | 46 |

| Figure 19 etching in the thin film                                                             | 46 |

| Figure 20 the thin film after removing the sensitive material, bulk micromachining             | 46 |

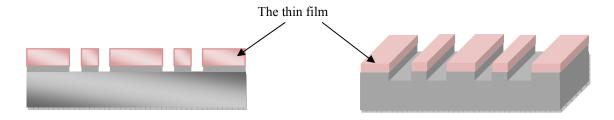

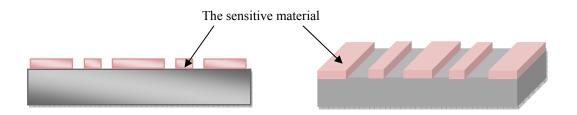

| Figure 21 sensitive material after developing, surface micromachining                          | 48 |

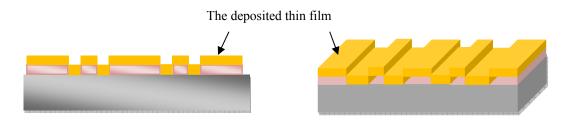

| Figure 22 the deposited thin film, surface micromachining                                      | 48 |

| Figure 23 the thin film after removing the sensitive material, surface micromachining.         | 48 |

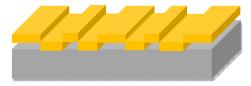

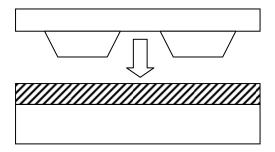

| Figure 24 Moulding: material flow into mould master                                            | 51 |

| Figure 25 Stamping: the stamp modifies material already on the wafer                           | 51 |

| Figure 26 the LIGA process                                                                     | 57 |

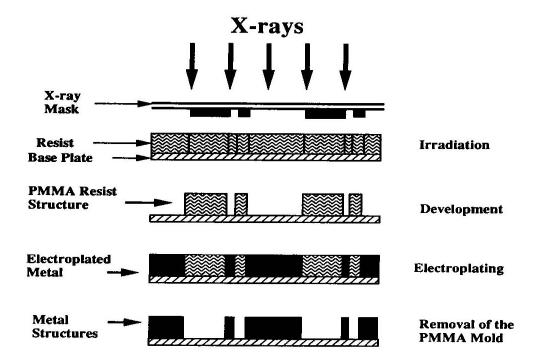

| Figure 27 The LIGA process utilizes X-ray masks and a synchrotron source [87]                  | 60 |

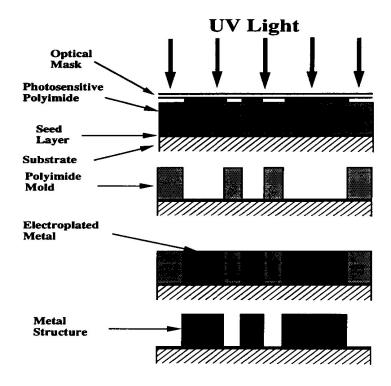

| Figure 28.The process utilizes standard optical masks and a standard UV source <sup>[87]</sup> | 61 |

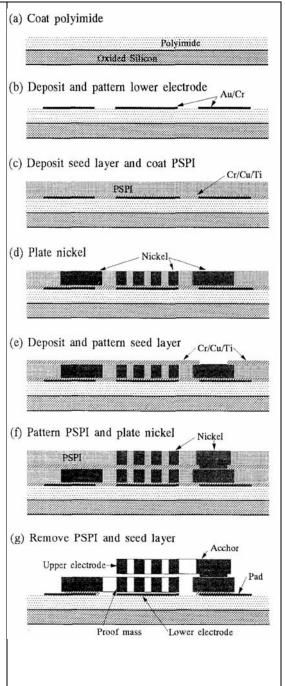

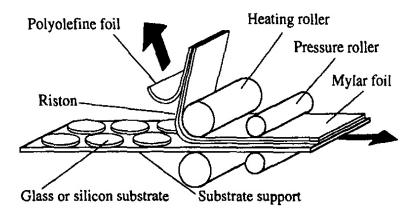

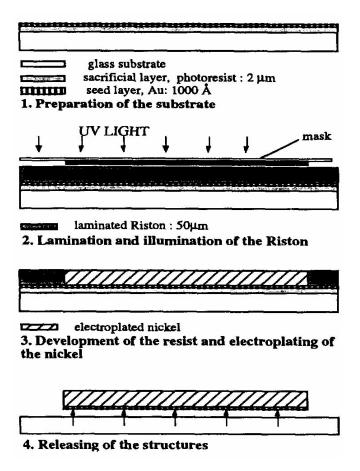

| Figure 29 the Riston technique by lamination <sup>[92]</sup>                                   | 64 |

| Figure 30 utilizing dry photo resist by using multilayer process <sup>[92]</sup>               | 65 |

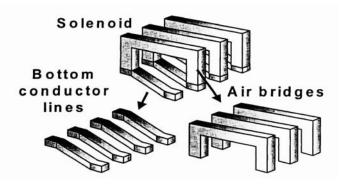

| Figure 31 3D of the micro coil <sup>[96]</sup>                                                 |    |

| Figure 32 3D multilevel mould of micro coil <sup>[96]</sup>                                    |    |

| Figure 33 3D multilevel mould of micro coil <sup>[96]</sup>                                    |    |

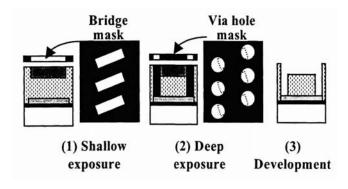

| Figure 34 a process for fabricating multi level metal structures <sup>[98]</sup>               |    |

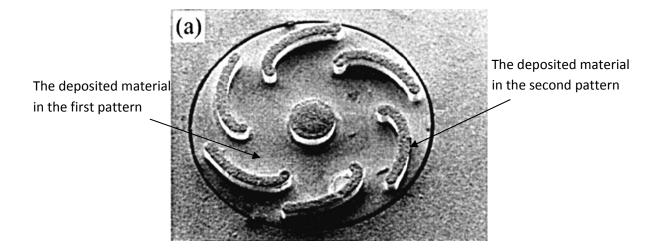

| Figure 35 a turbine produced by using six layers <sup>[98]</sup>                               |    |

| Figure 36 a turbine which was produced with six levels <sup>[98]</sup>                         |    |

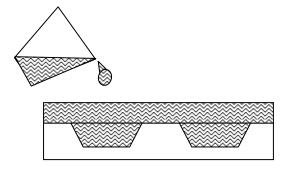

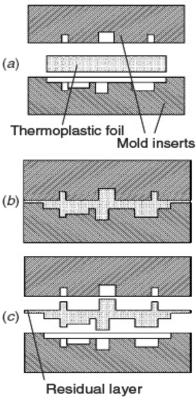

| Figure 37 principal process steps of hot embossing <sup>[101]</sup>                            |    |

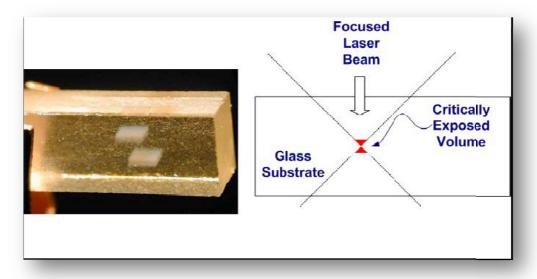

| Figure 38 3D Direct-Write <sup>[37]</sup>                                                      |    |

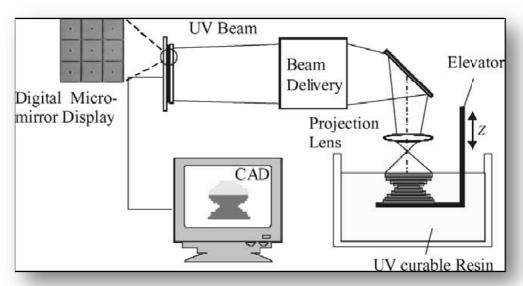

| Figure 39 Schematic diagram of projection micro-stereo lithography <sup>[44]</sup>             |    |

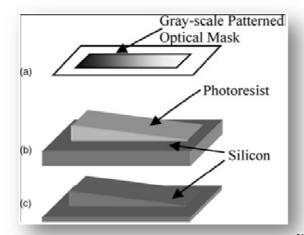

| Figure 40 the primary steps in gray-scale technology [104]                                     |    |

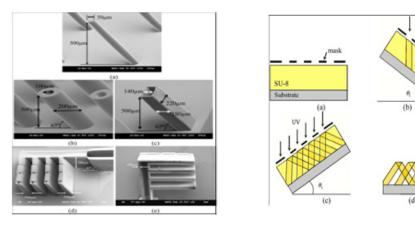

| Figure 41.Fabricated structures with inclined exposure <sup>[84]</sup>                         | 78 |

| Figure 42 process of 3D X-LIAG lithography with unscrewing [86]                | 79          |

|--------------------------------------------------------------------------------|-------------|

| Figure 43.Transfer of the 2D structure [52]                                    | 84          |

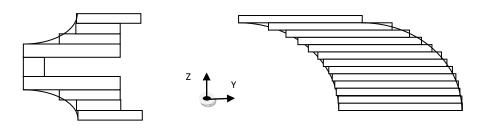

| Figure 44 the XYZ planes                                                       | 84          |

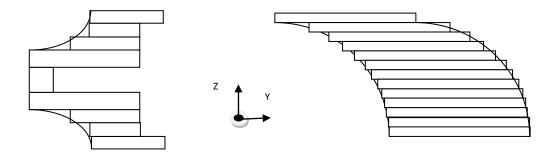

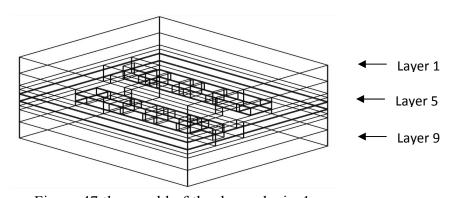

| Figure 45 the multi layer planes                                               | 85          |

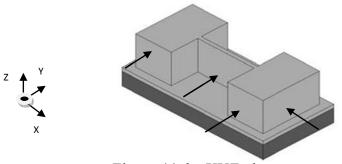

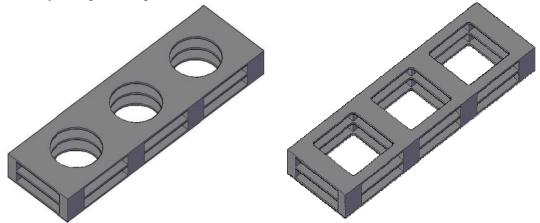

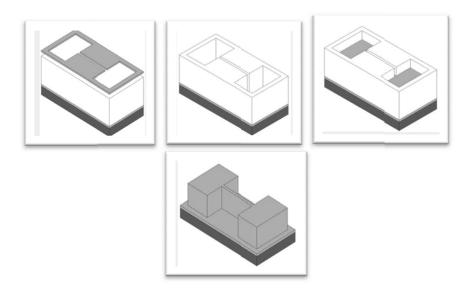

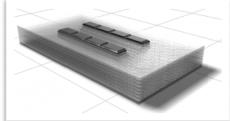

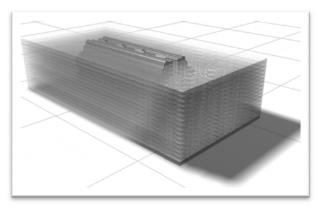

| Figure 46 the demo-device1                                                     | 87          |

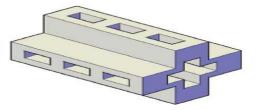

| Figure 47 the mould of the demo-device1                                        | 87          |

| Figure 48 depositing a seed layer                                              | 88          |

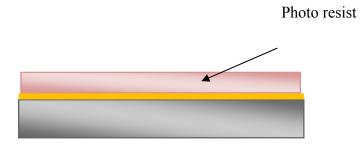

| Figure 49 depositing a photo resist                                            | 88          |

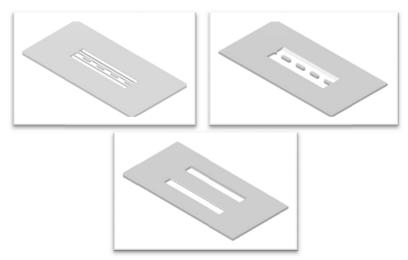

| Figure 50 the first mask                                                       | 89          |

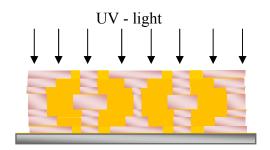

| Figure 51 exposing the photo resist with UV light                              | 89          |

| Figure 52 the developed photo resist (the mould)                               | 89          |

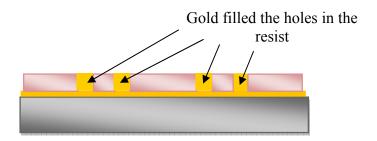

| Figure 53 deposition of gold                                                   | 90          |

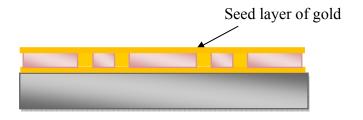

| Figure 54 deposition of the second seed layer                                  | 90          |

| Figure 55 the demo-device1                                                     | 91          |

| Figure 56 the cleaning process                                                 | 91          |

| Figure 57 removing the photo resist                                            | 92          |

| Figure 58 removing the seed layer                                              | 92          |

| Figure 59 the final product                                                    | 92          |

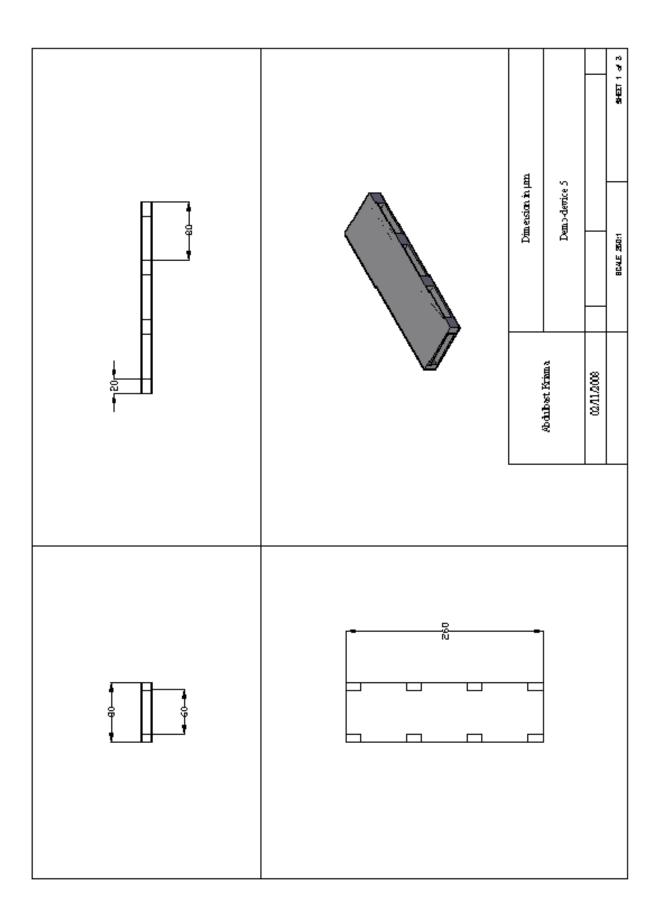

| Figure 60 demo-device2                                                         | 95          |

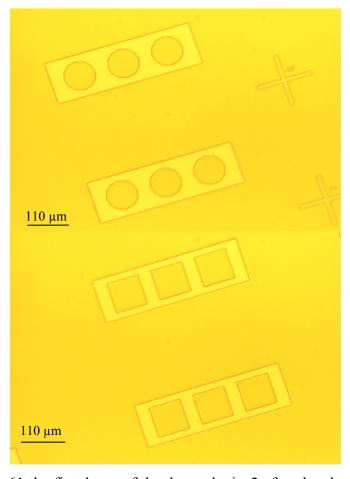

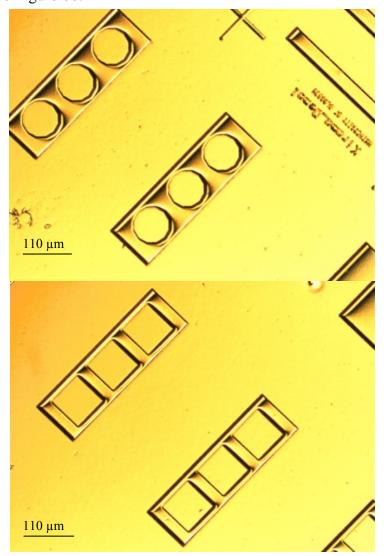

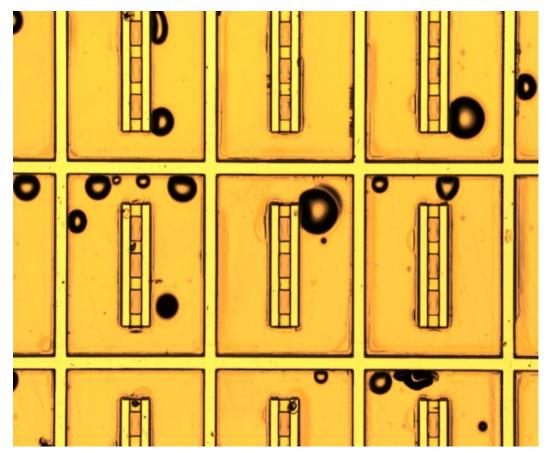

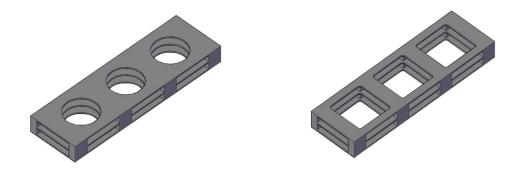

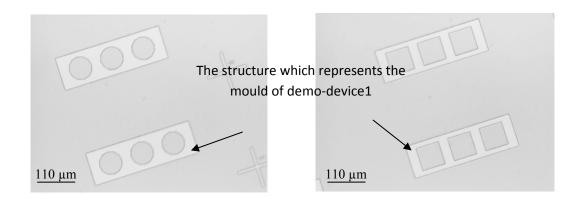

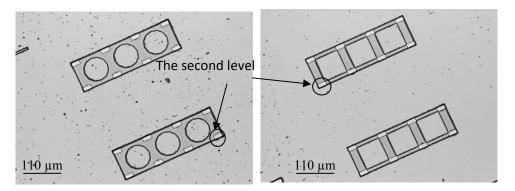

| Figure 61 the first layer of the demo-device2 after developing                 | 100         |

| Figure 62 the first layer of the demo-device1 after developing                 | 100         |

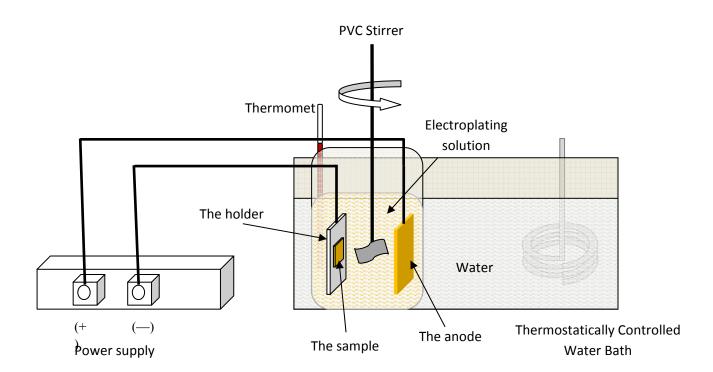

| Figure 63 electroplating equipment in JWNC                                     | 101         |

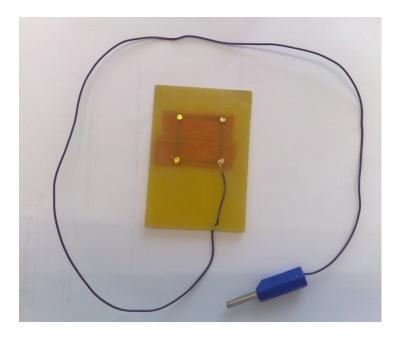

| Figure 64 experiment of electroplating                                         | 102         |

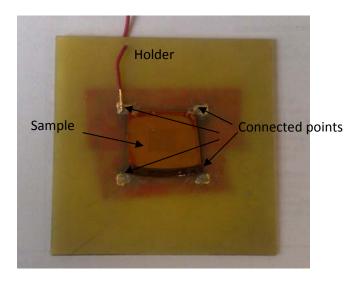

| Figure 65 the cathode                                                          | 103         |

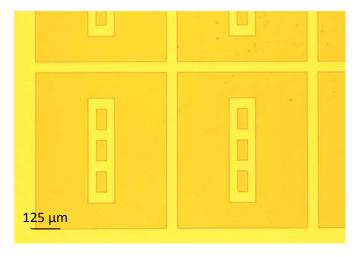

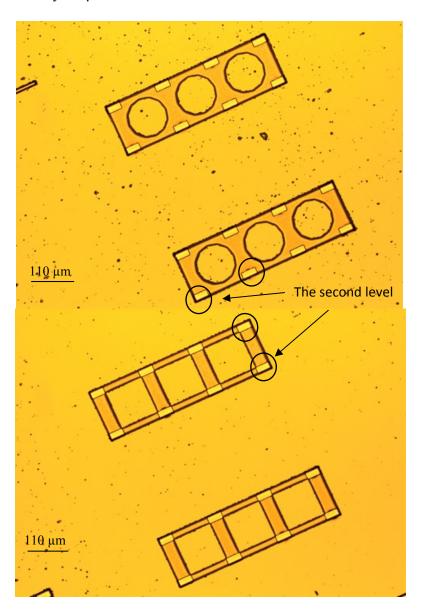

| Figure 66 the second layer of the demo-device2 after the deposition of the see | d layer 105 |

| Figure 67 the second layer of the demo-device2 after developing                | 106         |

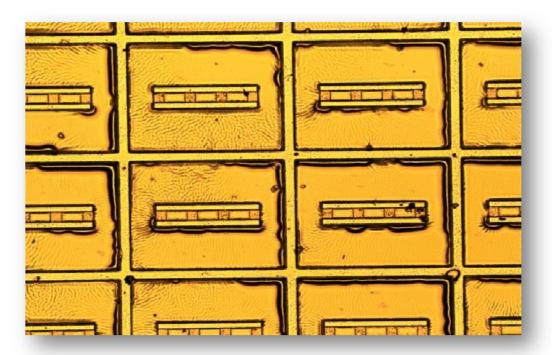

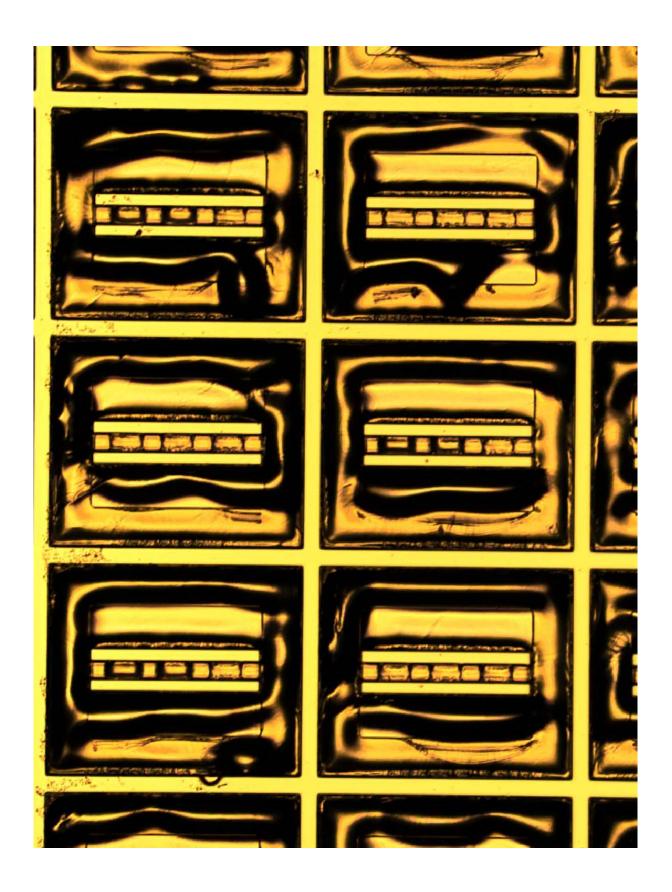

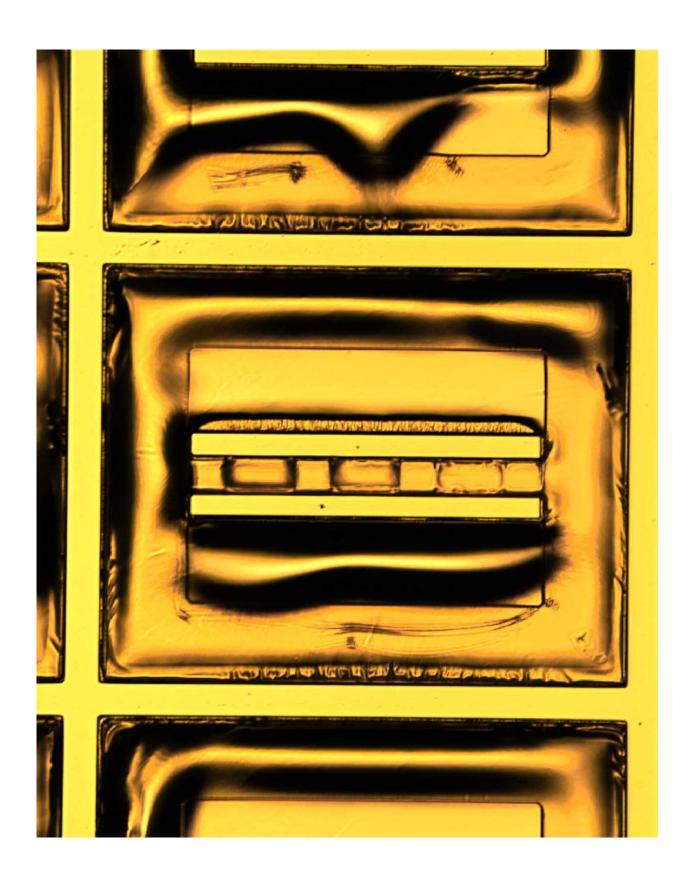

| Figure 68 demo-device2 after fabrication 1                                     | 109         |

| Figure 69 demo-device2 after fabrication 2                                     | 110         |

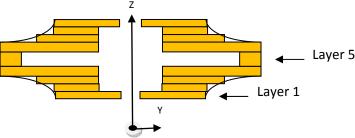

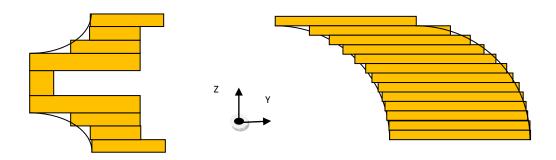

| Figure 70 demonstration of making a device with curve surface                  |             |

| Figure 71 demo-device1 after fabrication (1)                                   | 112         |

| Figure 72 demo-device1 after fabrication (2)                                   | 112         |

| Figure 73 removing of the SU 8                                                 | 115         |

| Figure 74 the photoresist after developing                                     | 117         |

| Figure 75 the photoresist after electroplating                                 | 118         |

| Figure 76.The lips after one hour in the oven                                  | 122         |

| Figure 77 the lips after one hour and fifteen minutes in the oven              | 122         |

| Figure 78 the lips after one hour and thirty minutes in the oven               | 123         |

| Figure 79 the lips after one hour and forty-five minutes in the oven           |             |

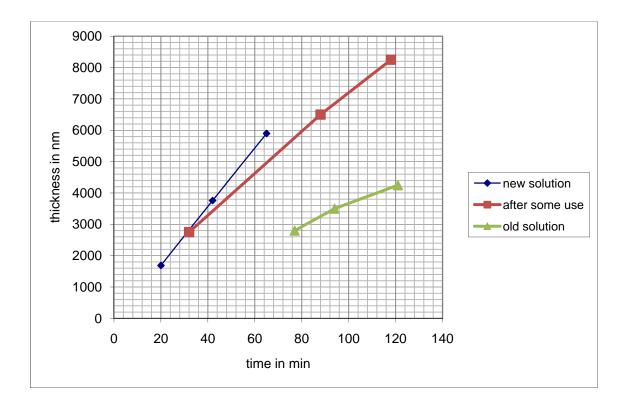

| Figure 80 the deposited ratio                                                  |             |

| Figure 81 the designed holder                                                  | 127         |

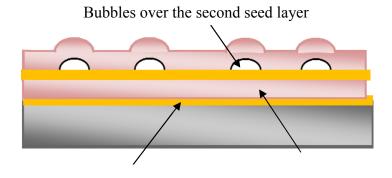

| Figure 82 bubbles appeared in the second level under the photoresist           | 129         |

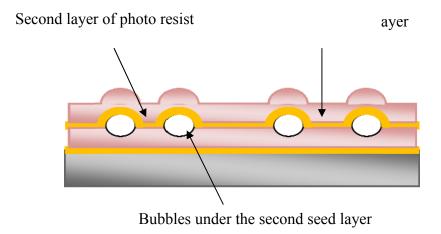

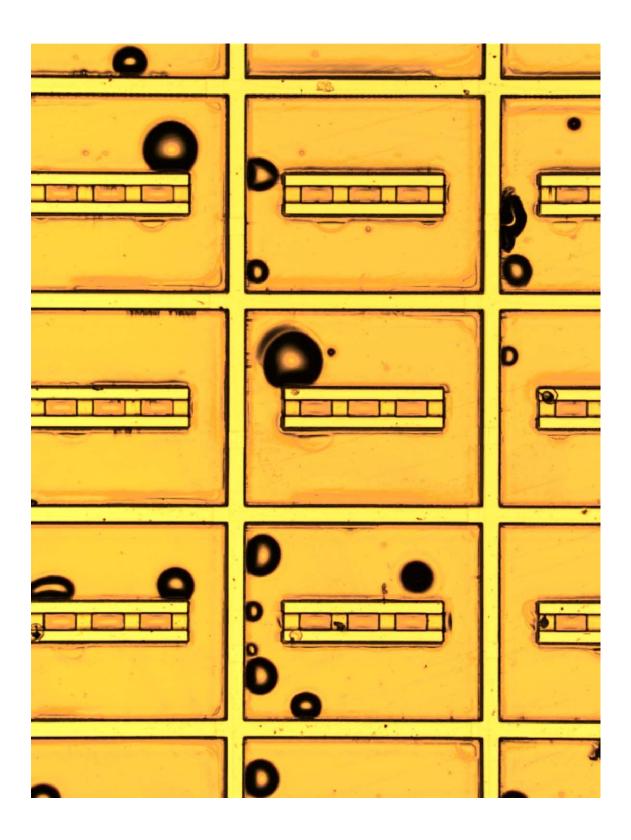

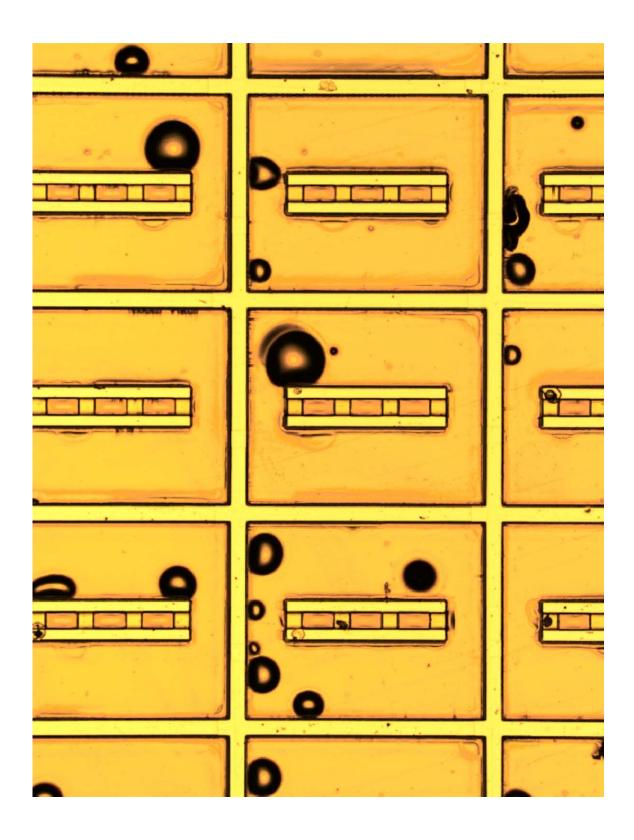

| Figure 83 bubbles appeared under the second level                              | 130         |

| Figure 84 bubbles over the second seed layer                                 | 130 |

|------------------------------------------------------------------------------|-----|

| Figure 85 bubbles under the seed layer                                       | 131 |

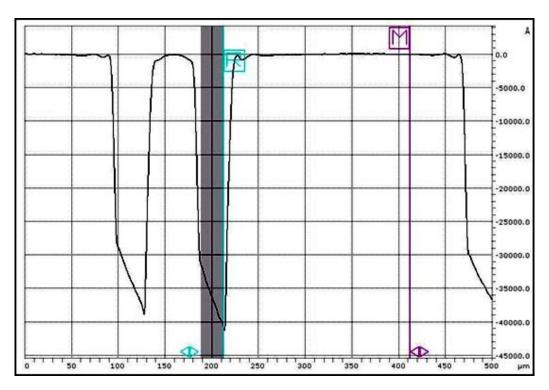

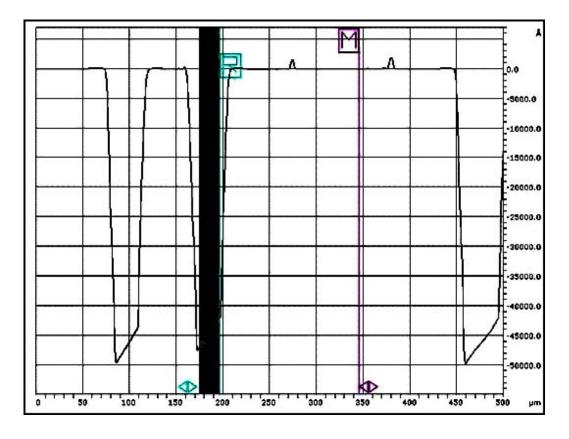

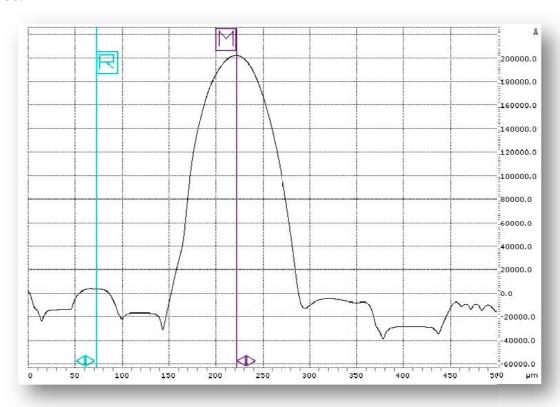

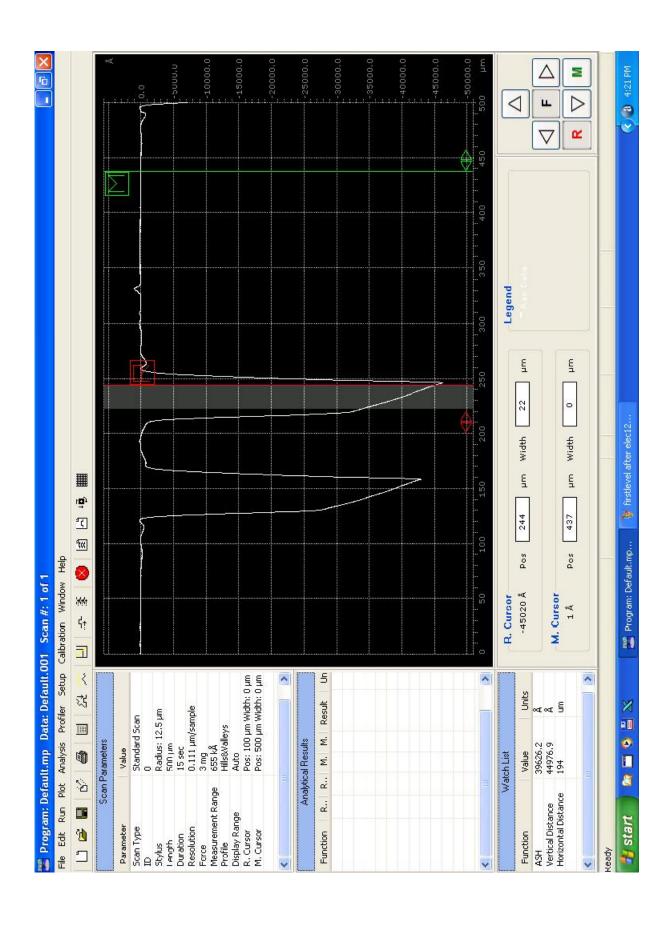

| Figure 86 the height for some bubbles                                        | 131 |

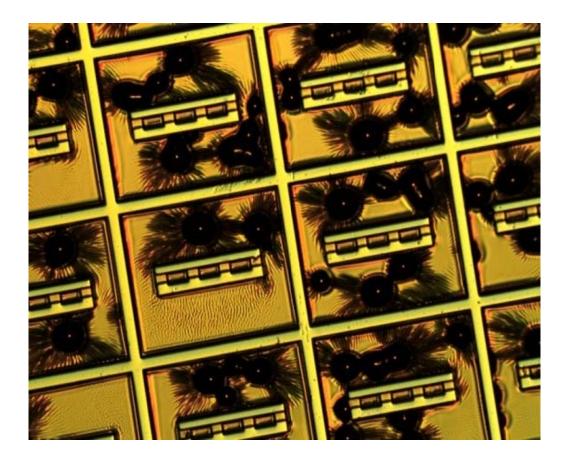

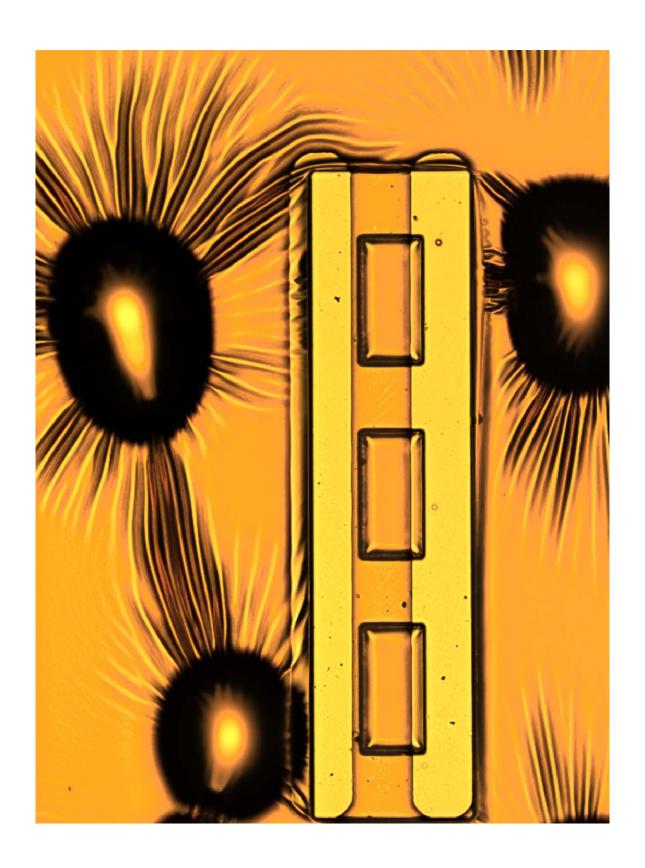

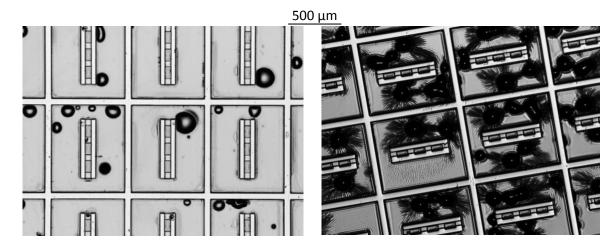

| Figure 87 wrinkled surfaces                                                  | 133 |

| Figure 88 wrinkled surface                                                   | 136 |

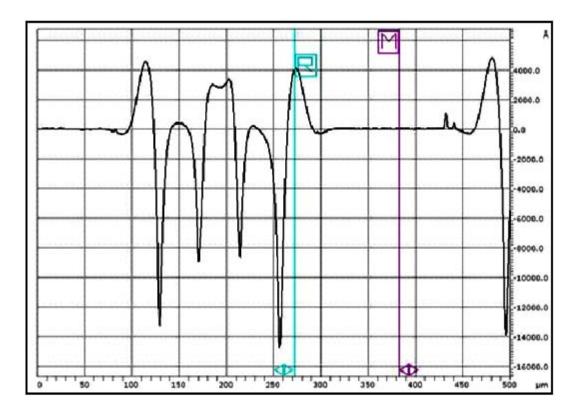

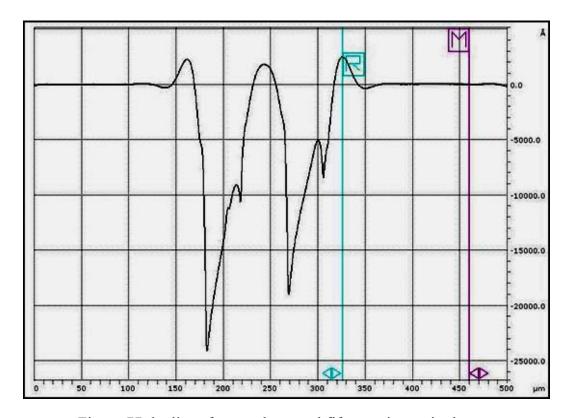

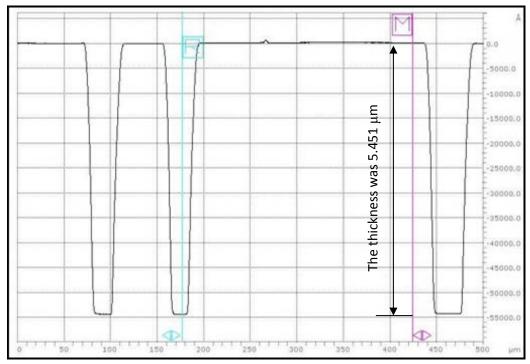

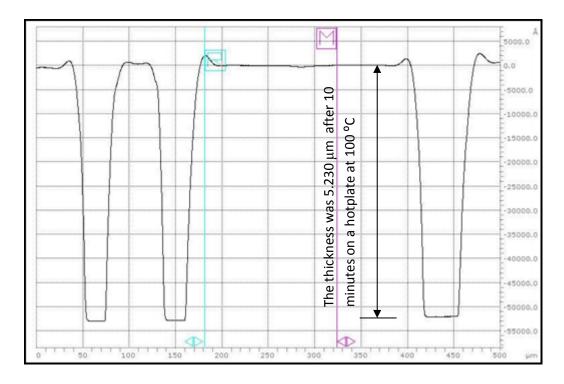

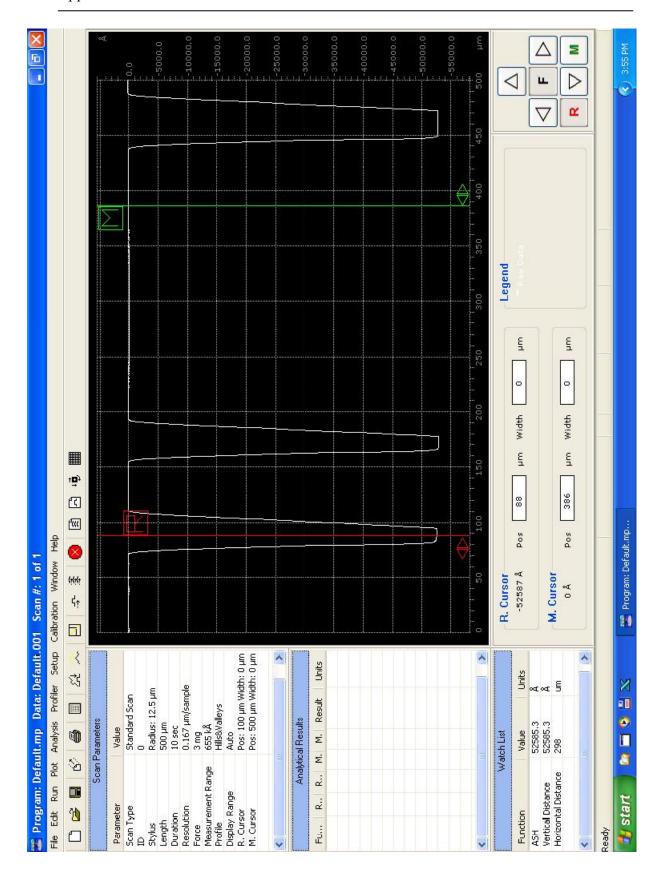

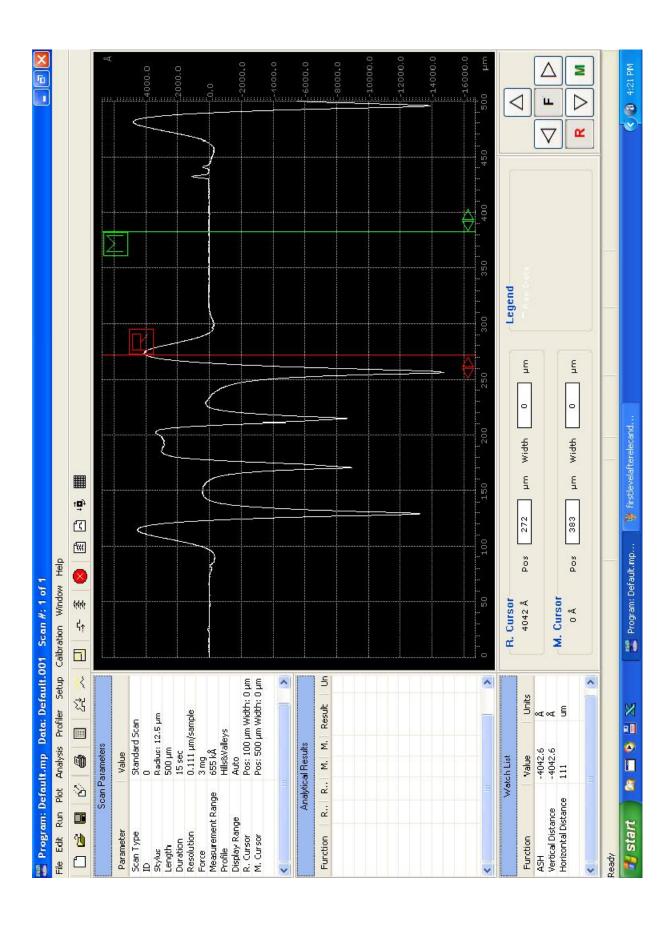

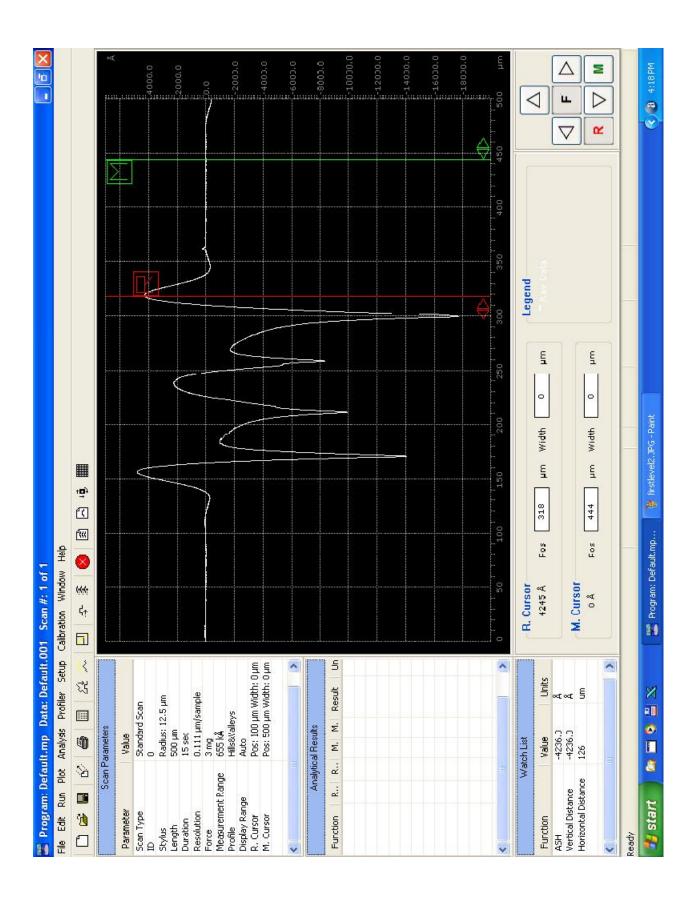

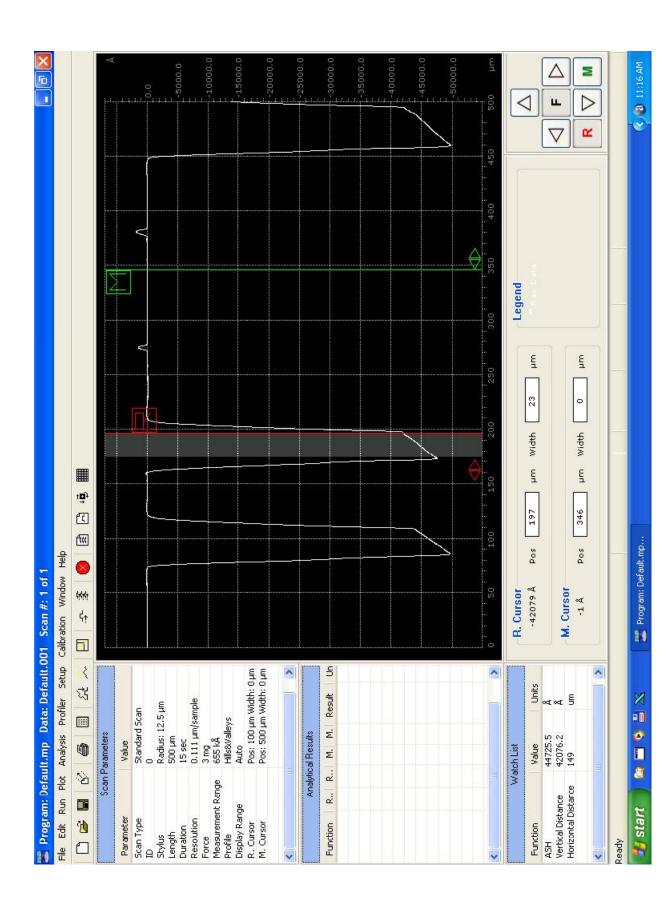

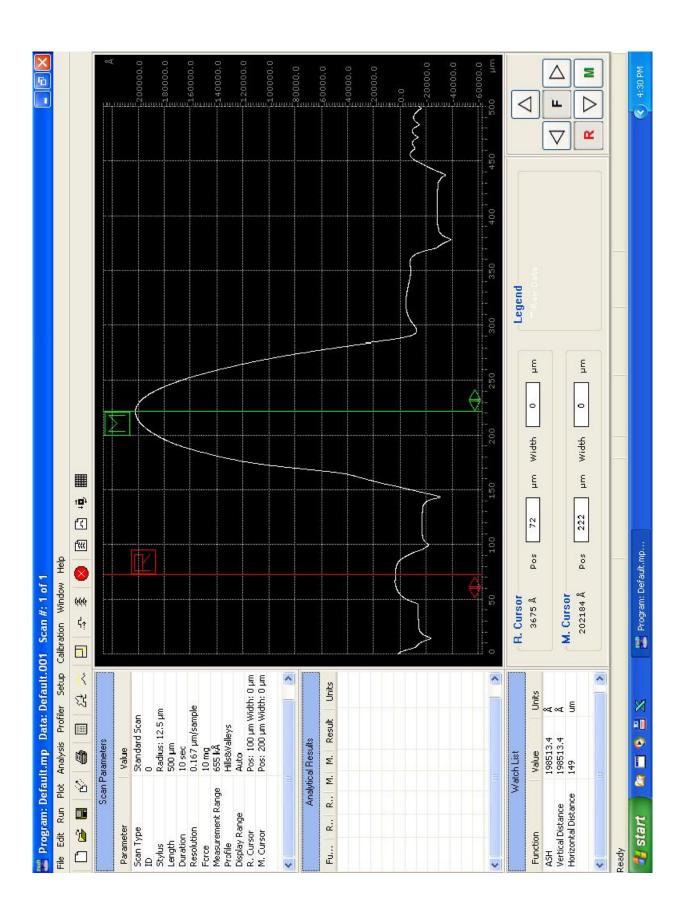

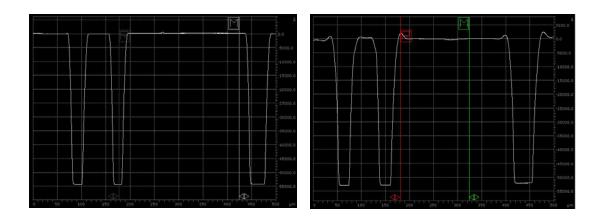

| Figure 89 the thickness of the photoresist "AZ4562" after the development    | 137 |

| Figure 90 The thickness was 5.230 μm after 10 minutes on a hotplate at 100°C | 137 |

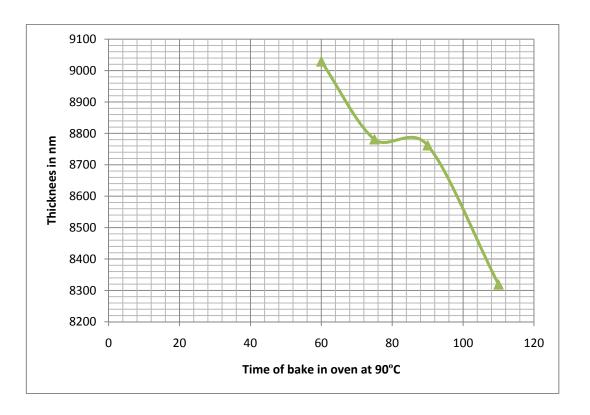

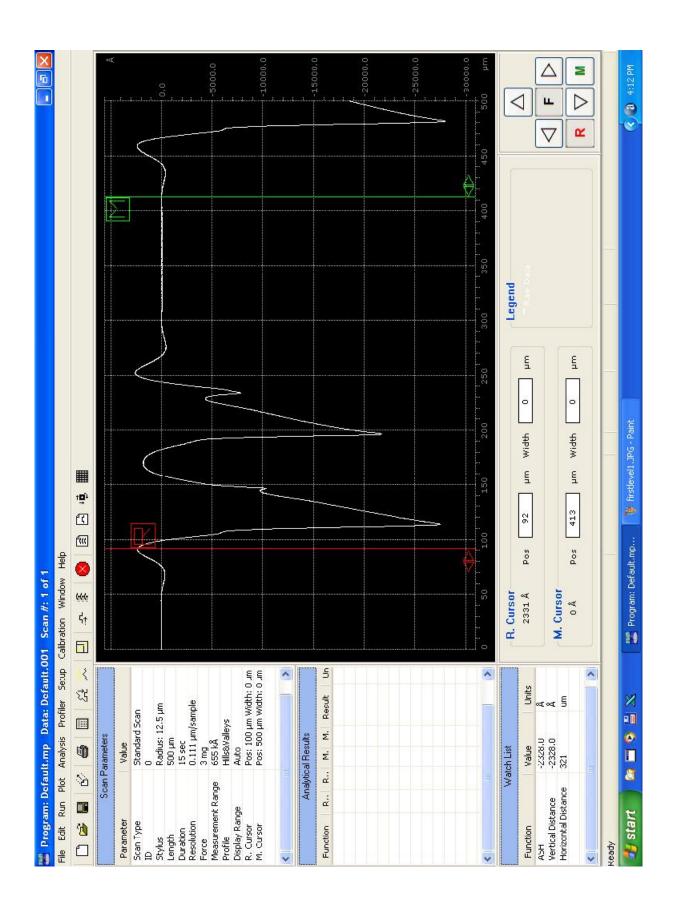

| Figure 91 the shrinking in the photoresist                                   | 138 |

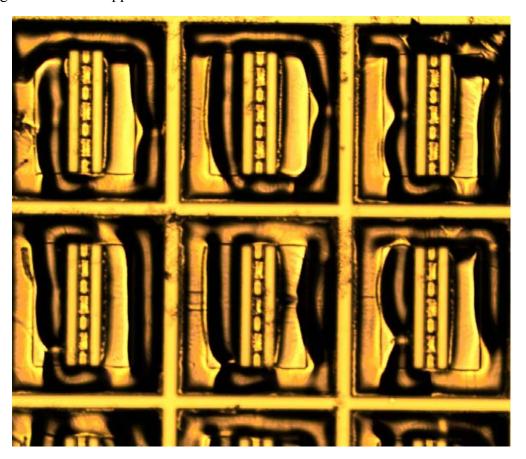

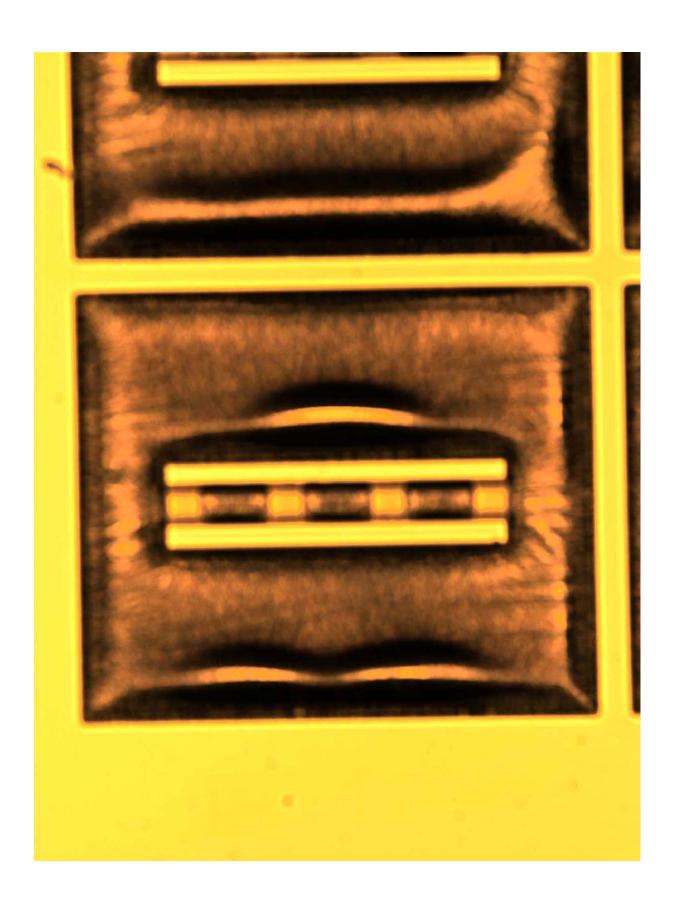

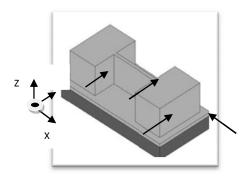

| Figure 92 3D microscope pictures of the demo-device1                         | 139 |

| Figure 93 demo-device2 with 5 layers                                         | 145 |

| Figure 94 demo-device1 with 6 layers                                         | 146 |

| Figure 95 the multi layer planes                                             | 149 |

| Figure 96 the division of the require mould                                  | 150 |

### List of table

| Table 1 the Advantages and Disadvantages the evaporation and sputtering deposition             | [46] |

|------------------------------------------------------------------------------------------------|------|

|                                                                                                | 28   |

| Table 2 the Advantages and Disadvantages the CVD deposition mouthed <sup>[4, 28, 41, 48]</sup> |      |

| Table 3 utilizing polyimide by using multilayer process <sup>[55]</sup>                        | 63   |

| Table 4 the technique of the sacrificial metallic mould <sup>[97]</sup>                        | 69   |

| Table 5 the photoresist thicknesses for demo-device1                                           | 96   |

| Table 6 the photoresist thicknesses for demo-device                                            | 96   |

| Table 7 the thickness of az4562 and S1818 layers                                               | 97   |

### **List of Acronyms**

MEMS Micro Electro Mechanical Systems

NEMS Nano Electro Mechanical Systems

MST Micro Systems Technology

HF hydrofluoric acid

3D three dimensional

RGT resonant gate transistor

MOS Metal-Oxide-Semiconductor

IC integrated circuit

TIJ Thermal Inkjet Technology

LIGA lithography, electroforming, and moulding

AFM atomic force microscope

SCREAM Single Crystal Reactive Etching and Metallization

EFAB electrochemical fabrications

DRIE Deep Reactive-Ion Etching process

SUMMiT Sandia Ultra-planar, Multi-level MEMS Technology

DNA Deoxyribonucleic acid

LOC lab-on-a-chip

GLAD Glancing Angle Deposition

PVD physical Vapor Deposition

CVD Chemical Vapor Deposition

APCVD Atmospheric pressure CVD

LPCVD Low Pressure CVD

PECVD Plasma Enhanced CVD

HDCVD High Density Plasma CVD

UV Ultraviolet

RIBE Reactive-Ion-Beam Etching ECR Electron Cyclotron Resonance ICP Inductively Coupled Plasma

RIE Reactive Ion Etching IB LIGA ion beam LIGA

PMMA polymethylmethacrylate SU 8 Organic Resin Solution

AZ4562 methooxy-propyl acetate (PGMEA)

# Chapter 1

Introduction

#### 1.1. Definition of MEMS

To make small machines which are almost invisible to human eyes has been one of the dreams of mankind. This dream was achieved by a technique called 'MEMS'. It is an acronym for four words 'Micro Electro Mechanical System' and generally refers to the devices that integrate electrical devices and mechanical structures at the micrometer ( $10^{-6}$  m = 0.0000001 m) scale. Similarly, NEMS is an acronym for 'Nano Electro Mechanical System', having devices on nano meter ( $10^{-9}$  m = 0.0000000001 m) scale.

MEMS combine two systems together, Micro-Electronics System and Micro-Mechanical System. Micro-Electronics Systems consist of electronic circuits on silicon chips and Micro-Mechanical Systems are the structures and moving parts of the MEMS device. MEMS are also referred to as micromachines (in Japan), or Micro Systems Technology - MST (in Europe) or microelectromechanical systems (in US)<sup>[1]</sup>.

Micro Electro Mechanical Systems is a term coined around 1989 by Prof. R. Howe to describe an emerging research field, where mechanical elements, like cantilevers or membranes, had been manufactured at a scale more akin to microelectronics circuits. Prof. Howe demonstrated techniques to fabricate micro beams from polycrystalline silicon films. Following this demonstration, Prof. Howe built the prototype polysilicon MEMS, the first fully integrated micromechanical and microelectronic system which he demonstrated in use as a chemical vapour sensor<sup>[2, 3]</sup>. In addition, Micro-Electro-Mechanical Systems (MEMS) consist of extremely tiny mechanical elements, often integrated mechanical elements, sensors, actuators, and electronics on a common silicon substrate through microfabrication technology<sup>[4]</sup>. Previously, sensors and

actuators were the most costly and unreliable part of a macro scale sensory-actuator-electronics system. However, with the advent of this technology "MEMS" these complex electromechanical systems are being manufactured using batch fabrication techniques with drastically reduced cost and improved reliability of the sensors and actuators.

#### 1.2. MEMS Application

As mentioned, MEMS is a class of systems that are physically small. This system technology is miniaturized systems which comprise sensors, actuators and electronic functions thereby opening up a whole range of new applications which would not be possible with purely microelectronic systems. These systems have both electrical and mechanical components.

Sensors and actuators are the two main categories of MEMS. A sensor is a device that measures information from a surrounding environment and provides an electrical output signal in response to the parameter it measures. An actuator is a device that converts an electrical signal into an action. It can create a force to manipulate itself, other mechanical devices, or the surrounding environment to perform some useful function.

More recently a wide range of MEMS applications prototypes have been developed. MEMS are highly miniaturized devices that integrate a number of functions including fluidics, optics, mechanics and electronics on a single silicon chip using traditional integrated circuit process technology. MEMS merge sensing, actuating and computing into miniature systems that enable enhanced levels of perception, control and performance.

The field of Micro Electro Mechanical System has evolved during the last thirteen years from the techniques developed for the microelectronics industry. Nowadays, there are numerous possible applications for MEMS and Nanotechnology, here are a few applications of current interest:

#### 1. Accelerometers

An example application includes advanced sensor technology used for airbag deployment for the automotive industry.

### 2. Biotechnology

Another example of a successful MEMS application is the optical device which is the miniature disposable pressure sensor used to monitor blood pressure in hospitals.

#### 3. Inkjet printer head

One of the most successful MEMS applications is the inkjet printer head. Inkjet printers use a series of nozzles to spray drops of ink directly onto a printing medium.

More applications relate MEMS technology will be mentioned in the next chapters.

#### 1.3. Motivation

Because of the high performance that Micro electro mechanical systems have shown at low cost, the demand for this technique has increased in various fields. Therefore, Micro electro mechanical systems have attracted researchers in many application fields. Hence the dreams of manufacturing mini devices become a reality, as a result of conducting a great variety of basic research into this technology and recently the fabrication technique as a general machining tool in micro scale is also a significant subject.

Since the use of conventional micro machining processes, such as anisotropic etching and surface micro machining, to make the first transistor from silicon in 1947, these techniques were suitable to build devices with two dimensional structures. Until this day, researchers have innovated and developed techniques such as ink jet nozzle arrays in 1978 and in 1982 the silicon was used to fabricate some mechanical components. Recently, in 2007, hybrid techniques used two or more techniques to improve the performance of MEMS. In the next chapter "History of MEMS" I will discuss the developments of MEMS.

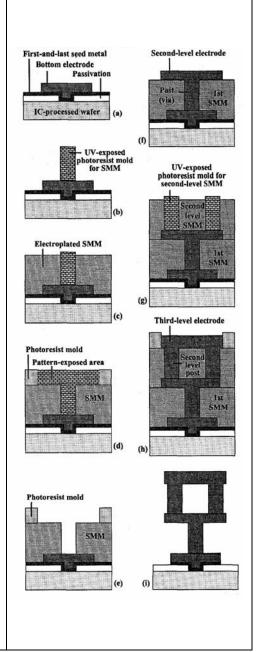

In the 90's a multi layer process was able to produce a three-dimensional structure with dimensions of the order of micrometers. The researchers succeeded in producing a special device and they used three layers and offered new vistas for researchers interested in this technology. From this date until today the researchers have tried to use this technique for an unlimited number of layers. Researchers in some areas succeeded in producing a device with 5 levels, but they did not use conventional techniques. They manipulated the different known conventional techniques to provide a hybrid technique. However, these hybrid techniques usually need high cost of manufacturing time and processing.

On the other hand, all researchers are having great difficulties creating three dimensional (3D) shapes with a high aspect ratio. Moreover, the selection of materials is limited to silicon or glass. Even the LIGA process, which can be used to create a micro structure with a high aspect ratio, cannot create general 3D structures with a curved surface. Also, all researches using the conventional technique in the multi layer process, mentioned that many unexpected problems appeared during the process, such as Lips, wrinkled surfaces and bubbles. After considering previous research that used the multi layer process in their technique, I did not find any research that treated these problems carefully. Most researchers have mentioned these problems in general although some researchers have reported that the problem is in the formation of gas bubbles. That is why all researchers have stopped using the conventional multi layer technique to produce 3D structure.

These issues have made serious limitations on the design and function of MEMS applications. On this account, a new micro fabrication technique satisfying real 3D by using multi layer moulds and a wide material selection is investigated for the mould by the author. In this thesis, a new method is proposed and verified experimentally.

#### 1.4 Objectives

The objective of this work is to find and design a technique which can manufacture a complex 3D shape in micro/ nano scale: this technique should:

- be easy to use and low-cost,

- > be suitable for different materials,

- > save time, "if compared with any other techniques".

To build a 3D structure device with a curved surface in the vertical direction was an aim for many researchers. None of them have been able to reach this aim in an easy way or by using conventional processes, but they have achieved it in complex and expansive ways. With the proposed technique, I will be able for the first time in the MEMS technology to fabricate a curved surface in the vertical direction of the device.

The proposed technique is based on improving conventional techniques and develops a hybrid technique using multiple techniques in one. I use a hybrid technique which consists of:

- ➤ LIGA, LIGA can produce 3D structure, but not a curved surface,

- thin film technique, this technique can produce a 3D structure, but not a curved surface,

- > multi layer technique, which had many problems addressed in this work.

To make a 3D structure, there has to be a thin film deposited and then applied to the LIGA process, one layer on top of the other. The whole structure can then be stacked together using multi layers to meet the device requirement. This technique has improved the conventional technique. This improvement has made the MEMS technology cheap and efficient compared with any previous technique. With this technique I improved the LIGA process and any structure could be made using any material.

In this work, the author has researched a suitable material for the dissolvable mould and the technique that should be followed. All of the information available from previous research was somewhat conflicting and it was not clear which information should be followed. It was decided to do experiments to collect information about these materials and discover if they were good for these techniques or not. The experiments had two goals; to make demodevices and discover the best material for the mould in this technique.

This work has solved many problems appearing in MEMS technology by using the conventional technique for the first time. The author has conducted many experiments to address many problems such as lips, bubbles and wrinkled surfaces and has found a good and effective technique to solve them.

# 1.2. Research Program

| Task | Task name                                                       | 2007 2008 |    | 2009 |    |    |    | 2010 |    |    |    |    |    |

|------|-----------------------------------------------------------------|-----------|----|------|----|----|----|------|----|----|----|----|----|

| Task | Task name                                                       | Q4        | Q1 | Q2   | Q3 | Q4 | Q1 | Q2   | Q3 | Q4 | Q1 | Q2 | Q3 |

| 1    | Literature review on MEMS and its development                   |           |    |      |    |    |    |      |    |    |    |    |    |

| 2    | Identification of difficulties on building 3D structure in MEMS |           | 1  |      |    |    |    |      |    |    |    |    |    |

| 3    | Proposal of the project                                         |           |    |      |    |    |    |      |    |    |    |    |    |

| 4    | Looking for published relating to the proposed idea             |           |    |      |    |    |    |      |    |    |    |    |    |

| 5    | First year report                                               |           |    |      |    |    |    |      |    |    |    |    |    |

| 6    | Visiting an Institute of Microstructure Technology in Germany   |           |    |      |    |    |    |      |    |    |    |    |    |

| 7    | Training courses in E-beam lithography                          |           |    |      |    |    |    |      |    |    |    |    |    |

| 8    | Executing the experimental part                                 |           |    |      |    |    |    |      |    |    |    |    |    |

| 9    | Participate conference paper                                    |           |    |      |    | (  |    |      |    |    |    |    |    |

| 10   | Second year report                                              |           |    |      |    |    |    |      |    |    |    |    |    |

| 11   | Prepare to journal paper                                        |           |    |      |    |    |    |      |    |    |    |    |    |

| 12   | Writing up the thesis                                           |           |    |      |    |    |    |      |    |    |    |    |    |

| 13   | Submitted the thesis                                            |           |    |      |    |    |    |      |    |    |    |    |    |

#### 1.3 Structure of the Thesis

To achieve the objectives of this research, the very first step was to understand the development of the field of micro electro mechanical system. In chapter 2 presents a Literature review in MEMS and I divided it in three sections. First section gives us a general introduction to the history of the MEMS and its development during these fifty years and to give the reader a good knowledge about this technique that I improved its performance by producing directly a device with 3D structure. The MEMS fabrication is a set of technologies used to manufacture structures with micrometric features. This task is a new technology and it is different from the traditional fabrication techniques such as milling, drilling, etc. In section 2 gives us an overview of the MEMS fabrication that helps the reader to understand the technique that I have used and improved. In the section 3, I am going to discuss some of the previous research and compare it with the proposed technique. The thesis concludes with a summary of this work and recommendations for future research. A number of important outcomes of this research are highlighted.

I will present in chapter 3 a guide line and demonstrate my proposed technique and how a device with a curve could be produced. This technique is a hybrid technique which consists of LIGA and thin film technique. The detailed explanation of this technique is in chapter 4. In this chapter I demonstrate how a device can be built by repeating two masks and when a successful product has been produced through this procedure, I have applied this technique using multi masks to fabricate a relatively complex shaped-device. Chapter 5 shows the problems and difficulties that I met during this work and a discussion about how these problems can be treated.

The author has contributed to the MEMS technology a new technique which can build a 3D complex shape device using conventional techniques. Therefore, he has offered a technique which saved time and cost if compared with any other techniques. The author published the idea in a conference in Barcelona in Spain in 2008 and submitted the work to Proceedings of the Institution of Mechanical Engineers, Part B, and Journal of Engineering Manufacture in June 2010. Both the paper conference and the journal paper are attached in Appendix A.12, A.13.

# Chapter 2

Literature review

### 2.1. History of the MEMS

The field of Micro Electro Mechanical Systems (MEMS) has evolved during the last fifty years from techniques developed for the microelectronics industry. The technology for fabrication of microstructures in silicon has clearly played a key role in revolutionizing the impact of microelectronics on society. The fact that computers, that were once the size of entire rooms, have been replaced by small laptop computers of much higher performance illustrates this clearly.

For a comprehensive understanding of this technique of the MEMS technology I should know the history and the development that it has had during the last years. Consideration of the development that this technique has had, gives us a vision of how the researchers attention and their attempts have and still are ongoing to improve the performance of this technology. They have researched a way to make a device with a 3D structure in micro/nano scale. During these years this technology had amazing development which has started in the fifties of the last century with the discovery of the transistor and then the "integrated circuits (ICs)" which was a limited function and until today which the MEMs device interned in all of my devices that have an unlimited number of functions.

Until today researchers still try to support this technique to build directly a device with a 3D structure. Like any research, all of these researches have advantages and disadvantages. In this chapter I have tried to put in the hand of the reader a general introduction to the history of the MEMS and its development during these fifty years and to give him a good knowledge about this technique that I improved to produce directly a device with a 3D structure which I think will help mankind in our life.

#### 2.1.1. General Historical Overview

In 1947 at Bell Telephone Laboratories, the first transistor was invented by William Shockley, John Bardeen, and Walter Brattain<sup>[5]</sup>. The first transistor was made from germanium, a semi conductive chemical material.

In 1954, Charles S. Smith discovered the Piezoresistive Effect in Silicon and Germanium in Bell Telephone Laboratories<sup>[6]</sup>. He found that silicon and germanium could sense air or water pressure better than metal. These significant discoveries led to the development of the concept of "integrated circuits (ICs)". In 1958, Jack Kilby in Texas Instruments made the first "integrated circuits (ICs)". This IC was built as a "Solid Circuit" on one germanium chip: 1 transistor, 3 resistors, and 1 capacitor, which was made all together on one substrate and the whole device was made to a very small scale <sup>[4,7]</sup>.

In 1959, Richard Feynman gave a talk "There's Plenty of Room at the Bottom" at a meeting of the American Physical Society. In his talk he introduced the possibility of manipulating matter on an atomic scale and he challenged his audience to design and build a tiny motor or to write the information from a page of a book on a surface by using a scale of 1/25,000<sup>[8]</sup>.

In the 1950s, the use of electropolishing HF (hydrofluoric acid) showed the potential for deep etching in silicon substrates<sup>[9]</sup>. However the first silicon (pressure) sensor was fabricated using isotropic etching by Honeywell in 1962. This technology was a combination of wet and dry etching and oxidation<sup>[10]</sup>.

In the 1960's, H. A. Waggener developed a technique called "Electrochemically Controlled Thinning of Silicon". This technique is known

now as the bulk micromachining process. Bulk micromachining is a way to etch the bulk of the silicon substrate leaving behind the desired geometries. Since its foundation, bulk micromachining has remained a very powerful method for fabricating micromechanical elements such as micro-fluidic channels, nozzles, diaphragms, suspension beams and other moving or structural elements. The first surface micromachined structures were fabricated in the 1960s using metal mechanical layers<sup>[11]</sup>. Surface micromachining involves the formation of mechanical structures in thin films formed on the surface of the wafer. The early 1980s saw the growth of silicon based surface micromachining using polysilicon as the mechanical layer<sup>[12]</sup>.

In Westinghouse 1964, Harvey Nathanson produced the first fabricated MEMS device. His device joined a mechanical component with electronic elements and was called a resonant gate transistor (RGT)<sup>[13, 14]</sup>. The RGT was a gold resonating MOS (Metal-Oxide-Semiconductor) gate structure, in which a layer of material is deposited between structural layers for mechanical separation and isolation. This layer is removed during the release etch to free the structural layers and to allow mechanical devices to move relative to the substrate. A layer is releasable when a sacrificial layer separates it from the substrate. The device was around one millimetre long and it responded to a very narrow range of electrical input signals. It was utilized as a frequency filter for ICs<sup>[14]</sup>. The application of the sacrificial layer technique to micromachining in 1985 gave rise to surface micromachining, in which the Si substrate is primarily used as a mechanical support upon which the micromechanical elements are fabricated<sup>[5]</sup>.

The world's first single complete chip microprocessor was generated and made in 1971 and was introduced by Intel as the ''The Intel 4004''. The first application of the processor has to power the Busicom calculator<sup>[15]</sup>, figure 1.

Figure 1 the Intel 4004 Microprocessor, Busicom calculator<sup>[16]</sup>

Since 1970, the complexity of chips has doubled every two to three years and engineers have tried to minimize the chip and at the same time contain several functions.

In 1979 Hewlett Packard developed the Thermal Inkjet Technology (TIJ). In this technique the ink squirts through an array of nozzles onto paper. The ink jet nozzle array was the first MEMS devices to have three-dimensional structures with dimensions. The minimum dimension of manufactured devices and ICs has decreased from 20 microns to the sub micron levels of today<sup>[17, 18]</sup>.

The field of MEMS evolved during the 1980s giving the world the first product of micromachining parts (such as pressure-sensor diaphragms or accelerometer suspension beams) for Si microsensors<sup>[5]</sup>.

In 1982, Kurt Petersen published a paper, which was called "Silicon as a Mechanical Material". The paper provided information on material properties and etching data for silicon and was instrumental in enticing the scientific community into exploration of these areas<sup>[19]</sup>. In the same year a team at the Karlsruhe

Nuclear Research Center in Germany, developed a new process called LIGA<sup>[20, 21]</sup>. The abbreviation LIGA is an acronym for the German words, "Lithographie", "Galvanik", and "Abformung" (lithography, electroforming, and moulding). This process was developed under the leadership of Prof. Dr. E.W. Becker and Dr. W. Ehrfeld, using X ray lithography for mask exposure, electroforming to form the metallic parts<sup>[20]</sup> and moulding to produce micro parts with plastic, metal, ceramics, or their combinations<sup>[22]</sup>. This process is important in microsystems manufacturing because it allows for the manufacturing of high aspect ratio microstructures. High aspect ratio structures are very thin, or narrow, and tall, such as a channel. LIGA can achieve ratios as high as 100:1 and LIGA structures have precise dimensions and low surface roughness<sup>[21]</sup>.

In 1986, Binnig and Gerber from IBM Research Laboratory in Al-maden, California developed a micro device called the atomic force microscope (AFM). The AFM is a device that maps the surface of an atomic structure by measuring the force acting on the tip of a micro scale cantilever with a sharp tip or probe at its end. The cantilever is usually silicon or silicon nitride. The ultimate resolution of the AFM is down to about 10 Å<sup>[23]</sup>.

In 1980s the development of using this technique "MEMS" was very big and had many successfully researched and there were many new applications such as the Sensonor Crash sensor (Airbag) in 1985<sup>[24]</sup>, the first rotary electrostatic side drive motors in 1988 by Muller and the first polysilicon surface micromachined MEMS device integrated with circuits and lateral comb drive emerged where structures move laterally to the surface in 1989<sup>[25]</sup>.

In the 1990s, a great increase in the number of devices and applications greatly expanded the sphere of influence of MEMS. For example, but not

exclusively, in 1992 at Cornell University, a bulk micromachining process was developed called Single Crystal Reactive Etching and Metallization (SCREAM). It was developed to fabricate released microstructures from single crystal silicon and single crystal Gallium Arsenide (GaAs)<sup>[26]</sup>.

In 1993, Ikuta and Hirowatari developed a new process called IH process (Integrated Harden Polymer Stereo Lithography)" to conceive 3D objects with a high aspect ratio and a curved surface. This process is applicable for micro structures made of both polymer and metals and mainly used the micro stereo lithography and electro plating and it had been proposed in MEMS'93<sup>[27]</sup>.

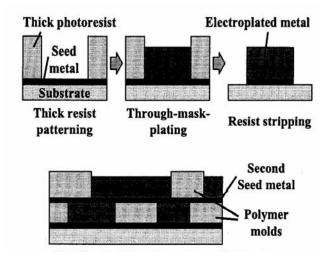

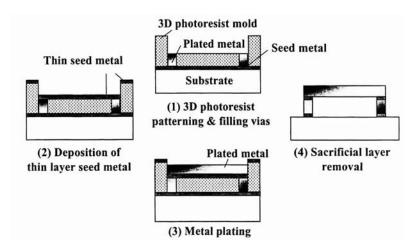

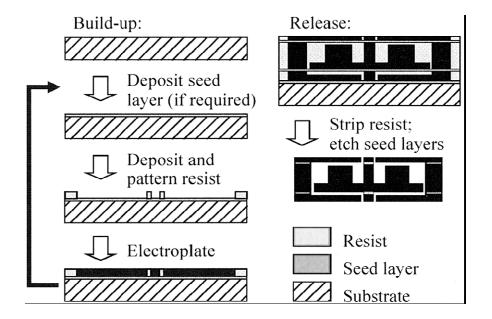

In the same year a new technique appeared which was called multi layer process. Figure 2 shows the conventional plating-through-mask technology and its multi layer formation. Most fabrication processes for thick metallic microstructures have their basis on this technology. The thick photo resist mould blocks the current flow in the electroplating bath, so that the electroplating happens only on the open-seed area. This technique has advanced in the last years such as the technique called EFAB in California<sup>[15]</sup>.

Figure 2 the process of multi layer using seed layers<sup>[28]</sup>

In 1994, Bosch, a company from Germany, developed a special Deep Reactive-Ion Etching (DRIE) process. The DRIE process stands for Deep Reactive Ion Etching and is a dry etch micromachining method<sup>[29]</sup>.

In 1998, another surface micromachining foundry began. This one was started at Sandia National Laboratories and the process was called SUMMiT IV. This process uses a five-layer polycrystalline silicon and later evolved into surface micromachining process. SUMMiT is an acronym for "Sandia Ultraplanar, Multi-level MEMS Technology<sup>[30]</sup>.

In the same year, Kim and Mark demonstrated how a copper coil could be manufactured using microsurface machines and electroplating<sup>[31]</sup>.

In addition, the 1990s witnessed the development of many techniques in this technology: such as embossing technology which appeared in the Karlsruhe Nuclear Research Center in Germany the Karlsruhe Nuclear Research Center in Germany as part of LIGA process<sup>[32]</sup>.

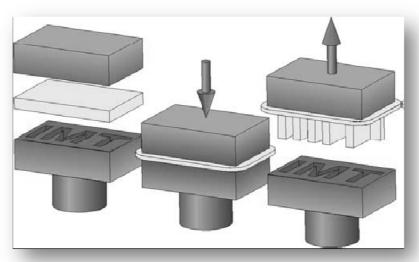

Figure 3 hot Embossing<sup>[32]</sup>

The increasing interest shown in sensors, actuators and other micro flow devices based on microfabrication techniques stems from the fact that they offer advantages such as small size, fast response times and small sample and dead volumes. The microfabrication techniques make multi-function systems possible, integrating sensors (e.g. for flow and pressure), actuators (e.g. valves and pumps), electronics and passive components (e.g. channels, valves and filters)<sup>[33]</sup>.

MEMS devices became commercially available in the early 2000s and it entered into our lives, in mobile phones, in automobiles and in home devices. Although time and cost have been reduced by using this technology, researchers continue trying to improve this technique and they are still discovering new ways to combine MEMS sensors and actuators with emerging bioMEMS technology. Applications include drug delivery systems, insulin pumps, DNA arrays, lab-on-a-chip (LOC), glucometers, neural probe arrays, and microfluidics, just to name a few. The area of bioMEMS has only just begun to be explored. Research and development at this time is occurring at a very rapid pace.

Since 2000 there has been a huge growth in the number of devices and many applications have appeared, (too many to mention individually). Nevertheless, I am going to mention a few particularly relevant examples:

In 2001, Metz, Holzer and Renaud developed a polyimide-based microfluidic device. They present a paper which describes the fabrication of the flexible microfluidic channels in various shapes and with a wide range of dimensions<sup>[34]</sup>.

To improve the Three-dimensional structures of the MEMS/NEMS device, in 2003 Kennedy, Jensen and Brett found a new way, which used the unique Glancing Angle Deposition (GLAD) technique to deposit a thin film<sup>[35]</sup>, Figure 4.

Figure 4 glancing Angle Deposition<sup>[35]</sup>

In year, 2005, an application from Moon, Lee and Kwon appeared which improved the LIGA process. They demonstrated a novel fabrication technology of the microneedle array. The fabrication technology consists of a vertical deep X-ray exposure and a successive inclined deep X-ray exposure with a deep X-ray mask whose pattern has a hollow triangular array<sup>[36]</sup>.

In 2004, Karam and Casler introduced a novel technique "A new 3D, direct-write, sub-micron microfabrication process that achieves true optical, mechatronic and packaging integration on glass-ceramic substrates". In this technique a laser beam was used to make a pattern<sup>[37]</sup>.

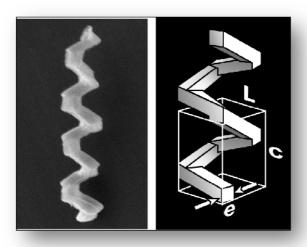

The researchers knew the difficulty in designing a 3D structure in this scale and they researched and are still researching to find a technique to make it perfectly. Figure 5 is an example device which was produced in 2006 by Harutaka

Mekaru et al. The researchers introduced a paper "Fabrication of a spiral microcoil using a 3D-LIGA process". In this paper they improved the LIGA process and they developed the 3D X-ray lithography and the warm injection moulding technology with the unscrewing release mechanism<sup>[38]</sup>.

Figure 5 spiral microcoil using a 3D-LIGA process<sup>[38]</sup>

In this section I have offered some development in the MEMS technology and I have demonstrated its history. Microsystems continue getting smaller. The applications and growth for MEMS and NEMS are endless and will continue to find their way into many aspects of our everyday lives. In this short history I have seen the development of this technology, in the beginning a small integrate circle with limited functions, then a computer the size of a house then in these days to a hand size computer with high performance. All of these developments have happened only in the last 50 years. From this the reader can see the amount of research that brought this technology to this efficiency and I can see the amount of demand to improve this technology more.

After this introduction to the MEMS history and its development, I have attempted to clarify the most important developments that have taken place in this new technology, but I know fully that I did not give the subject the correct attention, because it will take us a lot of time, and I have chosen to focus on the crucial points only. Now it is time to understand the procedure needed to produce a device with this technique.

## 2.2. Review of MEMS fabrication process

As seen in the first section this technique is a new technique if it is compared with any other processes such as casting or milling. This Micro fabrication is a set of technologies used to manufacture structures with micrometric features. This task can unfortunately not rely on the traditional fabrication techniques such as milling, drilling, turning, forging and casting because of the scale. The fabrication techniques have to come from another source<sup>[1]</sup>. This technique needs a special environment and must take place in an area which is called clean room. In this section I will give an overview of the MEMS fabrication "only the conventional techniques" that helps the reader to understand the technique that I have used and improved.

## 2.2.1. General description

MEMS technology is based on a number of tools and methodologies that are used to form small structures with dimensions in the micrometer scale. The important parts of this technology have been adopted from integrated circuit technology. For example, most devices are installed and built on wafers of silicon, such as ICs. The structures are realized in thin films of materials. They are patterned using lithography methods<sup>[39, 40]</sup>.

Generally, the lithography method starts by a surface preparation step like almost all microfabrication processes. In order to remove moisture, the wafers are baked <sup>[41]</sup>. The second step is the depositing of a thin film of metal on a substrate wafer usually silicon, in a process called deposition process or coating the substrate wafer directly with a special organic polymer (sensitive material), which is sensitive to light or X-ray, using a spinning process and called spin-coating. In

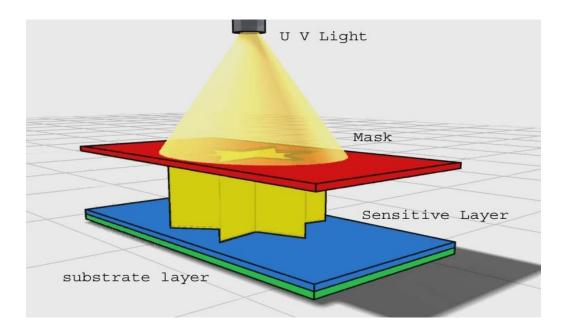

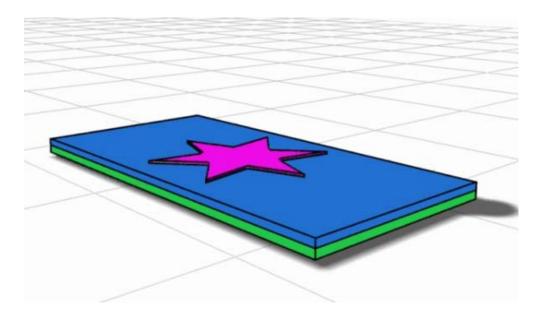

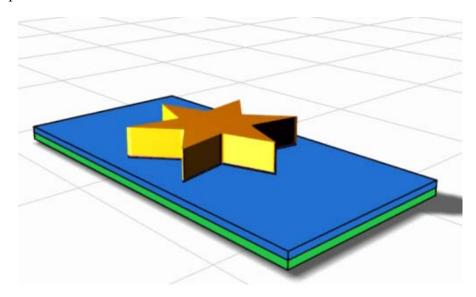

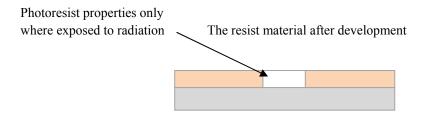

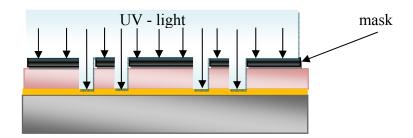

this process the polymer is poured on the substrate which is then set to high-speed rotation, spreading the photo resist in a thin-film with very uniform thickness. The polymer solvent is then evaporated by baking on a hotplate or in an oven. This is the baking process. Then a patterned mask is used via lithography methods, this mask has the negative shape of the desirable device in 2D, then is aligned on the organic polymer. The organic polymer is then exposed to ultraviolet (UV) light of a suitable wavelength, by photolithographic imaging in a process called pattern transfer. In this process the light passes through the shape in the mask onto the sensitive layer, Figure 6, the light changes the property of considered zone. The exposure time depends on the thickness of the organic polymer.

Figure 6 the light passes through the mask

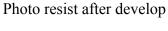

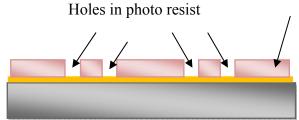

Next the sample is immersed in a special chemical solution, which removes the material that is exposed to UV light and leaves holes on the organic polymer, Figure 7, which represents the inverse of the desirable device structure. This process is called development<sup>[42, 43]</sup>.

Figure 7 transfer the 2D configuration

In some processes these holes are filled with a desirable material, Figure 8, this is the process that will be used in this research. In other processes the thin metal films deposited on the substrate wafer or the substance wafer is etched with features corresponding exactly to those holes, using the etching process. All of these processes will be discussed later.

Figure 8 Deposited material

In effect, this organic polymer is used as a sacrificial layer. This sacrificial layer is required to keep the other layers separated as the structure is being built up but is dissolved in the very last step allowing selective parts of the structure freedom to move<sup>[28]</sup>. The 2D configuration of the desirable device is drawn on a mask and the light passes through the mask to transfer the 2D onto the sensitive layer. The conversion into 3D depends on the thickness of the deposited layer or on the depth of the etching process. Thus this process is called 2.5D<sup>[27, 44, 45]</sup>. In other words, with this technique, I can only build a device that I can draw in 2 dimensions. This is the main disadvantage of MEMS technology. It cannot make the structure of the desirable device directly in 3D. In recent years researchers have developed many methods to improve the performance of the MEMS technology.

# 2.2.2. Depositing thin film

The ability to deposit thin films of substrate material is one of the major steps in MEMS processing. To make a device I should create a layer over this substrate wafer and I call this layer a thin film. How can I make this thin film over the substrate material? The process to make it is called deposition of thin film. Common deposition films include polysilicon, silicon nitride, silicon dioxide, tungsten, and aluminium. There are a number of different techniques that facilitate the deposition or formation of very thin films. MEMS deposition technology can be classified in two groups: chemical reaction and physical reaction<sup>[4, 41]</sup>.

### 2.2.2.1. Depositions resulting from physical reaction

In this process the deposited material is physically moved on to the substrate material. In other words, there is no chemical which forms the deposited material on the substrate material. Like chemical deposition, physical deposition comprises many different techniques<sup>[4]</sup>.

Within the physical deposition process there are many different types of technique to do this process but the common one is physical Vapor Deposition (PVD). PVD covers a number of deposition technologies in which a material is released from a source and transferred to the substrate. The two most important technologies are evaporation and sputtering. Table 1 shows us the Advantages and Disadvantages of each.

|               | Evaporation                                                                                                      | Sputtering                                                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Advantages    | high film deposition rates excellent purity of the film because of the high vacuum condition used by evaporation | synthesis of ultrathin films with minimal impurity easily controllable process parameters                       |

| Disadvantages | step coverage is more difficult to improve by evaporation than by sputtering                                     | High capital expenses are required  The rates of deposition of some materials (such as SiO2) are relatively low |

Table 1 the Advantages and Disadvantages the evaporation and sputtering deposition<sup>[46]</sup>

### 2.2.2.2. Depositions resulting from chemical reactions

Chemical deposition is a chemical process for depositing thin films of various materials. In this process the substrate layer is exposed to one or more volatile materials, which react and/or decompose on the substrate surface to produce the desired deposit<sup>[4, 28, 41, 47]</sup>. Under the chemical deposition process there are many different types of technique to do this process but the common one is Chemical Vapor Deposition (CVD).

Chemical vapor deposition (CVD) can be defined as a deposition technique, in which chemical components react in the vapor phase on a surface, to form a solid film. In this process the substrate material is placed inside a reactor to which a number gas is supplied. The fundamental principle of the process is that a chemical reaction takes place between the source gases. The product of reaction is a solid material which condenses on all surfaces inside the reactor<sup>[28, 48]</sup>. The four most important CVD technologies in MEMS are Atmospheric pressure CVD (APCVD), Low Pressure CVD (LPCVD), Plasma Enhanced CVD

(PECVD), and High Density Plasma CVD (HDCVD). Table 2 shows us the Advantages and Disadvantages of each.

|               | Atmospheric<br>pressure CVD<br>(APCVD)                          | Low Pressure CVD (LPCVD)                                                                                                   | Plasma Enhanced<br>CVD (PECVD)                                                                                                        | High Density<br>Plasma CVD<br>(HDCVD)                                                                                                                                                  |

|---------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advantages    | Simple reactor design  High deposition rates  Low temperature   | Excellent purity Excellent uniformity Good step coverage Lange wafer capacity Greater control of thickness and resistivity | Low temperature High deposition rates Good step coverage Better film composition adjustment Wider control of film density film stress | Low temperature High deposition rates Good step coverage Better film composition adjustment Wider control of film density film stress Improved gap fill More planarization Denser film |

| Disadvantages | Particle contamination  Gas phase reactions  Poor step coverage | High temperature Slow deposition rate                                                                                      | Chemical and particle contamination  Low film density                                                                                 | Plasma induced film damage Process complexity                                                                                                                                          |

Table 2 the Advantages and Disadvantages the CVD deposition mouthed  $^{[4,\,28,\,41,\,48]}$

Within the chemical deposition process there are many other different types of technique. For example, oxidation, dry oxidation, wet oxidation, selective oxidation, electro deposition, epitaxy, and thermal oxidation<sup>[48]</sup>

## 2.2.3. Electrodeposition

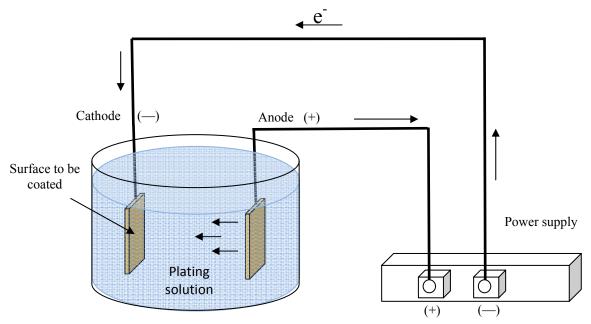

Electroplating or electrodeposition is a plating process that uses electrical current to deposit a desired material from a solution and coat a conductive surface with a thin layer of the material. In this process a substrate is placed in a liquid solution (plating solution) Figure 9. The part to be plated (the substrate wafer) is the cathode of the circuit. The anode is made of the metal to be plated on the part. Both components are immersed in the plating solution, which contains one or more dissolved metal salts.

Figure 9 process of the electroplating

The anode and cathode are both connected to an external supply of direct electrical current. The anode is connected to the positive terminal of the supply, and the cathode (the substrate wafer) is connected to the negative terminal. When the external power supply is switched on, the metal at the anode is oxidized from the zero valence state to form cations with a positive charge. These cations associate with the anions in the solution. The cations are reduced at the cathode to

deposit in the metallic, zero valence state. For example, in an acid solution, copper is oxidized at the anode to Cu<sup>2+</sup> by losing two electrons. The Cu<sup>2+</sup> associates with the anion SO<sub>4</sub><sup>2-</sup> in the solution to form copper sulphate. At the cathode, the Cu<sup>2+</sup> is reduced to metallic copper by gaining two electrons. The result is the effective transfer of copper from the anode source to a plate covering the cathode (the substrate wafer)<sup>[49]</sup>. In other words, when an electrical potential is applied between a conducting area on the substrate and a counter electrode in the liquid, a chemical redox<sup>[50]</sup> process takes place resulting in a deposition of a layer of material, which happens spontaneously on the substrate, and usually some gas generation at the counter electrode<sup>[51, 52]</sup>. Standard electroplating solutions exist for a range of metals such as copper, gold and nickel, including all noble metals.

In many 3-D structures fabrication the use of gold electroplating is preferred because of its excellent corrosion resistance, solderability and bondability and its high electrical and thermal conductivity<sup>[51]</sup>. In this work, gold electroplating will be used to form the desired device. It is also used to fabricate elevated structure of the MEMS switches<sup>[53]</sup>. The electroplating system in the University of Glasgow uses an electrical current to reduce cations of a desired metal from a plating solution and coat a conductive object with a thin layer of the metal. The anode and cathode in the electroplating cell are both connected to an external supply of direct current. The plating current was set by this equation.

Plating Current  $(mA) = (sample \ holder \ area - sample \ area) \ mm^2 x \ 0.013^{[54]}$

Controlling the thickness of the electroplated object generally depends on altering the time the object spends in the salt solution. The longer it remains inside the bath, the thicker the electroplated shell becomes. It depends on the

temperature of the solution and on the current<sup>[55, 56]</sup> as well. Of course there must also be an adequate amount of metallic ions in the bath to continue coating the object. The shape of the object will also have an effect on the thickness. Sharp corners will be plated thicker than recessed areas. This is due to the electric current in the bath and how it flows more densely around corners<sup>[51, 52]</sup>.

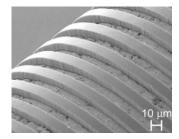

The electroplating process for gold or any other material is shown schematically in Figure 10. In this process, the substrate is typically covered with a conductive, which acts as the plating base and an underlying adhesion; also it prevents contamination of the plating solution (barrier layer). Typically these metal seed layers are deposited using sputtering or evaporation. The seed layer for gold electroplating usually is two level metallization such as Ti/Au or NiCr/Au for good adhesion. The substrate is then patterned with a photoresist, and gold is selectively electroplated into the resist-free areas. Following plating of the structures to the desired height, the photoresist mask is stripped and the metal plating base is removed by wet etching

Figure 10 the electroplating process to depositing gold

# 2.2.4. Photolithography

The second step in the MEMS manufacturing is Lithography or Photolithography. The lithography is a word which comes from the Greek words " $\lambda i\theta o\varsigma$  - lithos, 'stone' and  $\gamma\rho\dot{\alpha}\varphi\omega$  - grapho, 'to write". Literally translated as writing on stone", the lithographic printing technique has been known since the 18th century [57]. Through this technique a stone slab was used onto which an oil or fat was applied to divide the slab into hydrophobic and hydrophilic regions. Ink applied to the slab would adhere to only the hydrophilic regions and when paper was brought into contact with the slab the ink would transfer to the paper producing a copy of the hydrophilic regions on the slab.

Here the lithography in MEMS fabrication the 'stone' used is called a photomask and contains the pattern, and the 'paper', onto which the pattern will be 'printed', is known as the substrate or the thin film on which deposited.

To write on these substrates or the thin film there are numerous lithographic techniques. But the three techniques most commonly used are optical lithography, electron beam lithography and imprint lithography. In optical lithography a source of illumination is directed through a mask that contains the desired pattern, on to the top of the substrate. This is similar to how a slide projector produces an image of the slide on a projector screen. In this work I will use optical lithography. In electron beam lithography a beam of electrons is applied on the substrate surface which is mounted on a motorised stage. Carefully moving the sample and detecting the electron beam across the whole of the substrate's surface allows the desired pattern to be traced out<sup>[58, 59]</sup>. With imprint lithography a deformable layer on top of the substrate is directly structured using a moulding process<sup>[59, 60]</sup>.

Lithography is the one major process in MEMS fabrication by which the geometric patterns that define the devices are transferred from a reticle (also called a photomask, or mask) to a light-sensitive chemical material (photoresist, or simply "resist") which has been deposited on the substrate wafer. It uses UV light or X-ray radiation to transfer the geometric pattern from the mask onto the resist material. This method is used because it allows exact control over the shape and size of the objects it makes, and because it can make many patterns over an entire surface simultaneously, Figure 11. The main disadvantage to this method is that it requires a flat substrate to start with, and it can require extremely clean operating conditions<sup>[4,61]</sup>.

Figure 11 the Photolithography processes

Photolithography work flow consists of the following major steps when viewed from the point of view of the wafer:

- 1. Preparation of the photosensitive film (photoresist)

- 2. The Photomask and Alignment of the substrate wafer

- 3. Exposure of the photoresist

- 4. Development of patterns.

### 2.2.4.1. Preparation of the photosensitive film (photoresist)

The silicon wafer or the deposited material is coated with a light-sensitive material (Photoresist layer) or resist material layer or sacrificial layers as some like to call it. These resists materials are often produced in liquid (as a solvent) form and are typically cast onto the substrate by spin coating. The spin coating is the standard resist application method, Figure 12. A few millilitres of resist is applied on the substrate wafer at the centre of it and slowly rotated. Then acceleration increased to ca. 10000 rpm spreads the resist over the wafer towards the edges, leaving a very uniform layer with thicknesses range from 0.1 µm up to 500µm depending on the rotated speed.

Figure 12 spin coating process

The most common method of coating planar surfaces is spin coating in MEMS fabrication. However, there are other techniques for special coating such as spray coating for a uniform resist layer over a nonplanar surface<sup>[62, 63]</sup>.

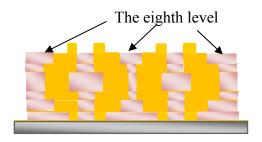

The main parameters for film thickness control are not only the spin speed but also the viscosity and solvent evaporation rate. Spin coated films fill cavities and recesses because they are liquids during spin coating. This is advantageous for gap filling and smoothing<sup>[4, 40]</sup>. The remaining solvent evaporates during the bake process and hardens the photoresist.