Hassan, F. (2011) *Design and modelling of variability tolerant on-chip communication structures for future high performance system on chip designs.* PhD thesis

http://theses.gla.ac.uk/2729/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Glasgow Theses Service http://theses.gla.ac.uk/ theses@gla.ac.uk

# Design and Modelling of Variability Tolerant on-Chip Communication Structures for Future High Performance System on Chip Designs

by

## Faiz-ul-Hassan

Thesis submitted in fulfilment of the requirements for the degree of

Doctor of Philosophy

in

**Electronics and Electrical Engineering**

at

## University of Glasgow

May 2011 Copyright © Faiz-ul-Hassan, 2011, all rights reserved.

#### Abstract

The incessant technology scaling has enabled the integration of functionally complex System-on-Chip (SoC) designs with a large number of heterogeneous systems on a single chip. The processing elements on these chips are integrated through on-chip communication structures which provide the infrastructure necessary for the exchange of data and control signals, while meeting the strenuous physical and design constraints. The use of vast amounts of on chip communications will be central to future designs where variability is an inherent characteristic. For this reason, in this thesis we investigate the performance and variability tolerance of typical on-chip communication structures. Understanding of the relationship between variability and communication is paramount for the designers; i.e. to devise new methods and techniques for designing performance and power efficient communication circuits in the forefront of challenges presented by deep sub-micron (DSM) technologies.

The initial part of this work investigates the impact of device variability due to Random Dopant Fluctuations (RDF) on the timing characteristics of basic communication elements. The characterization data so obtained can be used to estimate the performance and failure probability of simple links through the methodology proposed in this work. For the Statistical Static Timing Analysis (SSTA) of larger circuits, a method for accurate estimation of the probability density functions of different circuit parameters is proposed. Moreover, its significance on pipelined circuits is highlighted. Power and area are one of the most important design metrics for any integrated circuit (IC) design. This thesis emphasises the consideration of communication reliability while optimizing for power and area. A methodology has been proposed for the simultaneous optimization of performance, area, power and delay variability for a repeater inserted interconnect. Similarly for multibit parallel links, bandwidth driven optimizations have also been performed. Power and area efficient semi-serial links, less vulnerable to delay variations than the corresponding fully parallel links are introduced. Furthermore, due to technology scaling, the coupling noise between the link lines has become an important issue. With ever decreasing supply voltages, and the corresponding reduction in noise margins, severe challenges are introduced for performing timing verification in the presence of variability. For this reason an accurate model for crosstalk noise in an interconnection as a function of time and skew is introduced in this work. This model can be used for the identification of skew condition that gives maximum delay noise, and also for efficient design verification.

Dedicated

to

My Family

### Acknowledgements

I would like to thank almighty Allah for giving me health, knowledge and blessings that have made it possible to complete this work.

I would like to express my profound gratitude to my supervisor Dr. Fernando Rodríguez-Salazar for giving me the opportunity to work with him and for his inspiration, guidance and continuous support. Fernando your impressive knowledge, extreme patience, big heart and special attention on my needs have made it possible for me to comfortably complete this research. Thank you very much again for your special help and guidance.

Special thanks and appreciation to my co-supervisor, Dr. Wim Vanderbauwhede, who always gave me very useful comments and suggestions during my research. I would also like to thank Dr. Binjie Cheng from Device Modeling Group on his help in the area of device model cards. I would also like to acknowledge the guidance and encouragement by Dr. Scott. Roy; especially in the early period of my research.

Infinite thanks to my beloved parents for their prayers and wishes throughout my life. I am also thankful to my sisters and brothers for their continuous support and wishes without which I could not achieve my goal. Exclusive thanks to my beloved wife Farkahnda, my daughters Sumayyah, Juwariyah, Maria and son Bilal for providing me comfort and joy and also for their patience and sacrifices.

Finally, I acknowledge the worthy support of computer support staff, library staff and all my colleagues on helping me on several issues.

Faiz-ul-Hassan

University of Glasgow Glasgow, United Kingdom May 2011

#### **List of Publications**

The following list details publications that have been produced while undertaking this research project.

#### **Journal Papers**

- Faiz-ul-Hassan, Wim Vanderbauwhede, Fernando Rodriguez-Salazar, "Impact of Random Dopant Fluctuations on the Timing Characteristics of Flip-Flops," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Princeton, USA, 2011.

- Faiz-ul-Hassan, Wim Vanderbauwhede, Fernando Rodriguez-Salazar, "Performance Analysis of on-chip Communication Structures under Device variability," INVITED PAPER *in International Journal of Embedded and Real-Time Communication Systems* (*IJERTCS*), vol. 1(4), 2010, pp. 40-62.

#### **Conference Papers**

- Faiz-ul-Hassan, Wim A. Vanderbauwhede, Fernando Rodriguez-Salazar, "Optimization of on-chip link performance under area, power and variability constraints," *in Proceedings of IEEE International Conference on Microelectronics* (*ICM 2010*), pp. 48-51, 19-22 Dec. 2010, Cairo, Egypt.

- Faiz-ul-Hassan, Wim Vanderbauwhede, Fernando Rodriguez-Salazar, "Power dissipation in NoC repeaters under random dopant fluctuations," in *Proceedings of IEEE PrimeAsia 2009*, pp. 388-391, 19-21 Jan. 2009, Shanghai, China.

- Faiz-ul-Hassan, Binjie Cheng, Wim Vanderbauwhede, Fernando Rodriguez-Salazar, "Impact of Device Variability in the Communication Structures for Future Synchronous SoC Designs," *in Proceedings of IEEE International Symposium on System-on-Chip (SoC 2009)*, pp. 68-72, Tamepre, Finland.

- Faiz-ul-Hassan, Wim Vanderbauwhede, Fernando Rodriguez-Salazar, "Timing Yield of Pipelined Circuits under Statistical Device variability," in *Proceedings (on cd) of* 2<sup>nd</sup> IEEE Latin American Symposium on Circuits and \Systems (LASCAS 2011), 23-25 Feb. 2011, Bogota, Colombia.

- Faiz-ul-Hassan, Wim Vanderbauwhede, Fernando Rodriguez-Salazar, "Maximizing Bandwidth Over Faulty Links," 21<sup>st</sup> International Conference on Field Programmable Logic and Applications (FPL 2011), Sep. 5-7, 2011, Chania, Crete, Greece (ACCEPTED).

### **Table of Contents**

| Abstractii                                 |

|--------------------------------------------|

| Acknowledgementsiv                         |

| List of Publicationsv                      |

| Table of Contentsvi                        |

| List of Figuresxi                          |

| List of Tablesxix                          |

| List of Abbreviationsxxi                   |

| Author's Declarationxxiii                  |

| Chapter 11                                 |

| Introduction1                              |

| 1.1 Interconnect-Centric Design Paradigm2  |

| 1.1.1 Scaling                              |

| 1.1.2 Power Dissipation                    |

| 1.1.3 Crosstalk4                           |

| 1.1.4 Variability4                         |

| 1.2 Research Overview                      |

| 1.2.1 Research Objective 16                |

| 1.2.2 Research Objective 27                |

| 1.2.3 Research Objective 37                |

| 1.2.4 Research Objective 48                |

| 1.2.5 Research Objective 58                |

| 2.1 Thesis Organization                    |

| Chapter 210                                |

| On-Chip Communication Structures10         |

| 2.1 Communication Architectures for SoCs10 |

| 2.1.1 Buses                                |

| 2.1.2 Point-to-Point Direct Links                             | 13 |

|---------------------------------------------------------------|----|

| 2.1.3 Network Architecture                                    | 13 |

| 2.3 Performance of On-Chip Communication                      | 17 |

| 2.4 Interconnect Modelling in DSM Technologies                | 17 |

| 2.4.1 Parasitic Resistance                                    | 18 |

| 2.4.2 Parasitic Capacitance                                   | 18 |

| 2.4.3 Inductance                                              | 20 |

| 2.4.4 Impact of Technology Scaling on Interconnect Parasitics | 21 |

| 2.5 Performance Metrics                                       | 22 |

| 2.5.1 Signal Delay                                            | 22 |

| 2.5.2 Skew                                                    | 24 |

| 2.5.3 Delay Variability                                       | 27 |

| 2.5.4 Crosstalk                                               | 27 |

| 2.5.5 Power Dissipation                                       | 29 |

| 2.5.6 On-Chip Area                                            | 33 |

| 2.5.7 Throughput                                              | 34 |

| 2.5.8 Bandwidth                                               | 34 |

| 2.5.9 Parametric Yield                                        | 34 |

| 2.6 Performance Characterization Methodology                  | 34 |

| 2.6.1 Extraction of I-V Characteristics of MOSFETs            | 35 |

| 2.7 Summary                                                   | 37 |

| Chapter 3                                                     |    |

| Communication Structures under Device Variability             |    |

| 3.1 Technology Scaling and Gate Delay                         | 40 |

| 3.2 Delay Uncertainty in Buffers                              | 42 |

| 3.2.1 Skewness of Delay Distributions                         | 45 |

| 3.3 Ring Oscillator (RO)                                      | 46 |

| 3.4 Tapered Buffer Drivers                                    | 47 |

| 3.5               | Repeaters                                    | 52       |

|-------------------|----------------------------------------------|----------|

| 3.6               | Data Storage Elements (Flip-flops)           | 54       |

| 3.0               | 5.1 Timing Measurement Procedure             | 56       |

| 3.0               | 5.2 Results and Discussion                   | 58       |

| 3.7               | Interconnect                                 | 59       |

| 3.8 P             | Performance of Communication Links           | 59       |

| 3.8               | 8.1 Estimation of Link Performance           | 60       |

| 3.8               | 8.2 Link Failure Probability                 | 62       |

| 3.8               | 8.3 Case Study                               | 63       |

| 3.9               | Summary                                      | 64       |

| Chapter           | r 4                                          | 66       |

| SSTA o            | of Pipelined Communication Circuits          | 66       |

| 4.1               | Introduction to STA                          | 66       |

| 4.2 I             | ntroduction to SSTA                          | 68       |

| 4.3 R             | Representation of Characterization Data      | 69       |

| 4.4 E             | Estimation of the Timing Distributions       | 72       |

| 4.4               | 4.1 Pearson Distributions                    | 72       |

| 4.4               | 4.2 Johnson Distribution                     | 74       |

| 4.5 E             | Estimation of Timing Distributions and Yield | 76       |

| 4.6               | Timing Distributions of Pipelined Circuits   | 76       |

| 4.7               | Pipeline Delay                               | 77       |

| 4.8 S             | tatistical Analysis of the Timing Yield      | 79       |

| 4.9               | Experimental Setup and Results               | 80       |

|                   |                                              |          |

| 4.10              | Summary                                      | 86       |

|                   | Summary                                      |          |

| Chapter           |                                              | 88       |

| Chapter<br>Optima | r 5                                          | 88<br>88 |

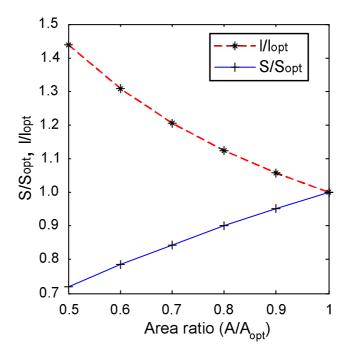

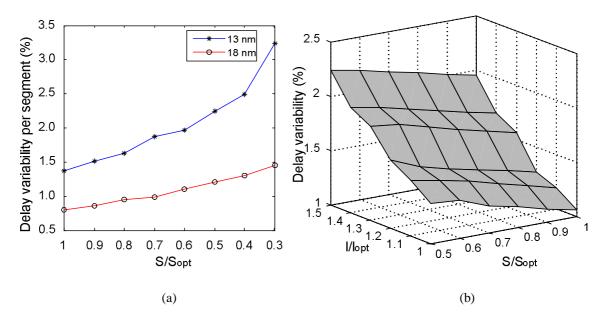

| 5.3 Results and Discussion                                |     |

|-----------------------------------------------------------|-----|

| 5.3.1 Impact on Repeater Inserted Links                   | 95  |

| 5.3.2 Impact of Repeater Size on Power Dissipation        | 95  |

| 5.3.3 Impact on NoC links                                 | 96  |

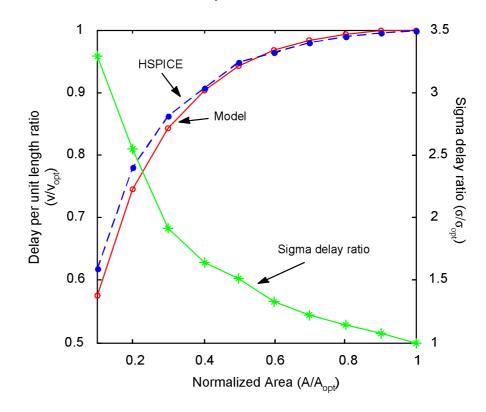

| 5.4 Power and Area Optimal Repeater Insertion             | 97  |

| 5.4.1 Unconstrained Repeater Insertion                    | 97  |

| 5.4.2 Repeater Insertion under Area Constraints           | 98  |

| 5.4.3 Repeater Insertion under Power Constraint           |     |

| 5.4.4 Communication Reliability                           |     |

| 5.5 Optimization Methodology                              |     |

| 5.5.1 Case Study                                          |     |

| 5.6 Summary                                               |     |

| Chapter 6                                                 |     |

| Design of Variability Tolerant Data Channels              |     |

| 6.1 Inter-Resource Communication                          |     |

| 6.2 Channel Configuration and Modelling                   |     |

| 6.2.1 Interconnect Resistance                             |     |

| 6.2.2 Interconnect Capacitance                            |     |

| 6.2.3 Interconnect Delay                                  |     |

| 6.3 Repeater Insertion                                    |     |

| 6.4 Bandwidth Estimation                                  |     |

| 6.4.1 Bandwidth as a Function of Length                   | 117 |

| 6.5 Channel Performance under Variability                 | 117 |

| 6.5.1 Sensitivity Analysis of the Delay under Variability |     |

| 6.6 Area Constrained Channel Bandwidth                    |     |

| 6.6.1 Experimental Setup and Simulation Results           | 121 |

| 6.6.2 Results                                             |     |

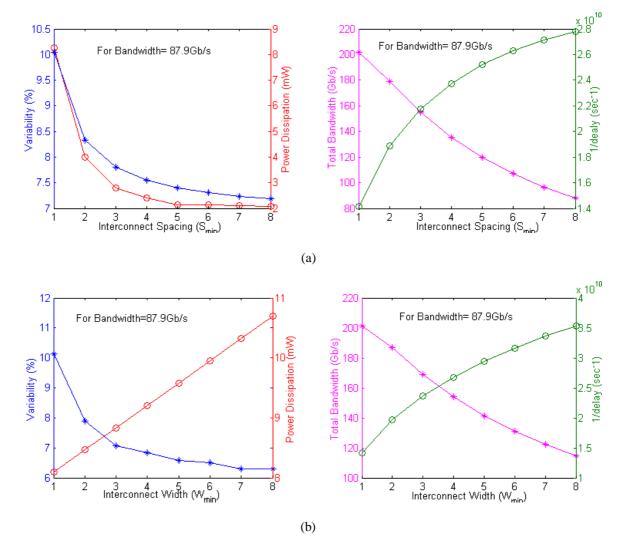

| 6.7 Optimization under Different Trade-offs               |     |

| 6.8 Failure of Channels under Variability   | 131 |

|---------------------------------------------|-----|

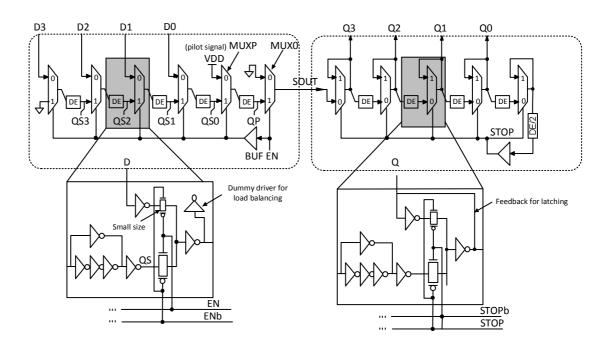

| 6.9. Channel Serialization                  | 134 |

| 6.9.1 Concept                               | 134 |

| 6.9.2 Channel Structure                     | 135 |

| 6.9.3 Experimental Results                  | 138 |

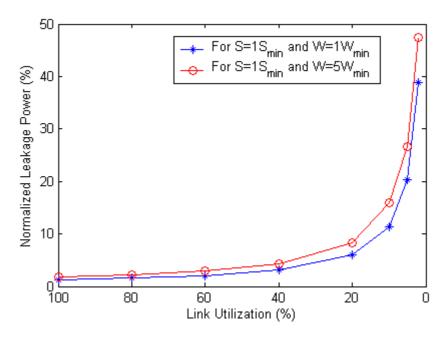

| 6.10 Link Utilization and Power Dissipation | 139 |

| 6.11 Summary                                | 140 |

| Chapter 7                                   | 142 |

| Crosstalk in Coupled Interconnects          | 142 |

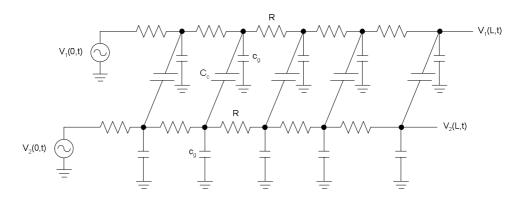

| 7.1 Introduction                            | 142 |

| 7.2 Coupled RC Transmission Lines           | 143 |

| 7.2.1 Voltage Representation                | 144 |

| 7.2.2 Model Validation                      | 145 |

| 7.3 Skew Amplification under Variability    | 147 |

| 7.4 Summary                                 | 149 |

| Chapter 8                                   | 150 |

| Conclusions and Future Work                 | 150 |

| 8.1 Conclusions                             | 150 |

| 8.2 Future Work                             | 154 |

| Appendix A                                  | 155 |

| References                                  | 161 |

## List of Figures

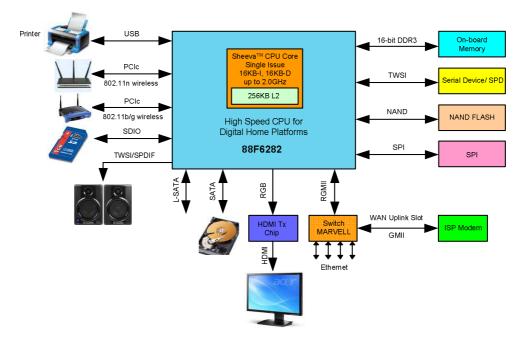

| Figure 1.1: Typical system implementation of Marvell 88F6282 SoC [3]2                         |

|-----------------------------------------------------------------------------------------------|

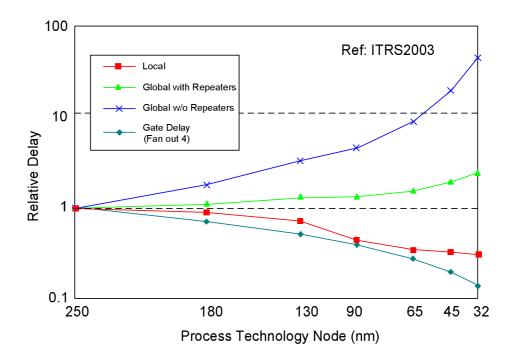

| Figure 1.2: Projected relative delay of devices and interconnects (local and global) for      |

| different technology generations. The relative performance of the global interconnect is      |

| decreasing with technology scaling                                                            |

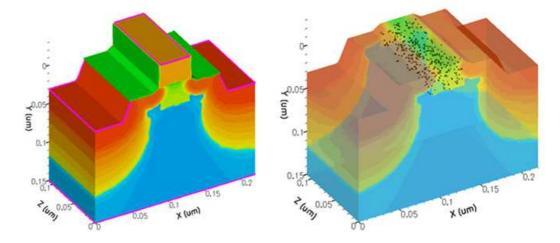

| Figure 1.3: Random discrete dopant effects in deep sub-micrometer CMOS devices [21].          |

| The figure on the left hand side is a solid model of a CMOS transistor and that on the right  |

| side is its transparent version showing the discreteness due to dopants in the channel        |

| region                                                                                        |

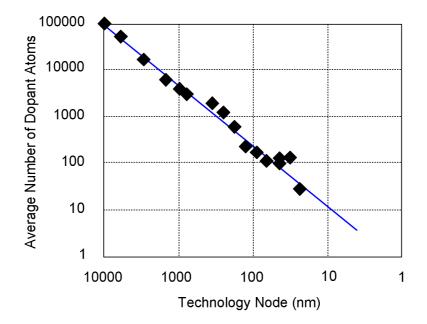

| Figure 1.4: Impact of technology scaling on the average number of dopant atoms in the         |

| channel                                                                                       |

| Figure 2.1: A SoC in which different components are integrated through the bus                |

| communication architecture                                                                    |

| Figure 2.2: A simple shared bus, allowing different FUs to share the same communication       |

| channel                                                                                       |

| Figure 2.3: A bus divided into two sub-buses using a bridge                                   |

| Figure 2.4: An example of AMBA bus. The bridge provides an interface to connect two           |

| different types of buses                                                                      |

| Figure 2.5: A point-to-point communication architecture                                       |

| Figure 2.6: A conceptual realization of a NoC [34]14                                          |

| Figure 2.7: A 4×4 grid structured NoC. Each intellectual property (IP) block is connected     |

| to a router through a network interface (NI) adapter. The routers are connected with each     |

| other through communication links in a certain topology                                       |

| Figure 2.8: A bidirectional link. There is a shared interconnect between the transmitter and  |

| receiver16                                                                                    |

| Figure 2.9: A unidirectional link16                                                           |

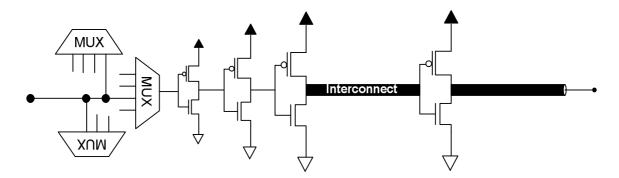

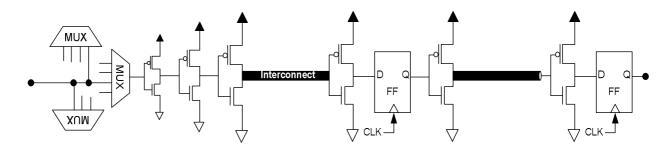

| Figure 2.10: Repeater inserted interconnect16                                                 |

| Figure 2.11: Flip-flop inserted pipelined interconnect                                        |

| Figure 2.12: Different interconnect models, (a) the 'T', (b) the 'pi' and (c) the 'ladder'. A |

| long wire is divided into N segments using ladder model and is shown in (d)18                 |

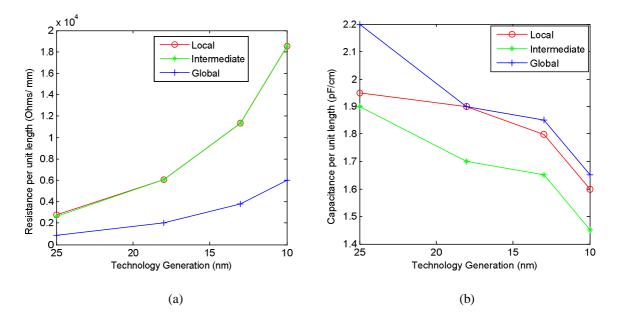

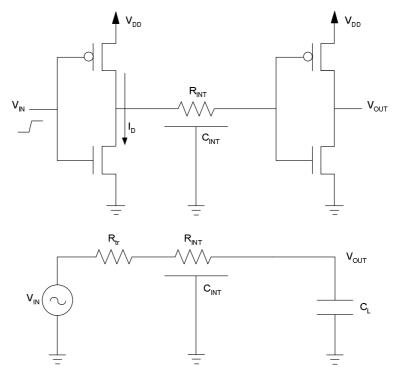

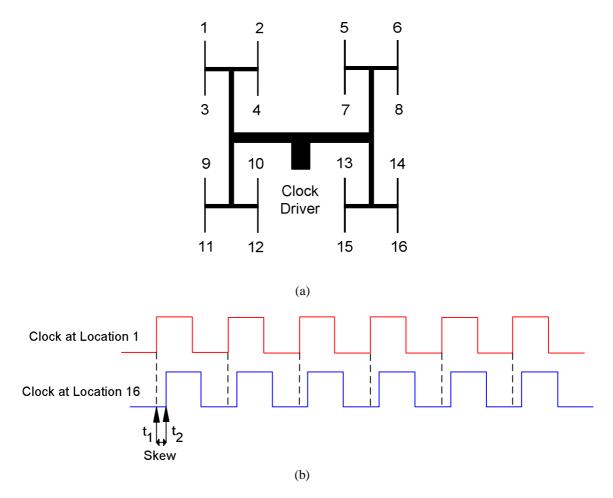

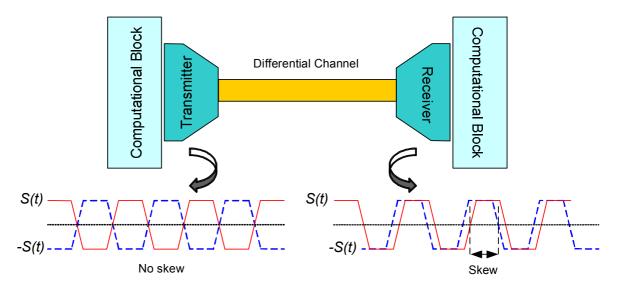

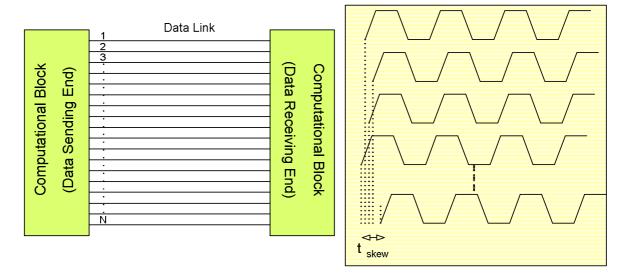

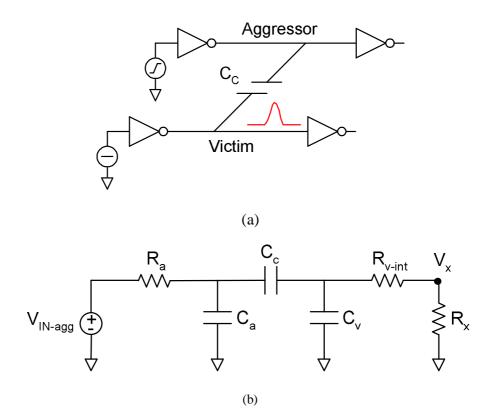

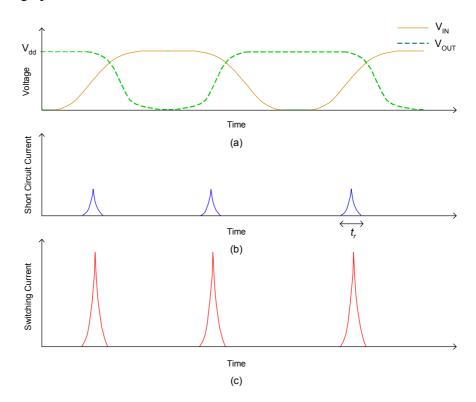

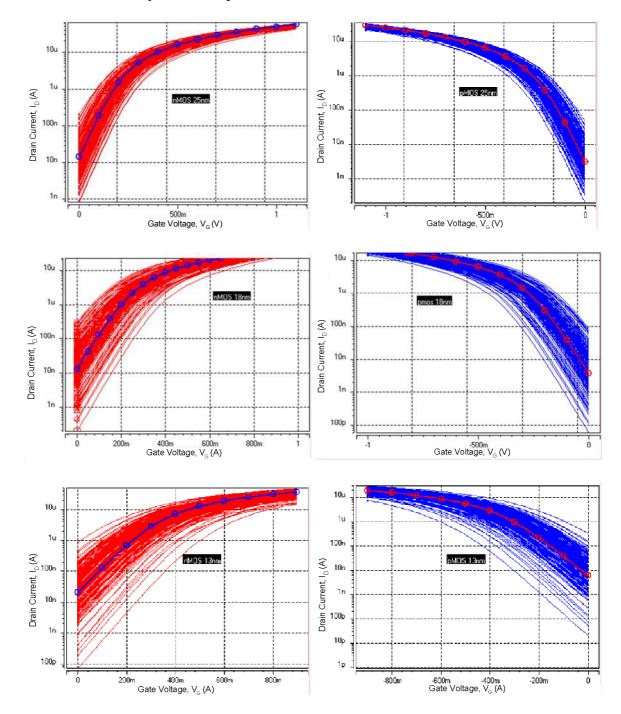

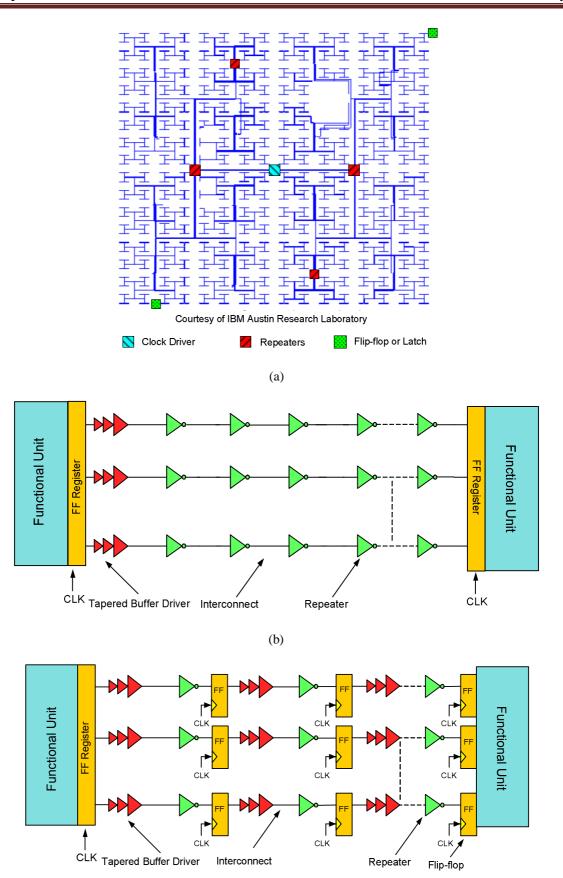

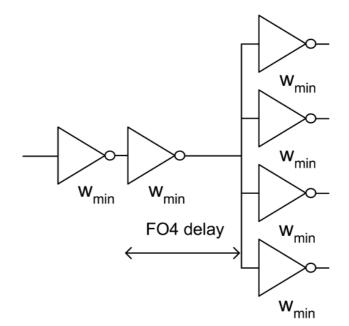

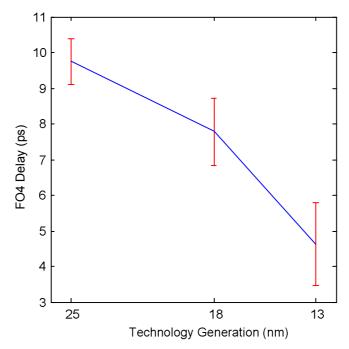

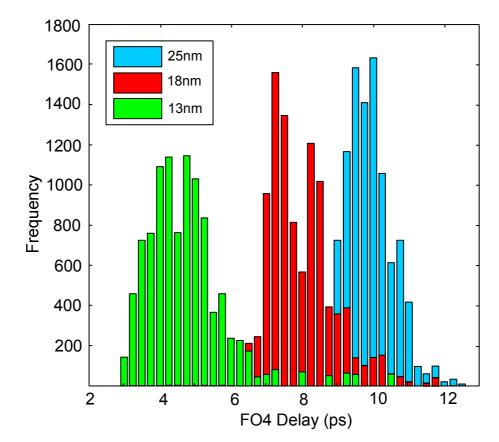

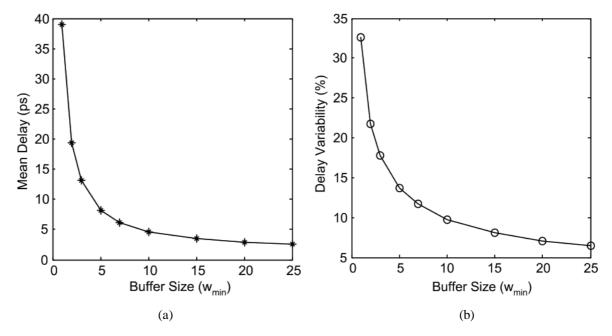

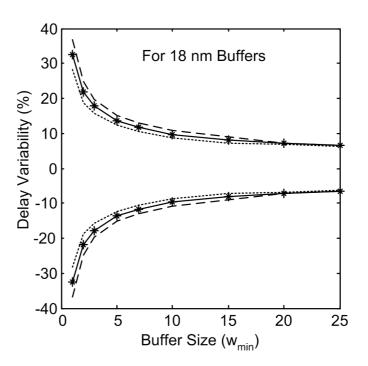

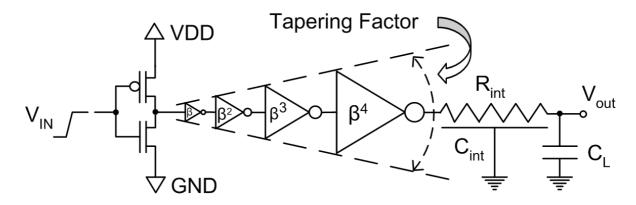

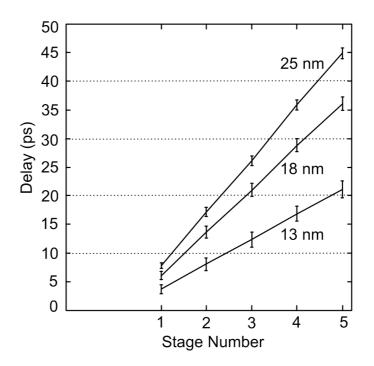

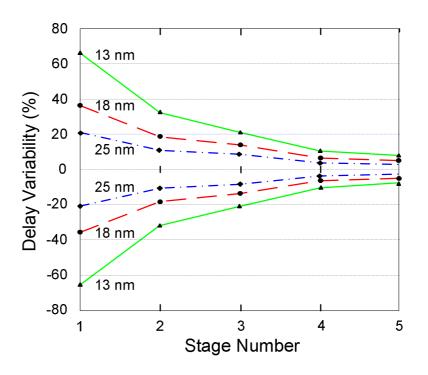

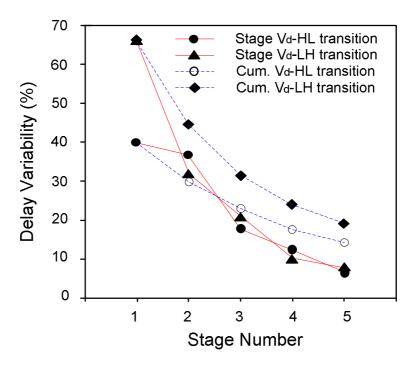

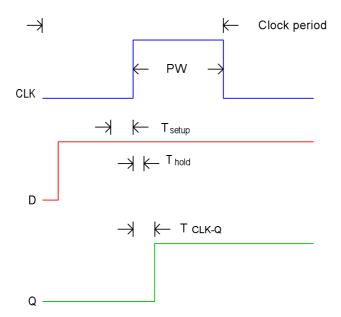

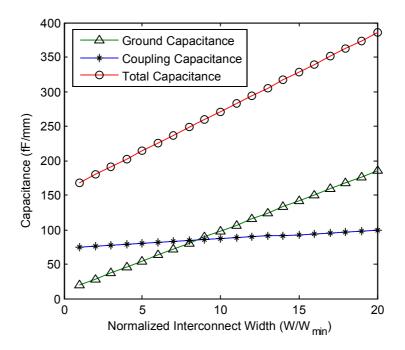

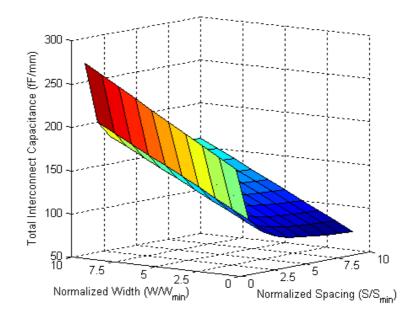

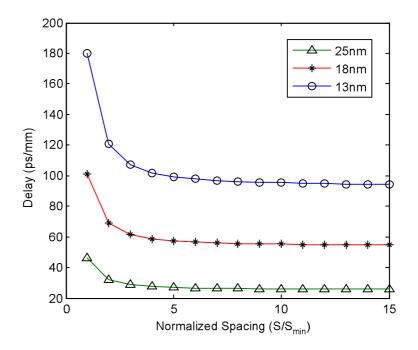

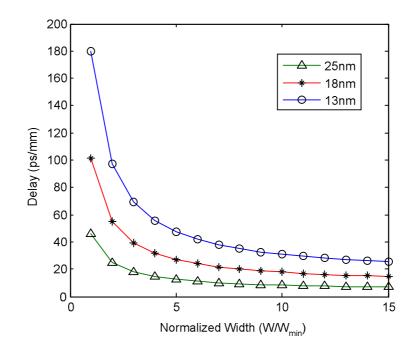

Figure 2.13: The cross-sectional view of an interconnect surrounded by two parallel similar interconnects over a ground plane (in the top global layer) showing different components Figure 2.14: Impact of technology scaling on interconnect resistance and capacitance per unit length (Fig. (a) and (b) respectively) for local, intermediate and global interconnects Figure 2.15: The circuit used for the derivation of the delay expression, where an interconnect is driven by an input buffer and at the output another buffer is connected.....23 Figure 2.16: (a) A simple H-tree with 16 nodes, and (b) an illustration of skew in the clock signals due to difference in their arrival times at location 1 and location 16 of the H-tree. 25 Figure 2.17: A high speed differential serial link. The skew beyond a limit can also effect Figure 2.18: An N-bit parallel link. The skew reduces the amount of the bit overlap. ......26 Figure 2.19: Two RC coupled interconnects. Due to switching of the aggressor line, a voltage is induced in the victim line as shown in (a). The equivalent circuit of the crosstalk Figure 2.20: (a) A rough sketch of voltage and current waveforms of a simple buffer circuit, (a) input and output voltage waveforms, (b) the short circuit current peaks appear when both nMOS and pMOS conduct, and (c) the switching current used for the charging Figure 2.21: I-V characteristic curves of 200 devices for each of nMOS (left) and pMOS (right) for the technology generations of 25, 18 and 13nm. Along with each set of curves, the characteristic curve for the uniformly doped device is also plotted and the dispersion of Figure 3.1: Communication structures in CDN and data channels: (a) an H-type CDN, (b) a repeater inserted synchronous data channel, (c) a flip-flop based pipelined data channel. .39 Figure 3.3: FO4 delay for different technology generations. The error bars represent the Figure 3.4: Delay distribution of minimum sized inverters with a fan-out of four for the Figure 3.5: Mean buffer delay (a), Delay variability (b), plotted as a function of buffer size for 18 nm technology generation. The curves have been plotted for the average response in

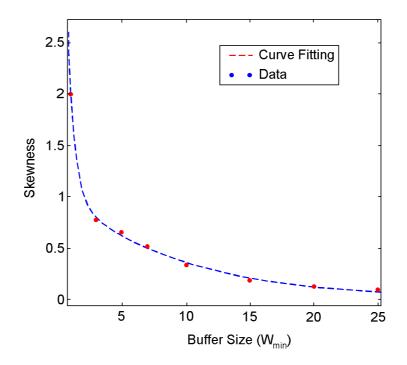

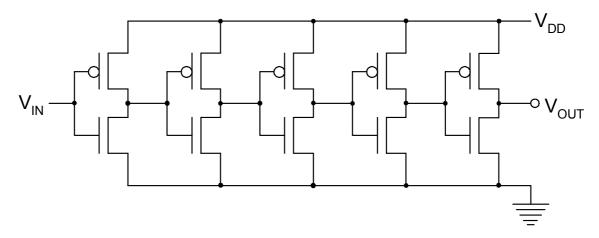

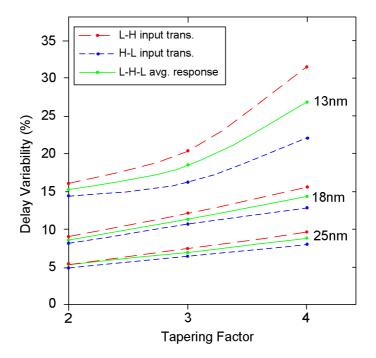

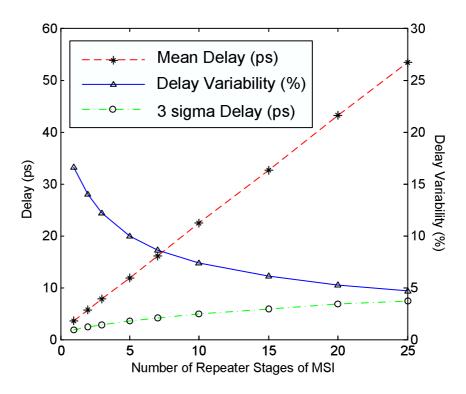

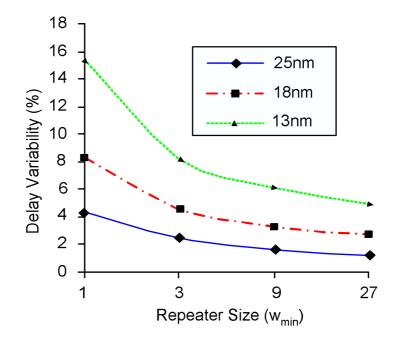

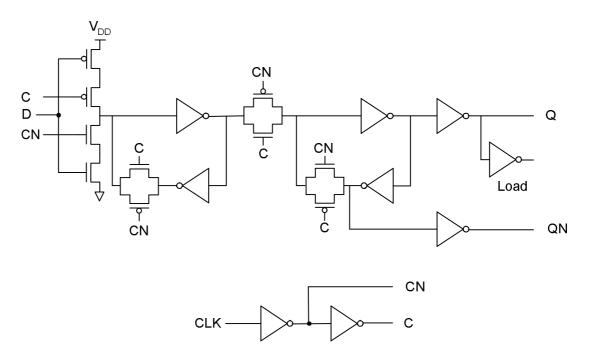

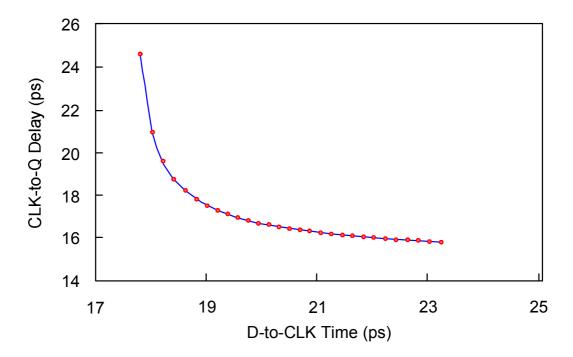

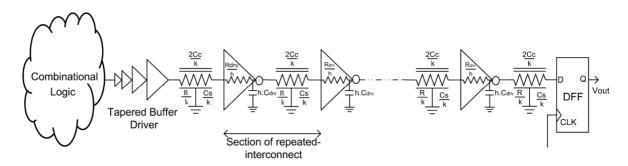

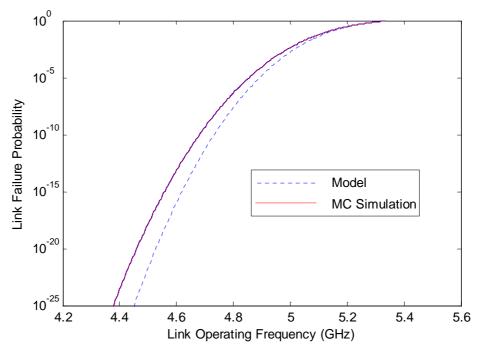

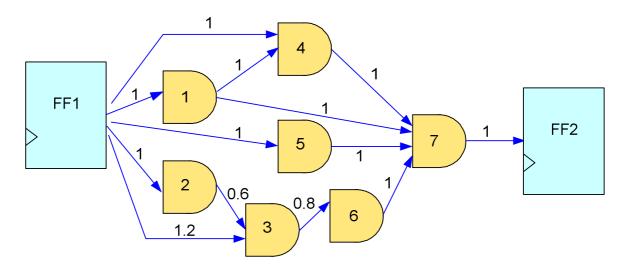

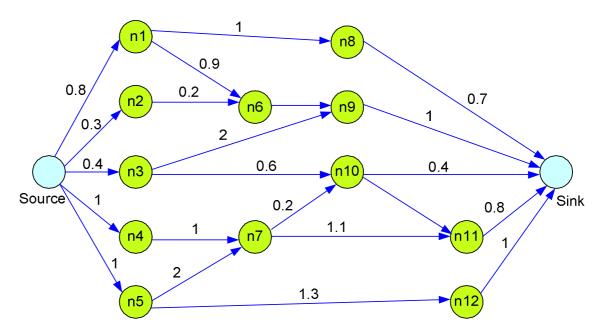

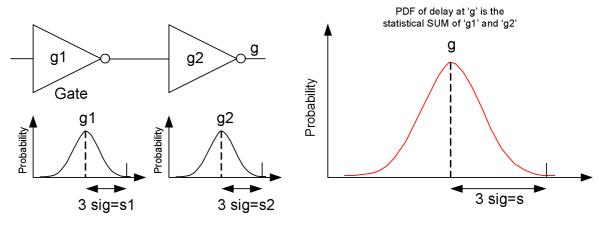

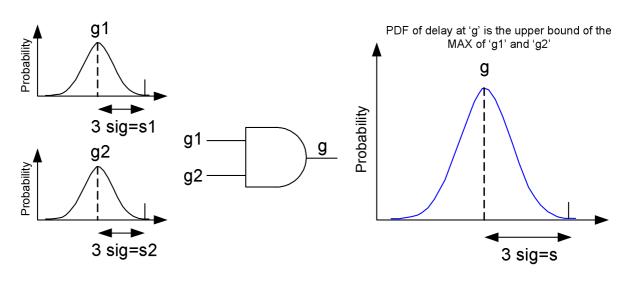

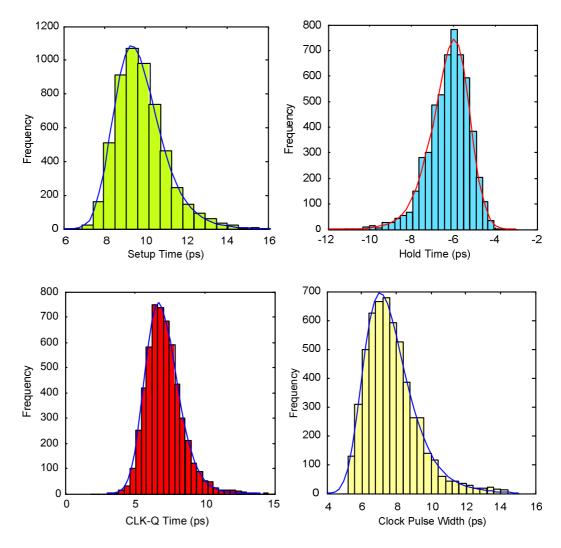

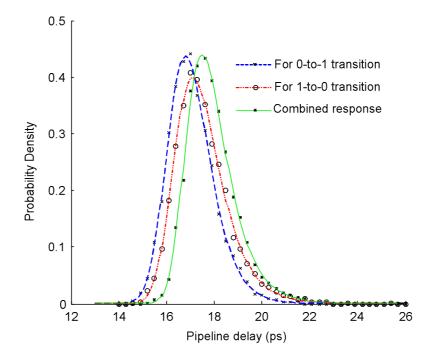

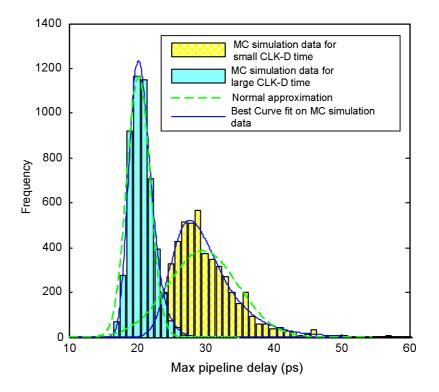

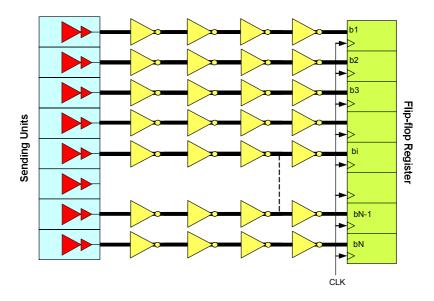

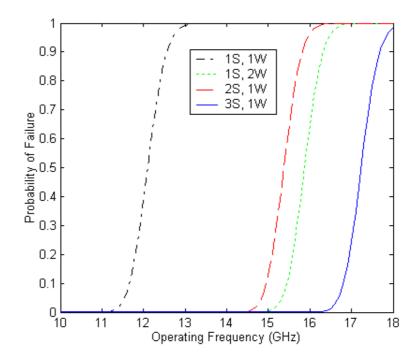

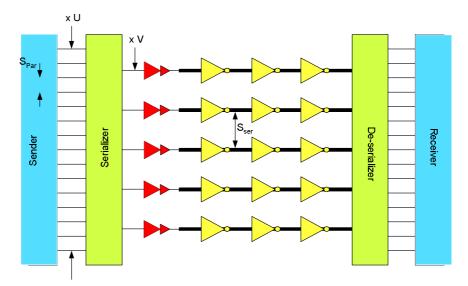

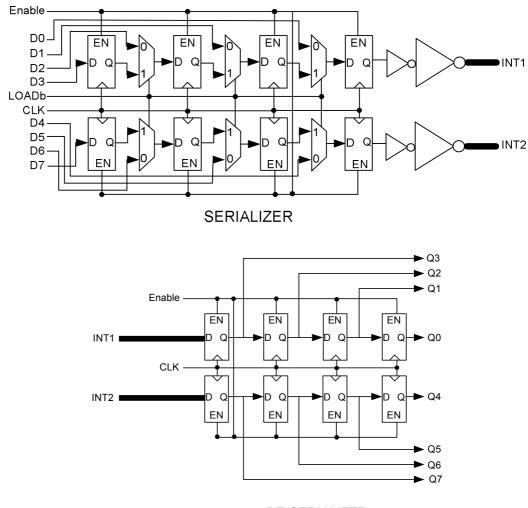

Figure 3.6: Delay variability plotted against buffer size for 18 nm buffers. The smaller dashed lines represent delay variability for low-to-high transition and bigger dashed lines for high-to-low transition. Similarly, the solid lines are for the average response......45 Figure 3.7: Skewness of delay distributions as a function of the buffer size for 13 nm Figure 3.8: A five-stage ring oscillator circuit constructed of minimum sized devices. .....47 Figure 3.10: Cumulative mean delay in tapered buffer drivers of the given three technology generations along with the delay uncertainty shown as error bars (corresponding to  $1\sigma$ ). .48 Figure 3.11: Delay variability introduced by different stages of the tapered buffer driver for Figure 3.12: Cumulative and stage delay variability during low-to-high and high-to-low Figure 3.13: Delay variability of tapered buffer drivers for different tapering factors during Figure 3.14: Delay variability in a chain of minimum sized repeaters of 13 nm plotted Figure 3.15: Cumulative delay variability plotted as a function of repeater size in a chain of Figure 3.16: Schematic view of a standard CMOS D flip-flop circuit [84]-[85]......55 Figure 3.20: A simple data communication link. The signal coming out from the combinational logic is powered up through tapered buffer driver and then it passes through Figure 3.21: Link failure probability as a function of link operating frequency, as Figure 4.2: An example of the timing graph for delay traversal from source to sink.......67 Figure 4.3: Basic statistical operations used in STA and SSTA. The SUM operation (a), and the MAX operation (b) [89].....69 Figure 4.4: Histograms of observed data taken through Monte Carlo simulations for the timing parameters of the FFs of 13 nm......71

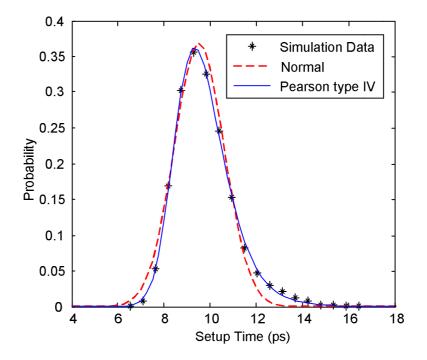

| Figure 4.5: The probability density function of setup time for the 13 nm flip-flops plotted          |

|------------------------------------------------------------------------------------------------------|

| with different systems74                                                                             |

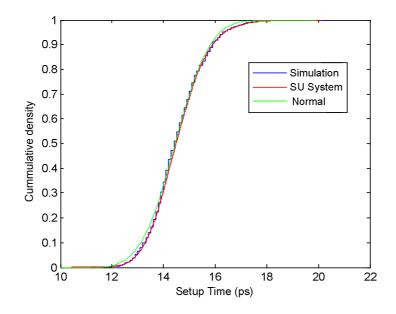

| Figure 4.6: Cumulative delay distribution of setup time of 18 nm flip-flops. The SU system           |

| from Johnson family of distributions better fits the simulation data as compared to normal           |

| distribution75                                                                                       |

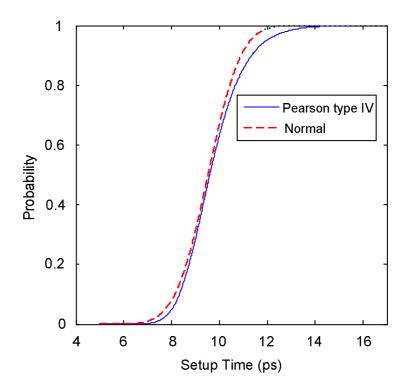

| Figure 4.7: Cumulative distribution functions for the setup time of 13 nm flip-flops with            |

| Normal and Pearson type IV approximations                                                            |

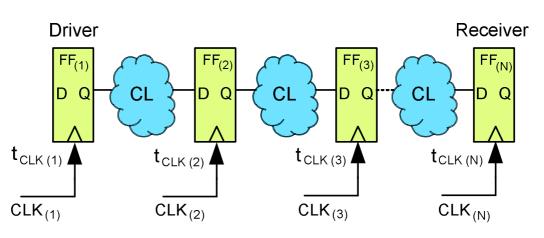

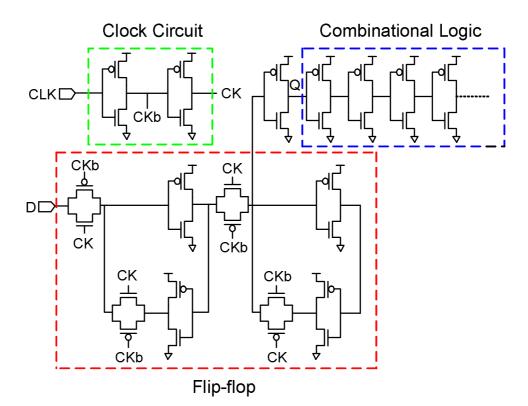

| Figure 4.8: N-stage flip-flop based pipeline78                                                       |

| Figure 4.9: Transistor level model of the pipeline segments                                          |

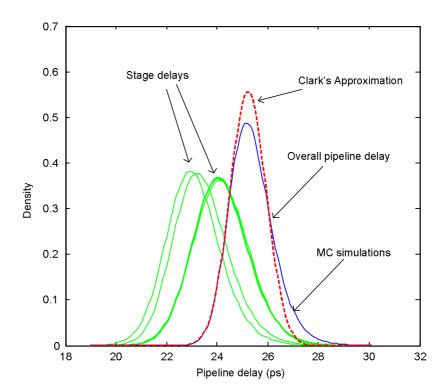

| Figure 4.10: MAX delay distributions of individual pipeline stages and overall pipeline for          |

| 18nm technology generation                                                                           |

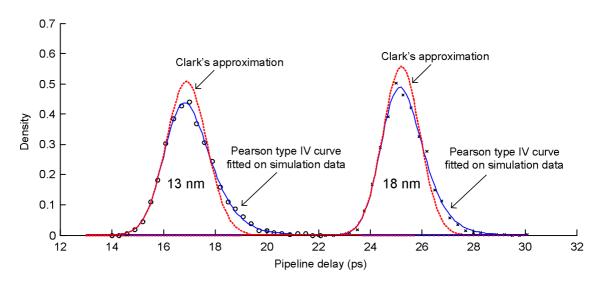

| Figure 4.11: Overall pipeline delay distributions of a pipeline consisting of 6 stages               |

| simulated for the technology generations of 18 and 13 nm                                             |

| Figure 4.12: Maximum delay distributions plotted for low-high and high-low transitions               |

| for the 13 nm pipeline83                                                                             |

| Figure 4.13: Histograms of timing variable comprising of D-CLK time, CLK-Q time and                  |

| combinational delay for a 13 nm pipeline84                                                           |

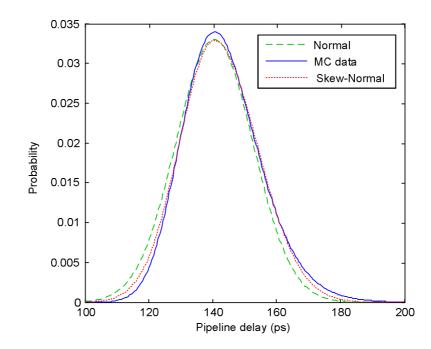

| Figure 4.14: Probability density functions for the pipeline delay with a combinational logic         |

| of 60 inverters in series for 13 nm85                                                                |

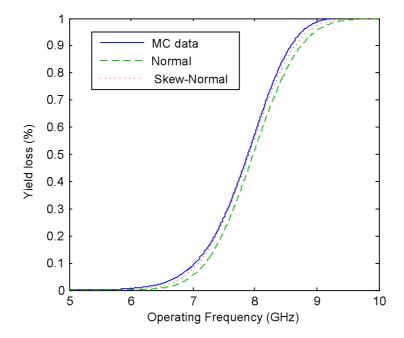

| Figure 4.15: Difference in timing yield estimation with normal and skew-normal                       |

| approximations                                                                                       |

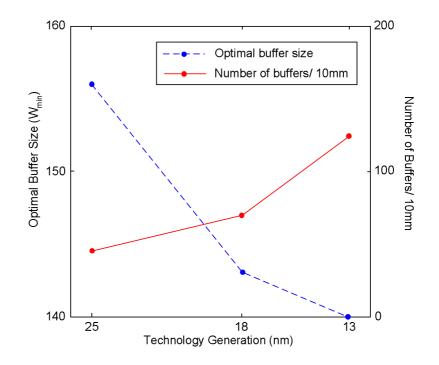

| Figure 5.1: Optimal number and size ( $\times Wmin$ ) of uniformly inserted buffers in an            |

| interconnect of minimum width and spacing for the three technology generations                       |

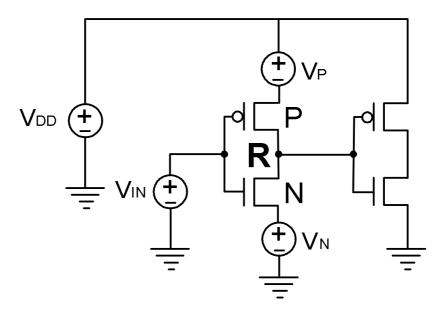

| Figure 5.2: Arrangement for the measurement of power dissipation in the repeater91                   |

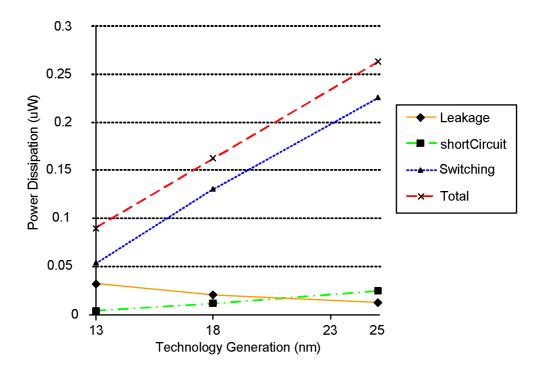

| Figure 5.3: Different components of power dissipation along with the total power in a                |

| minimum sized inverter (MSI). The inverter under investigation refers ' $\mathbf{R}$ ' in Figure 5.2 |

| operating at a frequency of 2GHz92                                                                   |

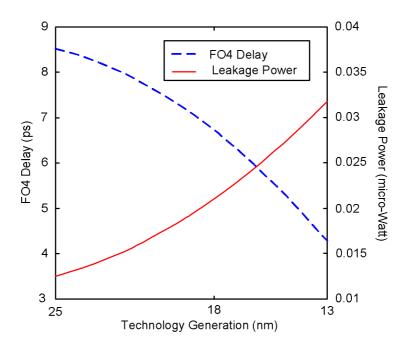

| Figure 5.4: A plot of FO4 delay and the leakage power in MSI                                         |

| Figure 5.5: Normalized power distribution components in MSI operating at 2GHz93                      |

| Figure 5.6: Histogram of leakage power in 25nm MSIs. The distribution is quite                       |

| asymmetric about the mean                                                                            |

| Figure 5.7: Effect of repeater size on leakage power. Leakage power and its variability              |

| increases with repeater size96                                                                       |

| Figure 5.8: Buffer inserted interconnect                                                             |

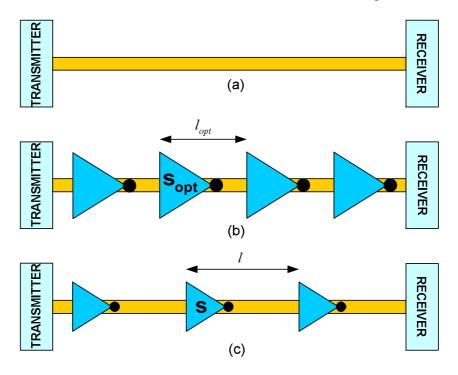

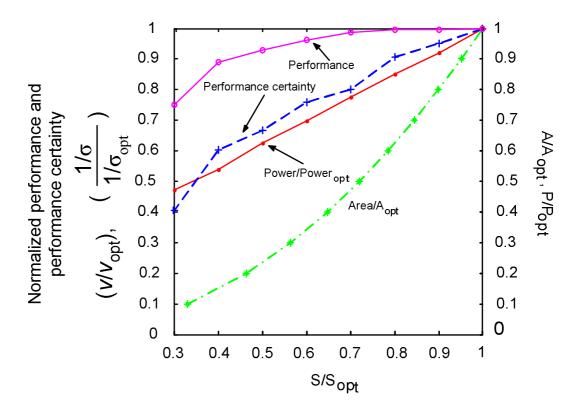

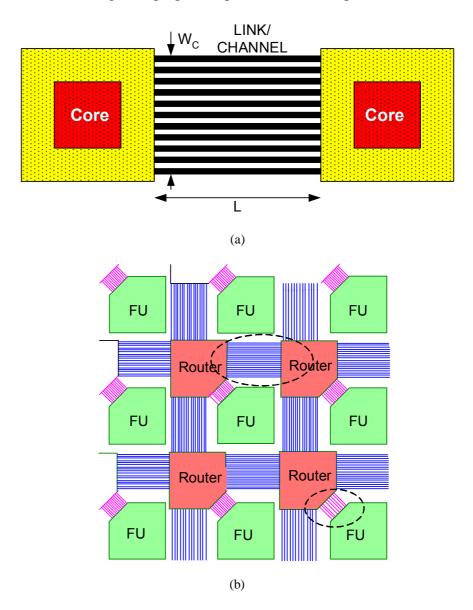

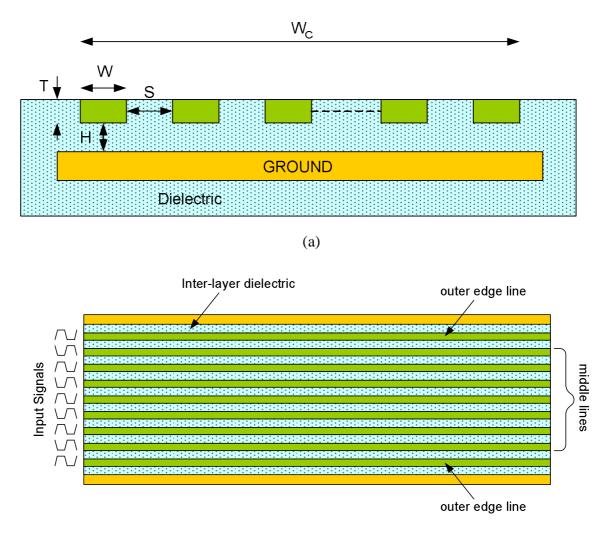

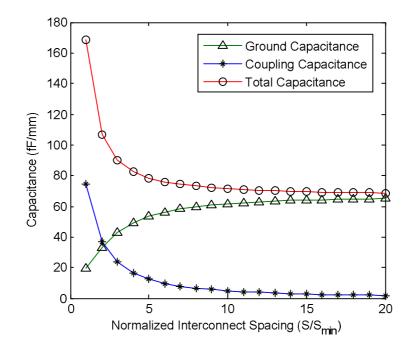

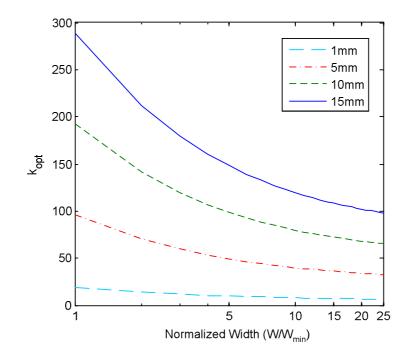

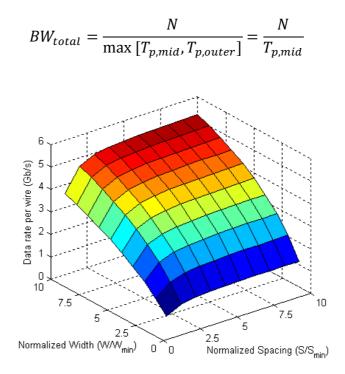

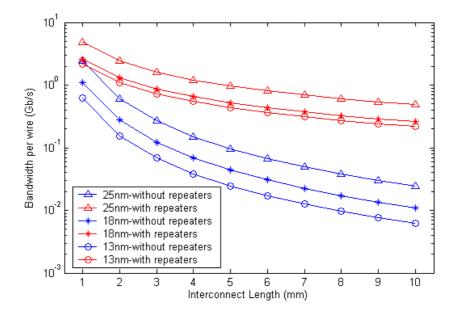

Figure 5.9: An interconnect between the transmitter and receiver (a), optimal buffer Figure 5.10: Optimal repeater size and inter-repeater segment length (both normalized) for Figure 5.11: Delay variability as a function of different ratios of repeater size, in the absence of crosstalk (a), Dependence of delay variability on repeater size and inter-repeater Figure 5.12: Comparison between analytical model and simulation results for performance Figure 5.13: Performance, area, power and performance certainty trade-off curves. ...... 104 Figure 6.1: Simple Core-Core link consisting of multiple interconnects (a), Functional unit-Figure 6.2: Structure of a multi-bit bus, where the number of interconnects in a fixed channel width WC depends on the interconnect width and spacing. (a) the cross-sectional view showing different dimensions and (b) the top view of the bus indicating outer and middle lines. The input signals on any two adjacent lines are opposite in phase, thus simulating the worst case of crosstalk. Each line in the bus can be considered as an Figure 6.3: Capacitance curves for minimum width global interconnects of 18nm plotted as Figure 6.4: Capacitance curves for 18nm global interconnects plotted as a function of Figure 6.5: The total capacitance of an interconnect (not at the outer edge) of a bus in 18 Figure 6.6: Propagation delay of the middle interconnect of minimum width of a bus for the given three technologies plotted as a function of the spacing between the conductors. Figure 6.7: Propagation delay of the middle interconnect of a bus with neighbouring interconnects at minimum spacing for the given three technologies plotted as a function of Figure 6.8: Optimum number of repeaters for minimum interconnect delay for different lengths of the global interconnect plotted as a function of the interconnect width. The interconnect is of 13 nm technology and the spacing between interconnects is S<sub>min</sub>......114

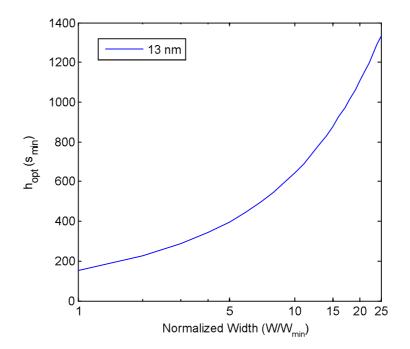

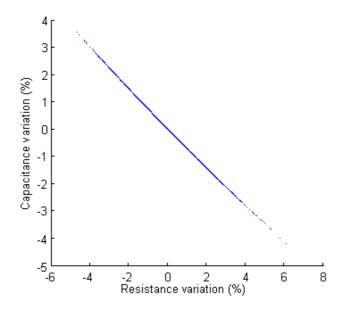

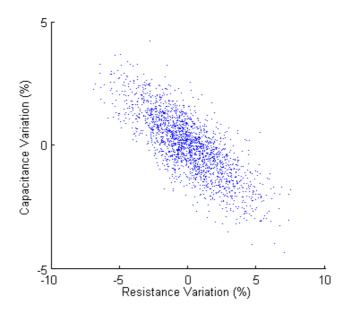

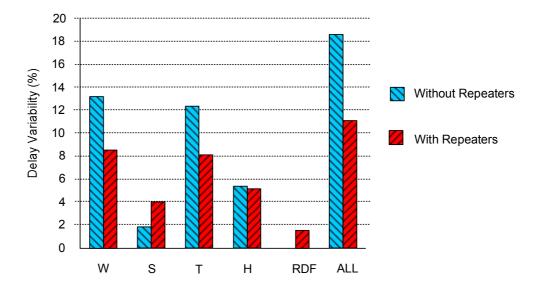

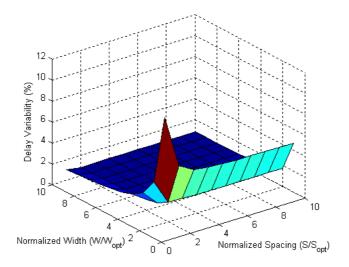

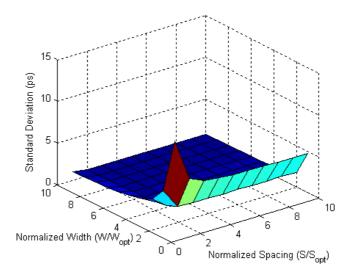

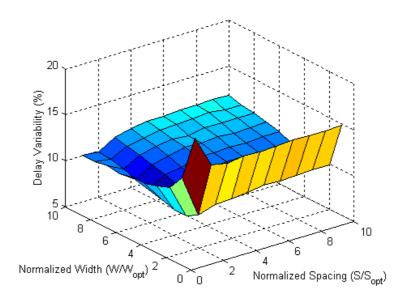

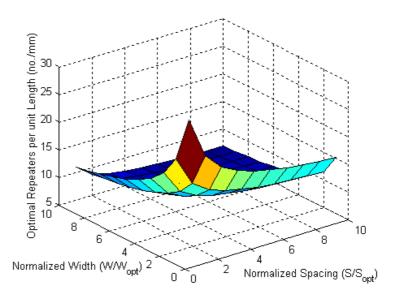

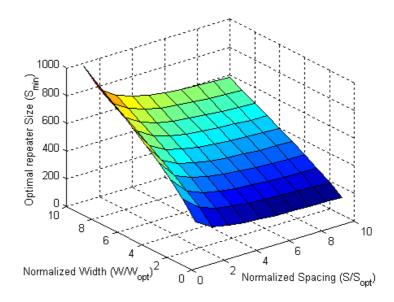

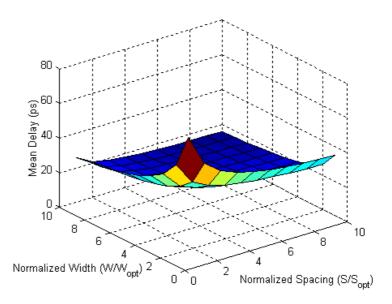

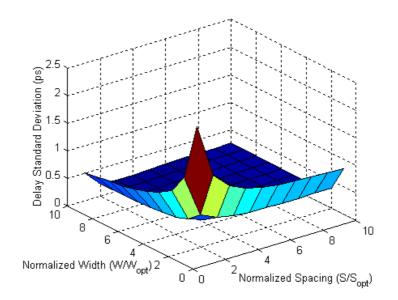

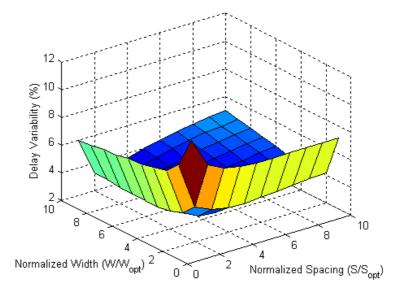

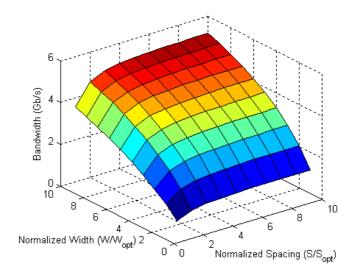

Figure 6.9: Optimum repeater size for minimum interconnect delay for different interconnect widths (global interconnect) for 13 nm technology. The spacing between Figure 6.10: Data rate per wire of a channel bus in 13nm technology plotted as a function of spacing and width.....116 Figure 6.11: Maximum allowed interconnect length for a particular bandwidth with and without the use of repeaters for the given three technologies. These curves have been Figure 6.12: Scatter plot of interconnect resistance and capacitance with thickness variation Figure 6.13: Scatter plot of interconnect resistance and capacitance with width and Figure 6.14: Contribution of different parametric variations on the delay of a bus line of Figure 6.15: Mean delay (in picoseconds) of interconnects (without repeaters) in the channel bus of 13 nm for different geometrical configurations under variability Case 1. 122 Figure 6.16: The standard deviation (in picoseconds) of the delay of interconnects (without repeaters) in the channel bus of 13nm for different geometrical configurations under Figure 6.17: Delay variability (%) of interconnects (without repeaters) in the channel bus Figure 6.18: The number of repeaters per unit length required for different interconnect dimensions (width and spacing) for a 13 nm bus under worst crosstalk. The numbers have been rounded-off......123 Figure 6.19: The size of the repeaters for different interconnect dimensions (width and spacing) for a 13 nm bus under worst crosstalk. The repeater sizes have been rounded-off. Figure 6.20: Mean delay (in picoseconds) of interconnects (with repeaters) in the channel Figure 6.21: The standard deviation (in picoseconds) of the delay of interconnects (with Figure 6.22: Delay variability (%) of interconnects (with repeaters) in the channel bus of 13nm for different geometrical configurations under variability Case 1......125

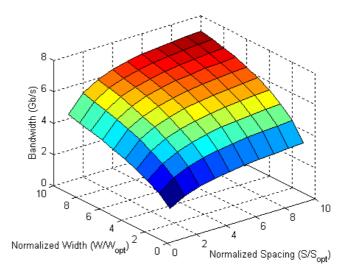

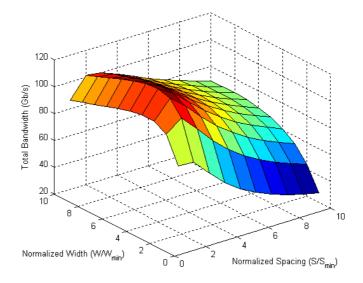

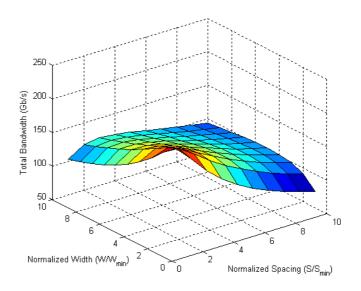

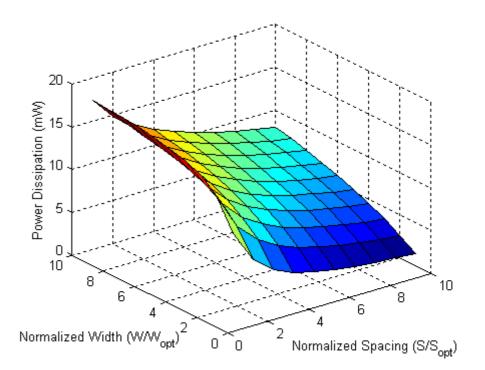

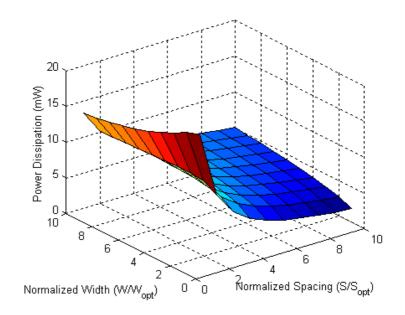

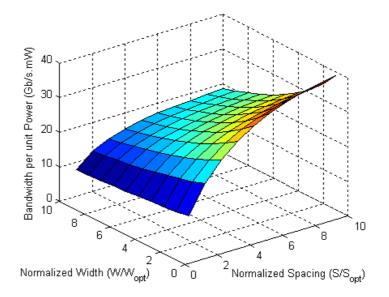

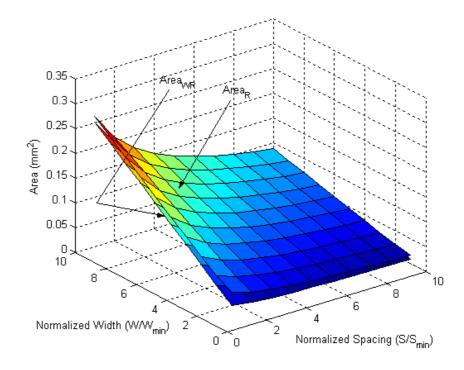

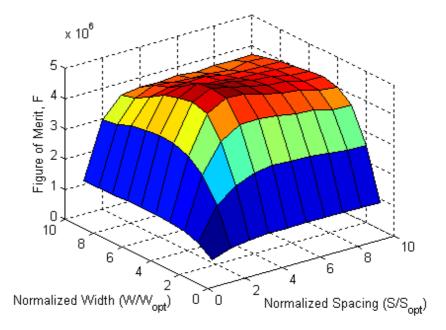

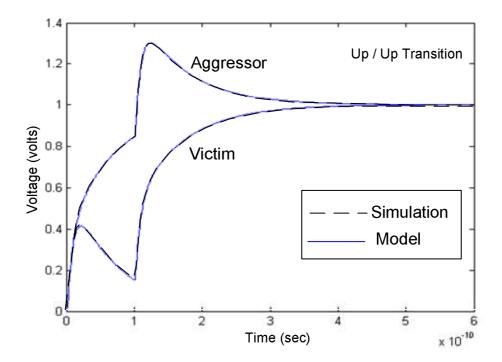

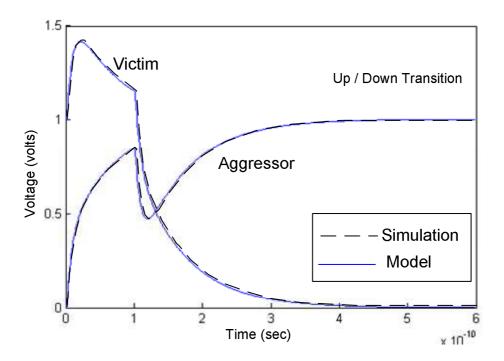

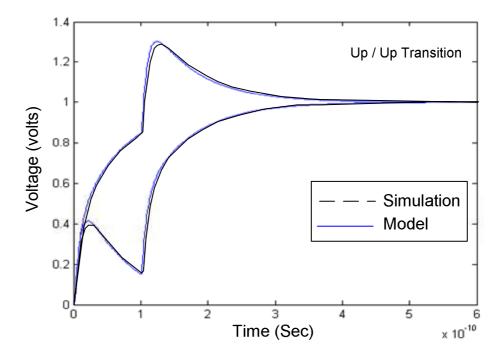

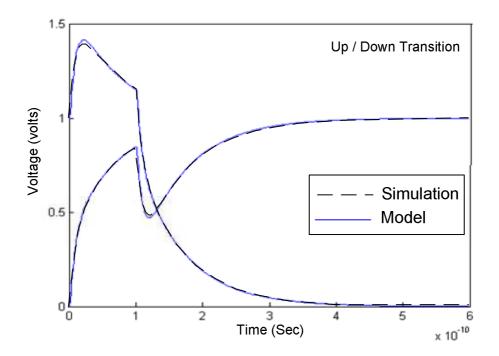

Figure 6.23: Bandwidth of the individual interconnect lines (without repeaters) in Gb/s Figure 6.24: Bandwidth of the individual interconnect lines (with repeaters) in Gb/s given Figure 6.25: Total bandwidth (Gb/s), without repeaters, plotted as a function of Figure 6.26: Total bandwidth (Gb/s), with repeaters, plotted as a function of interconnect Figure 6.27: Power dissipation (mW) at maximum bandwidth for the interconnect of 13 nm Figure 6.28: Power dissipation (mW) at maximum bandwidth for the interconnect of 13 nm Figure 6.29: Total bandwidth per unit power (Gb/s.mW) consumption for interconnects Figure 6.30: Surface plot of the area consumed by the channel bus interconnects, with and Figure 6.31: The figure of merit F plotted as a function of spacing and width for the Figure 6.32: A multi-bit communication link. Tapered buffers have been used on the Figure 6.37: Different performance metrics for a bus with different serialization ratios (1, 1.5, 2.0..., 4.5 corresponding to  $S = 1S_{min}$  to  $8S_{min}$  or  $W = 1W_{min}$  to  $8W_{min}$ ), (a) by increasing spacing and keeping width constant, (b) by increasing width and keeping spacing constant. Figure 6.38: Leakage power normalized with the total power for different link utilization Figure 7.2: Typical responses of aggressor and victim lines during up/up transitions for

| Figure 7.3: Typical responses of aggressor and victim lines during up/down to | ransitions for |

|-------------------------------------------------------------------------------|----------------|

| finite lines with open ends                                                   | 146            |

| Figure 7.4: Typical responses of aggressor and victim lines during up/up t    | ransitions for |

| finite lines with capacitive loads                                            | 147            |

| Figure 7.5: Typical responses of aggressor and victim lines during up/down to | ransitions for |

| finite lines with capacitive loads                                            | 147            |

### **List of Tables**

| Table 2.1: Interconnect Technology Parameters for the Three Wiring Tiers       21             |

|-----------------------------------------------------------------------------------------------|

| Table 3.1: Statistical Analysis of the Timing Parameters of a Standard Flip-flop              |

| Table 3.2: Statistical Delay Characteristics of Different Elements of the Link. These values  |

| have been taken from the characterization data of different elements                          |

| Table 4.1: Statistical Analysis of the Timing Parameters of the Standard Flip-flop shown in   |

| Figure 3.16                                                                                   |

| Table 4.2: Goodness of Fit Statistics (for Figure 4.5) in terms of R-Square, Sum of Squares   |

| due to Error (SSE), Adjusted R-Square, Root Mean Squared Error (RMSE)74                       |

| Table 4.3: Statistical Parameters of the MAX Delay Distribution of the Complete Pipeline      |

|                                                                                               |

| Table 5.1: Statistics of Power Measurements for MSI    94                                     |

| Table 6.1: Coefficients of the delay model for different switching patterns [135]112          |

| Table 6.2: Primary interconnect and device parameters based on the ITRS and the device        |

| model cards [76], [77]. The device parameters are for the uniformly doped devices 118         |

| Table 6.3: Performance of a parallel and a serial bus of degree 2 for the same throughput     |

|                                                                                               |

| Table 7.1: Monte Carlo simulation results for studying the effect of input signal variability |

| on skew amplification                                                                         |

| Table A.1: Mean delay (in picoseconds) of interconnects (without repeaters) in the channel    |

| bus of 13nm for different geometrical configurations under variability Case 1. The columns    |

| of the table show the interconnect spacing and the rows show the width155                     |

| Table A.2: The standard deviation (in picoseconds) of the delay of interconnects (without     |

| repeaters) in the channel bus of 13nm for different geometrical configurations under          |

| variability Case 1                                                                            |

| Table A.3: Delay variability (%) of interconnects (without repeaters) in the channel bus of   |

| 13nm for different geometrical configurations under variability Case 1155                     |

| Table A.4: The size of the repeaters for different interconnect dimensions (width and         |

| spacing) for a 13 nm bus under worst crosstalk. The repeater sizes have been rounded-off.     |

|                                                                                               |

| Table A.5: The number repeaters per unit length required for different interconnect           |

| dimensions (width and spacing) for a 13 nm bus under worst crosstalk. The numbers have        |

been rounded-off......156

| Table A.6: Mean delay (in picoseconds) of interconnects (with repeaters) in the channel        |

|------------------------------------------------------------------------------------------------|

| bus of 13nm for different geometrical configurations under variability Case 1156               |

| Table A.7: The standard deviation (in picoseconds) of the delay of interconnects (with         |

| repeaters) in the channel bus                                                                  |

| Table A.8: Delay variability (%) of interconnects (with repeaters) in the channel bus of       |

| 13nm for different geometrical configurations under variability Case 1157                      |

| Table A.9: Bandwidth of the individual interconnect lines (without repeaters) in Gb/s given    |

| as a function of the interconnect width and spacing for 13 nm157                               |

| Table A.10: Bandwidth of the individual interconnect lines (with repeaters) in Gb/s given      |

| as a function of the interconnect width and spacing for 13 nm                                  |

| Table A.11: Total bandwidth (Gb/s) through the bus constrained in channel width $Wc$ ,         |

| without repeaters in 13nm                                                                      |

| Table A.12: Total bandwidth (Gb/s) through the bus constrained in channel width $Wc$ , with    |

| repeaters in 13nm158                                                                           |

| Table A.13: Power dissipation (mW) at maximum bandwidth for the interconnect of 13 nm          |

| technology without repeaters159                                                                |

| Table A.14: Power dissipation (mW) at maximum bandwidth for the interconnect of 13 nm          |

| technology with repeaters                                                                      |

| Table A.15: Total bandwidth per unit power (Gb/s.mW) consumption for interconnects             |

| with repeaters                                                                                 |

| Table A.16: Probability of link failure (in parts per thousand) of the individual lines of the |

| channel under variability160                                                                   |

| Table A.17: Probability of link failure (in parts per thousand) for the channel under area     |

| constraint                                                                                     |

## List of Abbreviations

| ADC  | Analog to Digital Converter                         |

|------|-----------------------------------------------------|

| AMBA | Advanced Microcontroller Bus Architecture           |

| CDF  | Cumulative Density Function                         |

| CDN  | Clock Distribution Network                          |

| CMOS | Complementary Metal Oxide                           |

| СМР  | Chemical Mechanical Polishing                       |

| DAC  | Digital to Analog Converter                         |

| DCs  | Data Channels                                       |

| DFF  | Data Flip-Flop                                      |

| DSM  | Deep Sub-micron                                     |

| DSPs | Digital Signal Processors                           |

| FFs  | Flip-Flops                                          |

| FPGA | Field Programmable Gate Array Logic                 |

| FUs  | Functional Units                                    |

| IC   | Integrated Circuit                                  |

| ILD  | Inter layer Dielectric                              |

| IP   | Intellectual Property                               |

| ITRS | International Technology Roadmap for Semiconductors |

| LER  | Line edge roughness                                 |

| LFP  | Link Failure Probability                            |

| MC   | Mont Carlo                                          |

| MPU  | Microprocessor Unit                                 |

| MSI  | Minimum Size Inverter                               |

| NAs  | Network Adapters                                    |

| NoC  | Network-on-a Chip                                   |

- OTV Oxide thickness variation

- PDF Probability Density Function

- RAM Random Access Memory

- RO Ring Oscillator

- ROM Read only Memory

- RV Random Variable

- SerDes Serializer Deserializer

- SoC System-on a Chip

- SSTA Statistical Static Timing Analysis

- STA Static Timing Analysis

- VC Video Converter

- μP Microprocessor

### Author's Declaration

This thesis presents the work that was carried out at the Department of Electronics and Electrical Engineering, University of Glasgow under the supervision of Dr. Fernando Rodríguez-Salazar, during the period from June 2007 to January 2011. I declare that the work is entirely my own, except where reference is made to the work of others, and it has not been previously submitted for any other degree or qualification in any university.

Faiz-ul-Hassan

Glasgow, UK

May 2011

## Chapter 1

## Introduction

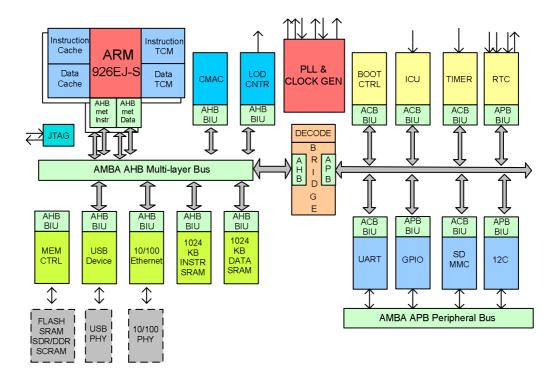

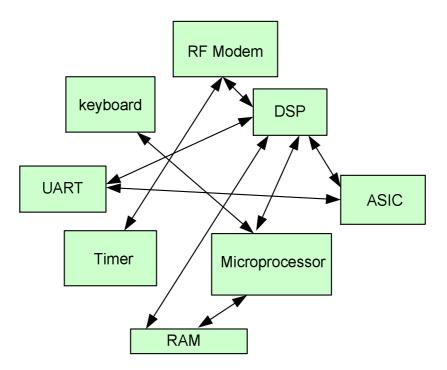

As transistor gate lengths continue to shrink according to Moore's law [1], designers are able to integrate increasingly complex systems in a single microchip. Although in principle it is possible to construct a multi-billion transistor chip in today's technology, the practical problems faced while designing and testing such designs have proven to be too arduous, as evidenced by the increasing designer's productivity gap [50]. Techniques, such as SoC design, where the design complexity is managed by the use of a hierarchy of interconnected modules, have been introduced to overcome this limitation. A typical SoC may include different functional units (FUs) like Microprocessors (µPs), Digital Signal Processors (DSPs), Random Access Memory (RAM), Read only Memory (ROM), Digital to Analog Converters (DACs), Analog to Digital Converters (ADCs), Video Controllers (VCs) and several other Intellectual Property (IP) elements, which typically have already been designed and validated independently (perhaps by third parties). The current state-ofthe-art SoCs allow the design and integration of highly diversified and complex systems using adaptive circuits and increased parallelism [2]. Figure 1.1 shows the example of a SoC with diversified functionalities. For such systems, the designer still faces a number of challenging problems in the design, project management, simulation and verification of these devices. For instance, as the number of FUs integrated into a SoC increases, the role played by the on-chip communication structures becomes progressively important. However the semiconductor industry predicts that future generation of SoCs may possibly

contain several thousands of cores. According to the International Technology Roadmap for Semiconductors (ITRS), on-chip communication is becoming the limiting factor in designing high performance and power efficient SoCs.

Figure 1.1: Typical system implementation of Marvell 88F6282 SoC [3].

#### 1.1 Interconnect-Centric Design Paradigm

Historically, the performance of designs was limited by that of the individual functional units, as communication (through wires) was substantially faster than computation (via transistors). However, the effect of technology scaling is not equally favourable for transistors and wires. With technology scaling, the performance of the devices is continuously improving, whereas the wires are becoming relatively slower, as highlighted by the ITRS [4] and shown in Figure 1.2. Several clock cycles are required for the signals to travel across newer chips. Therefore modern SoC designs, which are abundant with interconnects, are faced with the difficult task of orchestrating the computation of a large number of fast local islands, across the whole chip, by using (relatively) progressively slower interconnects. In order to mitigate this problem, the design paradigm has shifted from computation-centric to interconnect centric, in-line with the SoC methodology as we have seen. In DSM region, the interconnect has become the main bottleneck in the designing of high performance and complex SoCs [5], [6]. The design of efficient interconnects is affected by many issues, as detailed in the following subsections.

Figure 1.2: Projected relative delay of devices and interconnects (local and global) for different technology generations. The relative performance of the global interconnect is decreasing with technology scaling.

#### 1.1.1 Scaling

The objective of the technology scaling is to produce faster devices, increase on-chip component density and reduce energy per storing [7]. The impact of technology scaling on the computational units is that they can now be constructed in smaller sizes (due to device scaling) with same or even with much more functionalities. Therefore the local wires in the cores reduce. However, the global wires which are used to connect cores do not reduce. This allows the cores to operate at a higher frequency, whereas the communication between the cores do not speeds up in the same proportion [8]. Again according to ITRS the interconnect width and pitch decreases with technology scaling, while chip size increases. The result is that the devices and local wires scales with the process technology, whereas the global interconnect do not improve much [9].

#### **1.1.2 Power Dissipation**

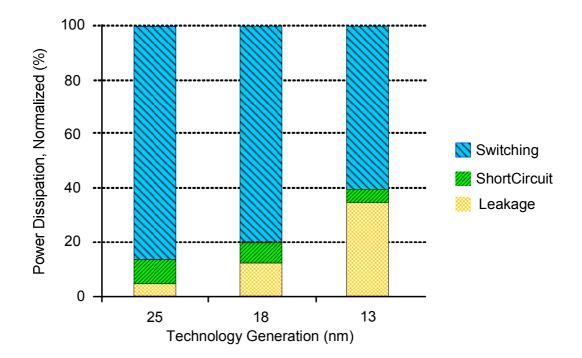

The circuits are designed to operate at higher and higher frequencies in the interest of improved performance. However very dense interconnects switching at high frequencies becomes a major source of power consumption in the circuits and this trend is continuously growing with technology scaling. It has been reported that in a 130nm microprocessor, about 50% of the total power is consumed in the interconnect [10]. In circuit designing, power consumption is taken as a design constraint [11] and designers are always struggling

to reduce it. However, in DSM technologies, reducing power consumption is quite challenging. The supply voltages are decreasing with technology scaling, requiring threshold voltages to decrease to prevent junction breakdown due to higher fields. However, there is an exponential dependence of the leakage current on the threshold voltage so it is expected to become the prevailing part of the total power [12]. Thus the dynamic power which was the dominant component of the power dissipation may not account for the maximum share of the total power in DSM technologies.

#### 1.1.3 Crosstalk

In order to incorporate more and more functionality, the number of transistors on a chip is continuously increasing for every new generation of SoCs [13]. Reduction in the gate delay of devices has made it possible to switch the circuits at higher frequencies to obtain higher performance. But this has introduced an important issue of Crosstalk, which can introduce functional noise and delay variation. The main reason behind the emergence of crosstalk in DSM region is the increase of capacitive and inductive coupling due to the shrinkage of geometries. The functional noise can cause a glitch on the victim line which can travel to the dynamic node causing circuit state to change and resulting in functional failures. Each victim line in a bus may experience different coupling capacitance due to which their propagation delay may vary significantly under different switching patterns of the neighbouring lines. Therefore, this introduces uncertainty in the timing of the signals, thus affecting the communication reliability. As we will demonstrate, crosstalk failures are particularly sensitive to skew variations, which are of course a prevailing characteristic of future designs.

#### 1.1.4 Variability

In the semiconductor industry, variability is often defined as the deviation of the process parameters from their intended or designed values. It has always been an important aspect of semiconductor manufacturing, process control and circuit design. As the semiconductor feature sizes continue to shrink with every new technology generation, the importance of the underlying variability is increasing; so much in fact that in DSM region, variability has become one of the major design challenges and is considered as the hindrance in the way of technology scaling [14]-[16]. The variability affects devices as well as interconnects causing significant unpredictability in the performance and power characteristics of the integrated circuits (ICs). This can lead to certain undesirable effects such as malfunctioning of circuits or performance degradation.

Amongst various sources of device variability, intrinsic parametric fluctuations play an increasingly important role in contemporary and future CMOS devices [17]. These variations are introduced due to the discreteness of charge and matter and cannot be controlled or diminished by tightening the process tolerances. Some of the sources of intrinsic device variability are

- Random dopant fluctuation (RDF)

- Local oxide thickness variation (OTV)

- Gate line edge roughness (LER)

- Strain variations

For state-of-the-art nano-scale circuits and systems, intrinsic parametric fluctuations have significantly affected the signal system timing [18] and behaviour of the circuits at higher frequencies [19]-[20]. In the circuits, it results in component mismatch and thus can reduce the yield and performance.

Figure 1.3: Random discrete dopant effects in deep sub-micrometer CMOS devices [21]. The figure on the left hand side is a solid model of a CMOS transistor and that on the right side is its transparent version showing the discreteness due to dopants in the channel region.

One of the most important sources of intrinsic parameter fluctuations is random dopant fluctuation (RDF) [17] which is caused by the randomness of the dopant position and number in the devices, thus making every device microscopically different from its counterparts. Therefore, the devices which are macroscopically identical will have different performance characteristics, mainly due to the variation in the threshold voltage (Vt). Figure 1.3 shows the significance of RDF in deep sub-micrometer CMOS technologies. The normalized magnitude of the variations due to random dopant

fluctuations increases steadily with technology scaling; as fewer number of dopant atoms are now left in smaller devices (see Figure 1.4 and [21]).

Figure 1.4: Impact of technology scaling on the average number of dopant atoms in the channel.

Variability is also affecting interconnects in deep submicron technologies causing variation in their width, spacing, thickness and inter-layer dielectric thickness. However, there could exist strong spatial pattern dependencies, especially when interconnect variability in chemical mechanical polishing (CMP) is considered. Therefore, total variability can be classified into systematic and random components. A significant portion of the systematic component of variations can be modelled by analyzing the layout characteristic; whereas random variations cannot be modelled.

#### 1.2 Research Overview

The challenges imposed by interconnects in the development of high performance SoCs, and ways to overcome them are an active field of academic research. The aim of this thesis is to advance this effort, in particular on understanding how variability intrinsically affects communication performance, fault tolerance, signal integrity, area and power consumption of the interconnect. To achieve this goal the following objectives are defined.

#### 1.2.1 Research Objective 1

On-chip communication involves the use of different circuit elements and interconnects to move data from one location of the circuit to another. The communication performance entirely depends on these elements. The intrinsic device variability cannot be eliminated in nanometer CMOS devices as it is process independent. This defines a minimum amount of variations in the circuit parameters for a particular size of the devices. In order to design communication structures for DSM technologies, an accurate and realistic estimation of the delay performance of all related circuit elements is required. Unfortunately, there is insufficient data available in this regard. Therefore the objective is:

Accurate characterization of the delay performance of on-chip communication circuit elements for future CMOS technologies in the presence of variability due to RDF.

This data is required to estimate the performance of a complete channel. Based on this information, it is possible to explore and design circuit level fault tolerant communication (sub) systems.

#### 1.2.2 Research Objective 2

In the presence of characterization data of circuit elements, it is more convenient to use computationally efficient analysis techniques like Static Timing Analysis (STA) or Statistical Static Timing Analysis (SSTA). Presently, SSTA is preferred over STA, being computationally efficient and more accurate than STA. The SSTA technique can be used to evaluate the performance of a communication link. However, its accuracy strongly depends on accurate representation of the characterization data of the associated circuit elements. So far, underlying timing distributions are assumed to be Normal, but its validity needs to be investigated in DSM technologies. Therefore objective 2 of this thesis is:

Study the nature of the timing distributions of communication elements and try to find their accurate probability density function. Once this is done, apply these distributions for the SSTA of a large communication channel.

#### 1.2.3 Research Objective 3

As pointed out in [10], as much as 50% of the chip power is consumed by the global interconnects. This power is mainly dissipated in the drivers and repeaters used to improve the delay performance of interconnects. Different coding techniques are used at software level for efficient data transmission [22], [23]. A power optimal repeater insertion technique proposed in [24] is commonly used along with data coding. This technique gives excellent results in terms of power and area savings at the cost of nominal performance degradation. However, the implications of this technique are yet to be investigated for DSM technologies where variability and leakage power effects become quite prominent. Therefore objectives 3 of this thesis is:

To measure different components of power dissipation in repeaters of future technology generations. This data can be useful by the designers to make a choice between low activity parallel links or high activity serial links (as low activity parallel links will dissipate a large amount of the leakage power as compared to the serial links, for particular data requirements). Similarly, a power-optimal repeater insertion technique which accounts for delay variability is required to be developed.

#### 1.2.4 Research Objective 4

Quite significant amount of academic work has been undertaken in finding the optimum configuration of a multi-bit communication channel for best possible performance under power and area constraints [25]-[27]. Again very little work is found in this area considering variability in the figure of merit. So objective 4 is:

Find the optimum configuration of the channel link which gives best bandwidth under power, area and variability constraints. Moreover, a comparison of serial and parallel links is also required to be made in this perspective.

#### 1.2.5 Research Objective 5

In order to ascertain signal integrity in the channel bus, accurate modelling of the crosstalk in aggressor and victim lines is required. In the past, many researchers have published crosstalk analysis models and algorithms [28]-[30] but all of them either require numerical techniques to solve them or do not give sufficient insight into the underlying crosstalk effects on signal responses. In order to reduce this difficulty, this thesis aims:

To find closed form expressions that give accurate voltages for the aggressor and victim lines in time domain, as a function of wire length, due to switching transitions on them. Also study the effect of variability on the delay performance of interconnects in the presence of crosstalk.

#### 2.1 Thesis Organization

The rest of the thesis is organized as follows:

**Chapter 2-** In the beginning of the chapter, different structures used for on-chip communication are briefly discussed. Subsequently, different performance metrics that have been used throughout the thesis to evaluate the performance of on-chip communications are defined.

Chapter 3- In this chapter, the performance of on-chip communication structures under device variability has been characterized through HSPICE simulations. The

characterization results of all the basic elements have been included and discussed. At the end of the chapter, a methodology is given that can be used to estimate the performance of a complete channel link using the characterization data. Moreover, link failure probability has been estimated using this approach.

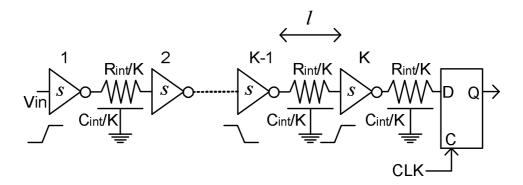

**Chapter 4-** If we talk about core-to-core or router-to-router (for NoCs) communication links, flip-flops are normally used at the input and output of the functional units. Therefore, the output of a router or functional unit is emitted from the flip-flops and is then amplified through the tapered buffer drivers before transmitting through the link. Similarly, at the receiving end, flip-flops are used at the input of the functional unit or router. Again, flip-flops are also used in pipelined interconnects. Therefore, in order to estimate the performance of a link using Statistical Static Timing Analysis (SSTA), accurate representation of the characterization data of the timing parameters of the flip-flops (in the form of PDFs) is required. Furthermore, accurate approximation of the probability distribution functions is also required. In this chapter, this aspect has been described in detail and its application in pipelined communication circuits has been discussed.

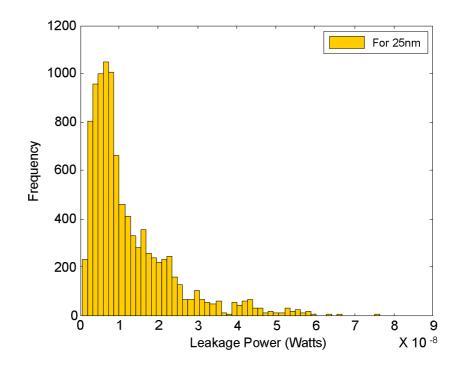

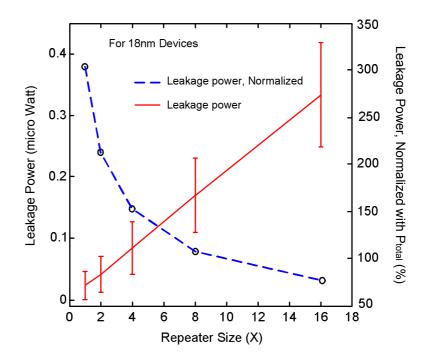

**Chapter 5-** In the start of this chapter, the measurement results for the power dissipation in repeaters for the given three technology generations have been presented. The impact of device variability on the leakage power has also been studied and its implication on NoC links has been discussed. In the next part of this chapter, the optimization of the performance of a single wire link under area, power and variability constraints has been described. The impact of repeater size and inter-repeater segment length on the delay, power, area and variability has been discussed and an optimization scheme has also been proposed.

**Chapter 6-** This chapter describes the performance of a multi-bit parallel link under area and power constraints. The optimization of bandwidth under area, power and variability constraints has been discussed. Moreover, a comparison of parallel vs. serial links has also been described.

**Chapter 7-** In this chapter analytical model for the voltages at aggressor and victim lines under crosstalk effects have been presented. The validity of the data through comparison with the simulation results has been demonstrated. Moreover, the effect of crosstalk on input skew variability has been studied.

**Chapter 8-** This chapter makes a conclusion of the study and also mentions some future work.

## Chapter 2

# On-Chip Communication Structures

A SoC design typically consists of many functional units (FUs) that work together to perform desired functions. The FUs always need to communicate with each other during the execution of the application and it is the responsibility of the on-chip communication structure/ architecture to provide a mechanism for the correct and reliable transfer of information from the source units to the destination units [31]. In addition to this, the on-chip communication structure must satisfy certain metrics like latency, bandwidth, area and power dissipation. The performance of SoC designs largely depends on the choice and design of the underlying communication architecture. Therefore, depending upon the performance requirements, a suitable communication architecture is designed or selected for the SoC design.

### 2.1 Communication Architectures for SoCs

#### 2.1.1 Buses

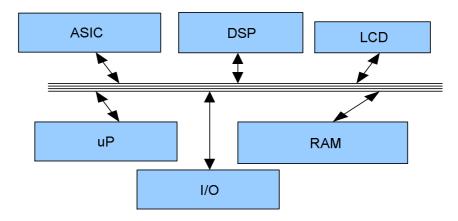

The simplest on-chip communication architecture which is widely used in SoCs is the bus interconnection network [8]. In its simplest form, a bus is a group of wires which provides

a communication media for the exchange of data between different functional units connected to it. Figure 2.1 [31] shows the example of a simple system with many functional units connected through on-chip buses.

Figure 2.1: A SoC in which different components are integrated through the bus communication architecture.

There are several types of bus configurations used in SoCs and the simplest one is called simple shared bus, as shown in Figure 2.2. In this case only one FU at a time has a control over the bus and transfers data. If some other unit also tries to use the bus at the same time in order to transfer data, this will cause bus contention. Arbitrators are used to resolve the conflict who gives the control to one of the units on the basis of the assigned priorities. In bus based systems, this is one of the major problems and efforts have been made to reduce this problem.

Figure 2.2: A simple shared bus, allowing different FUs to share the same communication channel.

In such systems, every unit attached to the bus adds capacitance which results in large delays and large power consumption. This allows only a limited number of components to be attached with the bus in order to keep the delay and power consumption within permissible limits. Due to this reason, the simple bus architecture is not *scalable*.

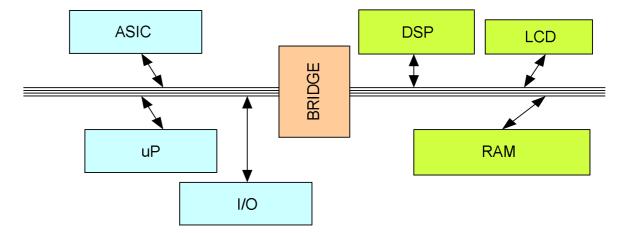

Figure 2.3: A bus divided into two sub-buses using a bridge.

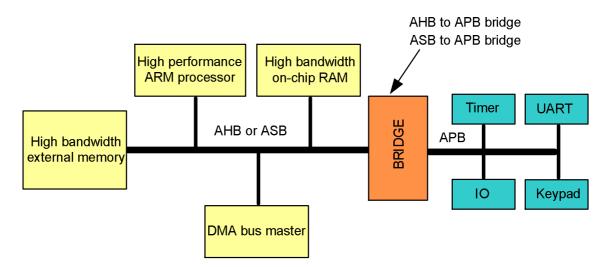

This difficulty is typically reduced by dividing a common bus into several buses using bridges [32]. Figure 2.3 shows a bus split up into two sub-buses using a bridge. The implementation of bridges is fairly simple if it connects buses with same protocols and operating frequencies. There are also other types of bus configurations used in SoCs. Amongst them, Advanced Microcontroller Bus Architecture (AMBA) from ARM [33] defines several bus types which are widely used in SoCs. AMBA proposes various bus solutions for SoCs ranging from simple bus architectures to multi-master high performance bus structures. An example of an AMBA bus is shown in Figure 2.4.

Figure 2.4: An example of AMBA bus. The bridge provides an interface to connect two different types of buses.

#### 2.1.2 Point-to-Point Direct Links

In this architecture, each functional unit is directly connected with a subset of other functional units on the chip, as shown in Figure 2.5. The point-to-point communication architecture eliminates the contention problem of shared medium (buses). Each functional unit, in this architecture, has a network interface block, usually called a router and is directly connected with the neighbouring functional units through the communication links. These links can either be of *input, output* or *bidirectional* type. Unlike buses, as the number of routers (nodes) in this architecture increases, the total bandwidth increases. This property makes point-to-point links suitable to make large scale systems [34]. Unfortunately the number of links (and hence the power and area) grows with the square of the number of functional units. Hence this architecture is not promising for very large systems.

Figure 2.5: A point-to-point communication architecture.

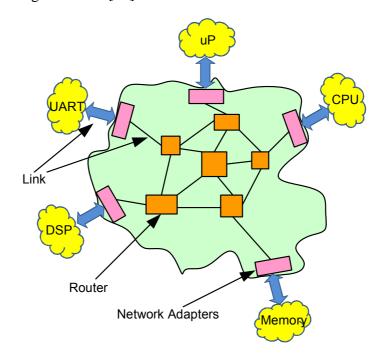

#### 2.1.3 Network Architecture

Network-on-Chip (NoC) has been proposed as a promising solution for on-chip communication in large SoC designs, where the complexity of the design is managed by the use of a number of networked, but self contained blocks [35], [36]. NoC provides a generalized scheme for on-chip global communication. Routing nodes (R) are spread over the chip and connected by point-to-point communication links. The resources or IP blocks are connected to NoC through network adapters (NAs), as shown in Figure 2.6. In a

Network-on-Chip, data is exchanged amongst computing elements (IP blocks) by transmitting and relaying data packets through the interconnection network. There are similarities between the conventional computer networks and NoC, like layered communication models and decoupling of computation and communication. However, there are also some differences which are mainly due to the difference in the cost ratio of wiring and processing resources [37].

Figure 2.6: A conceptual realization of a NoC [34].

In NoC the whole chip can be partitioned into several regions, each of which contains one (or several) IP block(s). These IP blocks can operate with their own clocks and exchange data with other IPs through the switches and communication links. In this way the requirement of a global synchronization is relaxed. Computations are undertaken within locally synchronous IP blocks, and global synchronization is obtained by the execution of semantics embedded within the global communications network. Similarly, in addition to communication infrastructure, NoC can also provide standard IP interfaces which will facilitate the reuse of already verified IP resources [37]. This can simplify the design process and also reduce verification efforts. Due to a layered structure, the signal integrity issues can be addressed at physical, data-link or any higher layer [38].

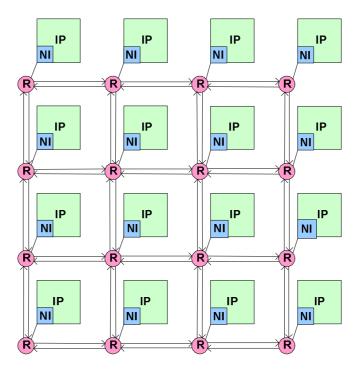

NoC can be constructed in different types of topologies such as 2D mesh, Star, Torus, Octagon, Hypercube [37], [39]. The topology defines the connectivity and layout of the nodes and links on the chip. A  $4 \times 4$  grid topology is shown in Figure 2.7 which presents a regular structure. The topology can be application specific having an irregular structure.

Depending upon the specific requirements of, say bandwidth, the protocol dictates how the nodes and links of NoC will be utilized in the operation.

Figure 2.7: A 4×4 grid structured NoC. Each intellectual property (IP) block is connected to a router through a network interface (NI) adapter. The routers are connected with each other through communication links in a certain topology.

# 2.2 Link as an important Communication Media

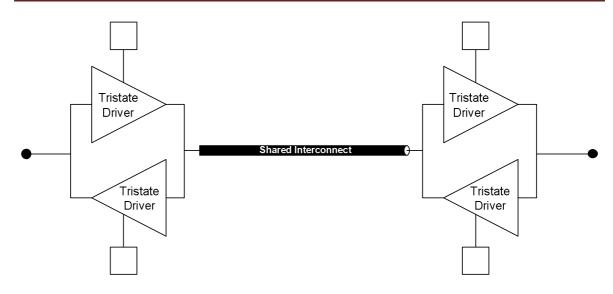

In all communication architectures, the underlying communication links between the functional units or between the functional units and routers are always used. These links form the backbone of any communication architecture. These links can be synchronous, asynchronous or self-timed. However, in this thesis we have chosen to focus on synchronous links due to their prevalence in the industry. Ideally these links should consist of a certain number of parallel wires running between the source and destination. However, in practical circuits (especially in DSM technologies), their construction is not so simple in order to meet certain design requirements. Therefore, it is of great importance to study these links in detail to design high efficiency links.

A link can be bidirectional or unidirectional as shown in Figure 2.8 and 2.9 respectively [40]. A bidirectional link allows the signals to travel in either direction. This provides a flexibility in the routing of interconnects and makes it possible to effectively use available metal tracks on the chip. The implementation of this approach requires the use of tristate buffers on transmitter and receiver sides, as shown in Figure 2.8.

Figure 2.8: A bidirectional link. There is a shared interconnect between the transmitter and receiver.

A unidirectional channel allows the signals to travel only in one direction and thus suggest that a pair of wires should be used in each channel. This approach is less flexible than the bidirectional approach for routing the tracks on the chip, however it provides less contention and more bandwidth.

Figure 2.9: A unidirectional link.

Furthermore, in each interconnect line, different circuit elements like tapered buffer drivers, repeaters and flip-flops are used and there are two basic designs for the interconnect-repeater inserted interconnects and flip-flop (or latch) inserted pipelined interconnects, as shown in Figure 2.10 and 2.11 respectively.

Figure 2.10: Repeater inserted interconnect.

Figure 2.11: Flip-flop inserted pipelined interconnect.

# 2.3 Performance of On-Chip Communication

The performance of on-chip communication in the physical layer can be evaluated from several aspects. In this thesis, however, we consider the metrics exposed in this chapter as important for interconnect centric circuits. We start with a short review on interconnect design. Subsequently, some basic concepts and the mathematical equations describing these metrics are provided. We will make use of these metrics in subsequent chapters for evaluating the merits of different interconnects and for quantifying the effects that variability introduces in the design.

# 2.4 Interconnect Modelling in DSM Technologies

In early days of VLSI design, the clock speeds and integration densities on the chip were low and so the signal integrity effects were minimal. However, with rapid evolution of the semiconductor technology, several important issues associated with interconnects in deep sub-micron technologies have emerged that are effecting the performance of high speed circuits. The problems such as interconnect delay, device and interconnect variability, power dissipation, crosstalk, substrate coupling, inductive coupling and IR drop are among the many emergent challenges which the circuit designers are facing [5], [6].

The fundamental parameters influencing the interconnect delay are on-resistance of the driver, output capacitance of the driver and wire parasitics. The interconnect parasitics of interest are the wire resistance and the wire capacitance (and inductance for very high frequency signalling). These parasitics are a function of the physical properties of the construction and layout of the wires, and will act as an RC load increasing the propagation delay.

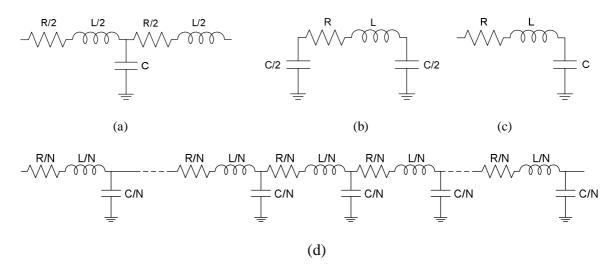

A simple lumped element model is not sufficiently accurate to model state of the art interconnects, which of course are formed by continuously distributed RC (or RLC) elements in space. For simulation purposes, an approximation to a distributed element model can be formed by breaking the interconnect into a large number (N) of smaller identical lumped sections (RLC cells). Some possible models are shown in Figure 2.12 [41]. The accuracy of the simulation results depends on the number of RLC cells (segments) used (i-e the resolution of the lumped RLC model). However, this number is limited in practice by the correspondingly large simulation time of the model.

Figure 2.12: Different interconnect models, (a) the 'T', (b) the 'pi' and (c) the 'ladder'. A long wire is divided into N segments using ladder model and is shown in (d).

#### 2.4.1 Parasitic Resistance

The signal speed through a wire depends, to a first order approximation, to the distributed RC constants in it, and hence to the parasitic resistance. The resistance depends on the wire dimensions and the type of the material used (gold, aluminium, copper or polysilicon). For an interconnect having thickness T and width W, the resistance can be calculated as [41]

$$R = \rho \frac{l}{TW} \tag{2.1}$$

where  $\rho$  is the resistivity and l is the length of the interconnect. Using this formula, the parasitic resistance of a wire of given dimensions can be estimated.

With technology scaling, the wires are becoming thinner and so the parasitic resistance per unit length is increasing for minimum wire widths (according to ITRS).

#### 2.4.2 Parasitic Capacitance

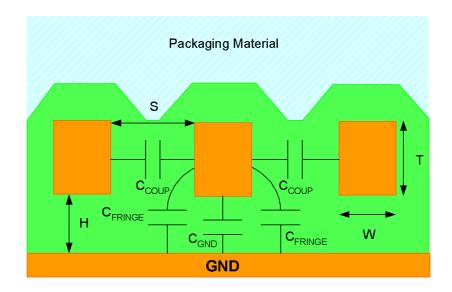

The accurate estimation of the parasitic capacitances of the interconnects in DSM technologies is a complex task. This is due to the fact that each interconnect is a three dimensional metal structure surrounded by a number of other interconnects with significant variations of shape, width, thickness and spacing with respect to other conductors and

ground planes [42]. Unlike the simplest way of calculating the capacitance of a parallel plate capacitor, the capacitance measurement in integrated circuits require the consideration of other factors like coupling capacitance and fringe capacitance in addition to ground capacitance, as shown in Figure 2.13. It has been observed that the contribution of the coupling capacitance in the total interconnect capacitance is increasing rapidly with technology scaling due to the reduction of interconnect spacing and an increased aspect ratio of wires.

Figure 2.13: The cross-sectional view of an interconnect surrounded by two parallel similar interconnects over a ground plane (in the top global layer) showing different components of capacitance.

An accurate estimation of the parasitic capacitance can be made by solving Maxwell's equations in three dimensions, provided all material and geometrical details are available. Presently, computer aided software tools like Raphael [43] and FASTCAP [44] are available which are based on 2D or 3D field solvers which can calculate the parasitic capacitance with reasonable accuracy. However, some important aspects of interconnect parasitic capacitance can also be calculated using closed form models such as [45] as follows- The ground capacitance per unit length (considering the fringe flux) to the underlying plane is given by

$$C_g = \varepsilon \left[ \frac{W}{H} + 3.28 \left( \frac{T}{T + 2H} \right)^{0.023} \left( \frac{S}{S + 2H} \right)^{1.16} \right]$$

(2.2)

Where  $\varepsilon$  is the dielectric constant of the insulating material and W, H, S and T are the geometrical dimensions shown in Figure 2.13. Similarly the coupling capacitance per unit length is given by

$$C_{c} = \varepsilon \left[ 1.064 \left( \frac{T}{S} \right) \left( \frac{T + 2H}{T + 2H + 0.5S} \right)^{0.695} + \left( \frac{W}{W + 0.8S} \right)^{1.4148} \left( \frac{T + 2H}{T + 2H + 0.5S} \right)^{0.804} + 0.831 \left( \frac{W}{W + 0.8S} \right)^{0.055} \left( \frac{2H}{2H + 0.5S} \right)^{3.542} \right]$$

(2.3)

The total capacitance of the wire can be calculated as

$$C_{Tot} = C_g + 2C_c \tag{2.4}$$

Typically such derivations are limited to particular domains. In this case the valid range for using the approximation is

$$0.3 \le \frac{W}{H} \le 10, \qquad 0.3 \le \frac{S}{H} \le 10, \qquad \frac{T}{H} \le 10$$

Other closed form capacitance models with different interconnect configurations are also given in [46], [47], [134].

#### 2.4.3 Inductance

Inductance is another important parasitic. It can be described by the magnetic flux generated due to the flow of current in a loop. In integrated circuits several electrical loops can exist which produce inductive parasitic effects. At high enough operational frequencies of the circuits, the inductive impedance associated with interconnects become comparable or prevail over the resistive part [48]. The inductive interference caused due to the interaction of the magnetic fields can affect the signal integrity in the form of signal distortion, delay variation, crosstalk noise and glitches.

In this research we have ignored the effects of inductance due to the following reasons:

(a) The interconnect delay is not significantly effected by the inductive effects. For scaled global interconnects, the line resistance per unit length increases (according to the ITRS) and so the effects of inductance on the performance of global interconnects actually diminishes [49]. This is true, especially for the technologies and interconnect geometries we have considered in this thesis. Using the delay models of [143] for RC and RLC interconnects, it has been found that the percent increase in the propagation delay caused by neglecting inductance and considering an RLC line as an RC line, is nominal. For instance, for the global interconnects of 25, 18 and 13 nm technology generations at S=1S<sub>min</sub> and W=1W<sub>min</sub>, this increase is 1.74%, 1.25% and 1.16% respectively. Similarly for the fastest interconnects with

$S=10S_{min}$ ,  $W=10W_{min}$  (we used in this thesis), the maximum increase in delay is 14.2%, 10.92% and 10.01% for the corresponding technologies.

- (b) The inductive effects have much longer spatial range in contrast to the capacitive effects which primarily depends on features in close proximity. The inductance matrix generally becomes very dense and is difficult to specify in a straightforward way. Therefore, accurately simulating inductive effects might not be practical [48].

- (c) The effective interconnect inductance in a chip environment is very difficult to predict accurately. For the estimation of the inductance associated with a wire, the return current path should be defined. However, the return current path can be dynamic in a real chip environment, as it depends strongly on the signal condition and the overall layout and configuration of the integrated circuit.

#### 2.4.4 Impact of Technology Scaling on Interconnect Parasitics