Bukhori, Muhammad Faiz (2011) *Simulation of charge-trapping in nanoscale MOSFETs in the presence of random-dopants-induced variability.* PhD thesis.

http://theses.gla.ac.uk/2810/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# Simulation of Charge-Trapping in Nano-Scale MOSFETs in the Presence of Random-Dopants-Induced Variability

#### Muhammad Faiz Bukhori

Submitted in fulfillment of the requirements for the Degree of *Doctor of Philosophy*

Department of Electronics & Electrical Engineering

School of Engineering

College of Science and Engineering

University of Glasgow

Copyright © Muhammad Faiz Bukhori, 2011.

#### **Abstract**

The growing variability of electrical characteristics is a major issue associated with continuous downscaling of contemporary bulk MOSFETs. In addition, the operating conditions brought about by these same scaling trends have pushed MOSFET degradation mechanisms such as Bias Temperature Instability (BTI) to the forefront as a critical reliability threat. This thesis investigates the impact of this ageing phenomena, in conjunction with device variability, on key MOSFET electrical parameters.

A three-dimensional drift-diffusion approximation is adopted as the simulation approach in this work, with random dopant fluctuations—the dominant source of statistical variability—included in the simulations. The testbed device is a realistic 35 nm physical gate length n-channel conventional bulk MOSFET. 1000 microscopically different implementations of the transistor are simulated and subjected to charge-trapping at the oxide interface. The statistical simulations reveal relatively rare but very large threshold voltage shifts, with magnitudes over 3 times than that predicted by the conventional theoretical approach. The physical origin of this effect is investigated in terms of the electrostatic influences of the random dopants and trapped charges on the channel electron concentration. Simulations with progressively increased trapped charge densities—emulating the characteristic condition of BTI degradation—result in further variability of the threshold voltage distribution. Weak correlations of the order of 10-2 are found between the pre-degradation threshold voltage and post-degradation threshold voltage shift distributions.

The importance of accounting for random dopant fluctuations in the simulations is emphasised in order to obtain qualitative agreement between simulation results and published experimental measurements. Finally, the information gained from these device-level physical simulations is integrated into statistical compact models, making the information available to circuit designers.

## Acknowledgements

I am grateful to have received research supervision from Dr. Scott Roy and Professor Asen Asenov. I have benefitted tremendously from Dr. Scott's prompt reviews of my work with helpful comments for improvement, as well as his articulations of complex semiconductor physics in easy terms and occasional humour. I am inspired by Professor Asen's exemplary passion in conducting research, his comprehensive knowledge and the general advice he gave related to career advancement, not to mention the self-esteem-boosting salutation with which he greets everyone at the group's weekly meetings — "Good morning to the very best of the device modelling world in the entire universe and all other parallel universes!".

Many thanks to the members of the Device Modelling Group — some of them for helpful discussions and technical assistances; others for being a nice bunch of colleagues composing a comfortable working environment. A hearty "*Terima Kasih*" also goes to the community of Malaysian postgraduate students and their families for generally making me feel at home here in Glasgow.

I am also privileged to have a fellow colleague who is also my wife. Throughout the years of our studies, Noor 'Ain Kamsani has been a supportive peer as well as a wonderful wife; and I hope that I have been reciprocative in that aspect. I owe a debt of gratitude to my parents in Malaysia for their persistent support, particularly for taking a good care of our Glasgow-born son, Neil Luqman, while both my wife and I were writing our theses. Finally, I would also like to acknowledge the sponsorship of my study provided by Universiti Kebangsaan Malaysia and the Ministry of Higher Education of Malaysia.

#### **Publications**

#### **Journals**

- M. F. Bukhori, S. Roy, A. Asenov, "Statistical Aspects of Reliability in Bulk MOSFETs with Multiple Defect States and Random Discrete Dopants", Microelectronics Reliability, vol. 48, no. 8-9, pp. 1549-1552, Aug./Sept. 2008.

- **M. F. Bukhori**, S. Roy, A. Asenov,, "Simulation of Statistical Aspects of Charge Trapping and Related Degradation in Bulk MOSFETs in the Presence of Random Discrete Dopants", *IEEE Transactions on Electron Devices*, vol. 57, no. 4, pp. 795-803, April 2010.

#### Conferences

- M. F. Bukhori, S. Roy, A. Asenov, "Statistical Simulation of RTS Amplitude Distribution in Realistic Bulk MOSFETs Subject to Random Discrete Dopants", 9th International Conference on Ultimate Integration of Silicon 2008, pp. 171-174.

- A. Asenov, S. Roy, A. R. Brown, G. Roy, C. Alexander, C. Riddet, C. Millar, B. Cheng, A. Martinez, N. Seoane, D. Reid, M. F. Bukhori, X. Wang, U. Kovac, "Advanced Simulation of Statistical Variability and Reliability in Nano CMOS transistors", *IEEE International Electron Devices Meeting 2008*, pp. 421.

- M. F. Bukhori, A. Brown, S. Roy, A. Asenov, "Simulation of Statistical Aspects

of Reliability in Nano CMOS", 2009 IEEE International Integrated Reliability

Workshop Final Report, pp. 82-85.

- M. F. Bukhori, T. Grasser, B. Kaczer, H. Reisinger, A. Asenov, "'Atomistic' Simulations of RTS Amplitudes Due to Single and Multiple Charged Defect States and Their Interactions", 2010 IEEE International Integrated Reliability Workshop Final Report, pp. 76-79.

J. Franco, B. Kaczer, Ph.J. Roussel, M. Toledano-Luque, T. Grasser, J. Mitard, L.-Å. Ragnarsson, L. Witters, T. Chiarella, M. Togo, W.-E Wang, N. Horiguchi, M. F. Bukhori, A. Asenov, and G. Groeseneken, "Impact of Single Charged Gate Oxide Defects on the Performance and Scaling of Nanoscaled FETs", IEEE International Electron Devices Meeting 2011, submitted.

# **Contents**

| Abst | ract    |         |            |         |        |      |       | •    | •    | •    | •    |      | •   | •   | •   | •        | • | • | ii  |

|------|---------|---------|------------|---------|--------|------|-------|------|------|------|------|------|-----|-----|-----|----------|---|---|-----|

| Ackı | nowle   | dgemei  | nts        |         |        |      |       | •    |      |      |      |      | •   | •   |     |          | • |   | iii |

| Publ | licatio | ns .    |            |         |        | •    |       | •    |      |      |      |      | •   | •   |     |          |   |   | iv  |

|      |         |         |            |         |        |      |       |      |      |      |      |      |     |     |     |          |   |   |     |

| 1.   | Intro   | oductio | n          |         |        |      |       | •    |      |      | •    |      | •   | •   | •   |          |   |   | 1   |

|      | 1.1     | Motiv   | ation .    |         |        |      |       |      | •    |      |      |      |     |     |     |          |   |   | 1   |

|      | 1.2     | Aims a  | and Objec  | etives  |        |      |       |      |      |      |      |      |     |     |     |          |   |   | 3   |

|      | 1.3     | Thesis  | Outline    |         |        |      |       |      |      |      |      |      |     |     |     |          |   |   | 4   |

|      | Chap    | ter Ref | erences    |         |        |      |       |      |      |      |      |      |     |     |     |          |   |   | 5   |

|      |         |         |            |         |        |      |       |      |      |      |      |      |     |     |     |          |   |   |     |

| 2.   | Back    | ground  | d          |         |        |      |       |      |      |      |      |      |     |     |     | •        | • |   | 8   |

|      | 2.1     | Intrins | sic Variab | ility   |        | -    |       |      |      |      |      |      |     |     |     |          |   |   | 8   |

|      |         | 2.1.1   | Random     | Dopar   | nts    |      |       |      |      |      |      |      |     |     |     |          |   |   | 11  |

|      | 2.2     | Charge  | e-Trappin  | g .     |        |      |       |      |      |      |      |      |     |     |     |          |   |   | 14  |

|      |         | 2.2.1   | Random     | Telegr  | aph S  | Sign | al    |      |      |      |      |      |     |     |     |          |   |   | 15  |

|      |         | 2.2.2   | Bias Ter   | nperatu | ıre In | stab | ility | /    |      |      |      |      |     |     |     |          |   |   | 18  |

|      |         |         | 2.2.2.1    | Cause   | s and  | Eff  | ects  | s of | fΒ   | ΤI   |      |      |     |     |     |          |   |   | 18  |

|      |         |         | 2.2.2.2    | Time-   | Depe   | nde  | nce   | M    | od   | el c | of E | 3TI  |     |     |     |          |   |   | 20  |

|      |         |         | 2.2.2.3    | Dynaı   | nic B  | TI:  | Fre   | que  | enc  | су а | and  | Dι   | ıty | Су  | cle | <b>e</b> |   |   |     |

|      |         |         |            | Deper   | ndenc  | ies  |       |      |      |      |      |      |     |     |     |          |   |   | 24  |

|      |         |         | 2.2.2.4    | Types   | and ]  | Ene  | rgy   | Dis  | stri | ibu  | tioı | n of | `th | e T | ra  | ps       |   |   | 26  |

|      |         |         | 2.2.2.5    | Time    |        |      |       |      |      |      |      |      |     |     |     |          |   |   |     |

|      |         |         |            | BTI a   |        |      |       |      |      |      |      |      |     |     |     |          |   |   | 28  |

|      |         |         | 2226       | Recov   | erv F  | Effe | et    |      |      |      |      |      |     |     |     |          |   |   | 30  |

|    |     | 2.2.2.7 BTI Characterisation Technique                         |

|----|-----|----------------------------------------------------------------|

|    |     | 2.2.2.8 Statistical Aspects of BTI Degradation 31              |

|    | 2.3 | Summary                                                        |

|    | Cha | pter References                                                |

| 3. | Sim | ulation Methodology                                            |

|    | 3.1 | Introduction                                                   |

|    | 3.2 | Simulation Techniques                                          |

|    |     | 3.2.1 Drift-Diffusion                                          |

|    |     | 3.2.2 Monte Carlo                                              |

|    |     | 3.2.3 Cost-Accuracy Analysis                                   |

|    | 3.3 | Glasgow 'Atomistic' Device Simulator                           |

|    |     | 3.3.1 Modelling Random Discrete Dopants and Trapped            |

|    |     | Charges                                                        |

|    |     | 3.3.2 The Simulated Device                                     |

|    | 3.4 | Summary                                                        |

|    | Cha | pter References                                                |

| 4. | The | Effects of Interface-Trapping of Single Discrete Charge 69     |

|    | 4.1 | Introduction                                                   |

|    | 4.2 | Simulation Approach                                            |

|    | 4.3 | Continuous Doping                                              |

|    |     | 4.3.1 Effects of a Single Trapped Charge Electron on Potential |

|    |     | Distribution and Electron Concentration                        |

|    |     | 4.3.2 Gate Bias Dependence                                     |

|    |     | 4.3.3 Positional Dependence                                    |

|    |     | 4.3.4 Drain Bias Dependence                                    |

|    | 11  | Atomistic Doning 70                                            |

|            |      | 4.4.1 Statistical Simulation of the Effects of a Single Trapped |    |

|------------|------|-----------------------------------------------------------------|----|

|            |      | Charge                                                          | 3  |

|            |      | 4.4.2 Distribution of Drain Current Change 84                   | 4  |

|            |      | 4.4.3 Origin of Anomalously Large Magnitudes of Current         |    |

|            |      | Reduction                                                       | 2  |

|            |      | 4.4.4 Distribution of Threshold Voltage Shift                   | 4  |

|            |      | 4.4.5 Gate Voltage Dependence of $\Delta V_{\rm G}$             | 7  |

|            | 4.5  | Summary                                                         | 01 |

|            | Cha  | ter References                                                  | 02 |

| 5.         | Stat | stical Simulation of Progressive PBTI Degradation 10            | 06 |

|            | 5.1  | Introduction                                                    | 06 |

|            | 5.2  | Simulation Approach                                             | 08 |

|            |      | 5.2.1 The Justification for the Choice of Simulated             |    |

|            |      | Device                                                          | 08 |

|            |      | 5.2.2 Statistical Assignment of Trapped Charges 10              | 09 |

|            | 5.3  | The Effects of Statistical Distribution of Trapped Charges 11   | 11 |

|            | 5.4  | Impact of Progressive Degradation                               | 15 |

|            |      | 5.4.1 Evolution of Threshold Voltage Distribution 11            | 15 |

|            |      | 5.4.2 Variability-Enhanced Degradation                          | 24 |

|            |      | 5.4.3 Correlations                                              | 27 |

|            |      | 5.4.4 Comparison Against Theoretical Predictions 12             | 29 |

|            | 5.5  | Summary                                                         | 32 |

|            | Cha  | ter References                                                  | 32 |

| <b>6</b> . | Inte | rating the Effects of Trapped Charges into Compact Models 13    | 36 |

|            | 6.1  | Introduction                                                    | 36 |

|            | 6.2  | Statistical Parameter Extraction Strategy                       | 38 |

|            | 6.2  | Extraction Popults and Evaluation of Acquiross                  | 11 |

|    | 6.4  | Generating Statistical Compact Models Parameters                  | 146 |

|----|------|-------------------------------------------------------------------|-----|

|    | 6.5  | Statistical Circuit Simulation: Impact of Progressive PBTI in the |     |

|    |      | Presence of Random-Dopants-Induced Variability                    | 154 |

|    | 6.6  | Summary                                                           | 157 |

|    | Chaj | pter References                                                   | 158 |

| 7. | Con  | clusion                                                           | 160 |

|    | 7 1  | Future Work and Outlook                                           | 163 |

# **List of Figures**

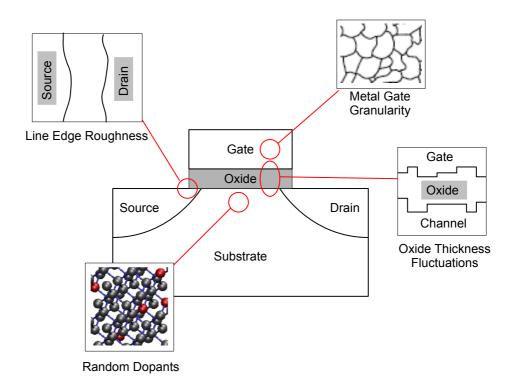

| 2.1: | Illustration of some key sources of intrinsic variability in conventional |    |

|------|---------------------------------------------------------------------------|----|

|      | bulk MOSFETs.                                                             | 10 |

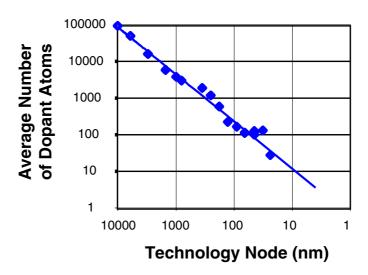

| 2.2: | Average number of dopant atoms in the channel expressed as a              |    |

|      | function of advancement of technology node.                               | 12 |

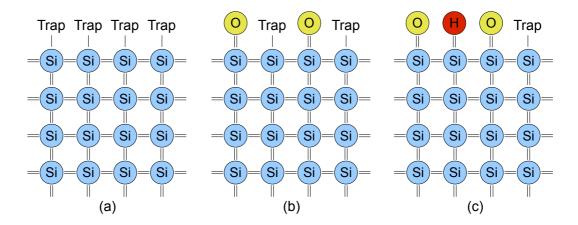

| 2.3: | (a) Unpaired valence electrons at the silicon surface form electrically   |    |

|      | active interface traps. (b) Thermal oxidation pairs most of the silicon   |    |

|      | surface atoms with oxygen atoms, thus reducing the number of              |    |

|      | interface traps. (c) After annealing with hydrogen ambient the amount     |    |

|      | of interface traps is further reduced.                                    | 15 |

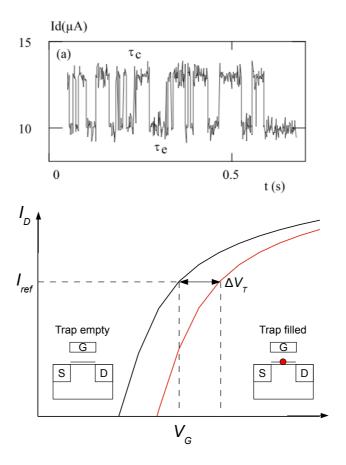

| 2.4: | (Top) Typical plot of drain current fluctuations due to RTS. (Bottom)     |    |

|      | Definition of threshold voltage shift by RTS                              | 16 |

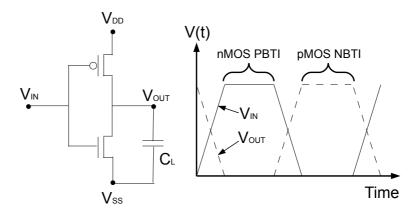

| 2.5: | (Left) Circuit schematic of a CMOS inverter driving a capacitive load.    |    |

|      | (Right) Timing diagram illustrating degradation modes during CMOS         |    |

|      | inverter operation.                                                       | 19 |

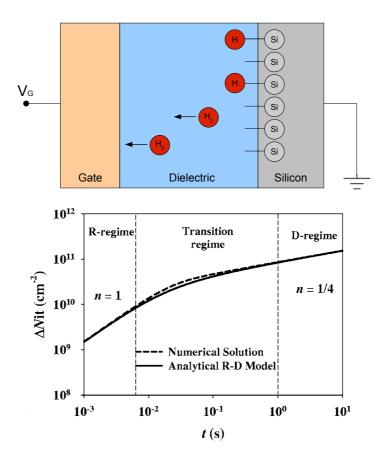

| 2.6: | (Top) Illustration of the RD model: passivated Si-H bonds at the          |    |

|      | interface are broken and the hydrogen diffuses away into the              |    |

|      | dielectric, leaving behind electrically active interface traps. (Bottom)  |    |

|      | Interface trap generation calculated with the analytical RD model,        |    |

|      | showing the reaction and diffusion regimes of NBTI.                       | 21 |

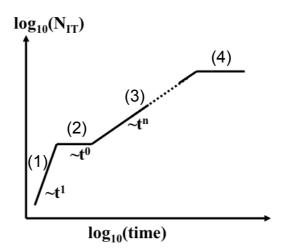

| 2.7:  | The schematic of 4 different regimes of the stress phase of the                                               |    |

|-------|---------------------------------------------------------------------------------------------------------------|----|

|       | classical RD model of NBTI. Regime 3 is the most observed                                                     |    |

|       | characteristic feature of NBTI stress, exhibiting the power-law stress                                        |    |

|       | time dependence of the degradation.                                                                           | 22 |

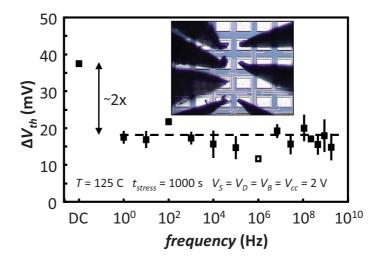

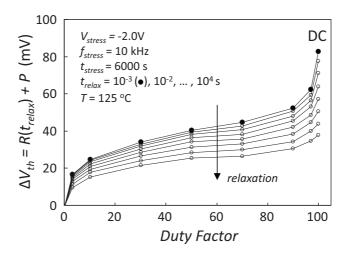

| 2.8:  | Threshold voltage shifts due to AC NBTI stress.                                                               | 25 |

| 2.9:  | Duty factor dependence of NBTI.                                                                               | 26 |

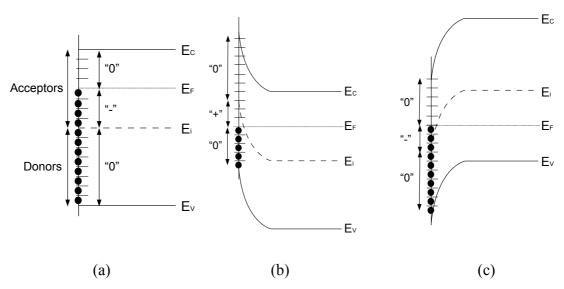

| 2.10: | (a) Band diagram at flat band condition of an n-type substrate                                                |    |

|       | illustrating the occupancy of the two types of interface traps and the                                        |    |

|       | resulting charge polarities. (b) Positively charged interface traps at the                                    |    |

|       | strong inversion of a p-channel MOSFET. (c) Negatively charged                                                |    |

|       | interface traps at the strong inversion of an n-channel MOSFET                                                | 27 |

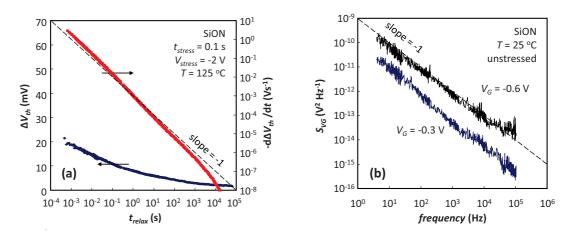

| 2.11: | (a) The rate of recovery $d\Delta V_{\rm th}/{\rm d}t_{\rm relax}$ extracted from the $\Delta {\rm Vth}$ NBTI |    |

|       | relaxation transient follows $1/t_{\rm relax}$ for ~7 decades. (b) Gate-referred                              |    |

|       | noise spectra measured on the same unstressed device shows a clear 1/                                         |    |

|       | f behaviour, which is widely accepted to be a superposition of states                                         |    |

|       | with widely distributed time scales.                                                                          | 28 |

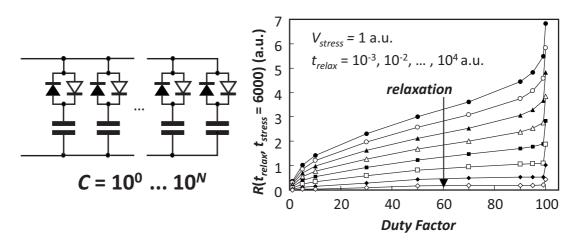

| 2.12: | (a) The capture and emission time constants of traps are modelled by                                          |    |

|       | asymmetric diodes, while the total threshold voltage shift is                                                 |    |

|       | proportional to the sum of voltages across the capacitors. (b) The                                            |    |

|       | experimentally reported DF-dependence of NBTI is qualitatively well-                                          |    |

|       | reproduced by the equivalent circuit over many relaxation times                                               | 29 |

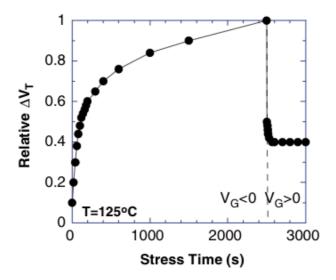

| 2.13: | Relative threshold voltage shift due to NBTI as a function of stress                                          |    |

|       | time                                                                                                          | 30 |

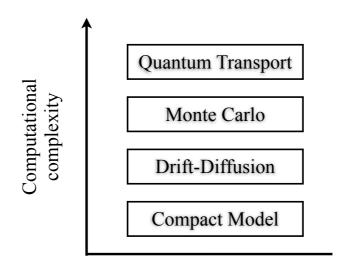

| 3.1:  | Simulation approaches available in the Glasgow Device Modelling                                               |    |

|       | Group and their hierarchical order of computational complexity                                                | 44 |

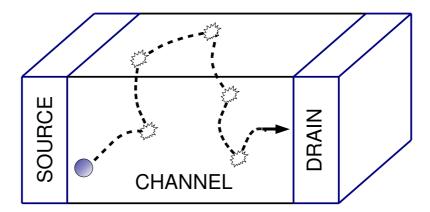

| 3.2: | Illustration of a carrier travelling from source to drain being randomly             |    |

|------|--------------------------------------------------------------------------------------|----|

|      | scattered in between periods of free-flight in a Monte Carlo                         |    |

|      | simulation.                                                                          | 48 |

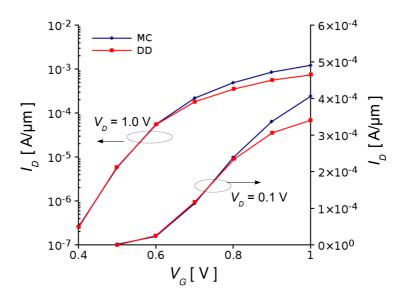

| 3.3: | Comparison of $I_D$ - $V_G$ characteristics from MC and DD simulations of            |    |

|      | the same device.                                                                     | 50 |

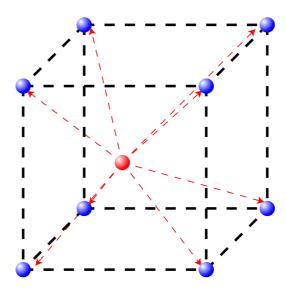

| 3.4: | The Cloud-in-Cell charge assignment splits the doping density of an                  |    |

|      | impurity atom (red sphere) to the 8 grid nodes of a mesh cell                        | 55 |

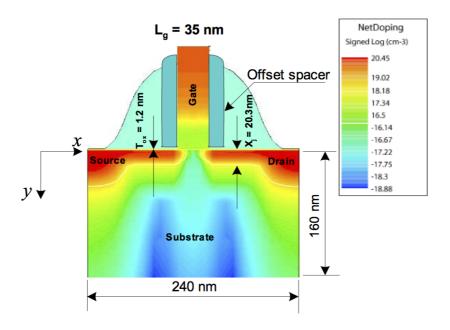

| 3.5: | The 2D doping net doping profile of the template device used in this                 |    |

|      | study.                                                                               | 60 |

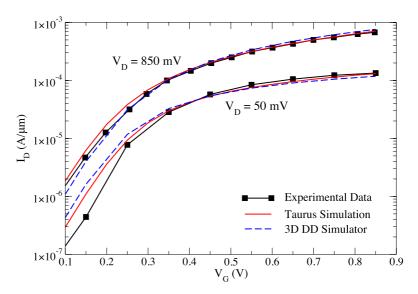

| 3.6: | The experimentally measured $I_D$ - $V_G$ characteristics of the 35 nm               |    |

|      | Toshiba MOSFET compare well with the characteristics obtained                        |    |

|      | from the TCAD and 'atomistic' simulator.                                             | 61 |

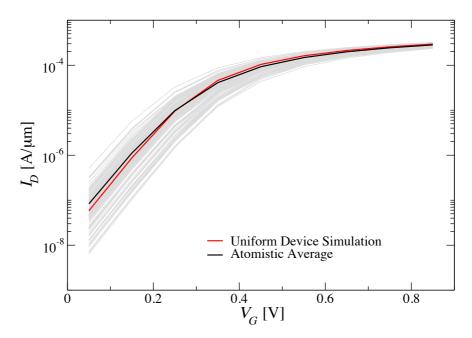

| 3.7: | The $I_D$ - $V_G$ characteristics of 200 microscopically different version of        |    |

|      | the testbed transistor simulated at low drain bias of $V_D = 100$ mV                 | 62 |

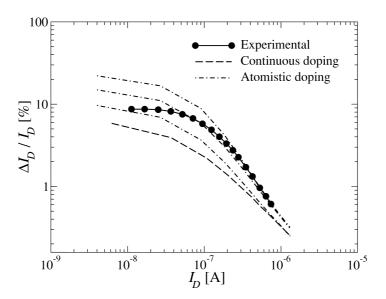

| 4.1: | Dependence of the RTS amplitude on the drain current in a relatively                 |    |

|      | large MOSFET with channel width 0.1 $\mu m$ , channel length 1 $\mu m$ ,             |    |

|      | oxide thickness 20 nm and channel doping $10^{17}~\text{cm}^{-3}$ measured and       |    |

|      | simulated at $V_D = 50 \text{ mV}$ .                                                 | 71 |

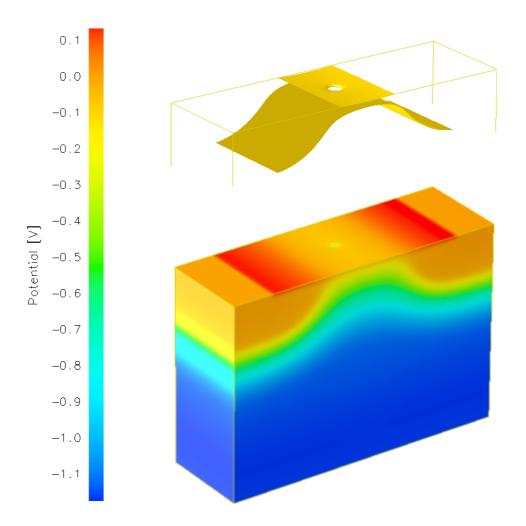

| 4.2: | Potential distribution inside a 35 $\times$ 35 nm n-channel MOSFET with a            |    |

|      | single electron trapped in the middle of the channel interface. The top              |    |

|      | plane shows an electron equi-concentration contour.                                  | 73 |

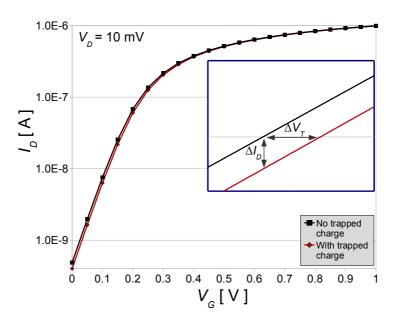

| 4.3: | $I_D$ - $V_G$ characteristic of a 35 $\times$ 35 nm n-channel MOSFET simulated       |    |

|      | with and without a single mid-channel trapped electron. Inset figure                 |    |

|      | shows the definition of threshold voltage shift $\Delta V_{\rm T}$ and drain current |    |

|      | change $\Delta I_{\rm D}$ caused by the trapped charge.                              | 75 |

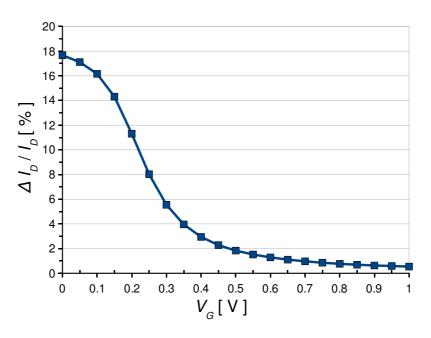

| 4.4:  | Gate bias dependence of the relative drain current change caused by a   |    |

|-------|-------------------------------------------------------------------------|----|

|       | single electron trapped in the middle of the channel.                   | 75 |

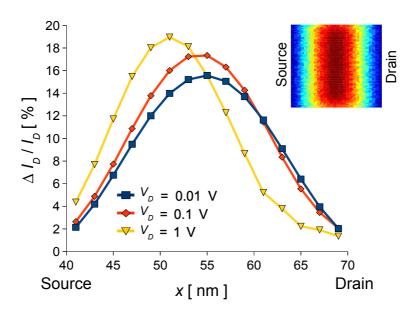

| 4.5:  | The relative current reduction caused by a single trapped electron      |    |

|       | moved across the width-centre positions along the channel-oxide         |    |

|       | interface from source to drain at various drain voltages                | 77 |

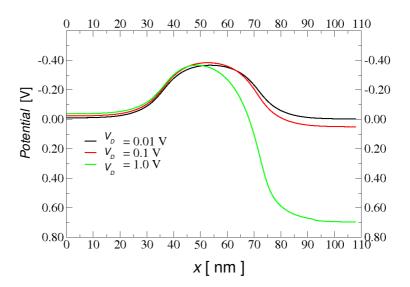

| 4.6:  | Potential profile along the channel interface plane from source to      |    |

|       | drain at various drain bias voltages.                                   | 78 |

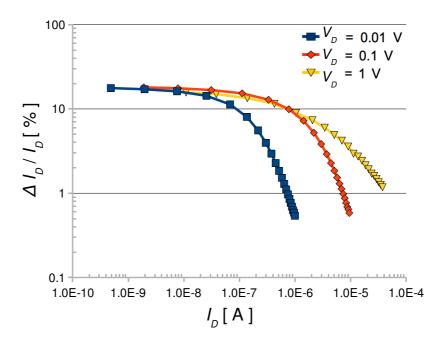

| 4.7:  | The dependence of relative drain current reduction on the drain         |    |

|       | current caused by a single trapped charge in the middle of the channel  |    |

|       | at various drain voltages.                                              | 79 |

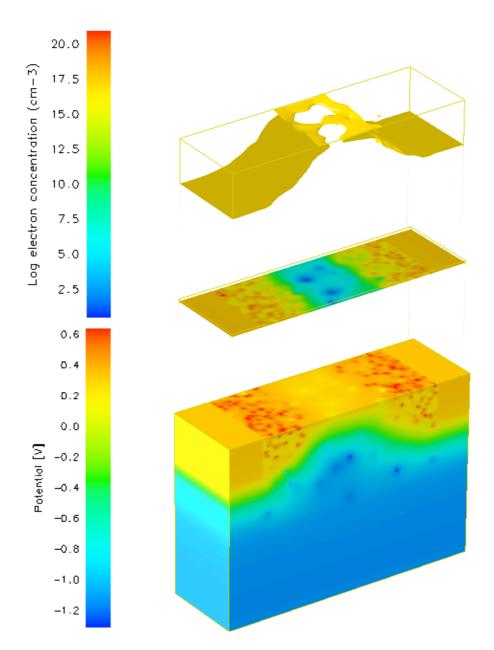

| 4.8:  | The effects of atomicity coming from the discrete impurities can        |    |

|       | clearly be seen as the random and localised variations of potential     |    |

|       | (bottom bulk) and electron concentration (middle and top plots)         | 81 |

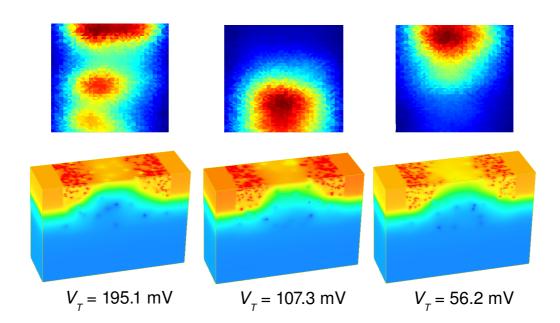

| 4.9:  | Potential distribution in three microscopically different transistors   |    |

|       | with random discrete doping is shown in the bulk. The positional        |    |

|       | dependence of relative current reduction mapped as a function of the    |    |

|       | trap's location over the entire channel area is projected on the top    |    |

|       | plane of each transistor.                                               | 82 |

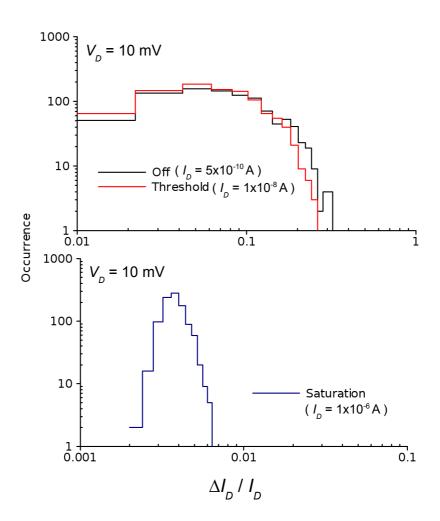

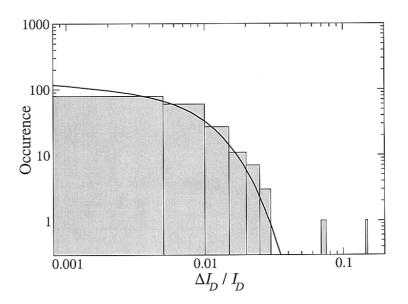

| 4.10: | Distribution of drain current reduction caused by a single trapped      |    |

|       | charge in 1000 35 $\times$ 35 nm MOSFETs simulated at three gate biases |    |

|       | corresponding to leakage, threshold and drive.                          | 85 |

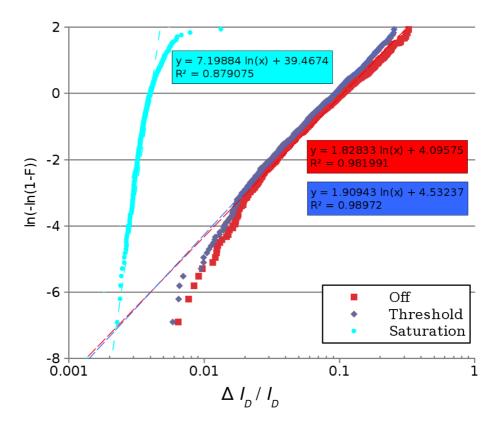

| 4.11: | Weibull probability plot of normalized drain current change caused by   |    |

|       | a single trapped charge in 1000 35 $\times$ 35 nm MOSFETs simulated at  |    |

|       | three gate biases corresponding to leakage, threshold and drive current |    |

|       | conditions                                                              | 87 |

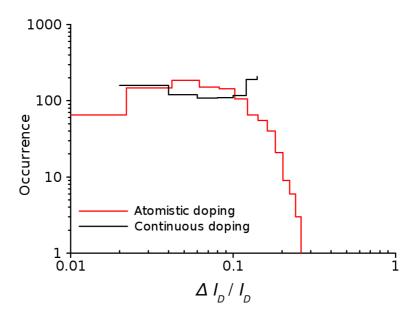

| 4.12: | Distribution of drain current change at threshold gate biases from      |    |

|       | continuous and 'atomistic' doping simulations in 1000                   |    |

|       | 35 × 35 nm MOSFFTs                                                      | 91 |

| 4.13: | Experimentally observed distribution of RTS amplitudes in 187                        |     |

|-------|--------------------------------------------------------------------------------------|-----|

|       | 500 × 500 nm MOSFETs                                                                 | 91  |

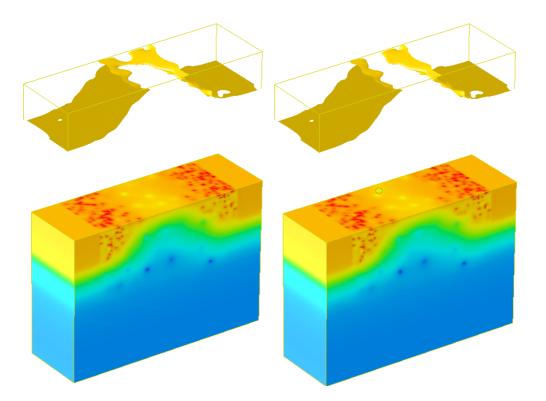

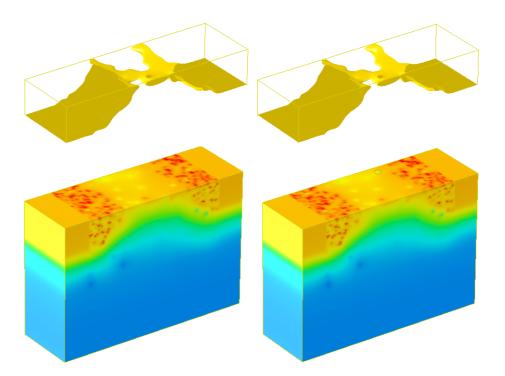

| 4.14: | Potential distribution in a MOSFET with a large current change; (left)               |     |

|       | with no trap, and (right) with a trapped electron (location is marked by             |     |

|       | circle) cutting off a critical current path. Top planes show electron iso-           |     |

|       | concentration surface.                                                               | 92  |

| 4.15: | Potential distribution in a MOSFET with a small current change; (left)               |     |

|       | with no trap, and (right) with a trapped electron (location is marked by             |     |

|       | circle) leaving the current path unaffected                                          | 93  |

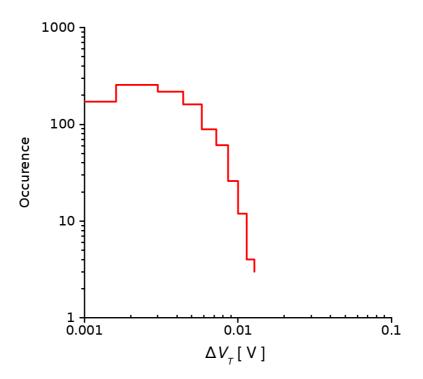

| 4.16: | Distribution of threshold voltage shift in an ensemble of 1000                       |     |

|       | atomistically doped 35 $\times$ 35 nm MOSFETs, each with a single                    |     |

|       | interface-trapped charge                                                             | 95  |

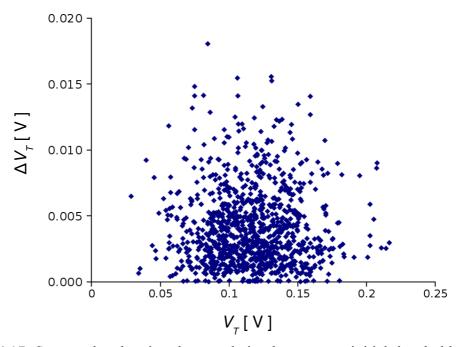

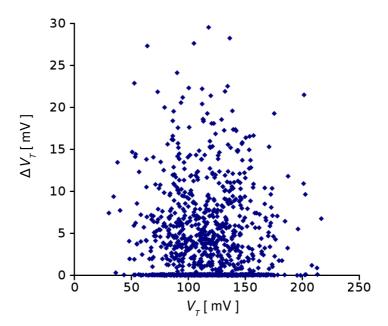

| 4.17: | Scatter plot showing the correlation between an initial threshold                    |     |

|       | voltage $V_T$ and the resulting threshold voltage shift $\Delta V_T$ in 1000,        |     |

|       | $35 \times 35$ nm MOSFETs subjected to a single trapped charge                       | 96  |

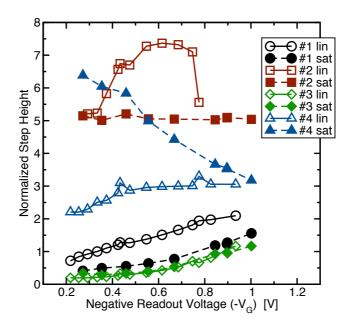

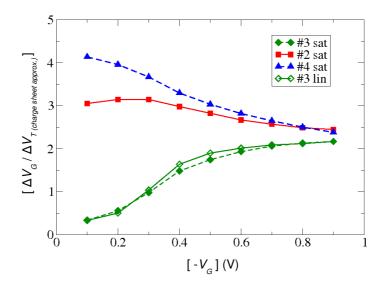

| 4.18: | Experimentally recorded step heights (measured gate voltage shift                    |     |

|       | normalised to the shift expected from charge sheet approximation) by                 |     |

|       | single defects in a pMOSFET across varying readout voltages                          | 98  |

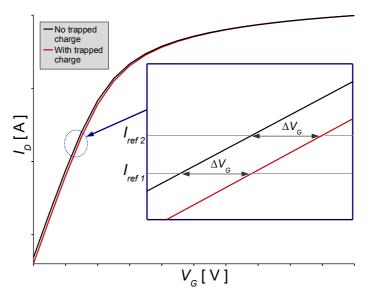

| 4.19: | The definition of the $\Delta V_{\rm G}$ parameter which is the change in gate       |     |

|       | voltage to give common reference current levels, before and after the                |     |

|       | charge trapping event                                                                | 99  |

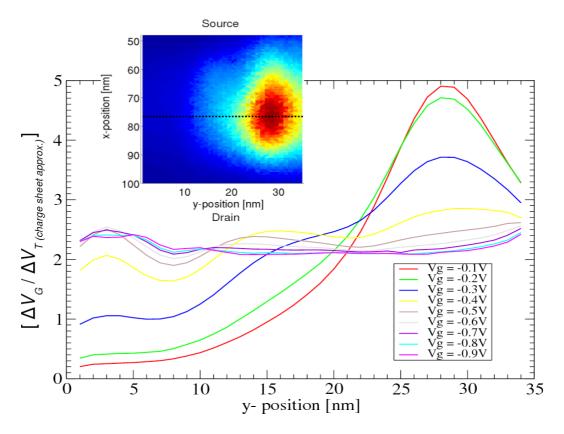

| 4.20: | The $\Delta V_{\rm G}$ registered by a single trapped charge at positions across the |     |

|       | width of the device. Inset figure shows the sensitivity map of the                   |     |

|       | entire channel area; the dotted line marks the path along which the                  |     |

|       | trapped charge is placed.                                                            | 100 |

| 4.21: | Selected defects from the simulations which closely replicate some of                |     |

|       | the experimentally measured responses shown in Figure 4.18                           | 101 |

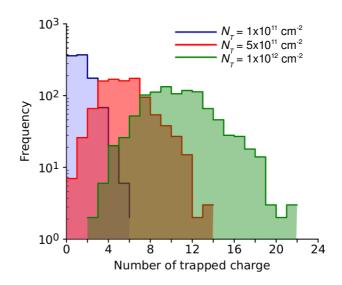

| 5.1: | The distribution of the number of trapped charges in the simulated                   |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | ensembles of 1000 MOSFETs is modelled by a Poisson distribution                      |     |

|      | for a given $N_T$ with its mean $(\mu)$ corresponding to the average number          |     |

|      | of trapped charge found in the whole sample                                          | 110 |

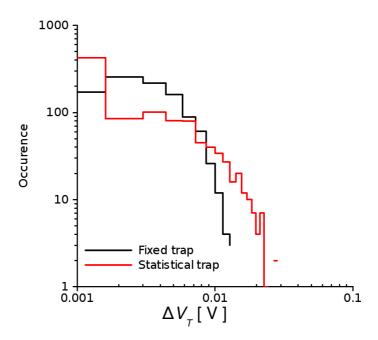

| 5.2: | The distribution of threshold voltage change in an ensemble of 1000                  |     |

|      | units of MOSFETs simulated with statistical number of trapped                        |     |

|      | charges and uniformly fixed, single trapped charge                                   | 112 |

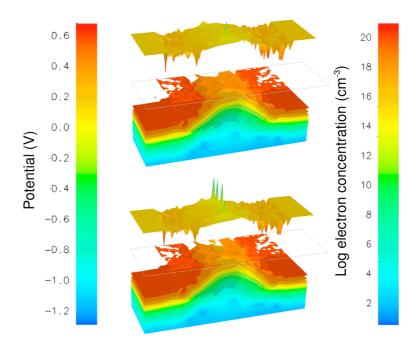

| 5.3: | Electron concentration at threshold gate voltage in a MOSFET with                    |     |

|      | large threshold voltage change; (top figure) with no trapped electrons;              |     |

|      | (bottom figure) with randomly trapped carriers blocking the main                     |     |

|      | current path. The top planes show the potential at the Si/SiO <sub>2</sub> interface |     |

|      | plane.                                                                               | 113 |

| 5.4: | Correlation plot between initial threshold voltage in 1000 'fresh'                   |     |

|      | devices and their post-stress threshold voltage shifts subjected to                  |     |

|      | trapped charge density of $N_T = 1 \times 10^{11}$ cm <sup>-2</sup>                  | 114 |

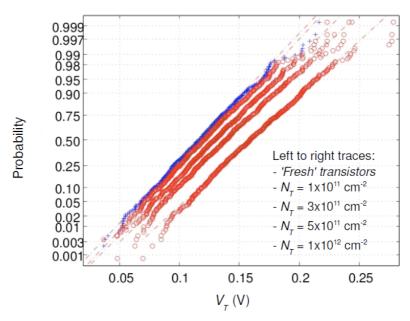

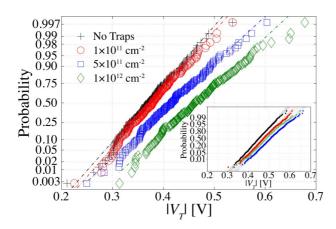

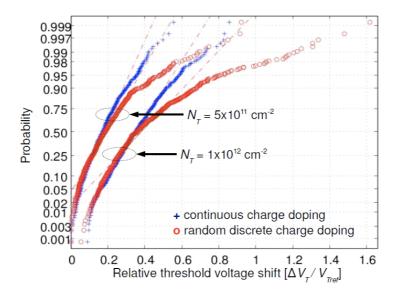

| 5.5: | Distribution of threshold voltages in 1000 'fresh' (blue crosses) and                |     |

|      | 'degraded' (red circles) MOSFETs subjected to progressive increase of                |     |

|      | the sheet density of trapped electrons.                                              | 116 |

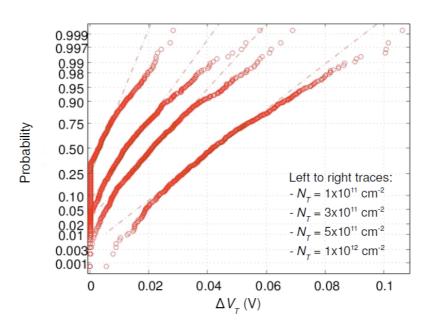

| 5.6: | The distribution of threshold voltage change in 1000 nMOSFETs                        |     |

|      | subjected to progressive increase of the sheet density of trapped                    |     |

|      | electrons.                                                                           | 117 |

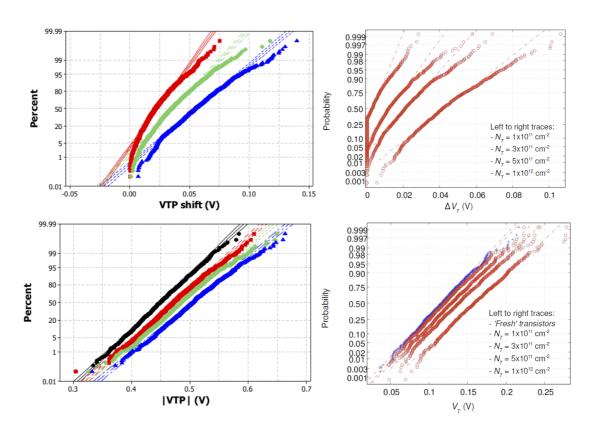

| 5.7: | (Left top and bottom) The experimentally measured distribution of                    |     |

|      | threshold voltage change and threshold voltage of more than a                        |     |

|      | thousand PMOS transistors at three different stress times. (Right top                |     |

|      | and bottom) The corresponding simulation results of this work                        | 119 |

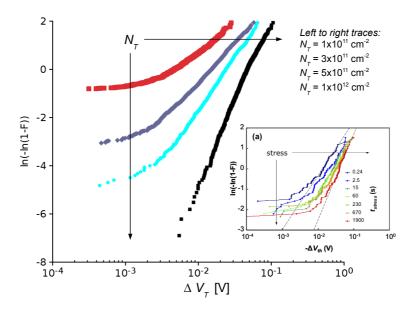

| 5.8: | Weibull plot of the distribution of threshold voltage change in 1000                 |     |

|      | nMOSFETs subjected to progressive increase of the sheet density of                   |     |

|      | trapped electrons.                                                                   | 120 |

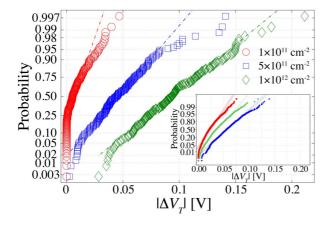

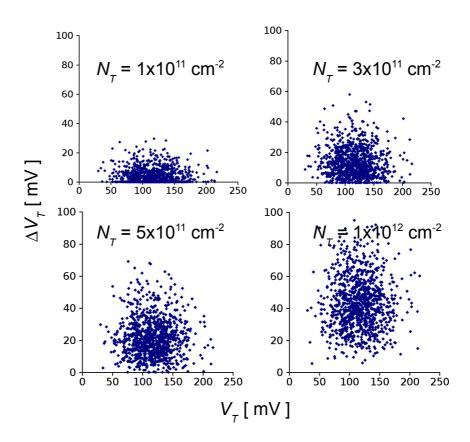

| 5.9:  | $V_{\rm T}$ and $\Delta V_{\rm T}$ of 200 microscopically different 45-nm p-channel devices           |     |

|-------|-------------------------------------------------------------------------------------------------------|-----|

|       | simulated in with trap sheet densities of $1\times10^{11}$ , $5\times10^{11}$ and $1\times10^{12}$ cm |     |

|       | <sup>-2</sup> . Inset shows experimental results for a similar device                                 | 123 |

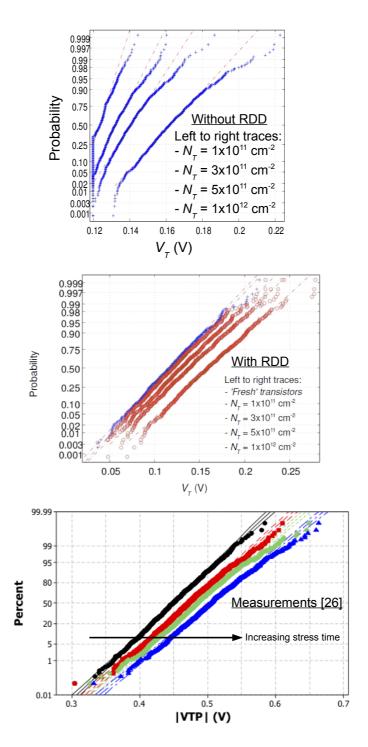

| 5.10: | ( $Top$ ) $V_T$ distribution obtained from simulations of MOSFETs                                     |     |

|       | subjected to progressive degradation without considering for the                                      |     |

|       | effects of random discrete dopants. (Middle) Corresponding                                            |     |

|       | distributions when the simulations take into account the random                                       |     |

|       | dopants effects. (Bottom) Experimentally measured $V_T$ distributions.                                | 125 |

| 5.11: | Relative threshold voltage change ( $\Delta V_{\rm T}/V_{\rm Tref}$ ) distribution from               |     |

|       | simulations of MOSFETs with continuous doping and random discrete                                     |     |

|       | dopants subjected to the same increasing densities of trapped                                         |     |

|       | charges                                                                                               | 126 |

| 5.12: | Correlation plot between initial threshold voltage $V_T$ in 1000 'fresh'                              |     |

|       | devices and their post-stress threshold voltage shifts $\Delta V_{\mathrm{T}}$ at four                |     |

|       | levels of interface-trapped charge density $N_{\rm T}$                                                | 128 |

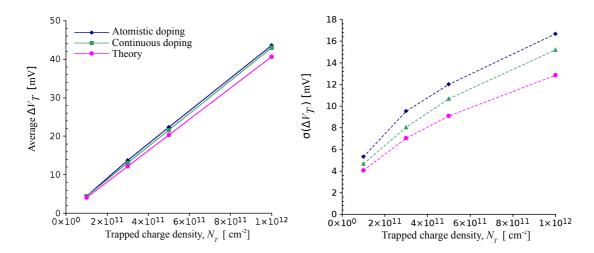

| 5.13: | (Left) Average threshold voltage change, and (Right) its standard                                     |     |

|       | deviation as a function of interface trap density obtained from the                                   |     |

|       | simulations compared against calculations.                                                            | 129 |

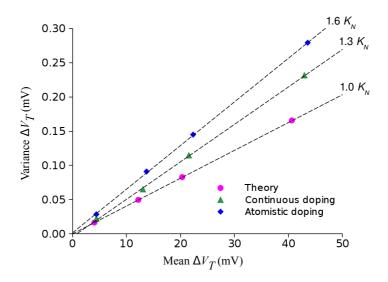

| 5.14: | Variance of threshold voltage shift $\Delta V_{\rm T}$ is fully described by mean $\Delta V_{\rm T}$  |     |

|       | and constant $K$ , which quantifies the impact of the position of the                                 |     |

|       | trapped charge and random dopants on the $\Delta V_{\rm T}$ distribution                              | 131 |

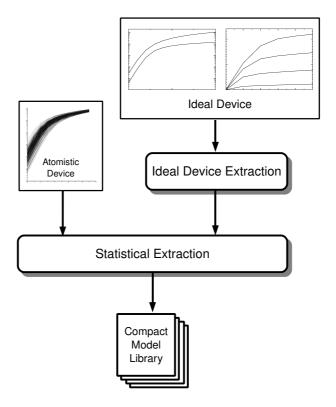

| 6.1:  | Flowchart of the two-stage compact model parameter methodology                                        |     |

|       | used in this work.                                                                                    | 139 |

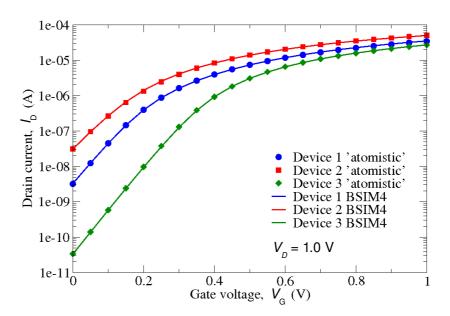

| 6.2:  | $I_D$ - $V_G$ characteristics of 3 microscopically different MOSFETs,                                 |     |

|       | obtained from HSPICE simulations utilising BSIM4 compact models                                       |     |

|       | containing key parameters extracted from the corresponding 3D                                         |     |

|       | 'atomistic' simulations.                                                                              | 140 |

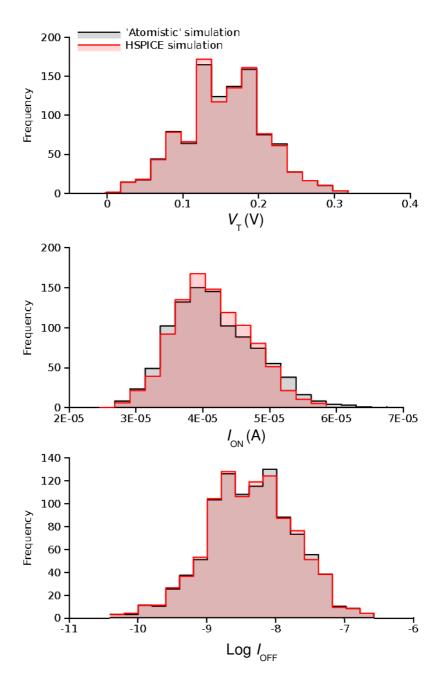

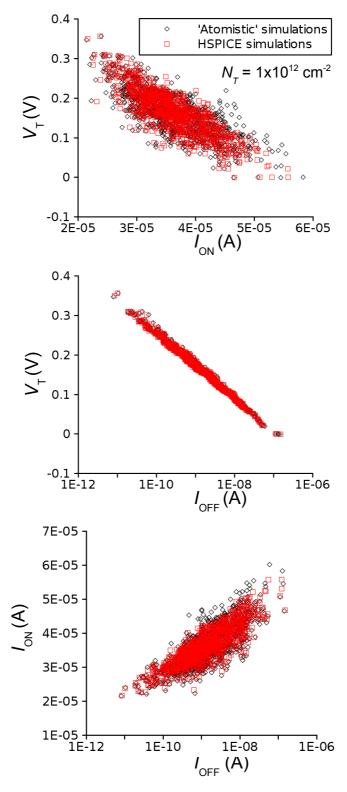

| 6.3:  | The distribution of threshold voltage, on current and leakage current            |     |

|-------|----------------------------------------------------------------------------------|-----|

|       | obtained from HSPICE simulations of 1000 nMOSFETs compared                       |     |

|       | against the corresponding distributions generated by 3D physical                 |     |

|       | simulations of the same ensemble of devices. The distribution shown              |     |

|       | are for MOSFETs with interface-trapped charge density of $N_{\rm T}$ =           |     |

|       | $2\times10^{11}~\text{cm}^{-2}$                                                  | 142 |

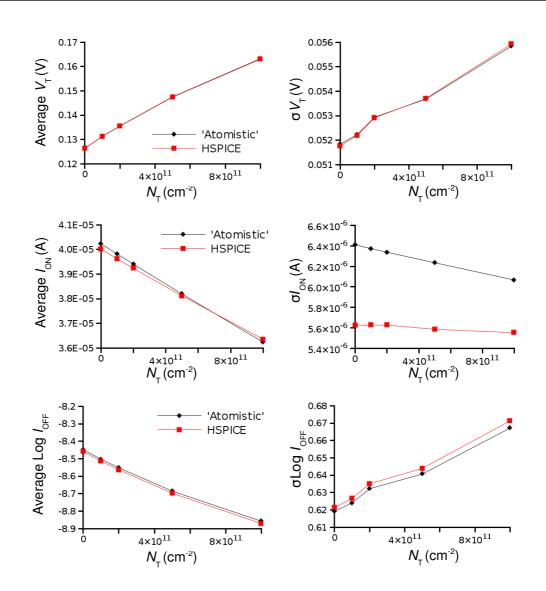

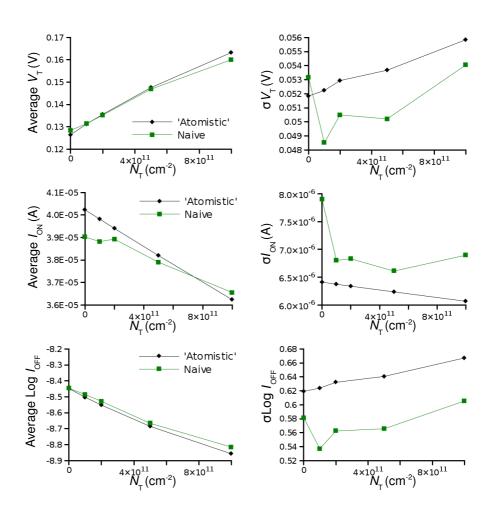

| 6.4:  | Mean and standard deviation of the figures of merit at increasing                |     |

|       | levels of interface-trapped charge densities, obtained from 'atomistic'          |     |

|       | simulations compared against the corresponding HSPICE                            |     |

|       | simulations                                                                      | 143 |

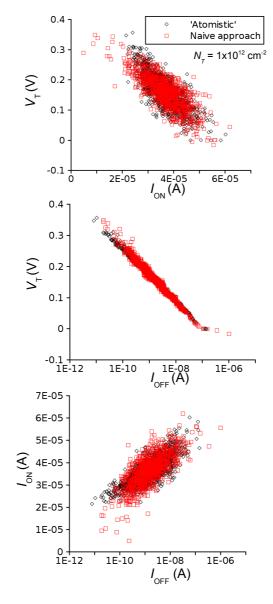

| 6.5:  | Scatter plots between figures of merit obtained from HSPICE and 3D               |     |

|       | 'atomistic' simulations of 1000 MOSFETs.                                         | 145 |

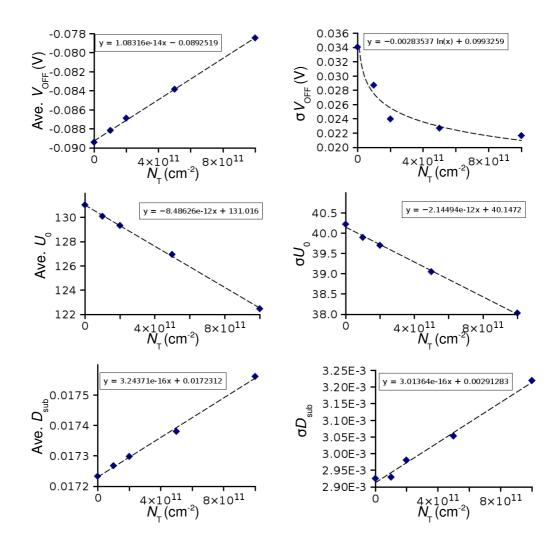

| 6.6:  | Mean and standard deviation of the 6 BSIM4 compact model                         |     |

|       | parameters extracted from 1000 physically simulated MOSFETs with                 |     |

|       | at various increasing levels of interface-trapped charge densities               | 147 |

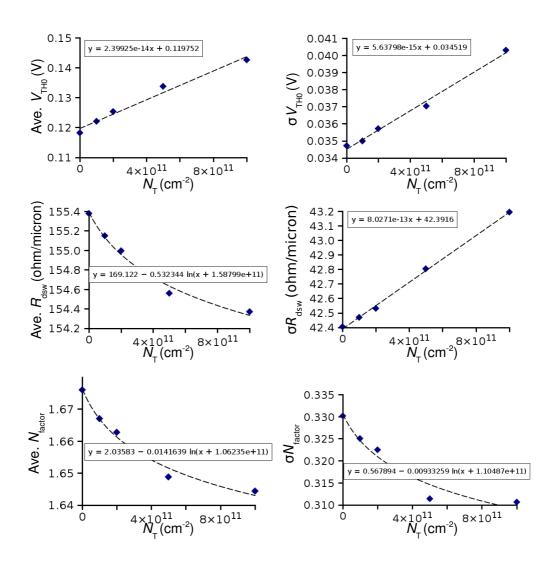

| 6.7:  | Mean and standard deviation of the figures of merit at increasing                |     |

|       | levels of interface-trapped charge densities obtained from 'atomistic'           |     |

|       | simulations and naïve approach.                                                  | 148 |

| 6.8:  | Scatter plots between figures of merit obtained from naïve approach of           |     |

|       | statistical compact model parameter generation, and 3D 'atomistic'               |     |

|       | simulations of 1000 MOSFETs.                                                     | 149 |

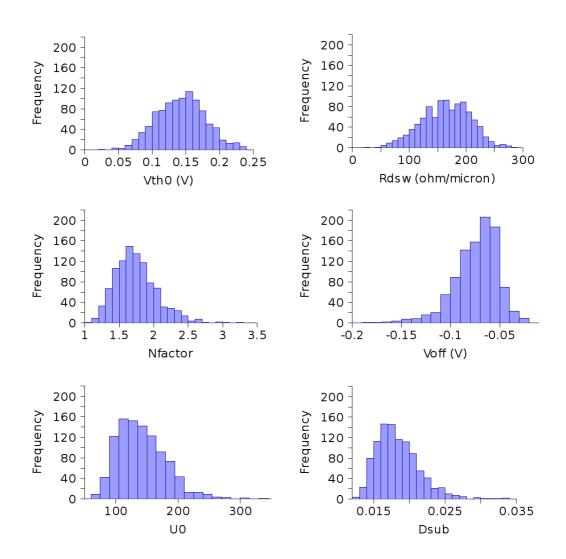

| 6.9:  | Distribution of compact model parameters directly extracted from the             |     |

|       | 3D 'atomistic' simulations of 1000 microscopically different                     |     |

|       | transistors subjected to $N_T = 5 \times 10^{11} \text{ cm}^{-2}$                | 151 |

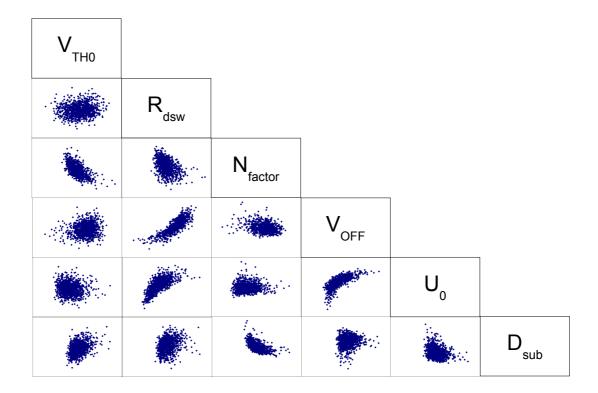

| 6.10: | Scatter plots illustrating the correlations between the compact model            |     |

|       | parameters directly extracted from the 3D 'atomistic' simulations of             |     |

|       | 1000 microscopically different transistors subjected to $N_T = 5 \times 10^{11}$ |     |

|       | $cm^{-2}$                                                                        | 152 |

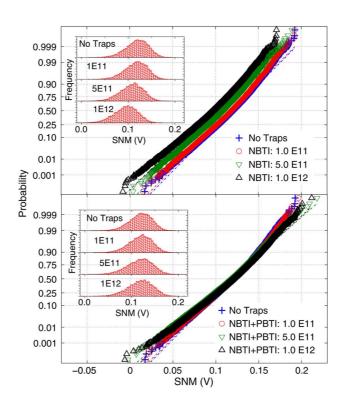

| 6.11: Probability plot of SNM for different degradation stages of NBTI only                      |     |

|--------------------------------------------------------------------------------------------------|-----|

| and NBTI + PBTI. Inset: Corresponding distributions of SNM                                       | 153 |

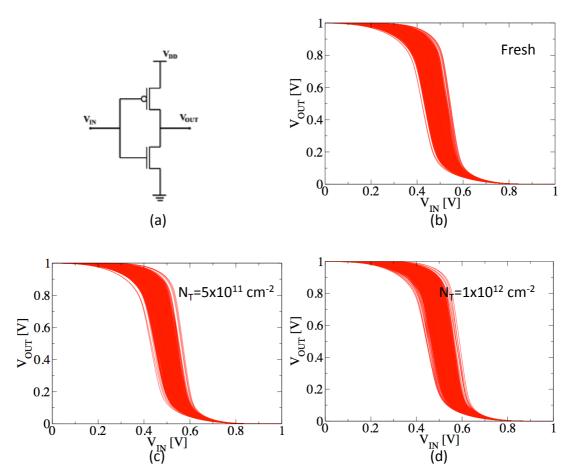

| 6.12: (a) Circuit schematic of a CMOS logic inverter. Transfer                                   |     |

| characteristics of 1000 inverters at (b) with no trapped charges, (c)                            |     |

| with trapped charge density $N_T$ =5x10 <sup>11</sup> cm <sup>-2</sup> , (d) with trapped charge |     |

| density $N_T=1\times10^{12}$ cm <sup>-2</sup> .                                                  | 155 |

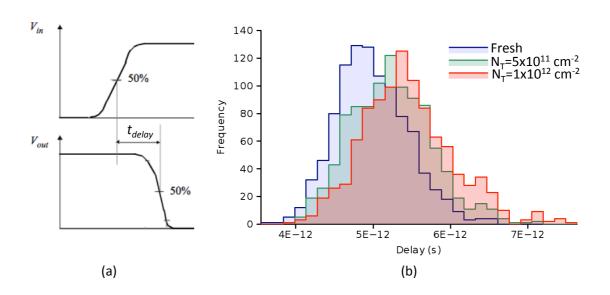

| 6.13: (a) Inverter circuit delay definition. (b) Distribution of delay of 1000                   |     |

| inverters at three different levels of trapped charge densities                                  | 156 |

# **List of Tables**

| 4.1: | Values of parameters $k$ and $\lambda$ are altered with the increase of gate bias,         |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | reflecting a change in the shape and dispersion of the $\Delta I_D/I_D$                    |     |

|      | distribution                                                                               | 88  |

| 5.1: | $V_{\rm T}$ distributions at various instances of increasing trapped charge                |     |

|      | densities $N_T$ .                                                                          | 116 |

| 5.2: | Effect of the increased sheet density of trapped charge and the relative                   |     |

|      | magnitude of rare threshold voltage shifts.                                                | 118 |

| 5.3: | Correlation coefficient between pre-stress threshold voltages $V_T$ and                    |     |

|      | the corresponding post-degradation threshold voltage shifts $\Delta V_{\mathrm{T}}$ of the |     |

|      | 1000 units of simulated transistors at various instances of increasing                     |     |

|      | interface-trapped charge density $N_{T}$                                                   | 128 |

| 6.1: | Correlation coefficient between figures of merit obtained from 3D                          |     |

|      | 'atomistic' simulations (bottom left figures) and HSPICE simulations                       |     |

|      | (top right figures) for $N_T = 1 \times 10^{12} \text{ cm}^{-2}$                           | 144 |

| 6.2: | Correlation coefficient between figures of merit obtained from 3D                          |     |

|      | 'atomistic' simulations (bottom left figures) and naïve approach (top                      |     |

|      | right figures) for $N_T = 1 \times 10^{12} \text{ cm}^{-2}$ .                              | 150 |

| 6.3: | Average and standard deviation of flip voltages of 1000 inverters at                       |     |

|      | three different levels of trapped charge densities                                         | 156 |

| 6.4: | Average and standard deviation of delays of 1000 inverters at three                        |     |

|      | different levels of trapped charge densities                                               | 157 |

# **Chapter 1**

# Introduction

This work investigates, by means of a numerical simulation, the effects of interface-trapped charges in conventional bulk metal-oxide-semiconductor field-effect transistors (MOSFETs). In this introductory chapter, the motivation behind this study is presented starting with a brief overview of the variability issues and reliability concerns associated with progressive downscaling of contemporary MOSFETs. These mould the aim and specific objectives of this project, as presented in Section 1.2. Following this, an outline of this thesis and a description of the subsequent chapters are laid out.

## 1.1 Motivation

The phenomenal growth of the semiconductor industry is characterised by the remarkable increase of transistor count in integrated circuits, as epitomised by the well-known Moore's Law [1]. In 1971, the world's first commercially available microprocessor the Intel 4004 held 2300 transistors; by contrast a typical microprocessor embedded in today's personal computers is a large scale integration of hundreds of millions of transistors. This was partly accomplished by downscaling (miniaturisation) of the transistors, which simultaneously increases component density and switching speed, enabling overall improvement of computational complexity, memory capacity and processing speed of the chip. However as scaling enters the nanometer scale, fundamental physical limits start to affect the operational integrity of bulk MOSFETs [2].

Among the critical issues affecting contemporary MOSFETs are intrinsic variability [3] and performance degradation due to stress [4]. Intrinsic variability refers to the stochastic dispersion of the electrical characteristics, caused by atomic scale variation in the structures of the otherwise macroscopically identical transistors. As transistor features are shrunk into the deca-nanometer scale, these microscopic non-uniformities start to exert an increasingly significant impact on the device behaviour. This variation is termed intrinsic because it arises from the microscopic granularity of matter, which cannot be eliminated by tightening the manufacturing process controls [5]. Well known sources of intrinsic variability in bulk MOSFETs are random dopants [6, 7], gate line edge roughness [8, 9], local oxide thickness variation [10] and metal gate granularity [11, 12]. It has been reported that random dopants alone account for approximately 60% of the threshold voltage variation measured from the fairly recent 45 nm transistors [5]. Intrinsic variability already affects SRAM design [13], and causes timing problems in logic circuits [14].

The typical operating environment of modern integrated circuits also exerts a tremendous amount of stress on the transistors. Over time, this condition leads to the device performance degradation which will eventually compromise circuit reliability. A general type of degradation is the defect formation occurring at the Si/SiO<sub>2</sub> interface, or deeper in the gate oxide layer, known as Bias Temperature Instability (BTI) [15-17]. This microscopic structural damage acts as a source of trapping centres for charge carriers in the channel, causing changes in the transistor's electrical parameters which shortens its functional lifespan. Experimental [18, 19] and 3D simulation studies [20, 21] have shown that the trapping of just a *single* charge carrier in a transistor of short channel length is sufficient to cause drastic changes in the device's electrical behaviour. This effect is, in essence, analogous to intrinsic variability where atomic scale phenomena exert a dramatic impact on the device's electrical characteristics. Anomalously large threshold voltage shifts of 0.5 V have been measured in 65 nm flash memory [22]. This imposes a critical challenge to the

reliability of memory, which relies on stable device threshold voltage for read and write operations [23].

In the past, relatively large, micron-scale bulk MOSFETs could reasonably be considered as identical in terms of electrical characteristics. Similarly, the application of a given stress would result in an identical magnitude of degradation across all the devices in a given design. With the gradual downscaling of transistor dimensions, performance variations between devices start to appear due to the various sources of variability. Consequently, the application of a fixed stress on such devices results in a distribution of the parameter shifts instead of identical and uniform parameters drift. Understanding this effect is crucial in order to correctly estimate the performance and reliability of transistors, and of the systems comprising them.

## 1.2 Aims and Objectives

The general aim of this Ph.D is to study the effects of interface-trapped charges in the presence of a dominant source of intrinsic variability. The specific objectives of this work are to:

- Investigate the electrostatic effects of single-charge trapping and the generic dependencies of the resulting magnitudes of current reduction and threshold voltage shift;

- Identify the ways in which the random dopants influence the statistical distribution of the magnitudes of current reduction and threshold voltage shift;

- Analyse the distribution of electrical parametric shifts arising from an ensemble of MOSFETs with random-dopants-induced variability, each of which is subjected to a single trapped charge at the Si/SiO<sub>2</sub> interface;

- Study the impact of progressive increase of interface-trapped charges on the

distribution of transistor electrical parameters;

Encapsulate the effects of interface charge-trapping in the presence of randomdopants-induced variability in device compact models, and investigate the impact of progressive BTI degradation on inverter circuit delay using the extracted compact models.

#### 1.3 Thesis Outline

This thesis is organised in the following structure — Chapter 2 details the essential background on the intrinsic variability of contemporary bulk MOSFETs. The origins of variability are described in more detail and the forms of variability classified. This is followed by a review of the degradation mechanisms, specifically related to charge-trapping, affecting current and future generations of transistors.

Chapter 3 discusses the simulation methodology employed in this study. It starts with a general description of well-established simulation approaches employed for the simulation of semiconductor devices. These are described in tandem with the relative advantages and drawbacks associated with each method, with respect to the objectives of this work. This is followed by an overview of the Glasgow 'atomistic' device simulator used in this research. The techniques used to implement each intrinsic variability source in the simulator are explained, along with the measures incorporated to ensure reliable solutions. This chapter concludes with a description of the testbed device henceforth simulated in this study.

Chapter 4 examines the impact of random dopants on the magnitudes of electrical parametric shift induced by interface-trapped charges. This chapter begins with a series of systematic simulations of single-charge trapping event, where the generic dependencies of the resulting magnitudes of current change are first identified.

Following this, we analyse the distribution of parametric shifts in a simulation sample of 1000 transistors in the presence of random-dopants-induced variability, each of which is subjected to single-charge trapping.

In Chapter 5, Positive Bias Temperature Instability (PBTI) degradation is simulated on statistical samples of 1000 transistors, by progressively increasing the density of interface-trapped charges. The effect of increasing trap density on the threshold voltage distribution of the transistors in the sample is analysed and compared against experimentally observed distributions and theoretical predictions.

Chapter 6, which is entitled "Integrating the Effects of Trapped Charges into Compact Models", focuses on the framework to incorporate the information gained from the physical simulations into device compact models, and thus make the information available to circuit designers. This chapter explains the compact model parameter extraction strategy, and evaluates the accuracy of the resulting compact models. Subsequently, the extracted compact models are also used in inverter circuit simulations, whereby the resulting delay degradation due to progressive increase of trapped charges is analysed.

Finally in Chapter 7, the findings of this thesis are summarised and restated. The direction of possible future work is also proposed.

#### **Chapter References**

- 1. G. E. Moore, "Progress in digital integrated electronics", *IEDM Technical Digest*, pp. 11-13, 1975.

- 2. R. W. Keyes, "Fundamental limits of silicon technology", *Proceedings of IEEE*, vol.89, no.3, pp. 227-239, 2001.

- 3. G. Declerck, "A look into the future of nanoelectronics", *Symposium on VLSI Technology Digest of Technical Papers*, pp. 6-10, 2005.

4. D. K. Schroder and J. A. Babcock, "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing",

Journal of Applied Physics, vol.94, no.1, pp. 1-18, 2003.

- 5. K. J. Kuhn, "Reducing variation in advanced logic technologies: Approaches to process and design for manufacturability of nanoscale CMOS.", *IEDM Technical Digest*, pp. 471-474, 2007.

- 6. R. W. Keyes, "Effect of randomness in the distribution of impurity ions on FET thresholds in integrated electronics", *IEEE Journal of Solid-State Circuits*, vol.10, no.4, pp. 245-247, 1975.

- 7. P. A. Stolk and D. B. M. Klaasen, "The effect of statistical dopant fluctuations on MOS device performance", *IEDM Technical Digest*, pp. 627-630, 1996.

- 8. M. Yoshizawa and S. Moriya, "Resolution limiting mechanism in electron beam lithography.", *Electronics Letters*, vol.36, pp. 90-91, 2000.

- 9. A. Asenov, "Intrinsic parameter fluctuations in decananometre MOSFETs introduced by gate line edge roughness.", *IEEE Transactions on Electron Devices*, vol.50, no.5, pp. 1254-1260, 2003.

- 10. T. Ohmi, K. Kotani, A. Teramoto, and M. Miyashita, "Dependence of electron channel mobility on Si-SiO2 interface microroughness.", *IEEE Electron Device Letters*, vol.12, no.12, pp. 652-654, 1991.

- 11. H. Dadgour, V. De, and K. Banerjee, "Statistical modeling of metal-gate work-function variability in emerging device technologies and implications for circuit design.", *Proc. of ICCAD*, 2008.

- 12. K. Ohmori, T. Matsuki, D. Ishikawa, T. Morooka, T. Aminaka, Y. Sugita, T. Chikyow, K. Shiraishi, Y. Nara, and K. Yamada, "Impact of additional factors in threshold voltage variability of metal/high-k gate stacks and its reduction by con-trolling crystalline structure and grain size in the metal gates.", *IEDM Technical Digest*, pp. 409–412, 2008.

- 13. B. Cheng, S. Roy, F. Adamu-Lema, and A.Asenov, "Impact of intrinsic parameter fluctuations in decanano MOSFETs on yield and functionality of SRAM cells.", *Solid-State Electronics*, vol.49, pp. 740-746, 2004.

- 14. N. A. Kamsani, B. Cheng, and et. al, "Statistical circuit simulation with supply voltage scaling in nanometer mosfet devices under the influence of random dopant fluctuations.", *FTFC*, 2008.

15. M. A. Alam, H. Kufluoglu, D. Varghese, and S. Mahapatra, "A comprehensive model for PMOS NBTI degradation: Recent progress.", *Microelectronics Reliability*, vol.47, pp. 853-862, 2007.

- 16. J. G. Massey, "NBTI: What we know and what we need to know. A tutorial addressing the current understanding and challenges for the future.", *IIRW Final Report*, pp. 199-211, 2004.

- 17. V. Huard, M. Denais, and C. Parthasarathy, "NBTI degradation: From physical mechanisms to modelling.", *Microelectronics Reliability*, vol.46, pp. 1-23, 2006.

- 18. H. Kurata, K. Otsuga, A. Kotabe, and et al., "Random Telegraph Signal in flash memory: Its impact on scaling of multilevel flash memory beyond the 90-nm node", *IEEE Journal of Solid-State Circuits*, vol.42, no.6, pp. 1362-1369, 2007.

- 19. P. Fantini, A. Ghetti, A. Marinori, G. Ghidini, A. Visconti, and A. Marmiroli, "Giant random telegraph signals in nanoscale floating-gate devices", *IEEE Transactions on Electron Devices*, vol.28, no.12, pp. 1114-1116, 2007.

- 20. A. Asenov, R. Balasubramaniam, A. R. Brown, and J. H. Davies, "RTS amplitudes in decananometer MOSFETs: 3-D simulation study", *IEEE Transactions on Electron Devices*, vol.50, no.3, pp. 839-845, 2003.

- 21. N. Ashraf and D. Vasileska, "1/f noise: Threshold voltage and on-current fluctuations in 45 nm device technology due to charged random traps.", *Journal of Computational Electronics*, vol.published online: 23 Oct, 2010.

- 22. Y. Cai, Y. H. Song, W. H. Kwon, and et al., "The impact of Random Telegraph Signals on the threshold voltage variation of 65 nm multilevel NOR flash memory.", *Japanese Journal of Applied Physics*, vol.47, no.4, pp. 2733-2735, 2008.

- 23. N. Tega, H. Miki, M. Yamaoka, H. Kume, T. Mine, T. Ishida, Y. Mori, R. Yamada, and K. Torii, "Impact of threshold voltage fluctuation due to random telegraph noise on scaled-down SRAM", *Proc. IRPS*, pp. 541-546, 2008.

# **Chapter 2**

# **Background**

This chapter lays out the essential background regarding MOSFET intrinsic variability, and the device reliability concerns associated with charge-trapping degradation, with an emphasis on their inter-related effects on device electrical characteristics. The classification, origins and effects of variability are first discussed. Subsequently, the mechanism and effects of charge-trapping degradation are elaborated through a review of the related existing studies.

## 2.1 Intrinsic Variability

It is widely recognised that one of the critical challenges to further downscaling of contemporary bulk MOSFETs is the variability of the device electrical parameters [1, 2]. This is because the variation of electrical parameters caused by the various sources of variability increases in every new technology generation, adversely affecting circuit designs and yield [3, 4].

The MOSFET variability has systematic and random components [5], both of which co-exist within a die. Systematic variability is normally related to the nature of the physics of the manufacturing processes and follows well understood trends. Examples of systematic variation are the optical proximity effect and layout mediated strain. The optical proximity effect is caused by light diffraction during the photolithography process which leads to structural irregularities, such as a printed line being narrower or wider than intended in the design. Such diffraction phenomena are unavoidable

because the patterned feature length in contemporary CMOS technologies is significantly smaller than the wavelength of the light which is used to print it. For example, the feature length of the 45 nm technology node is approximately 5.5 times smaller than the 193 nm wavelength of the light which prints it. The resulting layout distortions, if left uncorrected, may significantly alter the electrical characteristics of the patterned elements compared with their designed values. Strain engineering, which was first introduced in the 90 nm technology node to boost carrier mobility, is now an essential component of CMOS technology. However, the magnitude of the strain is strongly dependent on layout – such as the spacing between transistors and the distance to the nearest shallow trench isolation. The non-uniform stress distribution in transistors of different spatial arrangements on the die consequently results in variation of carrier mobility and hence drive current. Although systematic variability, as illustrated in the examples above, is critically important, it is deterministic in nature and therefore falls under certain measures of control. For example, layout distortions anticipated during the photolithography process can be largely eliminated by optical proximity correction [6], while the impact of layoutinduced strain variations can be accurately predicted and factored into the design stage, allowing optimised design margins [7, 8].

Random variability, on the other hand, is truly stochastic and varies from transistor to transistor. Unlike in the case of systematic variation whose impact can be predicted and modelled down to the level of individual transistor characteristics, in the case of random variability only the collective statistical behaviour of an ensemble of transistors can be simulated or characterised. The statistical nature of random variability is linked to the fundamental atomicity of matter and granularity of materials, which will occur even under ideal processing conditions. In that sense, the sources of random variability are *intrinsic* to the device and technology. Furthermore, random variability is exacerbated by transistor scaling, which widens the design margins needed to ensure circuit functionality. Transistor scaling into the deca-

Figure 2.1: Illustration of some key sources of intrinsic variability in conventional bulk MOSFETs.

nanometer regime has effectively decreased the ratio of the device dimensions with respect to the fundamental atomic scale. The granularity of matter at this extremely small spatial scales starts to become more obvious, appearing as non-uniform and abrupt changes in device structure. More importantly, these atomic-scale non-uniformities also start to affect the device electrical characteristics to a significant degree.

Figure 2.1 illustrates the well documented sources of intrinsic variability in conventional bulk MOSFETs. The sources are gate line edge roughness, microscopic oxide thickness variations, metal gate granularity and random dopant fluctuations, all of which causes device-to-device variation of electrical parameters. Gate line edge roughness is caused by molecular scale variation in the boundaries of the photoresist

which is transferred onto the patterned gate edge during fabrication process [9], causing the channel length in a transistor to locally deviate from an ideal uniformity throughout the width of the device. Microscopic oxide thickness fluctuations refers to the atomic scale roughness of the channel-oxide interface, which lowers the channel carrier mobility [10] and increases statistical gate leakage [11]. The random orientation of crystal grains in metal gates gives rise to local variations in the metal gate workfunction, which leads to threshold voltage variability [12, 13]. Random dopant fluctuations is the phenomena of device-to-device variation in the number and microscopic spatial location of individual impurity atoms, which cannot be controlled to atomic precision during the fabrication process. Random dopant fluctuations are currently the primary source of variability in contemporary bulk MOSFETs, contributing up to 60% and 65% of the threshold voltage variability measured in 45 nm and 65 nm technology generation transistors [5]. This thesis investigates the impact of interface-trapped charges in the presence of this dominant source of intrinsic random variability.

#### 2.1.1 Random Dopants

The effects of random dopant fluctuations on threshold voltage variability was first predicted in the 1970's [14, 15]. It has since been experimentally confirmed in a number of studies [16, 17], and extensively studied analytically [18, 19], and by 2D [20] and 3D [21-25] simulations. Figure 2.2 reports the decreasing average number of dopants in the channel region as the CMOS technology advances. In the past, transistor features were micron-scale sized and the dopant count in the channel region averaged in the thousands. As transistor dimensions are downscaled into the decananometer regime, device behaviour is determined by fewer and fewer impurity atoms, and consequently becomes increasingly sensitive to their exact number and spatial position in the device active region. The effect of the variation in the number of dopants on the threshold voltage can be understood from the following basic formulation of MOSFET threshold voltage:

Figure 2.2: Average number of dopant atoms in the channel expressed as a function of advancement of technology node. After [87].

$$V_T = V_{fb} + 2\psi_B + \frac{\sqrt{4\epsilon_{Si}qN_a\psi_B}}{C_{OX}} \tag{2.1}$$

where  $V_{fb}$  is the flat-band voltage,  $\psi_B$  is the difference between Fermi level and intrinsic Fermi level,  $\varepsilon_{Si}$  is silicon permittivity and  $C_{OX}$  is the oxide capacitance. The square root term represents the depletion charge which explicitly depends on the nominal substrate doping  $N_A$ , the variation of which, leads to a first order estimation of  $V_T$  variation. Transistor scaling has effectively reduced the number of dopants to such a level that the stochastic spread in the dopant distribution becomes increasingly significant. By way of a numerical example, based on the data in Figure 2.2, there were on average  $10^5$  dopant atoms in the channel of 10 micron transistors. Assuming that the actual dopants count from device to device follows a Poisson distribution, the standard deviation ( $\sqrt{10^5}$ ) represents a tiny percentage of  $\sim 0.3\%$  of the nominal doping. By comparison, there are around 100 dopant atoms in the sub-0.1 micron transistors. The standard deviation of the dopants count is then  $\sim \sqrt{100}$ , which constitutes around 10% of the nominal doping — clearly a significantly larger

#### fluctuation.

The above description does not provide a full picture of random dopants effects as it does not take into account the random spatial positions of the impurity atoms. The fabrication process of modern bulk MOSFETs involves several ion implantation steps to introduce doping impurities into the device [26]. During implantation, the dopants are beamed into the semiconductor with high energy, and randomly scatter many times before coming to a rest. The semiconductor is then annealed to activate the impurities, during which the dopants diffuse further and replace the silicon atoms in the crystal lattice. Due to the random scattering events during implantation and diffusion during annealing, the final positions of individual dopant atoms vary from one device to another. Each transistor is essentially microscopically unique even though they may share a macroscopically identical doping design and structural layout.

3D simulation studies have shown that threshold threshold voltage variability can occur due to the spatial variation of the dopant atoms, even in the chance cases when the number of dopant atoms are identical between two transistors [25]. For example, random dopants are shown to exert the greatest impact on the threshold voltage if they happen to be located in the middle of the channel where the maximum potential barrier separating the source and drain lies, and/or close to the oxide interface where inversion takes place [23]. The spatial distribution of dopants has also been shown to significantly influence transport properties in the inversion layer, causing transconductance variations and the spreading out of drive currents at high drain bias [27].

Random dopants introduce inhomogeneity into the electrostatic potential landscape of the transistor channel [28]. As a result, within any given transistor, local portions of the channel will turn on before others and there will exist random variations of local carrier concentration as the current percolates between the peaks in the electrostatic potential centred on discrete ionised impurities. None of these effects are accounted for in the conventional simulation approach where the MOSFET is modelled assuming an ideal continuous distribution of charge.

Intrinsic variability inevitably requires an adoption of a new paradigm in the simulation of ultra-scaled devices, in two major aspects: Firstly, the simulated device must reflect the real-world intrinsic variations in its structure, because these exert a significant degree of influence on the electrical metrics. Secondly, intrinsic variability necessitates that the simulations are done on a statistical scale because it is no longer sufficient to only simulate a single device. A statistical ensemble of microscopically unique transistors has to be simulated to describe the statistical behaviour of the electrical characteristics. In addition, intrinsic sources of variability must also be considered when assessing device reliability, because the transistors may not degrade identically under the application of a given stress.

## 2.2 Charge-Trapping

The silicon atom has four valence electrons and therefore requires four bonds to form a saturated valence shell. In the bulk crystalline structure, each silicon atom establishes bonds with its four neighbouring atoms, leaving no unpaired bond. At the bare surface however, silicon atoms are missing therefore there are unsatisfied, electrically active dangling bonds resulting in defect states in the band gap known as interface traps, as illustrated in Figure 2.3. After thermal oxidation, most of the traps are paired with oxygen atoms forming the SiO<sub>2</sub> layer. Further improvement of the interface quality is done through passivation with hydrogen, forming the inert Si-H bonds [29]. With this treatment, the interface traps density is reduced to  $10^{10}$  cm<sup>-2</sup> or below [30].

Figure 2.3: (a) Unpaired valence electrons at the silicon surface form electrically active interface traps. (b) Thermal oxidation pairs most of the silicon surface atoms with oxygen atoms, thus reducing the number of interface traps. (c) After annealing with hydrogen ambient the amount of interface traps is further reduced.

#### 2.2.1 Random Telegraph Signal

The remaining traps located at the interface or in the oxide can capture and re-emit some of the charge carriers flowing in the channel connecting the source and drain. When a trap captures a carrier, the drain current is affected because the number of available carriers for conduction changes, and the charged trap centre becomes a Coulomb scattering centre, affecting carrier mobility in the channel. The erratic trapping and detrapping of carriers at or near the interface defects is widely accepted to be responsible for the so-called Random Telegraph Signal noise [31-33].

Extensive studies of RTS are spurred by the increase of electrical noise in MOSFETs as the device is downscaled. For the case of an n-channel MOSFET, the random capture and emission of a single electron by an individual interface trap results in discrete switching between low and high current levels. As illustrated in Figure 2.4, RTS is characterised by the capture  $(t_c)$  and emission  $(t_e)$  times, and the amplitude of

Figure 2.4: *Top*) Typical plot of drain current fluctuations due to RTS, after [34]. *Bottom*) Definition of threshold voltage shift caused by RTS.

current and threshold voltage change. The threshold voltage shift caused by a single interface-trapped charge can be expressed to first order as [34-36]:

$$\Delta V_T = \frac{q}{C_{OX}WL} \tag{2.2}$$

where q is elementary charge,  $C_{\rm OX}$  is capacitance of gate dielectric per unit area and W and L are the channel width and length respectively. The corresponding amplitude of drain current change due to this electrostatic effect can then be expressed as  $\Delta I_{\rm D} = -g_{\rm m}$   $\Delta V_{\rm T}$ , where  $g_{\rm m}$  is the transconductance. RTS magnitude increases with scaling due to the inverse relationship with channel area [37, 38]. Already RTS amplitudes as high as

60% have been reported in deca-nanometer channel width devices [37]. RTS is particularly worrisome in memory circuits such as SRAM and flash memory where large magnitudes of RTS are a major concern due to the induced threshold voltage instabilities which compromise the reliability of read and write operations [39-41]. Other experimentally measured RTS amplitudes are widely scattered even for a given device design [38, 42], and sometimes amplitudes anomalously larger than estimated by the conventional formula described above have been reported [43-45]. These socalled 'giant' RTS amplitudes have been attributed to several factors. It was suggested, for instance, that the mobility fluctuations caused by Coulomb scattering by the trapped charge could amplify the RTS amplitudes [33, 36, 46]. Simultaneous trapping of multiple discrete charges has also been suggested as a possible mechanism responsible for anomalously large RTS magnitudes, as evidenced by the experimentally observed multiple discrete levels of current switching [41]. Inhomogeneous channel conduction was also thought to give rise to the statistical spreading of RTS amplitudes, where the channel non-uniformity is attributed to the potential fluctuations from oxide thickness variation [36] and fixed oxide charges [47].

A more recent proposition, in line with increased understanding of MOSFET intrinsic variability, is that the random dopants are responsible for the statistical spread and anomalously large RTS amplitudes. 3D simulation studies in [35, 44, 48-51] demonstrate that unlucky charge trapping in critical current paths of a random-dopants-induced inhomogeneous channel can result in large RTS amplitudes, much larger than predicted by the simple 1D approximation of Equation 2.2. However, with the exception of the more recent studies in [49], the previous authors have focused on the impact of single stray charges and did not consider the statistical distribution for a number of charged defect states in a single transistor. Such simplification may underestimate the distribution of current and threshold voltage changes recorded from the simulated ensemble of devices.

## 2.2.2 Bias Temperature Instability (BTI)

#### 2.2.2.1 Causes and Effects of BTI

BTI is a type of MOSFET degradation phenomena which is generally attributed to interface trap creation at the oxide interface [52, 53]. During fabrication, the transistors are annealed in ambient hydrogen to passivate the silicon dangling bonds, thus reducing the interface trap density. However, over the device operating lifetime these passivated bonds are gradually broken, causing performance degradation. With the downscaling of transistors, BTI has emerged as a significant reliability concern for digital and analog circuits in CMOS technology. In particular, the aggressively scaled oxide thickness which leads to higher oxide field, in conjunction with elevated operating temperatures (due to ambient dissipation from increasingly dense circuits), are found to accelerate the bond-breaking at the oxide interface [54, 55]. Typical stress temperatures lie in the range of 100 - 250°C, with oxide electric fields typically below 6 MV/cm. These are not only typical conditions encountered during burn in, but are also approached during routine operation of high performance ICs.

BTI degradation can be observed in both p- and n-channel MOSFETs. For a p-channel MOSFET, the degradation is found most profound when the device is stressed with negative gate voltages [52] causing the so-called Negative Bias Temperature Instability (NBTI). This stress corresponds to the routine operating condition of a CMOS inverter when the input voltage is at a low state, as illustrated in Figure 2.5. NBTI in pMOSFETs results in a build-up of positive charges at the interface or in the oxide layer, leading to performance reduction. With the introduction of high-*k* gate dielectrics in the 45 nm process technology, the Positive Bias Temperature Instability (PBTI) associated with electron trapping in n-channel MOSFETs started to emerge as a new reliability threat [56, 57]. The use of high-*k*/metal gates have proven to be an effective measure to suppress gate leakage and boost transistor performance [58], however the dielectric material exhibits significant charge-trapping due to its higher

Figure 2.5: (*Left*) Circuit schematic of a CMOS inverter driving a capacitive load. (*Right*) Timing diagram illustrating degradation modes during CMOS inverter operation.

trap density [59, 60].

It is helpful to review some basic MOSFET concepts in order to understand the effects of BTI. The MOSFET threshold voltage is given by:

$$V_T = V_{fb} + 2\psi_B + \frac{\sqrt{4\epsilon_{Si}qN_a\psi_B}}{C_{OX}} \tag{2.1}$$

where the flat-band voltage,  $V_{fb}$ , is given by:

$$V_{fb} = \phi_{ms} - \left(\frac{Q_f + Q_{it}}{C_{OX}}\right) \tag{2.3}$$

where  $\Phi_{ms}$  is the workfunction difference between the gate metal and the semiconductor,  $Q_f$  is the oxide fixed charge density and  $Q_{it}$  is the interface trapped charge density. From these equations, it can be seen that electron trapping in nMOSFET PBTI increases the threshold voltage  $V_T$  which leads to positive shift of threshold voltage. On the other hand, positively charged defect states in the case of pMOSFET NBTI cause negative threshold voltage shift. In both cases, the increase in the absolute value of  $V_T$  reduces the drain current, as indicated by the following basic

formulation of MOSFET saturation current:

$$I_D = (\frac{W}{2L})\mu_{eff}C_{ox}(V_G - V_T)^2$$

(2.4)

where  $V_G$  is the gate voltage and all other parameters have the same previously mentioned meanings. The effective carrier mobility in the channel,  $\mu_{eff}$ , is also affected by the interface traps via additional surface-related scattering [53] which also contributes to the drain current reduction. This performance degradation consequently reduces circuit switching speed (because lower current takes longer capacitor charging time) [61] and may eventually result in operational failure [62].

## 2.2.2.2 Time-Dependence Model of BTI

The Reaction-Diffusion (RD) model is the most prevalent description of NBTI [55, 63, 64], which was first proposed by Jeppson and Svensson in 1977 [65]. The model is capable of reproducing the stress time dependence of the device degradation due to NBTI over a wide range of measurements. There are various refinements to the standard RD model [66, 67] but only the elementary aspects of the basic RD model will be described here. The model attributes the degradation to a combination of two effects as illustrated in Figure 2.6. During the initial reaction phase, the passivated silicon-hydrogen bonds are dissociated with a linear dependence on stressing time generating interface traps and releasing hydrogen according to the model:

$$Si_3 \equiv SiH \rightarrow Si_3 \equiv Si^{\bullet} + H$$

(2.5)

where  $Si_3\equiv SiH$  is a hydrogen terminated silicon bonds at the interface and  $Si_{\bullet}$  is an unpaired silicon dangling bond. In the subsequent diffusion phase, the hydrogen diffuses away from the interface into the dielectric during which the trap generation exhibits a fractional power-law stress time dependence  $t^n$ , where n is frequently reported as 0.25. These different phases can be seen in Figure 2.6 as the change in rate

Figure 2.6: (*Top*) Illustration of the RD model: passivated Si-H bonds at the interface are broken and the hydrogen diffuses away into the dielectric, leaving behind electrically active interface traps. (*Bottom*) Interface trap generation calculated with the analytical RD model, showing the reaction and diffusion regimes of NBTI, after [63].