Feng, Hong (2011) *Impact of atomistic device variability on analogue circuit design*.

PhD thesis.

http://theses.gla.ac.uk/3074/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# Impact of Atomistic Device Variability on Analogue Circuit Design

## **Feng Hong**

Submitted in fulfilment of the requirements to award the degree of Doctor of Philosophy in Electronics and Electrical Engineering

**School of Engineering**

**University of Glasgow**

For Lingting and My Parents

## **Abstract**

Scaling of complementary metal-oxide-semiconductor (CMOS) technology has benefited the semiconductor industry for almost half a century. For CMOS devices with a physical gate-length in the sub-100 nm range, extreme device variability is introduced and has become a major stumbling block for next generation analogue circuit design. Both opportunities and challenges have therefore confronted analogue circuit designers. Small geometry device can enable high-speed analogue circuit designs, such as data conversion interfaces that can work in the radio frequency range. These designs can be co-integrated with digital systems to achieve low cost, high-performance, single-chip solutions that could only be achieved using multi-chip solutions in the past. However, analogue circuit designs are extremely vulnerable to device mismatch, since a large number of symmetric transistor pairs and circuit cells are required. The increase in device variability from sub-100 nm processes has therefore significantly reduced the production yield of the conventional designs.

Mismatch models have been developed to analytically evaluate the magnitude of random variations. Based on measurements from custom designed test structures, the statistics of process variation can be estimated using design related parameters. However, existing models can no longer accurately estimate the magnitude of mismatch for sub-100 nm "atomistic" devices, since short-channel effects have become important. In this thesis, a new mismatch model for small geometry devices will be proposed to address this problem.

Based on knowledge of the matching performance obtained from the mismatch model, design solutions are desired at different design levels for a variety of circuit topologies. In this thesis, transistor level compensation solutions have been investigated and closed-loop compensation circuits have been proposed. At circuit level, a latch-based comparator has been used to develop a compensation solution because this type of comparator is extremely sensitive to the device mismatch. These comparators are also used as the fundamental building block for the analogue-to-digital converters (ADC). The proposed comparator compensation scheme is used to improve the performance of a high-speed flash ADC.

## **Acknowledgments**

First of all, I would like to deeply express my great gratitude to Professor David R. S. Cumming for his support, guidance and encouragement throughout my PhD studies. His thoughtful comments and suggestions inspired me in extending my knowledge and skills. I would also like to thank my second supervisor Dr. Scott Roy for his useful feedback. I would say many thanks to Dr. Binjie Cheng for his insight discussions and comments. I would like to thank Dr. Sonia Caldwell for her kind advice and useful help during her stay in the department and during my painful job-hunting time. I would like to thank Dr. Tim Drysdale for his suggestions on how to write a good thesis, and how to prepare for the viva.

I would like to thank Dr. James Grant for his time and patient on reviewing my entire Thesis. I will not forget Pete Shield who also spent a lot of time in proofreading my papers and thesis. Furthermore, I would like to thank all the members of the MST for their help during my stay in the group. Shimul and I have co-authored four papers. Touquer and I had lots of great discussions on Variability.

Last but not least, I would thank my wife Tingting and my parents. Tingting quitted her job in China 3 year ago and came to UK in helping me to get though my PhD. I would also like to take this opportunity to say, "I love you" to my dear parents for their endless love, support and encouragement. My mum always influences on me with her optimistic attitude. The encouragement and understand from my dad always help me to get through the difficult times.

## **Publications**

## **Conference Papers:**

- [1] F. Hong, B. Cheng and D. Cumming, "Mismatch Modelling for a 35 nm Differential Amplifier with Impact of Variability", IEEE Proc. ULIS 2010, March. Glasgow, U.K. pp. 161-164

- [2] F. Hong, D. Cumming, "Source Compensation Scheme for Reducing Impact of Variability on Differential Amplifier in 35 nm CMOS", IEEE Proc. ICECS Dec. 2010, Athens, Greece, pp. 344-347

- [3] F. Hong, B. Cheng, S. Roy and D. Cumming, "An Analytical Mismatch Model for NanoCMOS Device Under the Impact of Intrinsic Device Variability", IEEE ISCAS May 2011, Brazil, pp. 2257-2260.

- [4] S. Saha, J. Grant, Y. Ma, A. Kalid, **F.Hong** and D. Cumming, "Terahertz Frequency Domain Spectroscopy for Polar Alcohol", Proc. IEEE IRMMW-THz, Oct. 2011, Houston Texas, U.S.

- [5] S. Saha, J.Grant, Y. Ma, A. Kalid, F. Hong and D. Cumming, "Frequency Domain Spectroscopy of DNA at Terahertz Frequency", Proceeding of Bioengineering, Sept. 2011, London, U.K.

## **Journal Papers:**

- [1] F. Hong and D. Cumming "A Novel Offset Compensation Scheme for Latch-type Comparator in 35 nm CMOS", IET Letter 2011 (Submitted)

- [2] S. Saha, J. Grant, Y. Ma, A. Kalid, **F. Hong** and D. Cumming, "Method for Vector Characterisation of Polar Liquids Using Frequency-Domain Spectroscopy", Journal of Optics Letter, Vol. 36, Iss. 17, pp. 3329-3331, 2011

- [3] S.Saha, J. Grant, Y. Ma, A. Kalid, F. Hong and D. Cumming, "Terahertz Frequency-domain Spectroscopy Method for Vector Characterization of Liquid Using an Artificial Dielectric", IEEE Trans. of Terahertz Science and Technology. (Accepted)

# **Table of Contents**

| Abstract                         |                   |

|----------------------------------|-------------------|

| Acknowledgments                  | I                 |

| Publications                     | II                |

| Table of Contents                | IV                |

| List of Figures                  | VI                |

| List of Tables                   | XI                |

| Glossary of Symbols              | XII               |

| Chapter 1 Introduction           |                   |

| 1.1 Motivation                   |                   |

| 1.2 Aims and Objectives          | :                 |

| 1.3 Thesis Outline               |                   |

| Chapter 2 Literature Review      | !                 |

| 2.1 Introduction                 |                   |

| 2.2 Origins of Variability       | •                 |

| 2.2.1 Systematic Variations      | •                 |

| 2.2.2 Random Variations          | 10                |

| 2.3 Modelling of Variability     | 14                |

| 2.3.1 Test Structure             | 1                 |

| 2.3.2 Device Mismatch Modellin   | ng 18             |

| 2.3.3 Circuit Performance & Yie  | eld Estimation 22 |

| 2.4 Design for Variability       | 24                |

| 2.4.1 Transistor Level Compens   | sation 2.         |

| 2.4.2 Circuit Level Compensation | on 2º             |

| 25 Summary                       | 3                 |

| Chapt | er 3 | Mismatch Modelling for Atomistic Device                                     | 33 |

|-------|------|-----------------------------------------------------------------------------|----|

| 3.1   | Imp  | pact of Variability at Transistor Level                                     | 34 |

| 3     | .1.1 | Impact of Mismatch on Nominally Identical Transistors                       | 36 |

| 3     | .1.2 | Monte Carlo Simulation Methodology                                          | 39 |

| 3.2   | Sho  | rt-Channel Device Mismatch Model                                            | 41 |

| 3     | .2.1 | Saturation Regime                                                           | 41 |

| 3     | .2.2 | Triode Regime                                                               | 44 |

| 3     | .2.3 | Drain Current Decrease Due to Mobility Degradation                          | 45 |

| 3     | .2.4 | Device Characterisation                                                     | 48 |

| 3     | .2.5 | Simulation Results                                                          | 51 |

| 3.3   | Lon  | g-Channel Device Mismatch Model                                             | 53 |

| 3     | .3.1 | Saturation Regime                                                           | 53 |

| 3     | .3.2 | Triode Regime                                                               | 54 |

| 3     | .3.3 | Device Characterisation                                                     | 55 |

| 3     | .3.4 | Simulation Results                                                          | 56 |

| 3.4   | A C  | ase Study: Modelling the Input Offset Voltage of A Simple Differential Pair | 58 |

| 3     | .4.1 | Input Referred Offset Voltage Estimation                                    | 58 |

| 3     | .4.2 | Simulation Verification                                                     | 61 |

| 3.5   | Sun  | nmary                                                                       | 63 |

| Chapt | er 4 | Compensation Schemes at Transistor Level                                    | 64 |

| 4.1   | Tra  | nsistor Level Compensation                                                  | 65 |

| 4     | .1.1 | Principles of Transistor Level Compensation                                 | 66 |

| 4     | .1.2 | Finite Gain Errors                                                          | 71 |

| 4.2   | Вос  | ly-Biasing Compensation Scheme                                              | 72 |

| 4     | .2.1 | Differential Amplifier Using Body-Biasing                                   | 72 |

| 4     | .2.2 | Proposed Body Biasing Compensation Scheme                                   | 76 |

| 4     | .2.3 | Simulation Results and Conclusions                                          | 80 |

| 4.3   | Dra  | in Compensation Scheme                                                      | 83 |

| 4     | .3.1 | Principle of Drain Compensation Scheme                                      | 84 |

| 4     | .3.2 | Proposed Drain Compensation Scheme                                          | 85 |

| 4     | .3.3 | Simulation Results                                                          | 86 |

| 4.4   | Sou  | rce Compensation Scheme                                                     | 87 |

| 4     | .4.1 | Principle of Source Compensation Scheme                                     | 87 |

| 4     | .4.2 | Proposed Source Compensation Scheme                                         | 88 |

| 4     | .4.3 | Simulation Results                                                          | 89 |

| 4.5   | C    | nmary                                                                       | 90 |

| Chapter 5 |        | Impact of Variability on High-Speed Comparator Design                | 92  |

|-----------|--------|----------------------------------------------------------------------|-----|

| 5.1       | Hig    | h-Speed Comparator Design Using Atomistic Device                     | 93  |

| 5         | .1.1   | High-Speed Comparator Design                                         | 94  |

| 5         | .1.2   | Performance Evaluation                                               | 98  |

| 5.2       | Off:   | set Compensation Scheme for High-Speed Comparator Design             | 102 |

| 5         | .2.1   | Proposed Compensation Scheme                                         | 103 |

| 5         | .2.2   | Performance Evaluation                                               | 105 |

| 5.3       | Sur    | nmary                                                                | 108 |

| Chapt     | er 6   | Impact of Variability on High Performance ADC Design                 | 109 |

| 6.1       | Hig    | h-Speed Flash ADC Design                                             | 110 |

| 6         | .1.1   | Proposed High-Speed Flash ADC                                        | 112 |

| 6         | .1.2   | Static Characteristics Evaluation                                    | 114 |

| 6         | .1.3   | Dynamic Characteristics Evaluation                                   | 120 |

| 6.2       | Hig    | h-Speed Flash ADC with Comparator Compensation Scheme                | 123 |

| 6         | .2.1   | Comparator with Compensation Scheme                                  | 124 |

| 6         | .2.2   | Static Performance Evaluation                                        | 126 |

| 6         | .2.3   | Noise and Distortion Evaluation                                      | 129 |

| 6.3       | Sur    | nmary                                                                | 131 |

| Chapt     | er 7   | Conclusions and Future Work                                          | 132 |

| 7.1       | The    | esis Summary                                                         | 132 |

| 7.2       | Fut    | ure Work                                                             | 135 |

| Refer     | ences  | S                                                                    | 137 |

| Annai     | ıdiv . | A. How to calculate the signal-to-noise and distortion ratio (SINAD) | 144 |

# **List of Figures**

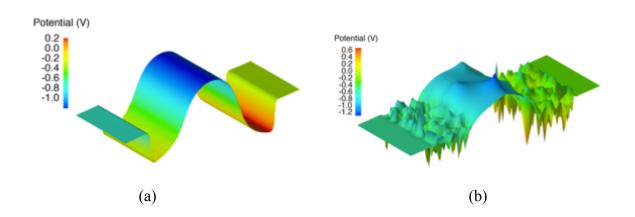

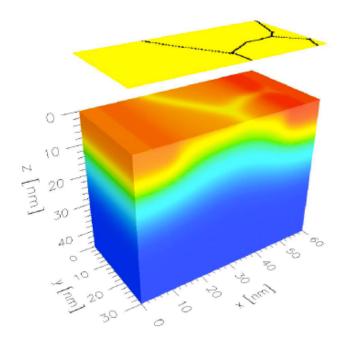

| FIGURE 2.1 POTENTIAL PROFILE OF (A) A CONTINUOUSLY DOPED DEVICE AND (B) AN ATOMISTIC DEVICE [74]11                     |

|------------------------------------------------------------------------------------------------------------------------|

| FIGURE 2.2 (A) TYPICAL ATOMISTIC SIMULATION DOMAIN AND DOPANT DISTRIBUTION USED IN THE SIMULATION OF A                 |

| $30 \times 50$ nm <sup>2</sup> n-channel MOSFET with oxide thickness $T_{ox} = 3$ nm, junction depth $x_j = 7$ nm, and |

| Channel acceptor concentration $N_A=5	imes10^{18}\mathrm{cm}^{-3}$ . (b) Potential distribution at threshold           |

| voltage obtained from the atomistic density gradient simulation of a $30\times50$ nm² MOSFET with                      |

| DESIGN PARAMETERS GIVEN IN (A) [70]11                                                                                  |

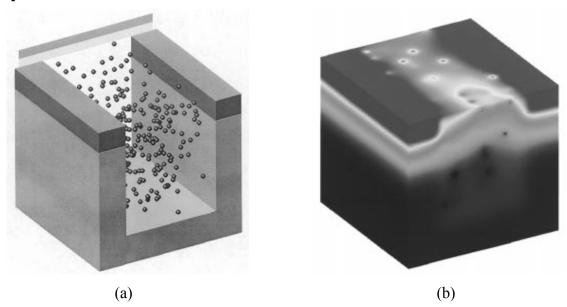

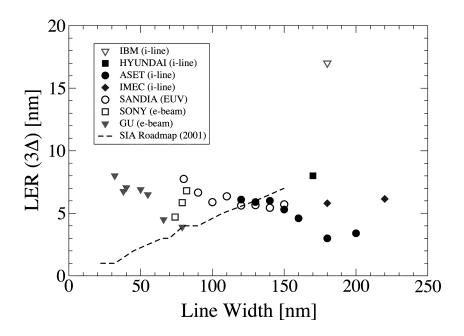

| FIGURE 2.3 ACTUAL DATA FROM VARIOUS ADVANCED LITHOGRAPHY PROCESSES REPORTED BY DIFFERENT LABS                          |

| SHOWING THAT LER DOES NOT SCALE WITH LINE WIDTH ACCORDING WITH THE ROADMAP REQUIREMENTS [15].                          |

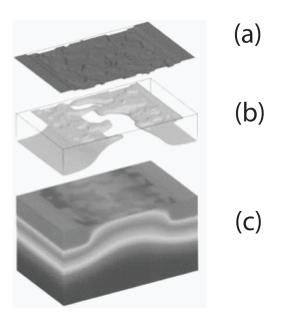

| Figure 2.4 (a) Typical profile of the random Si/SiO $_2$ interface in a $30 \times 30$ nm $^2$ MOSFET, followed by (b) |

| AN EQUICONCENTRATION CONTOUR OBTAINED FROM DENSITY GRADIENT SIMULATION, AND (C) THE POTENTIAL                          |

| DISTRIBUTION [68]13                                                                                                    |

| Figure 2.5 Electrostatic potential in a $30 \times 30 \text{ nm}^2 \text{ MOSFET}$ showing the impact on the channel   |

| POTENTIAL OF FERMI LEVEL PINNING AT THE POLYSILICON GRAIN BOUNDARIES. THE LOCATION OF THE GRAIN                        |

| BOUNDARIES ARE SHOWN IN THE PLANE ABOVE THE DEVICE [69]14                                                              |

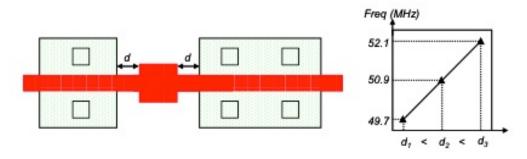

| FIGURE 2.6 MEASURED DEPENDENCE OF MEAN RING OSCILLATOR FREQUENCY ON POLYSILICON CONTACT LANDING PAD                    |

| TO THE DIFFUSION REGION SPACING [57]15                                                                                 |

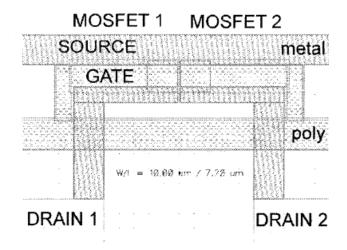

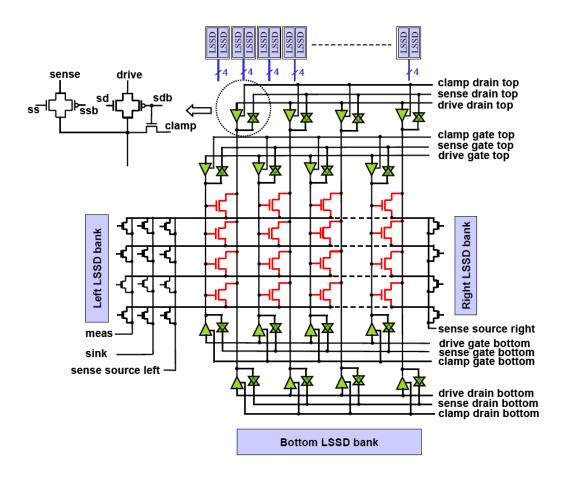

| FIGURE 2.7 LAYOUT OF TEST STRUCTURE [85]                                                                               |

| Figure 2.8 Device array for characterizing random variations [37]17                                                    |

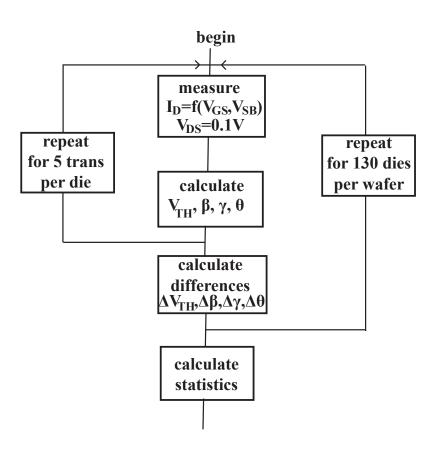

| FIGURE 2.9 RANDOM VARIATION EVALUATION PROCEDURE [30].                                                                 |

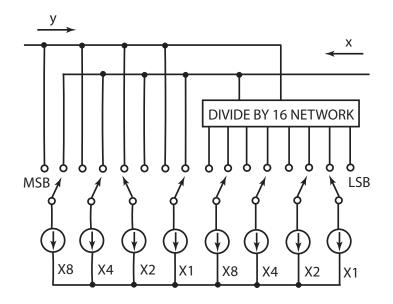

| FIGURE 2.10 SCHEMATIC OF A MULTIPLE CURRENT-SOURCE DAC [29]                                                            |

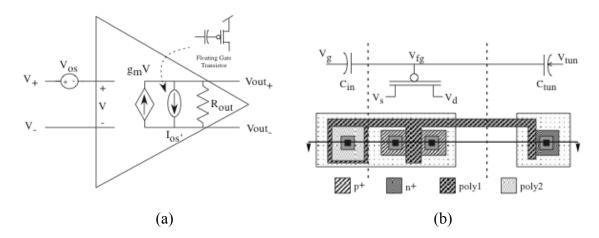

| FIGURE 2.11 (A) OFFSET CANCELLATION MACROMODEL: OFFSET VOLTAGE OF THE AMPLIFIER IS COMPENSATED BY                      |

| PROGRAMMING AN OFFSET CURRENT $I_{OS}$ . (B) CIRCUIT SCHEMATIC AND LAYOUT OF PMOS FLOATING-GATE                        |

| TRANSISTOR [47]26                                                                                                      |

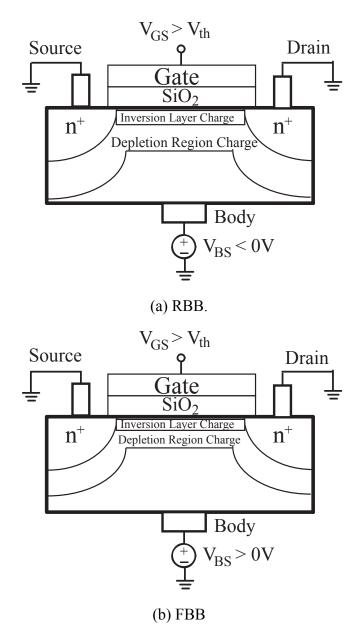

| FIGURE 2.12 BODY BIASING PRINCIPLES. (A) REVERSE BODY-BIASING. (B) FORWARD BODY-BIASING27                              |

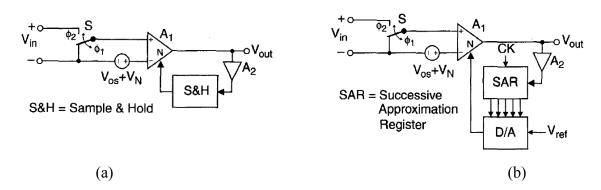

| FIGURE 2.13 BASIC AUTO-ZEROING STAGES. (A) ANALOGUE OFFSET CONTROL STORAGE AND (B) DIGITAL OFFSET                      |

| CONTROL STORAGE. [45]29                                                                                                |

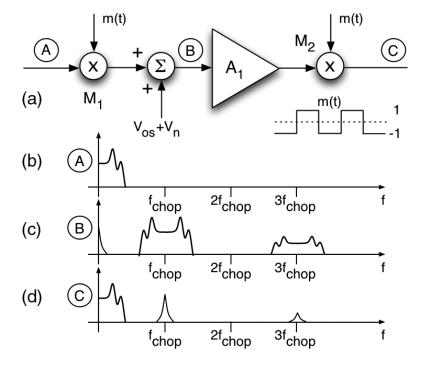

| FIGURE 2.14 CHOPPER STABILISATION PRINCIPLE.                                                                           |

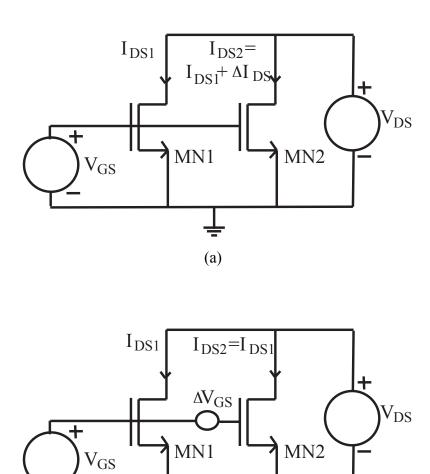

| Figure 3.1 (a) The transistor arrangement used to investigate drain current mismatch $\Delta I_{DS}$ of MOSFET             |

|----------------------------------------------------------------------------------------------------------------------------|

| DEVICES UNDER THE SAME VOLTAGE BIAS CONDITIONS. (B) A TRANSISTOR ARRANGEMENT USED TO INVESTIGATE                           |

| GATE VOLTAGE MISMATCH $\Delta V_{GS}$ FOR MOSFET DEVICES. In BOTH CIRCUITS MN1 IS SELECTED TO BE A                         |

| REFERENCE MODEL FOR ALL SIMULATIONS                                                                                        |

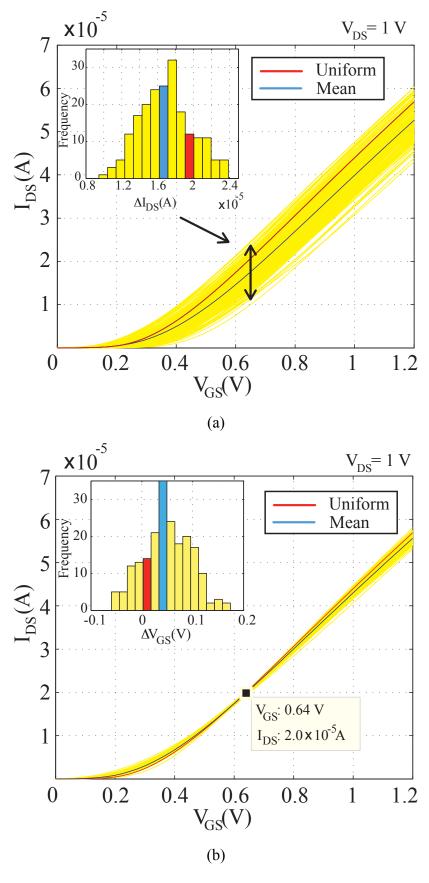

| Figure 3.2 (a) $I_{DS}$ / $V_{GS}$ characteristics of all model cards using the circuit arrangement in Figure 3.1 (a)      |

| Inset: A histogram of $\Delta I_{DS}$ . (b) $I_{DS}$ / $V_{GS}$ characteristics when $V_{GS}$ to MN2 is offset from MN1 to |

| MATCH $I_{DS}$ IN BOTH MOSFETS. INSET: A HISTOGRAM OF $\Delta V_{GS}$                                                      |

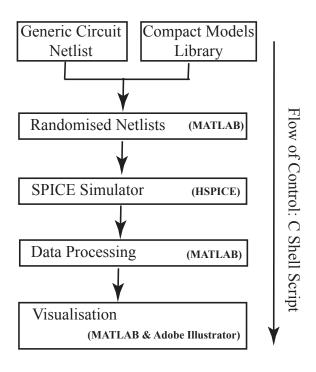

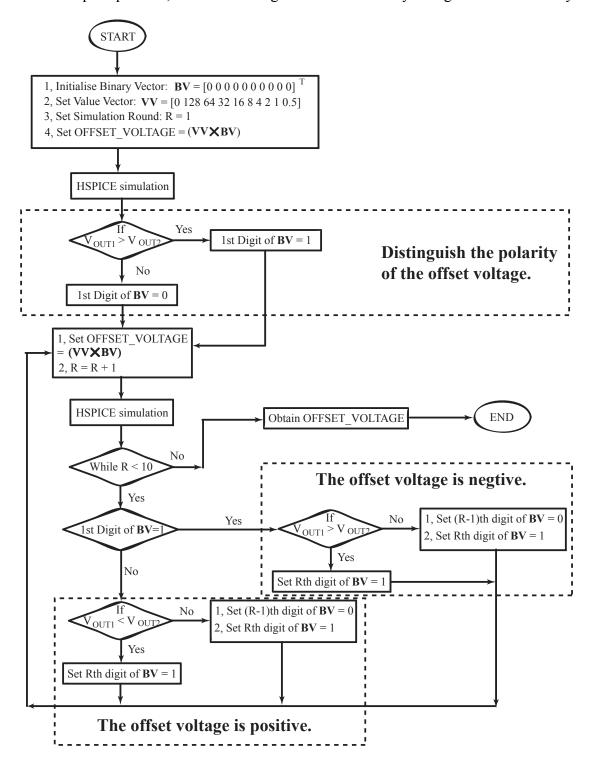

| FIGURE 3.3 THE MONTE-CARLO SIMULATION FLOW CHART                                                                           |

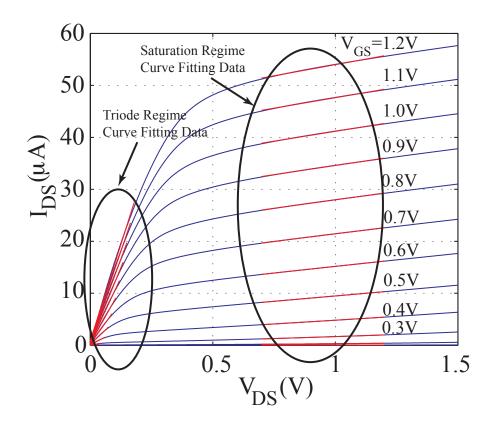

| FIGURE 3.4 THE OUTPUT CHARACTERISTIC CURVES OF A TYPICAL 35 NM NMOS TRANSISTOR WITH                                        |

| W=L=35 nm. The blue lines are simulation data. The red lines are curve fitted data48                                       |

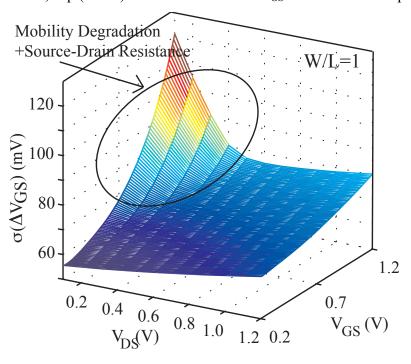

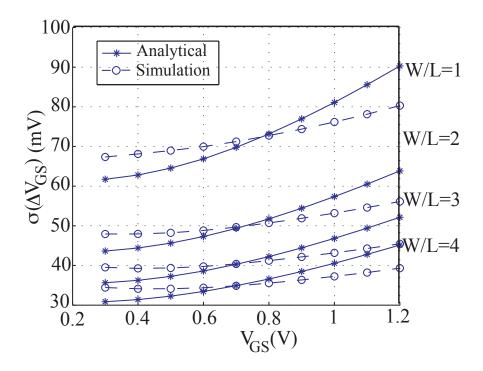

| Figure 3.5 A plot of the standard deviation of NMOS gate voltage mismatch $\Delta V_{GS}$ obtained by Monte                |

| Carlo simulation method. Each data point is based on a standard deviation of $40000\mathrm{simulation}$                    |

| RESULTS. THE DEVICE HAS A WIDTH RATIO OF $W/L=1$ . The results are dramatically increased when                             |

| $V_{GS}$ - $V_{DS}$ > $0.7~V$ occurs                                                                                       |

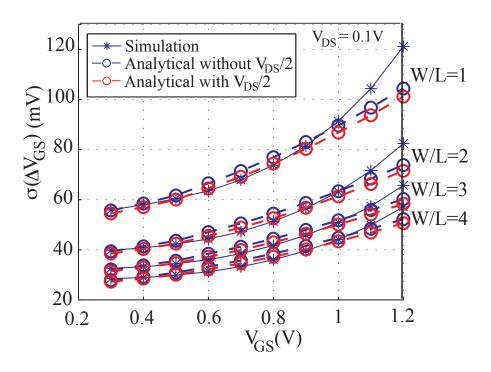

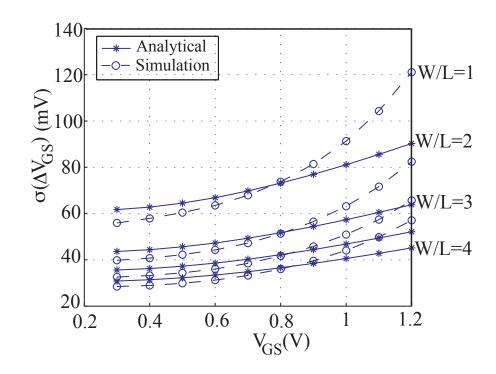

| Figure 3.6 A plot of the standard deviation of NMOS gate offset voltage $\Delta V_{GS}$ in the triode regime               |

| OBTAINED BY MONTE CARLO SIMULATIONS AND PROPOSED ANALYTICAL MODEL FOR DIFFERENT WIDTH RATIOS.                              |

| In this simulation $V_{\it DS}$ = $0.1$ V, when $V_{\it GS}$ > $0.8$ V, the standard deviations dramatically increases     |

| Due to mobility degradation. The differences with and without $V_{\it DS}/2$ have been plotted using                       |

| CIRCLE WITH DASHED LINES                                                                                                   |

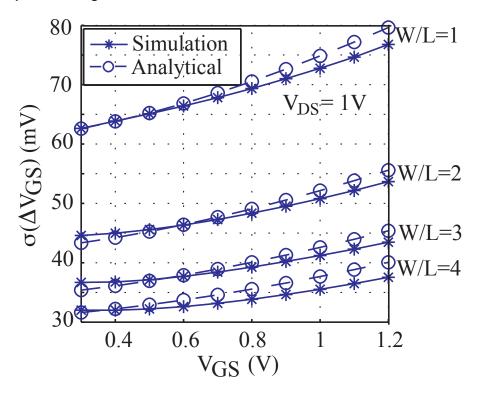

| Figure 3.7 A plot of the standard deviation of NMOS gate offset voltage $\Delta V_{GS}$ in Saturation regime               |

| OBTAINED BY MONTE CARLO SIMULATIONS AND PROPOSED ANALYTICAL MODEL FOR DIFFERENT WIDTH RATIOS.                              |

| In this simulation $V_{DS}$ = $1$ V, therefore the results are free from the impact of mobility                            |

| DEGRADATION                                                                                                                |

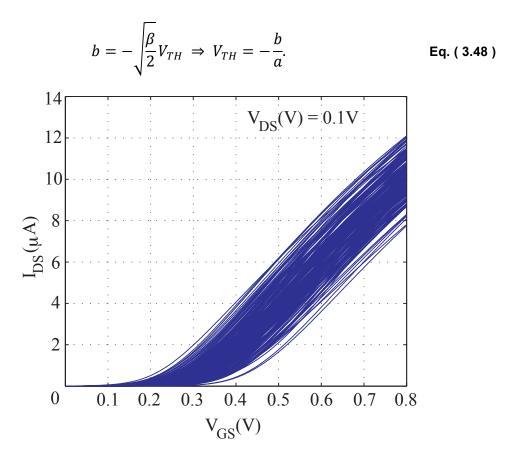

| Figure 3.8 Input curves ( $I_{DS}/V_{GS}$ ) of all BSIM4 model cards from the NMOS ensemble. The drain source              |

| voltage is configured to be $0.1\ V$ , since such a voltage will reduce the channel length modulation                      |

| EFFECT5                                                                                                                    |

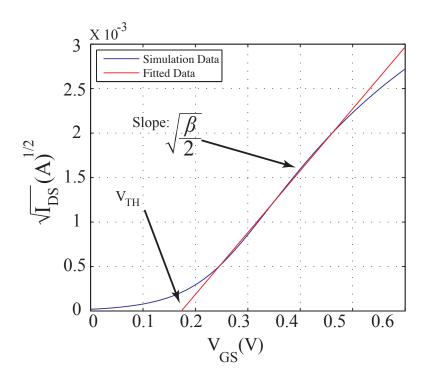

| FIGURE 3.9 CURVE FITTING PROCESS FOR LONG CHANNEL DEVICE CHARACTERISATION                                                  |

| Figure 3.10 A plot of standard deviation of NMOS gate offset voltage $\Delta V_{GS}$ in the triode regime                  |

| OBTAINED BY MONTE CARLO SIMULATIONS AND THE LONG-CHANNEL ANALYTICAL MISMATCH MODEL FOR                                     |

| DIFFERENT WIDTH RATIOS. THE DRAIN SOURCE VOLTAGE IS SET TO BE $V_{DS}$ = 0.1 V                                             |

| Figure 3.11 A plot of standard deviation of NMOS gate offset-voltage $\Delta V_{GS}$ in saturation regime                  |

| OBTAINED BY MONTE CARLO SIMULATIONS AND THE LONG-CHANNEL ANALYTICAL MISMATCH MODEL FOR                                     |

| DIFFERENT WIDTH RATIOS. THE DRAIN SOURCE VOLTAGE IS SET TO BE $V_{DS} = 1 \text{V}.$                                       |

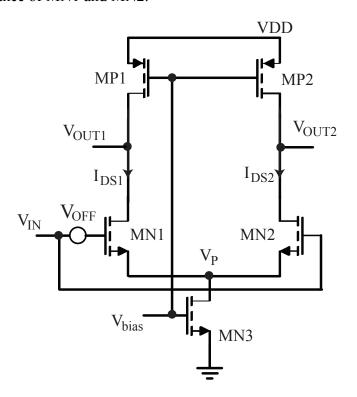

| FIGURE 3.12 OFFSET VOLTAGE EVALUATION TEST BENCH CIRCUIT                                                                   |

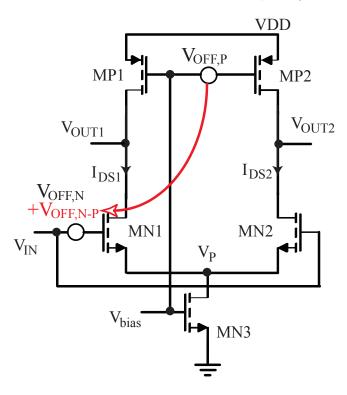

| FIGURE 3.13 OFFSET VOLTAGES CONTRIBUTED FROM MN1-MN2 AND MP1-MP2                                                           |

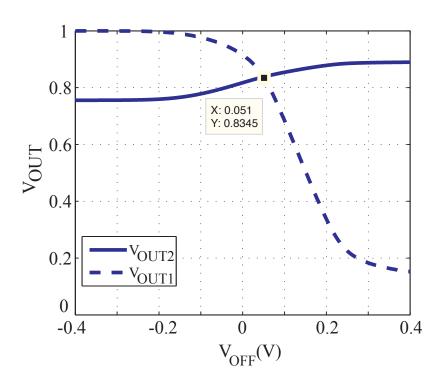

| Figure 3.14 The output voltages of a randomised netlist during the $V_{\text{OFF}}$ DC analysis6                           |

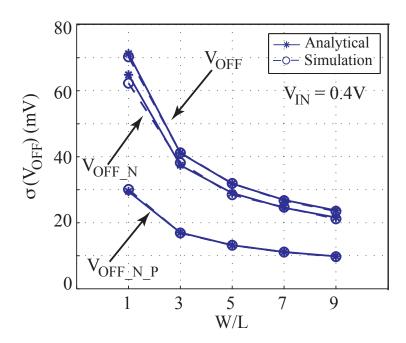

| FIGURE 3.15 THE COMPARISON BETWEEN SIMULATION RESULTS AND ANALYTICAL ESTIMATIONS OF THE DIFF-AMP                           |

| OFFSET VOLTAGE STANDARD DEVIATION MILITIPLE WIDTH RATIOS ARE TESTED 6                                                      |

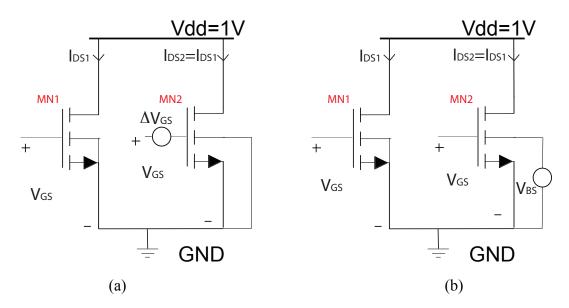

| FIGURE 4.1 OVER-DRIVE VOLTAGE MODIFICATION METHODS. (A) TO COMPENSATE DRAIN CURRENT MISMATCH BY                                      |

|--------------------------------------------------------------------------------------------------------------------------------------|

| APPLYING $\Delta V_{GS}$ at the gate of MN2. (b) To compensate drain current mismatch by applying                                    |

| BULK-SOURCE VOLTAGE $V_{\it BS}$ that further results a change in threshold voltage67                                                |

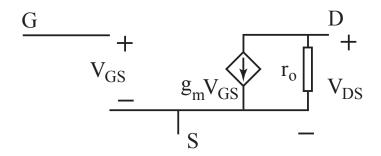

| FIGURE 4.2 MOSFET DEVICE SMALL SIGNAL EQUIVALENT CIRCUIT                                                                             |

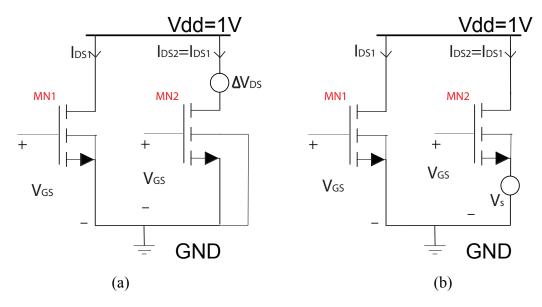

| Figure 4.3 Output impedance related methods. (c) To compensate drain current mismatch by applying an                                 |

| ADDITIONAL DRAIN-SOURCE VOLTAGE $\Delta V_{DS}$ . (D) TO COMPENSATE DRAIN CURRENT MISMATCH BY CHANGING THE                           |

| source voltage $V_S$ 69                                                                                                              |

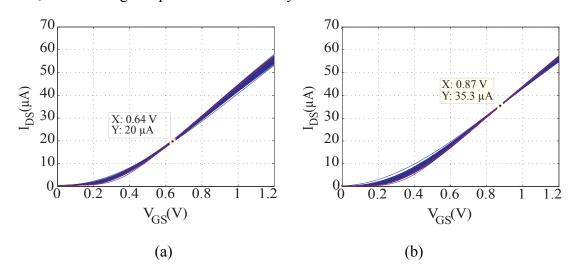

| FIGURE 4.4 (A) COMPENSATED $I_{DS}/V_{GS}$ AT $V_{GS}=0.64$ V. (B) COMPENSATED $I_{DS}/V_{GS}$ AT $V_{GS}=0.87$ V                    |

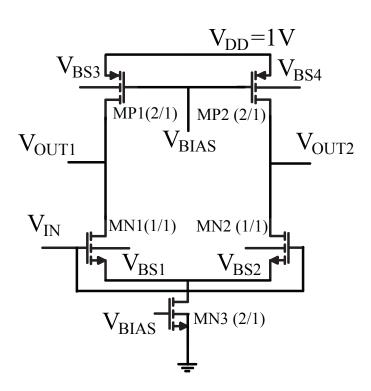

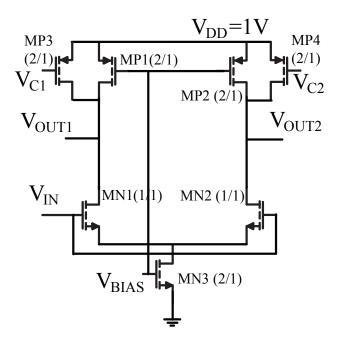

| FIGURE 4.5 TEST BENCH DIFFERENTIAL AMPLIFIER USED FOR BODY BIASING COMPENSATION SCHEME73                                             |

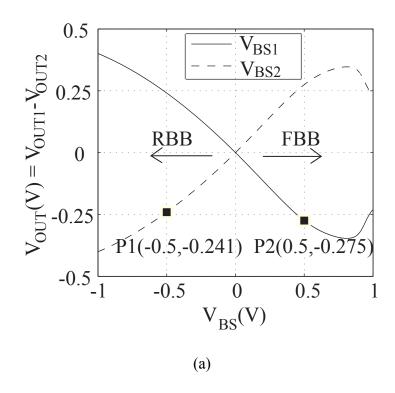

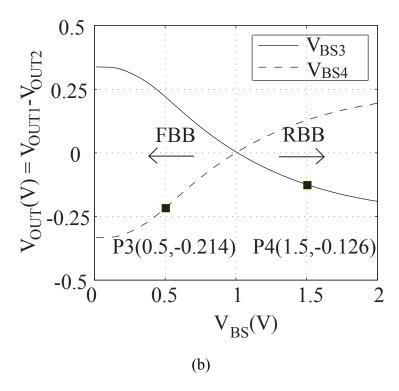

| Figure 4.6 Body biasing efficiency evaluation of the test bench differential amplifier. (a) Bulk voltage                             |

| $V_{\it BS1}$ and $V_{\it BS2}$ of MN1 and MN2 are swept by applying a DC analysis. If the voltage is positive, it is                |

| forward body biasing. Otherwise, it is reverse body biasing. (b) Bulk voltage $V_{\it BS3}$ and $V_{\it BS4}$ of MP1                 |

| and $MP2$ are swept by using the same DC simulation. It is forward body biased if the voltage lower                                  |

| THAN $1 \text{ V }(V_{DD})$ . Otherwise, it is reversely biased74                                                                    |

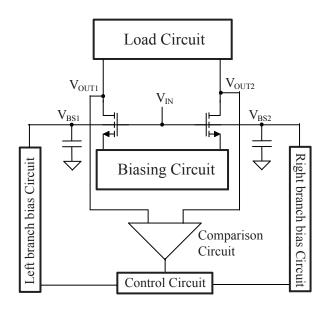

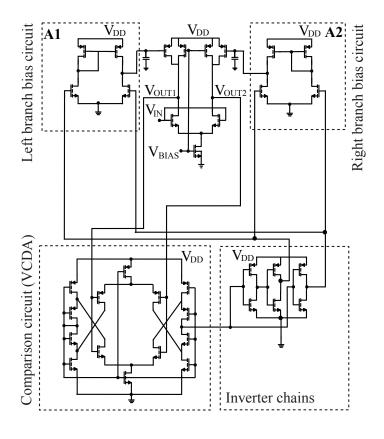

| FIGURE 4.7 BODY BIASING COMPENSATION SCHEME                                                                                          |

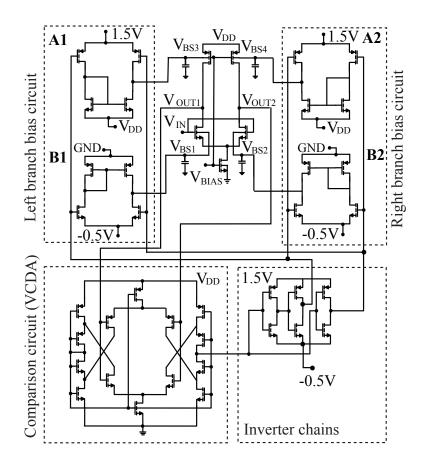

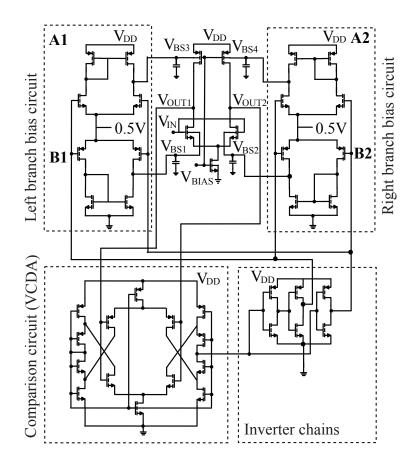

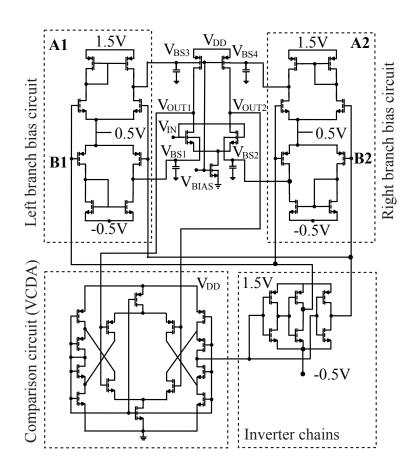

| FIGURE 4.8 PROPOSED REVERSE BODY BIASING SCHEME                                                                                      |

| FIGURE 4.9 PROPOSED FORWARD BODY BIASING SCHEME                                                                                      |

| FIGURE 4.10 PROPOSED ADAPTIVE BODY BIASING SCHEME80                                                                                  |

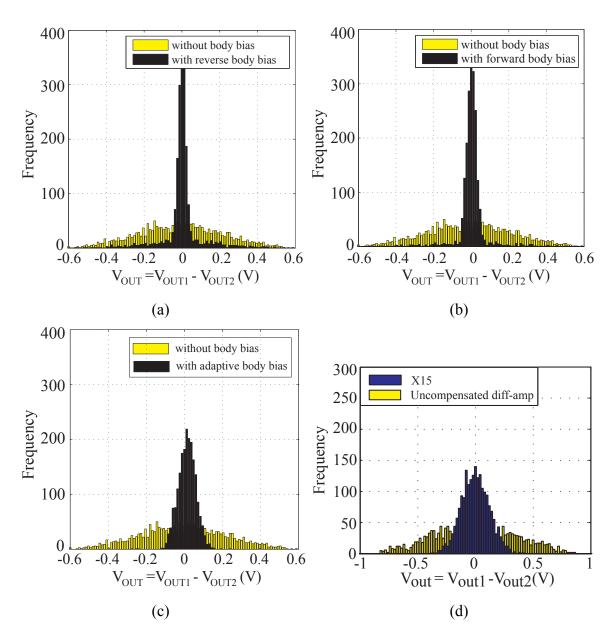

| Figure 4.11 $V_{\text{OUT}}$ histogram comparison before and after compensation. (a) Reverse body biasing is                         |

| APPLIED. (B) FORWARD BODY BIASING IS APPLIED. (C) ADAPTIVE BODY BIASING IS APPLIED. (D) THE TEST BENCH                               |

| CIRCUIT IS INCREASED BY 15 TIMES81                                                                                                   |

| FIGURE 4.12 DRAIN COMPENSATION TEST BENCH CIRCUIT                                                                                    |

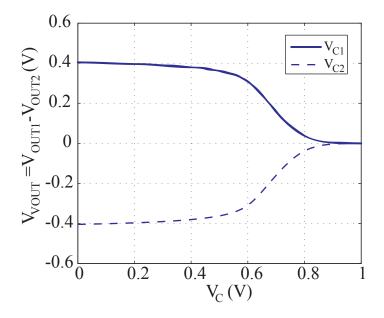

| Figure 4.13 The evaluation of drain compensation scheme efficiency. By applying $V_{C1}$ or $V_{C2}$ to the test                     |

| bench differential amplifier, the differential output voltage can vary from $-0.4~V$ to $0.4~V$ $84$                                 |

| FIGURE 4.14 PROPOSED DRAIN COMPENSATION SCHEME                                                                                       |

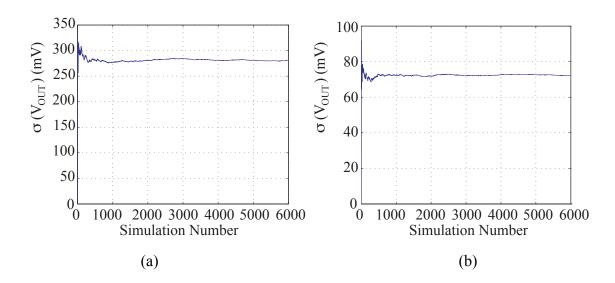

| Figure 4.15 Statistical trust region test. (a) The standard deviation of $V_{\it OUT}$ of the test bench circuit is                  |

| OBTAINED AS A FUNCTION DATA SAMPLE SIZE. (B) THE SAME PARAMETER OF DRAIN COMPENSATED RESULT IS                                       |

| PLOTTED AS A FUNCTION OF DATA SAMPLE SIZE86                                                                                          |

| FIGURE 4.16 TWO POTENTIAL APPROACHES TO IMPLEMENT SOURCE COMPENSATION                                                                |

| FIGURE 4.17 PROPOSED SOURCE COMPENSATION SCHEME.                                                                                     |

| Figure 4.18 (a) The output voltages of $V_{\it OUT1}$ after 2000 simulations. (b) $V_{\it OUT1}$ and $V_{\it OUT2}$ before and after |

| compensation89                                                                                                                       |

| FIGURE 4.19 HISTOGRAM OF DIFFERENTIAL OUTPUT VOLTAGE90                                                                               |

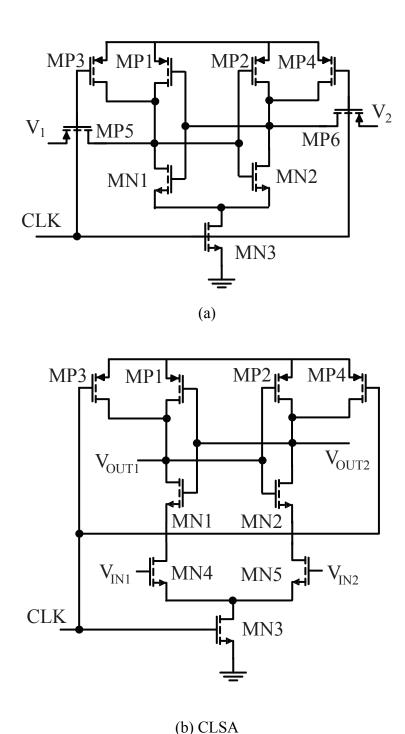

| FIGURE 5.1 THE SCHEMATICS OF CONVENTIONAL COMPARATOR DESIGNS. (A) VOLTAGE LATCH SENSE AMPLIFIER                           |

|---------------------------------------------------------------------------------------------------------------------------|

| (VLSA). (B) CURRENT LATCH SENSE AMPLIFIER (CLSA)95                                                                        |

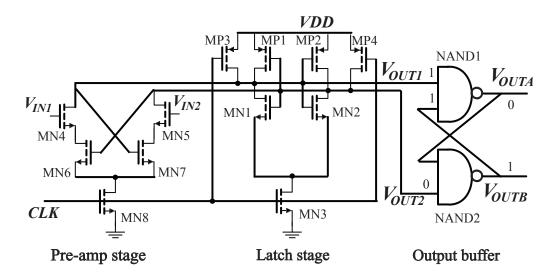

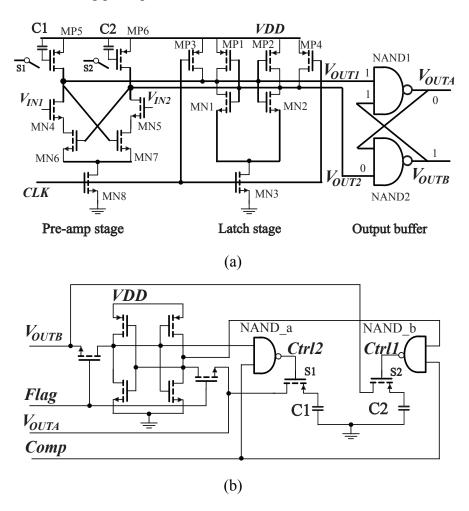

| FIGURE 5.2 PROPOSED HIGH-SPEED COMPARATOR                                                                                 |

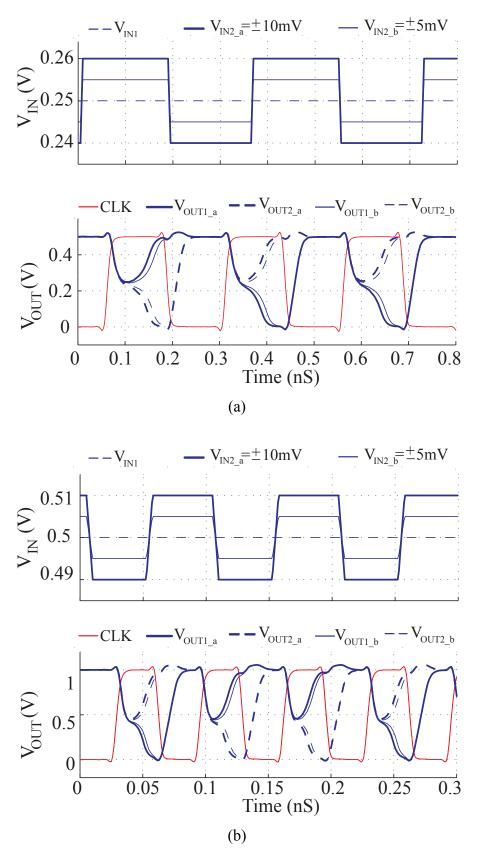

| FIGURE 5.3 DETAILED PLOTS OF SIGNALS FROM THE TRANSIENT ANALYSIS OF THE PROPOSED COMPARATOR. INPUT                        |

| voltage differences of $\pm 5$ mV and $\pm 10$ mV are applied using the testing. (a) The comparator is                    |

| tested with a $0.5~V$ supply voltage at a clock speed of $4~GHz$ . (b) The comparator is tested with a                    |

| 1 V SUPPLY VOLTAGE AT A CLOCK SPEED OF 15 GHz99                                                                           |

| FIGURE 5.4 THE FLOW CHART OF OFFSET EVALUATION USING A BINARY SEARCH ALGORITHM100                                         |

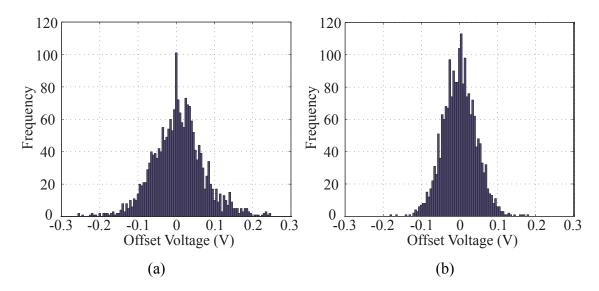

| Figure 5.5 Histograms of the offset voltage based on a sample of $2000\mathrm{randomised}$ comparator netlists.           |

| (a) The proposed comparator is tested using $0.5\ V$ supply voltage at a speed of $4\ GHz$ . (b) The                      |

| PROPOSED COMPARATOR IS TESTED USING 1 V SUPPLY VOLTAGE AT A SPEED OF 15 GHZ102                                            |

| FIGURE 5.6 PROPOSED COMPENSATION SCHEME. (A) TWO COMPENSATION TRANSISTORS MP5 AND MP6 ARE ADDED TO                        |

| THE DRAINS OF MN4 AND MN5, RESPECTIVELY. (B) THE COMPENSATION CIRCUIT IS COMPOSED BY A LATCH AND                          |

| TWO NAND GATES. IT IS USED TO CONTROL THE SWITCHES OF S1 AND S2104                                                        |

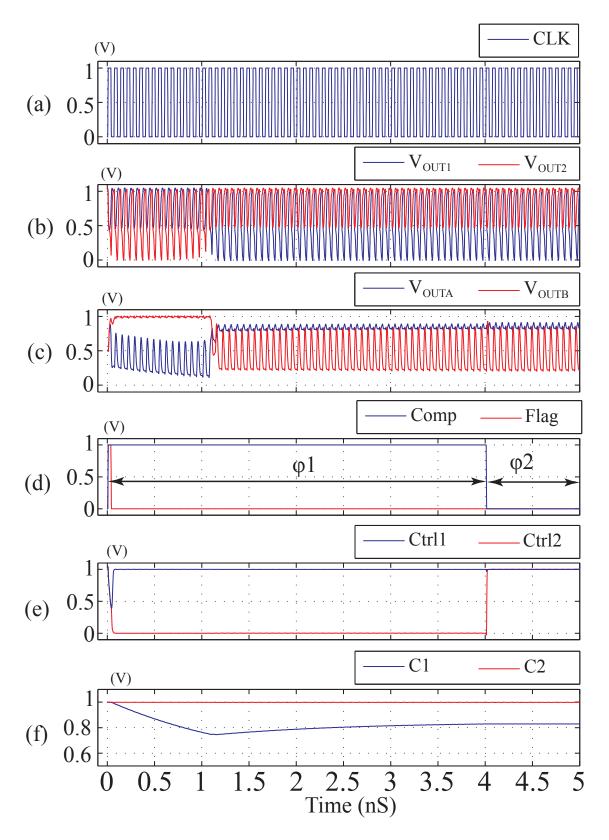

| FIGURE 5.7 TRANSIENT ANALYSIS THE COMPENSATED COMPARATOR. THE SIMULATION IS DIVIDED INTO COMPENSATION                     |

| phase $\phi 1$ and operational phase $\phi 2$ . (a) Clock signal at a speed on 15 GHz. (b) $V_{OUT1}$ and $V_{OUT2}$ from |

| THE LATCH STAGE. (C) $V_{\it OUTA}$ AND $V_{\it OUTB}$ FROM THE OUTPUT BUFFER STAGE. (D) TWO CONTROL SIGNALS "COMP"       |

| AND "FLAG" FOR THE COMPENSATION CIRCUIT. "COMP" CONTROLS THE WHOLE CIRCUIT WHETHER IN                                     |

| COMPENSATION PHASE $\phi 1$ OR OPERATIONAL PHASE $\phi 2$ . "FLAG" CONTROLS THE LATCH IN THE COMPENSATION                 |

| CIRCUIT TO HOLD THE OUTPUT POLARITY INFORMATION. (E) CONTROL SIGNALS "CTRL1" AND "CTRL2" FOR THE                          |

| SWITCHES S1 AND S2. (F) THE CHARGE STORED IN C1 AND C2106                                                                 |

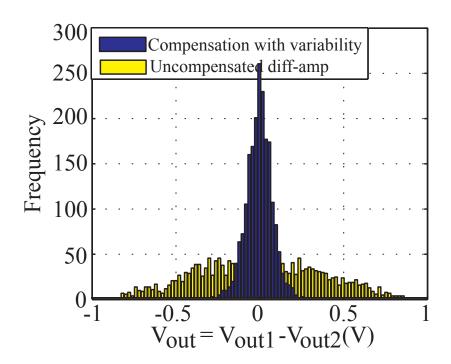

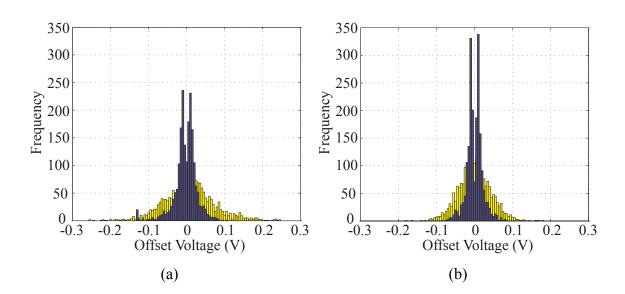

| FIGURE 5.8 THE HISTOGRAM OF THE OFFSET VOLTAGE OF THE COMPARATOR BEFORE AND AFTER COMPENSATION. 2000                      |

| RANDOMISED NETLISTS ARE USED AS DATA SAMPLE. THE UNCOMPENSATED RESULTS ARE PLOTTED IN YELLOW,                             |

| WHILST COMPENSATED RESULTS ARE PLOTTED IN BLACK. (A) THE PROPOSED COMPARATOR IS TESTED USING A                            |

| 0.5 V supply voltage at a speed of 4 GHz. Standard deviation of the offset voltage has been                               |

| improved from $67.4\text{mV}$ to $29\text{mV}$ . (b) The proposed comparator is tested using a $1\text{V}$ supply voltage |

| at a speed of $15\text{GHz}$ . Standard deviation of the offset voltage has been improved from $43.1\text{mV}$ to         |

| 20.3 MV                                                                                                                   |

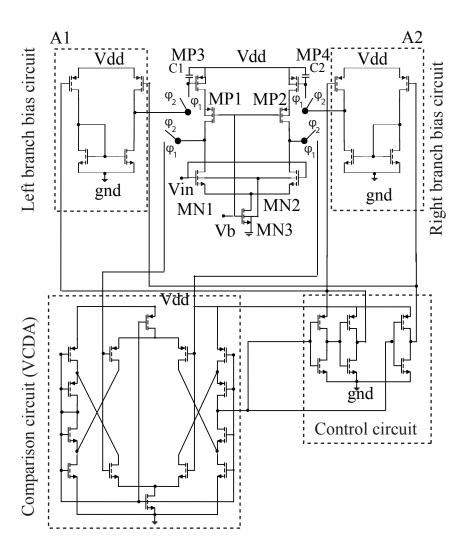

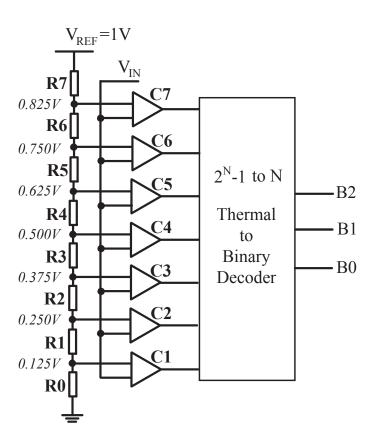

| FIGURE 6.1 THE SCHEMATIC OF THE PROPOSED 3-BIT 10 GSAMPLE/S FLASH ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 112    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

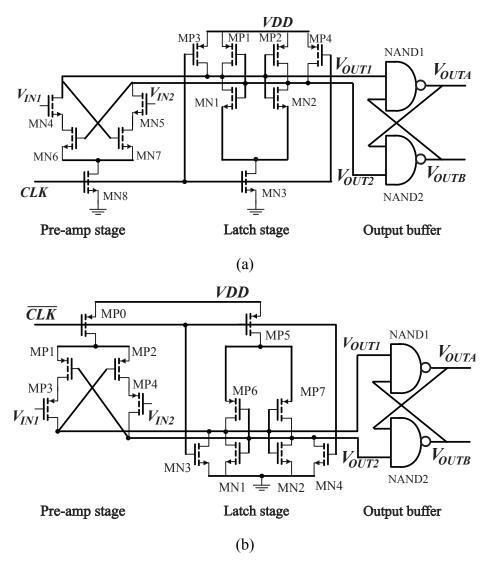

| FIGURE 6.2 COMPARATOR SCHEMATICS USED IN THE PROPOSED 3-BITS 10 GSAMPLE/S FLASH ADC. (A) N-TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| HIGH-SPEED COMPARATOR. (B) P-TYPE HIGH-SPEED COMPARATOR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 113    |

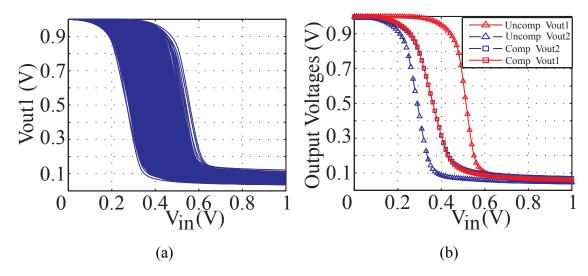

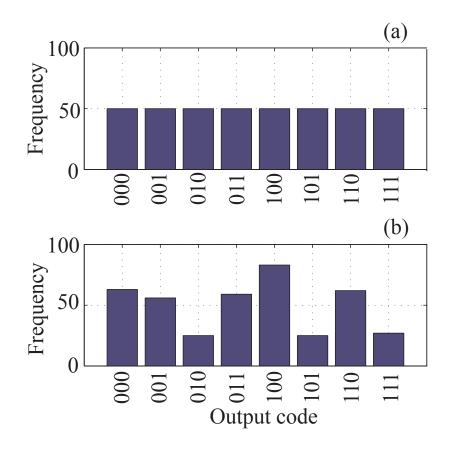

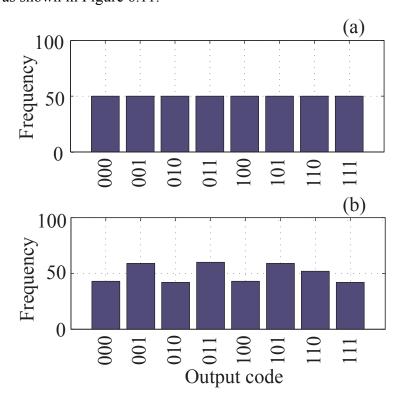

| Figure 6.3 Histogram of the output codes. (a) In the ideal case, 50 identical output codes will be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| COUNTED FOR EACH BIN WHERE THE BIN NUMBERS REPRESENT THE OUTPUT CODES. (B) IN A SIMULATED CAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SE,    |

| THE COUNTS VARY BETWEEN EACH BIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 116    |

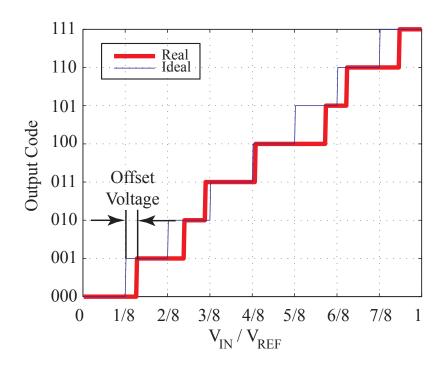

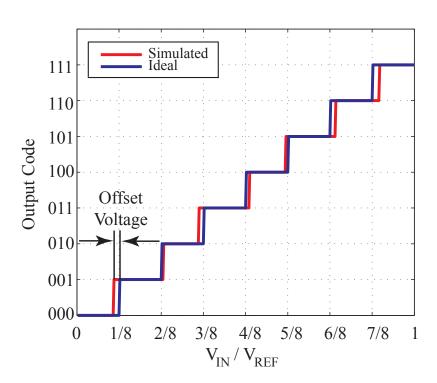

| $FIGURE\ 6.4\ TRANSFER\ CURVES\ FROM\ THE\ SIMULATIONS\ OF\ AN\ IDEAL\ AND\ A\ SIMULATED\ ADC\ WITH\ VARIABILITY\ TARGET AND A SIMULATED AND $ | AKEN   |

| INTO ACCOUNT. THE RED CURVE REPRESENTS THE SIMULATED DATA OF THE SIMULATED 3-BIT FLASH ADC. I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ГНЕ    |

| BLUE LINE REPRESENTS THE IDEAL TRANSFER CURVE OF THE ADC. THE OFFSET VOLTAGE IS HIGHLIGHTED IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | THIS   |

| FIGURE AS WELL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 116    |

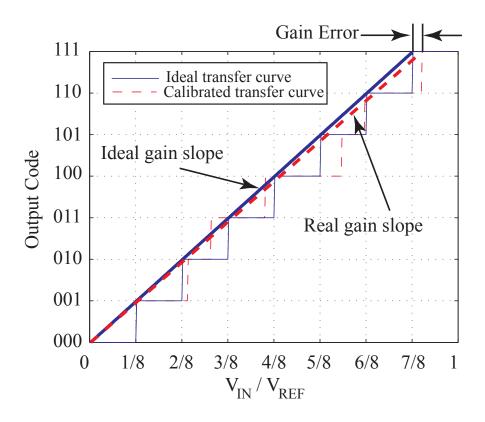

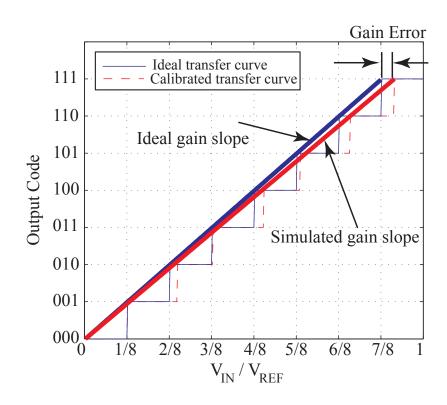

| Figure 6.5 Plot of gain error of a flash ADC. The gain error is the measured using the ideal gain slow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PE AS  |

| A REFERENCE. AFTER THE OFFSET VOLTAGE IS ELIMINATED, THE REAL GAIN SLOPE IS OBTAINED BY CONNECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ING    |

| THE FIRST AND THE LAST TRANSITION POINTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 117    |

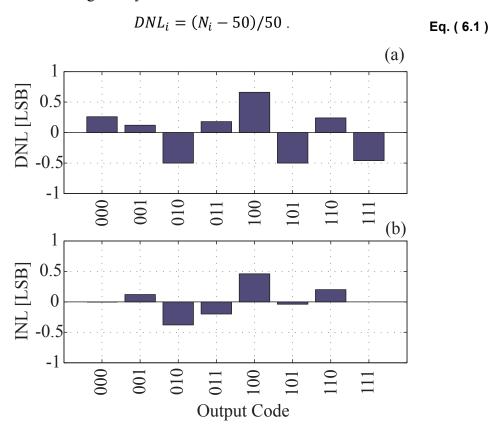

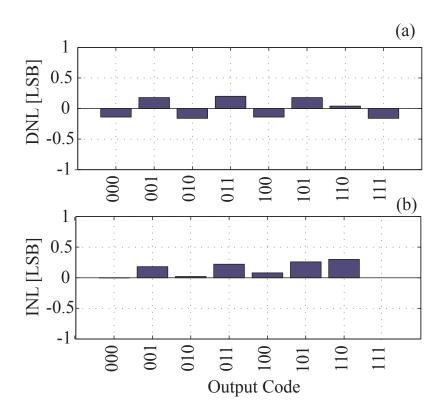

| FIGURE 6.6 (A) THE DNL AND (B) THE INL OF A RANDOMISED 3-BIT 10 GSAMPLE/S FLASH ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 118    |

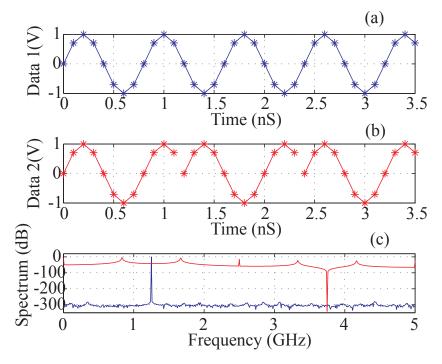

| FIGURE 6.7 FREQUENCY LEAKAGE PROBLEM. (A) CONTINUOUS SIGNAL. (B) DISCONTINUOUS SIGNAL. (C) FREQUENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CY     |

| SPECTRUM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 121    |

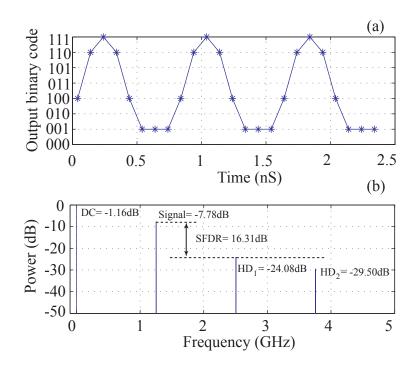

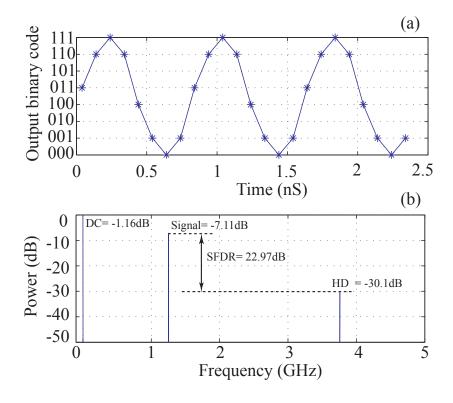

| Figure 6.8 Output power spectrum of a randomised 3-bit 10 GSample/s flash ADC. (a) The reconstru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | JCTED  |

| OUTPUT SIGNAL. (B) THE POWER SPECTRUM OF THE SIGNAL IN (A) ANALYSED BY FFT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123    |

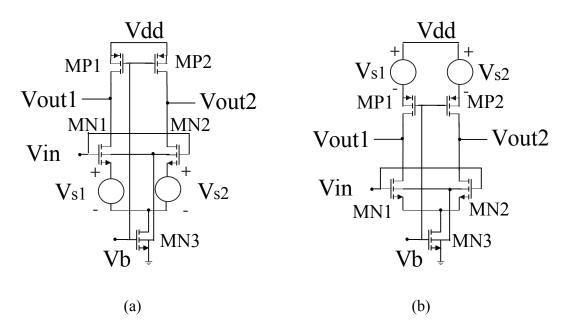

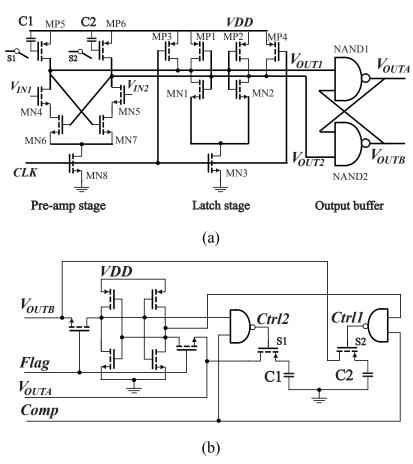

| Figure 6.9 Compensation scheme for the N-type high-speed Comparator. (a) The schematic of the N-type high-speed comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ГҮРЕ   |

| COMPARATOR. (B) THE SCHEMATIC OF THE CUSTOM DESIGNED COMPENSATION CIRCUIT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 124    |

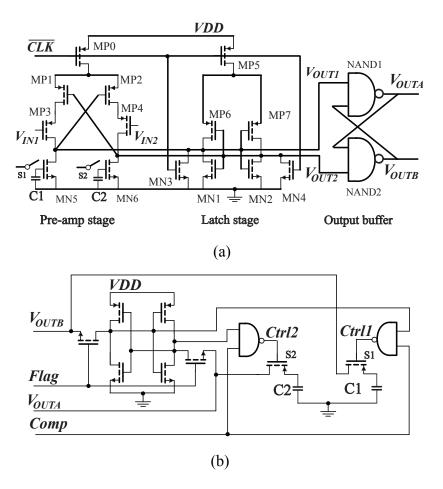

| Figure $6.10$ Compensation scheme for the P-type high-speed Comparator. (a) The schematic of the P-type high-speed comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ·TYPE  |

| COMPARATOR. (B) THE SCHEMATIC OF THE CUSTOM DESIGNED COMPENSATION CIRCUIT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 125    |

| Figure $6.11$ Output code histogram. (a) In an ideal case, $50$ output codes will be counted for each bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N. (B) |