Ferguson, Phillip David (2012) *Implementation exploration of imaging algorithms on FPGAs*. EngD thesis.

http://theses.gla.ac.uk/3419/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten:Theses <a href="http://theses.gla.ac.uk/">http://theses.gla.ac.uk/</a> theses@gla.ac.uk

# Implementation Exploration of Imaging Algorithms on FPGAs

Phillip David Ferguson MEng

A thesis submitted to

The Universities of

Glasgow

Strathclyde

Edinburgh

Heriot Watt

for the Degree of

Doctor of Engineering in System Level Integration

© Phillip David Ferguson, 14th May 2012

This thesis is dedicated to my mother and sister, Josephine and Katherine Ferguson, without your patience and support throughout the years this work would not have been possible. I love you both very much.

### Abstract

This portfolio thesis documents the work carried out as part of the Engineering Doctorate (EngD) programme undertaken at the Institute for System Level Integration. This work was sponsored and aided by Thales Optronics Ltd, a company well versed in developing specialised electro-optical devices. Field programmable gate arrays (FPGAs) are the devices of choice for custom image processing algorithms due to their reconfigurable nature. This also makes them more economical for low volume production runs where non-recoverable engineering costs are a large factor. Asynchronous circuits have had a remarkable surge in development over the last 20 years, to such an extent that they are beginning to displace conventional designs for niche applications. Their unique ability to adapt to environmental and data dependent processing needs have lead them to out-perform synchronous designs in ASIC platforms for certain applications.

The main body of research was separated into three areas of work presented as three technical documents. The first area of research addresses an FPGA implementation of contrast limited adaptive histogram equalisation (CLAHE), an algorithm which provides increased visual performance over conventional methods. From this, a novel implementation strategy was provided along with the key design factors for future use in a commercial context. The second area of research investigates the ability to create asynchronous circuits on FPGA devices. The main motivation for this work was to establish if any of the benefits which had been demonstrated for ASIC devices can be applied to FPGA devices. The investigation surmised the most suitable asynchronous design style for FPGA devices, a design flow to allow asynchronous circuits to function correctly on FPGAs and novel design strategies to implement consistent and repeatable asynchronous components. The result of this work established a route to implement circuits asynchronously in an FPGA. The final area of research focused on a unique conversion tool that allows synchronous circuits to run asynchronously on FPGAs whilst maintaining the same data flow patterns. This research produced an automated tool capable of implementing circuits on an FPGA asynchronously from their synchronous descriptions. This approach allowed the primary motivators of this work to be addressed. The results of this work show timing, resource utilisation and noise spectrum benefits by implementing circuits asynchronously on FPGA devices.

### Acknowledgements

Over the past 4 years, I have been supported by a number of people during this project and I would like to thank those that have offered me encouragement and help. Firstly I would likely to thank a number of individuals at Thales Optronics who have played a pivotal role in my studies and kept my feet grounded, both electrically and physically. I owe my industrial supervisors, Andrew Parmley and Danny Hume a significant amount of gratitude and thanks. Their insights and encouragement were always uplifting and beneficial. I would like to thanks especially Garry Widley, Adam Rixon and Steve Pattinson for instructing me in FPGA firmware design and patiently enduring my technical talks. I was never far from a sensible ear, a joke and a distracting conversation on Formula 1.

I am indebted to my academic supervisors who have been an outstanding source of insight and inspiration. Without the encouragement and suggested avenues of investigation from Tughrul Arslan and Ahmet Erdogan the initial probing of research directions would have been a much longer and troubling process. My eternal gratitude goes to Aristides Efthymiou, our discussions on asynchronous logic were invaluable. Without his support, guidance and encouragement this thesis might not have seen the light of day in the time that it has. I would also like to acknowledge Mathew Marshall for his encouragement and support in the early stages of the asynchronous logic research. A large amount of gratitude goes to my academic support mechanism, Khodor Fawaz. I will miss our conversations on research topics, life and being the only persons investigating asynchronous logic in Scotland.

I would like to address a few individuals that have kept a smile on face throughout the years and encouraged me to submit this thesis in a timely fashion. I would like acknowledge the coffee crew: The laughter was always a welcome break, never allowing the research to overwhelm me. I would like to acknowledge my good friends James Yorkshakes, Christopher Morrison, Iain Taylor and Stephen Bain. Without your support and snowboarding adventures, the days or research might not have been as much fun.

Finally I would like to especially thank my girlfriend and my extended family, Laura, Martin, Paul, Rachel, Michael, Carole, Maime, Jim and Nibbles the cat. I only hope you can forgive the time spent on this research, now it can be spent with you in front of the fire.

## Declaration of Originality

I declare that this portfolio thesis was composed entirely by myself and that the work contained herein is my own except where acknowledged in the text. A list of references has been given in the bibliography of each Technical Report. I also declare that this portfolio thesis has not been submitted for any other degrees or professional qualifications at any university. I am the sole author of this thesis and any errors contained herein are my own.

(Phillip David Ferguson)

## Contents

| A            | bstra | ct                                               | ii   |

|--------------|-------|--------------------------------------------------|------|

| A            | ckno  | wledgements                                      | iii  |

| D            | eclar | ation of Originality                             | iv   |

| Ι            | Po    | rtfolio Introduction                             | 1    |

|              | 1.1   | Executive Summary                                | . 2  |

|              | 1.2   | Portfolio Organisation                           | . 3  |

|              | 1.3   | Commercial Relevance                             | . 4  |

|              | 1.4   | External Events                                  | . 6  |

|              |       | 1.4.1 Academic and Industrial Events             | . 6  |

|              |       | 1.4.2 Conference Publications                    | . 7  |

|              | 1.5   | Taught Modules and Training                      | . 7  |

|              |       | 1.5.1 Technical Modules                          | . 8  |

|              |       | 1.5.2 Business Modules                           | . 9  |

|              |       | 1.5.3 Handshake Solutions TiDE Training          | . 10 |

| IJ           | T     | echnical Reports                                 | 12   |

| $\mathbf{R}$ | egior | -Based Contrast Enhancement                      | 13   |

|              | 2.1   | Aims and Introduction                            | . 14 |

|              | 2.2   | Contrast Enhancement Background                  | . 14 |

|              |       | 2.2.1 Algorithm Developments                     | . 14 |

|              |       | 2.2.2 Platform Developments                      | . 16 |

|              | 2.3   | Contrast Limited Adaptive Histogram Equalisation | . 17 |

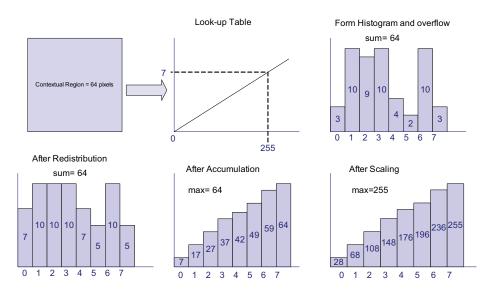

|              |       | 2.3.1 Histogram Creation                         | . 17 |

|              |       | 2.3.2 Clinning and Redistribution                | 18   |

Contents Page vi

|                          | 2.3.3                                                                                      | Forming the re-mapping function and smoothing artifacts                                                                                                                                                                                                                                                                                                    | 19                                                                              |

|--------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 2.4                      | CLAH                                                                                       | E Implementation                                                                                                                                                                                                                                                                                                                                           | 22                                                                              |

|                          | 2.4.1                                                                                      | Implementation Tool Flow                                                                                                                                                                                                                                                                                                                                   | 22                                                                              |

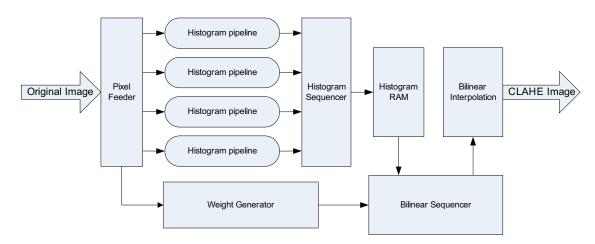

|                          | 2.4.2                                                                                      | Top Level Overview                                                                                                                                                                                                                                                                                                                                         | 23                                                                              |

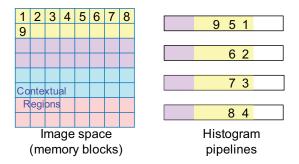

|                          | 2.4.3                                                                                      | Memory Management                                                                                                                                                                                                                                                                                                                                          | 24                                                                              |

|                          | 2.4.4                                                                                      | Pixel feeder                                                                                                                                                                                                                                                                                                                                               | 25                                                                              |

|                          | 2.4.5                                                                                      | Weight Generator                                                                                                                                                                                                                                                                                                                                           | 26                                                                              |

|                          | 2.4.6                                                                                      | Bilinear sequencer                                                                                                                                                                                                                                                                                                                                         | 26                                                                              |

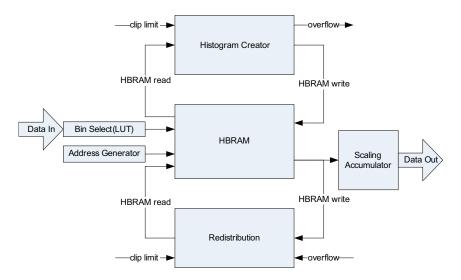

|                          | 2.4.7                                                                                      | Histogram Pipeline                                                                                                                                                                                                                                                                                                                                         | 29                                                                              |

|                          | 2.4.8                                                                                      | Smoothing Contextual Regions                                                                                                                                                                                                                                                                                                                               | 36                                                                              |

|                          | 2.4.9                                                                                      | Top Level FSM                                                                                                                                                                                                                                                                                                                                              | 38                                                                              |

| 2.5                      | Analys                                                                                     | sis and Results                                                                                                                                                                                                                                                                                                                                            | 39                                                                              |

|                          | 2.5.1                                                                                      | Image Correctness                                                                                                                                                                                                                                                                                                                                          | 39                                                                              |

|                          | 2.5.2                                                                                      | Resource Utilisation Results                                                                                                                                                                                                                                                                                                                               | 43                                                                              |

|                          | 2.5.3                                                                                      | Timing Results                                                                                                                                                                                                                                                                                                                                             | 44                                                                              |

|                          | 2.5.4                                                                                      | Power consumption                                                                                                                                                                                                                                                                                                                                          | 46                                                                              |

| 2.6                      | Conclu                                                                                     | sions and Future Work                                                                                                                                                                                                                                                                                                                                      | 51                                                                              |

| 2.7                      | Refere                                                                                     | nces                                                                                                                                                                                                                                                                                                                                                       | 53                                                                              |

| 4.1                      |                                                                                            |                                                                                                                                                                                                                                                                                                                                                            |                                                                                 |

|                          |                                                                                            | Asynchronous Circuits on FPGAs                                                                                                                                                                                                                                                                                                                             | 55                                                                              |

|                          | ishing .                                                                                   |                                                                                                                                                                                                                                                                                                                                                            |                                                                                 |

| $\mathbf{Establ}$        | ishing .<br>Aims a                                                                         | Asynchronous Circuits on FPGAs                                                                                                                                                                                                                                                                                                                             | 55                                                                              |

| Establ                   | ishing .<br>Aims a                                                                         | Asynchronous Circuits on FPGAs                                                                                                                                                                                                                                                                                                                             | <b>55</b>                                                                       |

| Establ                   | ishing A<br>Aims a<br>Challe                                                               | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | <b>55</b> 56                                                                    |

| Establ                   | Aims a<br>Challer<br>3.2.1<br>3.2.2                                                        | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | <b>55</b> 56 56                                                                 |

| Establ<br>3.1<br>3.2     | Aims a<br>Challer<br>3.2.1<br>3.2.2                                                        | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | <b>55</b> 56 56 56 57                                                           |

| Establ<br>3.1<br>3.2     | Aims a Challer 3.2.1 3.2.2 Techni                                                          | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | 55<br>56<br>56<br>56<br>57                                                      |

| Establ<br>3.1<br>3.2     | Aims a Challer 3.2.1 3.2.2 Techni 3.3.1 3.3.2                                              | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | 55<br>56<br>56<br>56<br>57<br>59                                                |

| 3.1<br>3.2<br>3.3        | Aims a Challer 3.2.1 3.2.2 Techni 3.3.1 3.3.2                                              | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | 555<br>566<br>566<br>577<br>599<br>600                                          |

| 3.1<br>3.2<br>3.3        | Aims a Challer 3.2.1 3.2.2 Techni 3.3.1 3.3.2 FPGA                                         | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | 555<br>566<br>566<br>577<br>599<br>600<br>655                                   |

| 3.1<br>3.2<br>3.3        | Aims a Challes 3.2.1 3.2.2 Techni 3.3.1 3.3.2 FPGA 3.4.1 3.4.2                             | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | 555<br>566<br>566<br>577<br>599<br>600<br>655<br>666                            |

| 3.1<br>3.2<br>3.3        | Aims a Challes 3.2.1 3.2.2 Techni 3.3.1 3.3.2 FPGA 3.4.1 3.4.2                             | Asynchronous Circuits on FPGAs and Introduction  Inges and Motivation  Previous Contributions  Fundamental Issues  cal Background  Synchronous Logic  Self-timed Logic  Implementation Considerations  Asynchronous Component Challenges  Design Tool Considerations                                                                                       | 555<br>566<br>566<br>577<br>599<br>600<br>655<br>666                            |

| 3.1<br>3.2<br>3.3        | Aims a Challes 3.2.1 3.2.2 Techni 3.3.1 3.3.2 FPGA 3.4.1 3.4.2 Design                      | Asynchronous Circuits on FPGAs and Introduction nges and Motivation  Previous Contributions  Fundamental Issues cal Background  Synchronous Logic  Self-timed Logic  Implementation Considerations  Asynchronous Component Challenges  Design Tool Considerations  Flow Proposal                                                                           | 555<br>566<br>566<br>577<br>599<br>600<br>65<br>666<br>688<br>733               |

| 3.1<br>3.2<br>3.3        | Aims a Challer 3.2.1 3.2.2 Techni 3.3.1 3.3.2 FPGA 3.4.1 3.4.2 Design 3.5.1 3.5.2          | Asynchronous Circuits on FPGAs and Introduction                                                                                                                                                                                                                                                                                                            | 555<br>566<br>566<br>577<br>599<br>600<br>65<br>666<br>688<br>733               |

| 3.1<br>3.2<br>3.3<br>3.4 | Aims a Challer 3.2.1 3.2.2 Techni 3.3.1 3.3.2 FPGA 3.4.1 3.4.2 Design 3.5.1 3.5.2          | Asynchronous Circuits on FPGAs and Introduction nges and Motivation Previous Contributions Fundamental Issues cal Background Synchronous Logic Self-timed Logic Implementation Considerations Asynchronous Component Challenges Design Tool Considerations Flow Proposal Standard FPGA Design Flow Modification Component Construction                     | 555<br>566<br>566<br>577<br>599<br>600<br>655<br>666<br>688<br>733<br>755       |

| 3.1<br>3.2<br>3.3<br>3.4 | Aims a Challes 3.2.1 3.2.2 Techni 3.3.1 3.3.2 FPGA 3.4.1 3.4.2 Design 3.5.1 3.5.2 Verifica | Asynchronous Circuits on FPGAs and Introduction nges and Motivation Previous Contributions Fundamental Issues cal Background Synchronous Logic Self-timed Logic Implementation Considerations Asynchronous Component Challenges Design Tool Considerations a Flow Proposal Standard FPGA Design Flow Modification Component Construction ation and Results | 555<br>566<br>566<br>577<br>599<br>600<br>655<br>666<br>688<br>733<br>755<br>81 |

Contents Page vii

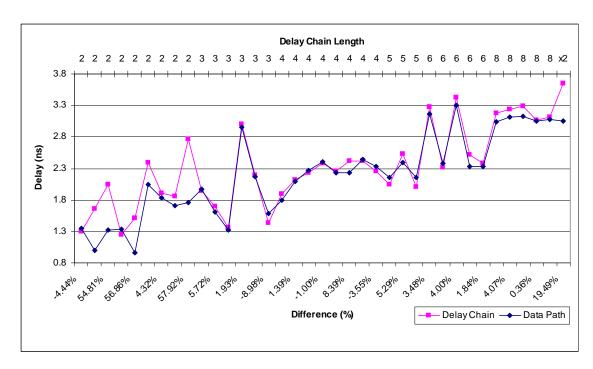

|               |                 | 3.6.3   | Delay Chain Matching                                 | . 84  |

|---------------|-----------------|---------|------------------------------------------------------|-------|

|               | 3.7             | Conclu  | sions and Future Work                                | . 86  |

| ,             | 3.8             | Refere  | nces                                                 | . 88  |

| Αu            | $\mathbf{tom}$  | ated A  | synchronous Circuits Implemented in FPGAs(AACIF)     | 92    |

|               | 4.1             | Aims a  | and Introduction                                     | . 93  |

|               | 4.2             | FPGA    | Design Flow Proposal                                 | . 93  |

|               | 4.3             | EDIF    | Circuit Representations                              | . 95  |

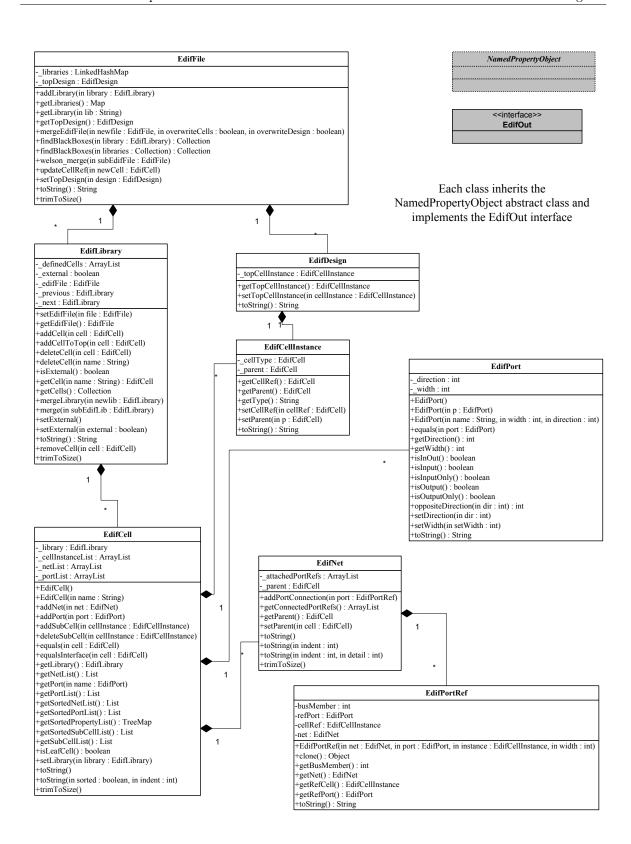

|               |                 | 4.3.1   | Mapping EDIF Files to Object Orientated Structures   | . 98  |

|               | 4.4             | Conver  | rsion Algorithm/Process                              | . 100 |

|               |                 | 4.4.1   | Parsing Input Files and Grouping Data Path registers | . 100 |

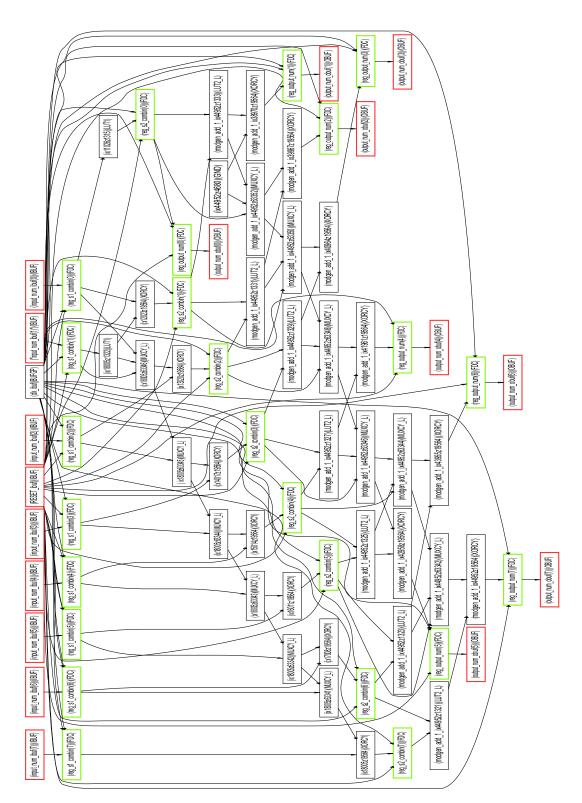

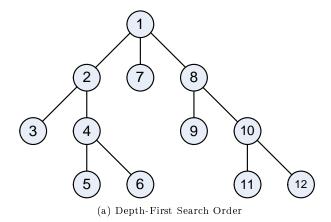

|               |                 | 4.4.2   | Graphing Structures                                  | . 101 |

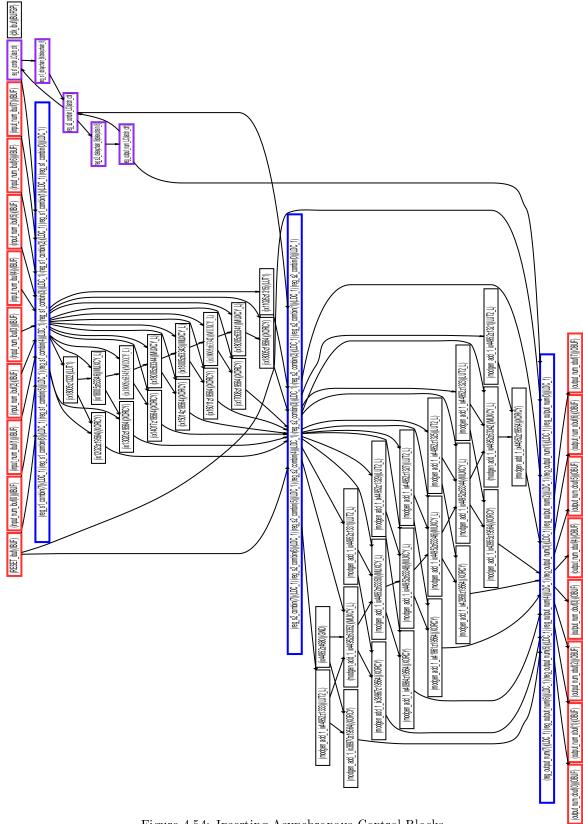

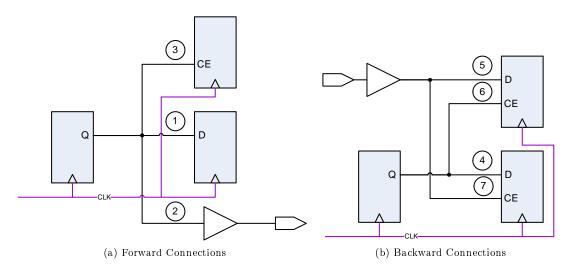

|               |                 | 4.4.3   | Register Duplication and Controller Insertion        | . 103 |

|               |                 | 4.4.4   | Register Mapping and Tracing Interconnections        | . 105 |

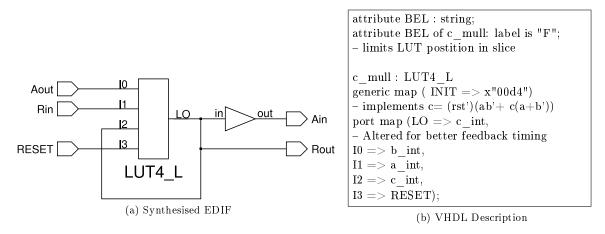

|               |                 | 4.4.5   | Connecting Controllers and Inserting Delay chains    | . 109 |

|               |                 | 4.4.6   | Constraint Insertion                                 | . 109 |

|               | 4.5             | Creatin | ng a Device Dependent Asynchronous library           | . 111 |

|               |                 | 4.5.1   | Delay Chains                                         | . 111 |

|               |                 | 4.5.2   | Asynchronous Controllers                             | . 111 |

|               | 4.6             | Analys  | sis and Results                                      | . 120 |

|               |                 | 4.6.1   | Timing Results                                       | . 121 |

|               |                 | 4.6.2   | Utilisation Results                                  | . 127 |

|               |                 | 4.6.3   | Power Spectrum Analysis and Core Voltage Stability   | . 129 |

|               | 4.7             | Conclu  | sions and Future work                                | . 134 |

|               |                 | 4.7.1   | Further Considerations                               | . 135 |

|               | 4.8             | Refere  | nces                                                 | . 136 |

| III           |                 | Conclu  | ısions                                               | 138   |

|               | 5.1             | Thesis  | Summary                                              | . 139 |

| ,             | 5.2             | Thesis  | Contributions                                        | . 140 |

| $\mathbf{IV}$ | A               | Additi  | onal Material                                        | 143   |

| $\mathbf{A}$  | $\mathbf{CL} A$ | AHE In  | nplementation and Analysis Supplements               | 144   |

|               |                 |         | E Design Tools                                       | . 144 |

|               |                 |         | l Path Synthesis View                                |       |

Contents Page viii

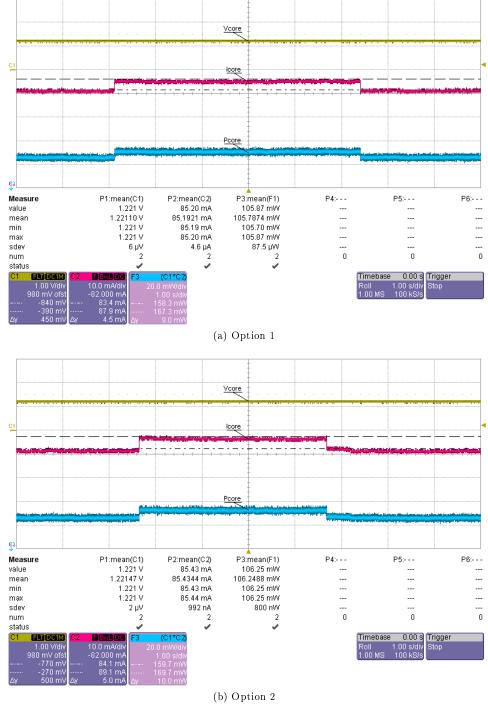

|              | A.3 | Histogram Pipeline Power Consumption      | 146 |

|--------------|-----|-------------------------------------------|-----|

| В            | Imp | plementations of Asynchronous Components  | 148 |

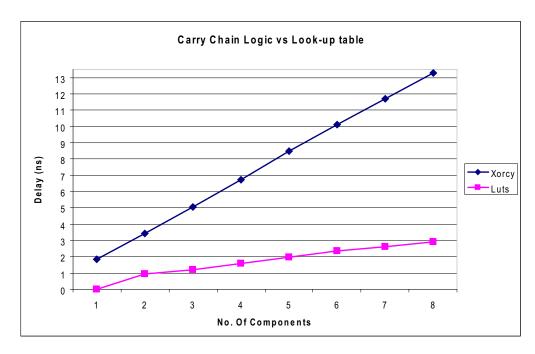

|              | B.1 | Delay Chains                              | 148 |

|              |     | B.1.1 XOR Carry Chains                    | 148 |

|              |     | B.1.2 Look Up Table Carry Chains          | 152 |

|              | B.2 | Muller C-element Implementations          | 154 |

|              | B.3 | Asynchronous Wrapper Implementation       | 156 |

| $\mathbf{C}$ | AA  | CIF Supplementary Material                | 157 |

|              | C.1 | EDIF Muller C-Element                     | 157 |

|              | C.2 | Controller Comparisons                    | 158 |

|              |     | C.2.1 Comparison TestBench Files          | 158 |

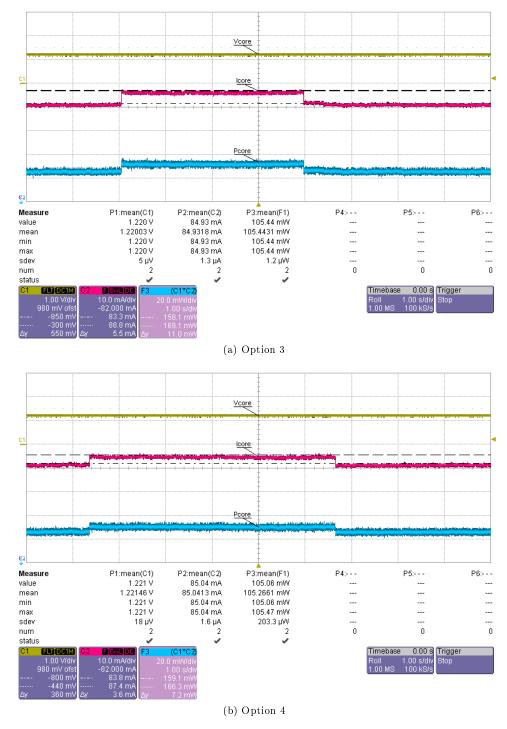

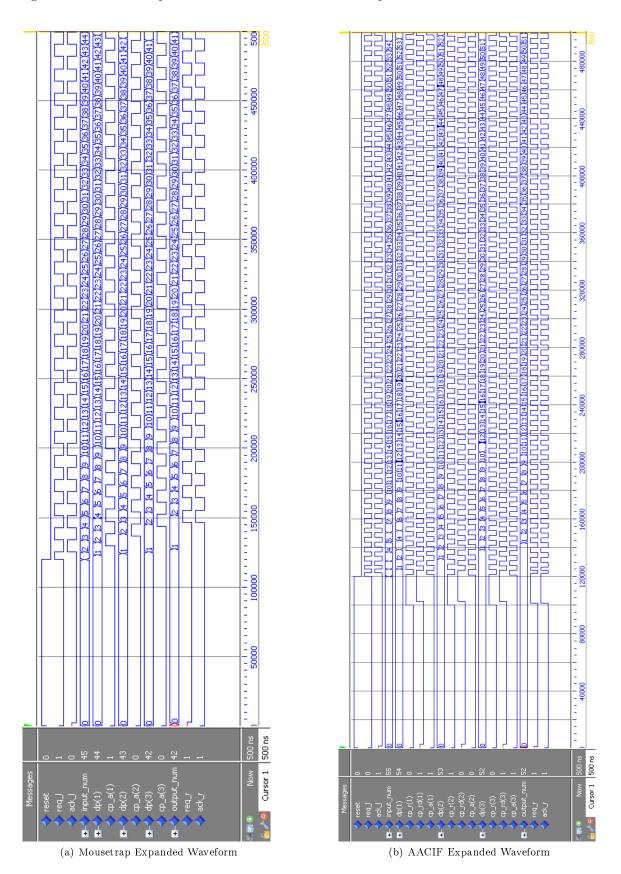

|              |     | C.2.2 Expanded Waveforms                  | 163 |

|              | C.3 | Power Spectrum Setup                      | 164 |

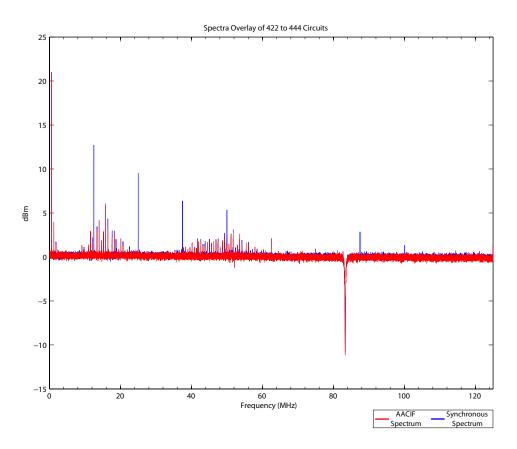

|              | C.4 | Power spectrum for the 422 to 444 circuit | 165 |

## List of Figures

| 2.1  | Histogram Equalisation Enhancements [15]     | 15 |

|------|----------------------------------------------|----|

| 2.2  | Contrast Limiting Effects on AHE [15]        | 16 |

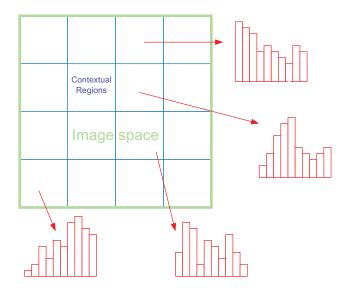

| 2.3  | Contextual Region Histograms                 | 18 |

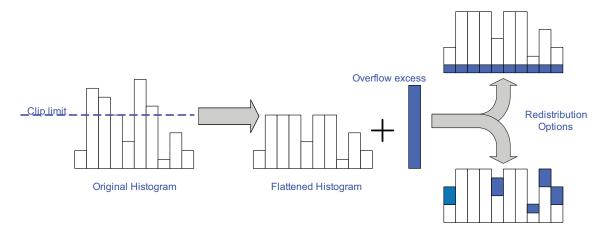

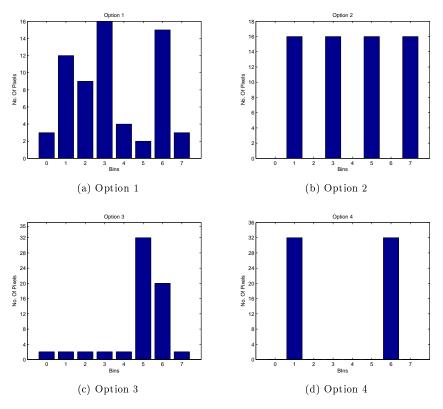

| 2.4  | Redistribution Options                       | 19 |

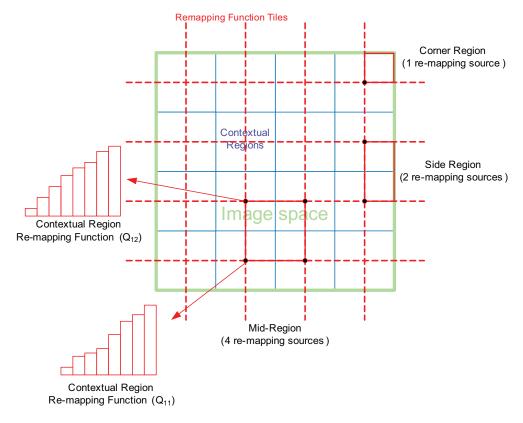

| 2.5  | Bilinear Regions over Image                  | 20 |

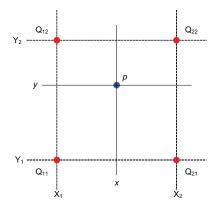

| 2.6  | Bilinear Interpolation                       | 21 |

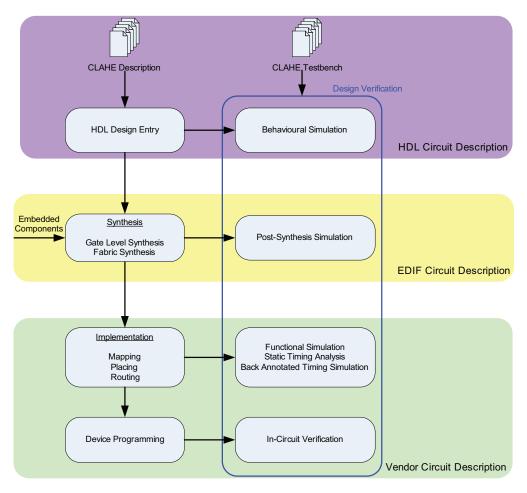

| 2.7  | Synchronous Design flow                      | 23 |

| 2.8  | CLAHE Processing Stages                      | 24 |

| 2.9  | Image Memory Configuration                   | 25 |

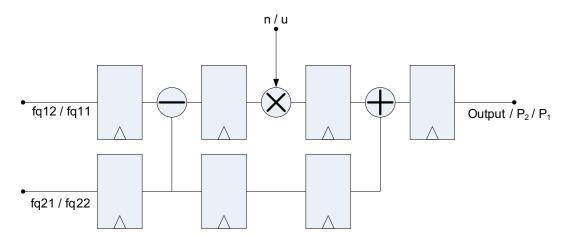

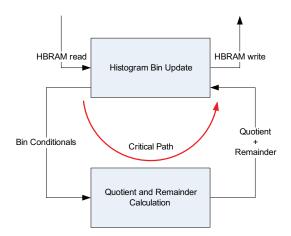

| 2.10 | Histogram Pipeline Arithmetic                | 29 |

| 2.11 | Histogram Pipeline Structure                 | 30 |

| 2.12 | Redistribution Options                       | 31 |

| 2.13 | Redistribution Waveform                      | 33 |

| 2.14 | Mach Band                                    | 34 |

| 2.15 | Histogram Pipeline with Finite State Machine | 35 |

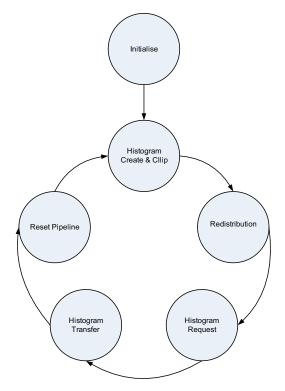

| 2.16 | Histogram Pipeline States                    | 35 |

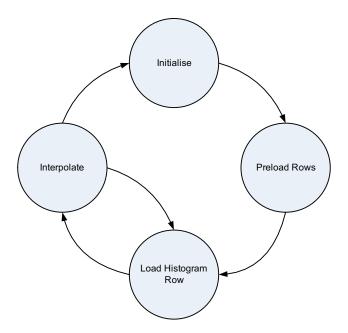

| 2.17 | Bilinear Interpolation Minimisation          | 37 |

| 2.18 | Top Level State Machine                      | 38 |

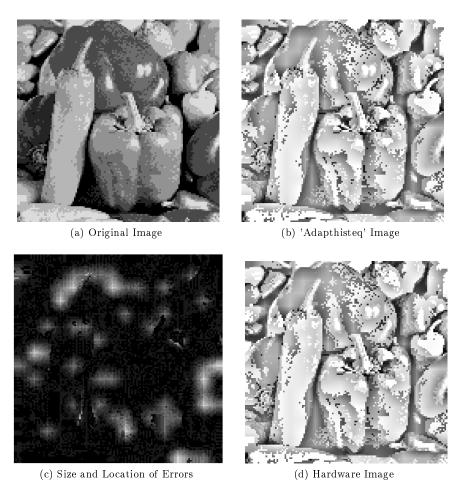

| 2.19 | Image Results Comparison                     | 40 |

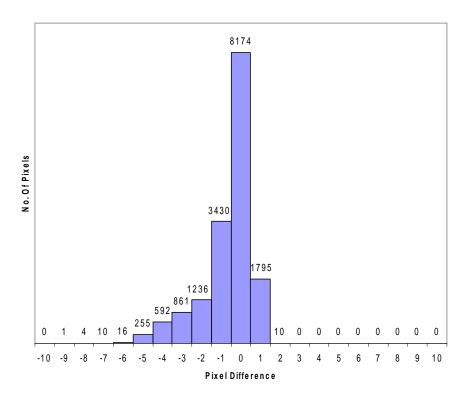

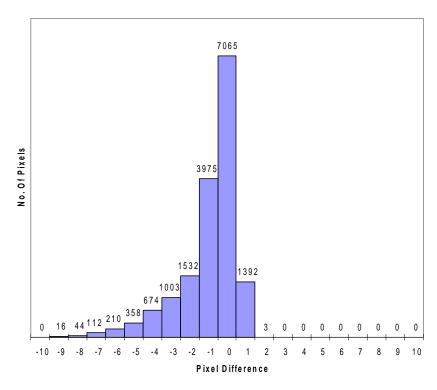

| 2.20 | Adapthisteq VHDL differences                 | 41 |

| 2.21 | Additional Image Results Comparison          | 42 |

| 2.22 | Consistent 'Adapthisteq' VHDL Differences    | 43 |

| 2.23 | Critical Path through Redistribution block   | 45 |

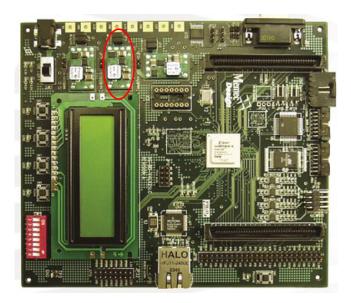

| 2.24 | Development Board                            | 46 |

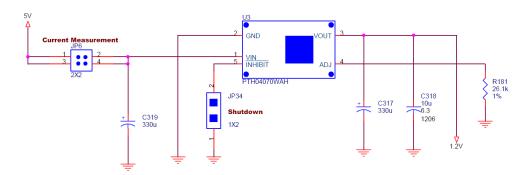

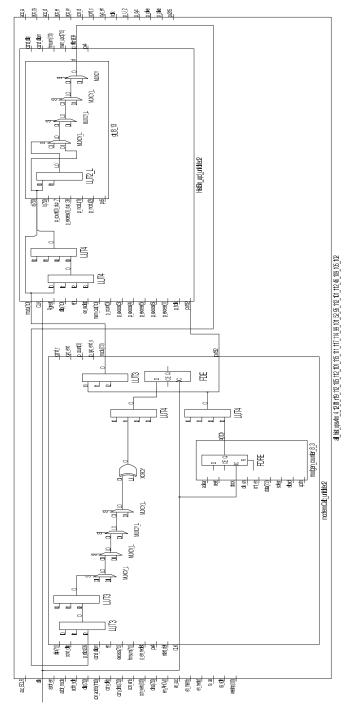

| 2.25 | Voltage Regulator for FPGA Core              | 47 |

| 2.26 | Input Variation Options                      | 48 |

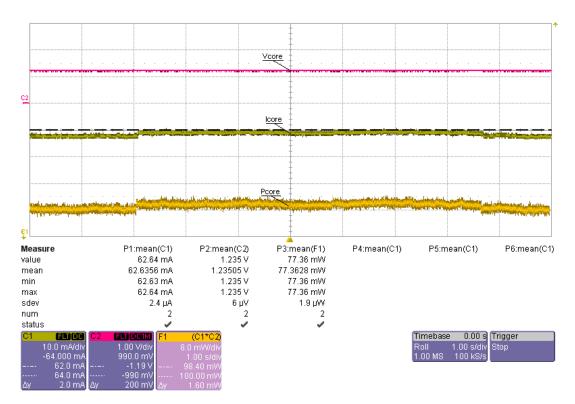

| 2.27 | Overall Power Drain                          | 50 |

List of Figures Page x

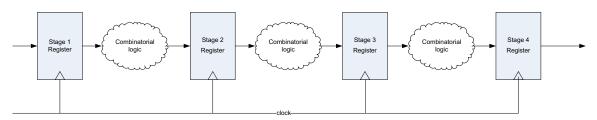

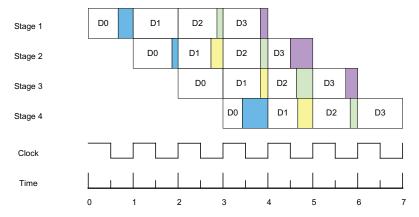

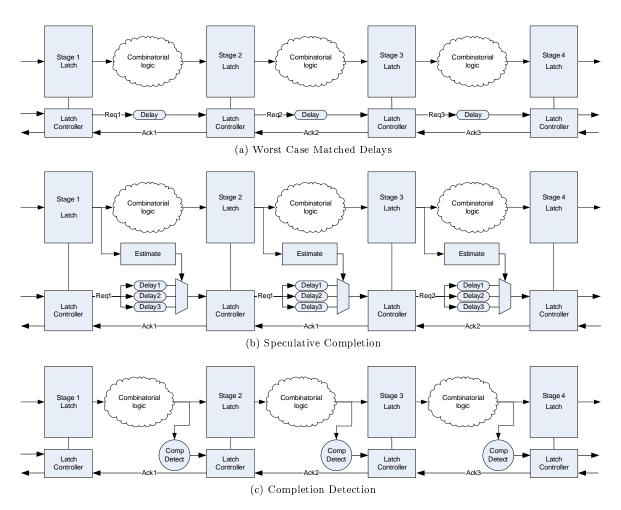

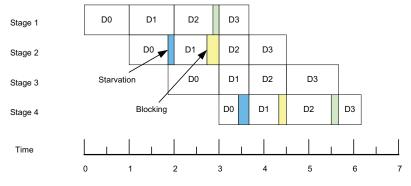

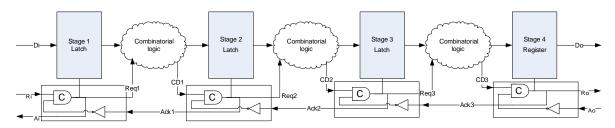

| 3.28 | 4 Stage Synchronous pipeline                | 59  |

|------|---------------------------------------------|-----|

| 3.29 | Synchronous Pipeline Occupancy              | 59  |

| 3.30 | 4 Stage Asynchronous Pipeline               | 60  |

| 3.31 | Asynchronous Pipeline Occupancy             | 61  |

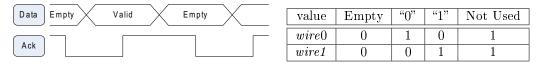

| 3.32 | Simple Dual-Rail Encoding                   | 62  |

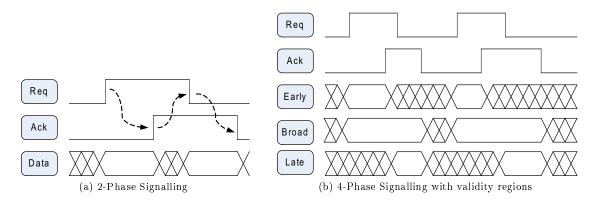

| 3.33 | Signalling and Validity Regions             | 64  |

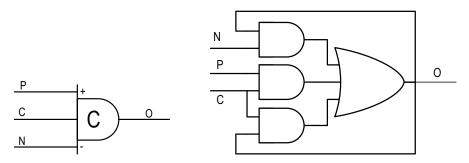

| 3.34 | Muller C-element                            | 66  |

| 3.35 | Half Latch Controller                       | 67  |

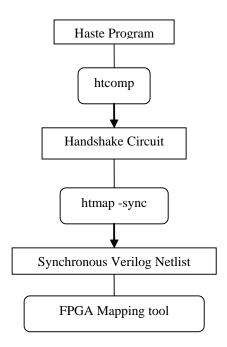

| 3.36 | Handshake Solutions Prototyping Design Flow | 69  |

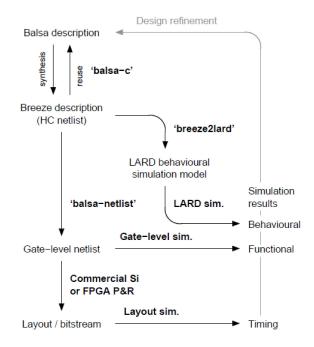

| 3.37 | Balsa Design Flow [25]                      | 70  |

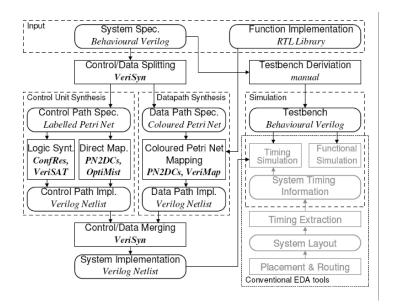

| 3.38 | BESST Design Flow [32]                      | 72  |

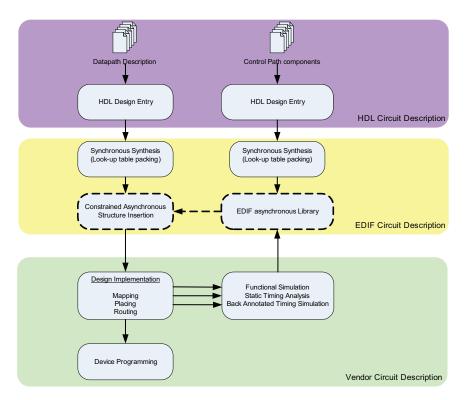

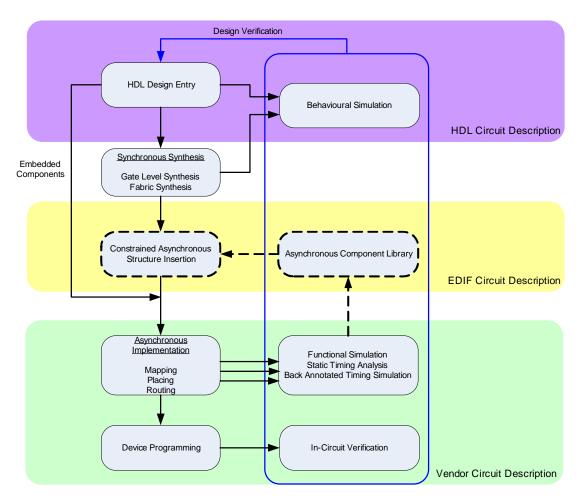

| 3.39 | Proposed Design Flow                        | 74  |

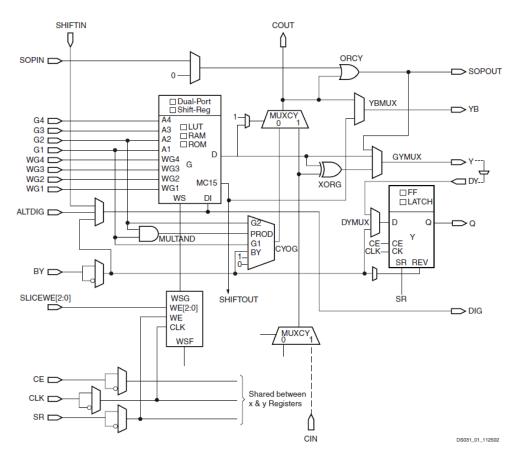

| 3.40 | Xilinx Slice Architecture [63]              | 75  |

| 3.41 | Delay Chain Variability Reductions          | 77  |

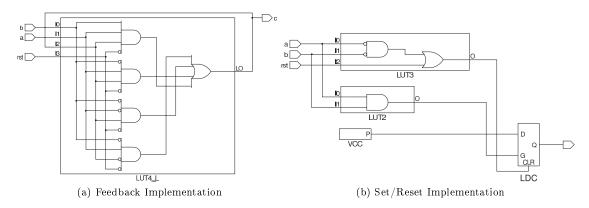

| 3.42 | Muller C-element FPGA Implementations       | 78  |

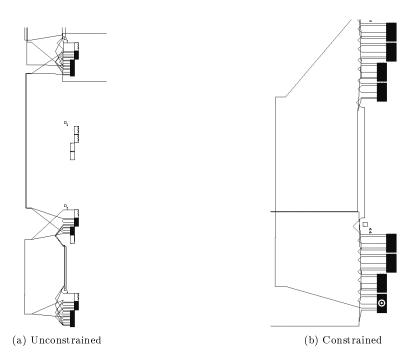

| 3.43 | Unconstrained Controller Routing            | 79  |

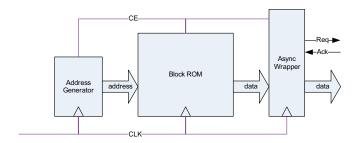

| 3.44 | ROM Wrapper Example                         | 81  |

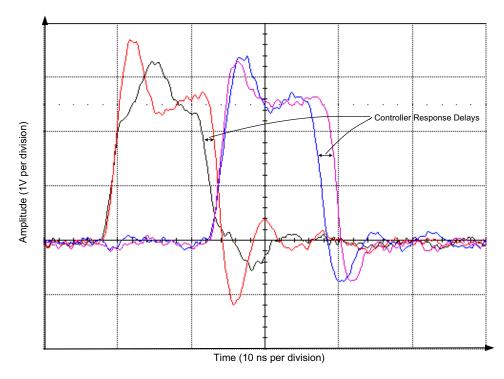

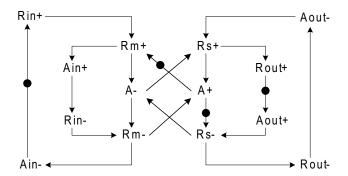

| 3.45 | Handshake Test Points                       | 82  |

| 3.46 | Back Annotated Waveform                     | 82  |

| 3.47 | Chipscope Waveform                          | 83  |

| 3.48 | Test Pin Outputs of Handshake Differentials | 84  |

| 3.49 | Delay Chain Comparison                      | 85  |

| 4.50 | FPGA Design Flow                            | 94  |

| 4.51 | EDIF Structure                              | 97  |

| 4.52 | UML Diagram of the EDIF Structure           | 99  |

| 4.53 | Flattened Linear Pipeline                   | 102 |

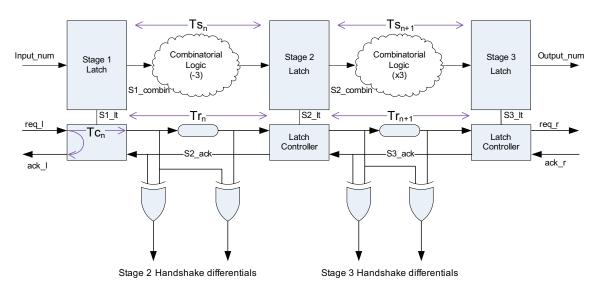

| 4.54 | Inserting Asynchronous Control Blocks       | 104 |

| 4.55 | Single Register Conversion with Feedback    | 105 |

| 4.56 | Register DFS connections                    | 107 |

| 4.57 | Register Depth First Search Algorithm       | 108 |

| 4.58 | EDIF Mapping Constraint                     | 110 |

| 4.59 | UCF Constraint Example                      | 110 |

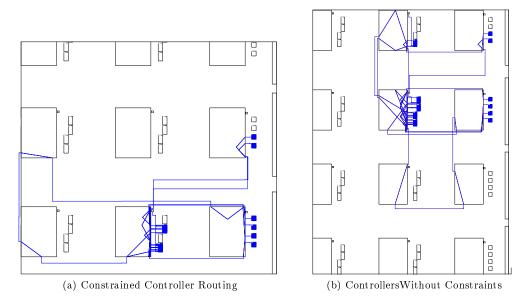

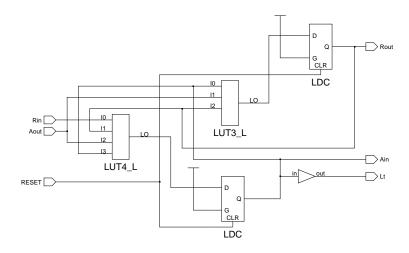

| 4.60 | Undecoupled Latch Controller                | 112 |

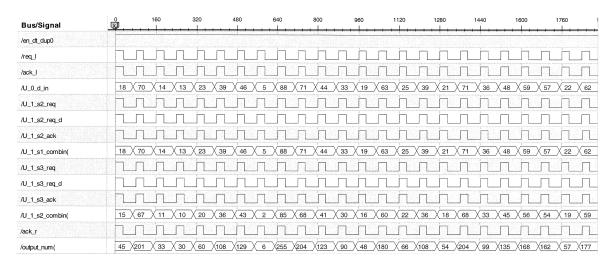

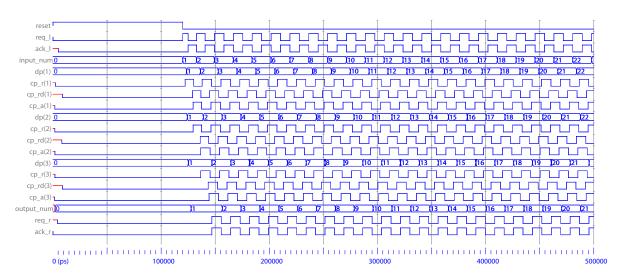

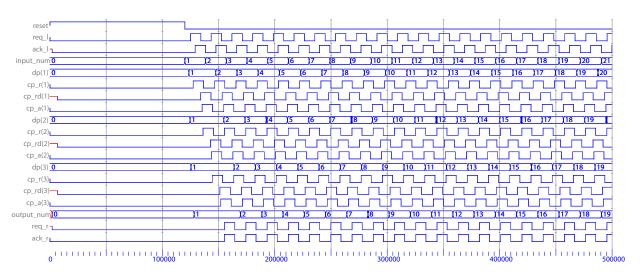

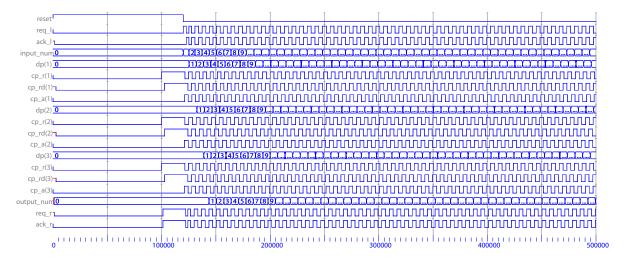

| 4.61 | Undecoupled Latch Controller Waveform       | 113 |

| 4.62 | Semi-Decoupled Latch Controller             | 114 |

List of Figures Page xi

| 4.63 | Semi Decoupled Latch Controller Waveform                 | 114 |

|------|----------------------------------------------------------|-----|

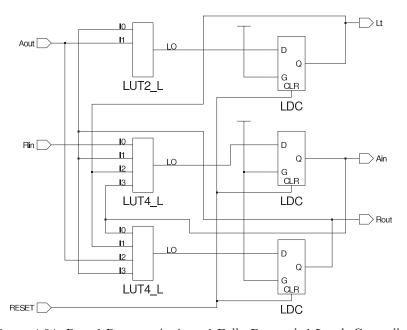

| 4.64 | Broad Request Activated Fully Decoupled Latch Controller | 115 |

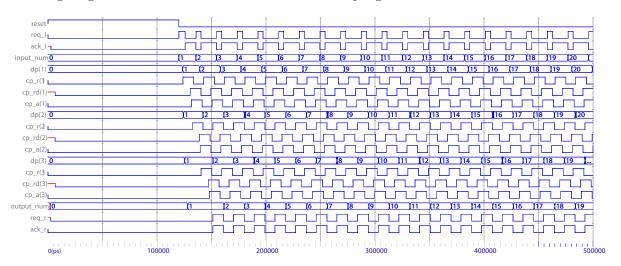

| 4.65 | BRF Latch Controller Waveform                            | 116 |

| 4.66 | Critical Arcs of the BRF Latch Controller                | 116 |

| 4.67 | Mousetrap Latch Controller                               | 117 |

| 4.68 | Mousetrap Latch Controller Waveform                      | 117 |

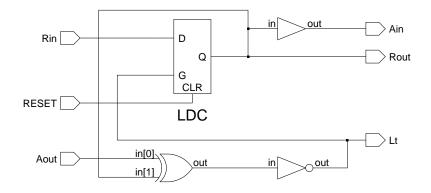

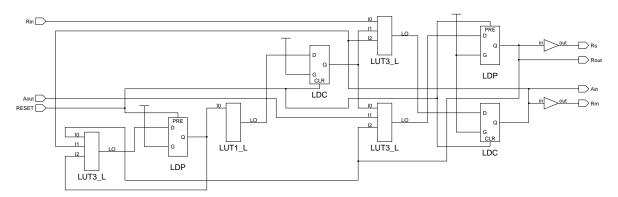

| 4.69 | AACIF Register Controller                                | 118 |

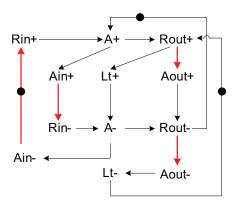

| 4.70 | AACIF Controller STG                                     | 119 |

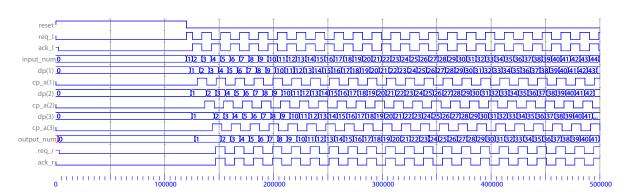

| 4.71 | AACIF Controller Waveform                                | 120 |

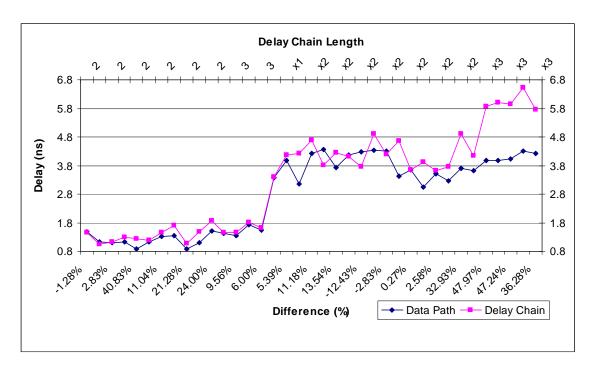

| 4.72 | Delay Chain Accuracy of 422 to 444 Circuit               | 122 |

| 4.73 | Delay Chain Accuracy of 444 to RGB Circuit               | 123 |

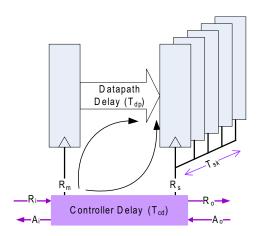

| 4.74 | Balancing Data Path and Controller Delay                 | 124 |

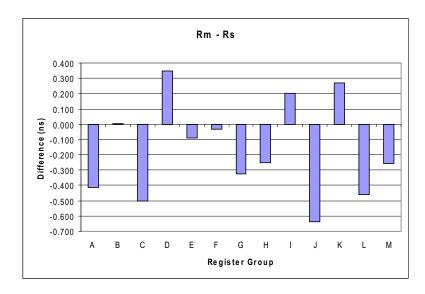

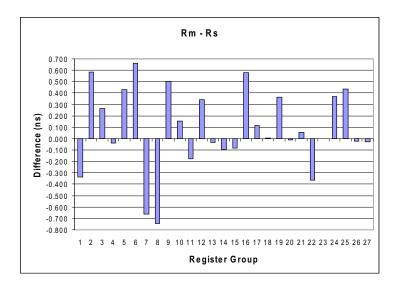

| 4.75 | Matching Clock Nets of 422 to 444 Circuit                | 125 |

| 4.76 | Matching Clock Nets of 444 to RGB Circuit                | 125 |

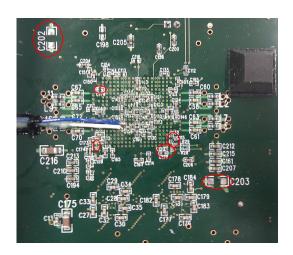

| 4.77 | Scope Probe with Decoupling Capacitors Removed           | 130 |

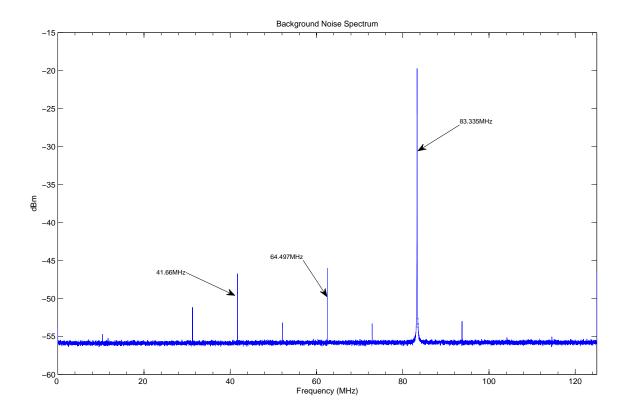

| 4.78 | Noise Spectrum of the Background                         | 131 |

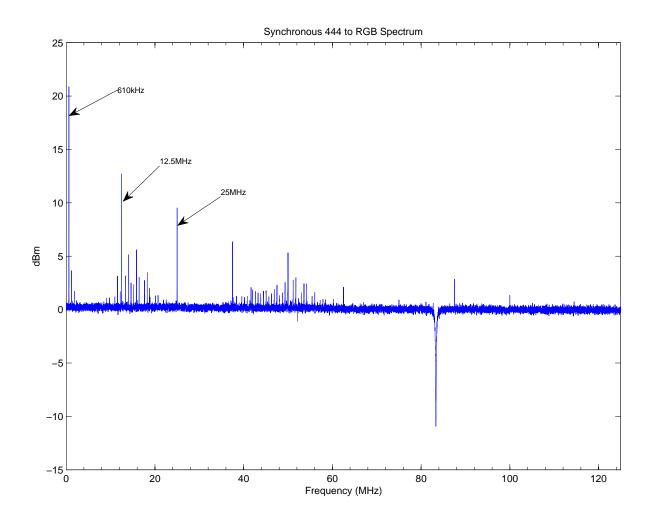

| 4.79 | 444 to RGB Circuit Noise                                 | 132 |

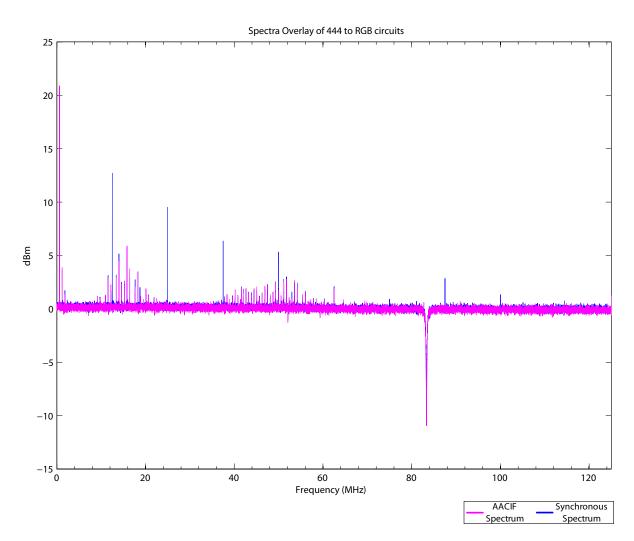

| 4.80 | 444 to RGB Circuits Noise Spectrum Overlay               | 133 |

| A.1  | Critical Path through Redistribution Block               | 145 |

| A.2  | Current Traces of Options 1 & 2                          | 146 |

| A.3  | Current Traces of Options 3 & 4                          | 147 |

| B.1  | VHDL Implementation of a Muller C-element                | 154 |

| B.2  | EDIF Implementation of a Muller C-element                | 155 |

| B.3  | VHDL Wrapper Implementation                              | 156 |

| C.1  | EDIF Muller C-element Description                        | 157 |

| C.2  | Expanded Waveforms                                       | 163 |

| C.3  | Board Setup                                              | 164 |

| C.4  | 422 to 444 Circuits Noise Spectrum Overlay               | 165 |

## List of Tables

| 1.1  | Technical Modules                                                                                  | 8   |

|------|----------------------------------------------------------------------------------------------------|-----|

| 1.2  | Business Modules                                                                                   | 9   |

| 2.3  | Redistribution Conditions 1, 2 & 4 $\dots$                                                         | 32  |

| 2.4  | Redistribution Condition $3$                                                                       | 32  |

| 2.5  | Device Utilisation                                                                                 | 44  |

| 2.6  | Histogram Parameter Summary                                                                        | 49  |

| 2.7  | Pipeline Xpower Consumption Estimate                                                               | 49  |

| 2.8  | Total Xpower Consumption Estimate                                                                  | 50  |

| 3.9  | 2-bit Data Channel Encoding Examples $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 63  |

| 4.10 | Controller Delays of the 422 to 444 circuit                                                        | 126 |

| 4.11 | Controller Delays of the 444 to RGB circuit                                                        | 127 |

| 4 12 | Resource Utilisation Comparison                                                                    | 128 |

### List of Abbreviations

AACIF Automated Asynchronous Circuits in FPGAs

API Application Programming Interface

ASIC Application Specific Integrated Circuit

CLAHE Contrast Limited Adaptive Histogram Equalisation

CLB Configurable Logic Block

CMOS Complementary Metal-Oxide Semiconductor

EDA Electronic Design Automation

EDIF Electronic Design Interchange Format

EM Electro Magnetic

FPGA Field Programmable Gate array

HDL Hardware Description Language

IP Intellectual Property

JTAG Joint Test Action Group

LED Light Emitting Diode

LUT Look-up Table

NAND Inverted logical AND gate

PCB Printed Circuit Board

RTEMS Real-Time Executive for Multiprocessor Systems

RTL Register-Transfer Level

${\bf SIMD~Single~Instruction~Multiple~Data}$

List of Tables Page xiv

STG Signal Transition Graph

UML Unified Modelling Language

VHDL VHSIC Hardware Description Language

VLIW Very Long Instruction Word

VLSI Very Large Scale Integration

### Part I

## Portfolio Introduction

### 1.1 Executive Summary

The objective of this engineering doctorate (EngD) research project, proposed in conjunction with the Institute of System Level Integration and Thales Optronics Ltd, was to investigate how asynchronous design techniques could be applied to FPGA designs for processing raw image detector data from electro-optical sensors. This potentially included the development of a methodology and practical implementation of the methodology on working hardware. The primary aim was to improve the implementation of FPGA designs by assessing the applicability of asynchronous design techniques to the processing of detector data.

This initial brief was designed to provide a large scope, allowing flexibility in the specific research direction. Although experts in producing optical sensors and imaging algorithms, Thales Optronics, due to the nature of their business environment, are inexperienced in state of the art design methodologies outwith the standard EDA practises that have a long history of reliable hardware implementations. The research methodology adopted involved looking at an advanced, state of the art imaging algorithm, suitable for use on a number of future product lines. Then an investigation into asynchronous circuit design on a FPGA device would determine the best approach to combine the two domains. The result being a methodology to evaluate the applicability to imaging algorithms. As a result there were three distinct areas of work undertaken.

The first major period of research was the design and implementation of a contrast enhancement algorithm. Contrast limited adaptive histogram equalisation (CLAHE) is a contrast enhancement algorithm that had the potential to be utilised in forthcoming projects within Thales Optronics. This provided an opportunity to become familiar with the FPGA design flow used in the company, investigate FPGA device architectures and assess their suitability for region based contrast enhancement algorithms. The novel implementation of the CLAHE algorithm was analysed and characterised in the context of design accuracy with respect to a golden reference model, FPGA resources utilisation, device timing and power consumption. These areas allow a summary of the key design factors to be formed for future projects and products.

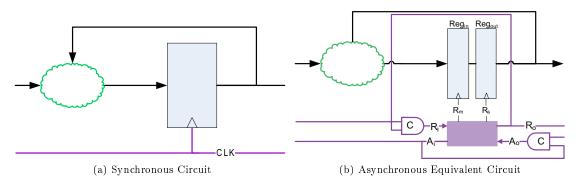

The second period of research initially involved investigations into design space of asynchronous logic. There are a number of different asynchronous design styles which exhibit characteristics dependent on the application. In recent times each branch of asynchronous logic has focused on a niche application, it was therefore important to determine the most suitable style for FPGA devices. Further to this an evaluation of design tools and methodologies was performed to determine existing methods of creating reliable asynchronous circuits. With each asynchronous design style came a series of tools from academic and industrial sources. Establishing their compatibility to current FPGA design flows and EDA standards was a critical in guiding the research direction. The main focus then turned to implementing a class of asynchronous circuits that use FPGA resources. This piece of research looked

into connecting the most primitive components available with the FPGA device to suit fundamental asynchronous behaviours. In doing so a design methodology was formed along with specific fabric level asynchronous structures and verification approaches. All of which integrated seamlessly into the conventional FPGA design flow.

The third major period of research moved into investigating the options on how to automate asynchronous circuits into the current FPGA design flow. A unique approach is presented which converts synchronous circuits to operate asynchronously. This approach maximises the compatibility of these circuits with existing EDA standards. The conversion focuses around the post-synthesis EDIF netlist. This process abstracts an EDIF netlist in the domain of graph theory using an object orientated approach to perform the conversion. There is a significant discussion on the stages of conversion including the constraints vital to the correct asynchronous circuit operation. A novel asynchronous controller specifically designed for FPGA devices is presented and compared. The analysis of this conversion process covers its timing accuracy and improvements, resource utilisation and power spectrum noise.

### 1.2 Portfolio Organisation

The introductory part of this portfolio thesis provides a context to the research period and the supporting work by the author. Firstly, the commercial context outlines what has motivated Thales Optronics Ltd to support the topics of research undertaken by the research engineer. The company has identified these topics as being beneficial to their future development. The second section details the external events that have been attended to publish research results and gain visibility within the wider research community as well as internal divisions of Thales Optronics Ltd. The third section discusses the taught elements to the EngD and external training course that have contributed to the success of this research. The taught business modules were of significant value within the industrial context, providing insight to the commercial forces around the EngD. The taught technical courses and external training provided a succinct technical context to guide the direction of research at a very early stage.

The core of this portfolio thesis is split into three technical reports that reflect the sub-projects there were undertaken during the period of research. The first report documents the research conducted investigated the use of region-based contrast enhancement within the current platforms used by Thales Optronics. The second report documents the investigations into establishing asynchronous circuits on FPGA devices. The third report presents an automated methodology to implement circuits asynchronously on FPGA devices. Each report contains individual aims and motivations as well as technical context and conclusions from for the research conducted.

The final part of this portfolio thesis summarises and concludes the contributions and novel as-

pects from each technical report and provides a direction for any future derivatives of this research.

Appendices and supporting material make up the remainder of this portfolio thesis.

#### 1.3 Commercial Relevance

Although this research provides novel technical contributions it must also be of value and commercial relevance to the sponsoring firm, Thales Optronics Ltd. This section will highlight the industrial value of the research and the commercial benefits it may bring in the future.

The first section of work on contrast enhancement produced an academically credible publication, but this project provided great value to the company in determining the FPGA resources required to implement such an algorithm on an embedded device. For thermal imaging cameras a large amount of effort is expended in determining algorithms that can enhance image quality and clarity. To this extent contrast enhancement methods are particularly important in minimising noise from an infrared photodetector and enhancing lower detail regions. FPGA devices are the choice at the heart of most thermal imaging cameras. Their configuration flexibility, performance and ability to service low volume manufacturing make them ideal to contain the required amount of corrective and enhancing image processing algorithms. Region based contrast enhancement algorithms (like CLAHE) show significant image quality benefits over image wide techniques, and so it was a logical conclusion for the firm to support the direction taken by the EngD research to investigate improving the current contrast enhancement algorithms with region based alternatives. This support could give the firm a key advantage over competitors in bringing products to market quicker. The research conducted in this area gives valid estimates on an industrial application of the same functionality. Non-recurring engineering costs are always targeted to minimise overall project costs, having a valid implementation that constitutes a more predictable element of a project massively reduces uncertainty and inevitably cost.

The second section of work on establishing asynchronous logic on FPGAs again has the potential to bring further savings and advantages to the the firm. Traditionally the large asynchronous design space has allowed for many niche applications to benefit from improved performance in terms of speed and power when utilising a particular asynchronous design style. These benefits have always been applied in the context of high-volume ASIC products. This research has identified the most appropriate method/framework that would allow low-volume FPGA products to assess these advantages within their own context. Applying various design styles to FPGA fabric could bring better performance to niche applications of the sponsoring firm. In a synchronous circuit implemented on an FPGA the clock network can consume a significant proportion of power required to operate the device. The drive current required to constantly switching an extensive clock network will affect the power supply design. The demands of many output pins switching altogether mean that printed circuit board designers need

to account for the high currents and cross coupling effects- all of which add the cost of designing an embedded system. Asynchronous systems average out power spikes as they have no clock and as a consequence this reduces supply variability which can reduce the cost of designing power supplies and PCBs. The speed of a synchronous circuits is governed by the slowest propagation delay between registers. In an asynchronous circuit the speed is governed by the average propagation delay between registers. Meaning that system latency can be significantly smaller than the synchronous equivalent. From a cost perspective, using a high speed grade device to sample input data very quickly could be replaced by a simple asynchronous circuit (with its average case performance) to sample input data just as quickly but with the benefit of using a lower speed grade device, which costs significantly less.

The third section of work on automated asynchronous circuits provides a unique ability to the firmware design capabilities of the firm. Automatically implementing circuits asynchronously on a synchronous FPGA device has a number of benefits the firm can leverage. Firstly designs do not need to learn asynchronous design techniques in order to operate circuits without a clock. This allows asynchronous benefits to be easily assessed against each circuit design. There may be applications that call for low EM noise from the PCB, response times where latency is the most important factor, power efficiency where there are limitations on the available current to operate a circuit or changeable environments that require circuits to be robust against single-event upsets and varying temperatures. All of these potential design scenarios may be instances where design implementation explorations reveals that an asynchronous design style maybe the best performing in that context. Providing the firm with the capability to assess the capability of asynchronous design styles with these design requirements is key competitive advantage. Although this a conversion flow, benefits are extracted further down the FPGA design flow. The novel aspect of this work is how the asynchronous circuits are implemented on the FPGA. Changing the behavioural description language to a dedicated asynchronous language or a modelling language could result would allow optimisation of different source languages to FPGA architectures. This low-level access to the FPGA fabric allows operations to be constructed with finer granularity, in the same manner that assembler code can be inserted into C-programs. This approach provides another potential competitive advantage, allowing circuit descriptions to make into products quicker (reducing time-to-market) or performing better than they normal would.

The commercial relevance of this work is very strong due to the industrial motivators for performing this research. This direction adds significant tangible value to the research described in this thesis as well as its novel contributions to knowledge. 1.4. External Events Page 6

#### 1.4 External Events

#### 1.4.1 Academic and Industrial Events

Throughout the period of research there were a number of events that provided welcome discussion and feedback on the work being undertaken. No attempt to contribute to these events was made, however the benefit came in networking opportunities and the ability to discuss and explain the directions of research. Since the (asynchronous) topic of research is significantly outwith the comfort zone of Thales Optronics Ltd, the opportunities provided by these events were significant.

#### 1.4.1.1 IEEE Symposium on Asynchronous Circuits and Systems

The symposium on asynchronous circuits and systems was attended between the 7th and 10th of April 2008. Although not presenting any papers, this symposium was of most value in being able to access, what is regarded as the latest research in asynchronous circuits. The symposium also acted as a networking opportunity to gain a number of peer contacts to question and query the direction of research. There were a few presentations that had commonalities with this line of research and provided an array of markers from which the research can be clearly defined. The most informative parts of this conference were the range of tools being used to design and verify asynchronous circuits on ASICs as well as the minimisation techniques used to reduce the number of asynchronous components that would explicitly limit the usage of asynchronous structures on FPGA devices.

#### 1.4.1.2 UK Asynchronous Forum

As part of maintaining connections made at the symposium for asynchronous circuits and systems, the 20th UK asynchronous forum was attended on the 1st of September 2008 to firstly discuss research ideas and secondly evaluate new ideas and concepts generated by the UK asynchronous research community. There are very few events that cater for the asynchronous design space and so this was a welcomed opportunity to discuss the research progress with an audience that are very familiar with region of interest this research occupies.

#### 1.4.1.3 Thales Group les Journée du Computing

The PhD computing day is an annual event held by the Computing Network of Excellence as part of the Software and Critical Information systems group in Palaiseu, France. This event was attended on the 16th of November 2011 and provided a concluding presentation of the work presented in this thesis to the sponsoring company. The goal of this event is to gather all the Thales Group PhD students working on computing research to share their research topics and recent progress, as well as their experience. This event was reasonably similar to the Asynchronous Forum, but with a 30

minute presentation and subsequent poster session, the finished work generated a significant amount of discussion and interest from various attendees.

#### 1.4.2 Conference Publications

Two contributions were given at major academic conferences. One involved a poster presentation and the other a full length 20 minute presentation slot, both contributions are accompanied by papers published in the conference proceedings for each event

#### 1.4.2.1 IEEE International System on a Chip Conference

Due to an accepted paper submission, 'Evaluation of contrast limited adaptive histogram equalization (CLAHE) enhancement on a FPGA' on contrast limited adaptive histogram equalisation, the international system on a chip conference was attended between the 15th and 20th of September 2008. The conference took place in Newport California and contained five days worth of paper and poster presentations, tutorials and discussions on many areas relevant to system on chip design- including image and video processing as well as a small asynchronous design tutorial. The paper was presented as a poster and received significant interest. There were a number of professional and academic organisations represented at this conference, presenting and discussing the latest topics of research and development. The networking and critical discussions at this conference were of great value to the direction of this research at that time.

#### 1.4.2.2 Euromicro Conference on Digital System Design

Another paper, 'Optimising Self-Timed FPGA Circuits' was accepted to the 13th Euromicro Conference on Digital System Design: Architectures, Methods and Tools in Lille, France, on the 1st to 3rd of September, 2010. This paper was specifically aimed at allowing the work around the design flow of AACIF circuits to be peer reviewed. The conference includes a number of topics within its scope, including system and circuit synthesis which aligns with the intentions of the paper. It focuses on advanced circuit and system design, design automation concepts, paradigms, methods and tools, as well as modern implementation technologies from full custom in nanometre technology nodes to FPGA and multicore infrastructures. As with the previous conference the event provided a good opportunity and discussion forum to seek feedback, different interpretations and impressions on the direction of research- all positive and beneficial.

### 1.5 Taught Modules and Training

As part of the EngD requirements, a total of 180 credits at Master's level are required. These are made up of 120 technical credits and 60 business and management credits. The technical modules

were sourced from the MSc in System Level Integration offered by the Institute for System Level Integration (ISLI) and Continuing Education in Electronics Systems Integration (CEESI). The business and management modules were sourced from the MBA programme of the University of Strathclyde Graduate School of Business (USGSB).

#### 1.5.1 Technical Modules

Out of the 120 MSc level technical credits required for the EngD course, 4 of them were taken in the first term of the MSc course from the ISLI, and 3 were taken in the second semester. The remaining came from the 3rd semester and external courses. Table 1.1 summarises the modules taken and their corresponding credit weightings. The most significant courses were:

| Subject                                    | Credits |

|--------------------------------------------|---------|

| Introduction to Hardware Design Automation | 8       |

| IP Block Authoring                         | 15      |

| Microcontrollers and Microprocessors       | 15      |

| VLSI Design                                | 15      |

| Embedded Software 1                        | 15      |

| Real Lift System Level Integration         | 8       |

| IP Block Integration                       | 15      |

| System Partitioning                        | 15      |

Table 1.1: Technical Modules

IP Block Authoring - provided a solid base in various design methodologies and discussed the attributes of the different classifications of I.P blocks. The main emphasis was on I.P. block re-use and power/speed/area evaluations.

Microcontrollers and Microprocessors - discussed design knowledge gained on instruction set architecture design. This also covered parallel and pipelined processor design with investigation into efficient cache architectures and brief coverage of VLIW and SIMD processor architectures.

VLSI Design - provided additional experience in fundamental CMOS circuit design, following the design flow from data path modelling and implementation down to the transistor layout design including automatic place and route techniques.

Embedded Software 1 - developed skills in embedded software construction, with extensive focus on DSP orientated data manipulation. This was tested with development of a responsive real time operating system embedded application using RTEMS.

IP Block Integration - provided hands on experience with hardware verification languages, Specman. The module covered simulation technologies with rapid prototyping, formal and timing verification tools. There was significant emphasis on design for test ability and test bench configuration.

System Partitioning - Increased awareness of modelling languages to aid system partitioning with a depth SpecC project. The module also covered models for computation and communication. The concise introduction to UML and the benefits from its features as a system specification language were highlighted from an object-orientated design perspective.

There was only one module that was taken outwith the MSc curriculum provided by the ISLI, 'Self-timed logic' provided by the University of Manchester on behalf of CEESI. This was a 16 week long distance learning course which will began in October 2008 and was worth 15 credits. This module was determined to be particularly useful in the context of the research brief provided by Thales Optronics Ltd. This module was taken by distance learning and provided a clear, concise insight and introduction into the asynchronous design space. The course covered a crucial number of topics that were of significant use in the latter part of the research, providing a preliminary understanding of asynchronous data and control protocols as well as asynchronous synthesis tools.

#### 1.5.2 Business Modules

The 60 business credits were obtained by completion of the classes listed in Table 1.2. Distance learning and part-time study was the most convenient and flexible method to undertake these classes whilst balancing the requirements of the technical research. The business modules provided an opportunity to look at the EngD from a theoretical commercial perspective. Although the EngD is minor in comparison to the activities within Thales Optronics Ltd as a business, considering the EngD in a business environment rather than a research perspective provided an insight into the support measures required.

The business modules also provided an understanding of the key performance indicators chosen by the business, the operations management that drive the internal procedures and the financial responsibilities that balance every decision throughout the company. As with all textbook interpretations, the real-life application of theoretical methodologies are always subject to commercial compromises. The subjects chosen (shown in Table 1.2) were very beneficial in allowing the technical requirements of the EngD to remain fully supported by the company whilst being unaffected by the commercial environment. Subjects such as Finance & Financial Management and Financial & Management Ac-

| Subject                             | Credits |

|-------------------------------------|---------|

| The Learning Manager                | 3       |

| Operations Management               | 12      |

| Marketing Management                | 12      |

| Financial and Management Accounting | 9       |

| Finance and Financial Management    | 12      |

| Making Decisions                    | 6       |

| Data Management                     | 6       |

Table 1.2: Business Modules

counting gave an insight into the costing practises, balance sheets, capital expenditure, and other financial topics which affect all engineering projects. These aspects are normally encompassed by project managers and purchasing departments but are rarely tackled by engineers on a wider scale than development work.

Operations Management showed businesses from a strategic perspective, outlining the operations function and how operations management acts to implement strategy by process design and improvement measures. This mechanism outlines how businesses judge their performance and quality of output. In Thales Optronics, primarily being a technology company, there is a strong operations influence on all aspects of the business. This class was a key insight into how the company transforms in adapting to market changes and optimising internal processes.

Marketing Management showed the importance of a customer-facing company. Technology-based companies tend to focus on producing advanced products because the technology is available and assume that the customer will follow. Understanding exactly what the customer needs and creating products to match those needs (as well as bettering the competition) is fundamental to a successful business. This class was particularly enlightening when considering the strategic marketing required by Thales Optronics Ltd to anticipate customer requirements 5 to 10 years in advance and predict how to meet those needs in that time frame. A substantial report was submitted for this class based upon the marketing activities for particular segment of Thales Optronics. This provided the first hand motivation to justify the direction of the research and development activities.

Making Decisions demonstrated the benefits of Multi-Criteria Decision Analysis (MCDA). A unique, methodical approach to decision making within a complex environment such as Thales Optronics Ltd. Decisions matter when an issue is sufficiently complex and detailed that there is conflict between criteria and the importance of criteria in the decision. In this situation a gut feel decision is not sufficient. The principle aim is to help decision makers identify preferred courses of action. This is achieved through the structuring of values and judgements from stakeholders who have influence/interest in the outcome of the decision. In the context of Thales Optronics, a parallel investigation was conducted, demonstrating MCDA on a decision required for the choice of software packages for engineering issue management. The conclusion of this investigation was another angle on the solution possibilities, a traceability document that justifies course of action from top level requirements and a support to the resultant action plan.

#### 1.5.3 Handshake Solutions TiDE Training

Following advice from an academic supervisor under the assumption that the tool of choice for implementing asynchronous structures in the near future would be supplied by Handshake Solutions, this 3-day course was attended between the 12th and 14th of November 2007. This course provided firstly, a very clear overview of the asynchronous design flow, TiDE (Timeless Design Environment) and an explanation of the requirements for a design language (Haste) to accurately represent asynchronous

circuits. Secondly, this course provided the first glimpse into the commercial design flow for creating asynchronous structures on an FPGA However it is important to note, that although this was the only commercially recognised asynchronous design flow it is not the only one in existence. There are a number of academic based asynchronous design flows in existence that automate different areas of the asynchronous design space.

## Part II

**Technical Reports**

## Technical Report 1:

# Region-Based Contrast Enhancement on a FPGA Platform

Author: Phillip David Ferguson

Academic Supervisors: Prof Tughrul Arslan, Univ. of Edinburgh

Dr Ahmet Erdogan, Univ. Of Edinburgh

Industrial Supervisor: Andrew Parmley, Thales Optronics Ltd

### 2.1 Aims and Introduction

The body of work contained in this Technical Report documents the initial period of research at Thales Optronics Ltd. The primary motivation for this research is based on an industrial need to improve the performance of image algorithms used in their products.

A primary element of these products is the contrast enhancement mechanism used to improve the clarity and definition of images from thermal imaging sensors. Previous contrast enhancement techniques have been based around computations that are applied to an entire image. This body of work evaluates the relative merits of using a region based contrast enhancement algorithm on a platform that is common to most imaging products from Thales Optronics Ltd - the field programmable gate array (FPGA). Region based contrast enhancement algorithms show significant image quality benefits over image wide techniques, and so it was a logical conclusion to assess the feasibility of suitable algorithms.

This work discusses the implementation considerations and performance limitations of CLAHE. In doing so the suitability of an FPGA for this type of contrast enhancement is analysed. At the time of writing there were no known FPGA implementations of region based contrast enhancement that evaluated the performance attributes of this type of contrast enhancement algorithm on an FPGA. This novel approach to implementing CLAHE provides the industrial benefit of trialling CLAHE on an FPGA device allowing the firm to surmise the hardware requirements for region based contrast enhancement algorithms.

### 2.2 Contrast Enhancement Background

Previous studies [12] have discussed simpler contrast enhancement algorithms within the same industrial context, however due to the superior image enhancement ability of CLAHE, these conclusions need to be reevaluated. The following sections document the considerations and implementations in exploring an FPGA implementation of CLAHE.

#### 2.2.1 Algorithm Developments

Contrast enhancement is familiar to most individuals through picture settings on their television or monitor. Changing this setting allows the contrast of an image to be adjusted to obtain better clarity and definition. This is achieved by scaling or offsetting the intensity values of the pixels so that the full range of the intensity values are used within the image. E.g. if each pixel has an 8-bit range from white to black of 255-0, an image may contain pixels values from 220-10. In this case, visually white may not be pure white and black my not be pure black. Adjusting the contrast setting scales the intensity values so that an image with a white equal to 220 now becomes an image with white equal

to 255. This scaling is a linear ramp with a particular gradient. The contrast setting on a monitor alters the gradient of this ramp that is applied to every pixel in the image.

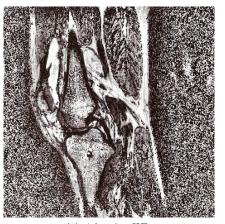

Histogram equalisation (HE) [1, 4] was initially developed to counteract the imbalance in pixel intensity created from computed tomography and magnetic resonance scanners to cathode ray tube display units. Previously a linear ramp had been used as a re-mapping function in a 1-to-1 pixel transform to improve the contrast of a given image. Histogram equalisation uses a non-linear ramp to provide an intensity level mapping that increases the output intensity level range dependent on the frequency distribution (a histogram) of the intensity levels within an image. This is accomplished by a cumulative distribution function to provide the re-mapping function which transforms the intensity values in an image such that the histogram intensity for a transformed image is constant. However the resultant image in some circumstances is worse than the equivalent image that had been enhanced using the linear ramp windowing method. This is due to large concentrations of background noise, creating peaks in the original histogram that once levelled out (see Figure 2.1) enhanced the visibility of background noise to the same levels as the image detail, thus losing minor local contrast changes.

(b) Histogram Equalisation Result

Figure 2.1: Histogram Equalisation Enhancements [15]

As HE uses the entire image to produce a re-mapping function, the next logical step was to minimise the size of the region with which the contrast enhancement was performed. Independent studies [9, 5, 3] of different variants began to explore the subtleties of balancing independent contrast regions. Creating an individual remapping function for a reduced region size creates an image where each region has been adaptively equalised. Adaptive histogram equalisation (AHE) improves overall image contrast for two reasons:

- Large peaks in background noise can be minimised to local regions, thus limiting the image wide noise enhancing effects.

- The human visual system adapts to the local context of images to evaluate the contents, as previously multiple linear ramps were applied to improve regions of interest in an image.

Splitting the image into contextual regions and then performing the remapping will inherently introduce visible contextual boundaries across the image. Thus a bilinear interpolation (discussed further in Section 2.3.3) is performed to remove these boundaries.

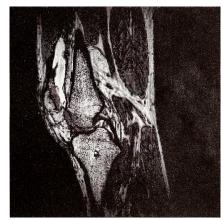

However now that important contextual regions can be enhanced with the benefits of histogram equalisation, the background regions of images, which are predominantly dark, suffer (shown in Figure 2.2) a dramatic enhancement in their noise content. To address this issue, spreading the histogram peaks over the entire contextual region removes any majority intensity and so reducing the intercontextual region contrast. Many methods [2, 13] have been devised to minimise this effect through a series of region weightings or modifications to the cumulative function.

(a) Adaptive HE

(b) Contrast limited AHE

Figure 2.2: Contrast Limiting Effects on AHE [15]

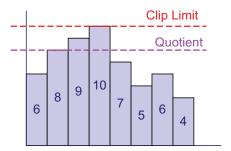

Contrast limited adaptive histogram equalisation (CLAHE) [9, 10] solves this inherent problem by limiting the contrast enhancement in homogeneous areas where grey levels are mostly constant. To accomplish this, CLAHE limits the maximum value a bin can hold in the image histogram. This has the cumulative effect of reducing the gradient of the re-mapping function. CLAHE analyses the image histogram and clips the offending bins to a maximum value. The excess of pixels creamed off the top of the histogram must be redistributed to maintain the total number of pixels in the histogram. The resulting transfer function restricts the output range of high concentration pixel intensities in the original histogram to their intended output range in the transformed image.

#### 2.2.2 Platform Developments

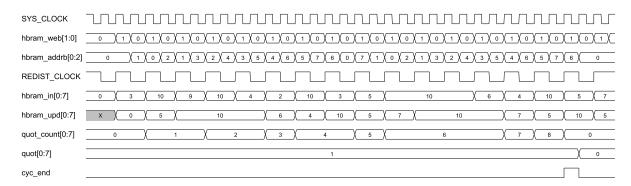

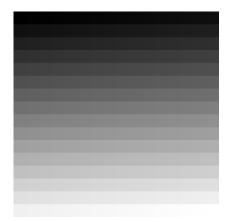

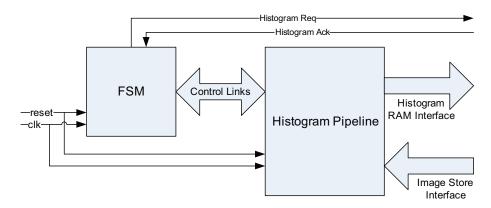

Currently implementations of CLAHE have mostly remained in the software domain. Pizer [9] initially performed operations on a VAX 11/780 using C or assembler as the implementation tool. This usually took around 2 minutes to complete with image sizes up to 512 x 512 pixels. The hardware of choice then moved to a dedicated multiprocessor machine, MAHEM [10], composed of 64 pixel processors that was able to reduce the run time of CLAHE to 4 seconds. Gauch [2] in 1992, used floating point