Moezi, Negin (2012) Statistical compact model strategies for nano CMOS transistors subject of atomic scale variability.

PhD thesis

http://theses.gla.ac.uk/3447/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# Statistical Compact Model Strategies for Nano CMOS Transistors Subject of Atomic Scale Variability

Negin Moezi

Submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in Electronics and Electrical Engineering

School of Engineering

College of Science and Engineering

University of Glasgow

February 2012

Copyright@Negin Moezi

#### **Abstract**

One of the major limiting factors of the CMOS device, circuit and system simulation in sub 100nm regimes is the statistical variability introduced by the discreteness of charge and granularity of matter. The statistical variability cannot be eliminated by tuning the layout or by tightening fabrication process control. Since the compact models are the key bridge between technology and design, it is necessary to transfer reliably the MOSFET statistical variability information into compact models to facilitate variability aware design practice.

The aim of this project is the development of a statistical extraction methodology essential to capture statistical variability with optimum set of parameters particularly in industry standard compact model BSIM. This task is accomplished by using a detailed study on the sensitivity analysis of the transistor current in respect to key parameters in compact model in combination with error analysis of the fitted I<sub>d</sub>-V<sub>g</sub> characteristics. The key point in the developed direct statistical compact model strategy is that the impacts of statistical variability can be captured in device characteristics by tuning a limited number of parameters and keeping the values for remaining major set equal to their default values obtained from the "uniform" MOSFET compact model extraction. However, the statistical compact model extraction strategies will accurately represent the distribution and correlation of the electrical MOSFET figures of merit. Statistical compact model parameters are generated using statistical parameter generation techniques such as uncorrelated parameter distributions, principal component analysis and nonlinear power method. The accuracy of these methods is evaluated in comparison with the results obtained from 'atomistic' simulations. The impact of the correlations in the compact model parameters has been analyzed along with the corresponding transistor figures of merit. The accuracy of the circuit simulations with different statistical compact model libraries has been studied. Moreover, the impact of the MOSFET width/length on the statistical trend of the optimum set of statistical compact model parameters and electrical figures of merit has been analyzed with two methods to capture geometry dependencies in proposed statistical models.

## Acknowledgment

I would like to take the opportunity to express my gratitude towards all the people who have assisted me in this work. Truly, finishing this PhD has been a milestone in my life and it has not been possible without their support. First and foremost, I would like to thank my supervisor Prof. Asen Asenov for his great ideas, countless suggestions, valuable comments and encouragements throughout this study. My second supervisor, Dr. Scott Roy devoted a lot of time and patience to the reading and correction of this thesis. My sincere thanks go to other members of Device Modelling Group at Glasgow University for their fruitful suggestions, among them I owe too much to Dr.Binjie Cheng for day to day discussions and progress of my research. Last but not least, I thank my parents and my beloved spouse for their endless support.

#### **Publications:**

- B. Cheng, N. Moezi, D. Dideban, G. Roy, S. Roy and A. Asenov, "Benchmarking the Accuracy of PCA Generated Statistical Compact Model Parameters Against Physical Device Simulation and Directly Extracted Statistical Parameters", in Proc. Simulation of Semiconductor Processes and Devices, Sept. 9-11, 2009, pp. 143– 146.

- U. Kovac, D. Dideban, B. Cheng, N. Moezi, G. Roy and A. Asenov, "A Novel Approach to the Statistical Generation of Non-normal Distributed PSP Compact Model Parameters using a Nonlinear Power Method", in Proc. Simulation of Semiconductor Processes and Devices (SISPAD), Bologna, Italy, Sept. 6-8, 2010, pp. 125–128.

- N. A. Kamsani, B. Cheng, C. Millar, N. Moezi, X. Wang, S. Roy and A. Asenov, "Impact of Slew Rate Definition on the Accuracy of nanoCMOS Inverter Timing Simulations", in Proc. Ultimate Integration on Silicon, Glasgow, Scotland, UK, Mar. 17-19, 2010.

- D. Dideban, B. Cheng, N. Moezi, N. A. Kamsani, C. Millar, S. Roy and A. Asenov, "Impact of Input Slew Rate on Statistical Timing and Power Dissipation Variability in nano CMOS", in Proc. Ultimate Integration on Silicon, Glasgow, Scotland, UK, pp. 45–48, Mar. 17-19, 2010.

- D. Dideban, B. Cheng, N. Moezi, X. Wang and A. Asenov, "Evaluation of 35nm MOSFET Capacitance Components in PSP Compact Model", *ICEE2010*, Isfahan, Iran, May 11-13, 2010.

Publications

B. Cheng, N. Moezi, D. Dideban, C. Millar, S. Roy and A. Asenov, "Impact of Statistical Parameter Set Selection on Accuracy of Statistical Compact Modeling", MOS-AK Workshop, Sapienza Università di Roma, Apr. 8-9, 2010.

- B. Cheng, D. Dideban, N. Moezi, C. Millar, G. Roy, X. Wang, S. Roy and A. Asenov, "Capturing Intrinsic Parameter Fluctuations using the PSP Compact Model", in Proc. Design, Automation and Test in Europe, Dresden, Germany, pp. 650–653, Mar. 8-12, 2010.

- 8. B. Cheng, D. Dideban, **N. Moezi**, C. Millar, G. Roy, X. Wang, S. Roy and A. Asenov, "Statistical Variability Compact Modelling Strategies for BSIM4 and PSP", *IEEE Design and Test of Computers*, Vol. 27, No. 2, pp. 26–35, Mar./Apr. 2010.

- 9. A. Asenov, B. Cheng, D. Dideban, U. Kovac, N. Moezi, C. Millar, G. Roy, A. Brown and S. Roy, "Modelling and Simulation of Transistor and Circuit Variability and Reliability", *Custom Integrated Circuit Conference*, San Jose, California, Sept. 19-22, 2010.

- 10. S. Markov, X. Wang, **N. Moezi** and A. Asenov, "Drain Current Collapse in Nano-Scaled Bulk MOSFETs Due to Random Dopant Compensation in the Source/Drain Extensions", *IEEE transaction on Electron Device*, VOL. 58, NO. 8, August 2011.

#### **Accepted:**

11. **N. Moezi**, D. Dideban, B. Cheng, S. Roy and A. Asenov, "Impact of Statistical Parameter Set Selection on the Statistical Compact Model Accuracy: BSIM4 and PSP Case Study", *Accepted for publication in Microelectronics Journal*.

# **Contents**

| 1 | Intr | roduction                            | 1  |

|---|------|--------------------------------------|----|

|   | 1.1  | Aims and Objectives                  | 4  |

|   | 1.2  | Outline                              | 5  |

|   |      |                                      |    |

| 2 | Back | kground                              | 6  |

|   | 2.1  | Clasification of Variability         | 9  |

|   | 2.2  | Statistical Variability in Nano-CMOS | 10 |

|   |      | 2.2.1 Random Discrete Dopants        | 14 |

|   |      | 2.2.2 Line Edge Roughness            | 11 |

|   |      | 2.2.3 Oxide Thickness Variations     | 13 |

|   |      | 2.2.4 High-κ Granularity             | 13 |

|   |      | 2.2.5 Poly/Metal Gate Granularity    | 14 |

|   |      |                                      |    |

|   | 2.3  | Phyical Simulation of Statistical Variability                        | 15 |

|---|------|----------------------------------------------------------------------|----|

|   |      | 2.3.1 Drift Diffusion Simulation                                     | 16 |

|   |      | 2.3.2 Important of Statistical Variability into Atomistic Simulator. | 17 |

|   | 2.4  | Effects of Variability in Device/Circuit                             | 18 |

|   | 2.5  | Review of Statistical MOSFET Models                                  | 21 |

|   | 2.6  | Summary                                                              | 24 |

|   |      |                                                                      |    |

| 3 | Unif | form Device BSIM4 Parameter Extraction and Optimization              | 25 |

|   | 3.1  | BSIM4 Compact Models                                                 | 26 |

|   |      | 3.1.1 Gate Dielectric Model                                          | 27 |

|   |      | 3.1.2 Effective DC and AC Channel Length and Width                   | 28 |

|   |      | 3.1.3 Threshold Voltage Model                                        | 31 |

|   |      | 3.1.4 Channel Charge Model                                           | 36 |

|   |      | 3.1.5 Mobility Model                                                 | 38 |

|   |      | 3.1.6 Source/Drain Resistance Model                                  | 40 |

|   |      | 3.1.7 Drain Current Model                                            | 42 |

|   | 3.2  | Template MOSFET                                                      | 46 |

vi

|   | 3.3   | Parameter Extraction and Optimization Methodology                | .48 |

|---|-------|------------------------------------------------------------------|-----|

|   | 3.4   | Summary                                                          | .55 |

| 4 | Stat  | istical Compact Model Extraction                                 | 56  |

|   | 4.1   | Simulation of Statistical Variability                            | .57 |

|   | 4.2   | Statistical Set of BSIM Parameters                               | .61 |

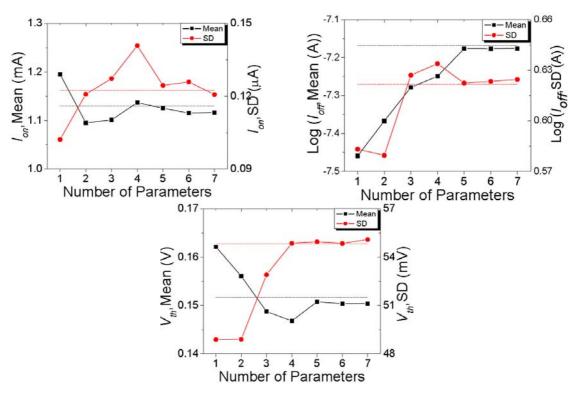

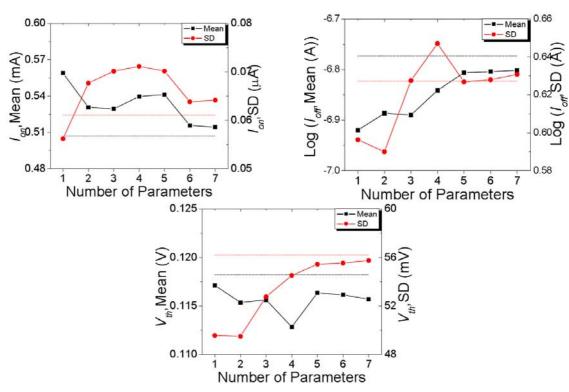

|   |       | 4.2.1 Impact of Parameter Set on the Accuracy of Individ         | ua  |

|   |       | Device                                                           | .64 |

|   |       | 4.2.2 Impact of Parameter Set on the Statistical Property        | of  |

|   |       | Device Figures of Merit.                                         | .69 |

|   |       | 4.2.3 Impact of Parameter Set on Statistical Circuit Simulation. | .74 |

|   | 4.3   | Accuracy of Full Parameter Set Extraction                        | .77 |

|   | 4.4   | Summary                                                          | .81 |

| 5 | Stati | istical Compact Model Parameter Generation Techniques            | 82  |

|   | 5.1   | Correlation of BSIM Parameters in Direct Statistical Parameter   |     |

|   |       | Extraction Strategy                                              | 84  |

|   | 5.2   | Statistical Parameter Generation Based on the Naïve Approach     | 20  |

| 5.3   | Statistical Parameter Generation Based on the PCA Approach                                                     | 91                                                                         |

|-------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 5.4   | MOSFET Figures of Merit Obtained from Statistical Parameter<br>Generation.                                     | .95                                                                        |

| 5.5   | Impact of Statistical Compact Modelling Generation Approache<br>on the Accuracy of Circuit Simulation          |                                                                            |

| 5.6   | Statistical Parameter Generation Based on the Nonlinear Power  Method                                          | r                                                                          |

| 5.7   | Summary                                                                                                        | 112                                                                        |

| Stati | stical Effect of Device Geometry on Statistical Dev                                                            | vice                                                                       |

| Cha   | racteristics                                                                                                   | 114                                                                        |

| 6.1   | Effect of Width on Variability                                                                                 | 114                                                                        |

|       | 6.1.1 Parallel Component Approach                                                                              | 115                                                                        |

|       | 6.1.2 Full Statistical Atomistic Simulation Approach                                                           | 119                                                                        |

|       | 6.1.3 MOSFET Figures ofMerit:Comparison of Parallel Compor<br>Component Approach and Full Atomistic Simulation |                                                                            |

|       | 6.1.4 Compact Model Parameter Extraction as a Function of Dev                                                  |                                                                            |

| 6.2   | Impact of Gate Length on Variability                                                                           | 131                                                                        |

|       | 6.2.1 Statistical Atomistic Simulation                                                                         | 132                                                                        |

|       | 5.4 5.5 5.6 5.7 Stati Char 6.1                                                                                 | 5.4 MOSFET Figures of Merit Obtained from Statistical Parameter Generation |

| CONTENTS | viii |

|----------|------|

|          |      |

|     |              | 6.2.2 Trends in Figures of Merit versus Gate Length | 133 |

|-----|--------------|-----------------------------------------------------|-----|

|     |              | 6.2.3 Parameter Extraction Trend versus Length      | 136 |

|     | 6.3          | Summary                                             | 136 |

| 7   | Cone         | clusion                                             | 138 |

|     | 7.1          | Summary of Results                                  | 138 |

|     | 7.2          | Future Work                                         | 142 |

| Ap  | pendi        | X                                                   | 144 |

| Bib | Bibliography |                                                     | 154 |

# **List of Figures**

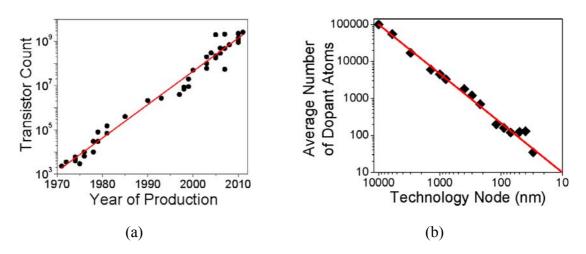

| 2.1 | Two manifests of MOSFET scaling: (a) Microprocessor             |

|-----|-----------------------------------------------------------------|

|     | transistor counts from 1971 to 2011, after [21], (b) Reduction  |

|     | in the average number of dopant atoms per technology            |

|     | generation, after [22]                                          |

|     |                                                                 |

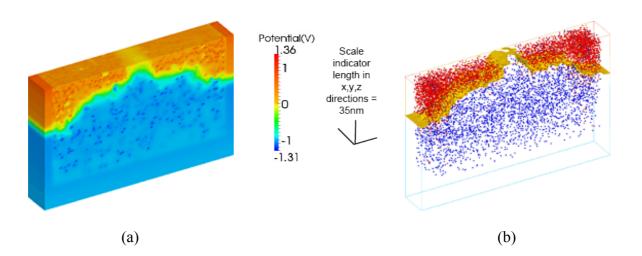

| 2.2 | Typical atomistic discrete dopant distribution inside a 35nm    |

|     | gate length MOSFET: (a) Potential distribution (positive        |

|     | potentials in source and drain are shown by orange and          |

|     | negative potential region in the bulk is shown by blue color)   |

|     | (b) Yellow color indicates the P-N junction and dopant          |

|     | positions are shown with bubbles (Red: Donors in source/drain   |

|     | Blue: Acceptors in bulk), used with permission from [47]        |

|     |                                                                 |

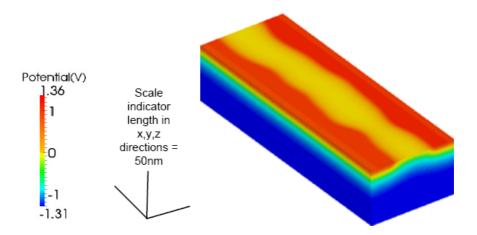

| 2.3 | The LER in a 50nm×200nm MOSFET. Red color shows the             |

|     | source/drain area with high potential and the blue color        |

|     | indicates the low potential in the bulk. Yellow illustrates the |

|     | potential area in the channel and depletion regions, used with  |

|     | permission from [58]                                            |

List of Figures x

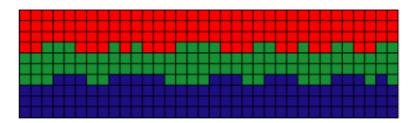

| 2.4 | The interface between gate, oxide and Silicon in an atomic                                                                                                                         |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | layer abstraction. The red, green and blue colors indicate                                                                                                                         |

|     | atomic layers in poly-silicon gate, oxide and silicon,                                                                                                                             |

|     | respectively. The fluctuations in the oxide thickness are clearly                                                                                                                  |

|     | shown, used with permission from [46]                                                                                                                                              |

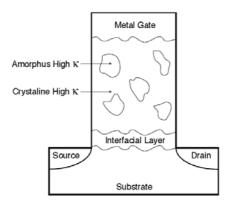

|     | The gate stack of a nano-CMOS using high-κ dielectrics and polycrystalline of high- which leads to vary dielectric thickness in each point of gate, used with permission from [46] |

|     | SEM micrograph of (a) poly-silicon and (b) metal gates, used with permission from [70]                                                                                             |

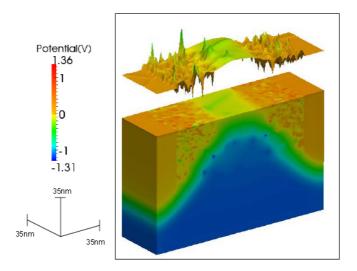

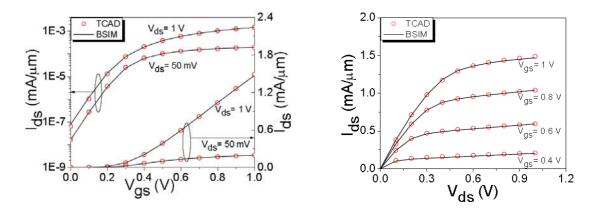

|     | Potential profile in a 35nm physical gate length device with RDD, LER and PGG, the numbers shown on the color bar indicate the electric potential in Volts.                        |

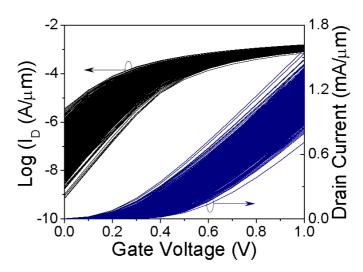

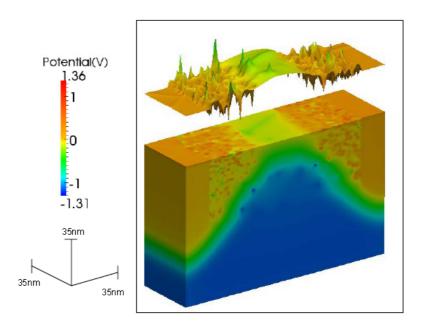

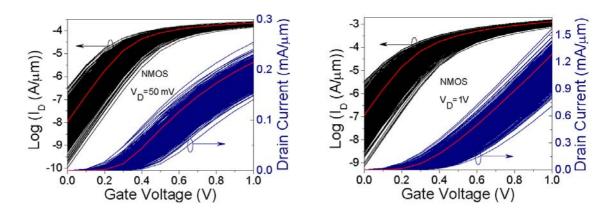

|     | The $I_D$ - $V_G$ characteristics of 1000 MOSFETs with 35nm gate lengths, obtained by Glasgow university atomistic simulator                                                       |

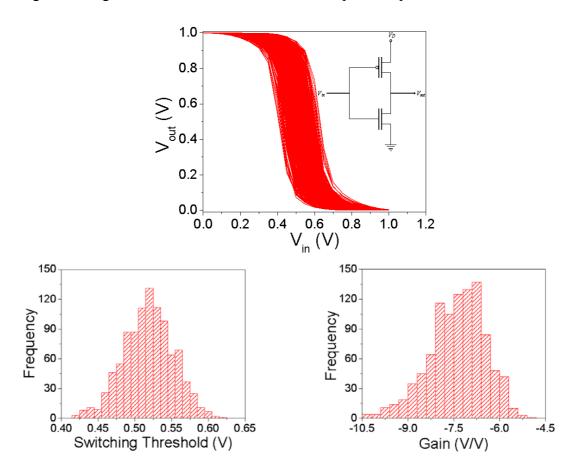

|     | The CMOS inverter transfer characteristic variations and distributions of the switching threshold and gain induced by RDD, LER and PGG                                             |

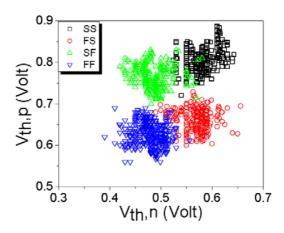

|     | Simulation of 200 p- and n-MOS transistors in 90nm process corners, after [36]                                                                                                     |

List of Figures xi

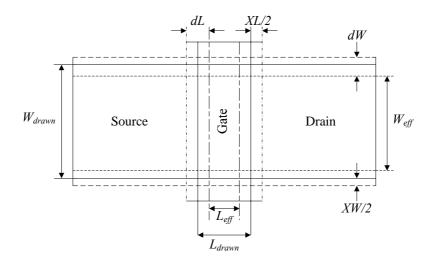

| 3.1 | Definition of $XL$ , $XW$ , $dW$ , $dL$ , $W_{eff}$ and $L_{eff}$                                                                                                                                                                                                                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

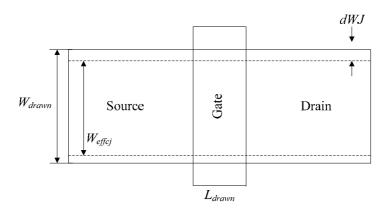

| 3.2 | Definitions of $DWJ$ and $W_{effcj}$                                                                                                                                                                                                                                                                               |

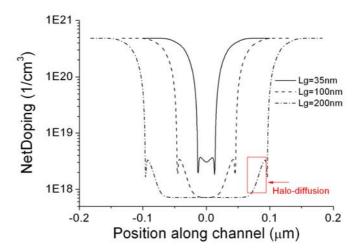

| 3.3 | Doping profile along the channel in a 35nm, 100nm and 200nm N-MOSFET with halo implantation from [108]                                                                                                                                                                                                             |

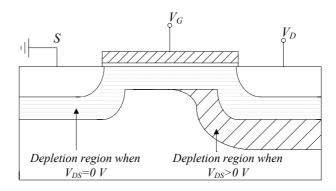

| 3.4 | Depletion layer thickness modulation caused by applied $V_{DS}$                                                                                                                                                                                                                                                    |

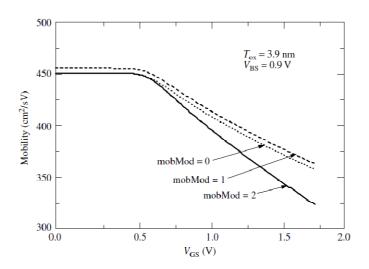

| 3.5 | $V_{GS}$ dependence of mobility behavior to different mobMod options from [105]                                                                                                                                                                                                                                    |

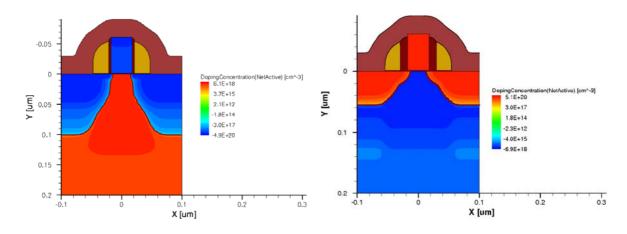

| 3.6 | p-MOSFET (left) 35nm; n-MOSFET (right) 35nm deviced doping profile simulated using Sentaurus based on the standard modern process flow. These devices are enhanced with strain engineering to match the performance of 45nm technology generation counterparts. The areas adjacent to the gate are called spacers. |

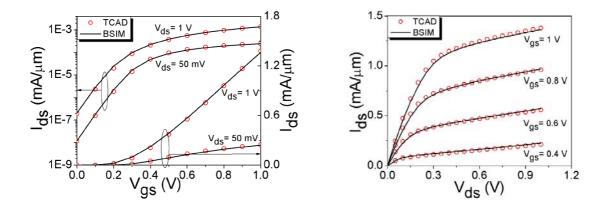

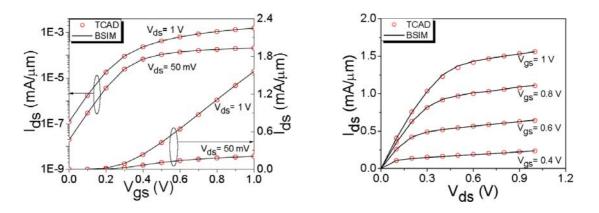

| 3.7 | Device $I_D$ - $V_G$ and $I_D$ - $V_D$ characteristic comparison between TCAD simulation and BSIM4 compact model extraction results for 30nm n-MOSFET                                                                                                                                                              |

| 3.8 | Device $I_D$ - $V_G$ and $I_D$ - $V_D$ characteristic comparison between TCAD simulation and BSIM4 compact model extraction results for 35nm n-MOSFET which was shown in Figure 3.6                                                                                                                                |

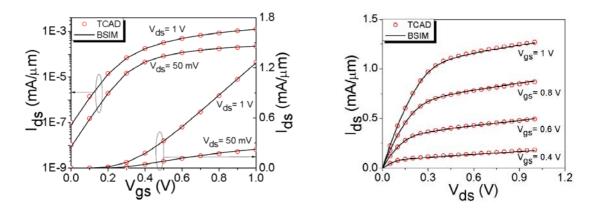

| 3.9 | Device $I_D$ - $V_G$ and $I_D$ - $V_D$ characteristic comparison between TCAD simulation and BSIM4 compact model extraction                                                                                                                                                                                        |

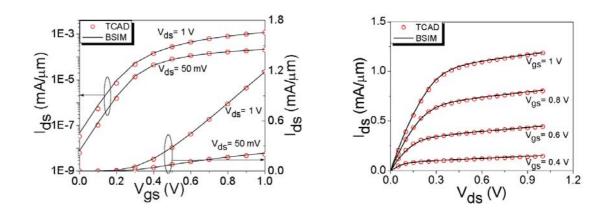

|      | results for 40nm n-MOSFET5                                               |

|------|--------------------------------------------------------------------------|

| 3.10 | Device $I_D$ - $V_G$ and $I_D$ - $V_D$ characteristic comparison between |

|      | TCAD simulation and BSIM4 compact model extraction                       |

|      | results for 14nm n-MOSFET                                                |

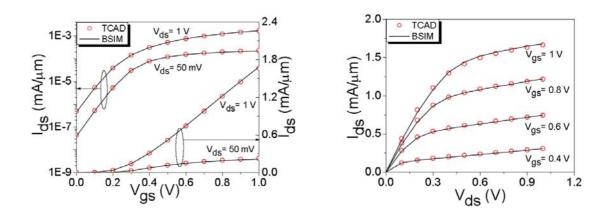

| 3.11 | Device $I_D$ - $V_G$ and $I_D$ - $V_D$ characteristic comparison between |

|      | TCAD simulation and BSIM4 compact model extraction                       |

|      | results for 18nm n-MOSFET                                                |

| 3.12 | Device $I_D$ - $V_G$ and $I_D$ - $V_D$ characteristic comparison between |

|      | TCAD simulation and BSIM4 compact model extraction                       |

|      | results for 22nm n-MOSFET                                                |

|      |                                                                          |

|      |                                                                          |

| 4 1  | Potential distribution in a 35nm n-MOSFET subject to source              |

|      | of variability. The drain bias is 1V                                     |

|      | of variability. The drain bias is 1 v                                    |

| 4.2  | Variability in the current voltage characteristics of a statistical      |

|      | sample of 1000 microscopically different 35nm gate length                |

|      | square $(W = L)$ n-NMOSFETs at $V_D = 50  mV$ and $V_D = 1V$ . Rec       |

|      | line shows characteristic of uniform device                              |

|      |                                                                          |

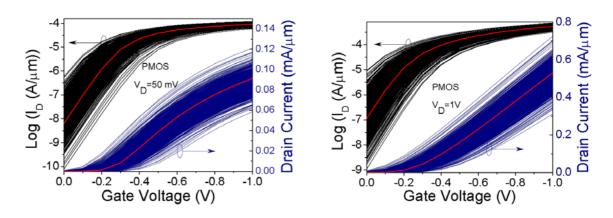

| 4.3  | Variability in the current voltage characteristics of a statistical      |

|      | sample of 1000 microscopically different 35nm gate length                |

|      | square $(W = L)$ p-MOSFETs at $V_D = 50  mV$ and $V_D = 1V$ . Rec        |

|      | line shows characteristic of uniform device                              |

List of Figures xiii

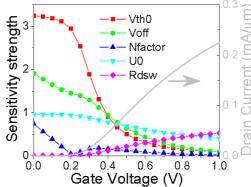

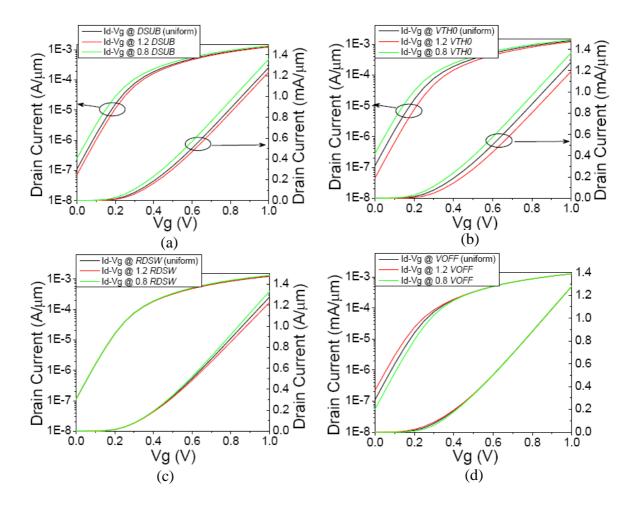

| 4.4  | The sensitivity strength of BSIM parameters as a function of                                                                                               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | gate voltage, low drain bias $(V_D = 50  mV)$                                                                                                              |

| 4.5  | The sensitivity strength of BSIM parameters as a function of                                                                                               |

|      | gate voltage under high drain bias $(V_D = 1V)$                                                                                                            |

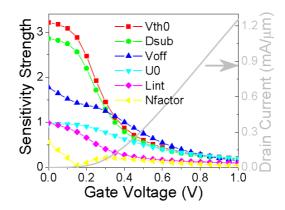

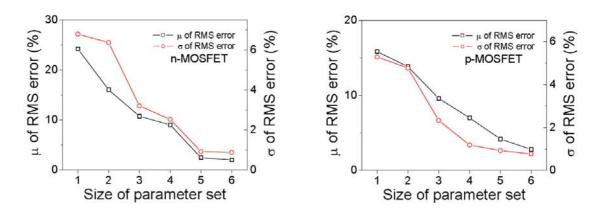

| 4.6  | The impact of statistical parameter set size on relative RMS                                                                                               |

|      | error of a statistical compact model. (Left) n-MOSFET and                                                                                                  |

|      | (Right) p-MOSFET. The parameters are selected based on the                                                                                                 |

|      | order presented in Table 4.1                                                                                                                               |

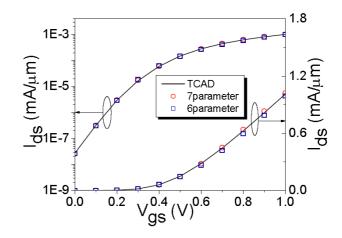

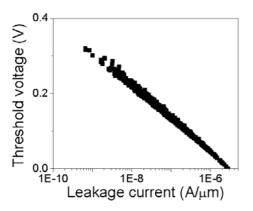

| 4.7  | Device $I_D$ - $V_G$ characteristic (high drain condition) comparison between TCAD simulation and BSIM4 compact model extraction results for 35nm n-MOSFET |

|      | CALIACTION TESURES FOR SOME IN-INTO ST LT                                                                                                                  |

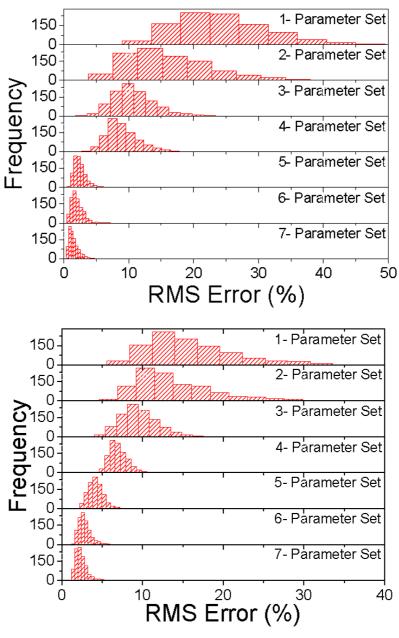

| 4.8  | The impact of statistical parameter set size on relative RMS                                                                                               |

|      | error of BSIM statistical compact model. (Up) n-MOSFET and                                                                                                 |

|      | (Down) p-MOSFET67                                                                                                                                          |

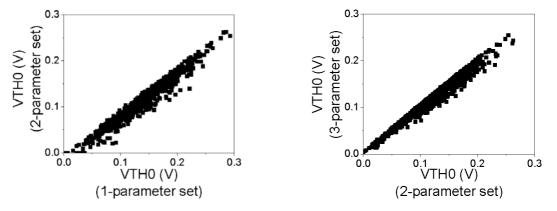

| 4.9  | The correlation between the same parameter at different parameter sets                                                                                     |

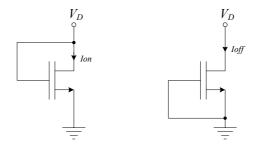

| 4.10 | A simple circuit for description of the $I_{on}$ and $I_{off}$                                                                                             |

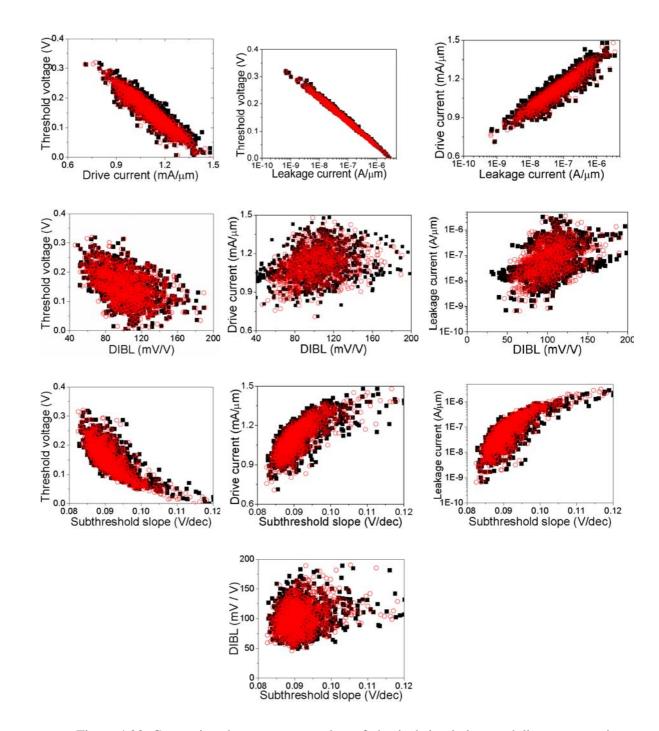

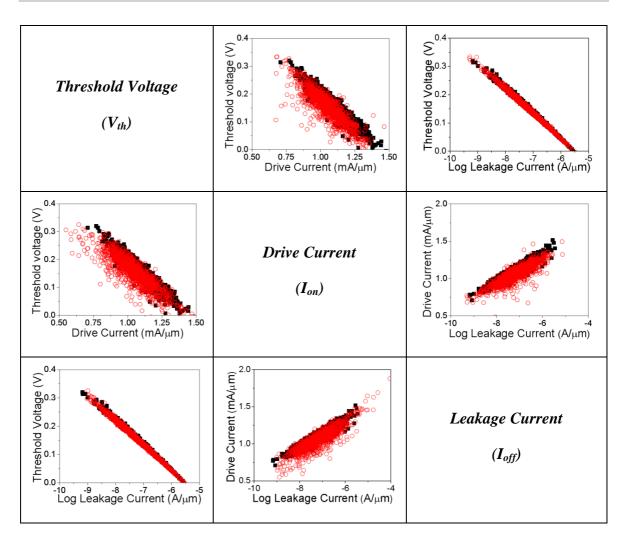

| 4.11 | The correlation between typical electrical figures of merit for a                                                                                          |

|      | statistical sample of 1000 microscopically different, 35nm gate                                                                                            |

|      | length, and square $(W = L)$ n-MOSFETs at $V_D = 1V$                                                                                                       |

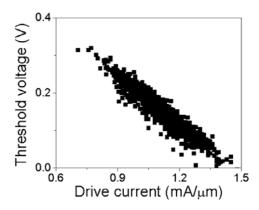

| 4.12 | Impact of parameter set selection in n-MOSFET device; dashed                                                                                               |

| line shows the results of the original physical atomistic simulations                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.13 Impact of parameter set selection in p-MOSFET device; dashed line shows the results of the original physical simulations                                                                                                      |

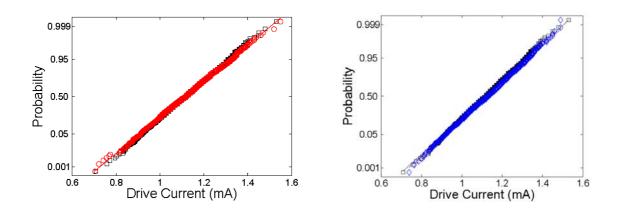

| 4.14 Probability plot of drive current in high drain bias. Black square: 7-parameter set; Red circle: 6-parameter set and Blue lozenge: 5-parameter set                                                                            |

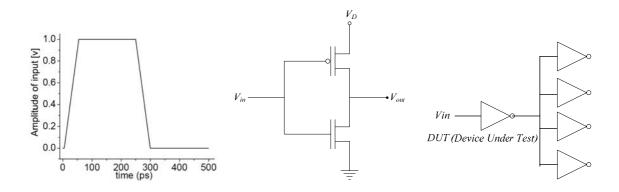

| 4.15 The input signal used for the simulation of inverter test bed (Left), the schematic of the CMOS inverter used for the simulation (middle) and the chain of inverters in fan out of (FO4) used as a realistic test bed (Right) |

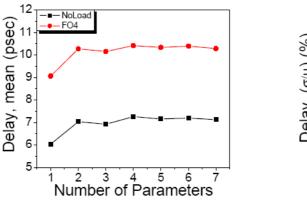

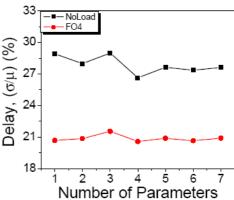

| 4.16 Impact of statistical parameter set selection on the mean and standard deviation of rise time delay of CMOS inverter in no load and FO4 conditions                                                                            |

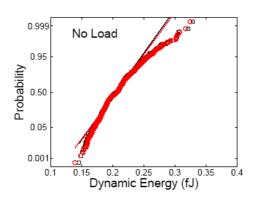

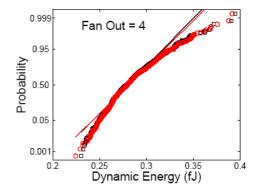

| 4.17 Probability plot of dynamic energy of inverter. Black square: 7 parameter set; Red circle: 5-parameter set statistical compact models. (Left) no load inverter, (Right) FO4                                                   |

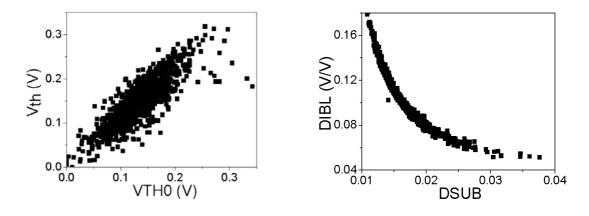

| 4.18 The correlation between typical electrical parameters and BSIM statistical parameters                                                                                                                                         |

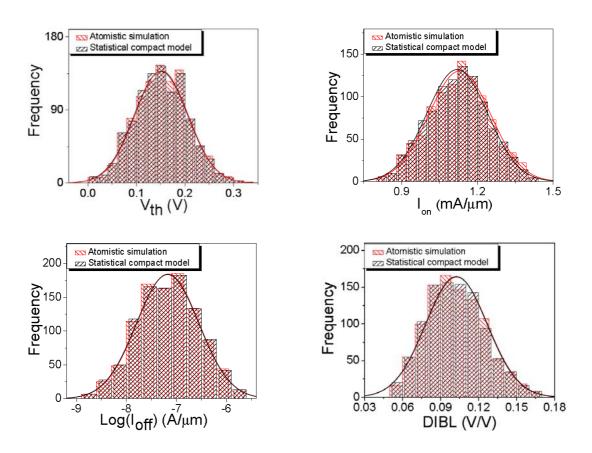

| 4.19 Comparison between figure of merits from 1000 atomistic simulations and direct extracted statistical compact mode simulations                                                                                                 |

List of Figures xv

| 4.20 Cc | omparison between scatter plots of physical simulations and   |

|---------|---------------------------------------------------------------|

| dir     | rect extracted statistical compact models. (Black square:     |

| Ph      | ysical simulations, Red circle: Direct extracted statistical  |

| co      | mpact models) 80                                              |

|         |                                                               |

|         |                                                               |

|         |                                                               |

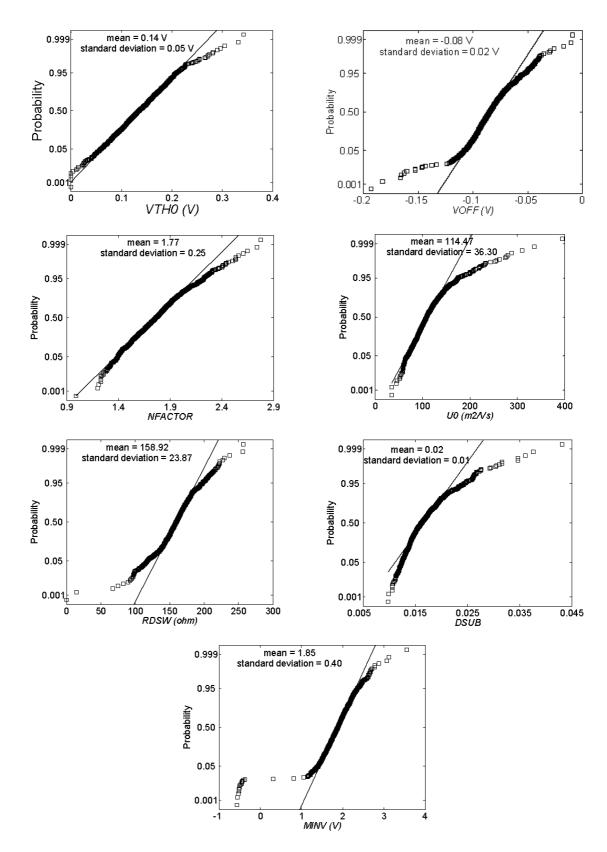

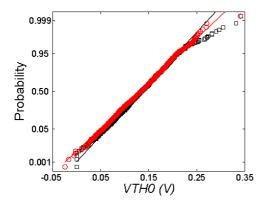

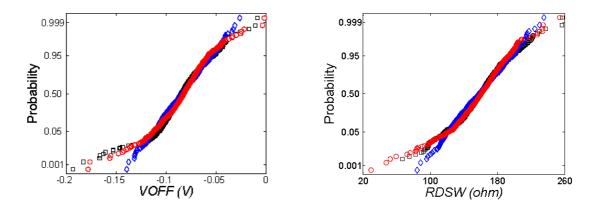

| 5.1 No  | ormality plots of BSIM statistical parameters                 |

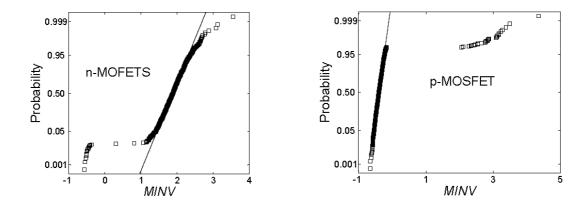

| 7.0 D   | 1 1 11 1 CAMPAGE MOGERT 1 MOGERT                              |

| 5.2 Pro | obability plot of <i>MINV</i> for n-MOSFET and p-MOSFET 86    |

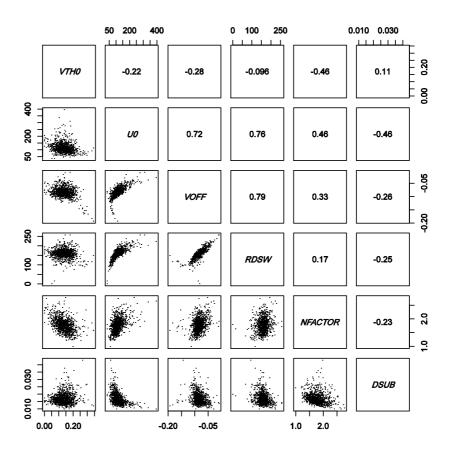

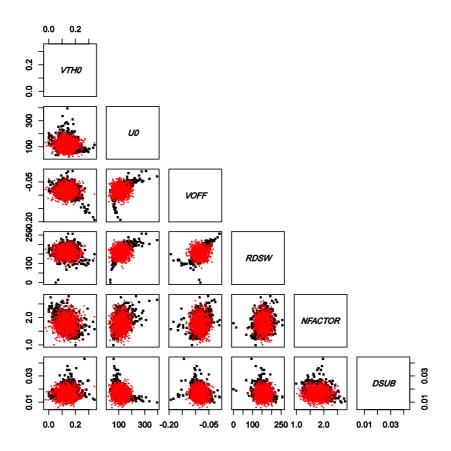

| 5.3 Sc  | atter plots of selected BSIM parameters from statistical      |

|         | traction of 35nm channel length of 1000 n-MOSFET devices 87   |

| CA      | traction of 33mm channel length of 1000 m-1005f L1 devices 67 |

| 5.4 Sc  | atter plots of selected BSIM parameters from statistical      |

|         | traction of 35nm channel length of 1000 p-MOSFET devices 88   |

|         |                                                               |

| 5.5 Pro | obability plot of typical BSIM4 statistical parameters        |

| ge      | nerated by Naïve approach. Black square: Direct extraction;   |

| Re      | ed circle: Naïve approach89                                   |

|         |                                                               |

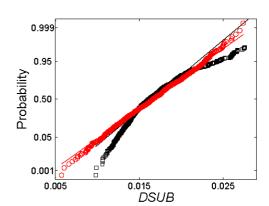

| 5.6 Sc  | atter plots between BSIM4 statistical parameters. Black       |

| sq      | uare: Direct extraction parameters; Red circle: parameters    |

| ge      | nerated by Naïve approach 90                                  |

|         |                                                               |

| 5.7 Sc  | atter plots between BSIM4 statistical parameters for n- and   |

| p-]     | MOSFET, respectively. Black square: Direct extraction         |

| pa      | rameters; Red circle: parameters generated by PCA             |

| tec     | chnique94                                                     |

List of Figures xvi

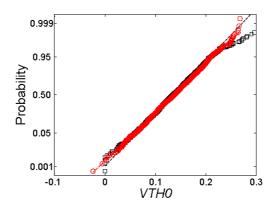

| 5.8  | Probability plot of typical BSIM4 statistical parameters              |

|------|-----------------------------------------------------------------------|

|      | generated by PCA approach. Black square: Direct extraction            |

|      | Red circle: PCA approach                                              |

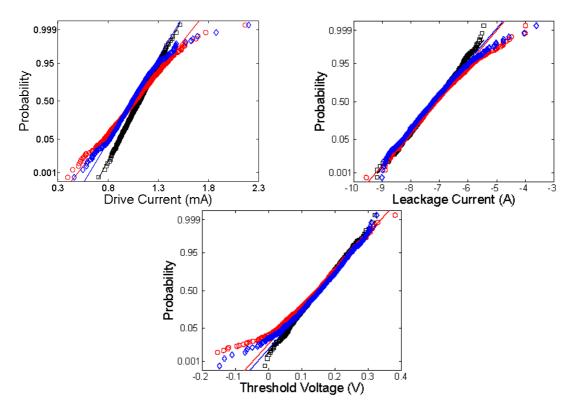

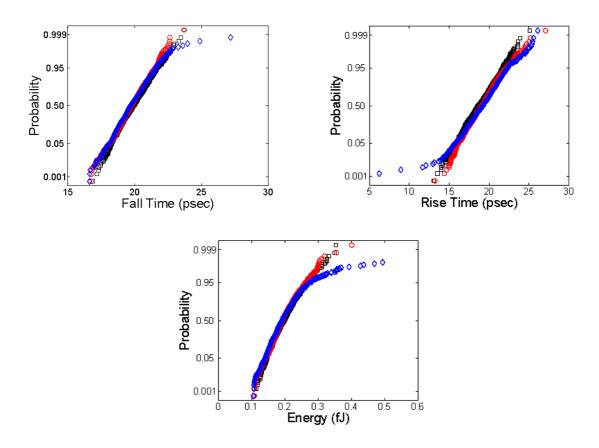

| 5.9  | Probability plot of figures of merit of n-MOSFETs generated           |

|      | by different statistical approaches in high drain conditions          |

|      | $V_D = 1V$ . Black square: direct extraction; red circle: Naïve       |

|      | approach and blue lozenge: PCA approach                               |

| 5.10 | Probability plot of figures of merit of p-MOSFETs generated           |

|      | by different statistical approaches in high drain conditions          |

|      | $V_D = 1V$ . Black square: direct extraction; red circle: Naïve       |

|      | approach and blue lozenge: PCA approach                               |

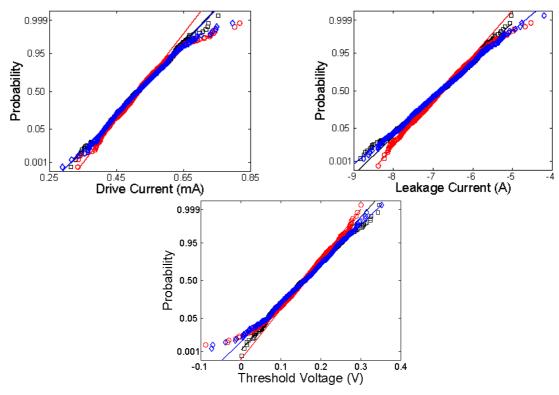

| 5.11 | Scatter plots between figures of merit for 1000 statistical BSIM      |

|      | compact models. Black square: physical simulation; Red circle         |

|      | show the PCA approach (the three plots in the bottom left             |

|      | corner) and the Naïve approach (the three plots in the top right      |

|      | corner) 99                                                            |

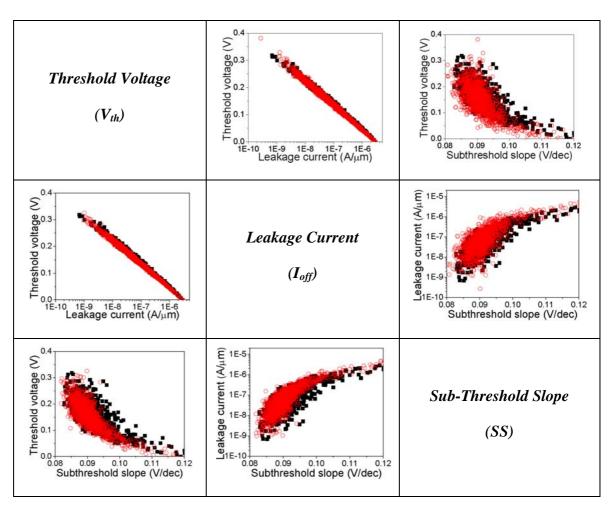

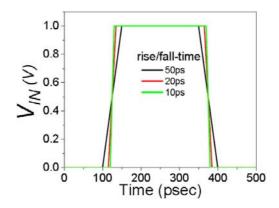

| 5.12 | Inverter input signal with various rise/fall time                     |

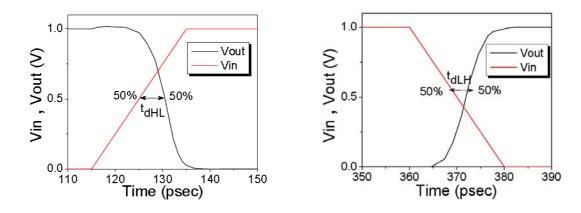

| 5.13 | Definitions of t <sub>dHL</sub> and t <sub>dLH</sub>                  |

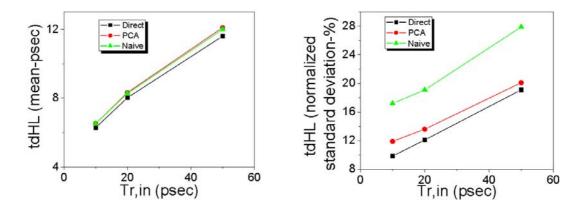

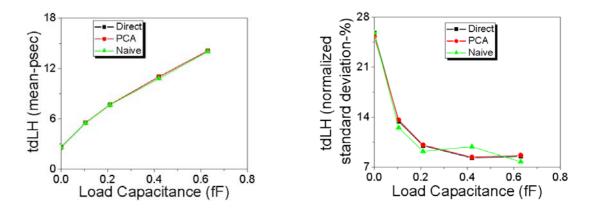

| 5.14 | statistical trend of inverter fall time delay versus input rise       |

|      | time, mean values (left), coefficient of variation values (right) 103 |

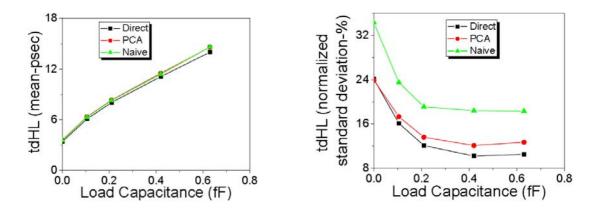

| 5.15 | Statistical trend of inverter fall time delay versus load             |

List of Figures xvii

| capacitance, mean values (left), coefficient of variation values (right)                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

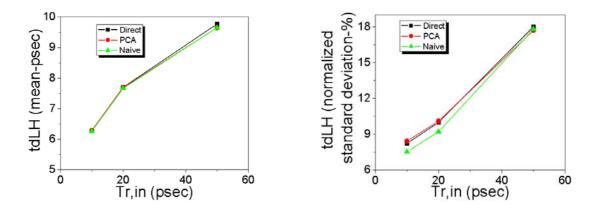

| 5.16 Statistical trend of inverter rise time delay versus input rise time, mean values (left), coefficient of variation values (right) 104                                                                                            |

| 5.17 Statistical trend of inverter rise time delay versus load capacitance, mean values (left), coefficient of variation values (right)                                                                                               |

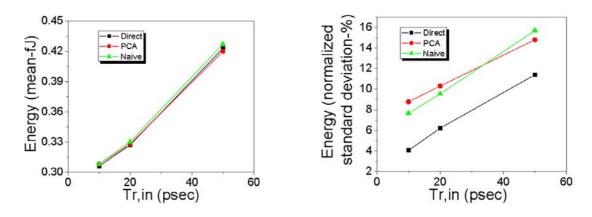

| 5.18 Statistical trend of inverter consumed energy versus input rise time, mean values (left), coefficient of variation values (right) 105                                                                                            |

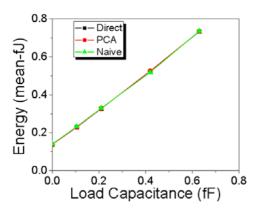

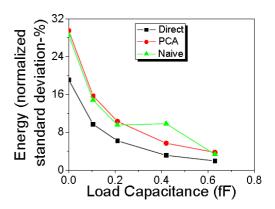

| 5.19 Statistical trend of inverter consumed energy versus load capacitance, mean values (left), coefficient of variation values (right)                                                                                               |

| 5.20 Probability plot of BSIM parameters from direct statistical parameter extraction compared with PCA and NPM generated parameter approach. Black square: direct extraction; red circle NPM approach and blue lozenge: PCA approach |

| 5.21 Correlation between electrical parameters. Bottom-left Comparison between results from direct statistical compact model and PCA; Top-right: Comparison between results from direct statistical compact model and NPM approach    |

| 5.22 Probability plot of rise, fall time delays and dissipated energy of inverter simulations using statistical directly extracted. PCA                                                                                               |

List of Figures xviii

|     | and NPM generated statistical compact model parameters                      |

|-----|-----------------------------------------------------------------------------|

|     | approach. Black square: direct extraction; red circle: NPM                  |

|     | approach and blue lozenge: PCA approach                                     |

|     |                                                                             |

|     |                                                                             |

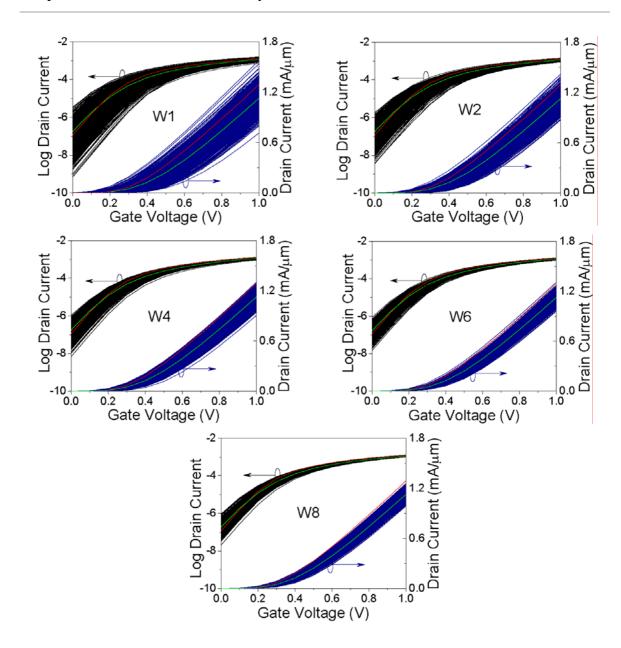

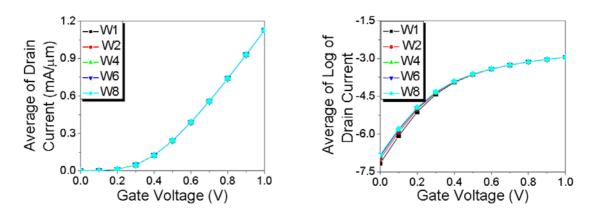

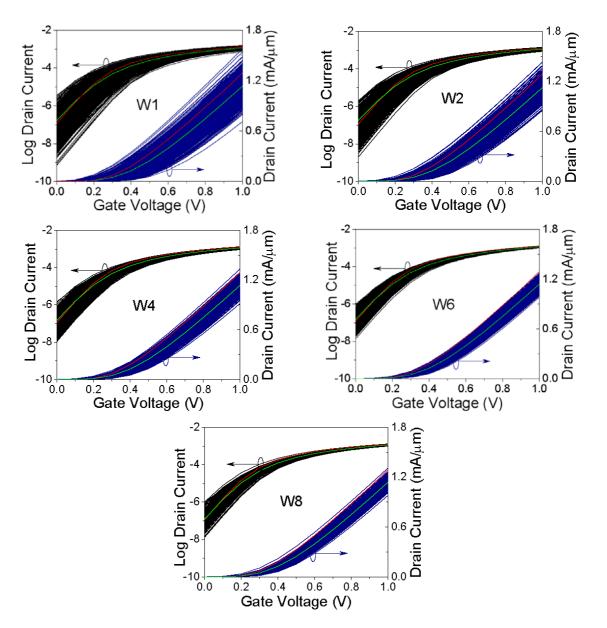

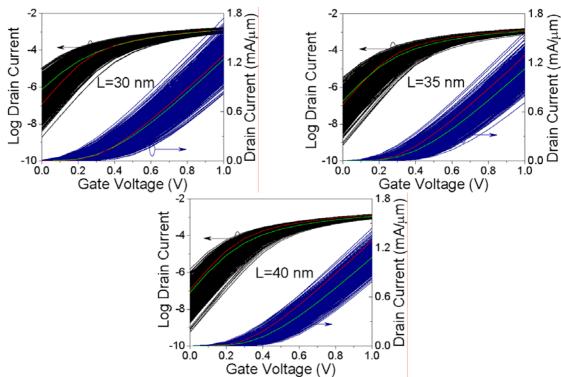

| 6.1 | Variability in the $I_d$ - $V_g$ characteristics of a statistical sample of |

| 0.1 | 1000 microscopically different 35nm n-MOSFETs whose gate                    |

|     | widths are multiples of 35nm ( $V_D = IV$ ). Red curves show                |

|     | idealised devices. Green curves are the average currents for                |

|     | each statistical set device                                                 |

|     |                                                                             |

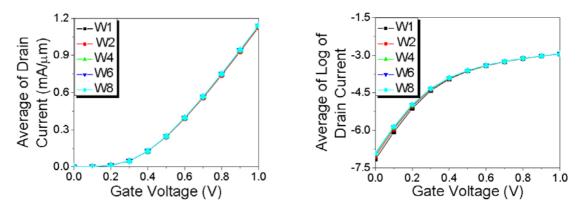

| 6.2 | Average drain currents obtained from Figure 6.1                             |

|     |                                                                             |

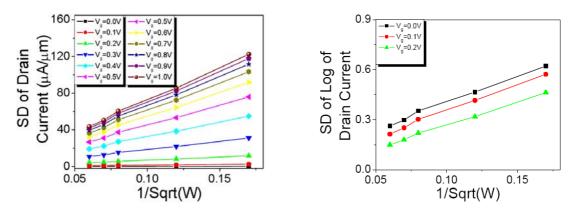

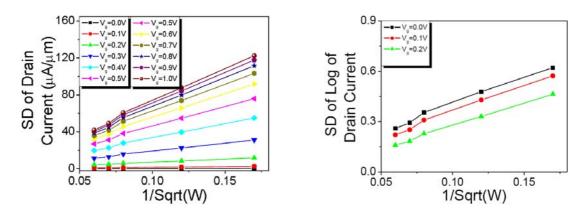

| 6.3 | Standard deviation of the drain current for different values of             |

|     | the gate voltages in different width set devices (The x-axis                |

|     | dimension is nm <sup>-0.5</sup> )                                           |

| 6.4 | Variability in the $I_d$ - $V_g$ characteristics of a statistical sample of |

| 0   | 1000 microscopically different 35nm n-MOSFETs whose gate                    |

|     | widths are multiples of 35nm ( $V_D = IV$ ). Red curves described           |

|     | idealized devices. Green curves are the average currents for                |

|     | each statistical set                                                        |

|     |                                                                             |

| 6.5 | Average drain currents obtained from Figure 6.4                             |

|     |                                                                             |

| 6.6 | Standard deviation of the drain current for different values of             |

|     | the gate voltages in different width set devices (The x-axis                |

|     | dimension is nm <sup>-0.5</sup> )                                           |

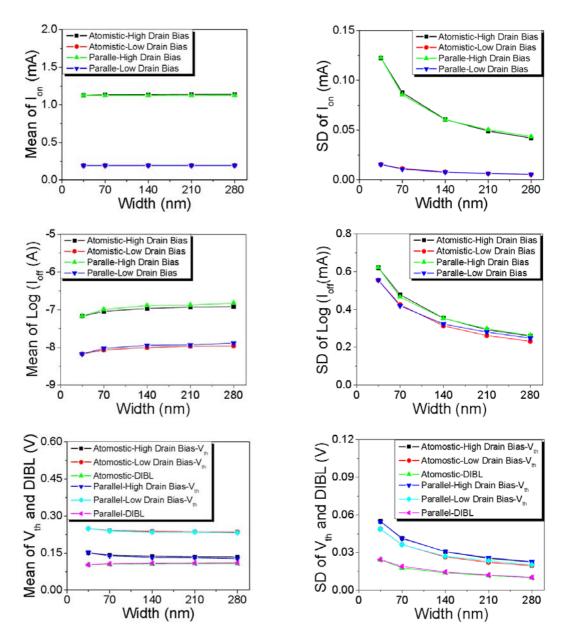

| 6.7 Trend of mean and standard deviation of figures of merit versus width                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

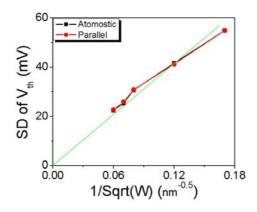

| 6.8 Trend of standard deviation of $V_{th}$ versus $1/\sqrt{W}$                                                                                                                                                                                                                             |

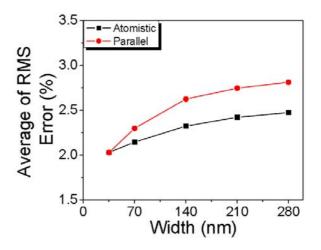

| 6.9 The average value of the RMS error between statistically extracted BSIM compact models                                                                                                                                                                                                  |

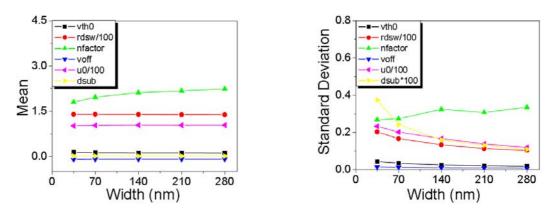

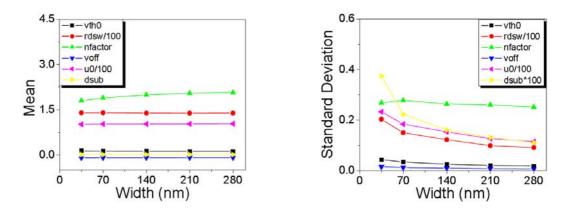

| 6.10 Value of different parameters of statistical parallel BSIM compact models versus width, mean values (left), standard deviations (right)                                                                                                                                                |

| 6.11 Value of different parameters of statistical atomistic BSIM compact models versus width, mean values (left), standard deviations (right)                                                                                                                                               |

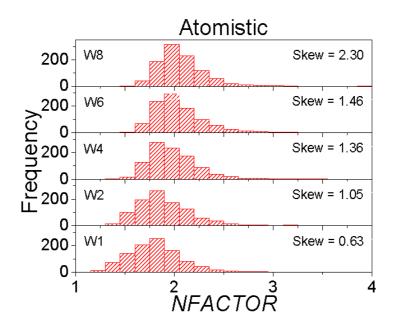

| 6.12 The impact of width of device on <i>NFACTOR</i> parameter of statistical compact models                                                                                                                                                                                                |

| 6.13 Variability in the $I_d$ - $V_g$ characteristics of a statistical sample of 1000 microscopically different 35nm n-MOSFETs whose gate widths are multiples of 35nm. $V_D = IV$ . Red curves described idealised devices. Green curves are the average currents for each statistical set |

| 6.14 Collected average drain currents from Figure 6.12                                                                                                                                                                                                                                      |

| 6.15 Figures of merit of uniform devices with different length                                                                                                                                                                                                                              |

List of Figures xx

| 6.16 Trend | of    | mean   | and   | standard   | deviation | n of     | figures   | of   | merit  |

|------------|-------|--------|-------|------------|-----------|----------|-----------|------|--------|

| versus     | widt  | h      |       |            | •••••     |          |           | •••• | 135    |

|            |       |        |       |            |           |          |           |      |        |

| 6.17 Value | of    | differ | ent j | parameters | of sta    | itistica | l parall  | el   | BSIM   |

| compa      | ct 1  | nodels | vers  | us width,  | mean      | value    | s (left), | sta  | andard |

| deviati    | ons ( | right) |       |            |           |          |           |      | 136    |

## **List of Tables**

| 3.1 | Drain current characteristic of n-MOSFET device illustrated in |

|-----|----------------------------------------------------------------|

|     | Figure 3.6 and comparison with real devices                    |

| 3.2 | The relative RMS errors of the final BSIM4 compact model in    |

|     | respect to device TCAD simulations                             |

| 3.3 | The relative RMS errors of the final BSIM4 compact model in    |

|     | respect to device TCAD simulations                             |

|     |                                                                |

| 4.1 | Statistical parameter extraction RMS errors for 1000 BSIM      |

|     | compact models 68                                              |

| 4.2 | Summary of simulation results for 1000 microscopically         |

|     | different, 35nm gate length, square $(W = L)$ n-MOSFETs        |

|     | including all statistical variability sources                  |

| 4.3 | Mean and standard deviation of figure of merits from atomistic simulations and direct extracted statistical compact model simulations and their errors |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | The correlation coefficient between parameters of n- and p-MOSFET; Down-left: Direct parameter; Up-right: PCA parameters                               |

| 5.2 | The statistical results of figures of merits for n- and p-MOSFET                                                                                       |

| 5.3 | The correlation coefficient between parameters; Down-left: Direct parameter; Up- right: NPM parameters                                                 |

| 6.1 | Statistical average of the drain current for different gate width n-MOSFETs                                                                            |

| 6.2 | Standard deviation of the drain current for different gate width n-MOSFETs                                                                             |

| 6.3 | Statistical average of the drain current for different gate width n-MOSFETs                                                                            |

| 6.4 | Standard deviation of the drain current for different gate width n-MOSFETs                                                                             |

List of Tables xxiii

| 6.5 Mean and standard deviation of statistical parameters obtained |

|--------------------------------------------------------------------|

| from atomistic and parallel component approaches in different      |

| width devices                                                      |

| 6.6 The correlation coefficient between parameters of devices with |

| 70nm gate width; Down-left: Atomistic compact models; Up-          |

| right: Parallel compact models                                     |

|                                                                    |

| 6.7 The correlation coefficient between parameters of devices with |

| 140nm gate width; Down-left: Atomistic compact models; Up-         |

| right: Parallel compact models                                     |

|                                                                    |

| 6.8 The correlation coefficient between parameters of devices with |

| 210nm gate width; Down-left: Atomistic compact models; Up-         |

| right: Parallel compact models                                     |

|                                                                    |

| 6.9 The correlation coefficient between parameters of devices with |

| 280nm gate width; Down-left: Atomistic compact models; Up-         |

| right: Parallel compact models                                     |

|                                                                    |

| 6.10 Means and standard deviations of MOSFET figures of merit 135  |

## **Nomenclature**

## **Physical Constants**

```

Permittivity of free space (8.85418782 \times 10^{-14} \, F/cm)

\varepsilon_{si} Silicon permittivity (11.68 \, \varepsilon_0)

Permittivity (11.68 \, \varepsilon_0)

Elementary (unit) charge (1.60 \times 10^{-19} \, C)

Intrinsic carrier concentration (8.72 \times 10^9 \, cm^{-3})

k_B Boltzmann's constant (1.38 \times 10^{-23} \, J/K)

```

## Other Symbols

| $\sigma$        | standard deviation                                                           |

|-----------------|------------------------------------------------------------------------------|

| $	heta_{th}$    | Basic form of physical expression for SCE                                    |

| $\mu$           | Mean                                                                         |

| $\mu_0$         | Low-field mobility                                                           |

| $\mu_{\it eff}$ | Effective mobility                                                           |

| λ               | Introduced to model the non-saturation effects which are found for P-MOSFETs |

Nomenclature xxv

$\Phi_S$  Surface potential

Y A constant which depends on device type and technology

$A_{bulk}$  Bulk charge effects

$C_0$  Constant

*C<sub>cen</sub>* Centroid Channel Charge Capacitance

$C_{oxe}$  Equivalent Gate Oxide Capacitance

$C_{oxeff}$  Effective Gate Oxide Capacitance

$E_0$  Critical electric field

$E_{eff}$  Effective field

$I_d$  MOSFET drain current

$I_{off}$  Channel leakage current

$I_{on}$  Drive current

$G_x$  Conductance

$l_t$  Characteristic length

L Device length

Effective length when the gate to source/drain regions is under flat-

$L_{active}$  band condition.

$L_{eff}$  Effective channel length

$L_g$  Gate length

N Multiple of the base device gate width

N Sub-threshold swing parameter

$Q_b$  Charge density in the bulk

$Q_{INV}$  Charge density in the channel

$Q_{ch}$  Channel charge density

$t_{dLH}$  Rise time delay

Nomenclature xxvi

t<sub>dHL</sub> Fall time delays

T Temperature

$V_A$  Early voltage

V<sub>ADITS</sub> Effect and drain-induced threshold shift

V<sub>ASCBE</sub> Early voltage due to substrate current

$V_{bi}$  Source/drain junction built-in voltage

V<sub>bs</sub> Bulk/source bias

$V_{bseff}$  Effective substrate bias

$V_{ds}$  Drain/source bias

$V_{dsat}$  Saturation voltage

$V_F$  Quasi-Fermi potential

$V_{fbSD}$  Flat-band voltage between the gate and source/drain diffusion regions

$V_g$  MOSFET gate voltage, relative to the source contact

$V_{gse}$  Effective gate voltage including the poly-silicon gate depletion effect

$V_{gsteff}$  Effective gate bias

$V_{in}$  Input voltage (V)

$V_t$  Thermal voltage

$V_{th}$  Threshold voltage

$V'_{off}$  Potential offset parameter

W Device width

Effective width when the gate to source/drain regions is under flat-

$W_{active}$  band condition.

$W_{eff}$  Effective channel width

$W_{effcj}$  Effective source/drain diffusion width

Nomenclature xxvii

$X_{DC}$  Equivalent DC centroid of the channel charge layer

$X_{dep}$  Depletion layer width in the channel with the influence of  $V_{bs}$

$X_{dep0}$  Depletion layer width in the channel when  $V_{BS} = 0$

#### Acronyms

1D One Dimension

2D Two Dimensions

3D Three Dimensions

AC Alternating Current

BPV Backward Propagation of Variance

BSIM Berkeley Short-channel IGFET Model

BSIM-MG BSIM Multi Gate

BSIM CMG BSIM Common and Multi Gate

BSIMSOI BSIM Silicon On Insulator

BTE Boltzmann Transport Equation

CESL Contact Etch Stop Layer

CLM Channel Length Modulation

CMC Compact Model Council

CMOS Complementary Metal Oxide Semiconductor

DIBL Drain Induced Barrier Lowering

DITVS Drain-Induced Threshold Voltage Shift

DC Direct Current

DD Drift Diffusion

DG Density Gradient

EIA Electronic Industries Alliance

Nomenclature xxviii

EOT Equivalent Oxide Thickness

FCLT Finite Charge Layer Thickness

FOM Figures of Merit

GIDL Gate Induced Drain Lowering

IC Integrated Circuit

LDD Low-Doped Drain

LER Line Edge Roughness

MC Monte Carlo

MOSFET Metal Oxide Semiconductor Field effect Transistor

NBTI Negative Bias Temperature Instability

NULD Non-Uniform Lateral Doping

NPM Nonlinear Power Method

NWE Narrow Width Effect

OTF Oxide Thickness Fluctuations

OTV Oxide Thickness Variations

PBTI Positive Bias Temperature Instability

PCA Principal Component Analysis

PGG Poly-silicon Gate Granularity

QT Quantum Transport

RDD Random Discrete Dopants

RDF Random Dopant Fluctuations

RMS Root Mean Square

SCE Short Channel Effect

SEM Scanning Electron Microscope

SS Subthreshold Slope

Nomenclature xxix

SPICE Simulation Program with Integrated Circuit Emphasis

SRAM Static Random Access Memory

STI Shallow Trench Isolation

TCAD Technology Computer Aided Design

ULSI Ultra Large Scale Integration

VHDL Very High Design Language

## Chapter 1

#### Introduction

Computer-aided design (CAD) tools are an essential part of the integrated-circuit (IC) design flow. Among them, the Simulation Program with Integrated Circuit Emphasis (SPICE) is widely used for analysis and verification of analogue, mixed mode and digital circuits employing billions of transistors [1]. Transistor compact models are key to the utility of SPICE, and acting as an interface between technology and design. Although the initial driving force of compact model development was the requirement of accurate modelling of circuit components in analogue IC design domain, compact models are now extensively used in transistor-level digital circuit design and verification, especially in the characterization of standard cells and in the SRAM (Static Random Access Memory) design process. Therefore, compact model accuracy is key to analogue, mixed mode and digital IC design.

BSIM4 (Berkeley Short-channel IGFET Model) is a threshold voltage based compact model for integrated circuit design purposes. This model is constructed on top of the BSIM3 framework. It shares the same basic equations with that bulk model so that the physical nature and smoothness of BSIM3 are preserved. BSIM series compact models have served the electronic industry for more than 20 years with focus on the simulation of planar bulk MOSFETs [2,3]. Recently, other flavours of BSIM compact models such as

BSIMSOI and BSIM-CMG have been developed to simulate SOI and multi gate MOSFETs [4,5]. Since planar bulk MOSFETs are still the workhorse of the semiconductor industry and their scaling is expected to continue until 2015, BSIM4 is still being used by semiconductor companies such as IBM and AMD and foundries such as TSMC. BSIM4 was selected by Electronic Industries Alliance (EIA) and Compact Model Council (CMC) as the standard MOSFET compact model in March 2000 [3]. Various compact models like PSP, HiSIM and EKV have been introduced later and are being used by semiconductor industry [6]. BSIM4 is used as the target compact model in this thesis.

Although the design of compact models, and the extraction of compact model parameters is a mature field (especially for bulk devices), this long standing interface between technology and design is now being seriously affected by a rapidly growing problem in device technology – atomic scale statistical MOSFET variability. As devices scale further into the sub-100nm regime, intrinsic parameter fluctuations between devices which result from the discreteness of charge and granularity of matter are now one of the major obstacles which limit scaling and integration [7]. In general, device variability can be broadly classified as global or local variability. Global variability refers to the changes in the behavior of nominally identical transistors from wafer to wafer or die to die [8,9], typically related to variations in processing resulting in change of transistor structural dimensions and doping profiles. Local variability can be subdivided into two types: systematic variability and statistical variability. Systematic variability is introduced by layout dependent optical proximity effects and strain variations. It can be reduced by the adoption of restricted design rules. Moreover, it is locally predictable using sufficient computing power. However, statistical variability, introduced by the granularity of matter and discreteness of charge (for example due to the precise configuration of discrete dopant atoms in a nanoscale device channel) cannot be eliminated by tuning the layout or by tightening fabrication process control and cannot be deterministically predicted using simulations. It is a significant and growing problem – it accounts for more than 50% of device variability in 45nm CMOS technology [10] – and is predicted to become the major source of transistor variations for future technology generations. In addition, because it effects every nominally identical transistor, even those placed side by side in a circuit, it is

an uncontrollable source of circuit mismatch. Simulation and modelling of intrinsic parameter fluctuations is crucial for understanding on predicting the statistical variability. Simultaneously circuit designers would much prefer information on intrinsic parameter fluctuations to be supplied in the familiar framework of compact models. This becomes crucial for high yield nanometer CMOS design.

Mismatch has historically been the subject of specific modelling, and the importance of device matching in the analogue domain drove early transistor mismatch modelling efforts. The first systematic mismatch models were reported in early '80s for MOS capacitors and MOSFETs [11,12], and this still remains an active research area today [13,14]. Mismatch studies target random, uncorrelated variation that cannot be improved by matching techniques [1,12]. However, most MOSFET mismatch models are based on simple MOSFET drain current formulae in the linear or saturation region [15,16]. Although they can provide important information regarding mismatch trends versus transistor design and dimensions, they cannot be integrated into design tools to directly support design activities. A natural way to incorporate mismatch into design flow is to employ *statistical compact modelling* techniques, and investigating such statistical compact modelling will be the aim of this work.

Most previous compact model based mismatch approaches rest upon the assumption of normal, uncorrelated distributions of compact model parameters [17,18,19]. Although this assumption was primarily made to ease theoretical prediction, it also allows the storage and transfer of relatively small compact model data files containing only the mean and standard deviation of parameters, rather than large statistical 'card indexes' capturing the full distributions and correlations of compact model parameters. If necessary, approximate statistical BSIM parameter ensembles could then be generated from these mean ( $\mu$ ) and standard deviation ( $\sigma$ ) values. A key aspect of our study will be to investigate the efficacy of this simplifying assumption, and study to what extent BSIM parameters generated from  $\mu$  and  $\sigma$  values, or from additional moments and correlations can provide accurate distributions and correlations of transistor characteristics and figures of merit.

#### 1.1 Aims and objectives

The aim of this work is to investigate accurate and efficient techniques for incorporation of statistical variability into industry standard compact models such as BSIM4. The main objectives include:

- 1. To develop a BSIM parameter extraction and optimization methodology using as a test bed a template 35nm and 18nm bulk MOSFETs.

- 2. To determine a subset of the BSIM compact model parameters that can accurately capture the effects of statistical variability over a statistical device ensemble.

- 3. To evaluate the accuracy of the methodology as a function of statistical parameter subset size, comparing with benchmark physics based 'atomistic' simulation results, and evaluating with respect to the distributions of typical MOSFET electrical figures of merit.

- 4. To develop statistical BSIM parameter generation techniques and to evaluate their accuracy and their ability to reproduce typical MOSFET electrical figures of merit in comparison with benchmark physics based simulations and directly extracted compact models.

- 5. To perform statistical circuit simulation of simple CMOS circuits using a statistical compact model library as a practical test of the accuracy of different parameter extraction and generation techniques.

- 6. To study the impact of statistical variability on different channel width/length MOSFETs and their electrical figures of merit.

### 1.2 Thesis Outline

The rest of this thesis is organized as follows. The second chapter presents background information about variability and the classification of variability in nanoscale MOSFETs. Statistical variability and its sources including Random Discrete Dopants (RDD), Line Edge Roughness (LER), Oxide Thickness Fluctuations (OTF), high- $\kappa$  granularity and Polysilicon Gate Granularity (PGG) are discussed. Physical simulation of statistical variability and the impact of variability on devices and circuits are explained. Existing techniques for statistical variability simulation are explored in details with emphasis on drift-diffusion simulation of statistical variability using the Glasgow University 'atomistic' simulator. Finally a literature review of the concept of statistical compact modeling is presented.

The third chapter focuses on the BSIM4 compact model parameter extraction and optimization with reference to the template/exemplar MOSFETs. Elements of the key BSIM4 compact model expressions for threshold voltage and drain current and the relationship between BSIM4 compact model parameters are reviewed. The physics and design of the template MOSFETs are then discussed, and the methodology of compact model parameter extraction and optimization for such devices is explored. The accuracy of results calculating the static behaviour of n- and p-MOSFET transistors is reviewed. The accuracy criteria are based on the RMS error for drain current between compact model results and the original TCAD physical simulations data from which the compact models were extracted.

In chapter 4, the statistical compact model extraction strategy is developed. First, atomistic simulations are carried out to obtain an ensemble of MOSFET  $I_d$ - $V_g$  characteristics which capture the main sources of variability in 35nm channel length transistors. A subset of compact model parameters which can accurately capture the impact of statistical variability on these MOSFET characteristics is determined based on first order sensitivity analysis of  $I_d$ . The accuracy of the fitting between the compact models and original  $I_d$ - $V_g$  curves is then discussed. The impact of the compact model parameter subset size on the statistical properties of MOSFET figures of merit is studied, and the accuracy

of figures of merit obtained from statistical parameter extraction is evaluated in comparison with the original atomistic simulations (including evaluation of the correlations between figures of merit). A simple CMOS inverter is simulated to study the impact of statistical parameter set size on the accuracy of practical circuit figures of merit – in this case the propagation delay and power dissipation of the inverter.

Chapter 5 is devoted to statistical compact model parameter generation techniques. The statistical properties of the directly extracted BSIM compact model parameters are first reviewed, including their distributions and the correlations between each pair of parameters. Naïve and PCA approaches are then introduced in an attempt to generate compact model parameter ensembles with the same statistical properties as the directly extracted compact model parameters, and the accuracy of these approaches is evaluated by comparing the parameter distributions, and how well they reproduce MOSFET and simple circuit figures of merit. In the last section, the Nonlinear Power Method, a statistical moment matching technique, is introduced and its accuracy is evaluated.

Chapter 6 investigates statistical compact modelling for different channel length/width MOSFETs. Full statistical atomistic simulation of different width/length devices is carried out to provide benchmark results. A computationally efficient approximation to obtain statistical results for different width/length devices – the parallel component approach – is described and its accuracy is investigated by considering trends in extracted BSIM parameters and device figures of merit.

Chapter 7 concludes this work. A summary of the results obtained in the bulk of the thesis is presented and future directions of research are given.

# Chapter 2

# **Background**

The semiconductor industry has always been driven by the scaling of CMOS transistors aiming to produce high performance devices (higher speed and lower power) and increased circuit density, following Moore's famous law [20]. Moore's law predicts the long-term trend in the number of transistors which can be located on an integrated circuit (IC), indicating that the number of transistors in a chip will double every two years [20]. Scaling has two important aims, first is to shrink device dimensions in order to obtain higher device density and therefore increased system functionality, and second to achieve higher devices/circuits performance. Figure 2.1(a) shows transistor count versus date of introduction for a number of noted microprocessors [21]. Due to scaling, the numbers of dopant atoms are reduced in scaled devices as shown in Figure 2.1(b) [22]. This reduction results in the impact of Random Dopant Fluctuations (RDF) on device characteristics. As a result, RDF has emerged as a significant source of statistical variability in contemporary and next generation CMOS devices. Moreover, device variability is the main factor restricting the scaling of the supply voltage, which for the last four technology generations has remained constant [22].

Figure 2.1: Two manifests of MOSFET scaling: (a) Microprocessor transistor counts from 1971 to 2011, after [21], (b) Reduction in the average number of dopant atoms per technology generation, after [22].

Reduction of channel length in bulk MOSFETs requires increasing the channel doping to control short channel effects such as threshold voltage roll-off and punch-through. High channel doping causes an increase in ionized impurity scattering which in turn degrades carrier mobility and reduces the drain current [23,24]. Moreover, devices with high level of channel doping are more susceptible to degradation in device performance caused by direct band-to-band leakage current in the drain region and gate-induced-drain-leakage (GIDL) effects [25,26]. Shallow source and drain extensions and lateral non-uniform doping such as pocket implants are needed to compensate for threshold voltage roll-off and punchthrough [27]. Threshold voltage scaling leads to an increased gate overdrive (difference between gate voltage and threshold voltage) and hence increased drive current and switching speed. Unfortunately, the source-drain leakage current increases exponentially with the reduction in threshold voltage and this increase results in high static power consumption. New materials and process technologies may need to be introduced to improve performance and continue scaling. For instance, strain has been introduced to compensate for the performance loss of scaled transistors by boosting the mobility and drive current [28,29,30].

To ensure adequate control of the channel by the gate, MOSFET oxide thickness should scale proportionately to channel length. However, decreasing oxide thickness increases the

gate tunneling current exponentially, which critically affects low power applications [31]. High- $\kappa$  hafnium-based dielectrics were introduced at the 45nm technology node to prevent such tunneling currents in the gate [32].

Intrinsic parameter fluctuations associated with discreteness of charge and granularity of matter are now one of the major obstacles which limit scaling [7], integration and the reduction of supply voltage and power consumption in ULSI applications. The accurate modelling and simulation of such effects is very important for the development of present and future generation semiconductor devices and their integration into giga-transistor count chips [33,34,35]. In this chapter we focus on the effects of statistical variability which have become dominant at the 45nm technology generation and cannot be further reduced by tightening process control on the device and circuit fabrication steps.

# 2.1 Classification of Variability

Several axes have been introduced in the literature for classification of device variability [36]. One axis classifies the variability into global and local variations [8,37]. Global variations refer to variation across or between fabricated wafers. This kind of variability is caused by lack of control on uniformity in the fabrication and is the difference in oxide layer thickness, physical gate length/width and doping concentration of two devices in different wafers or two devices in the same wafer but usually at a distance apart. By using better manufacturing equipment and process technologies this kind of variability can be controlled and significantly reduced.

Local variations refer to variation between adjacent devices in a chip and falls in two categories: systematic and statistical variations. Systematic variation is the component of the physically varying parameters that follow a well understood behavior and can be predicted and modelled. For instance, optical proximity effects [38], layout mediated strain [39] and well proximity effects [40] are some sources of systematic variability. Statistical variability sources will be considered in next section.

Another classification splits the variability into intrinsic variations and extrinsic variations [37]. Intrinsic variability is caused by the discreteness of charge and granularity of matter in a device which does not depend on fabrication accuracy. Extrinsic variability is associated with the operating dynamics, layout effects and uncontrolled changes in the fabrication process conditions [41].

In this thesis, the focus will be upon intrinsic or statistical variability. At the 45nm technology generation, statistical variability accounts for more than 50% of total variability [10,42] and in smaller devices in new technologies, the manifestation of statistical variability will be increased.

# 2.2 Statistical Variability in Nano-CMOS

Statistical variability which arises from discreteness of charge and granularity of matter is one of the fundamental limiting factors of CMOS scaling and integration in the nanometer regime [43]. Due to its purely random nature, statistical variability introduces increasing challenges for accurate compact modelling and statistical circuit simulation [13,17,19]. The major sources of statistical variability are introduced below.

# 2.2.1 Random Discrete Dopants

Random discrete dopants (RDD) are the most significant source of statistical variability in bulk MOSFETs. Threshold voltage variation due to random variations in the number and position of donor and acceptor atoms in the channel, source and drain regions is an increasingly important problem as device dimensions shrink and has received increasing attention [44,45]. The ionized dopant atoms are typically introduced into the silicon lattice by ion implantation. After annealing, they replace Si atoms in the lattice. These dopants have many collisions with atoms of lattice before coming to rest and consequently replacing Si atoms; therefore the final position of impurities will be determined by the implantation and annealing conditions and will inevitably result in a random dopant

distribution for each transistor. This effect leads to a random current-voltage characteristic change from device to device [46]. Figure 2.2 shows an example of random dopant distribution for a 35nm gate length MOSFET. Each impurity atom creates a discrete Coulomb potential peak in the channel of MOSFET which in turn will have an impact on electrical characteristics and current flow in the device.

Figure 2.2: Typical atomistic discrete dopant distribution inside a 35nm gate length MOSFET:

(a) Potential distribution (potential bar indicates higher positive potentials around donors located in source and drain and and negative potentials around acceptors in the bulk); (b) Dopant position map; Red bubbles are donors in source/drain; Blue bubbles are acceptors in bulk; Yellow color indicates the P-N junction, used with permission from [47].

Several research articles have been published which investigate the effects of discrete random dopants using analytical models [15,48,49,50,51]. Initial simulation studies of the effects of the discrete dopant distribution were accomplished using 2D simulations [51,52,45]. Since the random dopant fluctuations are essentially three dimensional in nature, more advanced and accurate simulators employ 3D numerical techniques [53,54,55].

#### 2.2.2 Line Edge Roughness

Line edge roughness (LER) is another source of intrinsic parameter fluctuations. It is caused by limitations inherent in the materials and tools used in the lithographic process [56,57]. LER is manifest as local variations in the active channel length along the channel width. Where the local channel length is langer, the localized threshold voltage is increased and both leakage and drive current decrease. Where the local channel length is smaller, the localized threshold voltage is reduced and leakage current increases exponentially. This is due to the fact that in those regions where local channel length decreases, short channel effects become strong. Figure 2.3 shows LER in a device with 50nm gate length.

Figure 2.3: LER pattern in a 50nm×200nm MOSFET. Red color shows the high potential associated with source/drain area the blue color indicates the low potential in the bulk. Yellow color illustrates the potential area in the channel and depletion regions, [58].

LER is characterized by two parameters: The RMS magnitude  $\Delta$  and the correlation length  $\Lambda$ . The usual definition of LER magnitude is  $3\Delta$ . The typical value for  $3\Delta$  is 5nm and  $\Lambda$  varies between 10nm to 50nm [59]. Simulations have shown that if the magnitude of the line edge roughness is not reduced below current levels, then the impact of LER will overtake that of RDD at devices scaled to approximately 18nm channel length [60]. LER effects in interconnects also result in resistance and capacitance variability which leads to variability in delay and power consumption of systems and circuits [61].

#### 2.2.3 Oxide Thickness Variations

The atomic scale roughness of the Si/SiO<sub>2</sub> and gate/SiO<sub>2</sub> interfaces will introduce significant intrinsic parameter fluctuations [62]. Indeed, when the oxide thickness is equivalent to only a few silicon atomic layers, the atomic scale interface roughness will result in significant relative oxide thickness variation within the gate region of an individual MOSFET. Figure 2.4 shows the variations in the oxide thickness.

Figure 2.4: The interface between gate, oxide and silicon in an atomic layer abstraction. The red, green and blue colors indicate atomic layers in poly-silicon gate, oxide and silicon, respectively. The fluctuations in the oxide thickness are clearly shown, used with permission from [46].

The random pattern of the gate oxide thickness and interface landscape makes a unique characteristic for each nano-scale MOSFET because the correlation length of the interface becomes comparable to the channel length, different from its counterparts and leads to variations in the surface roughness limited mobility and threshold voltage from device to device [63,64].

#### 2.2.4 High-κ Granularity

The reduction in oxide thickness of MOSFET devices leads to increased gate leakage. High- $\kappa$  dielectrics such as  $Al_2O_3$ ,  $HfO_2$  and  $ZrSiO_4$  have therefore superseded  $SiO_2$  or SiON in new technologies because they have higher permittivity and therefore, using them with larger thickness will provide the same equivalent oxide thickness of  $SiO_2$  while reducing the gate leakage current [46].

Figure 2.5: The gate stack of a nano-CMOS using high- $\kappa$  dielectrics and polycrystalline of high- $\kappa$  which leads to vary dielectric thickness in each point of gate, used with permission from [46].

The use of high-κ material in the gate stack of nano-CMOS devices leads to parameter fluctuations between devices. The polycrystalline nature of high-κ materials illustrated in Figure 2.5 may lead to non-uniformity of the dielectric properties across the oxide film, which in turn results in fluctuations in important device parameters such as threshold voltage [65,66,67].

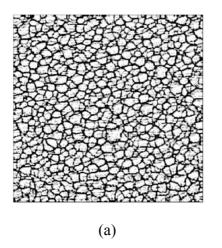

# 2.2.5 Poly/Metal Gate Granularity

The polycrystalline granular structure of the poly-silicon gate has also been identified as an important source of variability. Fermi level pinning at the boundaries of grains due to a high density of defect states introduces surface potential fluctuation within the MOSFET channel and leads to variation in threshold voltage and current characteristics [68,69]. The use of metal gates eliminates poly gate granularity (PGG) induced variability but there is still gate work-function variability associated with metal gate granularity (MGG). Figure 2.6 shows SEM micrographs of two typical poly-silicon and metal gates.

Figure 2.6: SEM micrograph of (a) poly-silicon and (b) metal gates, with 5nm scale for both figures as indicated in (b). Used with permission from [70].

# 2.3 Physical Simulation of Statistical Variability

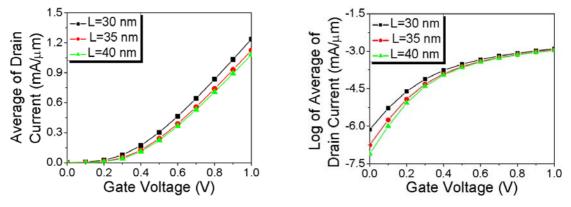

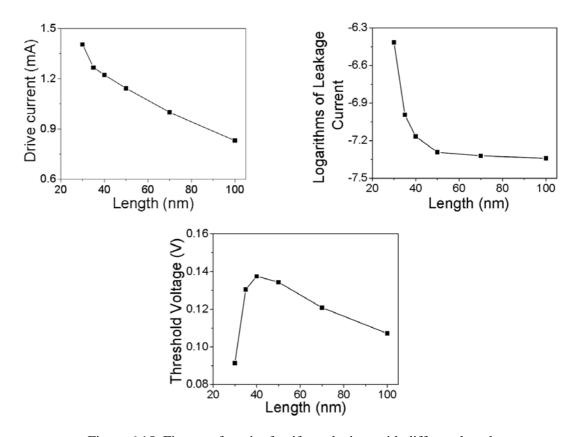

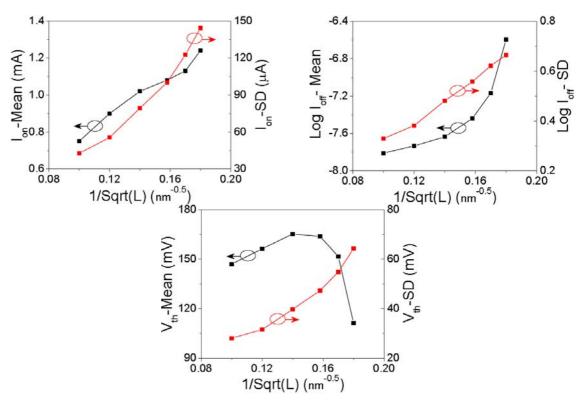

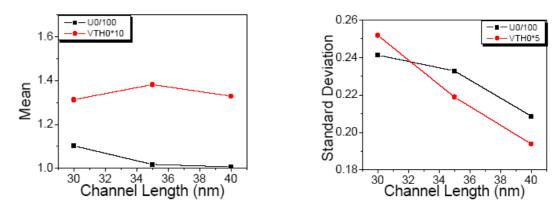

There are many simulation techniques used in the simulation of sub 0.1 µm MOSFET devices to forecast the statistical variability in future technology generations. All of the simulation approaches are differentiated by the level of approximations used in the solution of the Boltzmann transport equation and the handling of quantum effects [71]. Recently, advanced techniques have been reported in predictive physical simulation of statistical variability using Drift Diffusion (DD), Monte Carlo (MC) and Quantum Transport (QT) techniques [43]. The simulations must be carried out in full 3D due to the 3D nature of intrinsic parameter fluctuations. DD is the most computationally effective technique to simulate statistical variability and the Glasgow atomistic simulator, which has been used for physical atomistic simulations of statistical variability in this work, is a drift diffusion simulator.