# Theory And Applications Of Delta-Sigma Analogue-To-Digital Converters Without Negative Feedback

A Thesis Presented to The Academic Faculty

by

**Sven Soell**

In Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

Department of Electronics and Electrical Engineering University of Glasgow June 2008

Copyright © 2008 by Sven Soell

## **ACKNOWLEDGEMENTS**

I wish to acknowledge all the people who have assisted me in this work and made my experience at Glasgow so enjoyable. First and foremost, I thank my supervisor Bernd Porr for he has given me excellent guidance throughout the years. I would also like to thank Jack Sewell for his assistance in the beginning of my research and Wolfson Microelectronics for their financial and intellectual support.

A huge thank you goes to my office mates Mykhaylo Teplechuk alias Micha, Doyin Thompson alias The Bushwoman, Lynsey McCabe and Colin. They all offered much relief from the tedium of research work through long discussions about life, gossip and Bob The Builder. That in general as well as far too many meal and coffee breaks.

I would like to thank my family, for being very supportive and patiently listening to me trying to explain my research. I am indebted to them for the sacrifices that they made to put me through school as an undergraduate and graduate.

# TABLE OF CONTENTS

| AC  | KNO  | WLEDO   | GEMENTS                                    | ii |

|-----|------|---------|--------------------------------------------|----|

| LIS | T OF | FIGUI   | RES                                        | vi |

| LIS | T OF | SYMB    | OLS OR ABBREVIATIONS                       | ix |

| LIS | T OF | LISTI   | NGS                                        | X  |

| SUI | MMA  | RY .    |                                            | хi |

| I   | INT  | RODU    | CTION                                      | 1  |

|     | 1.1  | Motiva  | ntion                                      | 1  |

|     | 1.2  | Main (  | Contributions                              | 2  |

|     | 1.3  | Scope   | and Structure of the Thesis                | 4  |

| II  | SIG  | MA-DE   | CLTA MODULATORS                            | 5  |

|     | 2.1  | Nyquis  | st-rate A/D Converters                     | 5  |

|     |      | 2.1.1   | Sampling                                   | 5  |

|     |      | 2.1.2   | Quantization                               | 7  |

|     |      | 2.1.3   | Limitations of Nyquist-Rate A/D Converters | 11 |

|     | 2.2  | Over-S  | Sampling A/D Converters                    | 11 |

|     |      | 2.2.1   | The FIR Modulator Principle                | 14 |

|     |      | 2.2.2   | The Concept of Noise-Shaping               | 16 |

|     |      | 2.2.3   | Limit Cycles and Idle Tones                | 18 |

|     | 2.3  | Delta-  | Sigma Topologies                           | 19 |

|     |      | 2.3.1   | Delta-Sigma Low Pass                       | 20 |

|     |      | 2.3.2   | Delta-Sigma Band Pass                      | 22 |

|     |      | 2.3.3   | The Concept of Decimation                  | 25 |

|     |      | 2.3.4   | The Concept of Undersampling               | 27 |

|     | 2.4  | Higher  | Order Delta-Sigma Architectures            | 29 |

|     |      | 2.4.1   | Cascaded                                   | 29 |

|     | 2.5  | Summ    | ary                                        | 31 |

| Ш   | FIR  | ST-ORI  | DER FIR SIGMA DELTA MODULATORS             | 32 |

|     | 3.1  | Introdu | action and Review                          | 32 |

|     |      | 3.1.1 FIR S    | SDM Principle                                      | 38  |

|-----|------|----------------|----------------------------------------------------|-----|

|     | 3.2  | An FIR Sigm    | a Delta Modulator Utilizing an Asynchronous D-FF   | 42  |

|     | 3.3  | A FIR Sigma    | Delta Modulator Utilizing an Asynchronous Counter  | 45  |

|     | 3.4  | Theoretical Po | erformance                                         | 48  |

|     | 3.5  | Simulation Re  | esults                                             | 55  |

|     |      | 3.5.1 Non-l    | Linearities                                        | 59  |

|     | 3.6  | Discussion an  | nd Conclusion                                      | 64  |

| IV  | FIR  | DIGITAL MI     | CROPHONE UTILIZING UNDERSAMPLING                   | 66  |

|     | 4.1  | Conventional   | Condenser Microphones                              | 66  |

|     | 4.2  | RF-Topologie   | es                                                 | 68  |

|     |      | 4.2.1 LC-O     | Oscillator based FIR approach                      | 68  |

|     |      | 4.2.2 Schm     | itt-Trigger Oscillator FIR approach                | 79  |

|     | 4.3  | Conventional   | Setup                                              | 82  |

|     | 4.4  | Conclusion .   |                                                    | 85  |

| V   | SEC  | OND-ORDE       | R FIR SIGMA DELTA MODULATORS                       | 86  |

|     | 5.1  | Introduction   |                                                    | 86  |

|     | 5.2  | Second-Order   | r FIR Modulators                                   | 89  |

|     |      | 5.2.1 Version  | on I                                               | 89  |

|     |      | 5.2.2 Simul    | lation Results                                     | 96  |

|     |      | 5.2.3 Version  | on II                                              | 100 |

|     |      | 5.2.4 Theor    | retical Performance                                | 106 |

|     |      | 5.2.5 Simul    | lation Results                                     | 108 |

|     | 5.3  | Comparison 7   | Го The First-Order Modulator                       | 110 |

|     | 5.4  | Discussion an  | nd Conclusion                                      | 112 |

| VI  | DIS  | CUSSION AN     | D FUTURE WORK                                      | 117 |

|     | 6.1  | First-Order F  | IR Modulators                                      | 117 |

|     | 6.2  | Second-Order   | r FIR Modulators                                   | 118 |

|     | 6.3  | Undersamplin   | ng Digital Microphone                              | 120 |

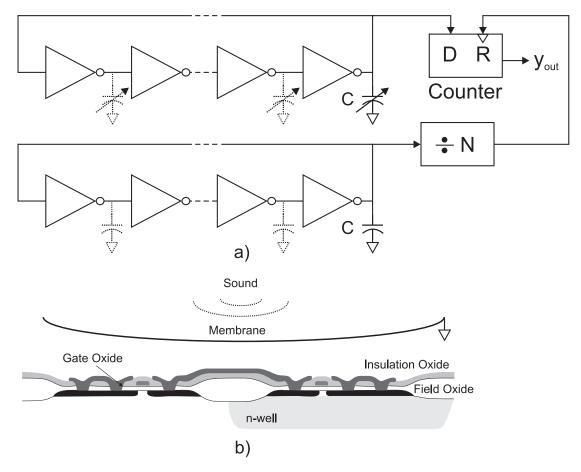

|     | 6.4  | Future Work:   | Microphone Utilizing an Integrated Ring Oscillator | 121 |

| API | PEND | IX A — V       | ERILOGA/AMS LISTINGS                               | 124 |

# LIST OF FIGURES

| Figure 2.1 | Fundamental Operations of Analog-to-Digital Conversion | 5  |

|------------|--------------------------------------------------------|----|

| Figure 2.2 | Sampling Process of an Analog Signal                   | 6  |

| Figure 2.3 | Additive Quantizer Model                               | 7  |

| Figure 2.4 | Uniform b-Bit Quantizer                                | 8  |

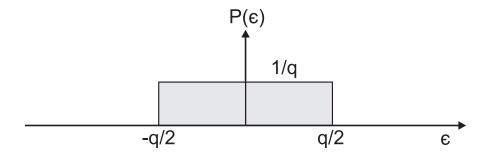

| Figure 2.5 | Quantization Error PDF                                 | 9  |

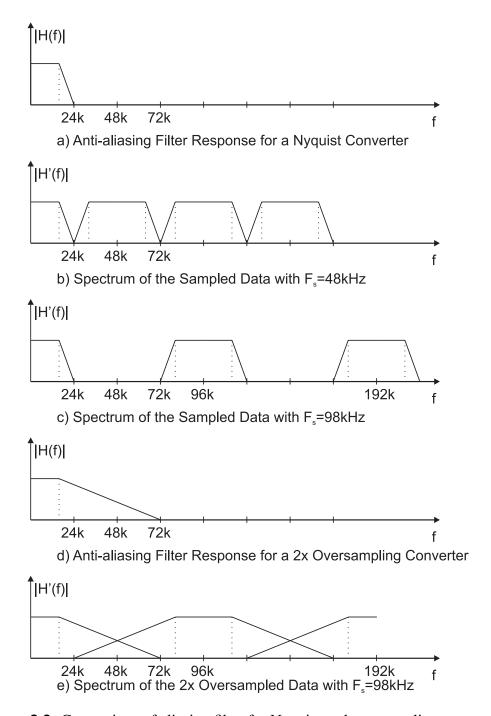

| Figure 2.6 | Sampling for Nyquist and Oversampling Converters       | 12 |

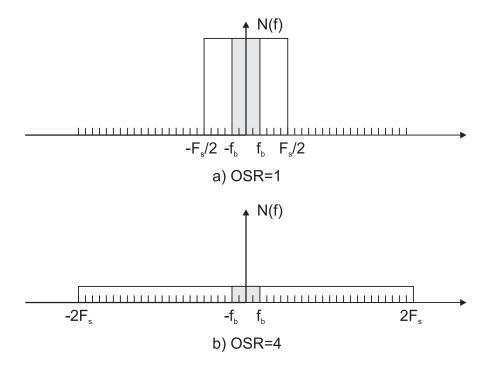

| Figure 2.7 | Quantization Noise Power                               | 13 |

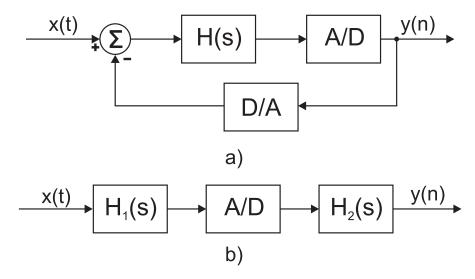

| Figure 2.8 | IIR and FIR First-Order Delta-Sigma Modulator          | 14 |

| Figure 2.9 | I/O Characteristics of a Delta-Sigma Modulator         | 15 |

| Figure 2.1 | O Noise Spectrum of a Nyquist Converter                | 16 |

| Figure 2.1 | 1 First order Delta-Sigma FIR and IIR Modulator        | 17 |

| Figure 2.1 | 2 Noise Shaping of Delta-Sigma Modulators              | 18 |

| Figure 2.1 | 3 First-Order Low Pass Delta-Sigma Modulator           | 20 |

| Figure 2.1 | 4 Low-Pass NTF                                         | 22 |

| Figure 2.1 | 5 LP to BP Transformation                              | 23 |

| Figure 2.1 | 6 CIC Decimation Filter                                | 26 |

| Figure 2.1 | 7 Illustration of Undersampling                        | 27 |

| Figure 2.1 | 8 Requirements on Sampling Frequency for Undersampling | 28 |

| Figure 2.1 | 9 Second-Order Cascaded Modulator                      | 30 |

| Figure 2.2 | O Second-Order FIR Cascaded Modulator                  | 30 |

| Figure 3.1 | Existing Topologies of Frequency-to-Digital Converters | 34 |

| Figure 3.2 | First-Order FIR Modulator Variations                   | 37 |

| Figure 3.3 | Three Principals Making Up Delta-Sigma Modulators      | 39 |

| Figure 3.4 | Principle of a VCO Acting as an Integrator             | 41 |

| Figure 3.5 | First-Order FIR Modulator with Phase-Detector          | 42 |

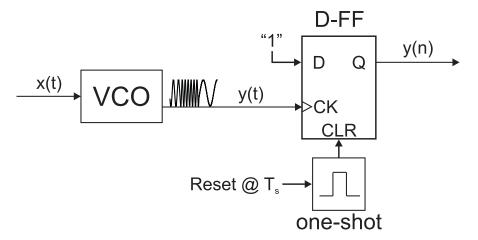

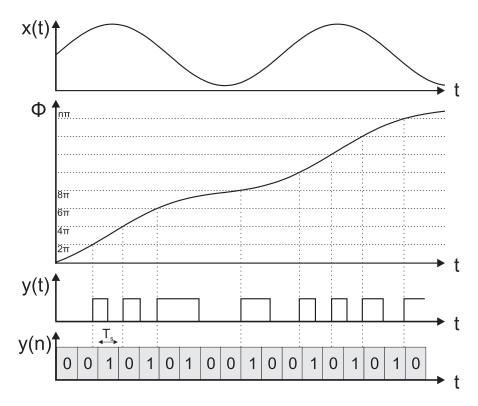

| Figure 3.6 | First-Order FIR Modulator with Asynchronous D-FF       | 43 |

| Figure 3.7 | Operation of the FIR Modulator with Asynchronous D-FF  | 44 |

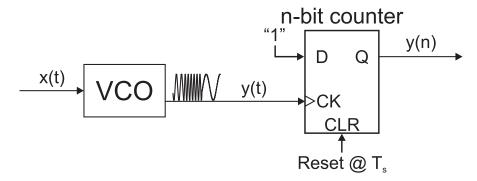

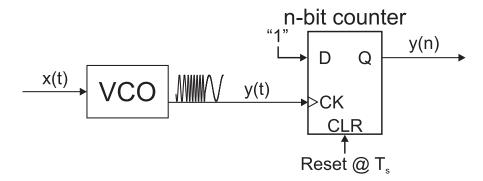

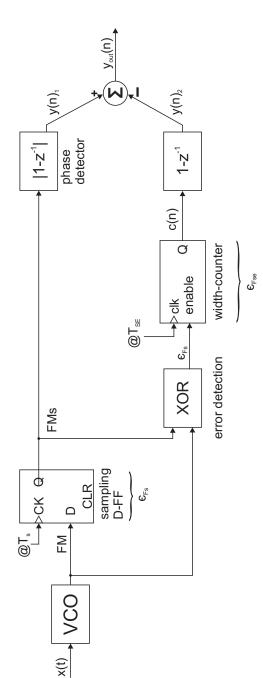

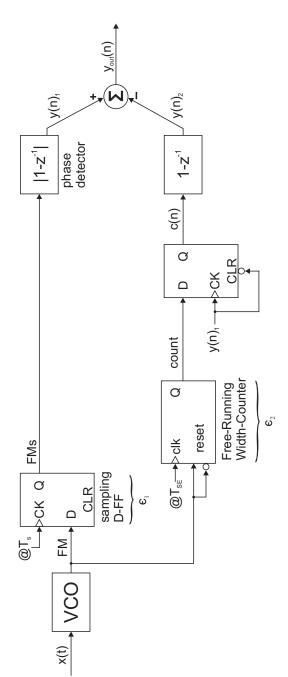

| Figure 3.8 | First-Order FIR Modulator with Asynchronous Counter    | 45 |

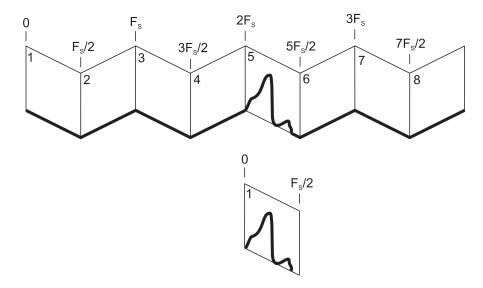

| Figure 3.9 | Spectral Reversal with Undersampling                   | 46 |

| Figure 3.10 E | Equivalent to the sinc filter                                              | 47 |

|---------------|----------------------------------------------------------------------------|----|

| Figure 3.11 E | Equivalent to the sinc accumulator                                         | 47 |

| Figure 3.12 F | FIR Modulator with Counter Absorbed in Decimation Filter                   | 48 |

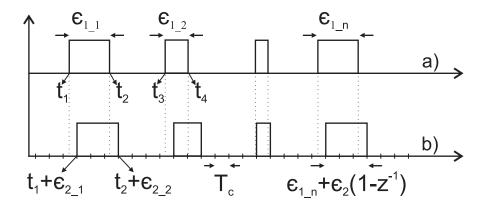

| Figure 3.13 E | Error Introduced in a FIR Modulator                                        | 49 |

| Figure 3.14 F | First-Order FIR Modulator with Asynchronous Counter                        | 55 |

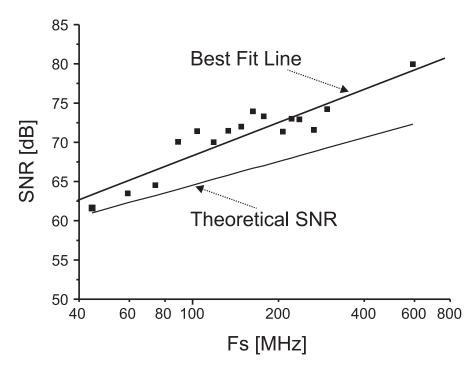

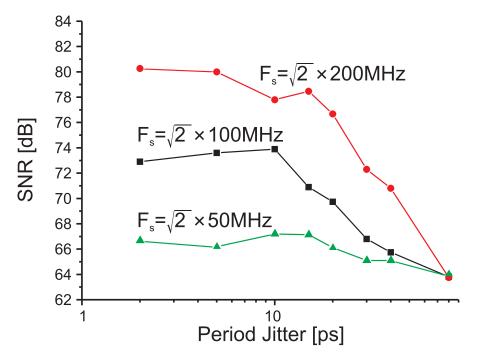

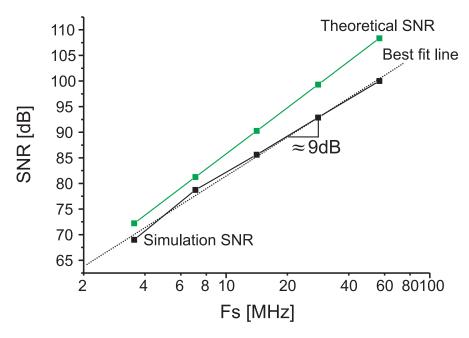

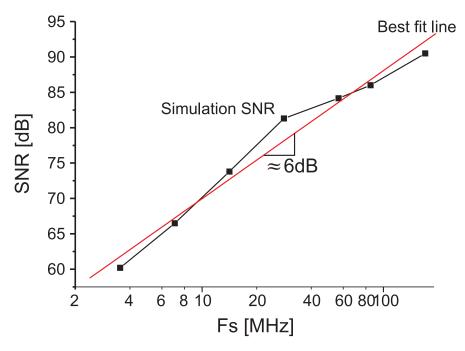

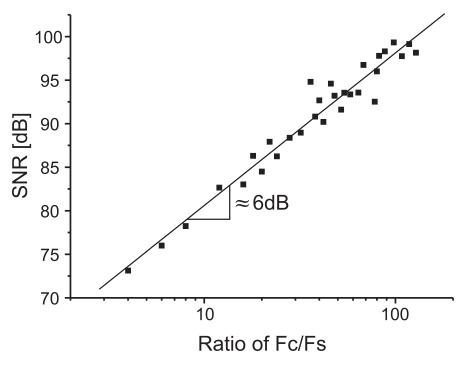

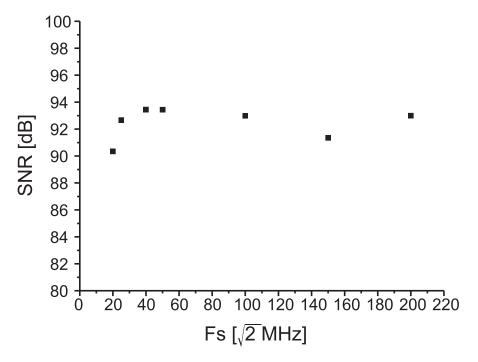

| Figure 3.15 S | Simulation of First-Order FIR Modulator as Function of $F_s$               | 56 |

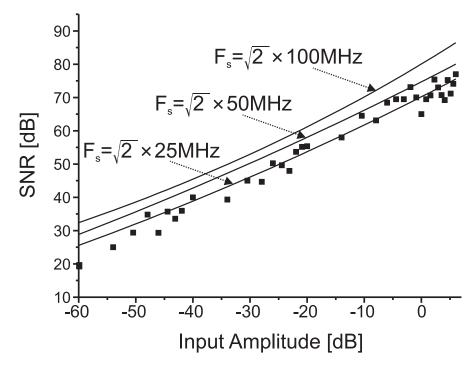

| Figure 3.16 S | Simulation of FIR Modulator as Function of Input Amplitude                 | 56 |

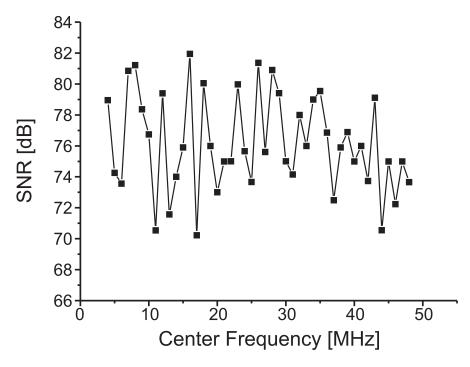

| Figure 3.17 S | Simulation of First-Order FIR Modulator as Function of $F_{VCO}$           | 57 |

| Figure 3.18 T | Total Power of Spectral Noise Components within the Baseband               | 58 |

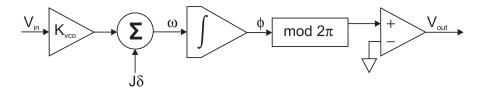

| Figure 3.19 B | Behavioral Model of a Jittered VCO                                         | 60 |

| Figure 3.20 S | Simulation of a 1 <sup>st</sup> FIR Modulator as a Function of Phase-Noise | 60 |

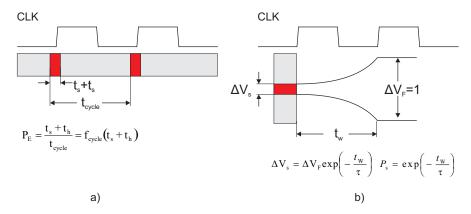

| Figure 3.21 N | Meta-Stability Illustration                                                | 62 |

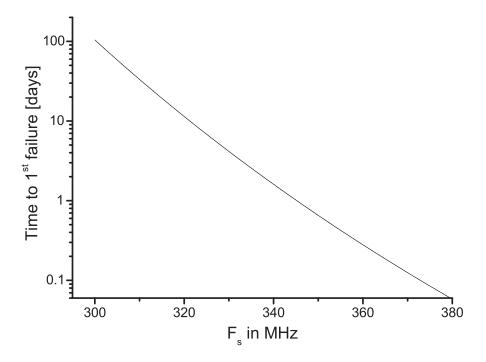

| Figure 3.22 N | Mean Time Between Failures Plot                                            | 63 |

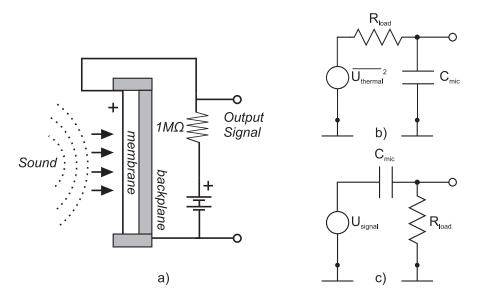

| Figure 4.1 S  | Schematic of a Condenser Microphone                                        | 67 |

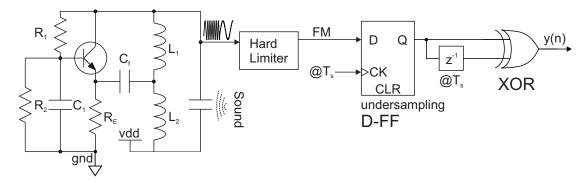

| Figure 4.2 D  | Digital Microphone Based on a LC-Oscillator                                | 69 |

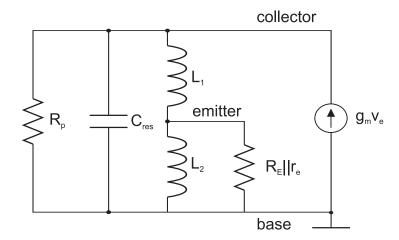

| Figure 4.3 S  | Small Signal Model of a Hartley CB Oscillator                              | 70 |

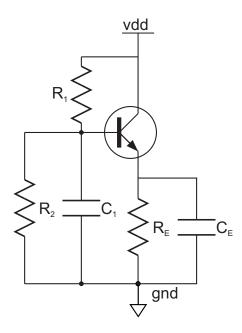

| Figure 4.4 B  | Biasing Scheme of the Oscillator                                           | 72 |

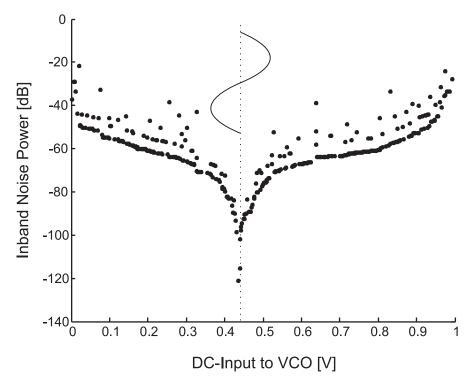

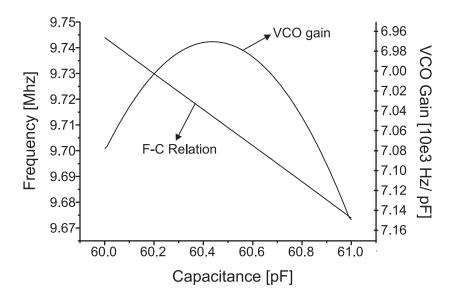

| Figure 4.5 L  | Linearity and Tuning Sensitivity of the Oscillator                         | 73 |

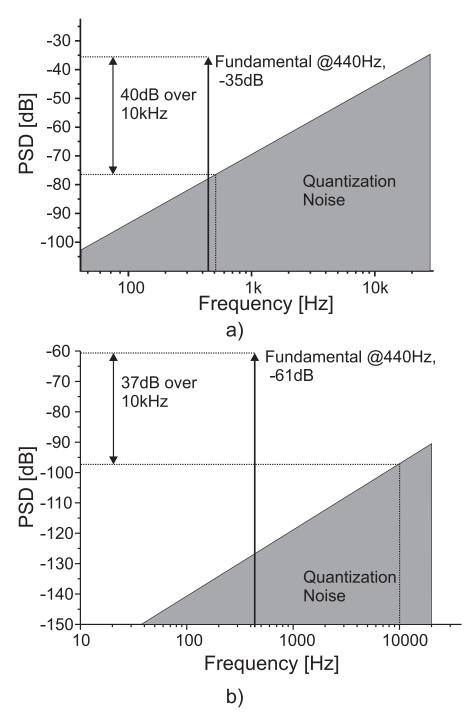

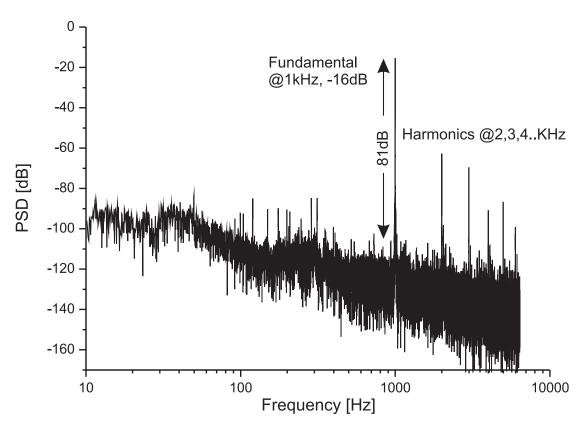

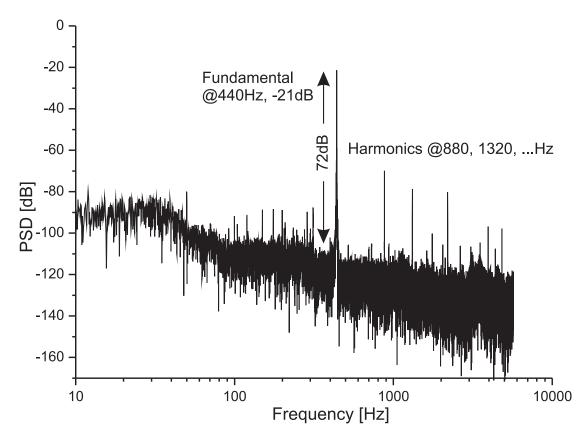

| Figure 4.6 P  | PSD Output of a 1 <sup>st</sup> Order LC-Oscillator Based FIR Modulator    | 75 |

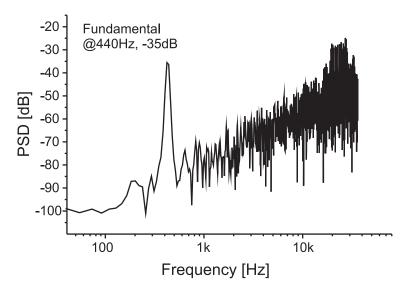

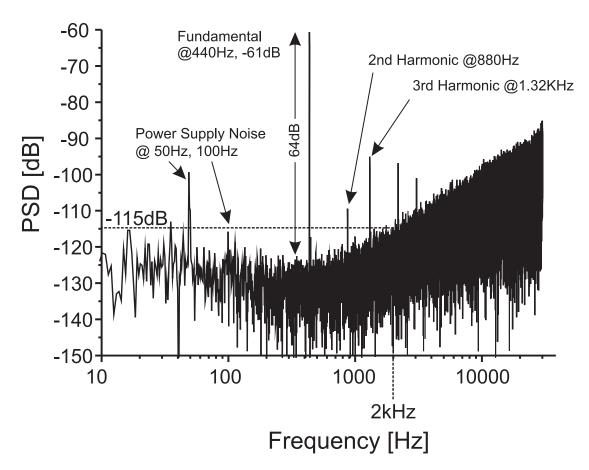

| Figure 4.7 E  | Experimental Results of a LC-Oscillator Based FIR Modulator                | 76 |

| Figure 4.8 C  | Comparison of the PSD plots between Spectre and Implemented Circuit        | 78 |

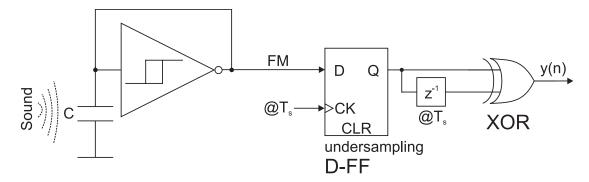

| Figure 4.9 D  | Digital Microphone Based on a Schmitt-Trigger-Oscillator                   | 79 |

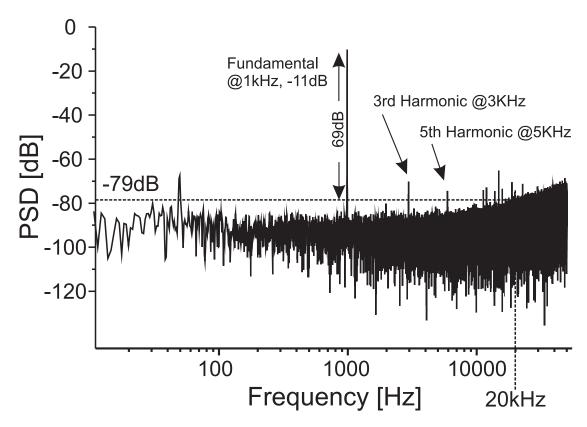

| Figure 4.10 E | Experimental Results of a Schmitt-Trigger Based FIR Modulator              | 81 |

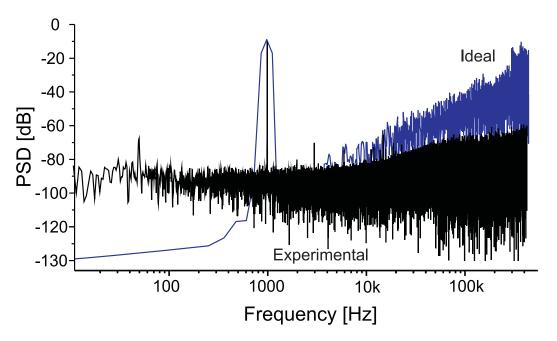

| Figure 4.11 S | Schmitt-Trigger Based FIR modulator comparend to Matlab modulator          | 81 |

| Figure 4.12 E | Experimental Results of a Conventional condenser Microphone I              | 83 |

| Figure 4.13 E | Experimental Results of a Conventional condenser Microphone II             | 84 |

| Figure 5.1 E  | Error when Sampling FM Signal                                              | 87 |

| Figure 5.2 E  | Error when Under-Sampling FM Signal                                        | 88 |

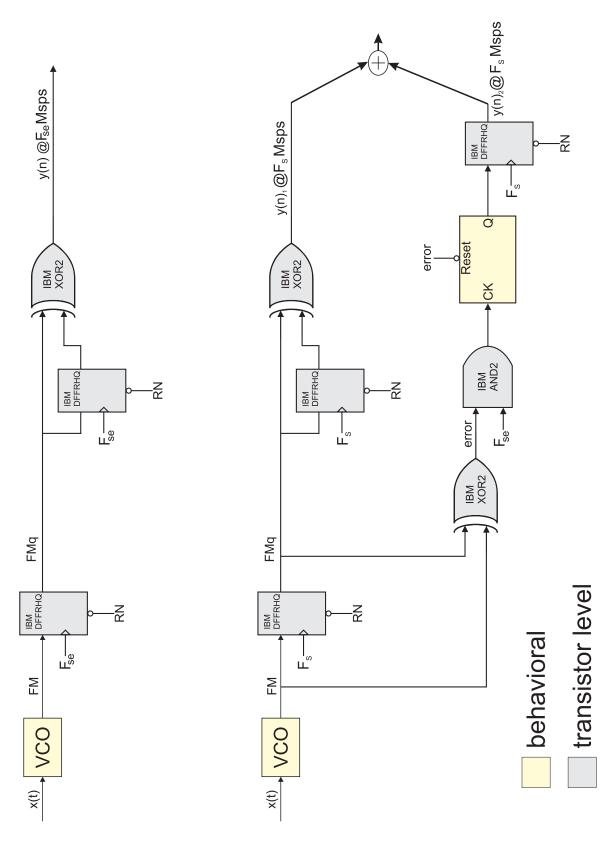

| Figure 5.3 S  | Second-Order FIR Modulator - Version I                                     | 90 |

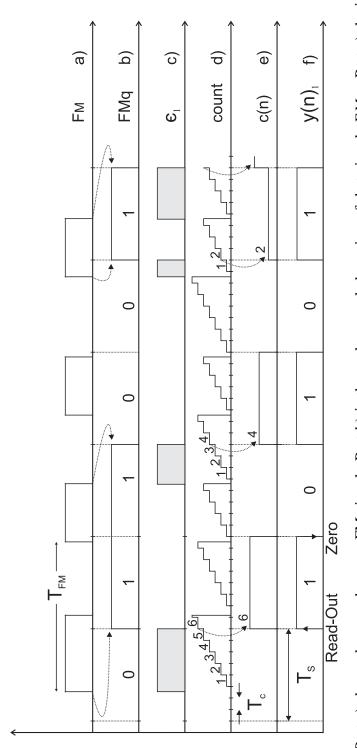

| Figure 5.4 S  | Signals in the Second-Order FIR Modulator I                                | 91 |

| Figure 5.5 S  | Signals in the Second-Order FIR Modulator II                               | 93 |

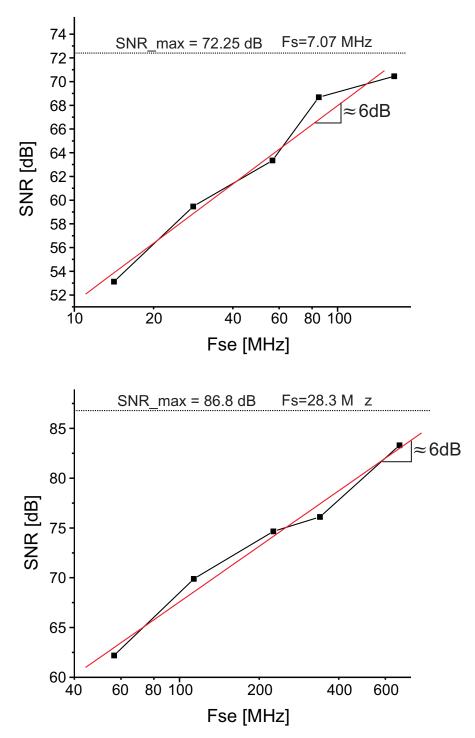

| Figure 5.6  | Simulation Results of the $2^{nd}$ Order FIR Modulator I 9        | 7  |

|-------------|-------------------------------------------------------------------|----|

| Figure 5.7  | Simulation Results of the 2 <sup>nd</sup> Order FIR Modulator II  | 8  |

| Figure 5.8  | Simulation Results of the 2 <sup>nd</sup> Order FIR Modulator III | Ю  |

| Figure 5.9  | Second-Order FIR Modulator - Version II                           | 1  |

| Figure 5.10 | Novel Noise Shaping Scheme                                        | 12 |

| Figure 5.11 | Second-Order FIR Modulator - Version II for Undersampling 10      | 13 |

| Figure 5.12 | Signals of the $2^{nd}$ Order Undersampling FIR Modulator 10      | 15 |

| Figure 5.13 | Simulation Results of the Second-Order FIR Modulator I 10         | 19 |

| Figure 5.14 | Simulation Results of the Second-Order FIR Modulator II 10        | 19 |

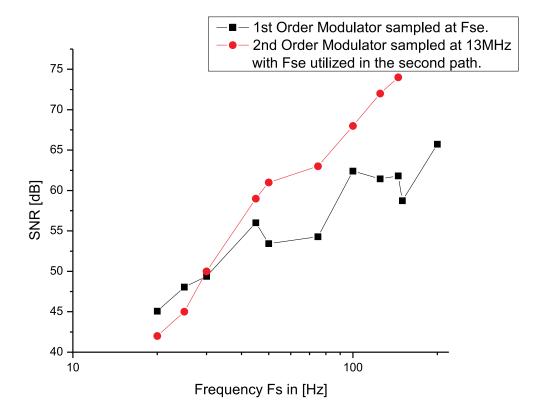

| Figure 5.15 | Testbench for the first- to second-order comparison               | 3  |

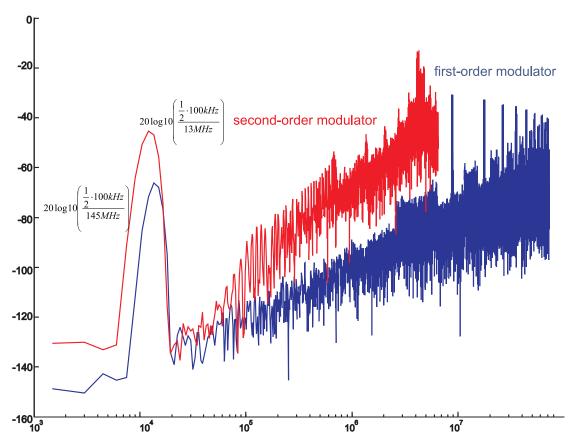

| Figure 5.16 | SNR comparison for the first and second order FIR modulators 11   | 4  |

| Figure 5.17 | PSD comparison for the first and second order FIR modulators 11   | .5 |

| Figure 6.1  | IC Approach                                                       | 23 |

## LIST OF SYMBOLS OR ABBREVIATIONS

**A/D** analog-to-digital.

**CT** continuous-time.

**D/A** digital-to-analog.

**DT** discrete-time.

$\epsilon$  quantization error introduced by the quantizer.

**f**<sub>bw</sub> band-width of interest.

**F**<sub>FM</sub> frequency of the frequency modulated signal.

**FIR** finite impulse response.

**FM** frequency modulated.

**F**<sub>c</sub> center frequency fo a voltage controlled oscillator.

**F**<sub>d</sub> decimated sampling frequency.

**F**<sub>s</sub> sampling frequency.

**F**<sub>se</sub> elevated sampling frequency.

$K_{vco}$  gain or sensitivity of a voltage controlled oscillator.

**MASH** multi-stage noise shaping.

**NTF** noise transfer function.

**Nyquist** states that the sampling frequency is twice that of the

highest signal frequency of interest.

**R** oversampling ratio.

$\sigma_{\epsilon}^2$  total noise power.

**SNR** signal-to-noise ratio.

**STF** signal transfer function.

**VLSI** very large-scale integration.

# LIST OF LISTINGS

| 1 | sdm.va             | • |  |  |  |  |  |  |  |  |  |  |  | • |  | 124 |

|---|--------------------|---|--|--|--|--|--|--|--|--|--|--|--|---|--|-----|

| 2 | 2ndVersionI.va     |   |  |  |  |  |  |  |  |  |  |  |  |   |  | 125 |

| 3 | finalLS2under.va . |   |  |  |  |  |  |  |  |  |  |  |  |   |  | 127 |

### **SUMMARY**

Analog-to-digital converters play a crucial role in modern audio and communication design. Conventional Nyquist converters are suitable only for medium resolutions and require analog components that are precise and highly immune to noise and interference. In contrast, oversampling converters can achieve high resolutions (>20bits) and can be implemented using straightforward, high-tolerance analog components. In conventional oversampled modulators, negative feedback is applied in order to control the dynamic behavior of a system and to realize the attenuation of the quantization noise in the signal band due to noise shaping. However, feedback can also introduce undesirable effects such as limit cycles, jitter problems in continuous-time topologies, and infinite impulse responses. Additionally, it increases the system complexity due to extra circuit components such as nonlinear multi-bit digital-to-analog converters in the feedback path. Moreover, in certain applications such as wireless, biomedical sensory, or microphone implementations feedback cannot be applied. As a result, the main goal of this thesis is to develop sigma-delta data converters without feedback. Various new delta-sigma analog-to-digital converter topologies are explored their mathematical models are presented. Simulations are carried out to validate these models and to show performance results. Specifically, two topologies, a first-order and a second-order oscillator-based delta-sigma modulator without feedback are described in detail. They both can be implemented utilizing VCOs and standard digital gates, thus requiring only few components. As proof of concept, two digital microphones based on these delta-sigma converters without feedback were implemented and experimental results are given. These results show adequate performance and provide a new approach of measuring.

## **CHAPTER I**

## INTRODUCTION

## 1.1 Motivation

The market for personal communication devices is rapidly expanding with the development of new services and applications. Devices such as cordless telephones, cellular telephones, and wireless LANs require low power and low cost solutions. The market for audio applications for automotive, home theater, and personal computer demands cost effective and easy interfacing solutions as well. This range of applications and devices has led to a proliferation of communication standards and modulation schemes. At the same time consumers are demanding low-cost, low-power, and small devices that satisfy these communication requirements. As a result, there has been much effort put into the in the design of integrated circuits for personal communication that can easily be integrated in a low cost technology. The relentless progress in VLSI silicon technology optimized for digital circuitry generally has made it economically advantageous to trade analog signal processing for digital signal processing. Moving from analog to digital signal processing, however, generally increases the demand on the data converters that provide the interfaces between analog and digital circuits [Manickavel and Pedar, 1974; Howell and Sander, 1969; Razavi, 1996]. One technique for providing the interface between the analog and the digital circuit is by using delta-sigma A/D converter. In literature the nomenclature delta-sigma or sigma-delta converters are equally used. However, the original name delta-sigma was coined by the inventors Inose and Yasuda and thus the term delta-sigma will be used in this work [H. Inose and Marakami, 1962]. While delta-sigma converters have been around for some time [H. Inose and Marakami, 1962], it is only in the last two decades that they have become more attractive. One reason being is that they are particularly suited for A/D conversion of narrow band signals used in audio, communication and instrumentation devices. That is, they can achieve

very high resolutions for low-bandwidths. Examples of such applications include digital telephone transmission, wireless phones, audio applications, and medical imaging. This thesis is concerned with the improvement of delta-sigma A/D converters. It is hoped that by using new and modified modulator topologies and digital signal processing the complexity of delta-sigma modulators can be reduced while still obtaining the same performance. Furthermore, as power dissipation is becoming an increasingly important issue in the design of analog to digital converters as signal processing systems move into applications requiring portability, a secondary goal of this thesis is to reduce the analog circuitry improving power dissipation.

## 1.2 Main Contributions

The main goal of this thesis is to develop delta-sigma data converters with reduced analog complexity and thus to bring the digital domain closer to the analog domain. Simplifications in the analog domain are achieved by removing the negative feedback path from delta-sigma converters while still achieving the desired results. To this extent, analog-to-digital data converters based on voltage-controlled oscillators are explored and developed. As an application, two digital microphones utilizing oscillator based analog-to-digital converters are realized. Undersampling is used as a powerful technique to efficiently deal with very high signal frequencies and thus reduce requirements on sampling and acquisition circuitry. The use of undersampling in conjunction with the use of simplified oscillator-based data converters results in a novel approach to realize digital microphones. Moreover, second-order oscillator based analog-to-digital date converters are developed, resulting in improved performance results compared to their first-order counterparts. In this context, different second-order circuit techniques are explored that result in performance improvements and/or trade-offs. In addition, a more general goal of this thesis is to develop techniques at both the architecture and circuit levels to minimize power dissipation. In the context of these goals, some key research results are summarized below:

• Demonstration of the reduction in circuit complexity of a frequency sigma-delta

modulator by utilizing a D-FF as a quantizer and differentiator.

Soell, S. and Porr, B. (2006) A VCO Based Digital Microphone Utilizing a FIR Sigma Delta Converter. IEEE International Conference on Mixed Design of Integrated Circuits and Systems

- Demonstration of a digital condenser microphone with reduced analog circuitry based on a LC-oscillator and a first-order sigma delta modulator without feedback.

- Soell, S. and Porr, B. (2007) An Undersampling Digital Microphone. IEEE International Symposium on Circuits and Systems

- Demonstration of a Schmitt trigger oscillator based digital microphone based on a first-order sigma delta modulator without feedback.

- Soell, S. and Porr, B. (2007) An Undersampling Digital Microphone Utilising Second Order Noise Shaping. IEEE International Conference on Mixed Design of Integrated Circuits and Systems

- Demonstration of utilizing undersampling as a technique to efficiently implement an oscillator based digital microphone.

- Soell, S. and Porr, B. (2007) An Undersampling Digital Microphone Utilising Second Order Noise Shaping. IEEE International Conference on Mixed Design of Integrated Circuits and Systems

- Demonstration of realizing oscillator-based higher order noise shaping analog-todigital converters.

- Soell, S. and Porr, B. (2007) An Undersampling Digital Microphone Utilising Second Order Noise Shaping. IEEE International Conference on Mixed Design of Integrated Circuits and Systems

## 1.3 Scope and Structure of the Thesis

This work is divided into six chapters. After this introduction the second chapter introduces the concept of analog-to-digital conversion and discusses methods used to characterize analog-to-digital converters. This includes both Nyquist and oversampling converters. An introduction of the most important analog-to-digital oversampling architectures such as low-pass and band-pass topologies and their performance characterization is given. In this context, essential concepts are reviewed such as decimation, undersampling, and non-idealities in oversampling analog-to-digital converters. Chapter 3 then focuses on a first order delta-sigma analog-to-digital converter without feedback. After a review of existing work, the theory of the modulator topology is explained by revisiting established frequency modulation and de-modulation techniques. New and improved first-order analog-to-digital converters are introduced and a mathematical model for performance evaluation is given. The chapter then verifies obtained results with simulations and concludes with a general discussion. These simulations include both, ideal analog-to-digital converters as well as non-ideal topologies. Subsequently, as a proof-of-concept, the discussed analog-to-digital converter is implemented in a practical application. Chapter 4 covers this. More specifically, two digital oscillator-based microphones are presented based upon analog-to-digital converters without feedback. An LC-oscillator and also a Schmitt-trigger based oscillator are used to realize digital condenser microphones. Both topologies utilize undersampling to deal with high frequency signals. Experimental results are presented and discussed. Chapter 5 then improves the performance of first order analog-to-digital converters by presenting two second-order modulator topologies, also without utilizing feedback and based on oscillators. A mathematical background is established and the topologies are evaluated using simulations. Again, simulation results are presented which also address nonlinearities. Chapter 6 contains a summary of the conclusions of this research and the goals which were achieved, along with a comparison with existing works. This is followed by a proposal for future research, which is given in more detail at the end of Chapter 6.

## **CHAPTER II**

## SIGMA-DELTA MODULATORS

## 2.1 Nyquist-rate A/D Converters

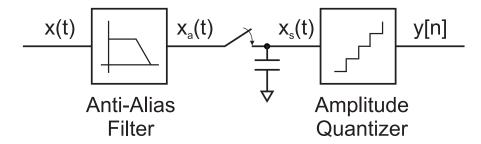

Analog-to-digital conversion is the process of encoding an analog signal that is continuous in time and amplitude into a signal that is discrete with respect to time and quantized with respect to amplitude. There are three fundamental operations involved in the conversion process of a general A/D system. These are illustrated in Figure 2.1. The analog input signal, x(t), first passes through a bandlimiting low-pass filter, removing the signal components that lie above one-half of the sampling rate of the subsequent sampler. Otherwise, from the Nyquist sampling theorem [Nyquist, 1928], high frequency components of x(t) would alias into the baseband upon sampling, causing distortion. Following the anti-aliasing filter, the now bandlimited signal,  $x_a(t)$ , is sampled, thus yielding the discrete-time signal,  $x_s(t)$ , which is still continuous in amplitude. The sampled-data analog signal is then quantized in amplitude by utilizing a quantizer before being encoded into the digital output data signal, y[n].

#### 2.1.1 Sampling

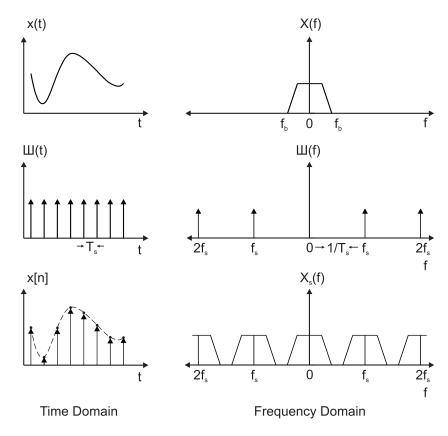

In the sampling process, a continuous signal is sampled at uniformly spaced time intervals,  $T_s$ . The samples x[n], of the continuous time signal, x(t) can be expressed as  $x[n] = x(nT_s)$ . The process of sampling a continuous-time signal is shown in Figure

**Figure 2.1:** Fundamental operations comprising analog-to-digital conversion.

**Figure 2.2:** Sampling Process of an Analog Signal. On the left side the signals are represented in the time-domain, to the right in the frequency domain.

2.2. In the figure, a continuous signal, x(t), is multiplied by a Dirac comb, often also described as a Shah function, III(t). The Shah function is a series of Dirac pulses spaced at width  $T_s$  [Bracewell, 2000, pp.81ff]:

$$III(t) = \sum_{n = -\infty}^{\infty} \delta(t - nT_s). \tag{2.1}$$

The effect, in the frequency domain, of the sampling process is to create periodically repeated versions of the signal spectrum, X(f), at multiples of the sampling frequency  $F_s = 1/T_s$ . The spectrum of the sampled signal,  $X_s(f)$ , is depicted in the right hand side of Figure 2.2. In general, the signal,  $X_s(f)$ , can be reconstructed back to its continuous counterpart, x(t), if the repeated versions of the signal spectrum do not overlap. As a result, the signal must be band limited to half the sampling rate,  $F_s$ . In turn, a signal with bandwidth  $f_b$  must be sampled at a rate great than twice of its bandwidth,  $F_s \ge 2f_b$ . This is known as the Nyquist-Shannon sampling theorem [Nyquist, 1928]. An important fact to note is that sampling is a linear operation. Therefore, the effects of sampling amplitude can be divided into two effects: the effect of sampling the original signal,

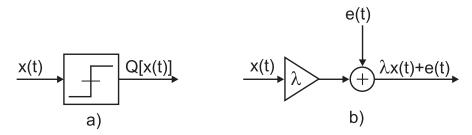

**Figure 2.3:** Additive Quantizer Model: a) 1-bit quantizer b) noise model including gain variation

and the effect of sampling noise superimposed with the original input. Nyquist rate converters sample analog signals which have maximum frequencies slightly less than the Nyquist frequency.

#### 2.1.2 Quantization

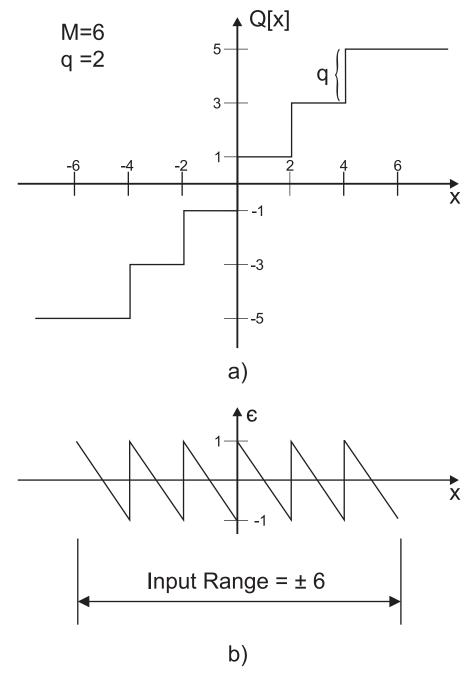

Once sampled, the time-discrete signal samples must also be quantized in amplitude to a finite set of output values. Quantization is the process of converting an analog signal into a finite range number system [Goodall, 1951]. Quantization thus introduces an error signal that depends on how well the signal is being approximated. Unlike sampling, quantization of a signal is a non-reversible operation [van de Plassche, 2003, pp.7ff]. The process of quantization in shown in Figure 2.3 a) where a 1-bit quantizer maps an analog signal into the digital domain by rounding up or down to the nearest step size. Alternatively, an example of multi-level quantization is depicted in figure 2.4 a). The quantization step, q, of a b-bit quantizer is given as:

$$q = \frac{V_{ref}}{2^b},\tag{2.2}$$

where  $V_{ref}$  is a reference signal. Figure 2.3 b) depicts a model for an approximation to the 1-bit quantizer. [van Engelen and van de Plassche, 1999, p.38]. The model includes a time invariant gain  $\lambda$  because adding quantization power to to an input signal with variable power would not model the 1-bit quantizer accurately. In case of the 1-bit quantizer the gain can have any value greater than zero. For multi-bit quantizers, the gain would be closer to unity. Assuming a gain of unity, the quantization error is given as the difference between the quantized input, Q[x(t)], and ideal input, x(t):

$$\epsilon(t) = Q[x(t)] - x(t). \tag{2.3}$$

**Figure 2.4:** Part a) depicts a uniform b-bit quantizer utilizing M=6 quantization levels, with a quantization step of q=2. Here, the input to the quantizer is a ramp-signal. Part b) shows the introduced error  $\epsilon$  which is the sawtooth error signal.

**Figure 2.5:** Quantization error with a uniform probability density.

The error  $\epsilon(t)$  forms a periodic sawtooth waveform in this case as depicted in figure 2.4 b). When expressed as a Fourier series expansion the quantization error  $\epsilon(t)$  is given as [van de Plassche, 2003, p.12]:

$$\epsilon(t) = \frac{q}{\pi} \sum_{k=1}^{\infty} \left\{ \frac{1}{k} \sin\left[2\pi k \frac{x(t)}{q}\right] \right\}$$

(2.4)

Equation 2.4 illustrates that the quantization error  $\epsilon(t)$  due to quantization forms a harmonic series of phase-modulated sinusoids. This can be seen when realizing that the argument of each sine term is a linear function of input x(t). Consequently, phase modulation maps to amplitude quantization [Hawksford, 2002, p.589]. The model in Figure 2.3 b) assumes that the quantization error is largely uncorrelated from sample to sample and has equal probability of lying anywhere in the range of  $\pm \frac{q}{2}$  ([van de Plassche, 2003], p.7 ff). This property is illustrated in Figure 2.5. However, for dc-inputs and inputs that change regularly by multiples or sub-multiples of the step size in between sample times, as happens in feedback circuits, the linear noise model does not hold anymore [Norsworthy et al., 1997, p.5]. Under the assumption that the error is uncorrelated to the input signal and has uniform distribution, its total noise power value  $\sigma_{\epsilon}^2$  is given by [Staff, 1982, p.55]:

$$V_{Q_{rms}}^{2} = \sigma_{\epsilon}^{2} = \int_{-q/2}^{q/2} \epsilon^{2} P(\epsilon) d\epsilon = \frac{1}{q} \int_{-q/2}^{q/2} \epsilon^{2} d\epsilon = \frac{q^{2}}{12}.$$

(2.5)

The average value of the error is zero with the assumptions made. Since the size of the quantization level q is halved for each additional quantizer bit, equation 2.5 shows that the noise power decreases by 6dB for each additional bit. For a sinusoidal input with peak-to-peak amplitude,  $V_A$ , of  $2^bq/2$ , the rms signal value,  $V_{A_{rms}}$ , is given by  $\frac{2^bq}{2\sqrt{2}}$ . Then

the signal-to-noise ratio can be calculated:

$$SNR_{dB} = 20log \left( \frac{V_{A_{rms}}}{V_{Q_{rms}}} \right)$$

$$= 20log \left( \frac{2^{b}q}{2\sqrt{2}} \frac{1}{\sqrt{12}} \right) = 20log \left( \sqrt{\frac{3}{2}} 2^{b} \right)$$

$$= 6.02 b + 1.76 dB.$$

(2.6)

Equation 2.6 shows that the signal-to-noise ratio of a quantizing system increases by 6 dB when an extra bit is added. It is often useful to express equation 2.5 as a total noise power density per unit bandwidth [van de Plassche, 2003, pp.9ff],  $\sigma_e^2(f)$ :

$$\sigma_{\epsilon}^{2}(f) = \frac{q^{2}}{12f_{bw}} = \frac{q^{2}}{6F_{s}},\tag{2.7}$$

where  $f_{bw}$  is the quantization noise bandwidth and  $F_s$  is the sampling frequency. Since the signal-to-noise ratio is calculated over a bandwidth equal to half the sampling frequency we have  $f_{bw} = 1/2F_s$ . Thus, for systems that use Nyquist sampling the signalto-noise ratio as a density can be written as:

$$SNR = 2^{b-1} \sqrt{3F_s} (2.8)$$

Then the SNR for a system with a bandwidth equal to  $f_{bw}$  is found by dividing equation 2.8 by  $\sqrt{f_{bw}}$  to give:

$$SNR = 2^{b-1} \sqrt{\frac{3F_s}{f_{bw}}}$$

(2.9)

Equation 2.9 is convenient for dynamic range calculations of systems which do not use Nyquist sampling. As will be shown shortly increasing the ratio  $\frac{F_s}{f_{bw}}$  reduces the quantization noise density, resulting in higher SNR. Summarizing, if the resolution of an A/D converter is limited by quantization noise, then its dynamic range increases by approximately 6dB with every additional bit of resolution, b. It might be noted that in practical applications sometimes circuit noise, thermal noise, or other non-linearities determine the ultimate resolution of the A/D converter.

#### 2.1.3 Limitations of Nyquist-Rate A/D Converters

A typical limiting factor in Nyquist-rate architectures is that some operations such as comparison, amplification, or subtraction must be performed to the overall precision of the converter [Aziz et al., 1996, p.64]. This typically translates into the need for precise component matching unless special calibration, error-correction, or trimming techniques are used. A steep anti-aliasing filter must also precede any Nyquist-rate A/D converter. This band-limiting filter rejects frequency components of the signal located above one-half of the sampling frequency in order to prevent aliasing distortion. These anti-aliasing filters are often quite difficult to design to allow for a large signal bandwidth [van de Plassche, 2003, pp.27ff]. In addition, it is still quite difficult to realize precise analog filters to high order in a VLSI technology without resorting to active circuits.

## 2.2 Over-Sampling A/D Converters

The demands on the circuitry of the A/D converter and their individual required precision can be relaxed by exploiting speed, or oversampling [Walden, 1999]. The use of over-sampling is advantageous as it alleviates the problems mentioned for Nyquist A/D converters above. In particular, Figure 2.6 shows how oversampling can reduce the demands on the aliasing filter. The spectrum of the input signal is shown in 2.6 a) as having a bandwidth of interest of 22kHz. Since the sampling frequency is 48kHz, anything above 24kHz will be aliased into the band of interest. Thus a steep anti-aliasing filter is needed. With such a filter the sampled data has the spectrum as shown in Figure 2.6 b). When oversampling the input signal the anti-aliasing filter can be relaxed. This is illustrated in 2.6 c) and d). It is now sufficient for the filter to attenuate signals above 72kHz without polluting the band of interest with aliased components. In particular, Figure 2.6 d) shows that the band of interest does not contain any aliased components as oversampling was used. Besides reducing the requirements on aliasing filters, the main advantage of oversampling is that it lowers the noise power introduced by quantization in the band of interest. This is because the quantization error is spread out

Figure 2.6: Comparison of aliasing filter for Nyquist and oversampling converters.

Figure 2.7: Quantization noise power for two oversampling ratios

over a larger frequency band. As a result the error density is reduced and the effective resolution of the converter increases [Cherry and Snelgrove, 1999]. This is depicted in figure 2.7. Figure 2.7 a) shows the quantization noise power for a Nyquist converter. Meanwhile, in Figure 2.7 b) an oversampling factor of 4 reduces the quantization noise power in the band of interest by a factor of 4. Only a relatively small fraction of the total noise power falls within the band of interest and the noise outside the bandwidth can be greatly attenuated by means of digital low-pass filtering. In general, for each doubling of the sampling frequency  $F_s$ , 1/2 bit of increase in resolution is achieved [Johns and Martin, 1997, p.535]. The signal-to-noise ratio is then given as:

$$SNR = 2^{b-1} \sqrt{3} \sqrt{R}, (2.10)$$

where, the oversampling ratio, R, is defined as  $R = \frac{F_s}{2f_{bv}}$ . Converting to decibels gives:

$$SNR_{dB} = 6.02 b - 1.25 + 10\log(R)$$

. (2.11)

Again, the total noise power introduced due to quantization is exactly the same as in the case of a Nyquist rate converter, but its frequency distribution is different because of the higher sampling rate.

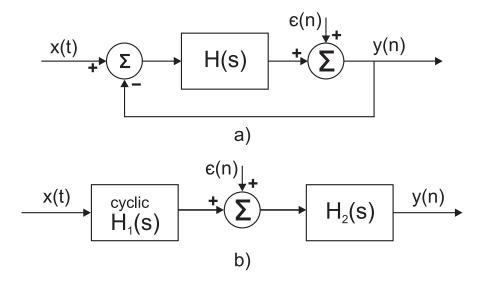

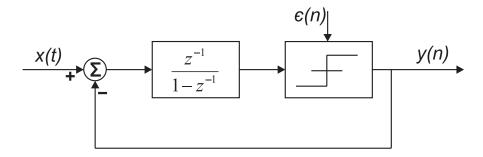

**Figure 2.8:** First-Order Delta-Sigma Modulator. Figure a) shows the typical implementation of an arbitrary delta-sigma modulator. Part b) depicts the less conventional modulator employing no negative feedback.

#### **2.2.1** The FIR Modulator Principle

The basic thought behind every delta-sigma modulation is the exchange of resolution in time for resolution in amplitude. That is, That is, narrow band signal can be digitized to a very accurate level. As will be shown later, conventional delta-sigma modulators are synonymous with negative feedback; however, they can also be realized without negative feedback. Thus, there are essentially two main implementations for the basic delta-sigma modulator, both of which are depicted in Figure 2.8. Part a) of the figure shows a delta-sigma modulator consisting of a coarse analog-to-digital converter, a digital-to-analog converter, and a loop-filter, H(s), placed within a feedback loop. In this thesis, however, the focus is on delta-sigma converters without feedback. A general principle is depicted in figure 2.8 b). This modulator also consists of a coarse analogto-digital (A/D) converter and a loop-filter,  $H_1(s)$ , but lacks the D/A converter in the feedback loop. Instead a second filter,  $H_2(s)$ , is needed. In the case of the modulator with feedback the input signal, x(t), gets quantized to form a digital signal [Cherry and Snelgrove, 1999, p.2]. The D/A converter converts the digital output back to an analog signal which is then compared to the input signal as depicted in figure 2.8 a). The binary pulses represent the in the integrator accumulated sign of the difference between the input and feedback signals, hence the prefix delta  $(\Delta)$ . The feedback loop causes the

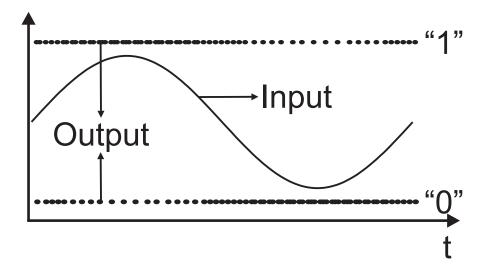

**Figure 2.9:** Input and output of a first-order delta-sigma modulator.

quantization error to be suppressed for signals falling within the pass-band of the loop filter. The prefix sigma stems from the use of an integrator within the filter (summation =  $\Sigma$ ). In the case of the modulator without feedback, the input signal, x(t), gets quantized to form a digital signal also. However, since no feedback loop, the quantization error will be noise shaped by a second filter  $H_2(s)$ . Consequently, the prefix ( $\Delta$ ) does not apply. However, the prefix  $\Sigma$  from the use of an integrator within the filter  $H_1(s)$  can still be used. The notation used to describe the modulator without feedback will be finite impulse response modulator (*FIR modulator*). This is similar to *FIR* filters as they lack a feedback loop also [Chan and Rabiner, 1973]. In either case of modulator, when the sinusoidal input to the two modulator topologies is close to a plus full scale, the digital output is positive during most clock cycles. Similarly, when the input is close to a full negative scale, the digital output is negative during most clock cycles. In both cases, the local average of the digital modulator output tracks the analog input. When the input is near zero, the value of the modulator output varies rapidly between a plus and a minus full scale with approximately zero mean. This is depicted in Figure 2.9. To further analyze the two modulator topologies we need to apply the previously introduced three main principles that make up any sigma-delta modulator and FIR modulator. These are over-sampling, quantization, and noise shaping. The properties of quantization outlined in section 2.1.2 apply to the two modulator topologies. As mentioned in section

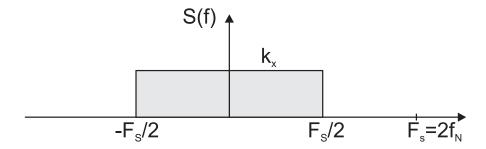

Figure 2.10: Noise spectrum of a Nyquist converter

2.2, specifically equation 2.11 showed that for doubling the sampling frequency a 3dB increase in resolution can be achieved. Delta-sigma and FIR modulators take advantage of this and over-sample to achieve better resolution. The performance modeling criteria designated the introduced quantization noise process as white, which means that the noise power is uniformly distributed between  $\left[\frac{-F_s}{2}, \frac{F_s}{2}\right]$ . This is depicted in figure 2.10. While this is true for delta-sigma modulators, it will be shown later that the quantization noise power might not necessarily be white for FIR modulators. Still, the total noise power is given by  $V_{Q_{rms}}^2 = \sigma_{\epsilon}^2$ . The spectral density height,  $k_x$ , can then be calculated [Johns and Martin, 1997, p.533]:

$$\int_{-\frac{F_s}{2}}^{\frac{F_s}{2}} S^2(f)df = \int_{-\frac{F_s}{2}}^{\frac{F_s}{2}} k_x^2 df = k_x^2 F_s = \sigma_{\epsilon}^2.$$

(2.12)

Equation 2.12 can be solved for  $k_x$  to give:

$$k_x = \sigma_\epsilon \sqrt{\frac{1}{F_s}}. (2.13)$$

Equation 2.13 shows that the total quantization noise power will be reduced by 3dB for doubling the sampling frequency  $F_s$ . In addition to this over-sampling advantage, both modulator topologies utilize noise shaping to further attenuate the quantization error.

#### 2.2.2 The Concept of Noise-Shaping

Noise-shaping is generally done by utilizing a high-pass filter to suppress unwanted components in the band of interest. There are two ways to realize a high-pass filter for the introduced quantization noise. Firstly, the in-band quantization noise power can be suppressed with a high-pass dramatically by embedding the quantizer in a feedback loop [Inose et al., 1966]. A filter can then be used to spectrally shape the quantization noise

**Figure 2.11:** First order Delta-Sigma (a) and FIR modulator (b) with an additive noise source for the quantizer.

so that the majority of it is moved out of the signal pass-band. Figure 2.11 a) shows this implementation. Notice that the quantizer was replaced by an additive noise source  $\epsilon(n)$ . Secondly, a high-pass filter can be implemented by using an explicit filter, such as a differentiator. This is depicted by  $H_2(s)$  in figure 2.11 b). For the two modulator topologies two transfer functions can then be written: a signal transfer function from the input to the output (STF), and a noise transfer function (NTF) from the input of the noise to the output. These are given for the delta-sigma modulator as:

$$STF_{DSM}(s) = \frac{y(n)}{x(t)} = \frac{H(s)}{1 + H(s)},$$

(2.14)

$$NTF_{DSM}(s) = \frac{y(n)}{\epsilon(n)} = \frac{1}{1 + H(s)}.$$

(2.15)

In the same way we have for the FIR modulator:

$$STF_{FIR}(s) = \frac{y(n)}{x(t)} = H_1(s)H_2(s),$$

(2.16)

$$NTF_{FIR}(s) = \frac{y(n)}{\epsilon(n)} = H_2(s). \tag{2.17}$$

Equation 2.15 shows that if the quantization noise is to be suppressed in the baseband, H(s) must have a large gain. As a result Equation 2.14 will become unity and the input signal passes the modulator un-attenuated. Equation 2.15 will then implement a

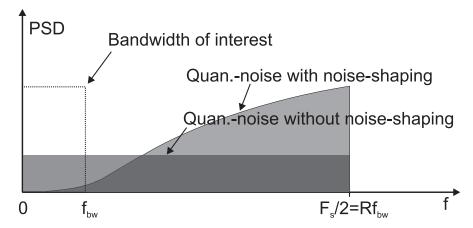

**Figure 2.12:** Spectrum at the output of an oversampling A/D converter: with and without noise-shaping. Note that the area under both curves is the same.

high-pass filter which shapes the quantization noise introduced by the quantizer. This depicted in Figure 2.12 which shows that noise shaping can further attenuate the quantization noise in the band of interest,  $f_{\rm bw}$ . In the case of the FIR modulator  $H_2(s)$  should attenuate the quantization error with a high-pass filter. For the STF to be unity,  $H_1(s)$  should ideally be the inverse of  $H_2(s)$ . It is important to note that the total noise level remains the same; noise shaping only pushes the quantization noise to higher frequencies where they can then be removed by an appropriate filter. There are various transfer functions for H(s) that can realize a high gain in the feed-forward path of figure 2.11 a). One class using an integrator is especially suited for VLSI implementation as the analog circuits required to implement the transfer function are simple and robust. The same applies to the FIR modulator, where  $H_1(s)$  is a cyclic continuous-time integrator and  $H_2(s)$  a high-pass filter or differentiator. The reason for choosing a cyclic integrator is due to the lack of feedback in the FIR modulator. As will be shown later, a voltage-controlled oscillator can realize such a cyclic integrator.

#### 2.2.3 Limit Cycles and Idle Tones

The performance modeling criteria in section 2.2.1 designated the noise process as white, which means that the noise power is uniformly distributed between  $\left[\frac{-F_s}{2}, \frac{F_s}{2}\right]$ . This is the basis for equation 2.12 which is used to predict the resolution of the various delta-sigma modulator topologies. This assumption is suitable for most busy input signals. However, for dc or slowly varying inputs, the white-noise model is far from

exact as the quantization error will be heavily correlated with the input signal [van Engelen and van de Plassche, 1999, p.8]. When the input signal is dc, the delta-sigma modulator output will bounce between two levels keeping its mean equal to the input signal. For certain dc input values the output sequence will be repetitive [Friedman, 1988]. If the repetition frequency lies in the signal band, the modulation will be noisy, if not, it will be quiet. Repetitive patterns that are present in the output of the modulator under zero input conditions are called idle patters. For example, the periodic pattern of  $[1, -1, 1, -1, 1, -1, \cdots]$  is defined as a first-order limit cycle [Magrath and Sandler, 1995, p.846]. Idle patterns are a result of limit cycles. These limit cycles create tones in the frequency spectrum. In general, a dc input signal can be expressed as a vulgar fraction,  $A_{dc} = \frac{n}{d}$ , with gcd(n, d) = 1. Then, the repetition frequency,  $F_R$ , for a first-order sigma delta modulator is given by [van Engelen and van de Plassche, 1999, p.46]:

$$F_R = \begin{cases} \left(1 - n\frac{2A_{dc}}{q}\right) \frac{1}{2}F_s & n \text{ odd} \\ \left(n\frac{2A_{dc}}{q}\right) \frac{1}{2}F_s & n \text{ even} \end{cases}$$

(2.18)

The low frequency repetitions in the output of a first-order delta-sigma modulator due to small dc-inputs cause a deviation in the signal-to-noise ratio as expressed by equation 2.26. This is due to the repetition frequencies residing within the band of interest,  $f_{bw}$ , over which the signal-to-noise ratio is calculated. As a result, for a constant sampling frequency,  $F_s$ , the quantization noise power will be a strong function of the power of the input signal. As will become apparent later, FIR modulators experience also idle tones and limit cycles which are equivalent to the idle tones and limit cycles in conventional Delta-Sigma topologies. However, since no feedback is involved in FIR modulators, these FIR topologies have no infinite filter response. Chapter 3 will treat the spectral behavior of FIR modulators in more detail.

## 2.3 Delta-Sigma Topologies

The two most commonly found delta-sigma modulators implement either a low-pass or a band-pass, depending on the desired application. These two architectures are analyzed in the next two sections. The methods used here are partially applicable to the analysis

Figure 2.13: First-order low pass delta-sigma modulator with a 1-bit quantizer

of the FIR modulators which are covered in chapter 3.

#### 2.3.1 Delta-Sigma Low Pass

If the signal of interest extends to dc then a low-pass modulator topology should be utilized. A discrete first-order low-pass delta-sigma modulator is shown in Figure 2.13. The filter H(z) was replaced with a one unit delay discrete-time integrator [Norsworthy et al., 1997, pp.5ff]. For the following analysis the quantizer was replaced with an additive noise source and a gain of unity. More accurate models for a 1-bit quantizer would include not only a time invariant gain  $\lambda$  but also a phase uncertainty. The reader is referred to [van Engelen and van de Plassche, 1999] which includes both parameters for a stability analysis of delta-sigma converters. By straightforward analysis of the system in Figure 2.13 the following signal and noise transfer functions, STF(z) and NTF(z), are obtained:

$$STF(z) = \frac{y(n)}{x(t)} = z^{-1},$$

(2.19)

$$NTF(z) = \frac{y(n)}{e(n)} = 1 - z^{-1}.$$

(2.20)

Clearly, the signal transfer function only introduces a unit delay and leaves the signal unaltered, whereas the noise transfer function high-pass filters the introduced quantization noise. Under the assumption that the quantization noise is white with power S(f), the total noise power in the range of  $[0...f_{bw}] = [0...F_s/2R]$  is given as:

$$P_{total} = \int_{-f_{bw}}^{f_{bw}} S^{2}(f)|NTF(z)|^{2}df = \int_{-f_{bw}}^{f_{bw}} \frac{q^{2}}{12} \frac{1}{F_{s}}|NTF(z)|^{2}df.$$

(2.21)

Here,  $F_s$  is the sampling frequency,  $f_bw$  the band of interest, and S(f) is the level of the noise power spectral density given by equation 2.13. With the help of equation 2.20, the magnitude squared of an  $L^{th}$  noise transfer function is given by:

$$\left|NTF(e^{2\pi jf/F_s})\right|^{2L} = \left|1 - e^{-2\pi jf/F_s}\right|^{2L}

= \left|sin\left(\frac{\pi f}{F_s}\right)2je^{-\pi jf/F_s}\right|^{2L}

= \left[2sin\left(\frac{\pi f}{F_s}\right)\right]^{2L}.$$

(2.22)

Making the assumption that,  $f_{bw} \ll F_s$ , one can approximate  $sin(\pi f/F_s)$  with  $(\pi f/F_s)$ . With this approximation we can re-write the integral in Equation 2.21 as a function of the sampling frequency,  $F_s$ , the oversampling ratio, R, and quantizer step, q:

$$P_{total} = \int_{-f_{bw}}^{f_{bw}} \frac{q^2}{12F_s} \left[ 2\left(\frac{\pi f}{F_s}\right) \right]^{2L} df$$

$$= \frac{q^2}{12} \left(\frac{\pi^{2L}}{2L+1}\right) \left(\frac{1}{R^{2L+1}}\right). \tag{2.23}$$

In the case of a converter with *b* quantization bits, the *rms*-value of the maximal signal amplitude which does not cause the quantizer to overload is given as:

$$V_{A_{rms}} = 2^b \frac{q}{2\sqrt{2}}. (2.24)$$

For a sinusoidal input signal the input power is then given as:

$$P_{sig} = (V_{A_{rms}})^2 = \frac{q^2 2^{2b}}{8}. (2.25)$$

Utilizing Equation 2.23 and Equation 2.25 the signal-to-noise ratio can be obtained. The signal-to-noise ratio for an  $L^{th}$  order low-pass modulator with an oversampling ratio R and an b-bit quantizer is given as the ratio of the signal power and the noise power resulting in:

$$SNR_{dB} = 10log\left(\frac{P_{sig}}{P_{total}}\right)$$

$$= 10log\left(\frac{q^{2}2^{2b}}{8}\right) - 10log\left(\frac{q^{2}}{12}\left(\frac{\pi^{2L}}{2L+1}\right)\left(\frac{1}{R^{2L+1}}\right)\right)$$

$$= 10log\left(\frac{3}{2}R^{2L+1}\frac{2L+1}{\pi^{2L}}2^{2b}\right).$$

(2.26)

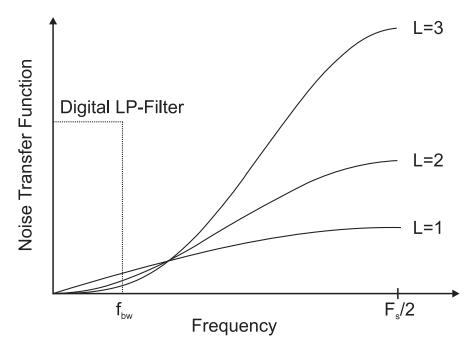

**Figure 2.14:** First, second, and third order low-pass noise transfer functions.

Equation 2.26 shows that for each doubling of R the signal-to-noise ratio improves by 9dB for a first-order low-pass with 1-bit quantizer. Mainly, 3dB are achieved due to oversampling and 6dB are achieved due to noise shaping. For an order L modulator the noise falls by 3(2L+1) dB for every doubling of R. This is depicted in Figure 2.14 which shows the attenuation of the noise in the band of interest which can be achieved for higher order noise transfer functions. Note, that compared to the first order sigma delta noise transfer function, higher order noise transfer functions provide more quantization noise suppression over the low frequency signal band and more amplification of the noise outside the signal band.

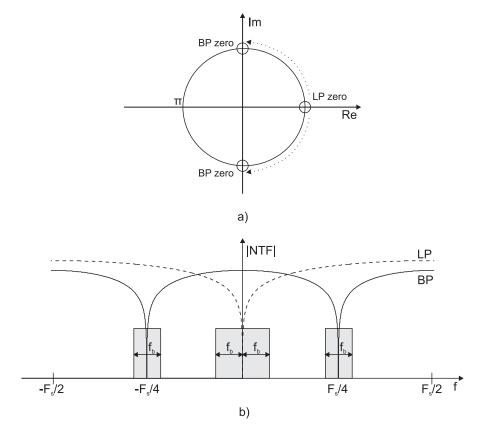

#### 2.3.2 Delta-Sigma Band Pass

So far, it was assumed that the sampling frequency,  $F_s$ , is much greater than the Nyquist rate. For low-pass signals, the highest frequency component is also the signal bandwidth  $f_{bw}$ . If a signal with bandwidth  $f_{bw}$  is narrow band but is located at a center frequency of  $f_c$ , its highest frequency component is now  $f_c + f_b$ . If  $f_c$  is large, choosing the sampling frequency much greater than the highest frequency component as in the low-pass case will yield unreasonable large sampling frequencies. Therefore, for bandpass modulation the sampling frequency is chosen to be much higher than the bandwidth of the

**Figure 2.15:** Low-pass to band-pass transformation: a) transformation of the NTF zeros b) resulting NTF spectrum

signal, rather than its highest frequency component [Jayaraman et al., 1997; Raghavan et al., 2001b]. The oversampling ratio is then given as  $R = \frac{F_s}{2(f_{max} - f_{min})}$  [Norsworthy et al., 1997, p.286]. The simplest way to design a bandpass modulator is to start with a low-pass modulator and apply a lowpass-to-bandpass transformation. For instance, applying the  $z^{-1} \rightarrow -z^{-2}$  transformation maps the zeros from dc to  $\pi/2$ . This transformation is particularly attractive as it does not affect the dynamics of the prototype low-pass modulator [Norsworthy et al., 1997, p.286]. The transformation has effectively doubled the number of zeros of the low-pass noise transfer function and rotated these zeros in the z-plane from z = 1 to z = j, as depicted in Figure 2.15. In the frequency domain, the noise suppression region has been shifted from dc to  $\pm Fs/4$ . Another transformation is the  $z \rightarrow \frac{z+a}{az+1}$ ,  $-1 \le a \le 1$  transformation which gives full control over passband location but does not preserve modulator dynamics [Norsworthy et al., 1997, p.287]. Note that the order of real band-pass modulators refers to the number of poles in the noise transfer function. With this definition, a fourth-order modulator has only two zeros in

the noise transfer function and the quantization noise is only suppressed with a secondorder transfer function in the signal passband. Thus, the order of a band-pass modulator is defined as 2L. The signal-to-noise ratio of a bandpass modulator can be estimated in the same manner as in the case of a low-pass modulator. If the  $z^{-1} \rightarrow -z^{-2}$  transformation is extended to the  $L^{th}$  order noise-transfer function of a low-pass architecture, the resulting magnitude squared of the noise transfer function is given as:

$$\left|NTF(e^{2\pi jf/F_s})\right|^{2L} = \left|1 + e^{-4\pi jf/F_s}\right|^{2L}$$

$$= \left|\cos\left(2\frac{\pi f}{F_s}\right)2je^{-2\pi jf/F_s}\right|^{2L}$$

$$= \left[2\cos\left(2\frac{\pi f}{F_s}\right)\right]^{2L}.$$

(2.27)

The quantization noise power over the frequency band of  $F_s/4 \pm f_{bw}$  is given as:

$$P_{total} = \int_{-\frac{F_s}{4} + \frac{f_{bw}}{2}}^{-\frac{F_s}{4} - \frac{f_{bw}}{2}} N(f)|NTF(z)|^2 df + \int_{\frac{F_s}{4} + \frac{f_{bw}}{2}}^{\frac{F_s}{4} - \frac{f_{bw}}{2}} N(f)|NTF(z)|^2 df$$

$$= 2 \int_{\frac{F_s}{4} + \frac{f_{bw}}{2}}^{\frac{F_s}{4} - \frac{f_{bw}}{2}} N(f)|NTF(e^{2\pi jf/F_s})|^2 df$$

$$= 2 \int_{\frac{F_s}{4} + \frac{f_{bw}}{2}}^{\frac{F_s}{4} - \frac{f_{bw}}{2}} \frac{q^2}{12F_s} \left[ 2\cos\left(2\frac{\pi f}{F_s}\right) \right]^{2L} df$$

(2.28)

If it is assumed that  $\frac{2f_{bw}}{F_s} \ll 1$  with  $f_{bw}$  as defined in Figure 2.15 then Equation 2.28 can be re-written to:

$$P_{total} = 2 \int_{-\frac{f_{bw}}{2}}^{\frac{f_{bw}}{2}} \frac{q^2}{12F_s} \left( 2\sin\left(2\frac{\pi f}{F_s}\right) \right)^{2L} df$$

$$= 2 \int_{-\frac{f_{bw}}{2}}^{\frac{f_{bw}}{2}} \frac{q^2}{12F_s} \left[ 2\left(2\frac{\pi f}{F_s}\right) \right]^{2L} df$$

$$= \frac{q^2}{12} \left( \frac{\pi^{2L}}{2L+1} \right) \left( \frac{1}{R^{2L+1}} \right).$$

(2.29)

As expected, Equation 2.29 is identical to Equation 2.23 because the noise suppression in a  $2L^{th}$  order band-pass modulator is the same as the one in a  $L^{th}$  order low-pass modulator. Thus the signal-to-noise ratio in decibels for a  $2L^{th}$  band-pass modulator with b-bit quantizer and oversampling ratio R is given as:

$$SNR_{dB} = 10log\left(\frac{3}{2}R^{2L+1}\frac{2L+1}{\pi^{2L}}2^{2b}\right). \tag{2.30}$$

Both modulator topologies, band-pass and low-pass need decimation to lower the frequency and filter out the noise-shaped quantization noise.

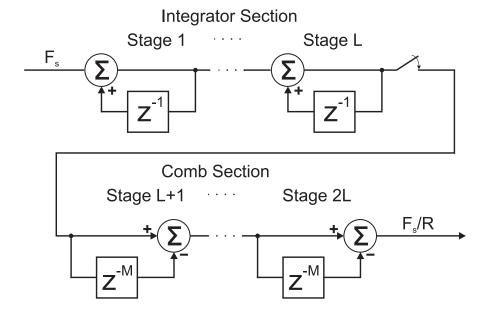

#### 2.3.3 The Concept of Decimation

To obtain a high-resolution signal from the low-bit stream from the output of the n-bit quantizer, decimation or averaging is used. Furthermore, decimation is needed to lower the date rate of the oversampled modulator. As was shown in figure 2.12, a key point of a delta-sigma and FIR converters is that the quantization noise spectrum is shaped in such a way as to place most of the noise power outside the signal band. To remove the quantization noise low-pass filters are used. However, appropriate filters tend to be difficult to realize at the elevated sampling rates of the modulator [Norsworthy et al., 1997, p.28]. As a result, decimation is needed to lower the bit rate of sigma delta, modulation and convert it to a form that is more suitable for processing and transmission [Crochiere and Rabiner, 1981]. The factor by which the rate is lowered is the decimation factor R, and is given as:

$$R = \frac{F_s}{F_d},\tag{2.31}$$

where  $F_s$  is the elevated sampling frequency of the sigma delta modulator and  $F_d$  is the reduced sampling rate at the output of a decimator as shown in [Norsworthy et al., 1997, p.30]. A convenient filter for decimation is based on the *sinc* function [Presti, 2000]. The transfer function of the filter is given as:

$$H(z) = \frac{1}{R} \sum_{i=0}^{R-1} z^{-i}.$$

(2.32)

Conceptually, the filter computes an output by forming the sum of the contents of the registers. Decimators based on *sinc* filters are appropriate for decimating sigma delta modulation down to four times the Nyquist rate [Candy, 1986]. Further decimation usually requires filters that cut off more sharply at the edge of baseband [Candy, 1986]. An efficient way to realize a decimation filter is known as the Hogenauer structure and consist of a series of cascaded accumulators followed by a cascade of differentiator (CIC) [Hogenauer, 1981] as expressed by:

$$H(z) = \left(\frac{1 - z^{-M}}{1 - z^{-1}}\right)^{L},\tag{2.33}$$

Figure 2.16: CIC decimation filter

where L is the order of the *sinc* filter. The Hogenauer structure is depicted in figure 2.16. With regard to overflow errors in all integrator stages, the two's complement binary format has two attractive characteristics. First, under certain conditions, overflow during the summation of two numbers causes no error. Second, with multiple summations, intermediate overflow errors cause no problems if the final magnitude of the sum of the b-bit two's complement numbers is less than  $2^{b-1}$  ([Lyons, 2004], section 12.1.5). Thus, a composite CIC filter would compute correct filter outputs provided the additions were performed with 2's-complement arithmetic and provided the bit field width of the accumulator exceeded the word width required by the final output sequence. The required bit width is the number of bits in the input data words plus the number of bits required to accommodate the maximum filter gain. Then the most significant bit at the output of the filter is ([Hogenauer, 1981], equation 11):

$$B_{max} = [N\log_2(RM) + B_{in} - 1]$$

(2.34)

With a bit width as expressed by equation 2.34, the accumulators can successfully recover from internal overflow.

**Figure 2.17:** Illustration of undersampling various signals with different bands of interest.

#### 2.3.4 The Concept of Undersampling

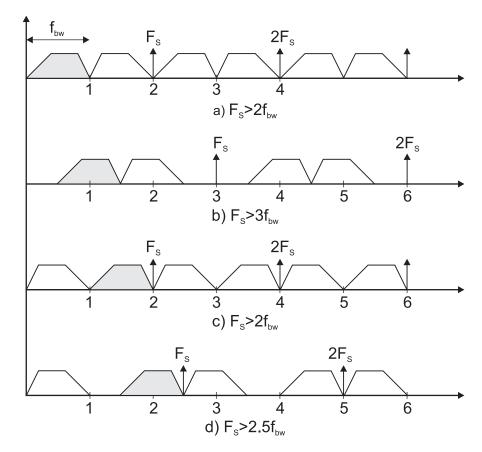

Undersampling is sampling at a rate below the Nyquist frequency, which generally implies a loss of information, unless the signal bandwidth,  $f_{bw}$  is restricted to less than  $F_s/2$ . For signals which do not extend to dc, however, the minimum required sampling rate is a function of the bandwidth of the signal,  $2f_{bw}$ , as well as its position in the frequency spectrum [Analog Devices, 1998], [Vaughan et al., 1991a]. When such a signal is undersampled, the aliased products can be used to translate the input signal down to baseband for further processing. The minimum required sampling frequency,  $F_s$ , will vary with the signals maximum frequency,  $F_{max}$ , and its bandwidth,  $f_{bw}$ . This can be illustrated with the help of figure 2.17 [Analog Devices, 1998]. In part a) of the figure, the signal occupies a band from dc to 1MHz, and therefore must be sampled at greater than 2MSPS. The second case shown in part b) shows a 1MHz signal which

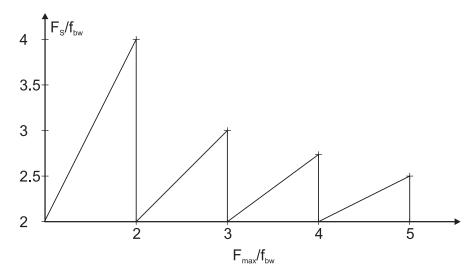

**Figure 2.18:** Minimum required sampling frequency as a function of the maximum signal frequency.

occupies the band from 0.5 to 1.5MHz. Now this signal must be sampled at a minimum of 3MSPS. In the third case, shown in part c), the signal occupies the band from 1 to 2MHz, and the required sampling rate for no aliasing reduces back to 2MSPS. In part d) of figure 2.17 the signal occupies the band from 1.5 to 2.5MHz. This signal must be sampled at a minimum of 2.5MSPS. Generalizing this analysis will lead to figure 2.18. The actual minimum required sampling rate is a function of the ratio of the highest frequency component,  $F_{max}$ , to the total signal bandwidth,  $f_{bw}$ . For large ratios of  $F_{max}$  to the bandwidth,  $f_{bw}$ , the minimum required sampling frequency approaches  $2f_{bw}$  [Vaughan et al., 1991a]. As a result, undersampling can be used to down-convert a signal residing at a high frequency to baseband where it can be processed further. This methodology will later be used in the FIR analog-to-digital modulator to downconvert a high frequency signal. That is, the narrow-band frequency modulated output of an oscillator is undersampled and digitized directly. A novel scheme will be proposed which reduces the requirements on the sampling circuitry as undersampling is performed, while still not suffering any drawbacks due to undersampling or spectral reversal common to conventional amplitude undersampling applications.

# 2.4 Higher Order Delta-Sigma Architectures

To achieve higher noise shaping of the introduced quantization error in the A/D conversion, higher order noise shaping architectures are utilized along with multi-bit quantization [Chao et al., 1990; Khoini-Poorfard et al., 1997; Kozak et al., 2000]. While there is an abundance of modulator topologies utilizing higher order loop filters [Brandt and Wooley, 1991; Leslie and Singh, 1990; Hairapetian and Temes, 1994], most of them fall into three categories. These are single-loop low order designs, single-loop high order designs or multi-loop designs. A detailed summary outlining the advantages and drawbacks of each topology can be found in [Norsworthy et al., 1997, p.166] and [Ribner, 1991]. As this work is concerned with low-order modulator architectures, the main focus is on multi-loop designs as these are comprised out of multiple low order single-loop topologies. Since FIR modulators do not have a feedback path, a cascaded approach of multiple first-order FIR modulators is a good way to improve noise performance. Cascaded architectures are reviewed next with emphasis on the later presented FIR modulators.

#### 2.4.1 Cascaded

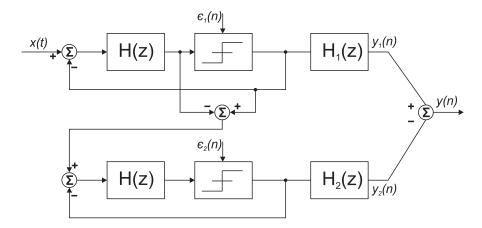

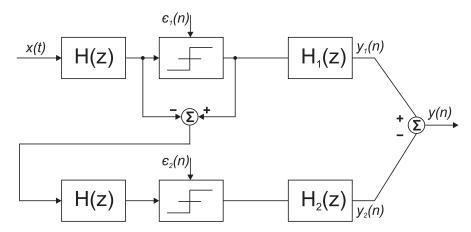

A simple solution to stability problems of higher order single loop topologies was suggested by Hayashi et al. [Hayashi et al., 1986]. In their work they proposed the use of multiple first-order stages instead of a single high order loop filter to reduce quantization errors. This principle is referred to as multi-stage noise shaping (MASH) or a cascaded topology. The principle of cascaded sigma-delta modulation is based on the use of multiple sigma-delta modulator stages in a cascade configuration [Matsuya et al., 1987]. In ideal multi stage architectures, each successive stage accepts the quantization noise of the preceding stage as its input in order to create a digital signal which perfectly cancels out the quantization error introduced in the preceding stage [Longo and Copeland, 1988]. A basic second-order cascaded topology is depicted in figure 2.19. As shown in the figure, two conventional first-order delta-sigma modulators utilizing feedback are utilized to realize a second order structure. Both first-order modulators

**Figure 2.19:** Second-order cascaded modulator topology based on two first-order delta-sigma converters.

**Figure 2.20:** Second-order cascaded modulator topology based on two first-order FIR delta-sigma converters.

need negative feedback to shape the quantization noise out of the band of interest. Later it will be shown how a similar second order system can be realized without the need for negative feedback. A simplified version of this scheme of cascaded FIR modulators is shown in figure 2.20. A brief analysis of figure 2.19 shows that the output y(n) is given as:

$$Y(z) = [X(z)STF(z) + \epsilon_1(z)NTF(z)]H_1(z) -$$

$$[\epsilon_1(z)STF(z) + \epsilon_2(z)NTF(z)]H_2(z)$$

(2.35)

The goal is to cancel the coarse quantization error  $\epsilon_1$ . This occurs when:

$$\epsilon_1(z)NTF(z)H_1(z) = \epsilon_1(z)STF(z)H_2(z). \tag{2.36}$$

The noise-transfer function and the signal transfer functions for  $H(z) = \frac{1}{1-z^{-1}}$  were given in section 2.3.1 as  $NTF(z) = 1 - z^{-1}$  and  $STF = z^{-1}$ . Then we can re-write equation

2.36 as:

$$\frac{NTF(z)}{STF(z)} = \frac{H_2(z)}{H_1(z)}$$

$$\frac{1-z^{-1}}{z^{-1}} = \frac{H_2(z)}{H_1(z)}.$$

(2.37)

Thus, choosing  $H_1(z) = z^{-1}$  and  $H_2(z) = 1 - z^{-1}$  will cancel  $\epsilon_1$  and leave the output of:

$$Y(z) = z^{-2}X(z) + \epsilon_2(z)(1 - z^{-1})^2$$

(2.38)

As a result, in the MASH topology the quantization error has been improved without increasing the order of the loop filter. However, the topologies are sensitive to the analog accuracy of implementation, typically limiting the resolution of analog-to-digital conversion to less than 14 bits, regardless of the order of the noise shaping [Cauwenberghs and Temes, 2000]. To circumvent this, calibration methods can be applied to in the digital domain to correct for analog imprecision, trading a small increase in the implementation complexity of the digital part for a significant increase in effective analog precision[Cauwenberghs and Temes, 2000; Kiss et al., 2000].

# 2.5 Summary

This chapter introduced the important concepts forming the foundation for the following chapters. The most vital aspects of every delta-sigma modulator, namely oversampling, quantization, noise shaping, and decimation where reviewed and can now be used to realize different A/D topologies. Also, other well established principles such as undersampling and higher order delta-sigma topologies were re-introduced, giving the tools needed to fully appreciate the following chapters.

# **CHAPTER III**

## FIRST-ORDER FIR SIGMA DELTA MODULATORS

## 3.1 Introduction and Review

While oversampling discrete-time (DT) and continuous-time (CT) analog-to-digital (A/D) modulators have widely been used for high resolution applications, they are almost exclusively synonymous with feedback. Generally, any type of feedback is applied in order to control the dynamic behavior of a system, to ensure stability, improve linearity, and compensate for the effect of disturbances [Franklin et al., 2006]. More importantly, in delta-sigma A/D converters the negative feedback path also realizes the quantization noise suppression in the signal band as shown in section 2.2.2. So why would we want to remove feedback from a system?

- Feedback entails having to deal with undesirable effects such as excess loop delay as in continuous time delta-sigma A/D converter [W. Gao and Snelgrove, 1997]. Ideally, the feedback digital-to-analog converter's currents respond immediately to the quantizer's clock edge, but the non-zero transistor switching time of the latched comparator (quantizer) and the digital-to-analog converter result in a finite delays [J.A. and W.M., 1999]. Excess loop delay will shift the poles of the noise transfer function and will therefore change the characteristic of the noise shaping or make the overall modulator unstable.

- Another problem encountered with multi-bit digital-to-analog converters in the feedback path is their inherent nonlinearity. Non-linearity of the quantizer (A/D) of the modulator in the feed-forward loop is reduced by the gain of the loop. However, non-linearity in the feedback D/A converter is a serious problem since this nonlinearity directly feeds into the input [Wang et al., 2001].

- Limit-cycles, inherent to systems with feedback, might cause instability

[Reefman et al., 2005; Tao et al., 1999a] in the modulator.

Feedback increases also the system complexity due to extra circuit components such as the digital-to-analog converter in the feedback path [Norsworthy et al., 1997]. Furthermore, in many systems feedback is simply not possible as no path exists.

As a result, delta-sigma converters without feedback are an interesting alternative to conventional topologies. As introduced in Section 2.2.1, delta-sigma A/D converters without feedback are based on frequency modulators followed by frequency-to-digital converters. The work on frequency-to-digital converters for delta sigma converters commenced in the early 90's. However, most of the methods used in these works are based upon well established frequency demodulation techniques. Different research groups have worked on the topic of frequency-to-digital converters since then, realizing different implementations with and without feedback. While there are a wide variety of publications on delta-sigma converters utilizing frequency modulation and demodulation techniques, three university groups have taken interesting yet different approaches to realize these modulators based in some form of frequency modulation and demodulation. One group in particular, is lead by Professor Ian Galton at the University of California, San Diego and includes William Huff, Paolo Carbone, and Eric Siragusa. Their implementation of a second order delta-sigma frequency-to-digital converter is presented in [Ian Galton and Siragusa, 1998]. There, a second-order modulator utilizing feedback is realized. Hence, the previous mentioned comments on using negative feedback apply. This topology which is depicted in Figure 3.1 a) simultaneously performs frequency demodulation and digitization. The topology presented is based on phaselocked loops and uses analog circuitry such as a charge-pump and a digital counter to realize two integrators. Figure 3.1 a) depicts the second-order delta-sigma PLL. As can be seen from the figure, the topology operates on a hard-limited version of the frequency modulated input signal and generates a 2-bit output sequence. Thus, the performance is equivalent to a conventional second order delta-sigma modulator. Note, that the topology requires an already generated frequency modulated input signal,  $x(t)_h$ . That is, no

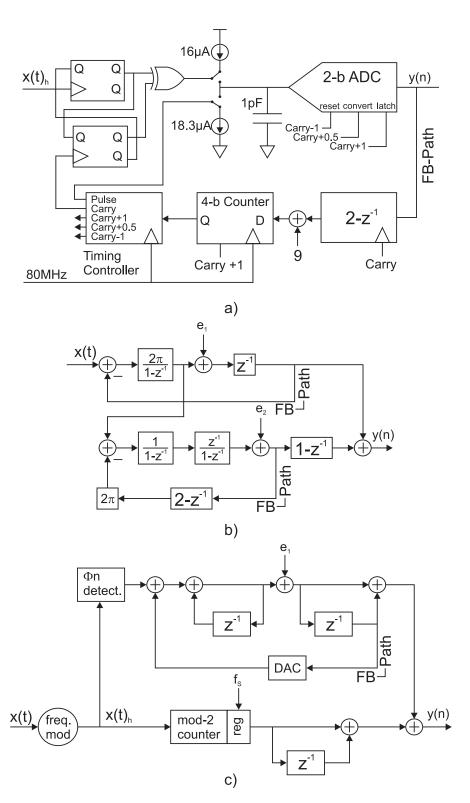

**Figure 3.1:** The three most important existing topologies. Figure a) shows the works of [Ian Galton and Siragusa, 1998], figure b) the works of [Thomas A. D. Riley and Plett, 1998], and figure c) the works of [Hovin et al., 1997].

frequency modulation is performed by the circuit. While excellent performance results are achieved, the overall complexity of the system is quite high, even more so when including a frequency modulation unit. Furthermore, a non-uniform to uniform decimation filter is required as the overall topology samples the FM signal asynchronously. This decimation filter will increase the complexity of the topology further. Follow-up publications to this work include [Izadi and Leung, 2002] and [Sharifkhani, 2004].

A second research group consists of Walt T. Bax, Thomas A. D. Riley, Miles A. Copeland, Tom A. D. Riley, Norman M. Filiol and Calvin Plett at Carleton University, Ottawa in Canada. Their realization of a delta-sigma frequency-to-digital converter is based on two delta-sigma phase-locked loops as described in

[Thomas A. D. Riley and Plett, 1998] and shown in Figure 3.1 b). As can be seen from the figure this topology mimics a 1-2 cascade typically found with conventional delta-sigma converters. The first stage integrates the input signal to convert the frequency content of the FM signal to phase. The signal content and error due to quantization are then fed into the second stage. Both stages need feedback to realize noise-shaping as explained in section 2.2.2 and hence increase circuitry complexity. Furthermore, the topology requires frequency dividers to down-convert the FM input signal to the reference clock. Again, the topology presented performs no frequency modulation. Another implementation utilizing a phase-locked loop and a frequency divider in described in [Riley et al., 1993].

Finally, the research group at the University of Oslo in Norway comprising out of Dag T. Wisland, Mats E. Hovin and Tor S. Lande introduced yet another version of a delta-sigma frequency-to-digital converter [Hovin et al., 1997; Wisland et al., 2002, 2003]. Their implementation is, however, different from the approach the other research groups took as the delta-sigma frequency-to-digital converter is implemented without feedback, thus, resulting in a more efficient modulator implementation. This topology is shown in Figure 3.1 c). Their topology could be realized by utilizing the frequency de-modulation technique patented by Akira Sogo in [Sogo, 1989]. The demodulation scheme provided by Akira Sogo in conjunction with an oscillator approach to perform

frequency modulation and a 1-1 cascade similar to conventional delta-sigma modulators thus realizes an efficient scheme to frequency demodulate and digitize an FM signal. However, as depicted in figure 3.1 c) the second path of the 1-1 cascade still utilizes feedback.

While these are the most important publications there are many others that are utilizing voltage-to-frequency conversion also to realize delta-sigma topologies [Watanabe et al., 2003; Ravinuthula and Harris, 2004; Yang and Sarpeshkar, 2005; Pekau et al., 2006]. However, all of them utilize some sort of feedback to shape out quantization noise.

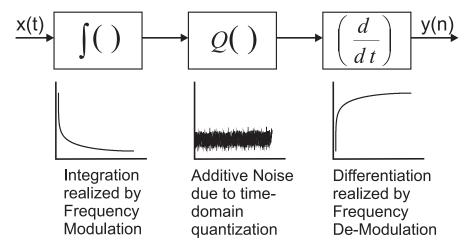

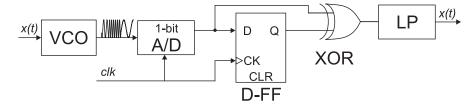

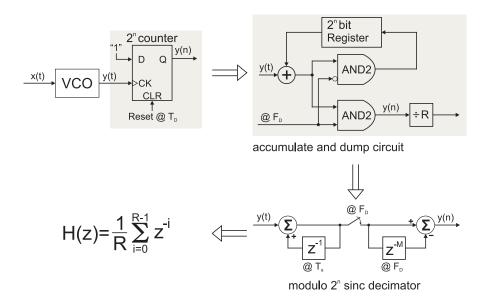

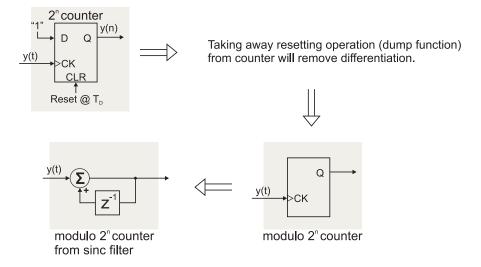

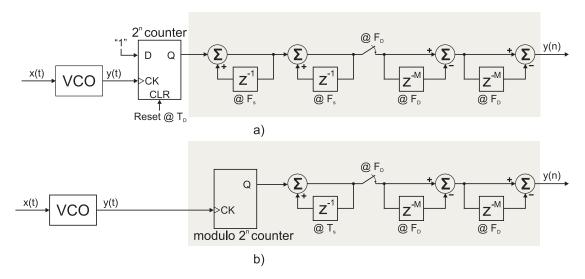

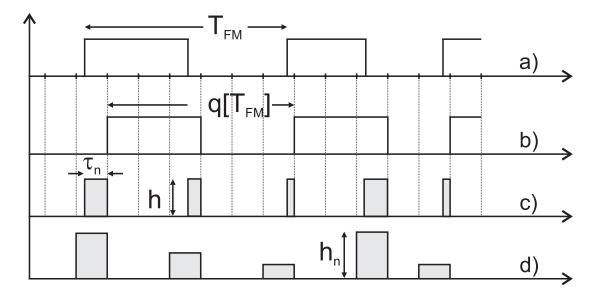

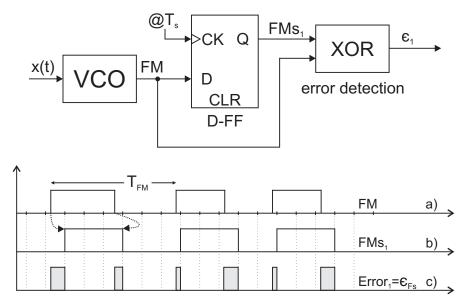

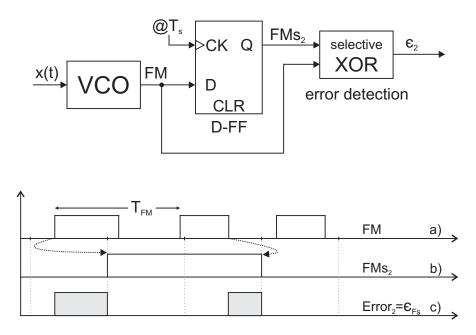

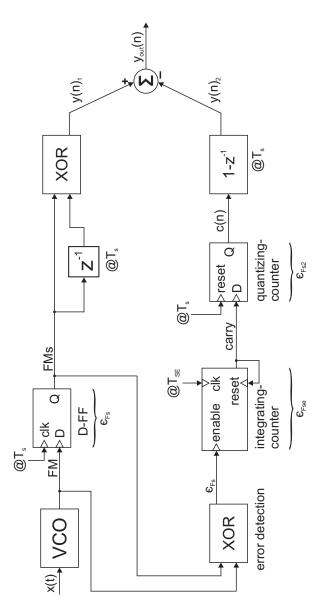

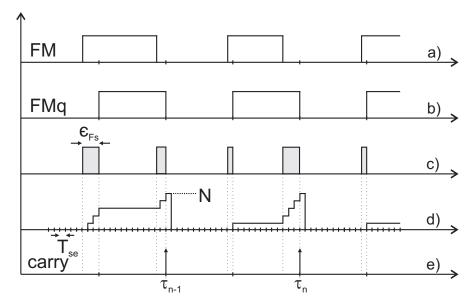

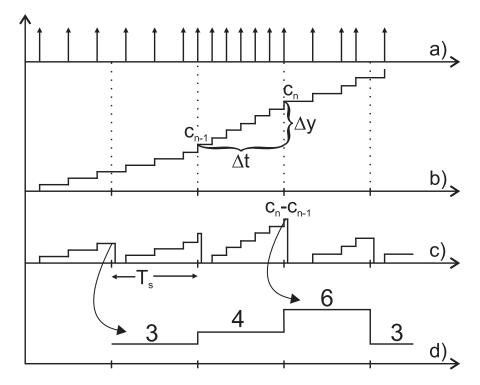

In this and the following chapters all feedback paths are removed while still realizing the noise-shaping characteristics synonyms to delta-sigma converters. Since these FIR modulators are based on frequency modulation and demodulation techniques, a brief review of these principles and how they can be used is given. Based on these principles various versions of FIR modulator topologies are presented and optimized. An overview of the presented structures and their simplifications is given in figure 3.2. Part a) of the figure shows a first-order FIR modulator where a VCO is used as a frequency modulator followed by an optional hard-limiter to rectify the frequency modulated signal. The frequency de-modulation technique proposed in [Sogo, 1989; Hovin et al., 1997] is given in the shaded region of figure 3.2 a). We simplified this topology by realizing that a simple asynchronous D-FF can realize a quantizer and differentiator at the same time. This simplification is depicted in figure 3.2 b) which shows a resetting D-FF followed by a sinc decimation filter. Alternatively, a resetting-counter can be utilized as depicted in figure 3.2 c). Furthermore, the concept of undersampling as introduced in Section 2.3.4 can be used with the counter from figure 3.2 c) or the implementation from figure 3.2 a), which alleviates the need for high clock frequencies. Utilizing a resetting counter in conjunction with undersampling will also eliminate the need for having to choose a certain sampling frequency. This will be outlined in later sections. Usually when utilizing undersampling the sampled signal must not cross an integer multiple of the sampling frequency  $F_s/2$ . Otherwise aliasing occurs. However, with

**Figure 3.2:** Part a) shows the topology adopted by [Hovin et al., 1997]. Part b) shows how we replaced the XOR gate and D-FF by a simple asynchronous D-FF, or more importantly, by a resetting counter as seen in part c). In part d) the counter was moved into the sinc decimation filter.

the counter this is not the case as it captures and retains all the frequency modulated signal edges in between sampling instances. As a result, this first-order topology as depicted in figure 3.2 c) is a marked departure from prior art. To further simplify the FIR modulators the counter from figure 3.2 c) can be absorbed into the decimation filter as shown in figure 3.2 d). However, this can only be done if the decimation filter is based on a cascade of integrators and differentiator. All simplified first-order FIR modulators are then analyzed in terms of non-linearities, phase noise, jitter, and metastability. Exact mathematical models are presented describing the noise suppression and hence the signal-to-noise ratio performance. Simulation examples are presented to give proof-of-concept and to discuss performance results. The performance is then compared to the mathematical model.

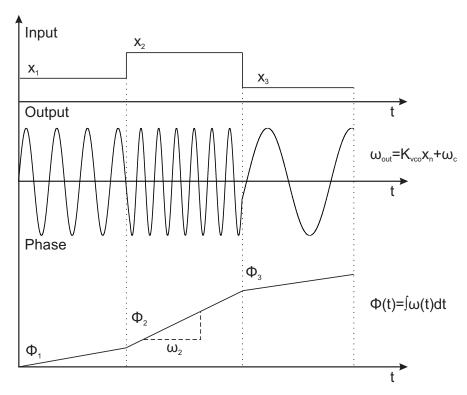

#### 3.1.1 FIR SDM Principle