Gupta, Shoubhik (2019) *Ultra-thin silicon technology for tactile sensors*. PhD thesis.

https://theses.gla.ac.uk/41053/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses

<a href="https://theses.gla.ac.uk/">https://theses.gla.ac.uk/</a>

research-enlighten@glasgow.ac.uk

# Ultra-Thin Silicon Technology for Tactile Sensors

### **Shoubhik Gupta**

A thesis submitted in fulfilment of the requirements for the degree of

Doctor of Philosophy

The University of Glasgow

School of Engineering, College of Science and Engineering

October 2018

#### **Abstract**

In order to meet the requirements of high performance flexible electronics in fast growing portable consumer electronics, robotics and new fields such as Internet of Things (IoT), new techniques such as electronics based on nanostructures, molecular electronics and quantum electronics have emerged recently. The importance given to the silicon chips with thickness below 50 µm is particularly interesting as this will advance the 3D IC technology as well as open new directions for high-performance flexible electronics. This doctoral thesis focusses on the development of silicon–based ultra-thin chip (UTC) for the next generation flexible electronics. UTCs, on one hand can provide processing speed at par with state-of-the-art CMOS technology, and on the other provide the mechanical flexibility to allow smooth integration on flexible substrates. These development form the motivation behind the work presented in this thesis.

As the thickness of any silicon piece decreases, the flexural rigidity decreases. The flexural rigidity is defined as the force couple required to bend a non-rigid structure to a unit curvature, and therefore the flexibility increases. The new approach presented in this thesis for achieving thin silicon exploits existing and well-established silicon infrastructure, process, and design modules. The thin chips of thicknesses ranging between 15  $\mu$ m – 30  $\mu$ m, were obtained from processed bulk wafer using anisotropic chemical etching. The thesis also presents thin wafer transfer using two-step transfer printing approach, packaging by lamination or encapsulation between two flexible layerand methods to get the electrical connections out of the chip. The devices realised on the wafer as part of front-end processing, consisted capacitors and transistors, have been tested to analyse the effect of bending on the electrical characteristics. The capacitance of metal-oxide-semiconductor (MOS) capacitors increases by ~5% during bending and similar shift is observed in flatband and threshold voltages. Similarly, the carrier mobility in the channel region of metal-oxide-semiconductor field effect transistor (MOSFET) increases by 9% in tensile bending and decreases by ~5% in compressive bending. The analytical model developed to capture the effect of banding on device performance showed close matching with the experimental results.

In order to employ these devices as tactile sensors, two types of piezoelectric materials are investigated, and used in extended gate configuration with the MOSFET. Firstly, a nanocomposite of Poly(vinylidene fluoride-co-trifluoroethylene), P(VDF-TrFE) and barium titanate (BT) was developed. The composite, due to opposite piezo and pyroelectric coefficients of constituents, was able to suppress the sensitivity towards temperature when

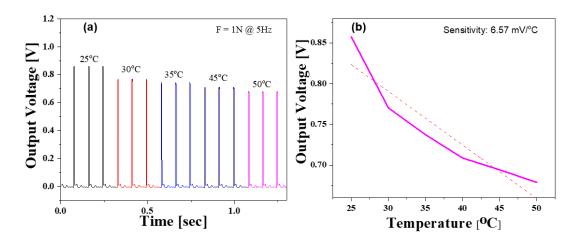

force and temperature varied together, The sensitivity to force in extended gate configuration was measured to be 630 mV/N, and sensitivity to temperature was 6.57 mV/°C, when it was varied during force application.

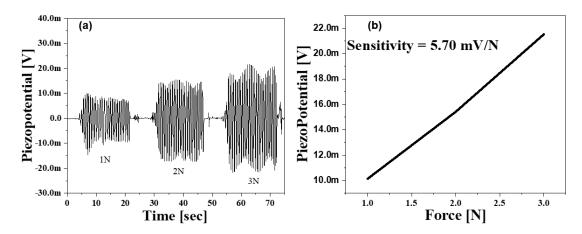

The process optimisation for sputtering piezoelectric Aluminium Nitride (AlN) was also carried out with many parametric variation. AlN does not require poling to exhibit piezoelectricity and therefore offers an attractive alternative for the piezoelectric layer used in devices such as POSFET (where piezoelectric material is directly deposited over the gate area of MOSFET). The optimised process gave highly orientated columnar structure AlN with piezoelectric coefficient of 5.9 pC/N and when connected in extended gate configuration, a sensitivity (normalised change in drain current per unit force) of 2.65 N<sup>-1</sup> was obtained.

### **List of Publication**

The work presented in this thesis has culminated in the following journal publications and conference proceedings:

### **Journal Articles (published)**

- 1) **S. Gupta**, W. T. Navaraj, L. Lorenzelli, and R. Dahiya, "Ultra-thin chips for high-performance flexible electronics," *Nature Flexible Electronics*, vol. 2, p. 8, 2018.

- 2) **S. Gupta**, D. Shakthivel, L. Lorenzelli, R. Dahiya "Temperature Compensated Tactile Sensing using MOSFET with P(VDF-TrFE)/BaTiO<sub>3</sub> Capacitor as Extended Gate" *IEEE Sensor Journal*, vol.9, issue.2, pp. 435-442, 2018.

- 3) W. T. Navaraj, **S. Gupta**, L. Lorenzelli, and R. Dahiya, "Wafer Scale Transfer of Ultrathin Silicon Chips on Flexible Substrates for High Performance Bendable Systems" *Advanced Electronic Materials*, vol. 4, issue.4, pp. 1700277, 2018.

- 4) N. Yogeswaran, W. T. Navaraj, **S. Gupta**, F. Liu, V. Vinciguerra, L. Lorenzelli, and R. Dahiya, "Piezoelectric Graphene Field Effect Transistor Pressure Sensors for Tactile Sensing," *Applied Physics Letters*, 2018.

- 5) A.Vilouras, H. Heidari, **S.Gupta**, R. Dahiya "Modelling of CMOS Devices and Circuits on Flexible Ultra-Thin Chips" *IEEE Transactions on Electronic Devices*, vol.64, pp: 2038 2046, 2017.

- 6) **S. Gupta**, H. Heidari, L. Lorenzelli, R. Dahiya, "Device modelling for bendable piezoelectric FET-based touch sensing system" *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 63, pp. 2200-2208, 2016.

- 7) N. Yogeswaran, W. Dang, W. T. Navaraj, D. Shakthivel, S. Khan, E. O. Polat, S. Gupta, H. Heidari, M. Kaboli, L. Lorenzelli, G. Cheng, and R. Dahiya, "New

materials and advances in making electronic skin for interactive robots" *Advanced Robotics*, vol. 29, pp. 1359-1373, 2015.

#### **Journal Articles (under preparation)**

- 8) **S. Gupta**, N. Yogeswaran, R. Dahiya "Fabrication of c-axis Oriented Aluminium Nitride Films by RF Magnetron Sputtering for Tactile Sensing"

- 9) A. Vilouras, **S. Gupta**, R. Dahiya "Flexible Ion-Sensitive Field-Effect Transistors on Ultra-Thin Chips"

- 10) **S. Gupta**, A. Vilouras, and R. Dahiya "Polydimethylsiloxane as polymeric protective coating for anisotropic silicon etching"

#### **Conferences Papers**

- 1) **S. Gupta**, N. Yogeswaran, F.Giacomozzi, , L. Lorenzelli and R. Dahiya, "Flexible AlN coupled MOSFET Device for Touch Sensing," *IEEE Sensors 2018*, New Delhi, India.

- 2) N. Yogeswaran, **S. Gupta**, and R. Dahiya, "Low Voltage Graphene FET Based Touch Sensor" *IEEE Sensors 2018*, New Delhi, India.

- 3) A. Paul, **S. Gupta**, and R. Dahiya, "<u>Corrugated Graphene Network based Pressure Sensor</u>" *IEEE Sensors 2018*, New Delhi, India, 2018.

- 4) **S. Gupta**, L. Lorenzelli, and R. Dahiya, "Multifunctional flexible P(VDF-TrFE)/BaTiO<sub>3</sub> based tactile sensor for touch and temperature monitoring," *IEEE Sensors 2017*, Glasgow, UK.

- 5) **S.Gupta**, A.Vilouras, H.Heidari, R.Dahiya "Device Modelling of Silicon based High Performance Flexible Electronic" *IEEE ISIE 2017*, Edinburgh, UK.

6) **S. Gupta**, F. Giacomozzi, H. Heidari, L. Lorenzelli, and R. Dahiya, "Ultra-Thin Silicon

based Piezoelectric Capacitive Tactile Sensor," EuroSensors 2016, Budapest,

Hungary.

7) S. Gupta, H. Heidari, L.Lorenzelli, R.Dahiya "Towards Bendable Piezoelectric Oxide

Semiconductor Field Effect Transistor based Touch Sensor", IEEE ISCAS 2016,

Montreal, Canada.

**Poster Presentations**

1) S. Gupta, F. Giacomozzi, L. Lorenzelli, R. Dahiya "Towards Fabrication of Ultra-Thin

Piezoelectric capacitor For Tactile Sensing" Terzo Convegno Nazionale Sensori (CNS)

2016, Rome, Italy.

2) S. Gupta, H.Heidari, L.Lorenzelli, R.Dahiya, "Analytical Modelling of Piezoelectric

Oxide Semiconductor Field Effect Transistor" innoLAE 2016, Cambridge, UK.

3) H.Heidari, S. Gupta, W.T.Navaraj, L.Lorenzelli, R.Dahiya "Simulation Scenarios for

Ultra-Thin Chips in Smart Large-Area Flexible Electronics", innoLAE 2016,

Cambridge, UK.

4) S. Gupta, L.Lorenzelli, R.Dahiya, "Device Modelling of Piezoelectric Oxide

Semiconductor Field Effect Transistor" NanotechItaly 2015, Bologna, Italy.

**Book**

A. Paul, **S. Gupta**, R. Dahiya, *Solid-State Sensors (in progress)*

Publisher: IEEE+ Wiley

٧

### कर्मण्येवाधिकारस्ते मा फलेषु कदाचन। मा कर्मफलहेतुर्भूर्मा ते सङ्गोऽस्त्वकर्मणि॥ - Bhagavad Gita 2-47

Karmanye vadhikaraste Ma Phaleshu Kadachana Ma Karmaphalaheturbhurma Te Sangostvakarmani

"You are entitled to do your duty and action, but never to the results of your actions. Let not the results be your motivation, and do not be attached to laziness and inaction." This dissertation is lovingly dedicated to my mother, Mrs. Sandhya Gupta. Her support, encouragement, and constant love have sustained me throughout my life.

### Acknowledgement

First of all, I would like to seek the blessings of Shri Ranisati Dadi ji without whom, nothing could have been possible.

I would like to express my sincere gratitude to my supervisor Professor Ravinder Dahiya for his boundless support and encouragement for my research career and personal development. His inspirational talks during our meeting kept me motivated to go through high and lows of graduate life. I am also greatly thankful to my second supervisor, Dr. Leandro Lorenzelli, for his technical support during my stay at Fondazione Bruno Kessler, and fun trips not to forget, the hiking on Cinque Terra. The help of Flavio Giacomozzi and Dr. Andrea Adami as the process evaluator was invaluable for the success of my project. I would also like to appreciate the efforts by Professor Aloke Dutta of IIT Kanpur who instilled in me the curiosity towards semiconductors.

I am thankful to my examining panel Prof. Themis Prodromakis from University of Southampton, Prof. Manuel.Salmeron-Sanchez and Prof. Sandy Cochran, both from University of Glasgow, whose valuable suggestions helped me in refining the thesis.

Special thanks goes to Wenting and Nivasan, the integral part of "*Trento Trio*" who stayed with me during the whole graduate journey, from Italy to UK. The hard work of Wenting to make Chinese vegetarian food for us and motivational talks of Nivasan will be missed.

I would to extend my thanks to all my colleagues at BEST group; especially

William: For the all the technical help which pushed me to learn more.

Anastasios: For being there during technology development and sharing the work.

Dr. Dhayalan: For managing the nanowire and UTC themes.

Dr. Libu: For the good Kerala food.

Dr. Ambarish: For letting me to speak in Hindi and of course clicking awesome pictures.

Fengyuan: For constantly reminding me that time never stops.

I would also like to thank all my friends from other research groups, whom I hang out with, Bhavana, for continuously accepting my criticism with smiling face, Pradeep for making delicious Turkish tea and Archan for providing guidance during initial phase, and Pavi for frequent home parties.

All my friends in the group made sure that life never go monotonous. Similarly, my colleagues at FBK, Dr. Sajina with whom I can talk on any random topic and Dr. Saleem, who stayed and supported me in all ways in Italy, I sincerely thanks them too.

The technicians and lab assistants help was equally important and I would like to thanks Severino, Paolo, Sara and Stefano of FBK, and Helen, Lesley, Eve, David, and Douglas of JWNC, who provided all the help. None of my work would have been possible without their hard work in maintaining the facility.

I gratefully acknowledged the European Commission in the framework of the FP 7 project CONTEST, and EPSRC for financially supporting the work.

Beyond academic work colleagues, I am grateful to all my friends in different parts of world, especially Swapnil, who talks on random topics in my Skype chat. Also, thanks to Sanchit, Jitendra, Sarthak and Arun with whom I spend good time at IIT Kanpur and still are part of my family.

Finally, and the most important, I like to thank my family. I am a very lucky person for getting such a wonderful family. My parents Ms Sandhya Gupta and Mr Rishikesh Gupta, who brought me up to this level, and my brother Shubham who supported the family in my absence. I strongly believe that without their support it would be very difficult for me to finish the Ph.D. studies in proper time.

This work has been possible due to the unconditional support of many people who has been there for me in so many ways and to whom I will always feel grateful.

### **Table of Contents**

| Abstract       |                                                  | i    |

|----------------|--------------------------------------------------|------|

| List of Public | cation                                           | iii  |

| Acknowledge    | ement                                            | viii |

| Table of Con   | tents                                            | X    |

| List of Table  |                                                  | xiv  |

| List of Figure | es                                               | xv   |

| Author's Dec   | elaration                                        | xxiv |

| Definitions/A  | Abbreviations                                    | XXV  |

| Chapter 1. Int | troduction                                       | 1    |

| 1.1 Bacl       | kground and motivation                           | 1    |

| 1.2 Obje       | ectives of the Ph.D. research                    | 2    |

| 1.3 Stru       | cture of the thesis                              | 3    |

| 1.4 Key        | contributions of this thesis                     | 4    |

| Chapter 2. St  | tate-of-the-Art in Ultra-Thin Silicon Technology | 6    |

| 2.1. Ultra     | a-thin silicon                                   | 6    |

|                | orical Perspective                               |      |

|                | a-thin silicon properties                        |      |

| 2.3.1.         | Mechanical properties                            | 12   |

| 2.3.3.         | Thermal properties                               | 15   |

| 2.3.4.         | Optical properties                               | 16   |

| 2.4. Ultra     | a-Thin Chip Methodologies                        | 18   |

|                | Physical Thinning                                |      |

| 2.4.2.         | Chemical Thinning                                | 21   |

| 2.4.3.         | Physico-Chemical Thinning                        | 24   |

| 2.5. Thir      | n Wafer Handling                                 | 32   |

| 2.5.1.         | With carrier wafer                               | 33   |

| 2.5.2.         | Without carrier wafer                            | 34   |

| 2.6. Thir      | n Wafer Dicing                                   | 34   |

|                | Laser Dicing                                     |      |

| 2.6.2          | Dry Etching                                      | 35   |

| 2.6.3.        | Blade Dicing                                               | 35 |

|---------------|------------------------------------------------------------|----|

| 2.7. Inte     | gration of ultra-thin chips                                | 35 |

| 2.7.1.        | Flip Chip Assembly on Flexible Substrate                   | 37 |

| 2.7.2.        | Laminating UTC between two polymer layers                  | 38 |

| 2.7.3.        | Chip on Foil with printed connections                      | 39 |

| 2.7.4.        | Heterogeneous Integration                                  | 39 |

| 2.8. App      | olication of Ultra-Thin Chips                              | 40 |

| 2.8.1.        | 3D Integrated Circuits                                     | 40 |

| 2.8.2.        | Medical/Life Healthcare                                    | 41 |

| 2.8.3.        | Robotics                                                   | 43 |

| 2.8.4.        | Large Area Electronics                                     | 43 |

| 2.9. Cas      | e Study: Ultra-thin silicon based tactile sensors          | 44 |

| 2.10. C       | onclusion                                                  | 45 |

| Chapter 3. Fa | abrication of MOSFET as an Active Device of Tactile Sensor | 47 |

| 3.1.1.        | Mask Design                                                | 47 |

| 3.2. Fab      | rication Steps                                             | 53 |

| 3.3. Cor      | nclusion                                                   | 71 |

| Chapter 4. Pi | ezoelectric Materials as Transducer for Tactile Sensor     | 72 |

| 4.1. Piez     | zoelectricity                                              | 72 |

| 4.2. Piez     | zoelectric Constitutive Equations                          | 72 |

| 4.3. Piez     | zoelectric Materials                                       | 74 |

| 4.3.1.        | Lead zirconate titanate                                    | 74 |

| 4.3.2.        | Barium Titanate                                            | 75 |

| 4.3.3.        | PVDF                                                       | 75 |

| 4.3.4.        | Piezoelectric composite                                    | 76 |

| 4.4. Mu       | Iti sensing using piezoelectric composite                  | 77 |

| 4.4.1.        | P(VDF-TrFE)/ BT composite based tactile sensor             | 79 |

| 4.4.2.        | Nanocomposite fabrication                                  | 79 |

| 4.4.3.        | Nanocomposite characterisation                             | 80 |

| 4.4.4.        | Sensor fabrication                                         | 85 |

| 4.5. Alu      | minium Nitride                                             | 86 |

| 4.5.1.        | Deposition Technique                                       | 90 |

| 4.5.2.        | Effect of sputtering pressure                              | 94 |

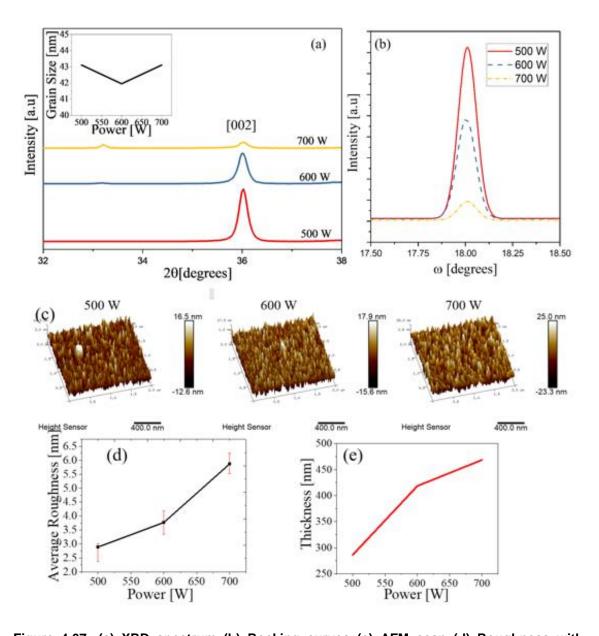

| 4.5.3.        | Effect of sputtering power                                 | 96 |

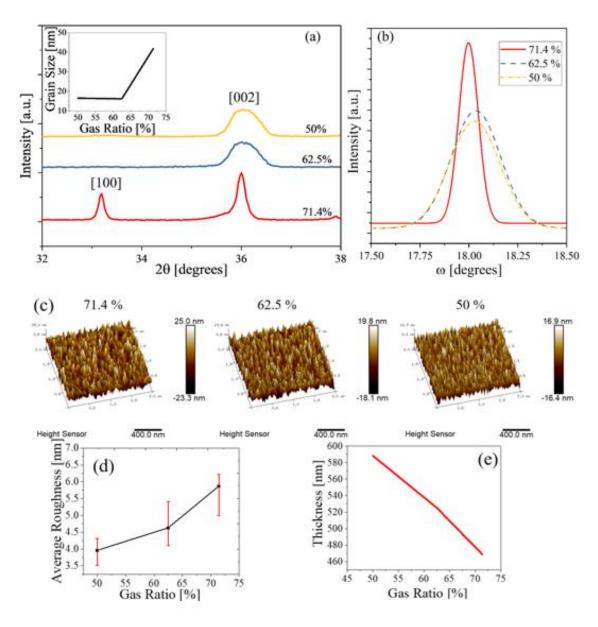

| 4.5.4.        | Effect of gaseous composition                              |    |

| 4.5.5.        | Sensor fabrication                                         | 99 |

| 4.6.          | Direct Deposition of AlN on MOSFET                          | 100 |

|---------------|-------------------------------------------------------------|-----|

| 4.7.          | Conclusion                                                  | 103 |

| Chapter       | 5. Post-Processing Techniques for Thinning Silicon          | 105 |

| 5.1.          | Wet etching of silicon in tetra methyl ammonium hydroxide   | 105 |

| 5.1           | .1. Mechanism of Si etching in TMAH                         | 105 |

| 5.1           | .2. Anisotropy in etching                                   | 106 |

| 5.1           | .3. Effect of TMAH concentration on etch rate               | 107 |

| 5.1           | .4. Hillock formation and surface roughness                 | 108 |

| 5.1           | .5. Aluminium protection                                    | 110 |

| 5.2.          | Ultra-thin silicon based piezocapacitor                     | 111 |

| 5.2           | 2.1. Piezocapacitor fabrication                             | 111 |

| 5.2           | 2.2. Post-processing                                        | 113 |

| 5.2           | 2.3. Thin chip encapsulation                                | 117 |

| 5.3.          | Wafer Scale Etching                                         | 120 |

| 5.3           | 3.1. Device Fabrication                                     | 120 |

| 5.3           | 3.2. Post processing                                        | 121 |

| 5.3           | 3.3. Thin wafer transfer                                    | 122 |

| 5.4.          | Chip Scale Thinning                                         | 124 |

| 5.5.          | Dry etching                                                 | 125 |

| 5.5           | 5.1. Effect of ICP power                                    | 125 |

| 5.5           | 5.2. Effect of chamber pressure                             | 125 |

| 5.5           | 5.3. Effect of SF <sub>6</sub> flow rate                    | 126 |

| 5.5           | 5.4. Effects of the C <sub>4</sub> F <sub>8</sub> flow rate | 126 |

| 5.5           | 5.5. Role of Helium                                         | 126 |

| 5.5           | 5.6. Sample preparation                                     | 127 |

| 5.5           | 5.7. Post-processing                                        | 127 |

| 5.6.          | Mechanical Grinding                                         | 130 |

| 5.7.          | Conclusion                                                  | 131 |

| Chapter       | 6: Flexible Electronics Device Modelling                    | 132 |

| 6.1. <i>A</i> | Analysis of Stress Effects on Ultra-Thin Chips              | 132 |

| 6.1           | .1. Analytical Modelling                                    | 133 |

| 6.1           | .2. Numerical Modelling                                     | 134 |

| 6.1           | .3. Electro-mechanical measurements                         | 135 |

| 6.2.          | Analytical Model of POSFET                                  | 135 |

| 6.2           | 2.1. Implementation of POSFET model in Verilog-A            |     |

| 6.2           | 2.2. Bendable POSFET model                                  | 145 |

| 6.2.3. Stress compensated circuit design using POSFET                    | 151 |

|--------------------------------------------------------------------------|-----|

| 6.3. Modelling the effect of bending on CMOS inverter                    | 155 |

| 6.4. Conclusion                                                          | 156 |

| Chapter 7. Results and Discussion                                        | 158 |

| 7.1. MOSFET characterisation                                             | 158 |

| 7.1.1. Single MOSFET characterisation                                    | 158 |

| 7.1.2. 2x2 array MOSFET characterisation                                 | 159 |

| 7.2. Electrical characterisation of ultra-thin piezo capacitor           | 161 |

| 7.2.1. Electrical Impedance Spectroscopy                                 | 161 |

| 7.2.2. Sensor characterisation                                           | 161 |

| 7.3. P(VDF-TrFE)/BT nanocomposite for tactile sensing application        | 163 |

| 7.3.1. Electrical characterisation of nanocomposite                      | 163 |

| 7.3.2. Sensor characterisation                                           | 164 |

| 7.3.3. Characterisation in extended gate configuration                   | 166 |

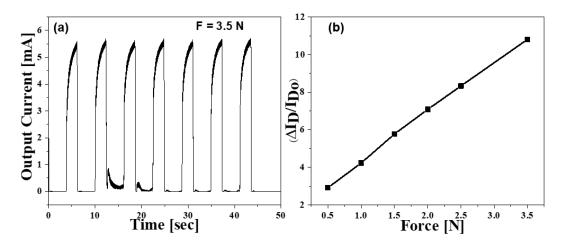

| 7.4. Piezoelectric AlN thin film                                         | 170 |

| 7.4.1. d <sub>33</sub> measurement                                       | 170 |

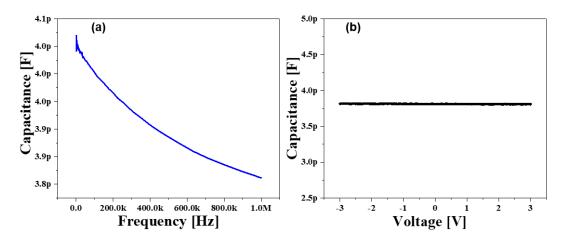

| 7.4.2. C-V measurement                                                   | 170 |

| 7.4.3. Sensor characterisation                                           | 172 |

| 7.4.4. Characterisation in extended gate configuration                   | 173 |

| 7.5. Characterisation of devices after wafer scale thinning and transfer | 174 |

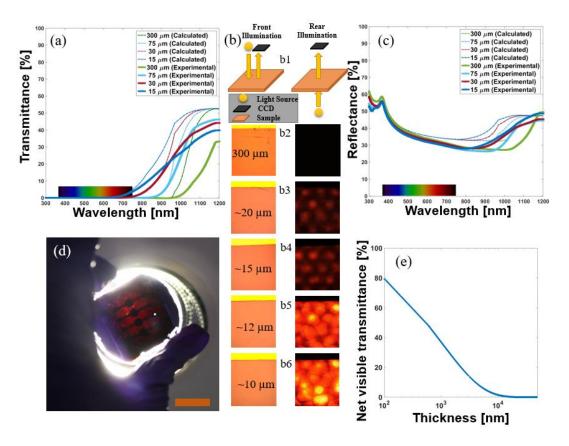

| 7.5.1. Optical characterisation of thin chip                             | 174 |

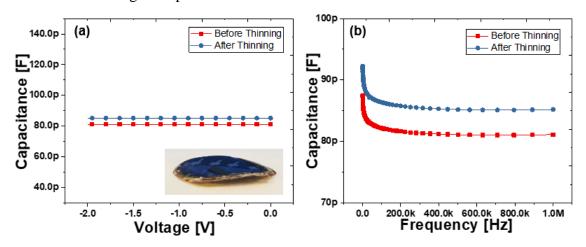

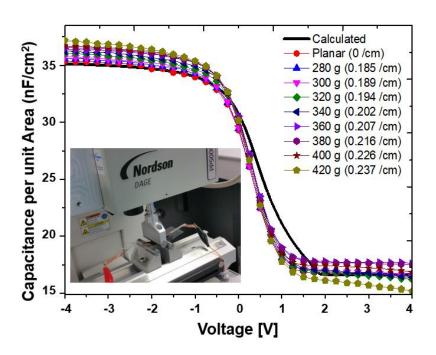

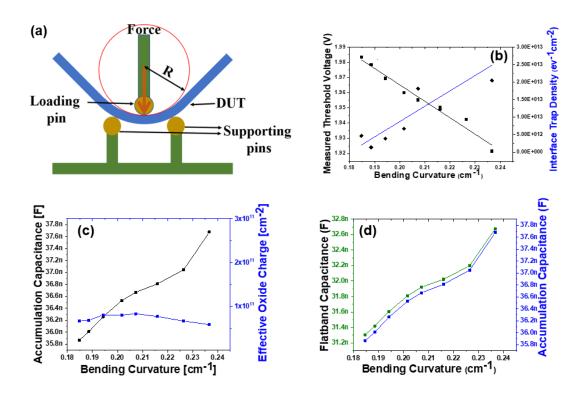

| 7.5.2. Effect of bending on MOSCAP                                       | 176 |

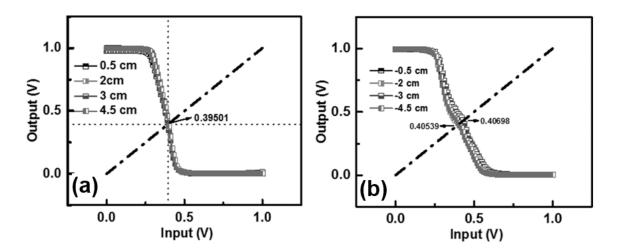

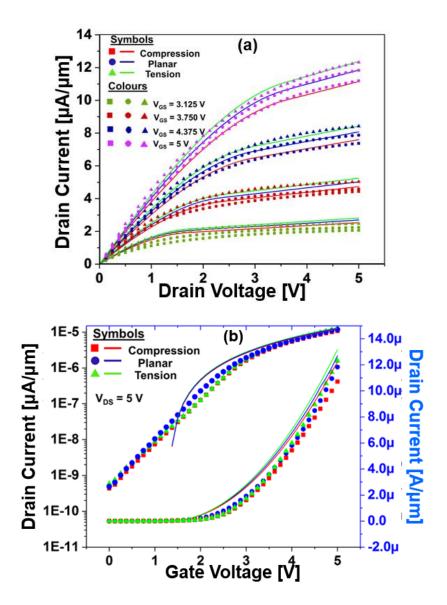

| 7.5.3. Bending Effect on MOSFET                                          | 179 |

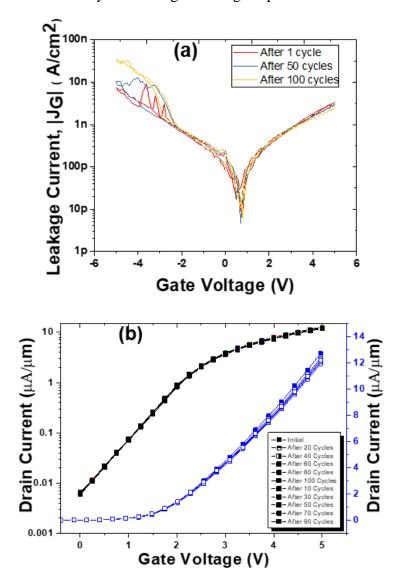

| 7.5.4. Effect of cyclic bending on device performance                    | 182 |

| 7.6. Effect of bending on inverter transfer characteristic (VTC)         | 183 |

| 7.7. Conclusion                                                          | 184 |

| Chapter 8. Conclusion and Future Perspective                             | 186 |

| 8.1. Conclusion                                                          | 186 |

| 8.2. Future Work and Perspectives                                        | 188 |

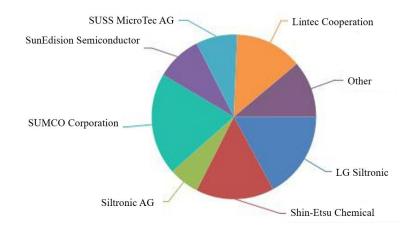

| Appendix 1: Market Analysis                                              | 190 |

| Appendix 2: Design Rule Check list                                       | 193 |

| Pafarancas                                                               | 105 |

### **List of Table**

| Table 2.1: Comparison between mobility, channel length and normalised cut-off frequency of transistors fabricated using different semiconducting materials8 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2: Summary and comparison of various thinning techniques                                                                                            |

| Table 2.3: Comparison between various flexible substrates used for packaging UTCs36                                                                         |

| Table 4.1: Various works reported in literature using PVDF and BT based composite78                                                                         |

| Table 4.2: Piezoelectric and Pyroelectric coefficient of BT and P(VDF-TrFE)79                                                                               |

| Table 5.1: Experimental data for binding energy of silicon planes                                                                                           |

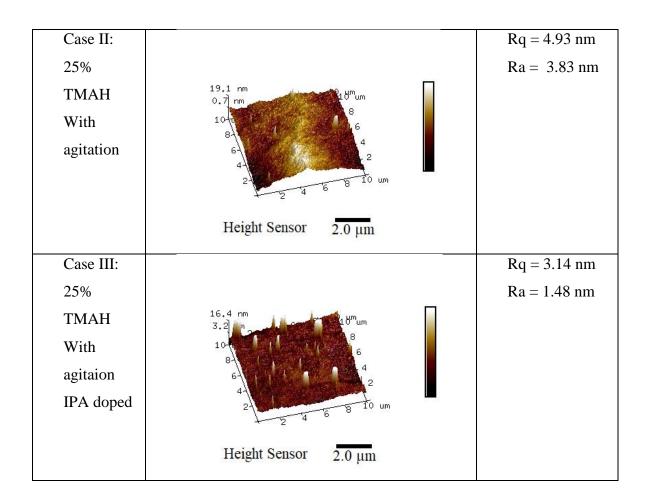

| Table 5.2: AFM scan images and surface roughness values of etched samples109                                                                                |

| Table 5.3: List of laser etching recipes tested for removing the encapsulation118                                                                           |

| Table 5.4: Sputtering parameters for AlN deposition                                                                                                         |

| Table 5.5: Process parameters used for cleaning step before the etching128                                                                                  |

| Table 5.6: Process parameters used for bulk etching of silicon                                                                                              |

| Table 6.1: Experimental values used for model validation                                                                                                    |

| Table 6.2: Stress value at different bending curvatures for 20 μm thick silicon on 50 μm thick polyimide.                                                   |

| Table 6.3: Piezoresistive coefficients for MOSFETs on (100) silicon (* 10 – 12Pa – 1) [226]                                                                 |

| Table 6.4: Product of effective piezoresistive coefficient and stress (~200 MPa) and current variation                                                      |

| Table 6.5: Characteristic parameters of inverter under different bending condition                                                                          |

| Table 7.1: Measured and extracted parameters of fabricated MOSFET158                                                                                        |

| Table 7.2: Comparison of P(VDF-TrFE)/BT sensor with other P(VDF-TrFE) based sensors                                                                         |

| Table 7.3: Normalised net transmittance at different thicknesses of silicon                                                                                 |

| Table 7.4: MOSCAP parameters in planar condition                                                                                                            |

| Table 7.5: Various parameters related to MOSFET characteristics                                                                                             |

| Table 7.6: Values of midpoint voltage, gain and operating points of inverter under planar and bent conditions                                               |

### **List of Figures**

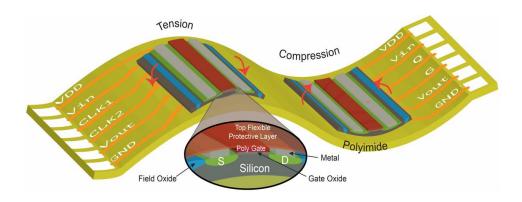

| Figure 1.1: Illustration of seamless integration of thin chip over the flexible substrate2                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1: Various application areas for UTC in the flexible electronics landscape. The left side shows the already demonstrated applications and the right side represents the future applications which will be enabled by these applications                                                                                                                                                                                                                                                                                                                       |

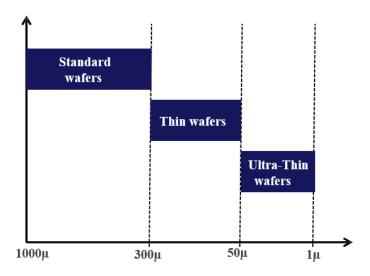

| Figure 2.2: Wafer thickness based terminology classification. For thickness above 300, wafers are termed as standard wafers whereas when their thickness falls below 50, they are termed as ultra-thin wafers                                                                                                                                                                                                                                                                                                                                                          |

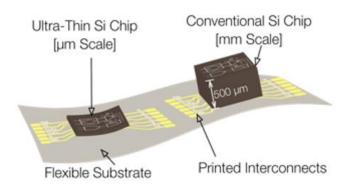

| Figure 2.3: Illustration showing the package volume when an UTC is used in comparison to a conventional chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

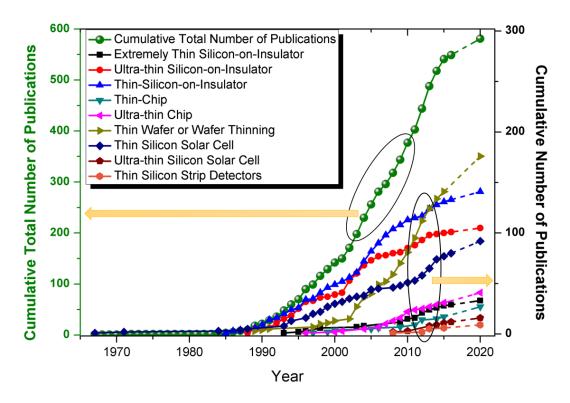

| Figure 2.4: Plot of cumulative number of publication in major area and cumulative total number of publication vs year showing the progress in area of ultra-thin silicon. [Source: Web of Science]                                                                                                                                                                                                                                                                                                                                                                     |

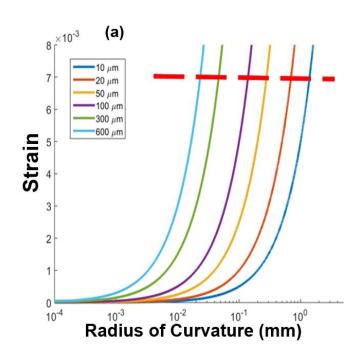

| Figure 2.5: (a) Plot showing the calculated bending strain vs. radius of curvature for various thicknesses of Si wafer. This plot of shows that at a constant strain level, thinner chip can undergo higher bending i.e. lower radius of curvature. (b) (i-ix) Optical pictures of silicon membrane of length 21 mm encapsulated between PDMS layers, under sequential bending. It can observed that the sample achieved the bending radius of 6 mm before breaking. [38]13                                                                                            |

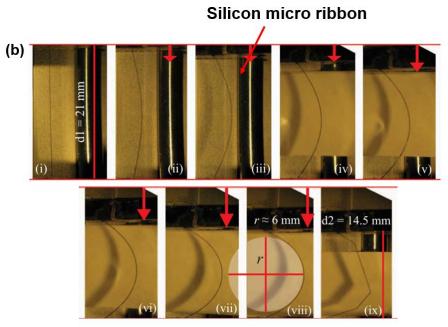

| Figure 2.6: Si conduction and valence bands as a function of biaxial strain. (a) The six Si conduction band valleys along three different directions are equally populated without strain; (b) schematics of bulk Si under biaxial tensile strain; (c) under tensile strain, the valleys are split into two groups. Electrons tend to populate the lower $\Delta_2$ valleys rather than the higher $\Delta_4$ valley; (d) and (e) show the three-top valence band near the $\Gamma$ point for the strain-free and 1.5% biaxial tensile-strained Si, respectively. [41] |

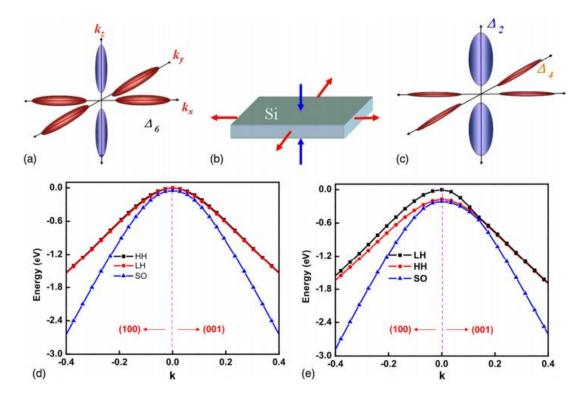

| Figure 2.7: COMSOL simulation of heat distribution in (a) $500 \mu m$ thick chip with area $1 mm^2$ showing creation of hot spots – up to $45^{\circ}C$ for a low input power density of $1 W/cm^2$ (b) $100 \mu m$ thick with area $100 mm^2$ , showing temperature rise of only $2^{\circ}C$ above ambient at same power density. [45]                                                                                                                                                                                                                               |

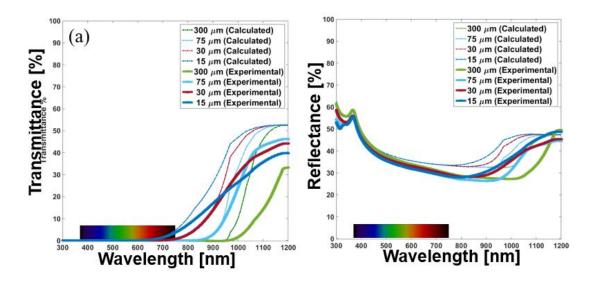

| Figure 2.8: (a) Trasnmittance percentage of light plotted against wavelength for different thickness of silicon (b) Reflectance percentage of light plotted against wavelength for different thickness of silicon. [38]                                                                                                                                                                                                                                                                                                                                                |

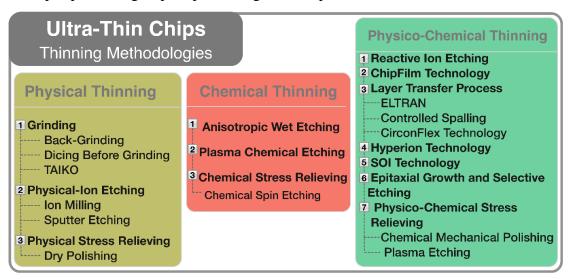

| Figure 2.9: Classification of thinning methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

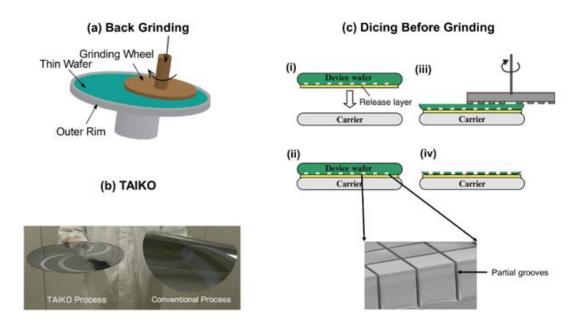

| Figure 2.10: (a) Illustration of Back Grinding. (b) Thin Wafer obtained by the TAIKO process in comparison to warped wafer obtained by conventional back grinding. [57] (c) Illustration of Dicing Before Grinding technique. [58]                                                                                                                                                                                                                                                                                                                                     |

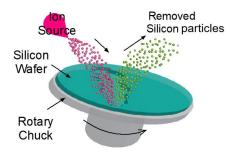

| Figure 2.11: Illustration of Physical Ion Etching21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

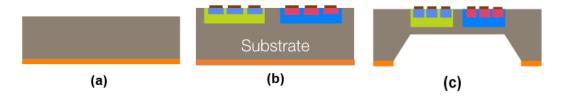

| Figure 2.12: Illustration of pre-processing and post-processing modules in Wet Etching22                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

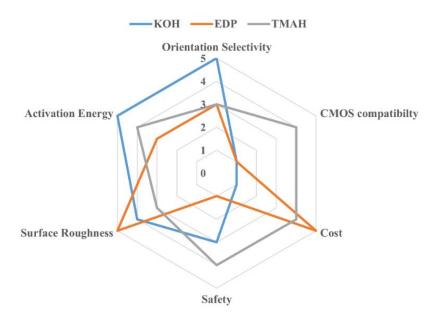

| Figure 2.13: Radar chart showing comparison between KOH, EDP and TMAH on major etching related parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

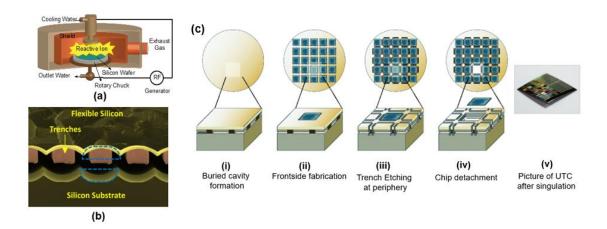

| Figure 2.14: (a) Illustration of RIE and (b) SEM image of trenches etched between released top layer and bulk substrate. [72] (c) Illustration of pre-processing and post-processing modules of ChipFilm. [73]                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

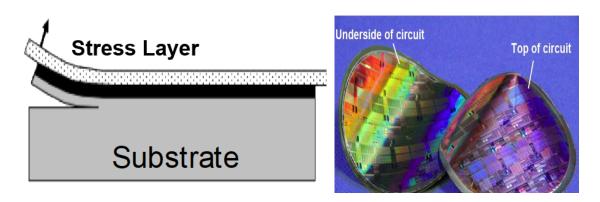

| Figure 2.15: (a) Illustration of controlled spalling process (b) Thin processed wafer obtained via controlled spalling technique. [79]                                                                                                                                                                      |

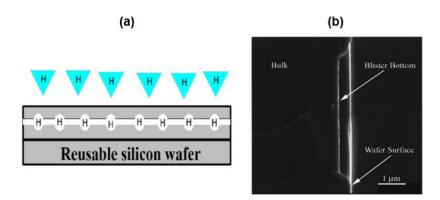

| Figure 2.16: (a) Illustration of proton induced exfoliation (b) Image of blister created after heating hydrogen implanted wafer. [83]                                                                                                                                                                       |

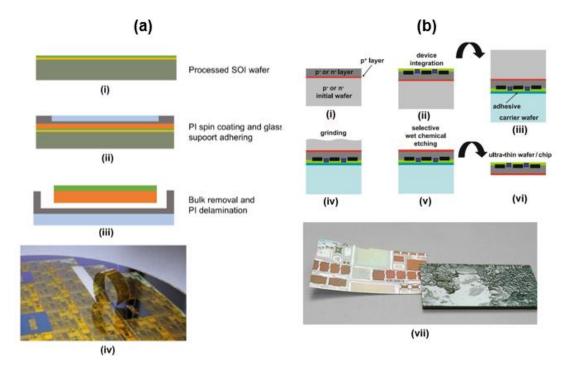

| Figure 2.17: (a) Illustration of CirconFlex technique using SOI wafer[94] (b) Various steps in epitaxial growth and selective etching approach. [95]29                                                                                                                                                      |

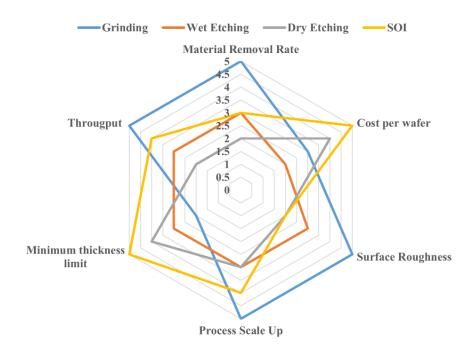

| Figure 2.18: Radar chart showing comparison between main four techniques of realizing UTCs.                                                                                                                                                                                                                 |

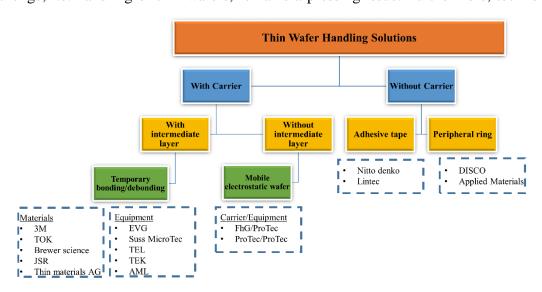

| Figure 2.19: Classification of major thin wafer handling practices                                                                                                                                                                                                                                          |

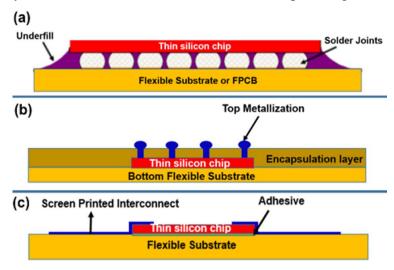

| Figure 2.20: Major schemes of packaging UTC: (a) Flip-Chip packaging of UTC (b) UTC lamination between two flexible layers (c) UTC on flexible substrate with screen-printed connection. [134]                                                                                                              |

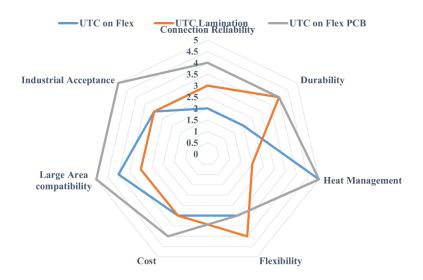

| Figure 2.21: Radar chart showing comparison between major packaging schemes for UTCs.                                                                                                                                                                                                                       |

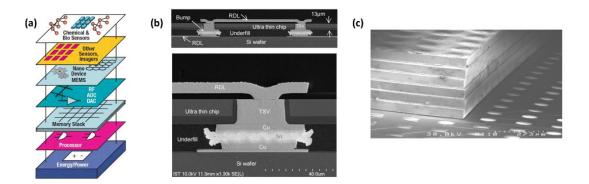

| Figure 2.22: (a) Conceptual structure of UTC based 3D super-chip. [149] (b) Cross-sectioned microstructure of (top) a pair of TSV joints and (bottom) one TSV joint. [150] (c) Six ultrathin silicon layers with TSV and thin silicon interconnections. [151]                                               |

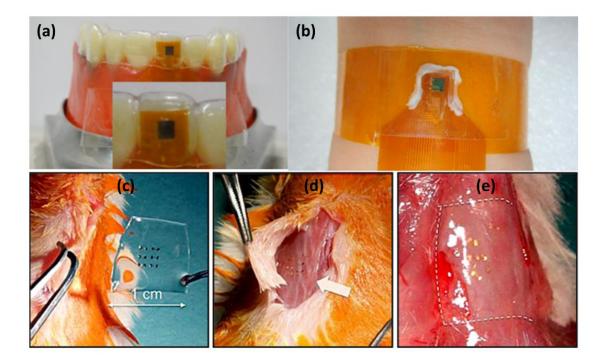

| Figure 2.23: Ultra-thin silicon chip (a) for orthodontic force measurement of invisible aligners (b) for measuring pulse on wrist. [158] Image of procedure and result of the animal toxicity test (c) before, (d) shortly after, and (e) two weeks after implantation silicon electronics on silk. [159]   |

| Figure 2.24: Radial cluster showing the major areas of work presented in the thesis44                                                                                                                                                                                                                       |

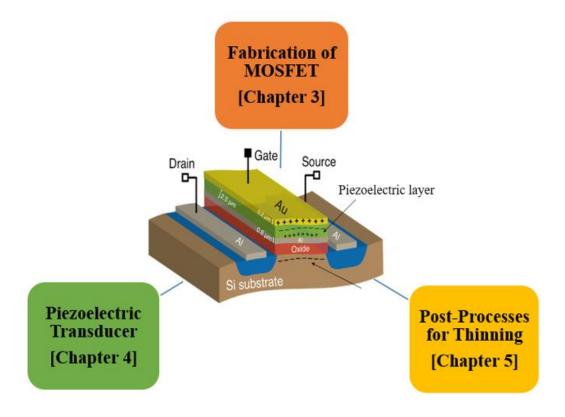

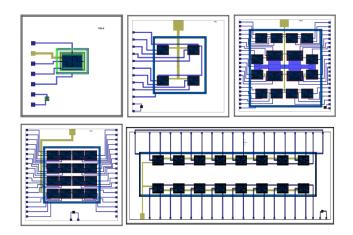

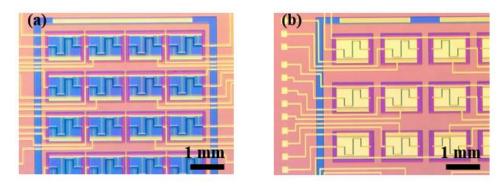

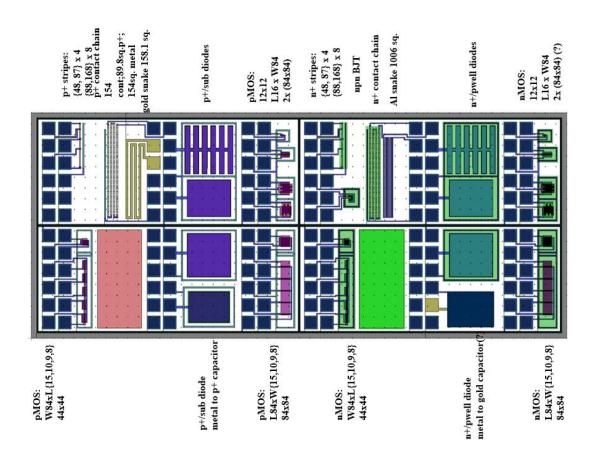

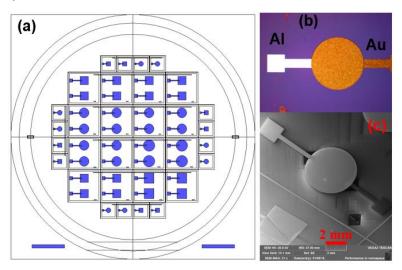

| Figure 3.1: Layout design of different arrangements of POSFET devices. These chips are designed for specific target areas, such as the 4x4 array is for fingertip where high resolution is needed, whereas, 8x2 array is designed for palm area where the large area covering with low resolution is needed |

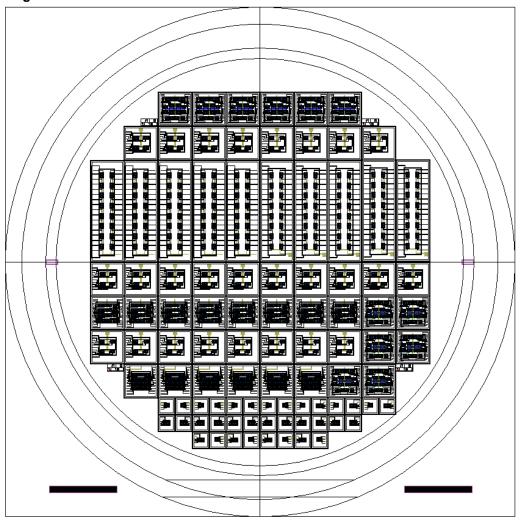

| Figure 3.2: Final layout of wafer consisting various arrangements. Total 96 chips are included in the wafer layout and extra area was left for defining the backside etching window. Two teststrips were also included in the design to monitor the key steps                                               |

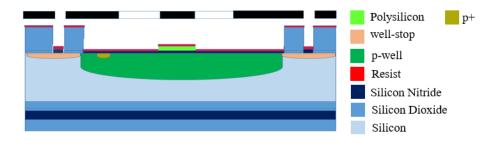

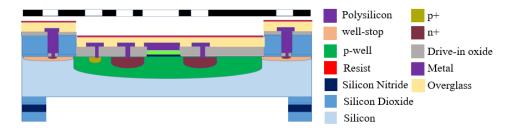

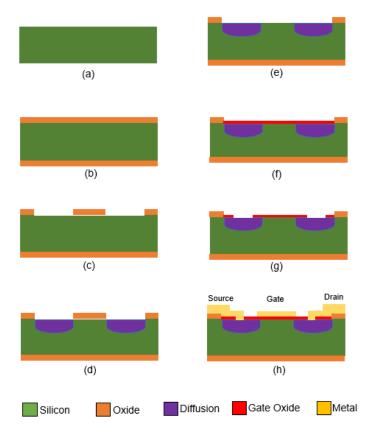

| Figure 3.3: Cross-sectional illustration of n-type double-sided polished wafer53                                                                                                                                                                                                                            |

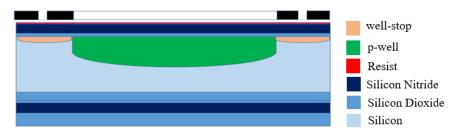

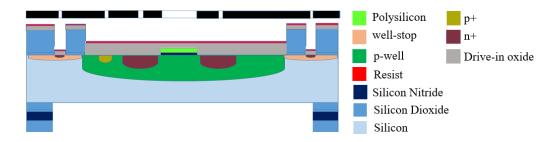

| Figure 3.4: Cross-sectional illustration of lithography performed to do first marker etching. 55                                                                                                                                                                                                            |

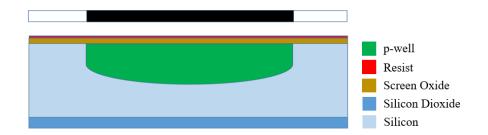

| Figure 3.5: Cross-sectional illustration of lithography performed to do p-well implant56                                                                                                                                                                                                                    |

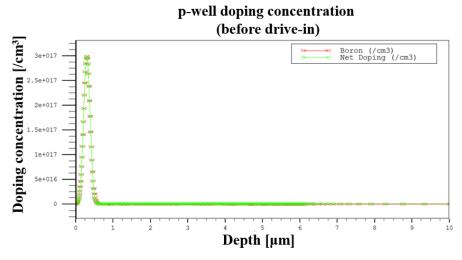

| Figure 3.6: Simulated profile of doping concentration immediately after boron implant. Simulation has been done using SILVACO and the plot shows the depth in silicon at which the concentration is highest, which is also characterised as junction depth immediately after implant                        |

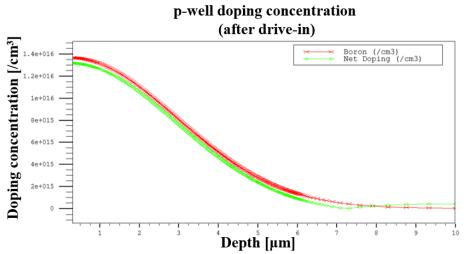

| Figure 3.7: Simulated profile of doping concentration after well drive-in. Simulation has been done using SILVACO and the plot shows the depth how the dopant concentration adopted Gaussian distribution form after the drive-in step                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.8: Cross-sectional illustration of lithography performed to do well stop implant58                                                                                                                                                                                                                                                                                                          |

| Figure 3.9: Cross-sectional illustration of lithography performed to define active area59                                                                                                                                                                                                                                                                                                            |

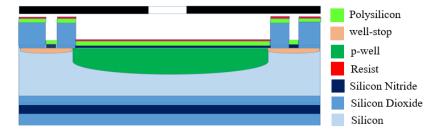

| Figure 3.10: Cross-sectional illustration of lithography performed to define the gate area of MOSFET61                                                                                                                                                                                                                                                                                               |

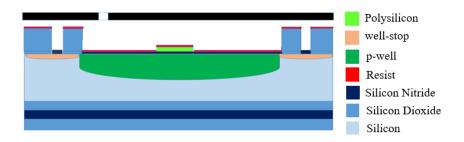

| Figure 3.11: Cross-sectional illustration of lithography performed to define the well contact region                                                                                                                                                                                                                                                                                                 |

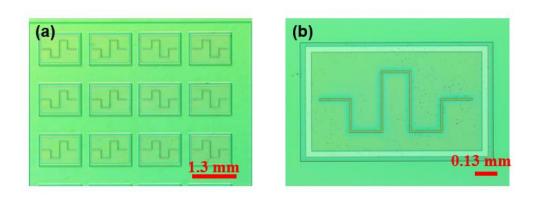

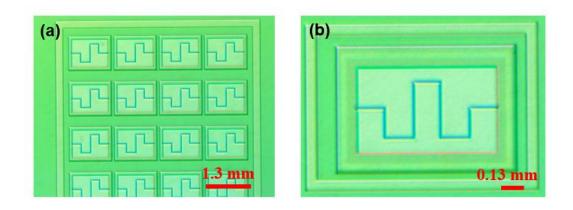

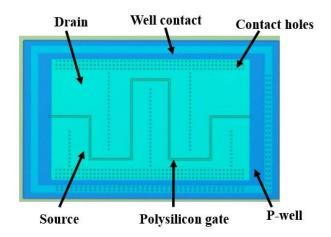

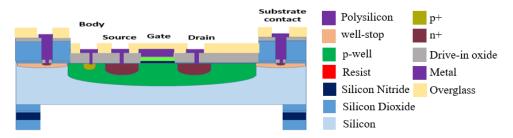

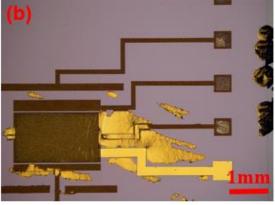

| Figure 3.12: Optical image of device after P-plus lithography. The image on left shows part of chip consisting an array of 3x4 and the image on right shows a single device with serpentine shape gate                                                                                                                                                                                               |

| Figure 3.13: Cross-sectional illustration of lithography performed to define source, drain and substrate contact region                                                                                                                                                                                                                                                                              |

| Figure 3.14: Optical image of device after N-plus lithography. (a) shows the image of a 4x2 array and (b) shows a single cell                                                                                                                                                                                                                                                                        |

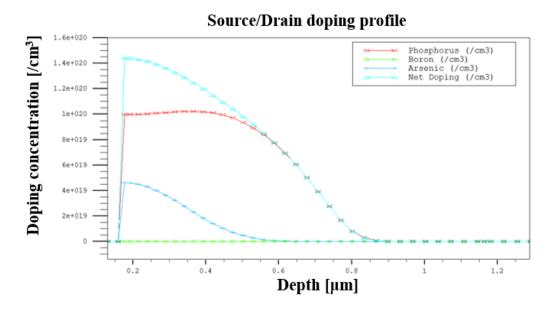

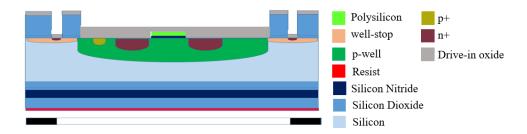

| Figure 3.15: Simulated profile of doping concentration after dopant drive-in. Simulation has been done using SILVACO and the plots shows the depth in silicon at which the doping concentration of phosphorus, arsenic and net doping becomes equal to the intrinsic doping concentration. This depth is called the junction depth of source/drain implant after drive-in and that is around 0.9 μm. |

| Figure 3.16: Cross-sectional illustration of lithography performed to define backside etching window65                                                                                                                                                                                                                                                                                               |

| Figure 3.17:Cross-sectional illustration of lithography performed to define contact holes in passivation layer65                                                                                                                                                                                                                                                                                     |

| Figure 3.18: Optical image of device after opening of contact holes, showing the different regions of the FET.                                                                                                                                                                                                                                                                                       |

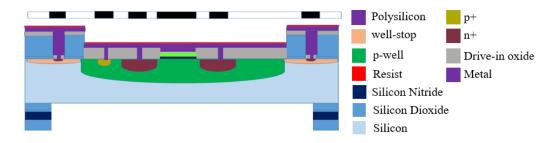

| Figure 3.19: Cross-sectional illustration of lithography performed to define metal layer67                                                                                                                                                                                                                                                                                                           |

| Figure 3.20: Optical images of devices after (a) patterning the resist for lift-off, and (b) deposited metal after contact sintering.                                                                                                                                                                                                                                                                |

| Figure 3.21: Cross-sectional illustration of lithography performed to define opening area in passivation layer                                                                                                                                                                                                                                                                                       |

| Figure 3.22: Cross-sectional image of wafer after protection layer patterning68                                                                                                                                                                                                                                                                                                                      |

| Figure 3.23: Optical images of devices at final stage after overglass deposition and patterning                                                                                                                                                                                                                                                                                                      |

| 68                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 3.24: Micrograph of the fabricated chips. The left image consist two individual MOSFETs, and the right image consists an array of 2x2.                                                                                                                                                                                                                                                        |

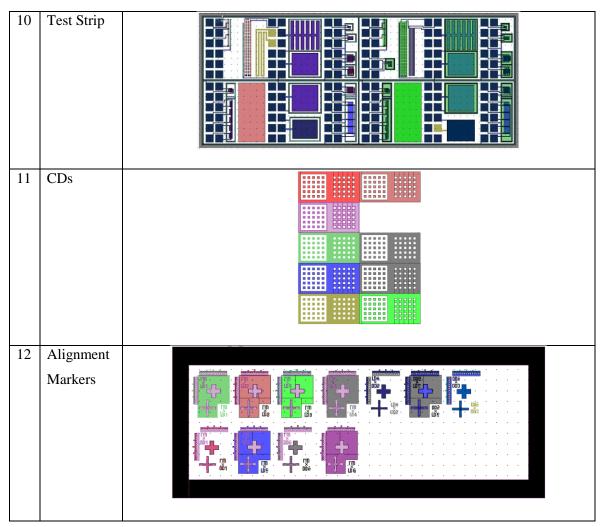

| Figure 3.25: Layout of test strip which was designed to monitor the processing steps. It consisted of nmos, pmos, bjt, capacitors, resistors, implant areas, and oxidation areas. The                                                                                                                                                                                                                |

| devices on this test strips were characterised during the fabrication stage to confirm the success of important steps and extract device parameters69                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

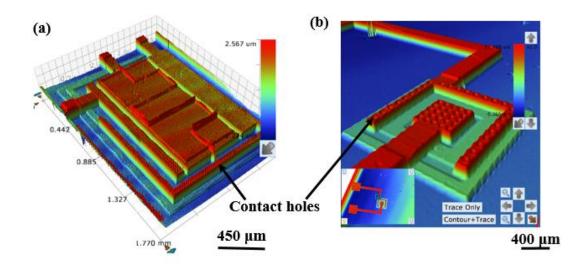

| Figure 3.26: Optical profilometer scan of (left) MOSFET (right) diode, showing the heigh contour of different layers. The scan also shows the contact holes etching over the implant and well-contact area. The optical profiling gives high precision measure of surface roughness quickly as compared to stylus profiling.                                          |

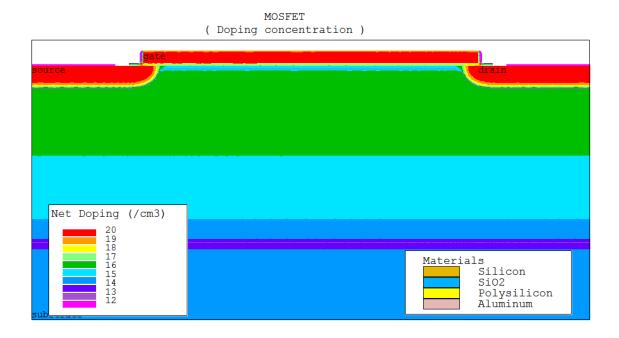

| Figure 3.27: Simulated doping profile of fabricated MOSFET. Simulation has been done using SILVACO and the colour plot shows the doping densities in the different region of MOSFET The source and drain region surface has the highest dopant concentration ( $\sim 10^{20} / \text{cm}^3$ ) and decreases till the p-well junction ( $\sim 10^{17} / \text{cm}^3$ ) |

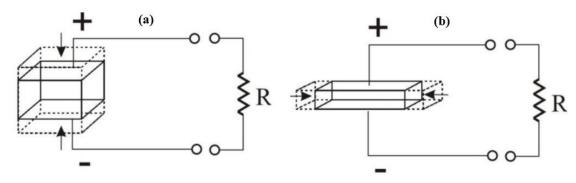

| Figure 4.1: Piezoelectric material in (a) 33 mode and (b) 31 mode. In 33 mode, direction o stress application are in same direction, whereas in 31 mode, they are in perpendicula direction.                                                                                                                                                                          |

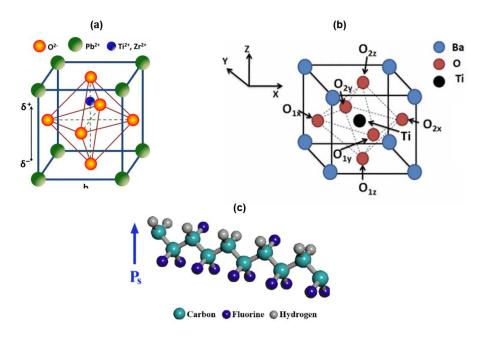

| Figure 4.2: Structure of (a) PZT (b) BT (c) P(VDF-TrFE) [176] [177] [178]76                                                                                                                                                                                                                                                                                           |

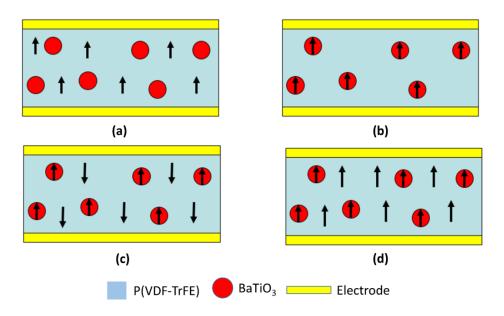

| Figure 4.3: The polarisation state in (a) poled P(VDF-TrFE); (b) poled BT; (c) P(VDF-TrFE and BT poled in opposite direction leading to strengthening of piezoelectric effect; (d) P(VDF TrFE) and BT poled in the same direction to lead to strengthening of pyroelectric effect. [188                                                                               |

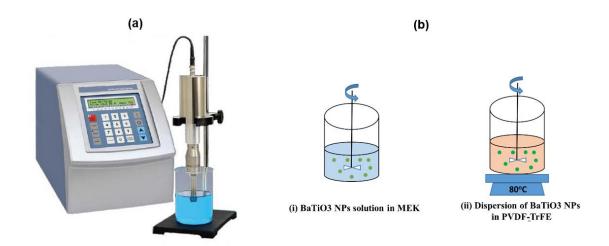

| Figure 4.4: (a) Image of probe-sonicator used for making the composite (b) Illustration of the two-step process adopted to achieve uniform dispersion of NPs in matrix. [196]80                                                                                                                                                                                       |

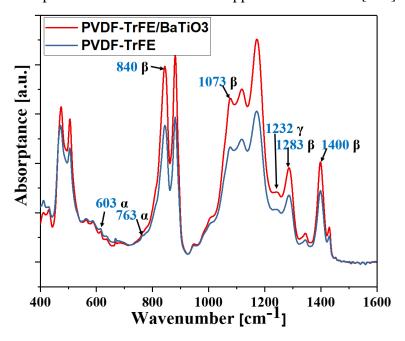

| Figure 4.5: FTIR spectra of P(VDF-TrFE) and P(VDF-TrFE)-BT nanocomposite showing the characteristic peaks of polar β phases, which are at 840 cm <sup>-1</sup> and 1283 cm <sup>-1</sup> . The increase in peak intensity observed is attributed to bonding between fluorine of polymer and barium titanate nanoparticles. [188]                                      |

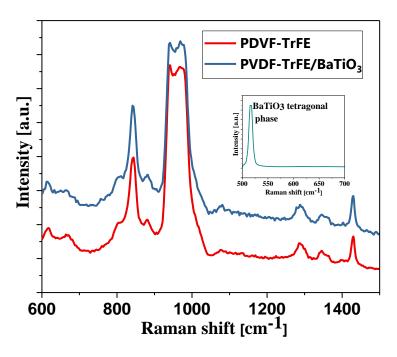

| Figure 4.6: Raman spectra of P(VDF-TrFE) and P(VDF-TrFE)-BT nanocomposite showing the β peak enhancement. Inset shows the tetragonal phase of BT. [188]82                                                                                                                                                                                                             |

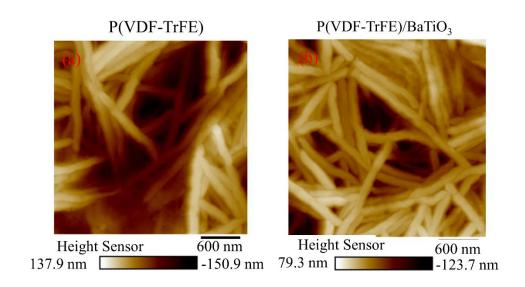

| Figure 4.7: AFM images of P(VDF-TrFE) and P(VDF-TrFE)-BT indicating the emergence of interconnected lamellae upon adding nanoparticles. [188]                                                                                                                                                                                                                         |

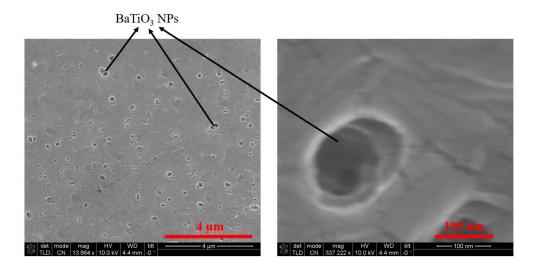

| Figure 4.8: SEM images of nanocomposite showing dispersion of BT nanoparticles in P(VDF TrFE) matrix. [188] There are observed agglomerations of particles as well as individua nanoparticles are also observed                                                                                                                                                       |

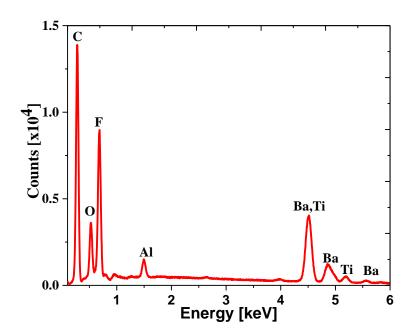

| Figure 4.9: EDX spectra of the nanocomposite highlighting the peaks related to its constituents. The peaks of carbon and fluorine are associated with P(VDF-TrFE) and peaks of Ba, Ti and Care due to the nanoparticles. [188]                                                                                                                                        |

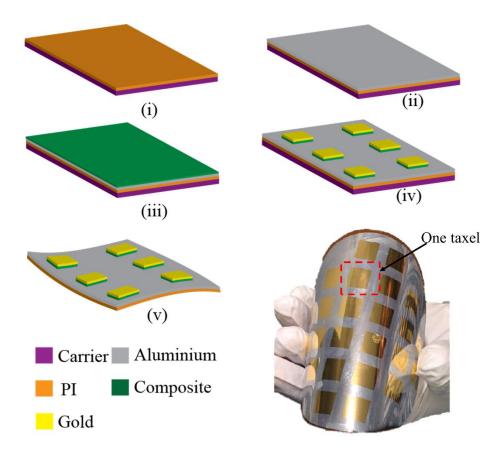

| Figure 4.10: Fabrication steps adopted for realising the P(VDF-TrFE)/BT based sensing structure and image of final flexible sensor. [188]                                                                                                                                                                                                                             |

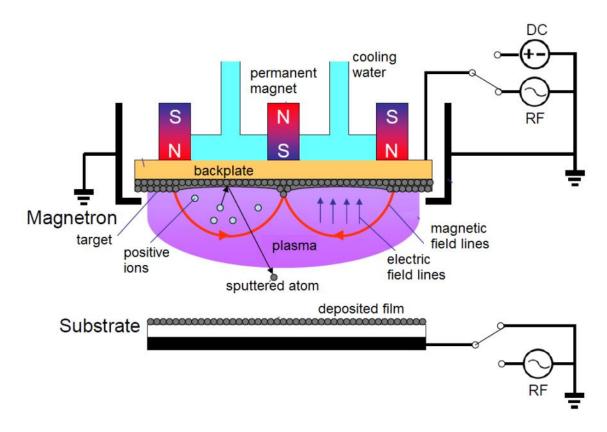

| Figure 4.11: Illustration of RF sputtering system used for AlN film deposition[206]9                                                                                                                                                                                                                                                                                  |

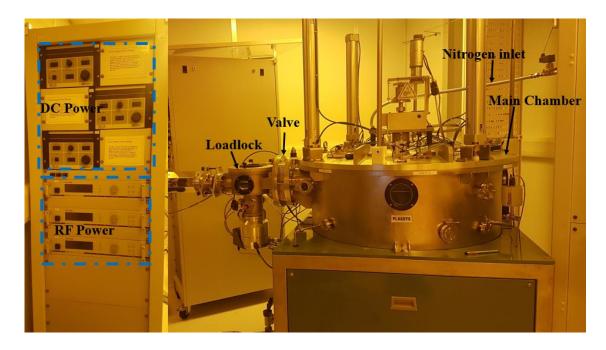

| Figure 4.12: Plassys 900s tool used for AlN deposition.                                                                                                                                                                                                                                                                                                               |

| Figure 4.13: Image of plasma generated during sputtering of AIN.                                                                                                                                                                                                                                                                                                      |

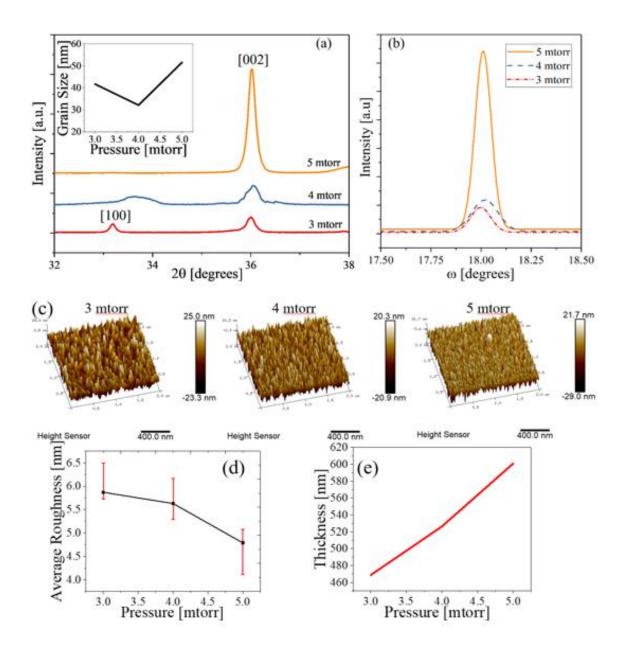

| Figure 4.14: (a) XRD spectrum (b) Rocking curves (c) AFM scan (d) Roughness with statistical variation between scanned sample and (e) Thickness of AlN film deposited at various pressures                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.15: (a) XRD spectrum (b) Rocking curves (c) AFM scan (d) Roughness with statistical variation between scanned sample and (e) Thickness of AlN film deposited at various power                                            |

| Figure 4.16:(a) XRD spectrum (b) Rocking curves (c) AFM scan (d) Roughness with statistical variation between scanned sample and (e) Thickness of AlN film deposited at various gas ratio                                         |

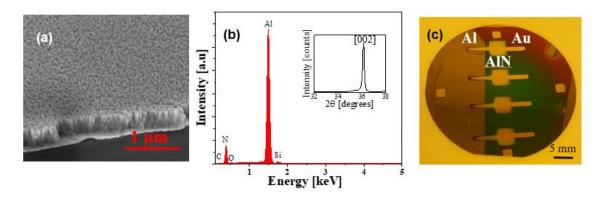

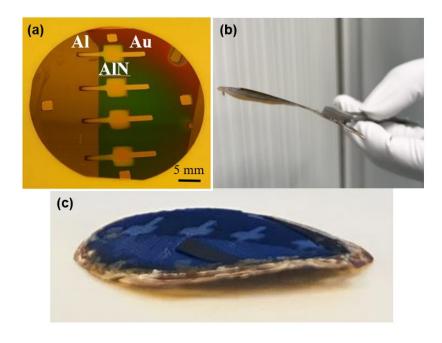

| Figure 4.17: (a) Cross-sectional SEM image of AlN showing the columnar structure of grains (b) EDX and XRD (inset) spectrum of AlN sputtered using optimised recipe (c) Picture of fabricated AlN piezocapacitor on silicon wafer |

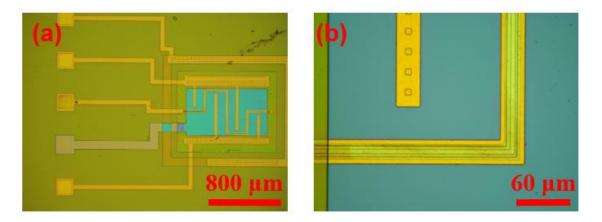

| Figure 4.18: Optical image of chip showing the patterned resist before AlN sputtering at different magnification level. The blue area in (a) is the top gate area which receive the sputtered AlN                                 |

| Figure 4.19: SEM images of the resist pattern after AlN sputtering. Due to the sputtering power ripples and re-flow of resist can be observed at the edges                                                                        |

| Figure 4.20: Optical images of chip after sputtering at 700W and overnight soaking in SVC-14. No lift-off of the AlN happened, as can be observed from the pictures102                                                            |

| Figure 4.21: Optical image of chip after (a) sputtering at 500 W (b) UV exposure, hard bake and sputtering at 500 W. The chip had significant amount of residues attached near the active area of MOSFET                          |

| Figure 4.22: Optical image chip after sputtering over pre-deposited thin Al film followed by lift-off. The chip was clean with some minor residues attached at the edges                                                          |

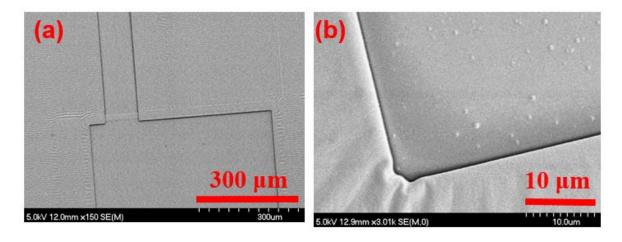

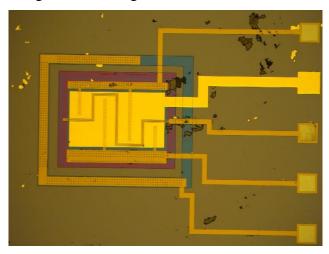

| Figure 5.1: SEM images after etching of silicon showing the anisotropic behaviour of process                                                                                                                                      |

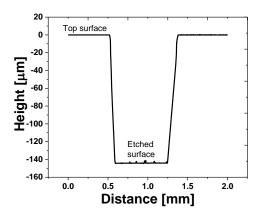

| Figure 5.2: Scan profile of etched pattern in 25% TMAH                                                                                                                                                                            |

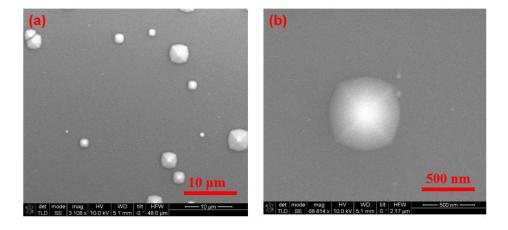

| Figure 5.3: SEM images of hillocks formed during etching                                                                                                                                                                          |

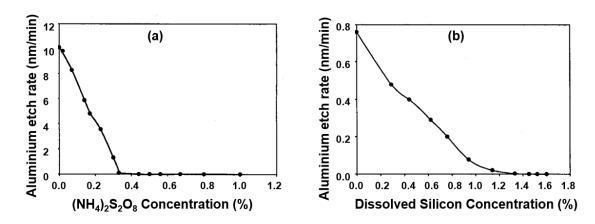

| Figure 5.4: The aluminium etching rate as a function of (a) (NH <sub>4</sub> ) <sub>2</sub> S <sub>2</sub> O <sub>8</sub> concentration (b) dissolved silicon concentration. [213]                                                |

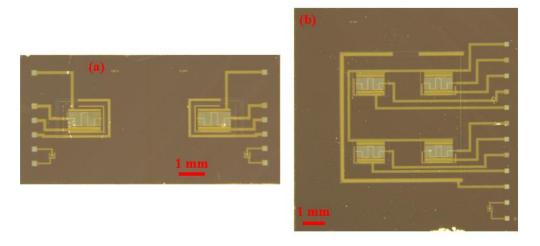

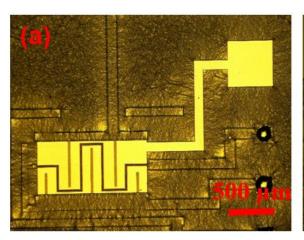

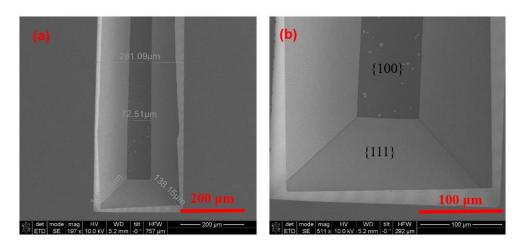

| Figure 5.5: (a) Mask layout for piezocapacitor fabrication. (b) Optical (c) SEM image of fabricated device.                                                                                                                       |

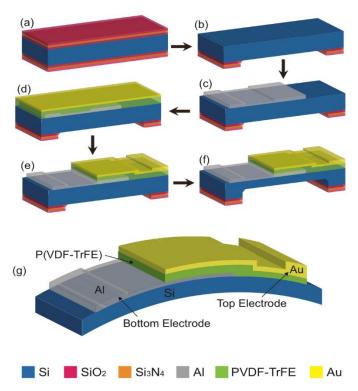

| Figure 5.6:Illustration of process steps followed for realising ultra-thin silicon based piezocapacitor.                                                                                                                          |

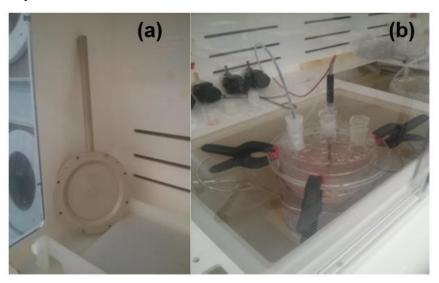

| Figure 5.7: (a) AMMT holder (b) Wet etch setup used for chemical etching of 6 inch wafer                                                                                                                                          |

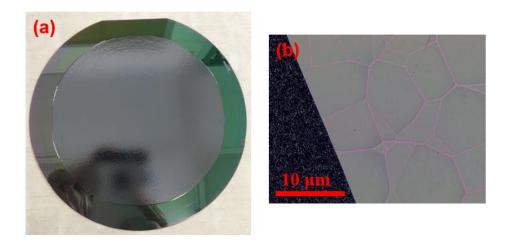

| Figure 5.8: (a) Backside image of thinned wafer (b) Optical image of backside showing the etch pits.                                                                                                                              |

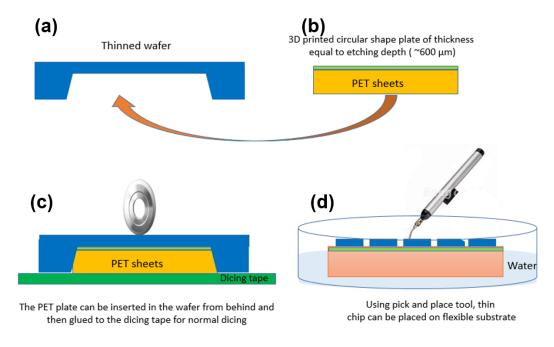

| Figure 5.9: Illustration of PET supported dicing.                                                                                                                                                                                 |

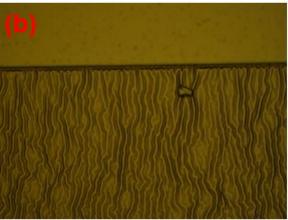

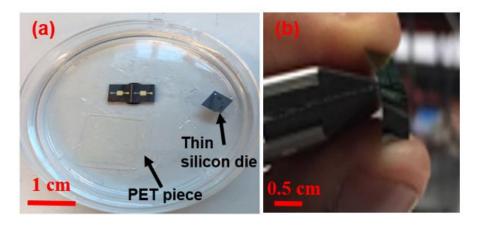

| Figure 5.10: Image of (a) thin chips in water after dicing (b) Bendable chip115                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

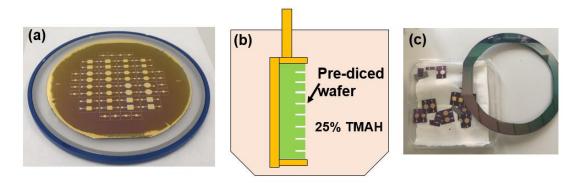

| Figure 5.11: (a) Pre-diced wafer (b) Illustration of dicing before etching process (c) Image of separated chips and outer ring                                                                                                                                                                                                        |

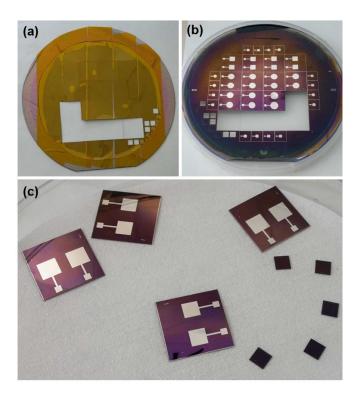

| Figure 5.12: Images of (a) Thinned wafer backside showing polyimide support (b) Front side of diced wafer showing the accuracy of the dicing (c) Separated thinned chips116                                                                                                                                                           |

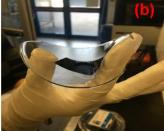

| Figure 5.13: (a) Release of the thin encapsulated chip from carrier wafer (b) Thin encapsulated chip in bent condition (c) Thin encapsulated chip placed on forearm, showing its conformability                                                                                                                                       |

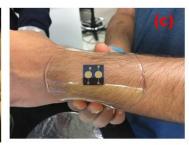

| Figure 5.14. (1-6) Optical images of vias etched in PET by carbon dioxide laser using the recipes tabulated in Table 5.3. Optical image of laser etched via over the (a) bottom and (b) top electrode of capacitor (c) Thin silicon-based capacitor laminated between two PET sheets.119                                              |

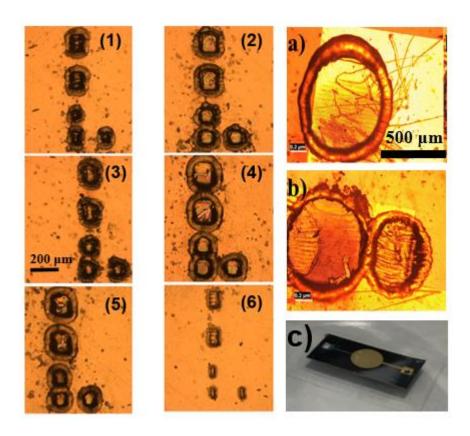

| Figure 5.15: Capacitance vs Voltage plots of thin silicon based capacitor before and after lamination                                                                                                                                                                                                                                 |

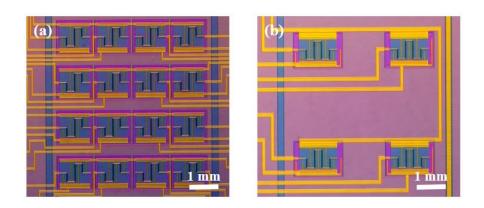

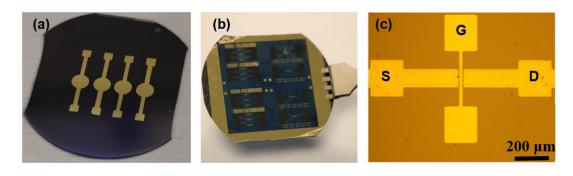

| Figure 5.16: Key process steps carried out to fabricate MOSFETs on bulk silicon wafer121                                                                                                                                                                                                                                              |

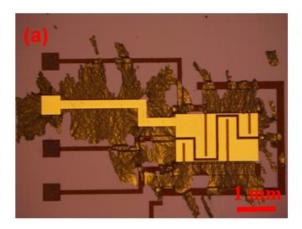

| Figure 5.17: Image of fabricated (a) MOSCAP (b) MOSFET (c) Optical image of single MOSFET                                                                                                                                                                                                                                             |

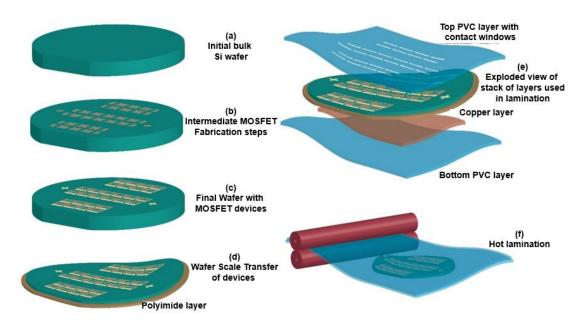

| Figure 5.18: Illustration of wafer-scale MOSFET fabrication, thinning and packaging122                                                                                                                                                                                                                                                |

| Figure 5.19: Image of bendable devices realised after wafer scale thinning and transfer 123                                                                                                                                                                                                                                           |

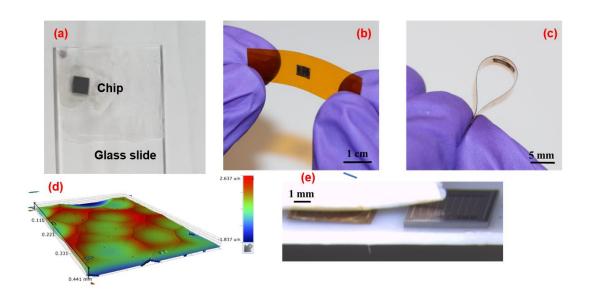

| Figure 5.20: (a) Image of thick chip adhered to glass slide in face down approach before thinning (b)-(c) Thin chip attached to polyimide using thin PDMS layer (d) Optical profilometer scan of etched surface showing etch pits (e) Image showing thickness comparison of chip before and after thinning. (submitted in ISSCC 2019) |

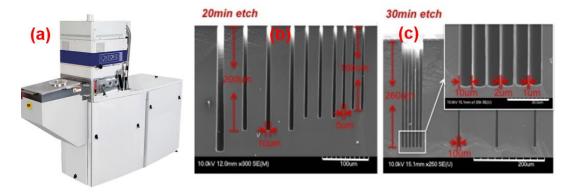

| Figure 5.21: (a) Image of Estrelas used for bulk Si etching (b)-(c) SEM images of deep trenches etched using high etch rate recipes.                                                                                                                                                                                                  |

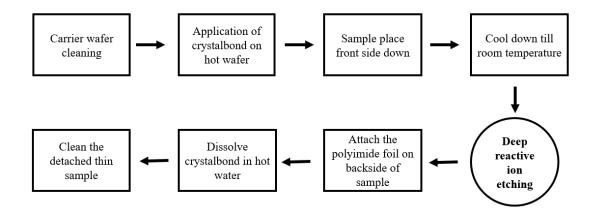

| Figure 5.22: Process flow of DRIE performed to obtain thin silicon                                                                                                                                                                                                                                                                    |

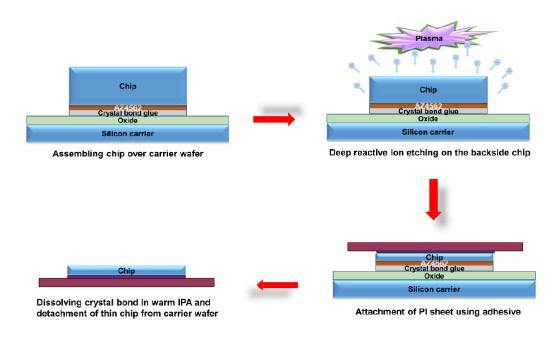

| Figure 5.23: Illustration of DRIE of sample and its transfer on flexible substrate129                                                                                                                                                                                                                                                 |

| Figure 5.24: Image of AlN piezocapacitor (a) before thinning (b-c) after thinning129                                                                                                                                                                                                                                                  |

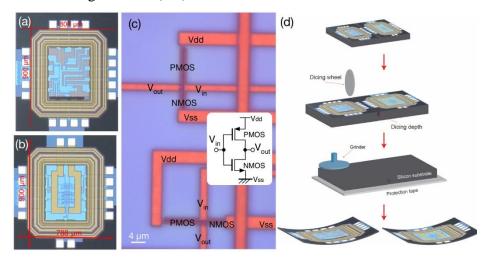

| Figure 5.25: (a) Microphotograph of the fabricated chip (d) Optical image of inverter (d) Dicing before grinding approach adopted for thinning the chip                                                                                                                                                                               |

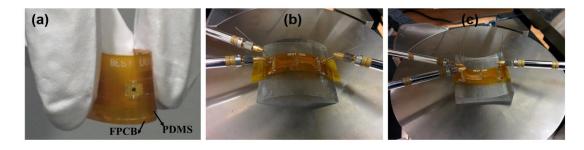

| Figure 5.26: Image of (a) Thin chip packaged on FPCB (b) Testing under tensile stress (c) Testing under compressive stress                                                                                                                                                                                                            |

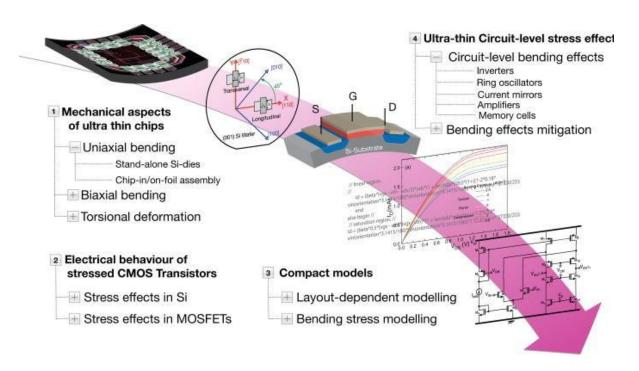

| Figure 6.1: Illustrative figure showing different techniques for modelling the effect of bending stress on devices and circuits. [214]                                                                                                                                                                                                |

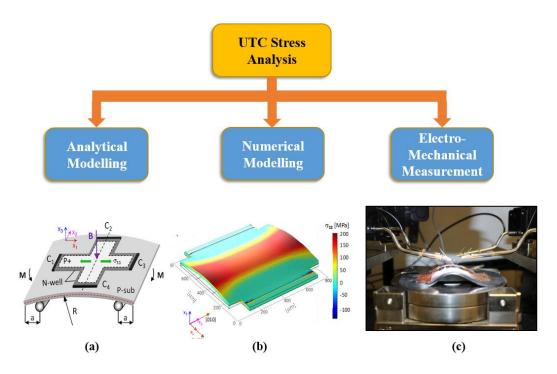

| Figure 6.2: Various techniques i.e. analytical modelling, numerical modelling and electromechanical measurements used for studying and analysing the effect of bending on device response. While the first two are used for the making predictive models, the actual measurements are necessary to fit those models.[214]             |

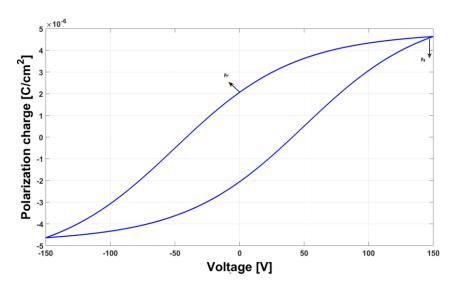

| Figure 6.3: Simulated Hysteresis curve of P(VDF-TrFE). The saturation polarisation state is the maximum charge which is attained at 150V and upon removing the electric field, the charge drops down to remnant polarisation state. [222]                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

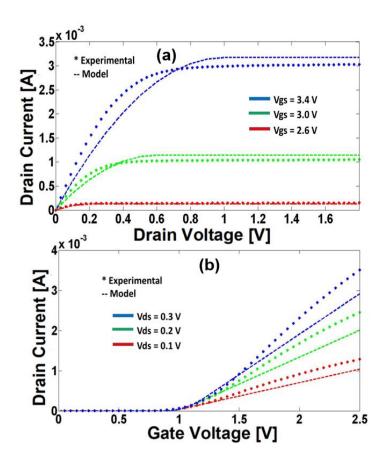

| Figure 6.4: Experimental vs model data plot of (a) output (b) transfer characteristics of POSFET. [222]                                                                                                                                                                                   |

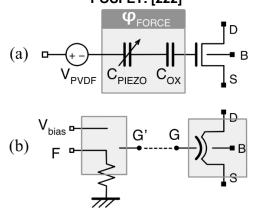

| Figure 6.5: (a) POSFET macro-model structure consisting the piezoelectric part and MOSFET, (b) Bendable POSFET Verilog-A sub-circuit blocks and external connections. [223]139                                                                                                            |

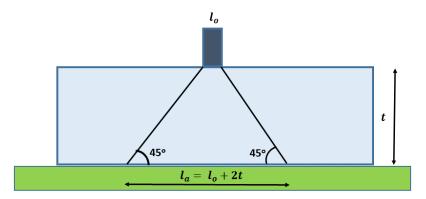

| Figure 6.6: Illustration of force distribution through PDMS. The tip has dimension of l <sub>o</sub> which during force application creates a cone of action and the base of that cone decides how much force is being experienced by the sensor                                          |

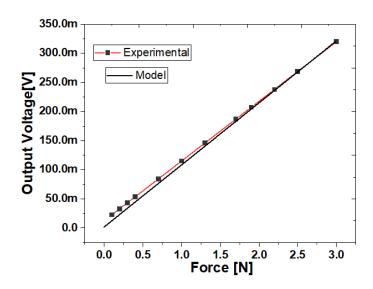

| Figure 6.7: Plot of POSFET response vs Force (experimental and model)144                                                                                                                                                                                                                  |

| Figure 6.8: Modelled dynamic response of POSFET to 1N force                                                                                                                                                                                                                               |

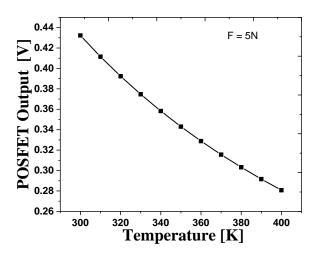

| Figure 6.9: Effect of temperature on POSFET output voltage. The temperature was varied from room temperature (300K) to the higher range, and due to decrease in carrier mobility, the output decreases under the application of a constant force of 5N                                    |

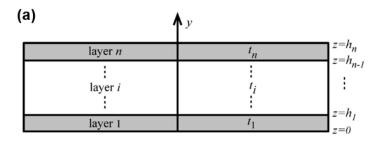

| Figure 6.10: An elastic multilayer strip considered (a) without and (b) with external bending external bending                                                                                                                                                                            |

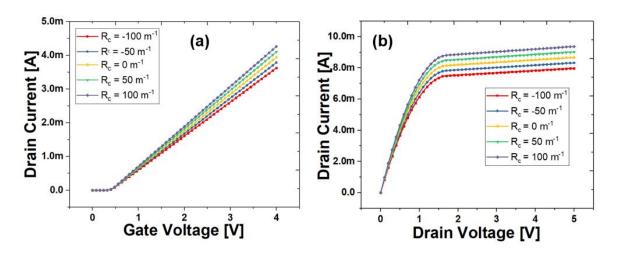

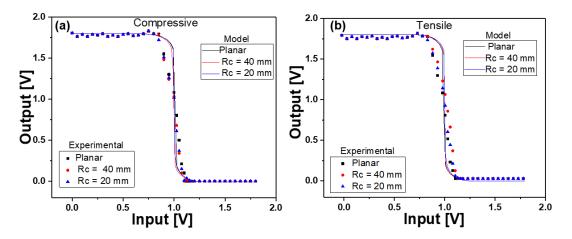

| Figure 6.11: (a) Transfer (b) Output characteristics of MOSFET under different bending conditions. As the bending move from tensile state to the compressive state, decrease in the current can be observed                                                                               |

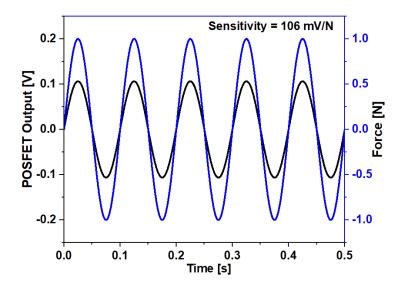

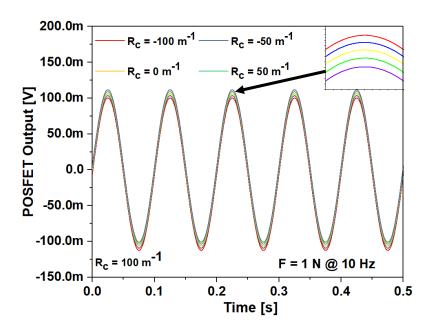

| Figure 6.12: POSEFT output with sinusoidal force applied under different bending conditions.  Under tensile stress, increase in drain current can be observed and opposite for compressive stress                                                                                         |

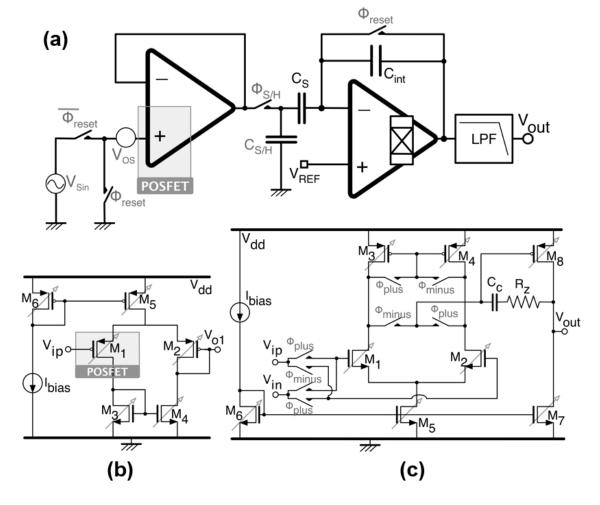

| Figure 6.13: (a) Block diagram of the proposed readout circuit for POSFET microsystem. (b) Schematic diagram of the POSFET biasing as voltage follower, and (c) Schematic circuit diagram of two stage single-ended amplifier. [223]                                                      |

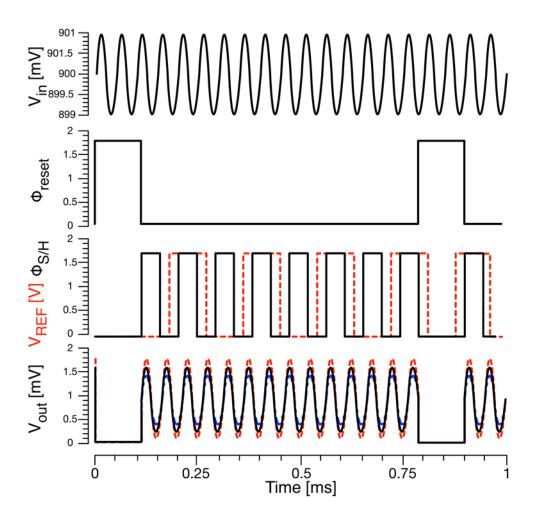

| Figure 6.14: Simplified timing diagram of a complete readout operation with transient response of output voltage. Black line shows the output voltage in planar state, where the red and blue dotted lines show the transient response under compression and tension, respectively. [223] |

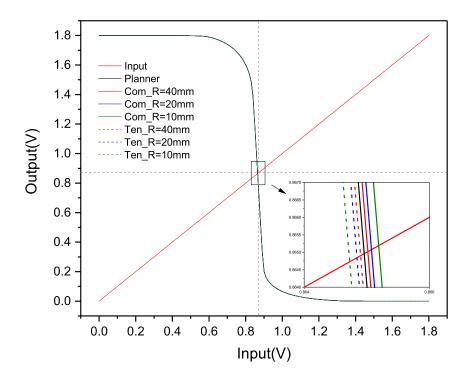

| Figure 6.15: DC characteristics of inverter with different bending radius in both tensile (dashed lines) and compressive stress (solid lines). The middle voltage point decreases under tensile and increases under compressive                                                           |

| Figure 6.16: VTC characteristics of flexible inverters at (a) Tensile stress (b) Compressive stress. [232]                                                                                                                                                                                |

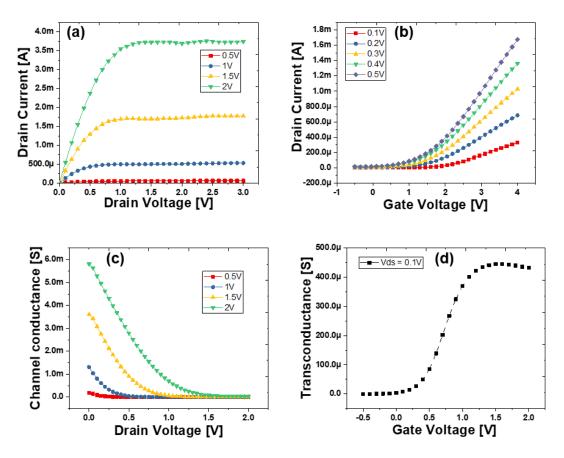

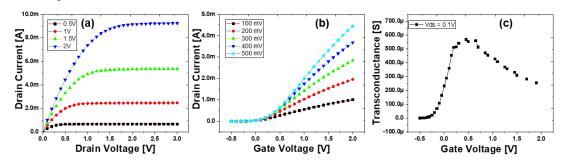

| Figure 7.1: (a) Output characteristics of MOSFET at different gate voltages (b) Transfer characteristics of MOSFET at different drain voltages (c) Channel conductance of MOSFET at different gate voltages (d) Transconductance plot of MOSFET at drain voltage of 100 mV.               |

|                                                                                                                                                                                                                                                                                           |

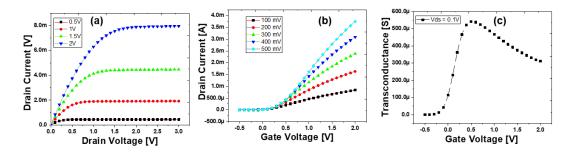

| Figure 7.2: (a) Output (b) Transfer characteristics (c) Transconductance plot of 1 <sup>st</sup> element of 2x2 array                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

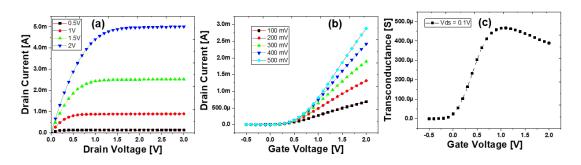

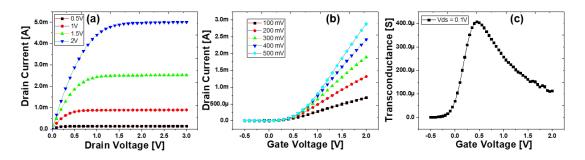

| Figure 7.3: (a) Output (b) Transfer characteristics (c) Transconductance plot of 2 <sup>nd</sup> element of 2x2 array                                                                                                                                                                                                                                                                                                     |

| Figure 7.4: (a) Output (b) Transfer characteristics (c) Transconductance plot of 3 <sup>rd</sup> element of 2x2 array.                                                                                                                                                                                                                                                                                                    |

| Figure 7.5: (a) Output (b) Transfer characteristics (c) Transconductance plot of 4 <sup>th</sup> element of 2x2 array.                                                                                                                                                                                                                                                                                                    |

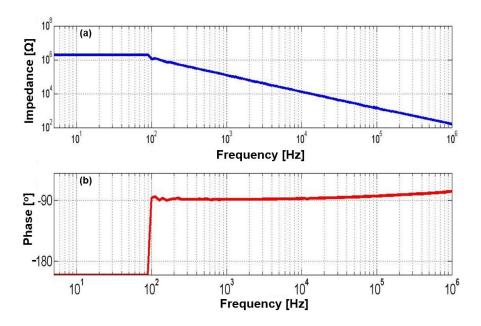

| Figure 7.6: (a) Magnitude and (b) Phase plot of ultra-thin silicon-based piezocapacitor. These plots confirms the capacitive behaviour of fabricated device and the obtained data was used to calculate the dielectric constant of material.[233]                                                                                                                                                                         |

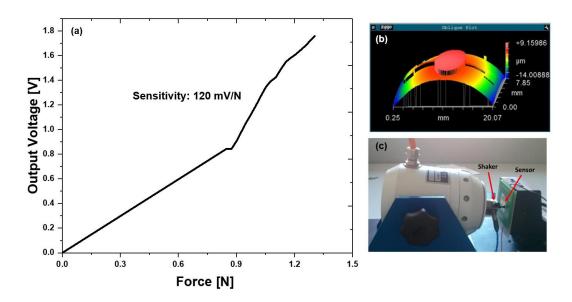

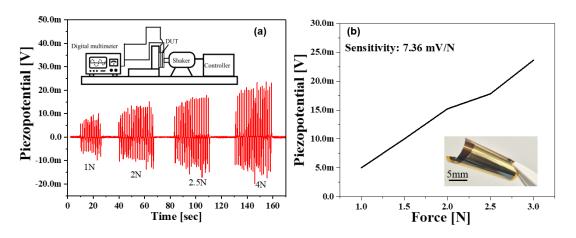

| Figure 7.7: (a) Sensor characteristic curve obtained by varying the force level over the sensing structure. The sensitivity of 120 mV/N was obtained during characterisation. (b) Optical profilometer scan of one sensing device where the warping effect due to low thickness can be observed. (c) The image of measurement setup consisting of a TIRA shaker, a piezotronic force monitor and the sample holder. [233] |

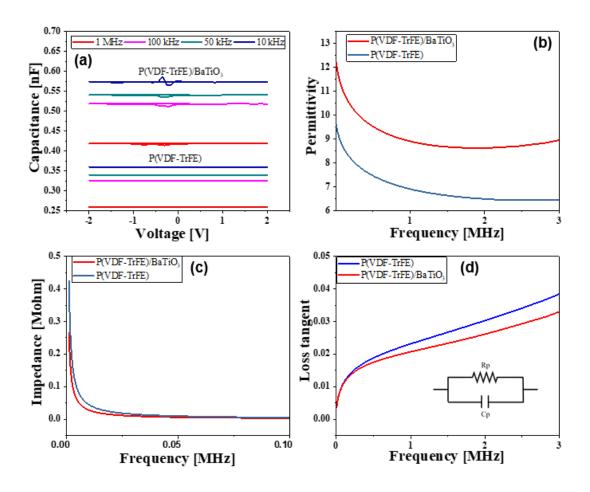

| Figure 7.8: Electrical characteristics plot of P(VDF-TrFE)–BT nanocomposite. (a) Capacitance vs Voltage, (b) Dielectric Permittivity vs Frequency (c) Impedance vs Frequency, (d) Loss tangent vs Frequency. [188]                                                                                                                                                                                                        |

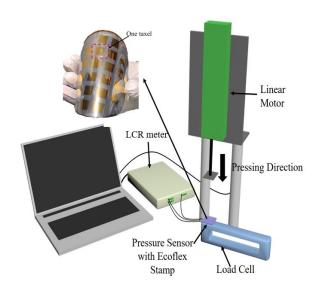

| Figure 7.9: The schematic of setup used for characterising the nanocomposite sensor. It consisted of a LabView controlled pressing setup and a load cell for monitoring the magnitude of applied force,                                                                                                                                                                                                                   |

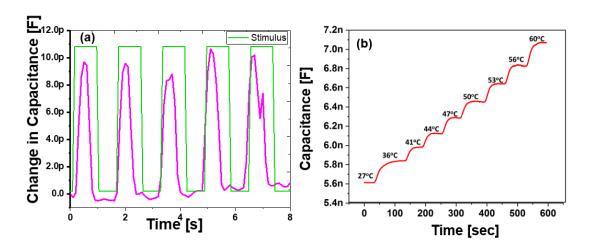

| Figure 7.10: Response of sensor to (a) periodic force of magnitude 45 mN (b) <i>stepwise increase</i> in temperature. [196]                                                                                                                                                                                                                                                                                               |

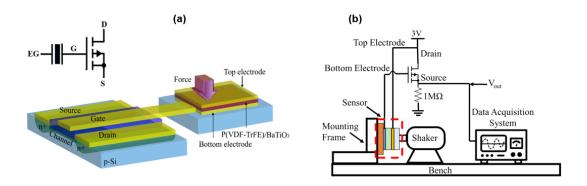

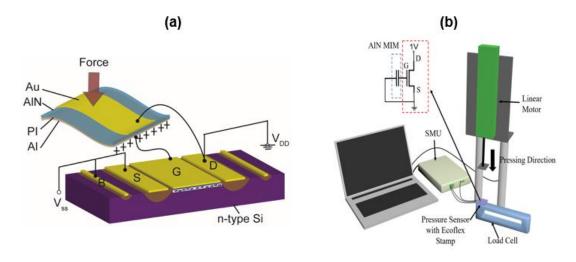

| Figure 7.11: (a) Illustration of P(VDF-TrFE)-BT nanocomposite coupled to a MOSFET in extended gate configuration and its symbolic representation.(b) Schematic of characterisation setup. [188]                                                                                                                                                                                                                           |

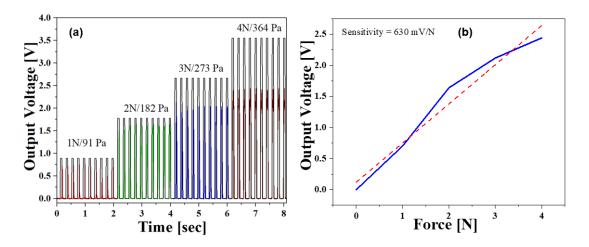

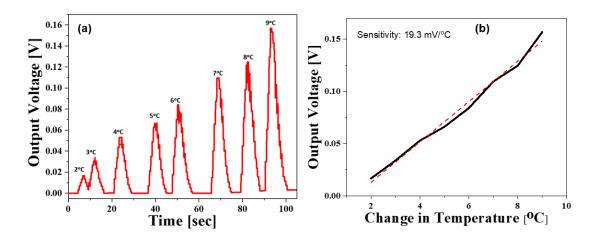

| Figure 7.12: (a) Variation of output voltage at different force levels, and (b) Calibration curves of P(VDF-TrFE)/BT nanocomposite for change in force. [188]                                                                                                                                                                                                                                                             |