Mohd Zain, Anis Suhaila (2013) Scaling and variability in ultra thin body silicon on insulator (UTB SOI) MOSFETs. PhD thesis

http://theses.gla.ac.uk/4281/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Glasgow Theses Service http://theses.gla.ac.uk/ theses@gla.ac.uk

# Scaling and Variability in Ultra Thin Body Silicon on Insulator (UTB SOI) MOSFETs

Anis Suhaila Mohd Zain

Submitted in fulfillment of the requirements for the Degree of Doctor of Philosophy

Department of Electronics & Electrical Engineering School of Engineering College of Science and Engineering University of Glasgow

Copyright © Anis Suhaila Mohd Zain, 2013

## **Dedication**

"So, verily, with every difficulty, there is relief. Verily, with every difficulty there is relief." (Al-Inshirah: 5-6)

To my husband, Nurulfajar Abd Manap – for his love, passion and fortitude my solehah princess, Nur Najla Alia – for her pure affection and sacrifice my dearest parents & families – for their endless *dua*' and supports

And my late son, Amir Yusuf – who has taught me the true meaning of patience, humble, perseverance, life and hope.

"With you, it wasn't long enough together, but it was long enough to last forever."

27 June 2008-6 March 2009

## Abstract

The main objective of this thesis is to perform a comprehensive simulation study of the statistical variability in well scaled fully depleted ultra thin body silicon on insulator (FD-UTB SOI) at nanometer regime. It describes the design procedure for template FD-UTB SOI transistor scaling and the impacts of statistical variability and reliability the scaled template transistor.

The starting point of this study is a systematic simulation analysis based on a welldesigned 32nm thin body SOI template transistor provided by the FP7 project PULLNANO. The 32nm template transistor is consistent with the International Technology Roadmap for Semiconductor (ITRS) 2009 specifications. The wellestablished 3D 'atomistic' simulator GARAND has been employed in the designing of the scaled transistors and to carry out the statistical variability simulations. Following the foundation work in characterizing and optimizing the template 32 nm gate length transistor, the scaling proceeds down to 22 nm, 16 nm and 11 nm gate lengths using typically 0.7 scaling factor in respect of the horizontal and vertical transistor dimensions. The device design process is targeted for low power applications with a careful consideration of the impacts of the design parameters choice including buried oxide thickness ( $T_{BOX}$ ), source/drain doping abruptness ( $\sigma$ ) and spacer length ( $L_{spa}$ ). In order to determine the values of  $T_{BOX}$ ,  $\sigma$ , and  $L_{spa}$ , it is important to analyze simulation results, carefully assessing the impact on manufacturability and to consider the corresponding trade-off between short channel effects and on-current performance. Considering the above factors,  $T_{BOX} = 10$ nm,  $\sigma = 2$ nm/dec and  $L_{spa} = 7$ nm have been adopted as optimum values respectively.

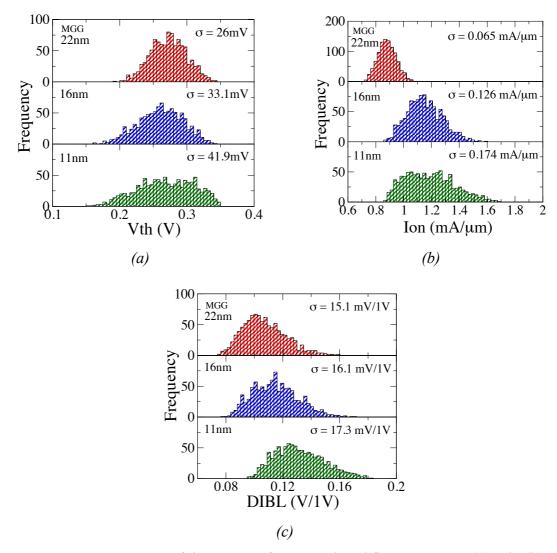

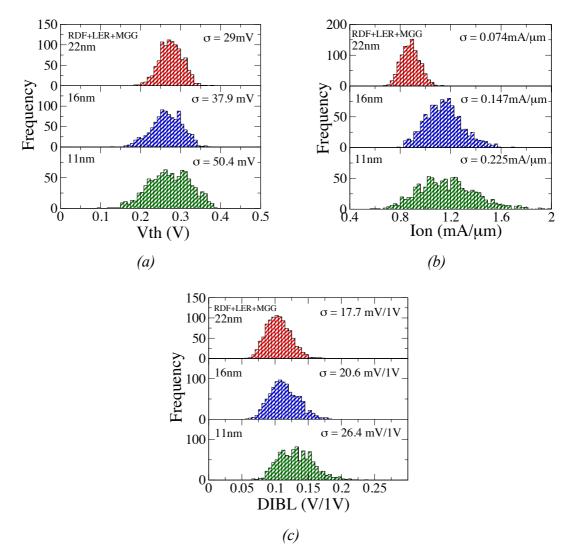

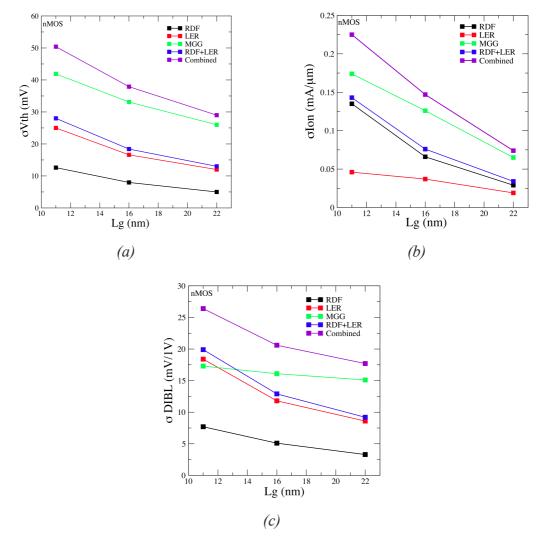

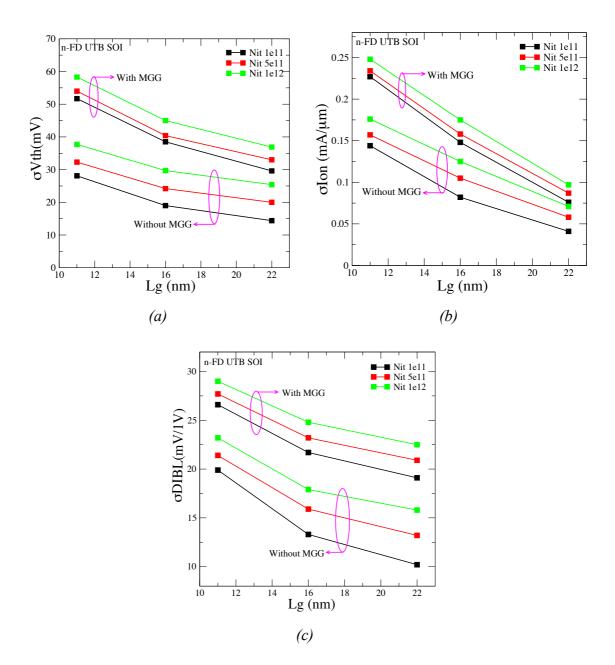

The statistical variability of the transistor characteristics due to intrinsic parameter fluctuation (IPF) in well-scaled FD-UTB SOI devices is systematically studied for the first time. The impact of random dopant fluctuation (RDF), line edge roughness (LER) and metal gate granularity (MGG) on threshold voltage  $(V_{th})$ , on-current  $(I_{on})$  and drain induced barrier lowering (DIBL) are analysed. Each principal sources of variability is treated individually and in combination with other variability sources in the simulation of large ensembles of microscopically different devices. The introduction of highk/metal gate stack has improved the electrostatic integrity and enhanced the overall device performance. However, in the case of fully depleted channel transistors, MGG has become a dominant variability factor for all critical electrical parameters at gate first technology. For instance,  $\sigma V_{th}$  due to MGG increased to 41.9 mV at 11nm gate length compared to 26.0 mV at 22nm gate length. Similar trend has also been observed in  $\sigma I_{on}$ , increasing from 0.065 up to 0.174 mA/ $\mu$ m when the gate length is reduced from 22 nm down to 11 nm. Both RDF and LER have significant role in the intrinsic parameter fluctuations and therefore, none of these sources should be overlooked in the simulations.

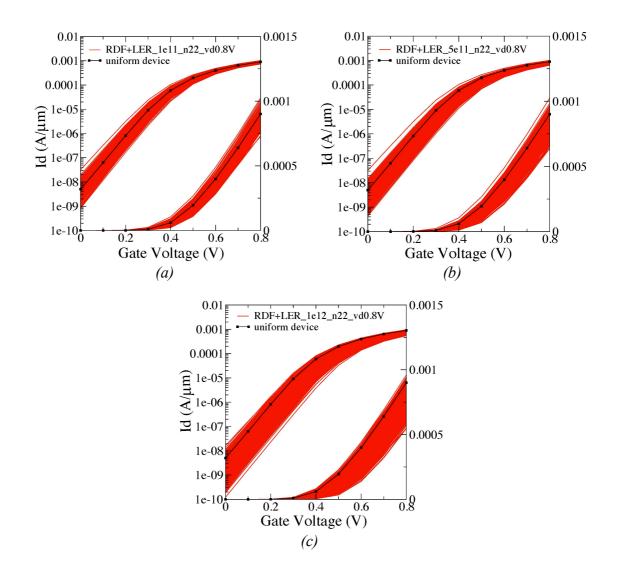

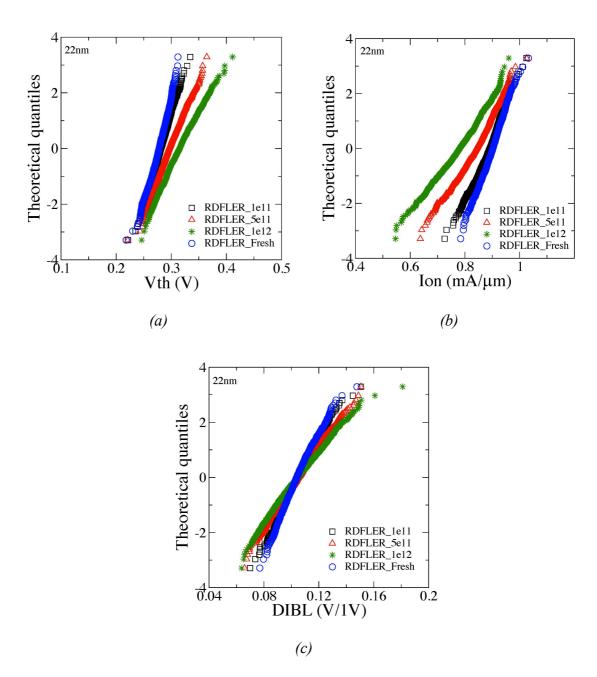

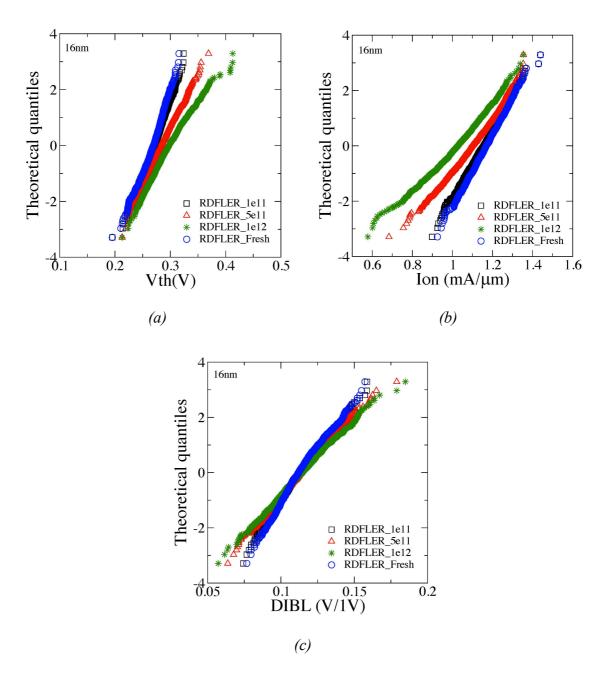

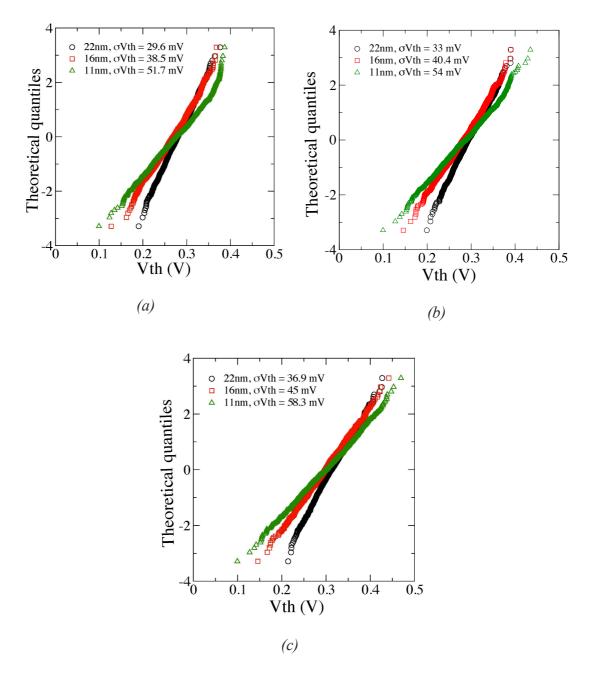

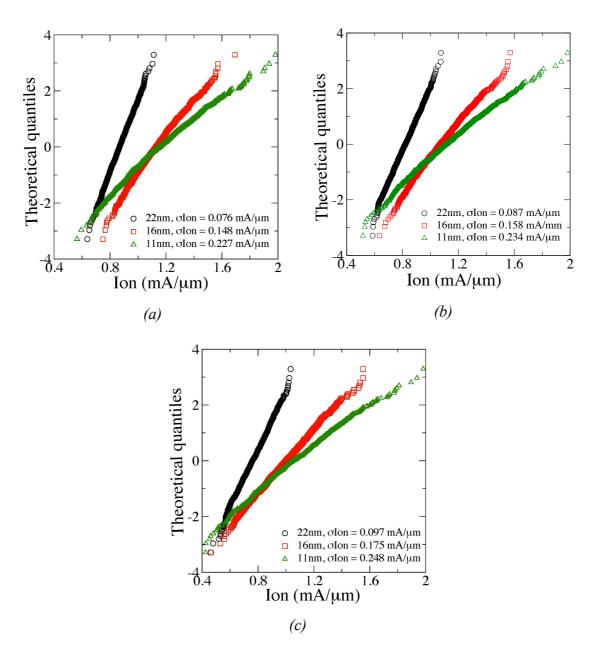

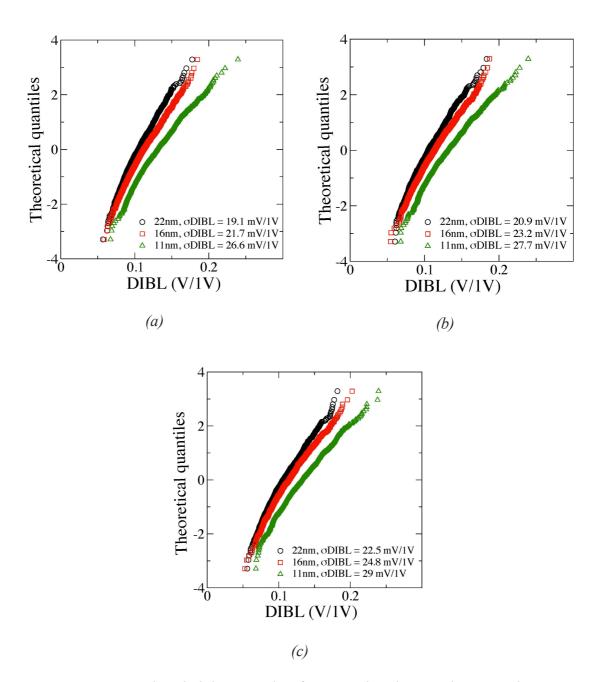

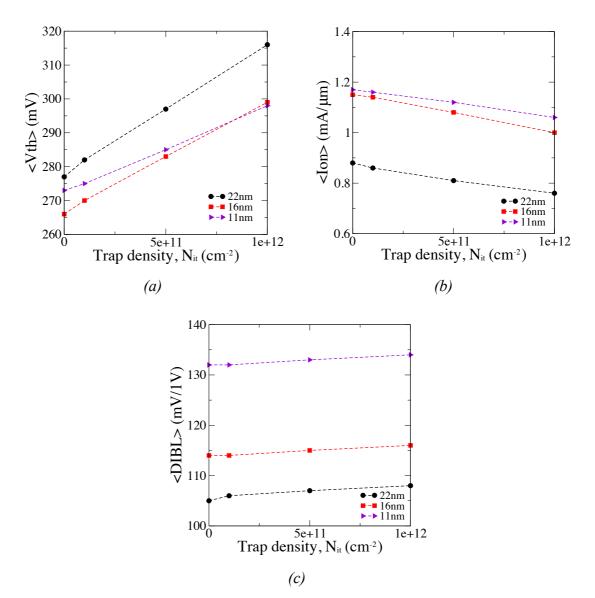

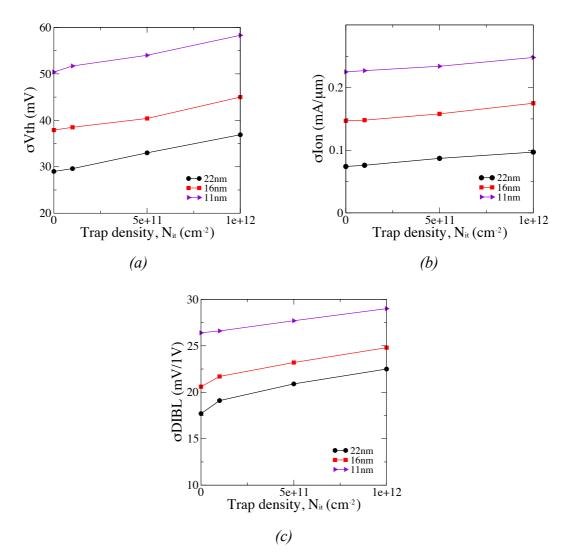

Finally, the impact of different variability sources in combination with positive bias temperature instability (PBTI) degradation on  $V_{th}$ ,  $I_{on}$  and DIBL of the scaled nMOSFETs is investigated. Our study indicates that BTI induced charge trapping is a crucial reliability problem for the FD-UTB SOI transistors operation. Its impact not only introduces a significant degradation of transistor performance, but also accelerates the statistical variability. For example, the effect of a late degradation stage (at trap density of  $1e12/cm^2$ ) in the presence of RDF, LER and MGG results in  $\sigma V_{th}$  increase to 36.9 mV, 45.0 mV and 58.3 mV for 22 nm, 16 nm and 11 nm respectively from the original 29.0 mV, 37.9 mV and 50.4 mV values in the fresh transistors.

## Acknowledgements

In the Name of ALLAH, the most Compassionate, the Most Merciful.

All praises be to ALLAH, Lord of the worlds and peace and blessings upon the beloved Prophet Muhammad SAW, the leader of all the prophets, the leader of the God fearing, the master of those whose faces will be shining on the day of Judgement, and peace upon all his descendents and companions.

During the years I was working on this thesis, I have been supported and inspired by many people, and it is a great pleasure for me to have this opportunity to put into words my sincere appreciation to them.

Firstly, I would like to express my heartfelt gratitude to *Professor Asen Asenov* who not only served as my supervisor but also has been encouraging and challenging me to be in this field. This PhD thesis could not have been written without his invaluable guidance, motivation, kindness and passion throughout the period of my study. I have been amazingly fortunate to have an advisor like him who always been there to encourage and support me in the most beneficial ways. I am also very grateful to him for his patient and deep commitment to his profession. I appreciate him greatly especially when he guided me during my steps almost faltered. I am blessed and honoured to be his student.

I am grateful to Dr. Binjie Cheng as my second supervisor for his valuable comments and ideas, encouragement, enforcing strict validation for each result and thesis reading. My big thanks also goes to Dr. Xingsheng Wang for his help and patient to solve problems when I appeared as a fresh device modeler especially regarding simulation tool. His pleasant and optimistic appearance greatly impressed me.

I am also indebted to the members of Device Modelling research group especially Stanislav, Fikru, Daniel, Gordon, Ewan, Salvatore and others who patiently guided and advised me in producing this thesis, never accepting less than my best efforts and also helped me to sort out the technical problems. I'm really thanks them all.

I like to convey my heartfelt thanks to my home institution, Universiti Teknikal Malaysia

Melaka (UTeM) and Ministry of Higher Education, Malaysia, which gave me their indispensable generous sponsoring throughout my study.

I also would like to express my love and gratitude to my 'happy family' in Scotland: Sister Asmaheram & Dr Khairul Azmi, Dr Zuraeda & Brother Rosli, Sister Zarina & Dr Nordin, Sister Ratifah & Dr Shahabuddin, Sister Haslina & Brother Zaidi, Ustazah Safinar & Ustaz Abduh, Dr Rosazra & Dr Che'Anuar, Sister Asma' & Brother Ariffin and Sister Aishah & Dr.Izani for their tears and laughs, endless supports and understanding. Not to be forgotten, thanks to all my dear friends for wonderful friendship and encouragement.

Very special grateful to my family members; my mother, Ramlah @ Ruby Daud, my father, Mohd Zain Saat; my in-laws: Jusiah Sukor and Abd Manap Arsat; and all my siblings, especially Sister Azizah & Brother Kamal. Their firm and kind-hearted personality have affected me to be steadfast and never bend to difficulty. Without their prayers, love, support and patience I could have never reached this point of my life.

Most importantly, none of this would have been possible without the love and patience of my own family. I am greatly indebted to my beloved husband Dr. Nurulfajar Abd Manap for his love and support without any complaint or regret. He has been and continues to be a constant source of inspiration and strength. He stood by me in every way and I am eternally grateful to have him as my better half. It has been a meaningful journey for both of us; a journey filled with happiness and challenges. May ALLAH grant all his wishes and give him more beautiful days ahead, in return.

To my solehah princess, Nur Najla Alia, thank you for the purest love, patience and sacrifices. May ALLAH bless you with full of happiness in here and hereafter.

In loving memory to my handsome little hero, Amir Yusuf who passed away in March 6, 2009 while I'm struggling on my intricate PhD journey. Wish you were here, see you in Jannah. Ameen.

Last but not least, to all those have significantly contributed directly or indirectly towards the completion of this thesis; I am truly grateful to all. Thank you again to Almighty ALLAH for giving me 'everything' for me to be where I am now.

" There is no power and strength except with ALLAH SWT "

## **Publications**

**A. S. M. Zain**, S. Markov, B. Cheng, X. Wang, and A. Asenov, "Comprehensive Study of the Statistical Variability in a 22nm Fully-Depleted Ultra-Thin-Body SOI MOSFET", *Solid-State Electronics*, pp. 1-5, 2013.

Y. Yunxiang, S. Markov, C. Binjie, **A. S. M. Zain**, L. Xiaoyan, and A. Asen, "Back-Gate Bias Dependence of the Statistical Variability of FDSOI MOSFETs With Thin BOX," *Electron Devices, IEEE Transactions on*, vol. 60, pp. 739-745, 2013.

S. Markov, A. S. M. Zain, B. Cheng, and A. Asenov, "Statistical variability in scaled generations of n-channel UTB-FD-SOI MOSFETs under the influence of RDF, LER, OTF and MGG," *IEEE SOI Conference (SOI)*, pp. 1-2, 2012.

S. Markov, B. Cheng, A. S. M. Zain, and A. Asenov, "Handbook of SOI Technology : CMOS Variability on SOI," O. Kononchuk and N. Bich-Yen, Eds., ed: Woodhead Publishing Limited, 2012 [*Submitted*].

Y. Yang, S. Markov, B. Cheng, A. S. M. Zain, X. Liu, and A. Asenov, "Impact of Back-Gate Bias on Statistical Variability in 22nm n-channel UTBB SOI MOSFETs under the Influence of RDF and LER," *VARI 2012*, pp. 1-4, 2012.

**A. S. M. Zain**, S. Markov, B. Cheng, X. Wang and A. Asenov, "Comprehensive Study of the Statistical Variability in a 22nm Fully-Depleted Ultra-Thin-Body SOI MOSFET", *EuroSOI 2012 Conference*, pp. 45-46, Jan. 23-25, 2012.

**A. S. Mohd Zain**, B. Cheng, X. Wang and A. Asenov, "Insights on Device Performance of SOI MOSFET with 60 nm and 15 nm BOX Thickness", *EuroSOI 2011 Conference*, pp. 107-108, Jan. 17-19, 2011.

# **List of Contents**

| Dedication                                                                | ii        |

|---------------------------------------------------------------------------|-----------|

| Abstract                                                                  | iii       |

| Acknowledgements                                                          | v         |

| Publications                                                              | vii       |

| List of Contents                                                          | viii      |

| List of Figures                                                           | xi        |

| List of Tables                                                            | xvi       |

| Nomenclatures                                                             | xvii      |

| CHAPTER 1                                                                 | 1         |

| 1.1 Motivation                                                            | 1         |

| 1.2 Aim and Objectives                                                    | 3         |

| 1.3 Thesis Organization                                                   | 4         |

| CHAPTER 2                                                                 | 7         |

| 2.1 Introduction                                                          |           |

| 2.2 Past Scaling Trends and Rules                                         |           |

| 2.2.1 Constant field scaling rule                                         |           |

| 2.2.2 Generalized field scaling rule                                      |           |

| 2.3 Limitations of MOSFET Scaling                                         | 12        |

| 2.4 Factors Impede the Scaling of Traditional Bulk MOSFET : Variabilit 16 | y Aspects |

| 2.5 New Device Architectures: SOI MOSFET vs FinFETs                       | 21        |

| 2.5.1 FD-UTB SOI                                                          | 22        |

| 2.5.2 FinFET                                                              | 23        |

| 2.6 ITRS Projection on Fully Depleted SOI for Next Generation             | 24        |

| 2.7 Summary                                                               | 27        |

| CHAP               | TEF       | 3                                                                 | 28   |

|--------------------|-----------|-------------------------------------------------------------------|------|

| 3.1                | Inti      | oduction                                                          | 28   |

| 3.2                | De        | vice Simulation Techniques                                        | 29   |

| 3.                 | 2.1       | The DD simulation approach                                        | 30   |

| 3.                 | 2.2       | Mobility models                                                   | 32   |

| 3.3                | The       | e 3D 'Atomistic' Simulator, GARAND                                | 38   |

| 3.                 | 3.1       | Random Dopant Fluctuation (RDF)                                   | 38   |

| 3.                 | 3.2       | Line Edge Roughness (LER)                                         | 40   |

| 3.                 | 3.3       | Metal Gate Granularity (MGG)                                      | 43   |

| 3.4                | Su        | nmary                                                             | 45   |

| CHAR               |           |                                                                   | 16   |

| <b>CHAP</b><br>4.1 |           | <b>R 4</b>                                                        |      |

| 4.1<br>4.2         |           | I Technology Review                                               |      |

| 4.2                |           | m FD-UTB SOI Transistor Design                                    |      |

|                    | 3.1       | Device structure design based on ITRS specifications              |      |

|                    | 3.2       | Impact of the BOX thickness                                       |      |

|                    | 3.3       | Impact of the Source/Drain doping abruptness                      |      |

| 4.                 | 3.4       | Spacer length optimization                                        |      |

| 4.                 | 3.5       | Substrate bias effects                                            | 64   |

| 4.4                | Des<br>66 | sign of 16nm and 11nm Technology Generations FD-UTB SOI Transisto | rs   |

| 4.5                | Su        | nmary                                                             | 69   |

| CUAD               |           |                                                                   | 70   |

|                    |           | R 5                                                               |      |

| 5.1                |           | roduction.                                                        |      |

| 5.2                | -         | pact of Statistical Variability in FD-UTB SOI Scaled Devices      |      |

| 5.                 | 2.1       | Random Dopant Fluctuation (RDF) : 22nm, 16nm and 11nm             | 72   |

| 5.                 | 2.2       | Line Edge Roughness (LER) : 22nm, 16nm and 11nm                   | 78   |

| 5.                 | 2.3       | Metal Gate Granularity (MGG) : 22nm, 16nm and 11nm                | 81   |

| 5.                 | 2.4       | Combined variability sources WITHOUT MGG: 22nm,16nm and 11nm      | 1.84 |

| 5.     | 2.5 Combined variability sources WITH MGG: 22nm,16nm and 11nm | 88  |

|--------|---------------------------------------------------------------|-----|

| 5.3    | Summary                                                       | 93  |

|        |                                                               |     |

| CHAP   | TER 6                                                         | 94  |

| 6.1    | Introduction                                                  | 94  |

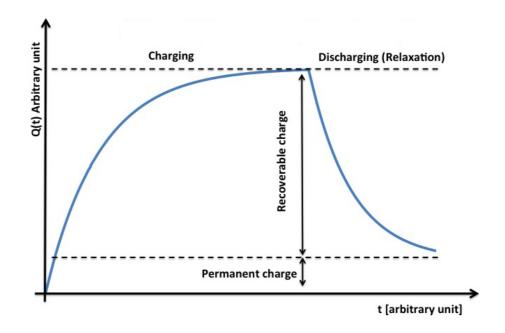

| 6.2    | Reliability Issues and Future Challenges                      | 95  |

| 6.3    | Statistical Reliability Simulations in the Absence of MGG     | 98  |

| 6.4    | Statistical Reliability Simulations in the Presence of MGG    | 114 |

| 6.5    | Summary                                                       | 129 |

| СНАР   | TER 7                                                         | 131 |

| 7.1    | Conclusions                                                   |     |

|        |                                                               |     |

| 7.2    | Outlook                                                       | 135 |

| Refere | nces                                                          | 136 |

# **List of Figures**

| Figure 1.1: Main part of thesis organization                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1: Illustration of past scaling concept of bulk-MOSFET transistor by a factor α. Redraw from [3]                                                                                                                                              |

| Figure 2.2 : Power crisis as the downsizing of transistor gate length                                                                                                                                                                                  |

| Figure 2.3 : Transition of gate dielectric material from SiO <sub>2</sub> to high-k for three different device gate length [16]                                                                                                                        |

| Figure 2.4 : Migration from Poly/SiON (Poly/Silicon Oxynitride) to metal gate/high-k (MG/HK) and the dependence of gate dielectric thickness and gate leakage on technology scaling [13]                                                               |

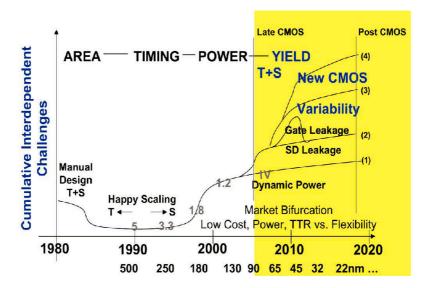

| Figure 2.5 : Major challenges as a function of time and technology nodes [28]16                                                                                                                                                                        |

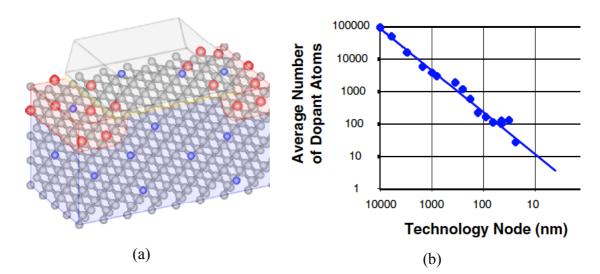

| Figure 2.6 : (a) Schematic of 4.2 nm MOSFET under the influence of RDF. Red/blue dots represent donor/acceptor dopants, while the grey dots are silicon crystalline lattice [35], (b) average number of dopant atoms versus technology generation [36] |

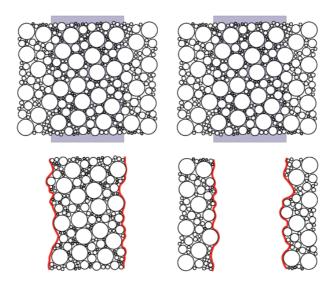

| Figure 2.7 : Typical LER in photoresist when negative/positive resists are used [35]18                                                                                                                                                                 |

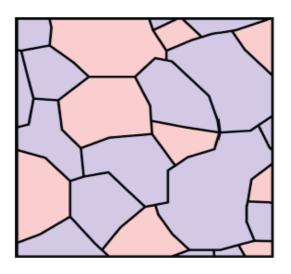

| Figure 2.8 : Metal grain pattern of 35x35 nm gate with an average grain diameter of 10 nm [40]                                                                                                                                                         |

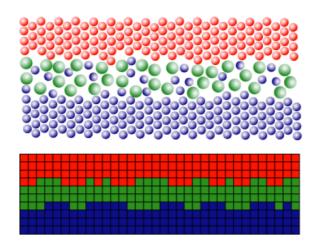

| Figure 2.9 : Illustration of OTV impact at the interface of silicon/silicon dioxide and silicon dioxide/poly-si gate [35]. The Red, green and blue colors signify poly-si gate, silicon dioxide and silicon respectively. 20                           |

| Figure 2.10 : Transition of field effect transistor (FET) transistor to proceed further scaling, (a) bulk-MOSFET, (b) ultra thin body silicon on insulator (UTB SOI) and (c) FinFET [9]                                                                |

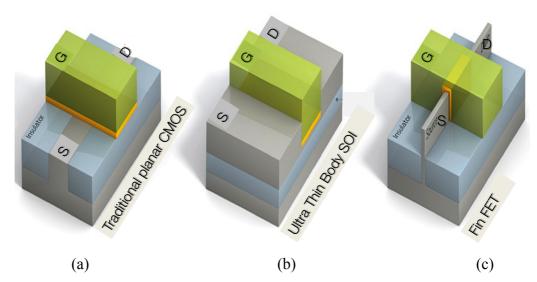

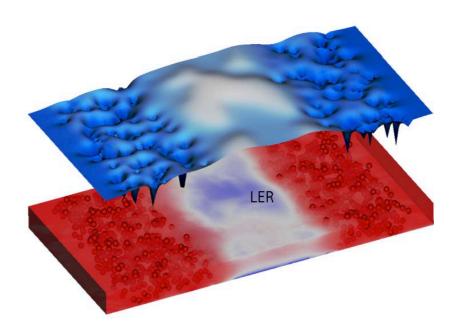

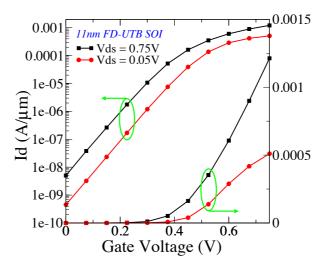

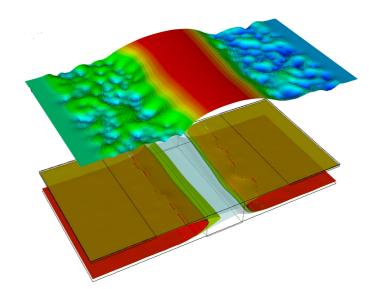

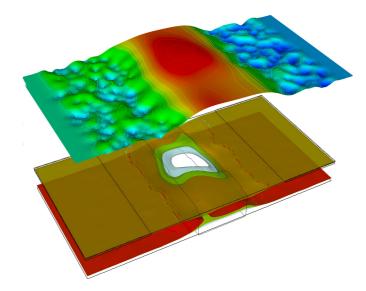

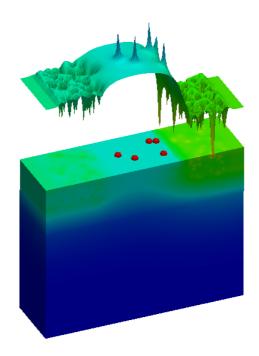

| Figure 3.1 : The electron distribution in the silicon body subjected to RDF in 22nm FD-UTB SOI nMOSFET with the surface potential shown above                                                                                                          |

| Figure 3.2 : The impact of line edge under different resist flavors (a) the effect of a negative resist removing the region that is unexposed and (b) the effect of a positive resist where the exposed region is removed away [35]                    |

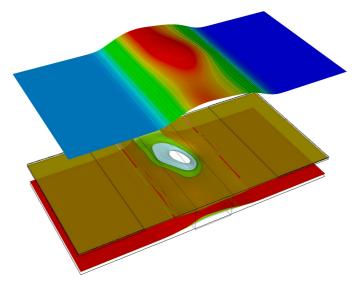

| Figure 3.3 : The electron distribution in the silicon body showing the impact of LER (2nm) in 22nm FD-UTB SOI nMOSFET with the surface potential shown above42                                                                                         |

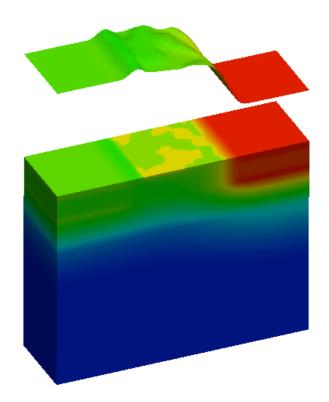

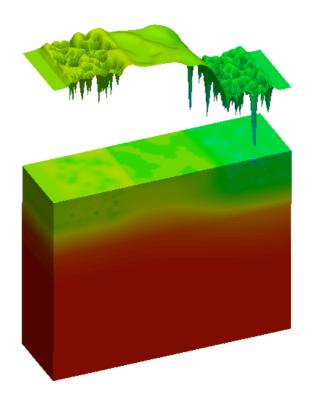

| Figure 3.4 : The electrostatic potential in a generic 22nm FD-UTB SOI nMOSFET with the surface potential shown above. The average grain diameter ( $\emptyset$ ) is 5nm                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.5 : Electrostatic potential for combined variability sources : RDF, LER and MGG for 22nm FD-UTB SOI device                                                                                |

| Figure 4.1 : Redesign of 32nm TB SOI PULLNANO, (a) physical dimensions and (b) device structure and its doping profiles                                                                            |

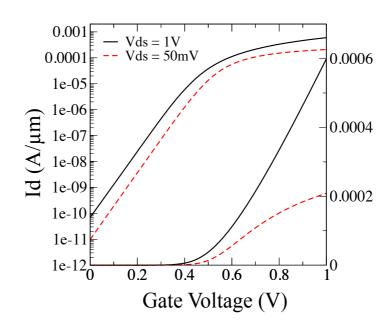

| Figure 4.2 : $I_dV_g$ for 32nm gate length TB SOI PULLNANO, biased at high and low drain voltage, in linear and logarithmic scales                                                                 |

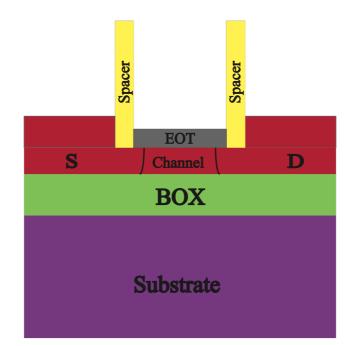

| Figure 4.3 : General structure of 22nm single gate FD-UTB SOI n-type MOSFET51                                                                                                                      |

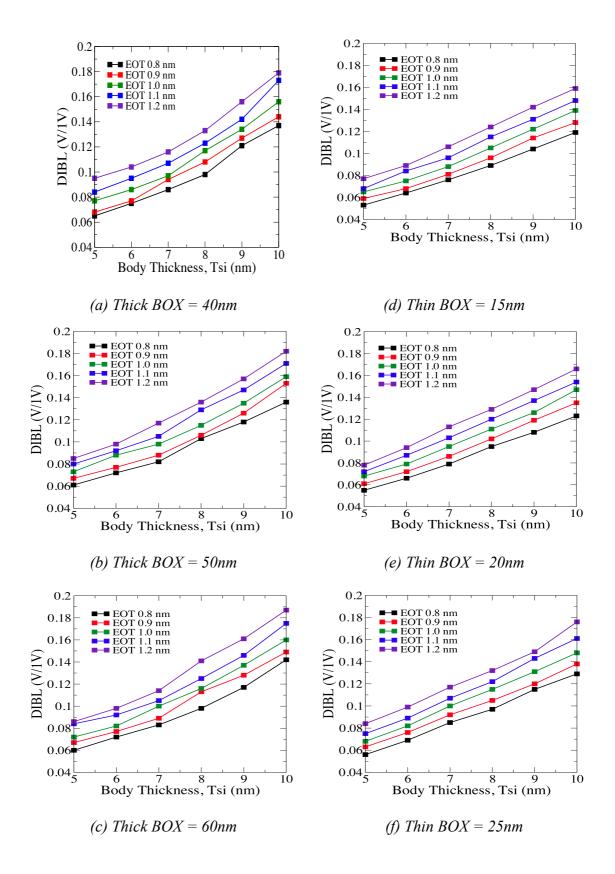

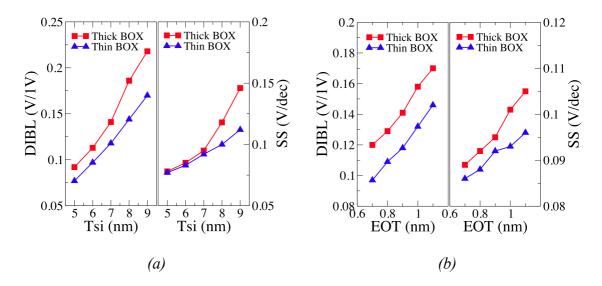

| Figure 4.4 : Impact of global variation of EOT and Tsi on DIBL for thick and thin BOX scenarios at high drain voltage ( $V_{ds}$ = 0.8V) with $N_{sub}$ = 1.0x10 <sup>16</sup> cm <sup>-3</sup> 54 |

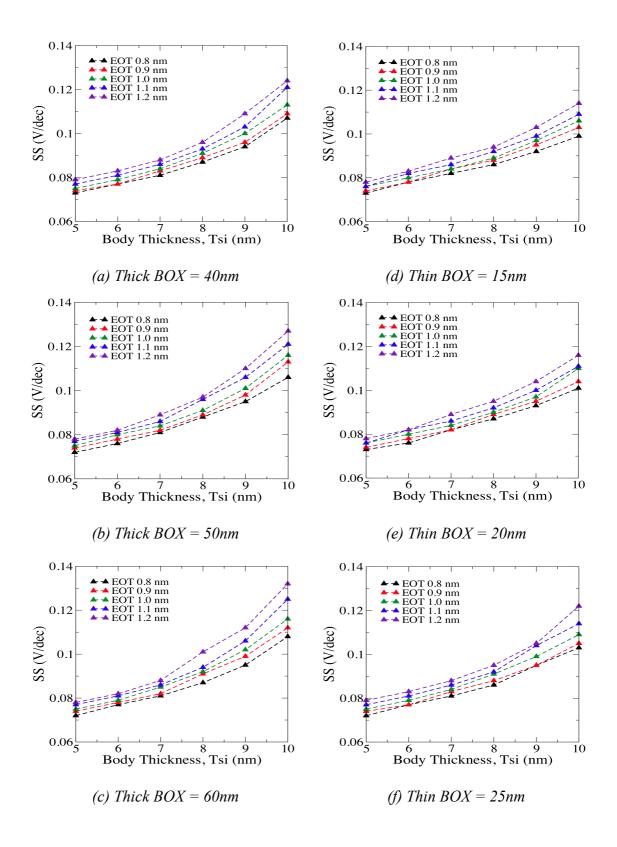

| Figure 4.5 : Impact of global variation of EOT and Tsi on SS for thick and thin BOX scenarios at high drain voltage ( $V_{ds}$ = 0.8V) with $N_{sub}$ = 1.0x10 <sup>16</sup> cm <sup>-3</sup> 55   |

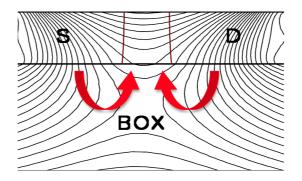

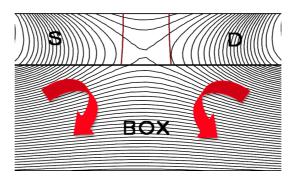

| Figure 4.6 : Electrostatic potential contours for thick and thin BOX at $V_{ds} = 0.05V$ indicating 2D coupling through the BOX                                                                    |

| Figure 4.7 : Trend of DIBL and SS against variation of (a) Tsi and (b) EOT for 60nm thick BOX and 15nm thin BOX                                                                                    |

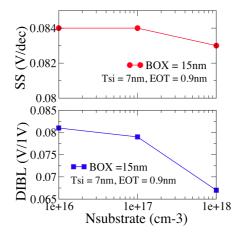

| Figure 4.8 : Impact of different substrate doping concentration on SS and DIBL for the thin BOX device of 15nm, Tsi of 7nm and EOT of 0.9nm                                                        |

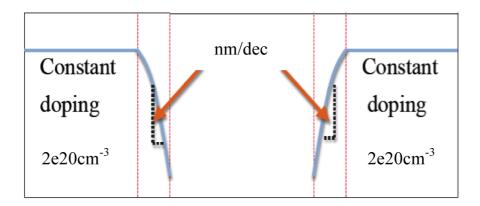

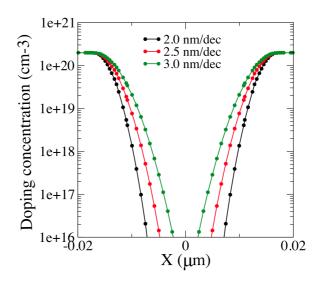

| Figure 4.9 : Doping abruptness (nm/dec) under the spacer and doping profile based on Gaussian function                                                                                             |

| Figure 4.10 : Illustration of various lateral S/D doping abruptness along the channel; 2.0, 2.5 and 3.0 nm/dec, with L <sub>spa</sub> of 6nm                                                       |

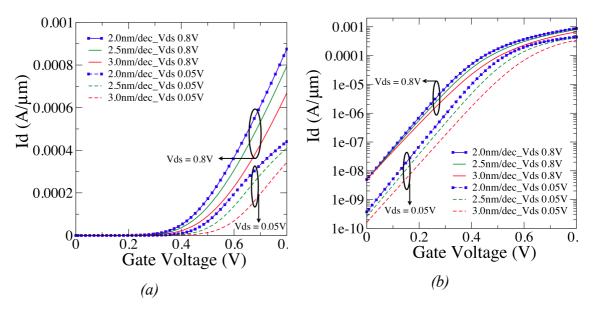

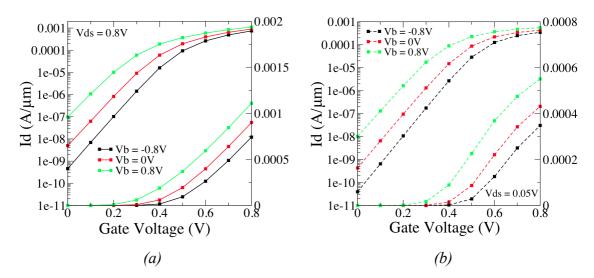

| Figure 4.11 : $I_dV_g$ for three different $\sigma$ (nm/dec), biased at high and low drain voltage;<br>(a) linear and (b) logarithmic scales                                                       |

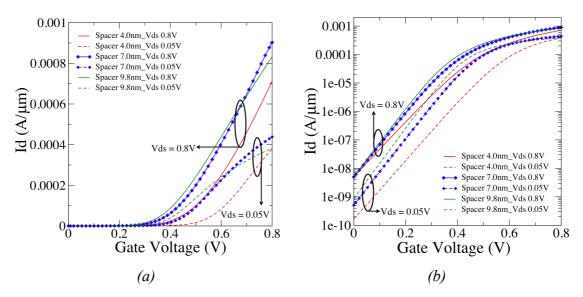

| Figure 4.12 : $I_dV_g$ for 22nm at dissimilar spacer lengths , biased at high and low drain voltage; (a) linear and (b) logarithmic scales                                                         |

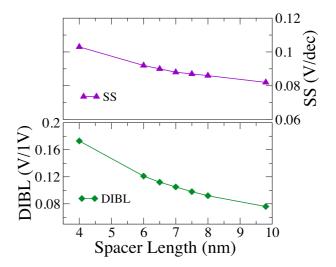

| Figure 4.13 : Impact of spacer length variation on DIBL and SS                                                                                                                                     |

| Figure 4.14 : $I_dV_g$ for different substrate bias, $V_b = -0.8V$ , 0V and 0.8V in linear and logarithmic scales, (a) saturation and (b) linear modes                                             |

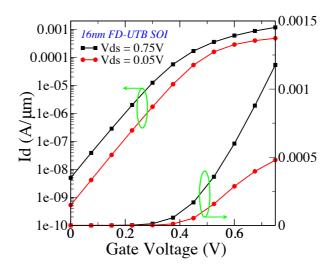

| Figure 4.15 : $I_dV_g$ characteristics in linear and logarithmic scales for 16nm FD-UTBSOI MOSFET                                                                                                  |

| Figure 4.16 : $I_dV_g$ characteristics in linear and logarithmic scales for 11nm FD-UTBSOI MOSFET                                                                                                  |

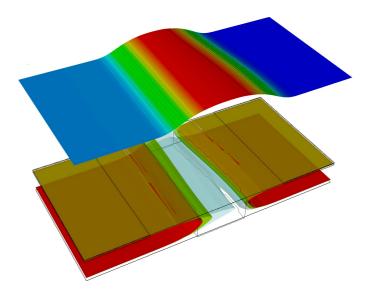

| Figure 5.1 : Electron potential landscape and electron concentration surface in the body of the device in the presence of RDF                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

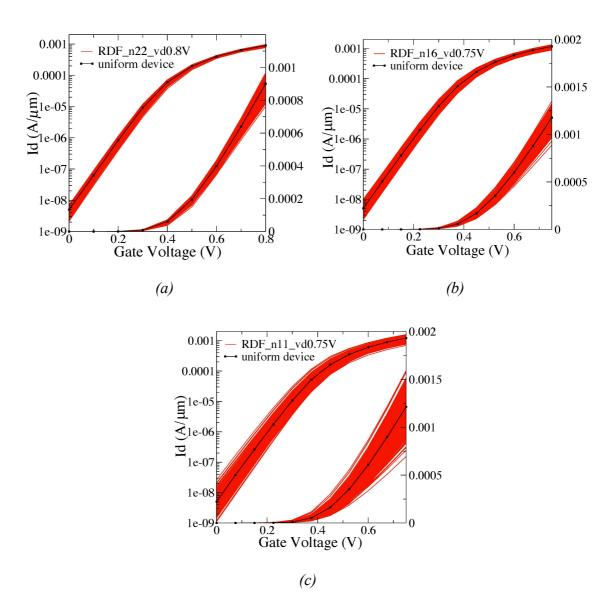

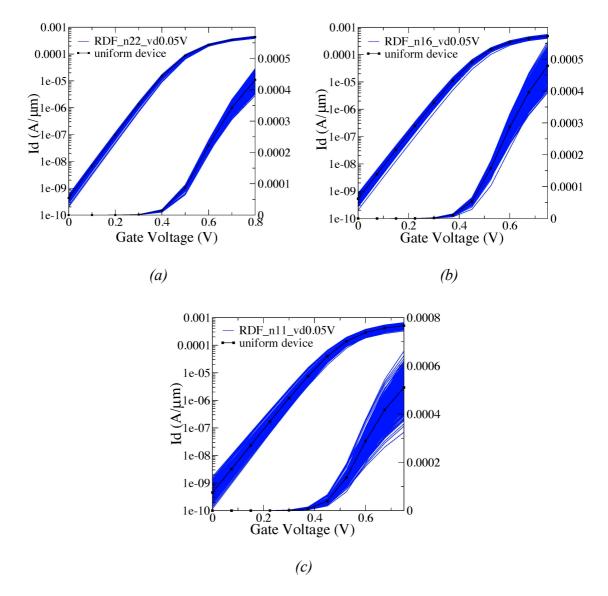

| Figure 5.2 : Saturation transfer characteristics of (a) 22nm, (b) 16nm and (c) 11nm device ensembles under influence of RDF                                                                 |

| Figure 5.3 : Linear transfer characteristics of (a) 22nm, (b) 16nm and (c) 11nm device ensembles under influence of RDF                                                                     |

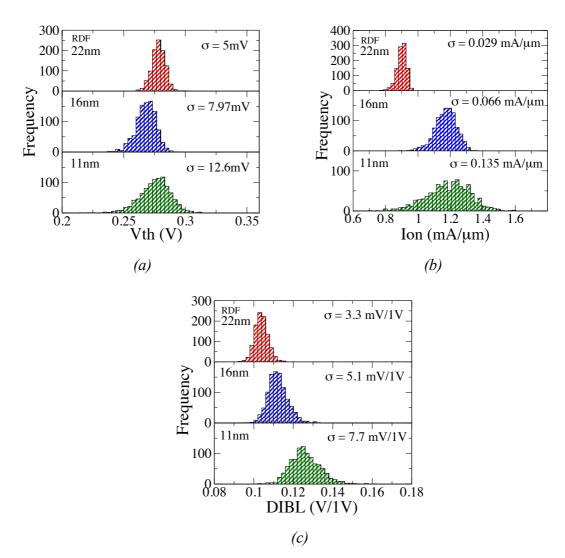

| Figure 5.4 : Histograms of the impact of RDF-induced fluctuations on (a) $V_{th}$ , (b) $I_{on}$ and (c) DIBL for 22nm, 16nm and 11nm devices77                                             |

| Figure 5.5 : Electron potential landscape and electron concentration surface in the body of the device in the existence of LER                                                              |

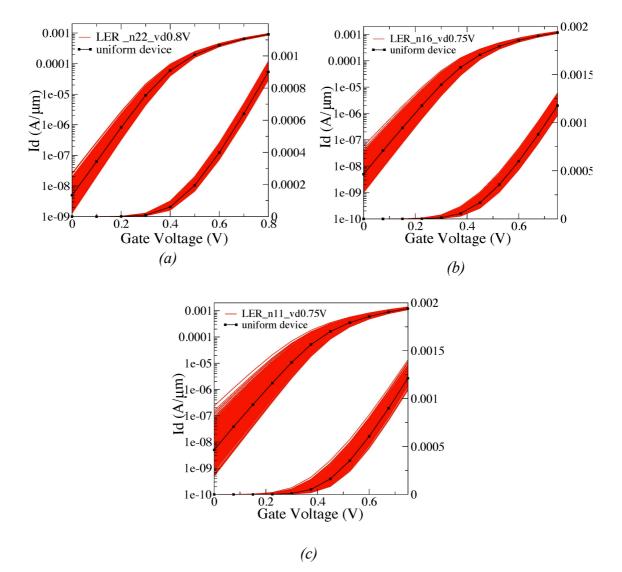

| Figure 5.6 : Saturation transfer characteristics of (a) 22nm, (b) 16nm and (c) 11nm device ensembles under influence of LER                                                                 |

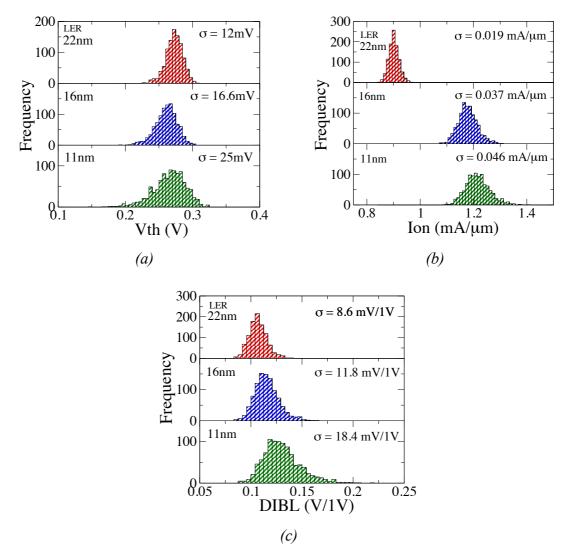

| Figure 5.7 : Histograms of the impact of LER-induced fluctuations on (a) $V_{th}$ , (b) $I_{on}$ and (c) DIBL for 22nm, 16nm and 11nm devices80                                             |

| Figure 5.8 : Electron potential landscape and electron concentration surface in the body of the device in the presence of MGG                                                               |

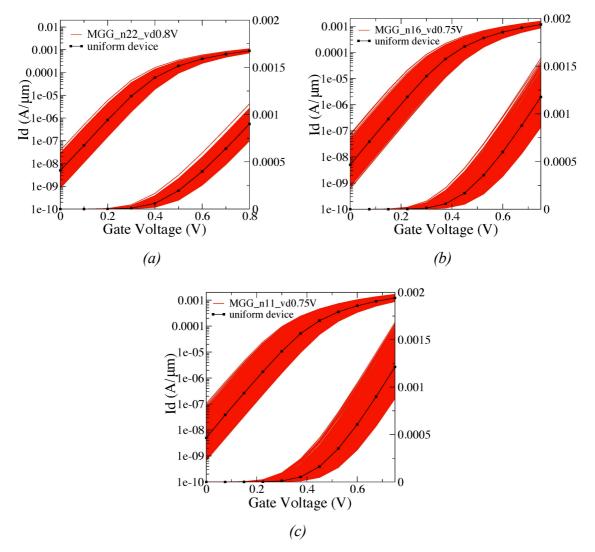

| Figure 5.9 : Saturation transfer characteristics of (a) 22nm, (b) 16nm and (c) 11nm device ensembles under influence of MGG                                                                 |

| Figure 5.10 : Histograms of the impact of MGG-induced fluctuations on (a) Vth, (b) Ion and (c) DIBL for 22nm, 16nm and 11nm devices                                                         |

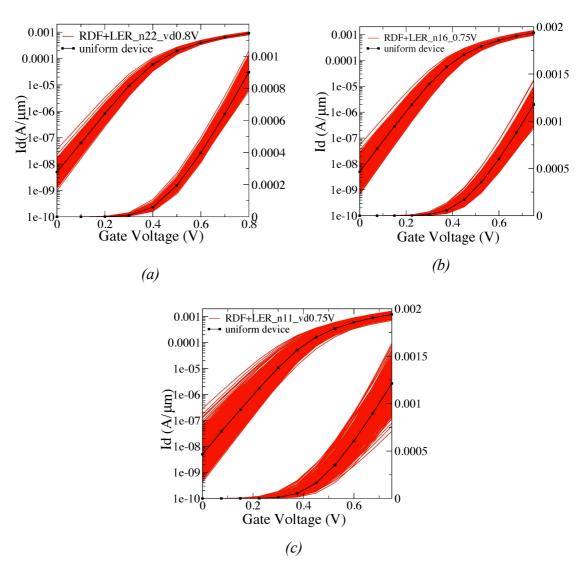

| Figure 5.11 : Saturation transfer characteristics of (a) 22nm, (b) 16nm and (c) 11nm device ensembles under influence of combined variability sources; RDF+LER                              |

| Figure 5.12 : Histograms of the impact of RDF+LER-induced fluctuations on (a) $V_{th}$ , (b) $I_{on}$ and (c) DIBL for 22nm, 16nm and 11nm devices                                          |

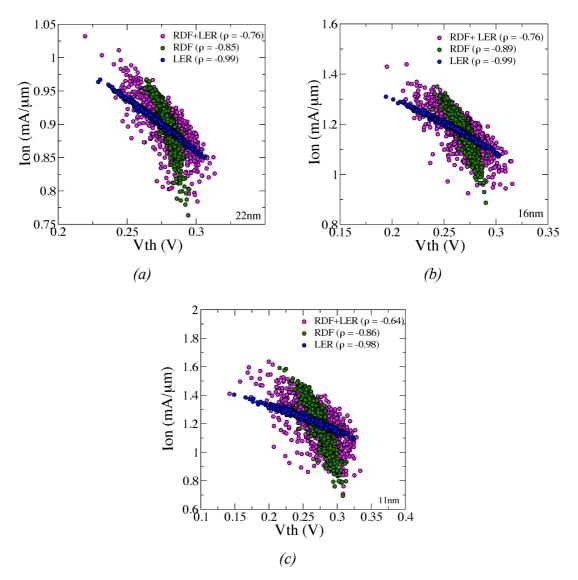

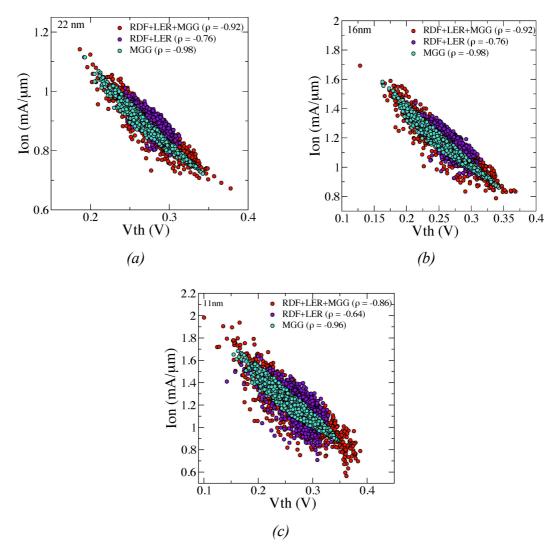

| Figure 5.13 : Scatter plots of $I_{on}$ versus $V_{th}$ at saturation for the device ensembles with RDF, LER and RDF + LER for (a) 22nm, (b) 16nm and (c) 11nm devices                      |

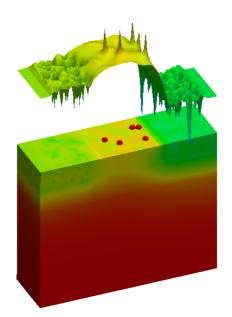

| Figure 5.14: Electron potential landscape and electron concentration surface in the body of the device in the presence of combined variability sources; RDF+LER+MGG.                        |

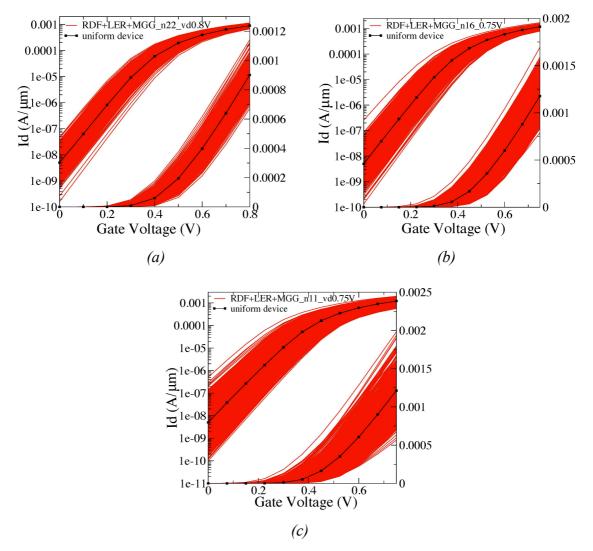

| Figure 5.15 : Saturation transfer characteristics of (a) 22nm, (b) 16nm and (c) 11nm device ensembles under influence of combined variability sources; RDF+LER+MGG 89                       |

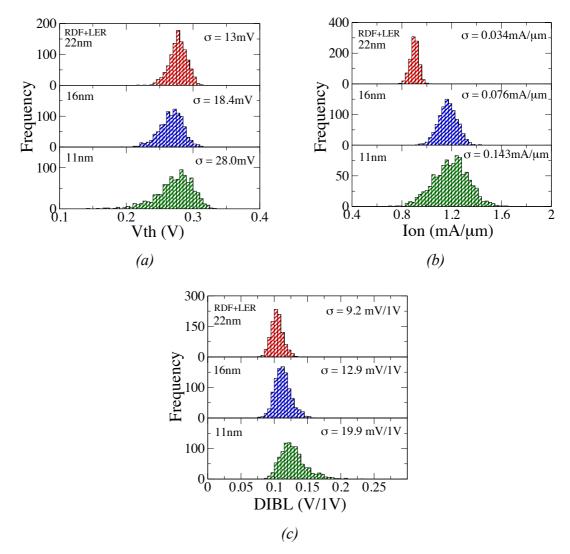

| Figure 5.16 : Histograms of the impact of RDF+LER+MGG-induced fluctuations on (a) $V_{th}$ , (b) $I_{on}$ and (c) DIBL for 22nm, 16nm and 11nm devices90                                    |

| Figure 5.17 : Scatter plots of I <sub>on</sub> versus V <sub>th</sub> at saturation for the device ensembles with MGG, RDF+LER and RDF+LER+MGG for (a) 22nm, (b) 16nm and (c) 11nm devices. |

|                                                                                                                                                                                             |

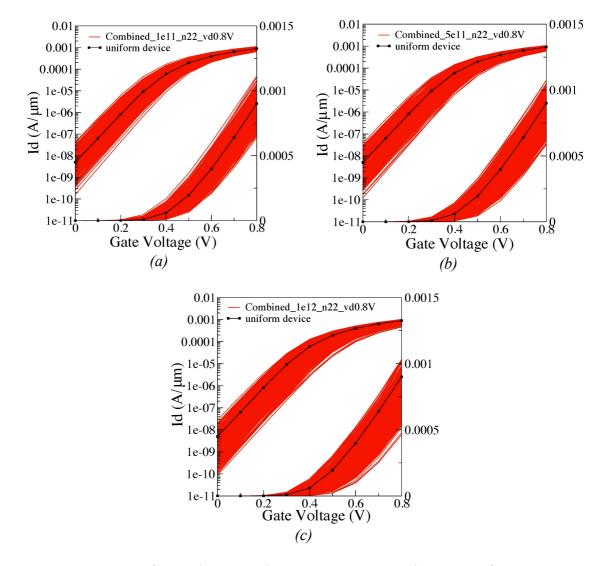

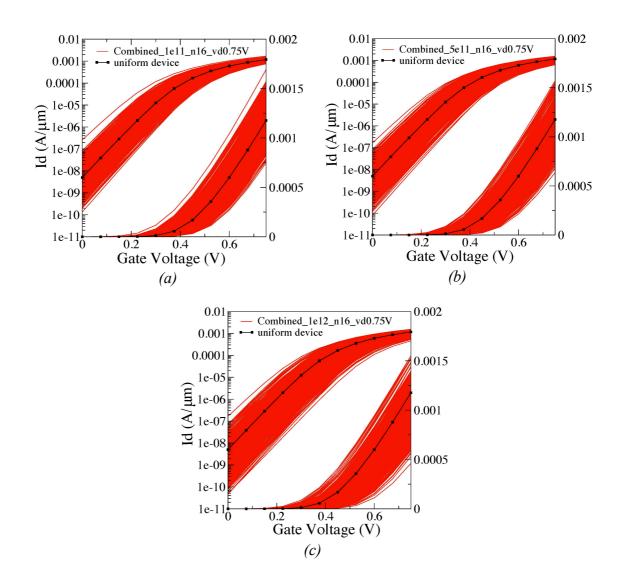

| Figure 6.15 : $I_dV_g$ of 1000 devices with RDF, LER, MGG and increase of PBTI degradations (a) 1e11cm <sup>-2</sup> (b) 5e11cm <sup>-2</sup> and (c) 1e12cm <sup>-2</sup> for 22nm gate length115                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

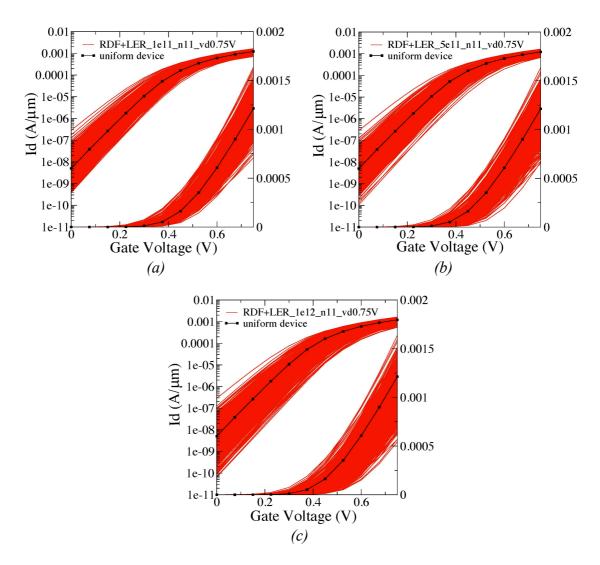

| Figure 6.16 : $I_dV_g$ of 1000 devices with RDF, LER, MGG and increase of PBTI degradations (a) $1e11cm^{-2}$ (b) $5e11cm^{-2}$ and (c) $1e12cm^{-2}$ for 16nm gate length                                                                         |

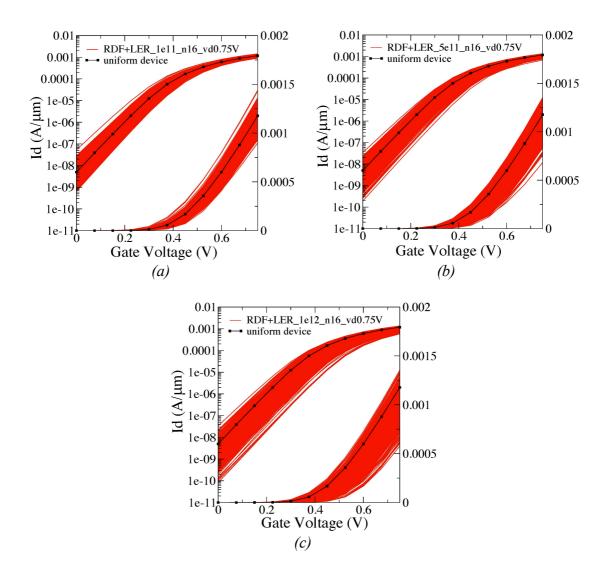

| Figure 6.17 : $I_dV_g$ of 1000 devices with RDF, LER, MGG and increase of PBTI degradations (a) 1e11cm <sup>-2</sup> (b) 5e11cm <sup>-2</sup> and (c) 1e12cm <sup>-2</sup> for 11nm gate length117                                                 |

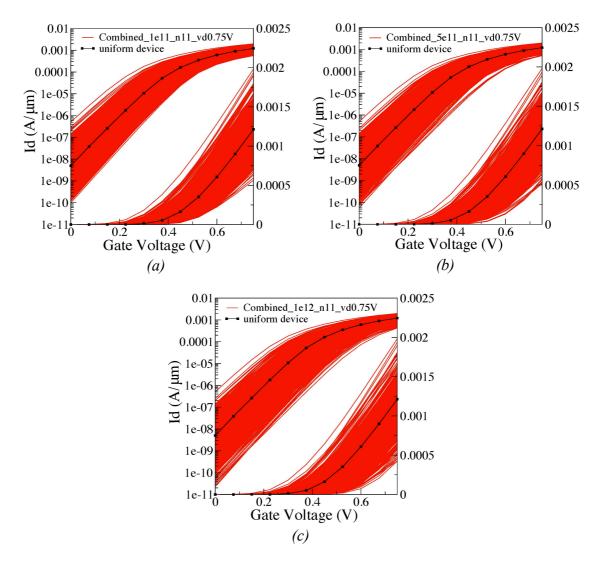

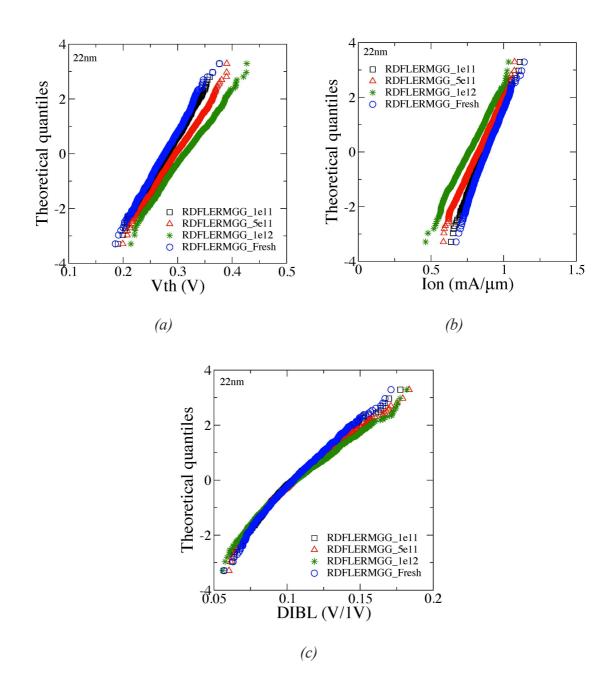

| Figure 6.18 : Normal probability QQ-plots for (a) V <sub>th</sub> , (b) I <sub>on</sub> and (c) DIBL due to combinations of RDF, LER and MGG at different level of degradations, subjected to 22nm gate length technology                          |

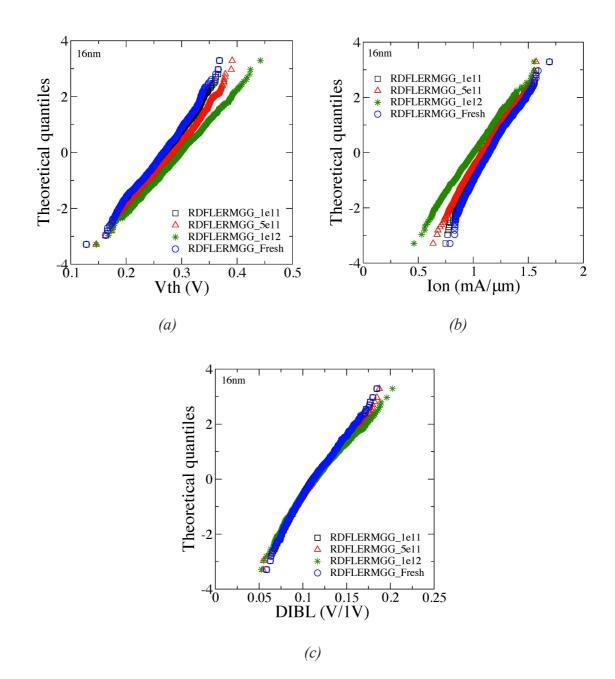

| Figure 6.19 : Normal probability QQ-plots for (a) V <sub>th</sub> , (b) I <sub>on</sub> and (c) DIBL due to combinations of RDF, LER and MGG at different level of degradations, subjected to 16nm gate length technology                          |

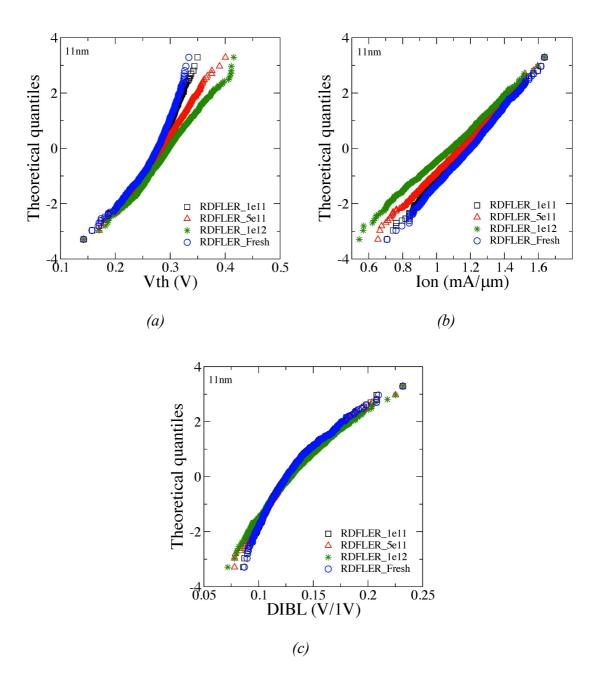

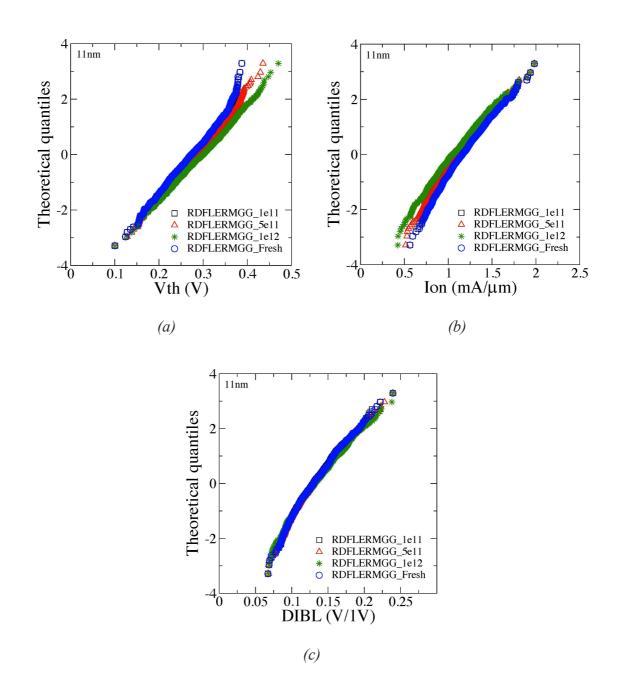

| Figure 6.20 : Normal probability QQ-plots for (a) $V_{th}$ , (b) $I_{on}$ and (c) DIBL due to combinations of RDF, LER and MGG at different level of degradations, subjected to 11nm gate length technology                                        |

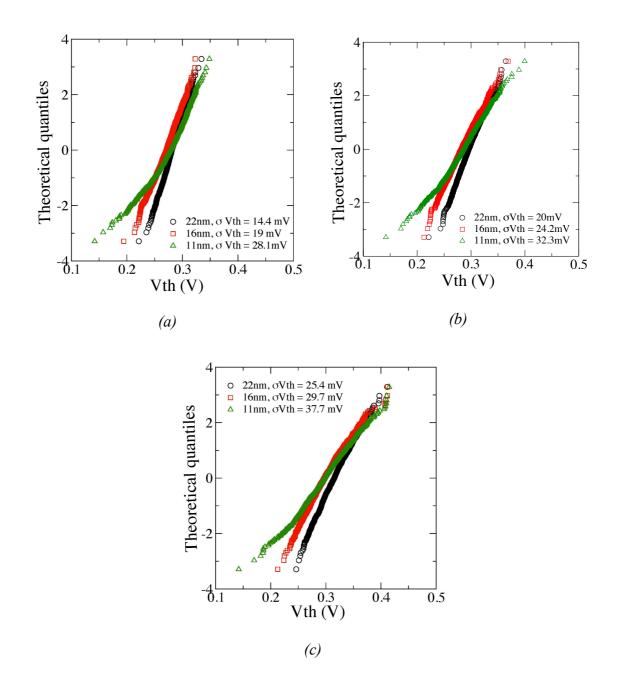

| Figure 6.21 : Normal probability QQ-plots for $V_{th}$ , distributions due to combinations of RDF, LER, MGG and $N_{it}$ at (a) 1e11 cm <sup>-2</sup> (b) 5e11 cm <sup>-2</sup> (c) 1e12 cm <sup>-2</sup> , comparing three different gate lengths |

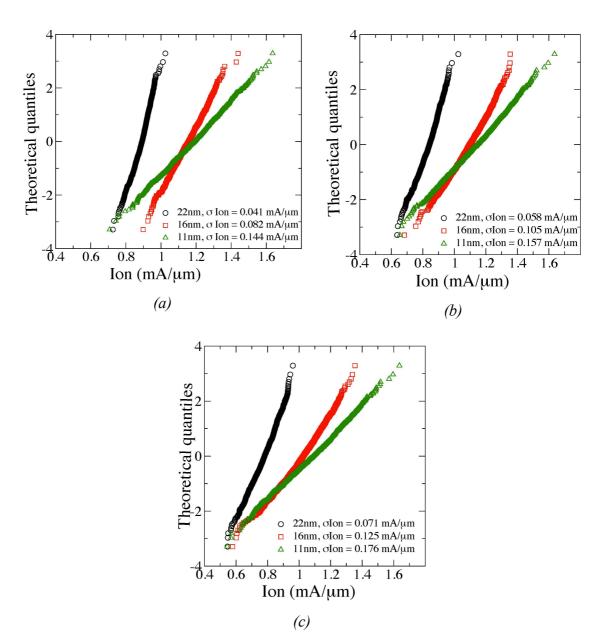

| Figure 6.22 : Normal probability QQ-plots for $I_{on}$ distributions due to combinations of RDF, LER, MGG and $N_{it}$ at (a) 1e11 cm <sup>-2</sup> (b) 5e11 cm <sup>-2</sup> (c) 1e12 cm <sup>-2</sup> , comparing three different gate lengths   |

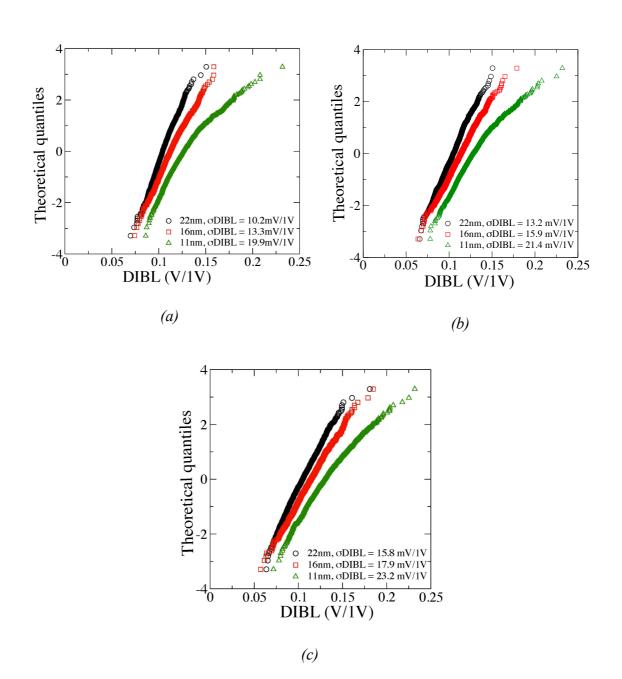

| Figure 6.23 : Normal probability QQ-plots for DIBL distributions due to combinations of RDF, LER, MGG and $N_{it}$ at (a) 1e11 cm <sup>-2</sup> (b) 5e11 cm <sup>-2</sup> (c) 1e12 cm <sup>-2</sup> , comparing three different gate lengths       |

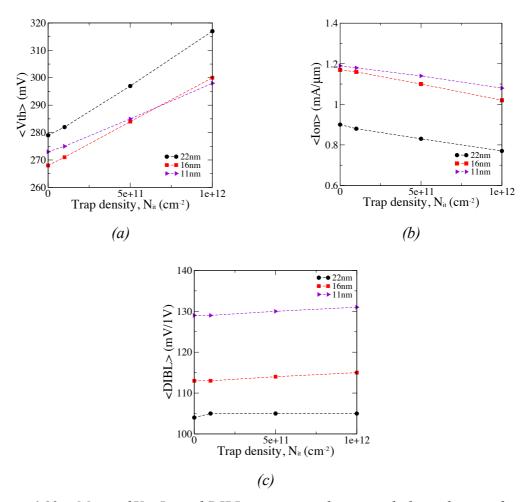

| Figure 6.24 : Mean of $V_{th}$ , $I_{on}$ and DIBL versus trap density with the inclusion of static variability sources of RDF, LER and MGG                                                                                                        |

|                                                                                                                                                                                                                                                    |

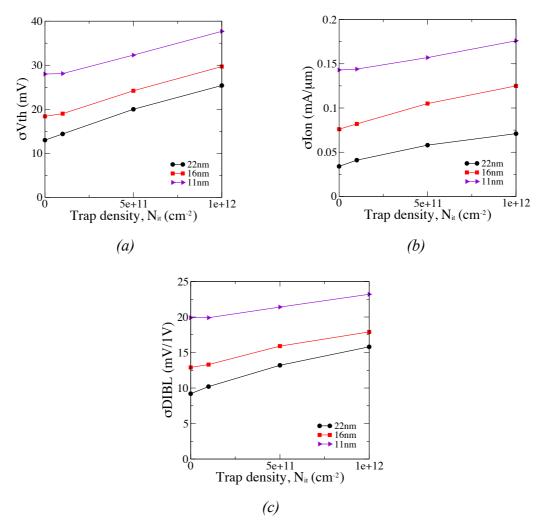

| Figure 6.25 : Standard deviation of $V_{th}$ , $I_{on}$ and DIBL versus trap density with the inclusion of static variability sources of RDF, LER and MGG127                                                                                       |

# **List of Tables**

| Table 2.1 : Device parameters and scaling rules [3].                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2 : The long term year (2010-2024) projections of some critical parameters forUTB-FD, low power operation [12]                                                      |

| Table 3.1 : Default values of phonon related constant mobility model for Silicon (Si). 33                                                                                   |

| Table 3.2 : Masetti mobility model default parameters for silicon.    33                                                                                                    |

| Table 3.3 : Default values of Arora mobility model for silicon                                                                                                              |

| Table 3.4 : Default parameter values in Lombardi mobility model for silicon                                                                                                 |

| Table 3.5 : Default parameters of Canali model for silicon (high-field mobility)37                                                                                          |

| Table 3.6 : Grain orientations with corresponding probability and work-function for         TiN.                                                                            |

| Table 4.1 : Physical device parameters considered for 22nm device.    52                                                                                                    |

| Table 4.2 : Simulation environment for Thick and Thin BOX scenarios.    53                                                                                                  |

| Table 4.3 : Device parameters for three technology generations                                                                                                              |

| Table 4.4 : Key electrical parameters of the device templates for 3 technology generations.                                                                                 |

| Table 5.1 : Variability in performance of 22nm, 16nm and 11nm FD-UTB SOI devices.                                                                                           |

| Table 6.1 : Effect of interface trapped charge density on $V_{th}$ , $I_{on}$ and DIBL distributions in the background of RDF and LER for three different gate lengths113   |

| Table 6.2 : Effect of interface trapped charge density on $V_{th}$ , $I_{on}$ and DIBL distributions in the background of RDF, LER and MGG for three different gate lengths |

## Nomenclatures

## Acronyms

| 1D         | One dimension                                       |

|------------|-----------------------------------------------------|

| 2D         | Two dimensions                                      |

| 3D         | Three dimensions                                    |

| BOX        | Buried Oxide                                        |

| BTI        | Bias Temperature Instability                        |

| CIC        | Cloud In Cell                                       |

| CMOS       | Complementary Metal Oxide Semiconductor             |

| DD         | Drift-Diffusion                                     |

| DG         | Density Gradient                                    |

| DI         | Dielectric Isolation                                |

| DIBL       | Drain Induced Barrier Lowering                      |

| EOT        | Equivalent Oxide Thickness                          |

| ESD        | Elevated Source Drain                               |

| FD-UTB SOI | Fully Depleted Ultra Thin Body Silicon on Insulator |

| FinFET     | Fin Field Effect Transistor                         |

| FIPOS      | Full Isolation Porous Oxidized Silicon              |

| GAA        | Gate All Around                                     |

| GIDL       | Gate Induced Drain Leakage                          |

| GSS    | Gold Standard Simulations                           |

|--------|-----------------------------------------------------|

| IC     | Integrated Circuit                                  |

| IPF    | Intrinsic Parameter Fluctuation                     |

| ITRS   | International Technology Roadmap for Semiconductors |

| LER    | Line Edge Roughness                                 |

| LOP    | Low Operating Power                                 |

| LTTV   | Layer Total Thickness Variation                     |

| МС     | Monte Carlo                                         |

| MGG    | Metal Gate Granularity                              |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor   |

| NBTI   | Negative Bias Temperature Instability               |

| NTRS   | National Technology Roadmap for Semiconductors      |

| OTV    | Oxide Thickness Variations                          |

| PBTI   | Positive Bias Temperature Instability               |

| RDF    | Random Dopant Fluctuation                           |

| SCE    | Short Channel Effect                                |

| S/D    | Source/Drain                                        |

| SIA    | Semiconductor Industry Association                  |

| SIMOX  | Separation Implantation of OXygen                   |

| SNM    | Static Noise Margins                                |

| SOS    | Silicon on Sapphire                                 |

| SRAM   | Static Random Access Memory                         |

| SS     | Sub-threshold Slope                                 |

| TB SOI | Thin Body Silicon on Insulator                      |

| TCAD    | Technology Computer Aided Design     |

|---------|--------------------------------------|

| UTB SOI | Ultra Thin Body Silicon on Insulator |

## Symbols

| $A_{vt}$         | Pelgrom coefficient/ mismatch coefficient |

|------------------|-------------------------------------------|

| Ion              | On-current                                |

| I <sub>off</sub> | Leakage current                           |

| k                | Boltzmann's constant                      |

| Lg               | Gate length                               |

| L <sub>spa</sub> | Spacer length                             |

| Na               | Doping concentration                      |

| N <sub>it</sub>  | Trapped charge density                    |

| N <sub>sub</sub> | Substrate doping                          |

| R <sub>SD</sub>  | Access resistance                         |

| Si               | Silicon                                   |

| $SiO_2$          | Silicon dioxide                           |

| SiON             | Silicon oxynitride                        |

| t <sub>ox</sub>  | Gate dielectric thickness                 |

| Т                | Temperature                               |

| T <sub>BOX</sub> | Buried oxide thickness                    |

| TiN              | Titanium nitride                          |

| T <sub>Si</sub>  | Silicon body thickness                    |

| $V_b$            | Substrate bias                            |

| V <sub>ds</sub>          | Drain voltage                        |

|--------------------------|--------------------------------------|

| V <sub>th</sub>          | Threshold voltage                    |

| Wf                       | Work function                        |

| $X_j$                    | Junction depth                       |

| α                        | Scaling factor                       |

| ε                        | Electric field                       |

| σ                        | Source/Drain doping abruptness       |

| μ                        | Carrier mobility                     |

| Δ                        | RMS amplitude                        |

| Λ                        | Correlation length                   |

| Ø                        | Grain diameter                       |

| $\sigma V_{th}$          | Threshold voltage standard deviation |

| $\sigma I_{on}$          | On-current standard deviation        |

| σDIBL                    | DIBL standard deviation              |

| $\langle V_{th} \rangle$ | Average threshold voltage            |

| <[>                      | Average on-current                   |

| <dibl></dibl>            | Average DIBL                         |

Supply voltage

$V_{dd}$

# **CHAPTER 1**

## Introduction

#### 1.1 Motivation

The inventions of first transistor and integrated circuit (IC) have opened up a successful path for a broad range of micro and nano electronic applications. Until now, the technology scaling captured by the famous Moore's law has been the drive force behind the enormous success of the semiconductor industry. The planar bulk CMOS technology has been the work-horse of the semiconductor industry for over 40 years. However, the conventional planar bulk MOSFET is approaching the limits of scaling. Among the critical problems of conventional bulk-MOSFET scaling are the short channel effect (SCE). Very high channel doping concentration and extremely thin gate oxide are needed to control electrostatic integrity, which results in the degradation on channel mobility and gate leakage performance. In the same time, further transistor scaling dramatically increases the statistical variability resulting from the discreteness of charge and granularity nature of matter. The dominant source of statistical variability

CHAPTER 1 : Introduction

are the random discrete dopants from heavily doped channel region, which unavoidably introduce huge variation in the bulk transistor electrical characteristics.

The high statistical variability introduces significant complications in the design of circuit and system, limiting the overall yield and performance in nanoscale CMOS applications. Since the planar bulk-MOSFET scaling may not deliver the expected benefits beyond the 28nm CMOS, new device architectures are needed in order to enable the benefits of scaling for future generations. Significant efforts have been invested in inventing and developing new device structures to overcome the limitations of planar bulk technology scaling. It is expected by the International Technology Roadmap Semiconductor (ITRS) that bulk-MOSFET will be succeeded by Ultra Thin Body Silicon on Insulator (UTB SOI) transistors. This is due to the fact that, the UTBSOI architectures can tolerate very low channel doping concentration due to much improved electrostatic integrity, and as a result, the variability that originates from random dopants (RDF) could be dramatically reduced. In addition, simultaneously the buried oxide in the SOI substrate can reduce the junction capacitance, which results in faster switching and signal propagation. However, there are other variability sources that are becoming important in UTB SOI devices including the line edge roughness (LER) and the metal gate granularity (MGG). Therefore it is very urgent to investigate the impact of different variability sources on the characteristics of properly scaled UTB SOI transistors. Throughout this study, fully depleted ultra thin body silicon on insulator (FD-UTB SOI) transistors are designed on the impact of the statistical variability thoroughly investigated.

2

### 1.2 Aim and Objectives

The aim of this research is to study the realistic scaling of advanced fully depleted ultra thin body silicon on insulator (FD-UTB SOI) MOSFETs and their statistical variability and reliability. This aim can be accomplished by the following objectives:

- To design realistic highly scaled FD-UTB SOI transistors corresponding to advanced technology generations.

- Design study of 22 nm FD-UTB SOI MOSFET

- device structure design based on ITRS specification.

- buried oxide (BOX) design, thick or thin BOX?

- source/drain doping abruptness design : 2.0, 2.5 and 3.0 nm/dec.

- spacer length design : simulation study of spacer length selection, trade-off/compromise between I<sub>on</sub>, I<sub>off</sub>, DIBL and SS for low power devices.

- investigate the impact of substrate bias effects on device behaviour.

- Scaling of single gate FD-UTB SOI MOSFET down to 16 nm and 11 nm gate lengths, follow the trends from design template of 22 nm technology generation.

- 2. To perform physical simulation with different sources of statistical variability such as RDF, LER, MGG; investigate the impact of statistical variability on threshold voltage ( $V_{th}$ ), on-current ( $I_{on}$ ) and drain induced barrier lowering (DIBL). The impact is analysed both individually and in combined sources.

- RDF

- LER 2nm

- MGG average grain size is 5 nm

- 3. To carry out statistical reliability simulation on the designed devices. This includes the impact of trapped charge as a result of positive bias temperature instability (PBTI) of n-type FD-UTB SOI MOSFET.

- Simulation with combined variability sources at different degradation levels '*without*' MGG. The trapped charge density are 1e 11 cm<sup>-2</sup>, 5e 11 cm<sup>-2</sup> and 1e 12 cm<sup>-2</sup>.

- Simulation with combined variability sources at different degradation levels '*with*' MGG. The same trapped charge density are employed, 1e 11 cm<sup>-2</sup>, 5e 11 cm<sup>-2</sup> and 1e 12 cm<sup>-2</sup>.

#### **1.3 Thesis Organization**

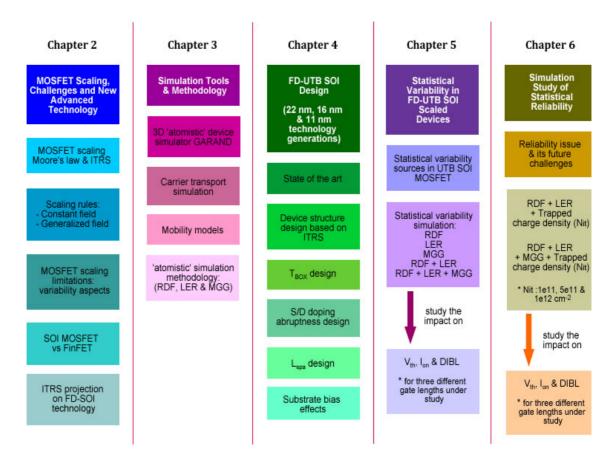

This PhD thesis consists of seven chapters, and is organized as follows:

- *Chapter 1* describes the motivation, the aim and objectives of this PhD study, as well as thesis organization.

- *Chapter 2* begins with the scaling of conventional bulk-MOSFET, Moore's law and the ITRS. It describes the scaling concept of bulk-MOSFET such as constant field scaling and generalized field scaling rules. Several scaling challenges in terms of variability are also discussed in detail. The discussion expands to new device architectures that can replace the conventional bulk transistor. Finally, it reviews the ITRS projection in respect of FD-UTB SOI for next generations to look at possible future direction of this technology.

- Chapter 3 focuses mainly on the simulation tools and methods used in this research. This includes the description of the 3D 'atomistic' device simulator GARAND, carrier transport, mobility models and finally the 'atomistic' simulation techniques.

- *Chapter 4* presents the scaling study of single gate FD-UTB SOI n-type MOSFET. It starts with the vigilant design exercise of 32nm thin body SOI MOSFET in the FP7 project PULLNANO. This starting device is then scaled down to 22nm gate length. Certain device parameters such as buried oxide thickness, source/drain doping abruptness and spacer length are optimized to achieve the performance according to the ITRS goals. Later, the scaling proceeds further to 16nm and 11nm physical gate lengths by following the same design procedures as for the 22nm template device.

- *Chapter 5* presents the predictive simulation study of statistical variability in the scaled FD-UTB SOI MOSFETs. The impact of the principle variability sources such as RDF, LER and MGG on  $V_{th}$ ,  $I_{on}$  and DIBL for three technology generations is investigated. All variability sources are treated individually and in combination.

- Chapter 6 presents the simulation study of statistical reliability in scaled FD-UTB SOI devices for 22 nm, 16 nm and 11 nm technology generations. The PBTI variability associated with trapped charge is simulated in conjunction with other variability sources (RDF,LER and MGG). The impact of combined variability sources at different trapped charge levels on V<sub>th</sub>, I<sub>on</sub> and DIBL is analysed. Under this study, two scenarios are considered; combined variability sources at different degradations 'without' and 'with' MGG.

- *Chapter* 7 draws the conclusion of this research and outlines some directions for future research.

Figure 1.1 illustrates the main part of thesis contents, it covers from chapter 2 up to chapter 6. Chapter 1 and 7 comprise of introduction and conclusion respectively, which is not describe in this figure.

Figure 1.1: Main part of thesis organization

# **CHAPTER 2**

# MOSFET Scaling, Challenges and New Advanced Technology

#### 2.1 Introduction

Since the beginning of the integrated circuit (IC) technology in 1959, the minimum feature gate length has been continuously reduced and the expectation is that the scaling of feature length will be continued in the foreseeable future. The reduction of device dimensions can increase the chip's density, lower the manufacturing cost, speed up the performance and lower the power consumption per functionality. As the metal oxide semiconductor field effect transistor (MOSFET) dimensions are reduced, the transistors need to be designed properly in order to reduce short channel effect (SCE) and to improve performance. Researchers in the semiconductor sector and academia race to propose new device architectures assisted by ITRS (International Technology Roadmap for Semiconductors) guidance in order to improve MOSFET scalability and performance and to allow the Moore's predictions to become a reality.

Moore's law describes a long-term trend in the history of the semiconductor industry in which the number of transistors that can be placed on an integrated circuit are increased exponentially doubling every year [1], resulting in more compact integration, upgraded performance and decreased cost per transistor. The law is named after Intel co-founder Gordon E. Moore, who introduced the concept in 1965. The Moore's law survived more than 40 years and has become the central driving force of semiconductor industry growth for a long period of time. This law has a significant impact on the electronics industry as a whole and continuously improves user applications in terms of increasing performance and functionality, as well as decreasing cost of the electronic devices.

In order to sustain the semiconductor industry growth, in 1992, the Semiconductor Industry Association (SIA) produced a document called the National Technology Roadmap for Semiconductors (NTRS) to provide 15 years outlook of semiconductor industry trends that provides guidelines in terms of equipment, material and provided clear target for research and technology development. After 7 years, in 1999, the first International Technology Roadmap for Semiconductors (ITRS) was born after a comprehensive revision of NTRS 1997, including a set of latest technology requirements, potential transitions and timing for semiconductor industry [2]. The purpose of the ITRS is to ensure advancements in the performance of integrated circuits and to remove any barriers to the continuation of Moore's Law journey. The ITRS efforts and assessment is a joint venture of global industry manufacturers and suppliers, government organizations, consortia and universities. They work together to ensure that the Moore's law remains alive. Every year, the ITRS identifies the technological challenges and needs facing the semiconductor industry over the next 15 - 16 years. The latest edition (ITRS 2011)<sup>cs</sup> shows the targets and requirements as a challenge to the CMOS technology in maintaining the Moore's law. In fact, the Moore's law and the ITRS strongly complement each other.

<sup>&</sup>lt;sup>cs</sup> The ITRS 2011 has been published during the 'end' of this study

#### 2.2 Past Scaling Trends and Rules

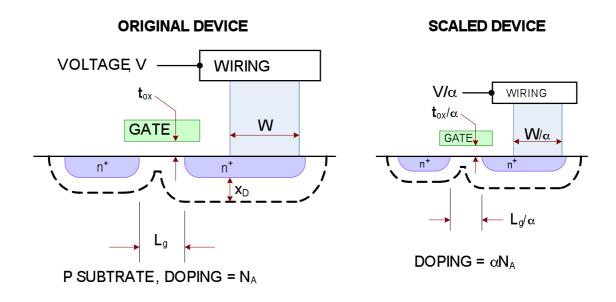

The integrated circuits miniaturization is referred to as scaling down of the transistor size, aiming to achieve high speed, high density and multi functionality. The best possible scenario to the device scaling is to reduce all device dimensions and supply voltage while maintaining constant internal electric field. This requirement is very important to avoid SCE. Device scaling not only involves geometry parameter reduction, but also significantly influences the device electrical characteristics. Therefore appropriate scaling rules must be employed in order to mitigate SCE that degrade the transistor performance. Figure 2.1 illustrates the scaling concept of MOSFET transistor. They are two basic sets of scaling rules; the constant field scaling rule and the generalised scaling rule. Each of them will be discussed in the next subsection.

*Figure 2.1: Illustration of past scaling concept of bulk-MOSFET transistor by a factor a. Redraw from [3].*

#### 2.2.1 Constant field scaling rule

The simple principles of scaling of a MOS transistor formulated by R.H. Dennard [4, 5] and aiming to enhance the performance of MOSFET, stipulate that the supply voltage and the transistor size must be reduced linearly. In the same time the doping concentration needs to be increased to allow the electric field to remain constant. This method should preserve the field in the transistor unchanged. The design parameters of the device will be scaled by the same scaling factor,  $\alpha$ . The scaled down device will have a reduced supply voltage ( $V_{dd}/\alpha$ ), gate length or horizontal dimension ( $L_g/\alpha$ ), vertical dimensions (oxide thickness,  $t_{ox}/\alpha$  and junction depth,  $X_j/\alpha$ ) and an increased doping concentration ( $\alpha N_a$ ). Since the dimensions and supply voltage are scaled by the same ratio, the intensity of the electric field remain unchanged and assures that the reliability of new scaled device is not worse than the original device.

#### 2.2.2 Generalized field scaling rule

Due to the non-scaling effect of sub-threshold slope, the supply voltage can hardly be scaled in proportion to the channel length, and as a result, the electric field in the transistor has been increasing during the scaling down of the transistors over the years. In order to allow both vertical and lateral electric fields to change with the same multiplication factor so that the shape of electric pattern is preserved, a generalized scaling rule was proposed by Baccarani *et* al. [6] in 1984. In the generalized scaling rule, the physical dimensions of the transistor are still reduced by a factor  $\alpha$  but the supply voltage and the doping concentration are scaled by  $\varepsilon/\alpha$  and  $\varepsilon\alpha$  respectively. The critical issue arises in the generalized scaling approach is the increase of the power density (Power/Area) by a factor of  $\varepsilon^2$ . This leads to challenges related to packaging and cooling in order to cope with the increasing power dissipation by the transistors on a chip. The list of physical parameters and scaling rules are presented in Table 2.1.

| Physical parameters                 | Constant<br>field scaling<br>rule | Generalized<br>field scaling<br>rule | Generalized<br>selective scaling<br>rule |

|-------------------------------------|-----------------------------------|--------------------------------------|------------------------------------------|

| Channel length, Insulator thickness | 1/α                               | 1/α                                  | $1/\alpha_d$                             |

| Wiring width, channel width         | 1/α                               | 1/α                                  | $1/\alpha_w$                             |

| Electric field in device            | 1                                 | ε                                    | ε                                        |

| Voltage                             | 1/α                               | ε/α                                  | $\epsilon/\alpha_d$                      |

| On-current per device               | 1/α                               | ε/α                                  | $\epsilon/\alpha_w$                      |

| Doping                              | α                                 | εα                                   | εα <sub>d</sub>                          |

| Area                                | $1/\alpha^2$                      | $1/\alpha^2$                         | $1/\alpha_{\rm w}^{2}$                   |

| Capacity                            | 1/α                               | 1/α                                  | $1/\alpha_{w}$                           |

| Gate delay                          | 1/α                               | 1/α                                  | $1/\alpha_d$                             |

| Power dissipation                   | $1/\alpha^2$                      | $\epsilon^2/\alpha^2$                | $\epsilon^2/\alpha_w \alpha_d$           |

| Power density (Power/Area)          | 1                                 | ε <sup>2</sup>                       | $\epsilon^2 \alpha_w / \alpha_d$         |

Table 2.1 : Device parameters and scaling rules [3].

\*  $\alpha$  is the dimensional scaling parameter,  $\varepsilon$  is the electric field scaling parameter, and  $\alpha_d \& \alpha_w$  are separate dimensional scaling parameters for the selective issue. The  $\alpha_d$  is applied to the device vertical dimensions and gate length, meanwhile the  $\alpha_w$  applies to the device width and the wiring.

#### 2.3 Limitations of MOSFET Scaling

The key driver of the enormous success of complementary metal oxide semiconductor (CMOS) technology is due to the scalability of the MOSFET transistor. However, when the CMOS technology entered deep submicron regime, the era of 'happy scaling' ended due to physical and technological limitations [7, 8]. The conventional scaling method to shrink horizontal (gate length) and vertical (gate dielectric thickness) device parameters as well as increase channel doping concentration are no longer practical and achievable. In addition, basic physical parameter such as kT and the related sub-threshold slope cannot be scaled. Scaling associated power crisis is becoming a major challenge for sustainability of the Moore's law. According to Figure 2.2 [9], the transistor leakage power that is approaching the active power required for switching the transistor state and carrying out digital computations, which is highly undesirable. This is eventually retarding already the transistors scaling pace, necessitating a solution to offer a second life to Moore's law. Therefore, new technology boosters including the channel and gate stack materials and new device architecture needed to achieve the performance requirements of the future CMOS technology generations, in association with device dimensions scaling have been adopted or are actively pursued in research [10].

Before we focus on the new possible alternative devices, it is imperative to identify the main obstacles affecting MOSFET scaling. The most critical issue that becomes a major focus of the MOSFET scaling is the short channel effect (SCE) due to the charge sharing in the channel of the short channel devices. When the gate length shrinks, there is a competition between the gate and source/drain regions over the control of the channel depletion region and the inversion layer charge due to the fact that the electrostatic control of source/drain regions has increased. An early description of the SCE and the charge sharing model can be found in [11].

*Figure 2.2 : Power crisis as the downsizing of transistor gate length.*

- *a)* The leakage power during off state quick approaching the active power for switching the transistor to the on state.

- *b)* The leakage problem slow down the transistor scaling pace, thus alternative architectures are required.

The SCE leads to device degradation and reliability concern such as;

- Threshold voltage  $(V_{th})$  roll-off the dependence of  $V_{th}$  upon gate length,  $L_g$ .

- Increase of leakage current (I<sub>off</sub>) and degradation of sub-threshold slope (SS) due to the loss control of the gate bias on the drain current.

- Drain induced barrier lowering (DIBL) due to the modulation of source/channel potential barrier by the drain voltage, where the V<sub>th</sub> decreased with the increasing drain voltage.

In order to retain the strong gate control over the channel, further technological improvements are very important to ensure continuing benefits from device miniaturization. In MOSFET transistor, gate dielectric thickness  $(t_{ox})$  is the most critical parameter and has been aggressively scaled until recently. The thin gate oxide can preserve good switching characteristics and can provide higher drive current at reduced

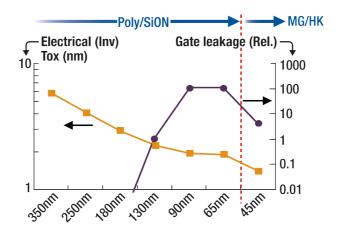

supply voltage, thus preventing the negative impact of the SCE. However, the aggressive scaling of the gate oxide has now reached fundamental physical limitation  $(1 \text{nm} \approx 4 \text{ atomic layer})$ , due to the direct quantum mechanical gate tunneling between the gate electrode and channel. The parasitic leakage current due to gate tunneling can significantly contribute to the total leakage current and standby power dissipation [3, 12]. Therefore, the use of high-dielectric constant (high-k) gate dielectric in combination with metal gate electrode has been introduced as a promising option to boost the performance and sustain the scaling from 45 nm to 32 nm technology generation.

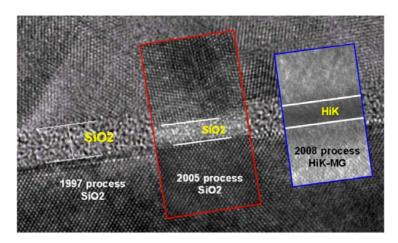

Figure 2.3 shows the gate dielectric transition from silicon dioxide (SiO<sub>2</sub>) to high-k stack for different technology generations. The introduction of a high-k/metal gate stack at 45nm technology node [13] has resulted in a significant improvement in performance, reduction of leakage and variability [14, 15]. Figure 2.4 illustrates the migration from Poly/SiON to metal gate/high-k gate stack and the dependence of gate dielectric thickness and gate leakage on technology scaling.

Figure 2.3 : Transition of gate dielectric material from  $SiO_2$  to high-k for three different device gate length [16].

Figure 2.4 : Migration from Poly/SiON (Poly/Silicon Oxynitride) to metal gate/high-k (MG/HK) and the dependence of gate dielectric thickness and gate leakage on technology scaling [13].

Another issue related to MOSFET scaling is the very high channel doping concentration needed for controlling of SCE. The moderated doping density of approximately 2.5e16 cm<sup>-3</sup> at Lg = 1  $\mu$ m [4] has been increased to more than 2e18 cm<sup>-3</sup> at Lg = 35 nm [17]. The reduction of gate length without heavy channel doping will result in accute threshold voltage roll-off and punch-through between source and drain. For sub-100 nm devices, halo/pocket implants and shallow source/drain junctions are used to block lateral field penetration (punch-through) and minimized the SCE without affecting the threshold voltage [18]. However, high channel doping concentration reduces carrier mobility due to impurity scattering [17], increases the sub-threshold slope and also introduces band-to-band tunneling.

On the top of SCE and leakage current limitations, the most challenging problems associated with scaling are the increasing statistical variations due to discreteness of charge and granularity of matter [19-21]. The main sources of intrinsic parameter fluctuation are random dopant fluctuation (RDF) [20, 21], line edge roughness of the gate (LER) [22, 23], metal gate granularity (MGG) [24, 25] and oxide thickness variations (OTV) [26]. It has been proven experimentally that the further scaling of bulk-MOSFET will introduce intolerable drain current and threshold voltage fluctuations and will dramatically degrade the circuit performance [27]. In the next section, the factors that impede the scaling of bulk-MOSFET in term of variability will be discussed.

## 2.4 Factors Impede the Scaling of Traditional Bulk MOSFET : Variability Aspects

In modern CMOS technology, the semiconductor industry aims to produce a high speed and low cost integrated circuits by shrinking the size of each transistor on a single chip. However, several limitations to scaling mark the end of 'happy scaling' era. These include the intrinsic parameter fluctuations (random dopant fluctuation-RDF, gate line edge roughness-LER, metal gate granularity-MGG and oxide thickness variation), the quantum mechanical effects (band to band tunnelling, direct gate oxide tunnelling and source to drain tunnelling), the degradation of carrier mobility, and the ever-increasing power dissipation. All the limitations and constraints are becoming more severe especially variability, and force the industry to shift the paradigm to new transistor structures and fabrication technologies which hopefully may tackle the limitations. Figure 2.5 shows the major challenges facing by the semiconductor industry in the 'late CMOS' phase, where new CMOS transistor architectures will be needed.

*Figure 2.5 : Major challenges as a function of time and technology nodes [28].*

It widely accepted that the statistical variability is a major concern for nanoscale CMOS technologies, hindering further device scaling and integration [14, 15, 29, 30]. Statistical variability is introduced by discreteness of charge and granularity of matter, which lead to significant fluctuations in the device characteristics.

Random dopant fluctuations (RDF) introduced by the ion implantation process and consequent activation and diffusion have became a dominant source of statistical variability in modern MOSFET technology [21, 31, 32]. During ion implantation process, the impurity atoms are implanted into the silicon with an adequate energy and activated using annealing in order to allow the impurity atoms to replace the silicon atoms in the lattice and to become activated. The combination of ion implantation and annealing causes random dopant distribution in every single device, leaving no two devices the same. RDF causes threshold voltage fluctuations due to the variation in dopant number and location [20, 21, 33, 34]. The magnitude of threshold voltage fluctuation becomes more pronounced in smaller gate length device due to the reduction in the number of discrete random dopants. This point is illustrated in Figure 2.6.

Figure 2.6 : (a) Schematic of 4.2 nm MOSFET under the influence of RDF. Red/blue dots represent donor/acceptor dopants, while the grey dots are silicon crystalline lattice [35], (b) average number of dopant atoms versus technology generation [36].

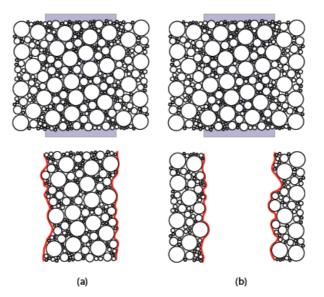

Another important source of intrinsic parameter fluctuation (IPF) is LER, which related to the patterning of the gate edge by using photolithography. The LER is due to the variations of the molecular structure of the resist polymer material, resulting in non-uniformities of the resist edge. In the past, the LER impact was negligible because the transistor gate length and width are much bigger than the roughness, however, as the devices shrinks, the LER causes appreciable fluctuation in the local length of the channel along the width of the transistor [37]. Figure 2.7 illustrates an example of polymer aggregates for negative/positive resists, where the unexposed/exposed regions are removed.

Figure 2.7 : Typical LER in photoresist when negative/positive resists are used [35].

Other possible statistical variability source is the metal gate granularity, which has been introduced when the technology moved to the higk-k gate dielectric materials at 45nm technology generation. The MGG is introduced by crystallization of the metal gate material during the high temperature annealing process leading to variation in the work function of the crystal grains in the metal gate [38]. This has became one of the major variability sources, affecting the transistor parameters distributions [15, 24, 25, 39, 40]. Figure 2.8 shows a typical metal grain pattern in a 35 nm gate length MOSFET with an average grain diameter of 10 nm and two different grain orientations.

*Figure 2.8 : Metal grain pattern of 35x35 nm gate with an average grain diameter of 10 nm [40].*

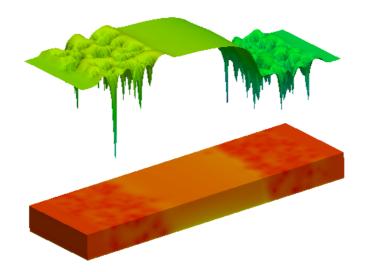

Additionally, oxide thickness variations (OTV) is another source of IPF associated with the silicon/silicon dioxide surface roughness at the interface between silicon, silicon dioxide and poly gate in MOSFET transistor. Such atomic scale roughness causes potential variation across the channel and leads to threshold voltage fluctuation [26, 41, 42]. The effect is more severe in scaled devices. Apart from threshold voltage variation, fluctuation in gate tunnelling current [43] and mobility are also affected by OTV since each individual device microscopically has dissimilar surface roughness and oxide thickness pattern as shown in Figure 2.9.

Figure 2.9 : Illustration of OTV impact at the interface of silicon/silicon dioxide and silicon dioxide/poly-si gate [35]. The Red, green and blue colors signify poly-si gate, silicon dioxide and silicon respectively.

Before the introduction of high-k/metal gate stack at 45 nm technology node, polycrystalline-silicon (poly-si) was used as the gate material. The poly-si granularity can result in large threshold voltage due to Fermi-level pinning at the grain boundaries at the poly-si/gate oxide interface [44] due to the high defect state densities [45].

All the principle sources of statistical variability described above can widen the threshold voltage distribution and degrading circuit and system performances of traditional bulk-MOSFET. This is related to the fact that, the progressive scaling of bulk-MOSFET needs a very high channel doping concentration to control SCE, leading to unacceptable high variability in threshold voltage due to the RDF [15, 46]. In this respect, new device architectures, materials and process steps should be introduced to allow further transistor miniaturization and mitigating the statistical variability introduced by RDF, although some of the other variability sources could still exist in new device architectures.

## 2.5 New Device Architectures: SOI MOSFET vs FinFETs

Scaling of traditional planar bulk-MOSFET is becoming more and more difficult in following the Moore's law in advanced technology nodes. The main detrimental effects are the difficult to control SCE and the increasing variability in the device characteristics. Therefore, there is a consensus among the semiconductor industry experts that introduction of new device architectures at nonometer regime is mandatory. The essence behind the invention of novel device structure is to maximize the control of gate terminal over the channel and minimize the impact of statistical variability on the device characteristics. Figure 2.10 shows an evolution of transistor structures that enable the continuing scaling down to a shorter gate length. A migration from conventional bulk-MOSFET to planar ultra thin body SOI (UTB SOI) and tridimensional FinFET is envisaged. The concept of both new structures is to improve the gate control and reduce the statistical variability.

Figure 2.10 : Transition of field effect transistor (FET) transistor to proceed further scaling, (a) bulk-MOSFET, (b) ultra thin body silicon on insulator (UTB SOI) and (c) FinFET [9].

#### 2.5.1 FD-UTB SOI

From a design point of view, the fully-depleted UTB SOI [47] (FD-UTB SOI) and FinFET [48] are very different device architectures. The planar FD-UTB SOI is built with a thin layer of crystalline silicon on top of an insulating layer (BOX). In FD-UTB SOI device, the SCEs are controlled by the silicon body thickness [49]. To acquire high performance, low sub-threshold slope and acceptable DIBL, the SCE can be controlled by the ratio of the gate length to the body thickness which should remain larger than four,  $L_{gate}/T_{Si} \ge 4$  [50].

The FD-UTB SOI transistors have demonstrated promising device performance, well controlled access resistance and significant reduction in statistical variability that originates from random dopant fluctuation (RDF), allowing the implementation of undoped channel. This leads to excellent matching performance [14, 51] and boosts carrier mobility. In addition, to excellent electrostatic integrity, improved scalability, and reduced DIBL, the UTB SOI also eliminates submerged leakage paths due to its ultra thin body structure. Since the manufacturing of the FD-UTB SOI transistors is relatively simple compared to the manufacturing of non-planar device, FD-UTB SOI offers advantages in terms of compatibility with planar CMOS processing and integration. As a result, the corresponding circuits can reach the market faster.

Another feature that makes planar device more attractive are the back-biasing capabilities [52-55]. This attribute is very useful for low power and low standby power applications. With the application of back-bias, the threshold voltage (multiple  $V_{th}$ ) and on/off current are easily tuned to meet design target [52, 56]. Simultaneously, performance enhancement can be achieved by applying forward back gate bias.

Simultaneously the optimization the '*SmartCut*' SOI wafer technology (pioneered by Soitec) was able to provide the wafer uniformity LTTV (layer total thickness variation) of +/- 0.5nm, which is in accordance with the FD-UTB SOI technology requirement [57]. Besides, most of the mobility enhancement technique can be applied to FD-UTB SOI to boost an extra performance [58, 59]. This is very important since the externally induced-stress (tensile/compressive liners; *t-CESL/c-CESL*) will be reduced with the reduction of the gate pitch as the gate length shrinks [60]. Furthermore, it has been

22

reported that FD-UTB SOI delivers currently the smallest  $V_{th}$  variation ( $A_{vt}$  -Pelgrom coefficient) [51, 61, 62] compared to the other devices with the same gate length.

#### 2.5.2 FinFET

In the FinFETs the thin silicon channel is turned by 90° out of the flat surface creating a '*fin*' [63]. The FinFET's gate wraps the channel on all three sides of the fin. As a result, the gate have improved control over the channel, leading to superior SCE control and better sub-threshold slope. The relatively large channel volume gives major advantage to FinFET in carrying high current density. In the FinFET structure, the fin width is the most critical parameter because it determines the SCE. As the fin width increased, the leakage current also dramatically increased due to the poor gate control over the channel [49]. It is imperative to achieve good control of the fin width since it also affecting other critical parameters such as threshold voltage [64-66] and mobility [67]. A key design guidelines for FinFET, allowing adequate reduction of the SCE, the fin width should be approximately one half of the gate length [48, 49].

It is widely accepted that the FinFET is the best structure for improving electrostatic integrity, achieving higher drive current and speed, small DIBL [68] and ideal sub-threshold slope (~ 60 mV/dec). Intel been first in introducing 3D Tri-Gate FinFET technology at 22 nm CMOS technology in their high end microprocessor *Ivy Bridge* with high volume of production starting in June 2012 [69]. However, from manufacturing standpoint, the FinFET is quite complicated and challenging because the fin definition must be narrow and uniform, with uniform gate dielectric on all sides and at the corners. In the FinFET manufacturing, all sources of process induced variations should be under control (on the few atomic layer scale) in order to achieve the promised benefit of the FinFETs. Furthermore, the FinFETs are very sensitive to fin line width and line edge roughness, which leads to threshold voltage fluctuation [64, 70]. In principle, the essential FinFET geometry introduces many edges and boundaries, therefore it unavoidably susceptible to extra parasitic coupling and substantial variations.

It is early to anticipate which device will be a winner in future applications with both FD-SOI MOSFETs and FinFETs having specific advantages and disadvantages. Certainly, both have the potential of taking over the bulk-MOSFET dominant position in future technology generations. Those in needs of high speed and high performance transistors nominate FinFET, meanwhile, others who are interested in low power mobile applications will find the FD-UTB SOI most desirable. On the whole, planar FD-UTB SOI has the potential of keeping the Moore's alive in low power and hand-held applications.

## 2.6 ITRS Projection on Fully Depleted SOI for Next Generation

Due to the physical limitations of the traditional planar bulk-MOSFET scaling, several options have been brought forward in the ITRS to extend the life of the transistor scaling. The emerging device technology has been added in the ITRS in order to improve device performance and replace the existing bulk-MOSFET via the introduction of multiple gates FET (e.g., FinFET) and SOI MOSFET (e.g., UTB-FD). It is foreseen by the ITRS that bulk-MOSFET will be superseded by UTB-FD at 22 nm gate length, while the multiple gate is expected to be introduced at 17 nm gate length, targeting low operating power technology [12].