### Reconfigurable Hardware for Control Applications

### Graeme Richard Milligan

A themed Portfolio submitted to the Universities of,

Glasgow,

Strathclyde,

Edinburgh

and Heriot-Watt

for the degree of Doctor of Engineering in

System Level Integration.

### ABSTRACT

This portfolio document is intended to present the work carried out in order to meet the requirements of the Engineering Doctorate (EngD) program undertaken at the Institute for System Level Integration (ISLI). This program was undertaken in partnership with the Universities of Glasgow, Edinburgh, Strathclyde and Heriott Watt and was funded by EPSRC and SLI Ltd.

The use of control systems is becoming ubiquitous with even the simplest of systems now employing some kind of control logic. For this reason the project investigated the use and development of reconfigurable hardware for control applications. This first involved a detailed analysis of the current state of the art in the reconfigurable field as well as some selected applications where it is thought this technology may be of benefit.

The main body of the project was separated into three distinct areas of research and is hence presented as a collection of three technical documents. The first of these areas was the use of reconfigurable hardware for the implementation of Finite State Machines (FSM) with particular reference to reducing the size of the hardware block required to implement these structures. From this a novel implementation method was developed based on the principle of Forward Transition Expressions which are capable of implementing FSMs on a reconfigurable device using run-time reconfiguration. The second area of research was the investigation of the characteristics of reconfigurable devices with a view to estimating the amount of hardware required within a device from high level parameters. The final area of research was the development of a custom reconfigurable device specifically tailored for the implementation of FSM.

### **Declaration of Originality**

I, Graeme Richard Milligan, declare that this thesis is my own work and has not been submitted in any form for another degree or diploma at any university or other institute of tertiary education. Information derived from the published and unpublished work of others has been acknowledged in the text and a list of references is given in the bibliography.

The material contained in this thesis is my own original work produced under the supervision of Wim Vanderbauwhede, Bob Adamson and Prof. Steve Beaumont. Some of the work contained in this thesis was produced in collaboration with Paul Jackson at Edinburgh University and as such, he is credited in the appropriate section.

Graeme Milligan

### **Dedication and Acknowledgements**

This thesis is dedicated to the memory of

Mr. Thomas Jude O'Neill

22nd Dec. 1970 - 12th Dec. 2002

and

Miss. Catriona Caulfield

11th Jan. 1977 - 27th Aug. 2004

Your memory lives on with

all who knew you.

The Author would like to acknowledge the help and support of his parents, Catherine and David, without their infinite patience and support this work would not have been possible. I love you both very much.

I would also like to thank all of the staff at the Institute for System Level Integration for all their help and in particular Mrs. Alexandra (Sandy) Buchanan.

Finally i would like to thank all of my friends, in particular Jocelyn, Antoine and Ruairi, for preventing me from talking about my project too much and allowing me to escape from time to time. Thanks everyone.

### PORTFOLIO DOCUMENT

# Portfolio Executive Summary and Introduction

Author: Supervisor:

Graeme Milligan Wim Vanderbauwhede

### Contents

| 1 | Exe | cutive Summary                                                       | 1  |

|---|-----|----------------------------------------------------------------------|----|

| 2 | Bus | iness Aspects                                                        | 3  |

|   | 2.1 | Area                                                                 | 4  |

|   | 2.2 | Speed                                                                | 5  |

|   | 2.3 | Power                                                                | 6  |

|   | 2.4 | Control Domain                                                       | 6  |

| 3 | Pro | ject overview                                                        | 7  |

|   | 3.1 | Implementation of Control Systems using Reconfigurable Hardware      | 8  |

|   | 3.2 | Investigation of the Characteristics of Reconfigurable Devices       | 9  |

|   | 3.3 | Development of a Hardwired Directional Reconfigurable Architecture . | 10 |

| 4 | Por | tfolio Organisation                                                  | 11 |

### 1 Executive Summary

This volume is intended to present the work carried out in order to meet the requirements of the Engineering Doctorate (EngD) program undertaken at the Institute for System Level Integration (ISLI). This program was undertaken in partnership with the Universities of Glasgow, Edinburgh, Strathclyde and Heriott Watt and was funded by EPSRC and SLI Ltd. The EngD requires that 120 SCOTCAT credits are obtained in relevant engineering subjects with a further 60 credits required in business related subjects with the remainder of the program being taken up by an extended period of investigation and development in a given research domain.

Initially the scope of the project suggested was "The use of Reconfigurable Hardware in Communication Applications". This title was designed to give a large scope to the project and as such an extensive literature review was undertaken in both the communications and reconfigurable hardware domains. The reason for the large scope of the project was SLI Ltds relative inexperience in this field. For this reason this project was intended to operate at a fairly high level and allow SLI Ltd to develop an in-house understanding of reconfigurable hardware and also identify areas of interest for future investigation by subsequent EngD research engineers.

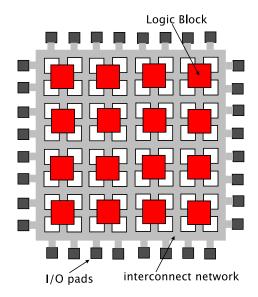

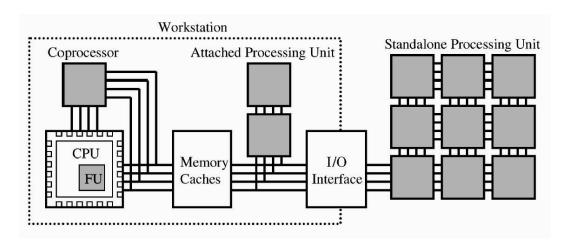

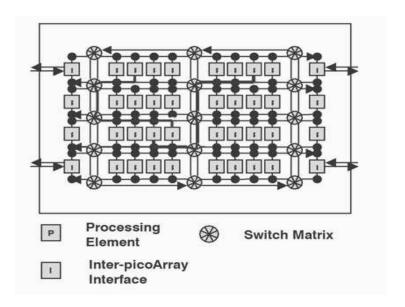

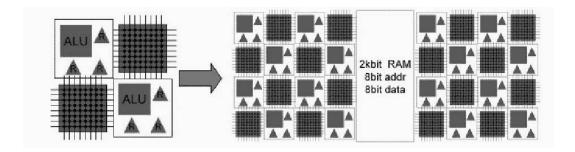

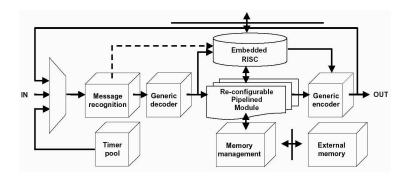

In order to address a lack of knowledge of the current state of reconfigurable hardware device development and to develop an understanding of the *state-of-the-art* in this field, an extended investigation was carried out into reconfigurable hardware. This investigation primarily focused on current novel reconfigurable architectures in both the academic and industrial domains with particular attention paid to devices specifically developed for the communications domain. During this period it was found that, for industrial devices in particular, the current devices under development were specifically targeted at the low level operations, such as encryption and encoding, carried out in the physical layers of communication protocol stacks. Due to the high speed and intensity of these operations these devices aimed to migrate any operations

carried out in software to take advantage of the characteristics of hardware to reduce the area and power required when caring out these operations while maintaining the speed required at these low levels. The report shown in appendix A1 was complied giving details of a selection of industrial and academic reconfigurable devices.

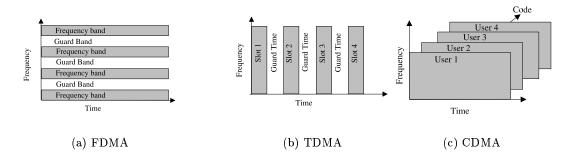

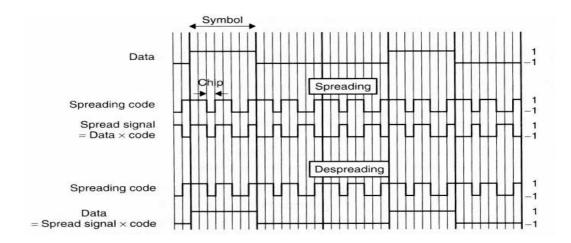

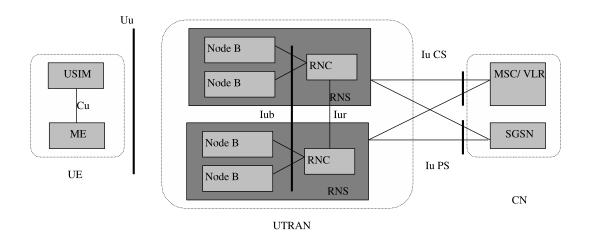

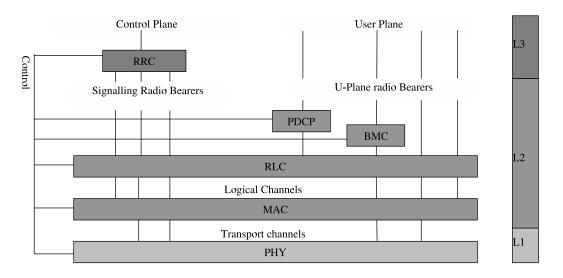

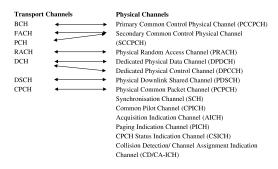

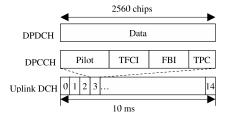

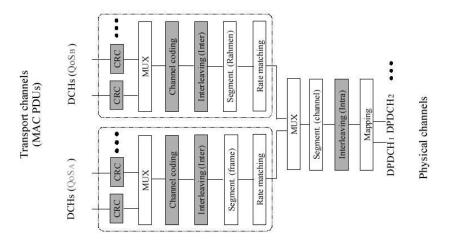

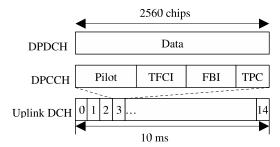

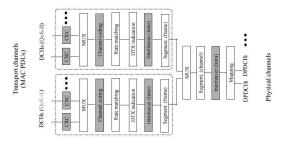

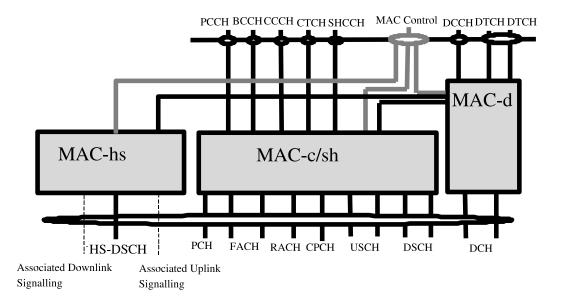

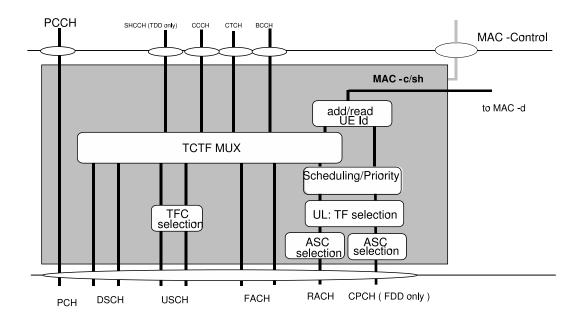

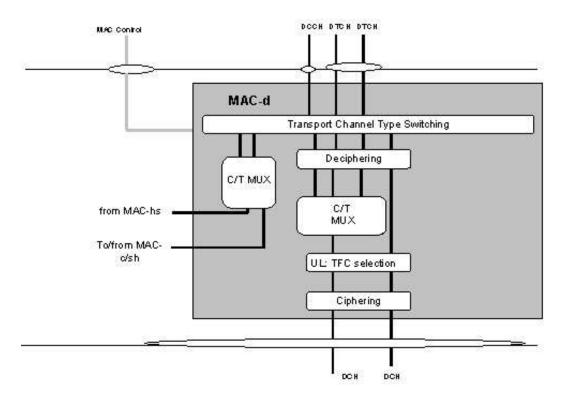

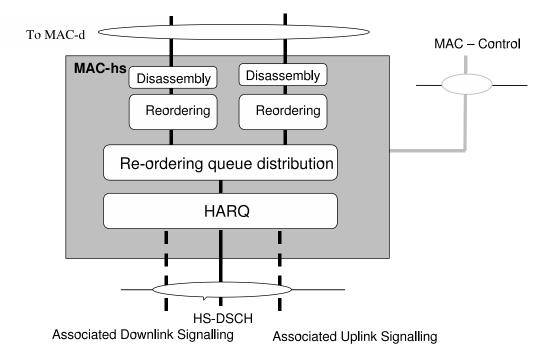

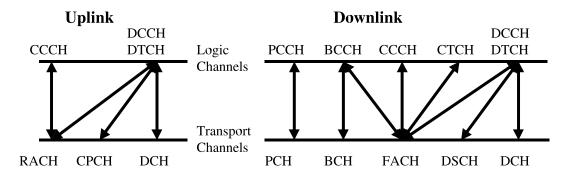

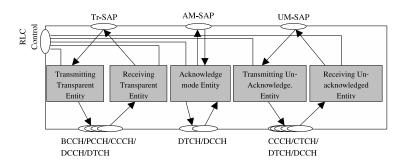

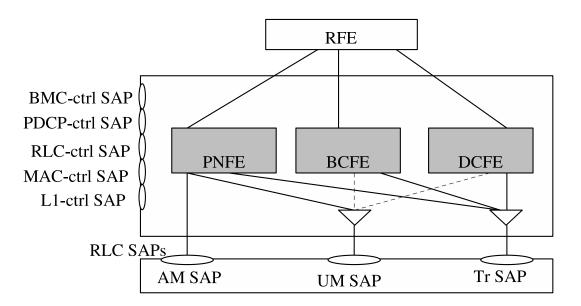

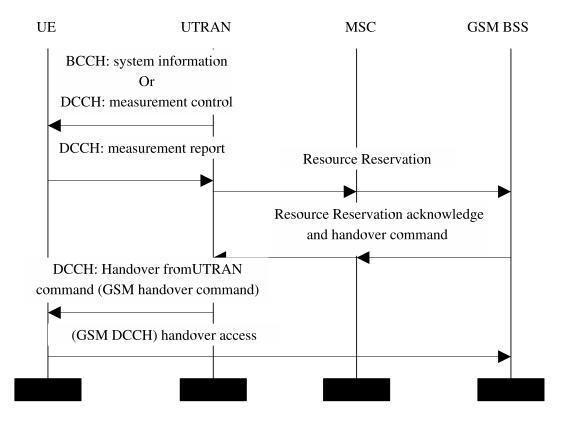

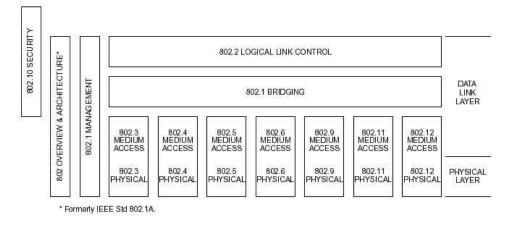

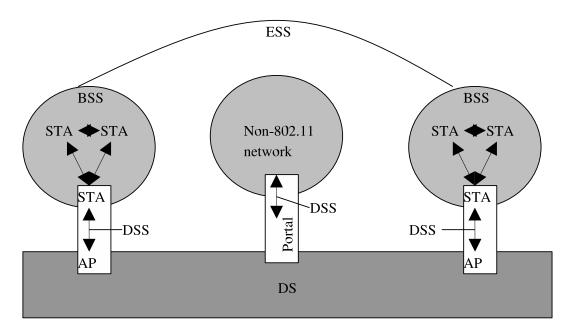

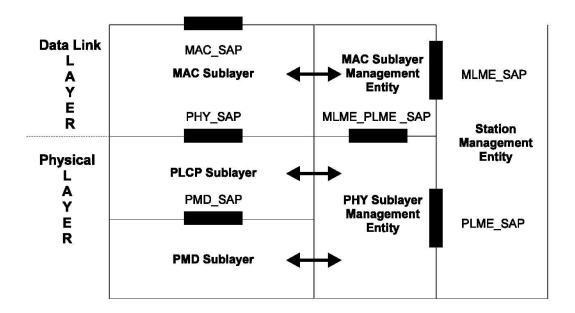

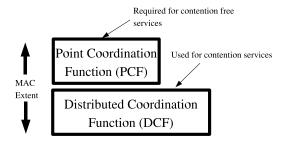

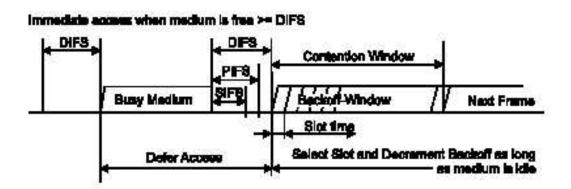

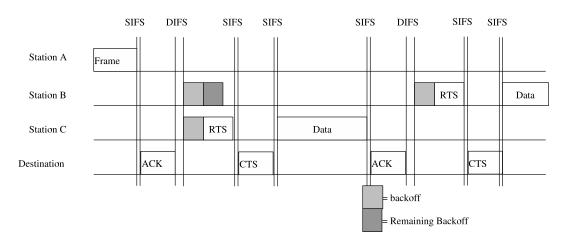

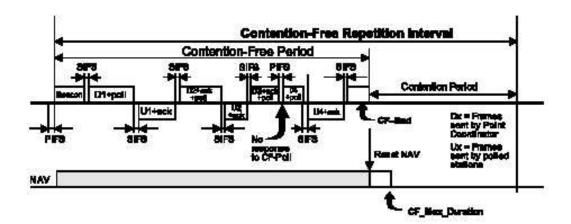

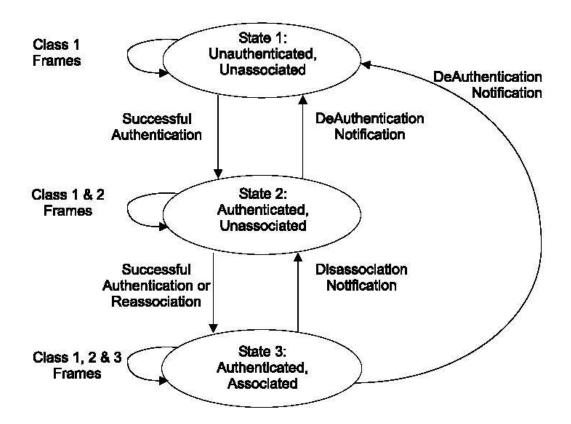

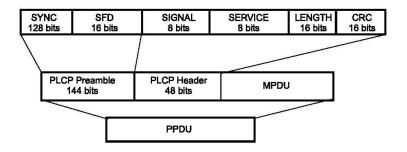

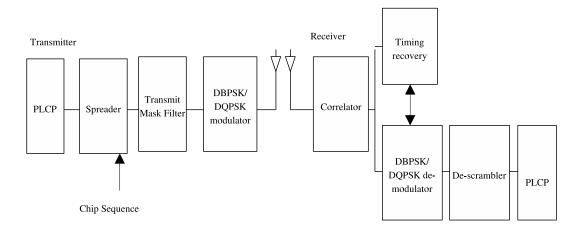

In order to identify possible areas in the communications domain that may benefit from the use of reconfigurable hardware it was first necessary to undertake an extended period of investigation into this field. Of particular interest is the possibility of creating a single reconfigurable device for mobile applications that is capable of implementing multiple communications protocols. In this way a single hardware device could be used to implement a range of communications protocols while making use of the low area, high speed and low power characteristics of digital hardware. For this reason it was decided that two example wireless protocols currently used in mobile applications should be analysed to identify areas that may be of interest for implementation using reconfigurable hardware. The protocols selected for analysis were the Universal Mobile Telecommunications System (UMTS) and the IEEE 8802.11 wireless LAN protocol. For each of these protocols a report was compiled and they are shown in appendix A2 and appendix A3 respectively. During this investigation it was seen that the upper layers (MAC, RLC etc.) of the communications stack can be modelled by a control path and a data path. The control path is responsible for determining the state of the device based on information provided by the network and the device. Based on the state of the control path, the data path performs the required data process on packets obtained from the layers immediately adjacent to the current layer in the communications protocol stack.

At this point the control path was identified as of particular interest due to the generality of the operations carried out. It can be seen that the control path can be implemented as a Finite State Machine (FSM) where the state of the machine is determined by information provided by the device and from the network currently in

use by the device. As FSMs are used in almost all control applications, the use of a reconfigurable hardware device specifically tailored for the implementation of these control systems has a market that is not limited to the implementation of communications protocols. For this reason the scope of the project was altered to narrow the domain of interest to the implementation of control systems and specifically the implementation of FSMs using reconfigurable hardware. This lead to the title of the project begin altered to "Reconfigurable Hardware for Control Applications"

As the project was intended to be used to build a general understanding within SLI Ltd. of the reconfigurable hardware domain and to suggest possible areas of interest for future EngD research engineers it was felt that rather than undertaking a single monolithic project on the use of Reconfigurable hardware in the control domain the remainder of the extended period of research should be split between a number of related sub-projects under the title of "Reconfigurable Hardware for Control applications" with particular focus on the development of a device tailored to the implementation of control applications. The following section gives an overview of the business aspects of the project and aims to provide enough information to allow the reader to assess the desicions made and advantages of the ideas proposed in the thesis from a business perspective. This is then followed by an overview of each of the sub-projects with the goals of each project being identified and the objectives achieved.

### 2 Business Aspects

Although much of the material presented here is mainly of a theoretical nature it is essential to be able to assess any benifits produced by the ideas presented from an industrial perspective. For this reason this section will outline the main design parameters, area, speed and power, and relate to the control/communications domain. This will allow comment to be made on the impact of the ideas presented here on

these parameters and how they can be related to the overall cost/benefit of utilising these ideas in a modern design flow.

Due to the large range of implementations that control systems find themselves their requirements vary greatly, a control system for use in the avionics systems must be far more reliable and faster acting than one found in a washing machine for example. The following section presents each of the key design metrics used in modern silicon chip design.

#### 2.1 Area

The area of the silion chip produced during manufacture is probably the most important design metric concerning the operation and cost of a new device. The area of the chip determines how many chips can be produced in a single production batch at a fixed cost. This means the smaller the area of the chip the larger the number that can be produced and hence the cost per chip is reduced. The size of the chip also has an impact on what is known as production yield. This is the percentage of all chips produced that operate correctly. It is found that the smaller the silicon area the larger the production yield as any defects may affect a larger number of chips but due to the small size this equates to a smaller percentage of the total amount produced.

The area of the silicon required is determined by the amount of hardware required to implement the required functionality, the wiring associated to connect these components (transistors) as required and the production method selected. For this reason much of the design time is concerned with the removal of redundant logic to ensure the chip is compact as possible and place and route to reduce the length and amount of logical interconnect required.

It is also important to ensure that before manufacture the chip has been proven to operate as required as it is very costly to correct mistakes after manufacture has begun and usually invovles returning to the design stage and restarting manufacture.

The area of the chip also has a direct effect on the other main design metrics as is outlined in the following sections.

### 2.2 Speed

The speed of operation of a silicon chip is an essential design paramter as it is essential to ensure that the chip operates fast enough to ensure correct operation. For example, a system design to control the avionics on a modern jet fighter must operate at far greater speeds than a system design as a user interface. In the later example the device is operating at "human speeds" and can thus can operate at relatively low speeds.

The speed of a silicon device is dependent on 2 main factors; the first of these are the delays introduced by the actual components or transistors on the chip and the second are delays introduced by capacitance in the interconnects between these components. The actual speed of operation is highly dependent on what is known as the critical path, this is the longest path from the inputs of the device to the outputs of the device. Due to the importnace of this factor much research has been carried out on modelling the delays in the critical path and optimisation to reduce the effect of the delays introduced.

Another aspect associated with the speed of a device is latency. This is mainly used when refering to synchrounous logic where a clock signal is required to allow components to pass data from their inputs to the outputs. This means that for every synchrounous component a signal must pass through a clock cycle is required. This should not be confused with the speed of the device which is the actual speed of the clock rate. It can be seen that the size of the chip will have a large effect on the speed of the device as smaller chips will have shorter interconnects and hence a shorter critical path.

#### 2.3 Power

The power consummed by a silicon device comes from 2 main sources; static and dynamic power consumption. Static power refers to all sources of power consumption present when the chip is in a steady state and is usually assocaited with leakage current from the transistors through the substarate of the device. Dynamic power consumption concerns all power that is used in a silicon device during operation. The main source of dynamic power consumption is the power required to drive the trnasistors on the device and the capacatance in the interconnects. Dynamic power is far more significant than static power consumption and as such much research has been produced aimed at reducing the dynamic power consumption of devices.

It can be seen that one of the most important factors in dynamic power is the size, or area, of the device as this dictates the number of transistors that must be charged during operation and also the capacitance of the interconnects. For this reason it is normal to assume that the smaller the silicon device the lower the power consumption but it should be noted that this is only true where the operating speed remains constant as reducing the size will be offset by the increase in frequency that the dynamic conponents must be charged.

### 2.4 Control Domain

Due to the varied nature of the control domain, the requirements of differing application will vary greatly. As stated, control systems are found in all application domains from space and military applications to simple consumer electronics devices. In general it can be seen that the selection of the method of implementation is highly dependent on the application and is in effect a balancing act between producing a technically acceptable solution and non-enginneering factors such as design time and cost. For this reason, although it would be desirable to produce the smallest, fastest and most power efficient implementation of the required control system, this is often

imractical due to the high cost of designing such a device.

If the control domain is concidered from the mobile communications device perspective, as was the original scope of this project, it is desirable to utilise very small device as this allows for the reduction in size of the communications device. It is also essential to ensure that the device be as power efficient as possible to increase the battery life of the device. Depending on the nature of the control system within the device, speed varies in importance as a design metric as user interface control systems are intended to work at "human" speeds whereas the undelying control systems for the communications protocols must operate at very high speeds and hence require a high speed device.

### 3 Project overview

As stated, the main period of extended research was divided into a collection of interrelated sub-projects under the umbrella of the overall project title. This allowed a

number of aspects of the use of reconfigurable hardware for control applications to

be researched with the view of developing an understanding of the possible uses

and also suggest future projects that could be undertaken by SLI Ltd. For this

reason two main areas were identified; the use of reconfigurable hardware in the

implementation of Finite State Machines (FSMs) and the investigation of a novel

device specifically tailored for this application. In order to achieve this the first subproject was primarily concerned with identifying the optimal use of reconfigurable

hardware in the implementation of the control structures. The remaining two subprojects undertaken were then concerned with investigating the characteristics of

the device required to implement these structures based on the use of reconfigurable

hardware suggested in the previous project.

The following presents a short overview of each of the sub-projects.

## 3.1 Implementation of Control Systems using Reconfigurable Hardware

This project was primarily concerned with the investigation of the optimal use of reconfigurable hardware when used to implement control systems and in particular FSMs. Although it is possible to simply map FSMs directly to reconfigurable devices it was considered that this does not make use of the particular characteristics, and in particular the ability of reconfigurable hardware to be programmed during device operation (run-time reconfiguration). As such the traditional method of implementation of FSM was investigated in great detail with a view to altering this to take advantage of the characteristics of reconfigurable hardware.

During this investigation a general model of FSM was developed and based on this a novel method of FSM representation was suggested. This representation was based on using the current state of the reconfigurable device to represent the current state of the FSM rather than using a feedback register as would traditionally be the case. This representation allowed a far smaller block of logic to be used when determining state changes.

In order to investigate the novel FSM representation presented in this sub-project a C based circuit generator was developed that is capable of implementing the hardware required to implement an FSM using the representation presented. This generator is capable of generating all of the components required to produce the device required to implement the FSM and has demonstrated in simulation the correct operation of this novel device and the novel FSM representation presented.

The work carried out during this sub-project was considered novel enough to be considered for patenting by SLI Ltd. Although extensive consultation was undertaken with patent lawyers, due to the length of time required to draft the patent application, at the time of writing this work, this patent has yet to be filed. Although the commercial advantage of patenting this work, and indeed the general use of patents

in this field, is questionable it is felt that the purpose of this process was to improve the profile of SLI Ltd. Due to the delays incurred by this application process and the patent not being filed by the end of the project a paper was instead submitted to the NASA/ESA Conference on Adaptive Hardware and Systems (AHS-2007) where it has since been accepted for publication.

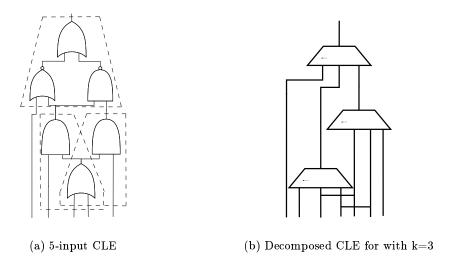

### 3.2 Investigation of the Characteristics of Reconfigurable Devices

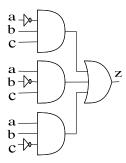

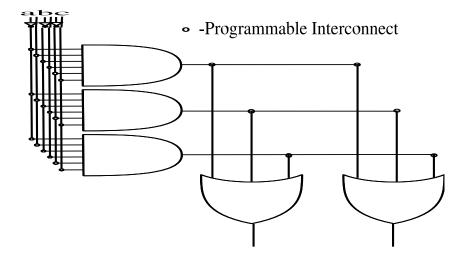

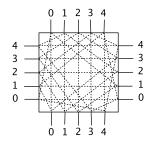

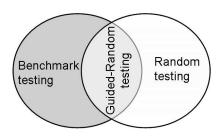

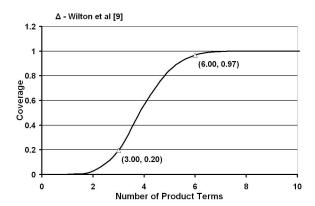

This sub-project was primarily concerned with the investigation of the hardware required within reconfigurable devices for the implementation of logic like that used in the calculation of the next state of FSMs. The next state of FSMs is calculated using a Combinatorial Logic Block (CLB) that calculates the next state of the FSM based on a set Combinatorial Logic Expressions (CLE). For this reason the hardware required to implement CLEs was investigated with the goal of determining the optimal amount of hardware that should be placed within the reconfigurable device fabric in order to allow for the implementation of these expressions.

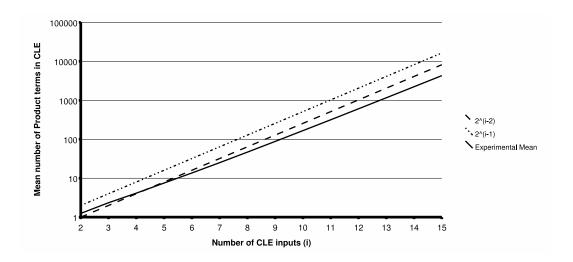

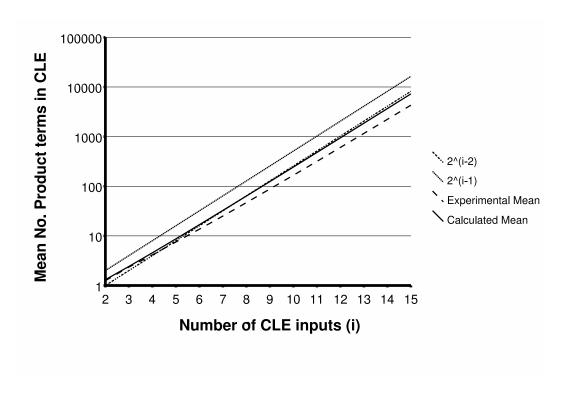

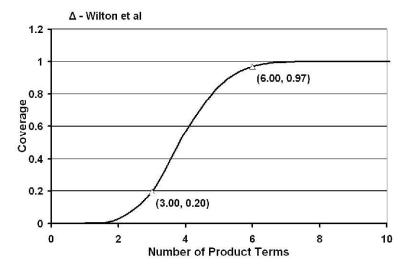

Initially the Sum-of-Products representation and Boolean simplification of CLEs was investigated in order to determine if a link existed between the number of inputs to an expression and the hardware required to implement these expressions. By generating every possible expression with a fixed number of inputs it was found that the number of inputs to the expression had a direct effect on the hardware required to implement these expressions but due to the extremely large number of possible expressions this form of exhaustive testing was impractical for expressions with even very small numbers of inputs. In order to extend this investigation a pseudo-random circuit generator was developed that was capable of generating very large numbers of expressions with a fixed number of inputs. The hardware required to implement these expressions could then be found and based on this the distribution of hardware requirements could be calculated. The results obtained using this method were then

compared to those obtained in a previous project, carried out to determine the average hardware requirements of logic based devices, to confirm the accuracy of the circuit generation method. This method was then extended to memory based architectures where no comparative research has been identified.

Although this method allows the hardware requirements of CLEs to be investigated it was found that even for the pseudo-random circuit generation method that the time taken to obtain results for CLEs with large numbers of inputs was prohibitive. For this reason a mathematical method of determining the average hardware requirements of CLEs was developed in conjunction with Dr. Paul Jackson at Edinburgh University. This method is based on cube cover and allows the calculation of the average hardware requirements of logic based reconfigurable devices based on the number of inputs to the expression.

Based on the work carried out in this sub-project a conference paper has been compiled and has been submitted to XXV IEEE Intenational Conference on Computer Design 2007 (ICCD-2007) where it currently in the process of peer review prior to publication.

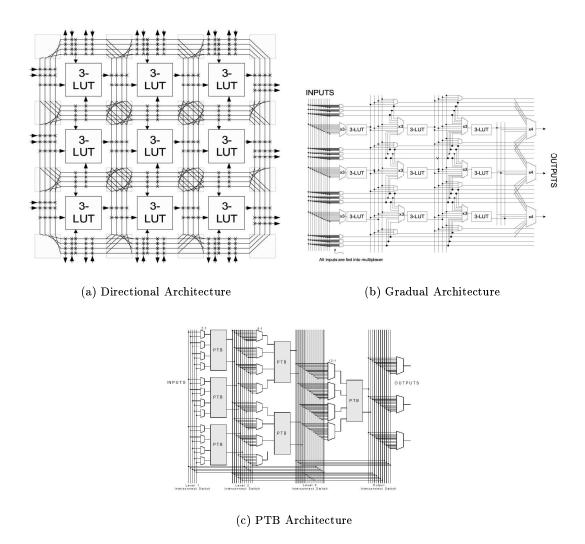

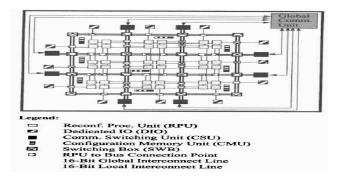

# 3.3 Development of a Hardwired Directional Reconfigurable Architecture

This sub-project focused on the development of a novel reconfigurable device for the implementation of CLEs like those used in the next state calculation of FSMs. In order to develop this device it was necessary to develop a sound understanding of the method by which these expressions are traditionally implemented in existing reconfigurable devices. Based on this a device architecture is suggested that makes use of the characteristics of these expressions to reduce the overhead introduced by reconfigurable hardware in providing the flexibility required by these devices.

A device generator was then developed to allow for the investigation of this ar-

chitecture. The generator is capable of generating all of the hardware components required to implement this architecture and produce a fully functioning device. Due to the nature of the device a novel synthesis tool was also developed to allow a high level description of the CLE to be synthesised to produce the bit-file required to implement the CLE on this novel reconfigurable device. The synthesis tool made use of existing synthesis algorithms to obtain a representation of the CLE suitable for implementation and automatically performs the place and route operation required to fully implement the CLE on the architecture suggested. The hardware characteristics of the device required to implement these CLEs could then be compared to those required using standard reconfigurable devices such as FPGAs.

Again the work presented in this sub-project was considered novel enough to be considered for patenting by SLI Ltd but due to time constraints this patent has yet to be filed.

### 4 Portfolio Organisation

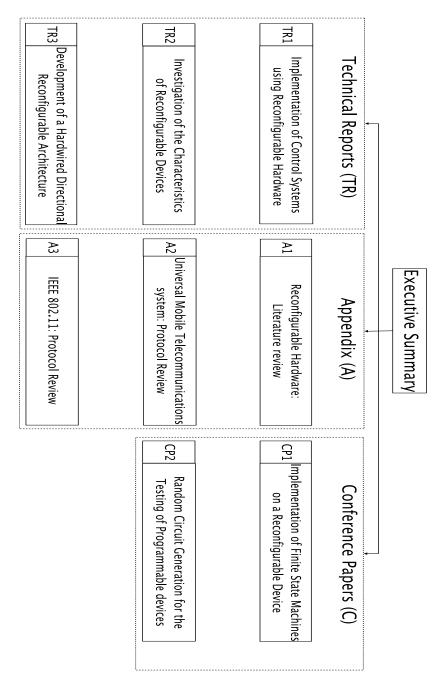

As the extended period of research was subdivided into three sub-projects a separate and distinct portfolio document has been produced to present each of these sub-projects. The structure of this document is shown in figure 1. As this shows each of the sub-project has its own distinct report entitled Technical report (TR) 1-3. The literature reviews carried out on communications protocols and reconfigurable hardware are presented in the appendix with titles appendix (A) 1-3. Finally the papers produced concerning TR1 and 2 are presented at the end of this document and are named Conference Paper (CP) 1 and CP2 respectively.

Figure 1: Portfolio Organisation Chart

### PORTFOLIO DOCUMENT TR1

### Implementation of Control Systems using Reconfigurable Hardware

Author:

Supervisor:

Graeme Milligan

Wim Vanderbauwhede

### Contents

| 1        | Inti | roduct                 | ion                                                            | 1               |  |  |  |  |

|----------|------|------------------------|----------------------------------------------------------------|-----------------|--|--|--|--|

| <b>2</b> | Bac  | kgrou                  | nd Theory                                                      | 9               |  |  |  |  |

|          | 2.1  |                        | al Definition of Finite State Machines                         |                 |  |  |  |  |

|          | 2.2  |                        | tional Implementation of Finite State Machines                 |                 |  |  |  |  |

|          |      | 2.2.1                  | Finite State Machine extraction                                |                 |  |  |  |  |

|          |      | 2.2.2                  | State Transition Graph representation of Finite State Machines | 6               |  |  |  |  |

|          |      | 2.2.3                  | State Transition Table representation of Finite State Machines | 8               |  |  |  |  |

|          |      | 2.2.4                  | State Labeling                                                 | Ć               |  |  |  |  |

|          |      | 2.2.5                  | Transition Expression (TE) Extraction and Optimization         | 10              |  |  |  |  |

|          |      | 2.2.6                  | ASIC implementation of FSMs                                    | 12              |  |  |  |  |

|          |      | 2.2.7                  | FSM implementation on a Reconfigurable Device                  | 13              |  |  |  |  |

|          |      | 2.2.8                  | FSM operation on a reconfigurable device                       | 14              |  |  |  |  |

| 3        | Nov  | vel rep                | resentation of FSMs for reconfigurable hardware                | 16              |  |  |  |  |

|          | 3.1  | Invest                 | igation of characteristics of CLB                              | 16              |  |  |  |  |

|          | 3.2  | Remo                   | val of current state feedback                                  | 17              |  |  |  |  |

|          |      | 3.2.1                  | Derivation of FTEs for Mead-Conway traffic light FSM           | 18              |  |  |  |  |

| 4        | FSI  | M imp                  | lementation on a custom reconfigurable architecture            | 18              |  |  |  |  |

| 5        | Rec  | onfigu                 | rable device for the implementation of FTEs                    | 21              |  |  |  |  |

|          |      | 5.0.2                  | Combinatorial Logic Block (CLB)                                | $2\overline{2}$ |  |  |  |  |

|          |      | 5.0.3                  | Configuration memory                                           | 24              |  |  |  |  |

|          |      | 5.0.4                  | State Controller                                               | 26              |  |  |  |  |

|          |      | 5.0.5                  | Memory Controller                                              | 26              |  |  |  |  |

|          |      | 5.0.6                  | Device operation                                               | 27              |  |  |  |  |

|          | 5.1  | Gener                  | ation of device Implementation of Custom Reconfigurable device | 29              |  |  |  |  |

|          |      | 5.1.1                  | Generation of Generic device                                   | 29              |  |  |  |  |

|          |      | 5.1.2                  | Generation of Domain specific device                           | 30              |  |  |  |  |

| 6        | Res  | $\operatorname{sults}$ |                                                                | 31              |  |  |  |  |

| 7        | Fut  | ure W                  | ork                                                            | <b>3</b> 4      |  |  |  |  |

|          | 7.1  | Virtua                 | al Output addressing                                           | 34              |  |  |  |  |

|          | 7.2  |                        | al Input addressing                                            |                 |  |  |  |  |

|          | 7.3  |                        | l reconfiguration and Configuration Caching                    |                 |  |  |  |  |

| 8        | Cor  | ıclusio                | n                                                              | 37              |  |  |  |  |

|          |      |                        |                                                                |                 |  |  |  |  |

### List of Figures

| 1           | Simplified FSM design flow for ASIC and Reconfigurable device                                                           | 5                    |

|-------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2           | FSM extraction                                                                                                          | 6                    |

| 3           | STG for Mead-Conway Traffic Light Controller [11]                                                                       | 7                    |

| 4           | FSM implementation on a reconfigurable device                                                                           | 13                   |

| 5           | General Hardware model of FSM using Reconfigurable hardware                                                             | 15                   |

| 6           | Hardware design flow of a FSM for Custom Reconfigurable Device                                                          | 20                   |

| 7           | Custom Reconfigurable device for implementation of FSMs                                                                 | 21                   |

| 8           | Configuration Memory Structure                                                                                          | 24                   |

|             |                                                                                                                         |                      |

| List        | of Algorithms                                                                                                           |                      |

| ~~          |                                                                                                                         |                      |

| 1           | FSM operation on a reconfigurable device                                                                                | 16                   |

| 2           | FSM operation on a custom reconfigurable device                                                                         | 28                   |

|             |                                                                                                                         |                      |

| List        | of Tables                                                                                                               |                      |

|             |                                                                                                                         |                      |

| 1           | STT of Mead-Conway Traffic Light Controller                                                                             | 8                    |

| 2           | Binary Encoding of State Labels                                                                                         | 9                    |

| 3           |                                                                                                                         |                      |

| 4           | Truth-Table representation of the Mead-Conway traffic light controller                                                  | 11                   |

| 4           | Truth-Table representation of the Mead-Conway traffic light controller Sub-truth-tables for state HG                    | 11<br>19             |

| 5           | - · · · · · · · · · · · · · · · · · · ·                                                                                 |                      |

|             | Sub-truth-tables for state HG                                                                                           | 19                   |

| 5           | Sub-truth-tables for state HG                                                                                           | 19<br>19             |

| 5<br>6      | Sub-truth-tables for state HG                                                                                           | 19<br>19<br>19       |

| 5<br>6<br>7 | Sub-truth-tables for state HG Sub-truth-tables for state HY Sub-truth-tables for state FY Sub-truth-tables for state FG | 19<br>19<br>19<br>19 |

### 1 Introduction

In modern engineering the use of control systems to implement complex system behaviour is ubiquitous and found in almost all engineering disciplines. Whether they are inferred or purposely designed into devices, control systems are required to allow devices to operate in an intelligent manner rather than simply reacting to the current operating conditions of the system. The use of control systems allows a device to determine its response to a sequence of events rather than simply producing a response based on a single event. Determining the response of devices in this way allows more complex behaviour to be implemented and allows a greater degree of automation, reducing the need for human intervention.

Although for simple applications it is often unnecessary to explicitly specify the control system, and it is instead inferred from the functional description of the application, for more complex applications a high-level model is required to allow designers to specify the control behaviour of the system. A commonly used high-level model is the Finite State Machine (FSM). FSMs are abstract models used to describe the behaviour of a control system in response to a sequence of inputs and are based on the theory of finite automata in computer science [9].

Due to the ubiquitous nature of FSMs a device capable of efficiently implementing these models would have applications in almost all domains. As the characteristics of FSMs are highly dependent on the particular application, it is dangerous to create a device for the implementation of general FSMs using domain profiling techniques such as that suggested in [7]. In this method benchmark circuits from a particular domain are used to determine the characteristics of reconfigurable device targeted at particular application domains such as communications or digital signal processing (DSP). Instead a more generalized approach is required to determine the most efficient use of reconfigurable hardware for the implementation of FSMs. The use of FSMs to implement the control behaviour of systems is well established and as such

a large number of texts are devoted to this subject including [6, 11, 12].

The implementation of FSMs can be broadly separated into two sections, the extraction of the FSM from the high level specification of the system and the implementation of the FSM. The extraction of FSMs is independent of the method of implementation and is concerned with developing a high-level description of the control aspects of the specification.

The implementation of the FSM can be split into two main groups, the FSM can either be implemented in software or hardware. Software implementation of FSMs allows rapid development and deployment due to short software design cycles. where as implementation in dedicated hardware involves the production of an Application Specific Integrated Circuit (ASIC) that implements the required behaviour. This approach produces devices with low area and power requirements but requires lengthy and expensive hardware design and manufacturing processes making it impractical for low volume applications or for developers with limited resources. An alternative to the use of full custom hardware is the use of reconfigurable devices such as the Field Programmable Gate Array (FPGA).

Reconfigurable hardware combines the speed and efficiency of hardware with the flexibility and programmability of software. The introduction of this flexibility and programmability requires the introduction of hardware required to program the device resulting in a lower efficiency when compared to full-custom ASIC design.

Recently there has been much interest in making use of the ability of reconfigurable devices to be programmed while the device is in operation. This allows devices to implement multiple functions simultaneously by dynamically switching between functions or 'contexts'. This process, known as run-time reconfiguration, allows a small reconfigurable device to masquerade as a larger device by implementing applications that require larger hardware resources than are available on a single reconfigurable device.

This section of the portfolio is intended to give details of the work carried out on the development of a novel method for the implementation of FSMs using reconfigurable hardware. This method makes use of a novel representation of FSMs that allows the implementation of these machines using a far smaller reconfigurable device than would be traditionally required. This section begins by presenting the formal definition of FSMs in section 2.1 and is followed by an overview of the traditional method of FSM implementation in full-custom hardware and on a reconfigurable device to allow for comparison with the novel method presented here.

The novel representation of FSMs suggested is then presented in section 3 before the design flow required to implement this representation is presented in section 4. Section 5 then presents the device required to implement the novel FSM representation presented. In order to prove the usefulness of this method it is then compared to the traditional method of implementation for a range of FSMs and the results of this comparison are presented in section 6 before final conclusions are made.

### 2 Background Theory

In order to investigate the most suitable use of reconfigurable hardware for the implementation of control systems it is first necessary to understand both the theory and implementation of FSMs. This section begins by presenting a formal definition of FSMs and is followed by a description of the process of FSM extraction before the implementation of FSMs is discussed for both the ASIC and reconfigurable device design flows.

### 2.1 Formal Definition of Finite State Machines

FSMs are abstract models used to represent the sequential behaviour of systems. They are used in control applications to define the response of a system to a sequence of input events. This allows designers to implement systems with complex behaviour as opposed to simple systems that can react to only the current operating conditions of the system.

An FSM can be fully described using the 6-tuple

$$M = (S, I, O, \Delta, \Lambda, R)$$

, where

- S is a finite set of states, and |S| is the total number of unique states,

- I is a finite input space, and |I| is the total number of inputs,

- $\bullet$  O is a finite output space, and |O| is the total number of outputs,

- $\Delta$ is a set state transitions based on the current state and the current inputs,

- Ais the output relation defined in terms of the current state and the current input vector,

- and R is a set of reset states.

State transitions are assigned to each state and based on the current inputs and current state are used to determine the next state of the FSM. The current state of the FSM is determined by the initial state of the FSM and the previous input sequence applied to the machine. This means if the previous input sequence and start state of the FSM is known it is possible to predict the current state of the FSM.

The output of the state machine (O) can be generated in two ways: either the output is dependent only on the current state (Moore machine) or is dependent on the current state and the current inputs (Mealy machine). In the case of the Moore machine the output relation  $\Lambda$  will contain only a single output for each state. This section is only intended to present the formal description and overview of FSMs, a more detailed discussion of FSMs can be found in many texts including [6, 11, 12].

It should be noted that as the novel implementation method suggested here is only concerned with the generation of the next and current state of the FSM it is applicable to both Moore and Mealy machines. In the case of the Mealy machine an addition block of logic would still be required to produce the final outputs.

### 2.2 Traditional Implementation of Finite State Machines

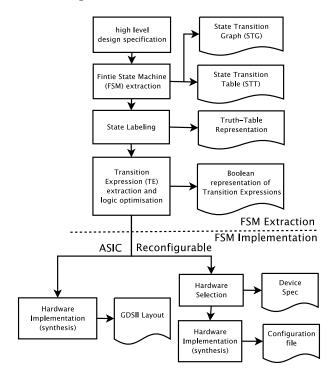

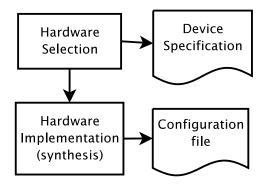

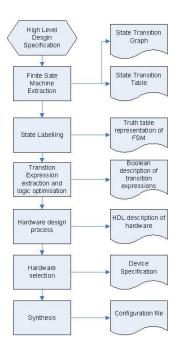

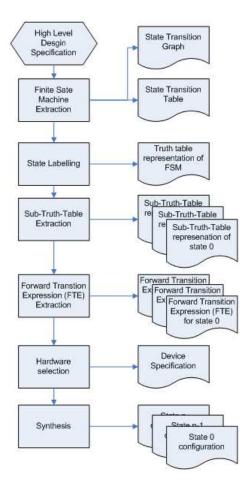

The implementation of FSMs can be broadly separated into two sections, the extraction of the FSM from the specification of the system and the implementation of the FSM using the appropriate technology. The FSM design flow for both full-custom ASIC and reconfigurable hardware devices is shown in figure 1. As this illustrates the extraction of the FSM is independent of the method of implementation and is hence common to both design flows.

Figure 1: Simplified FSM design flow for ASIC and Reconfigurable device

#### 2.2.1 Finite State Machine extraction

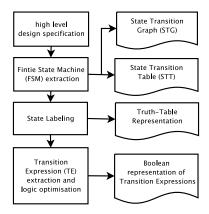

The conventional method of FSM extraction is shown in figure 2. As this shows a high level description of the control requirements of the proposed device are first extract from the initial specification of the system. This behaviour can then be expressed as an FSM using a high level model such as a State Transition Graph (STG) or State Transition Table (STT). Based on this model it is then possible to produce a description of the FSM suitable for the implementation of the control requirements of the system.

The following sections give details of each of the main stages in extraction of FSMs. For the purposes of clarity the Mead-Conway traffic light controller [11] will be used to provide a detailed worked example.

Figure 2: FSM extraction

### 2.2.2 State Transition Graph representation of Finite State Machines

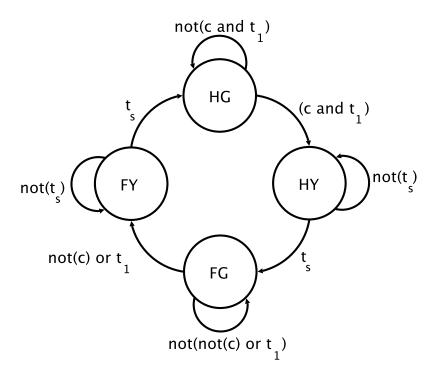

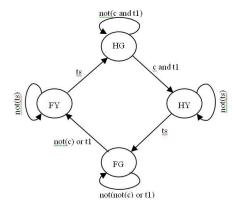

The State Transition Graph (STG) is a graphical representation of FSMs. The STG uses nodes to represent the states of the FSM and edges to represent state transitions. The output behaviour of the FSM is associated with the states as required and the edges are labeled with the input conditions necessary to cause transitions.

A sample STG of the classic Mead-Conway traffic light controller is shown in

figure 3. This is a simple 4-state (HG, HY, FG, FY) FSM, where |S| = 4, with an input alphabet of C,  $T_1$ ,  $T_s$ , |I| = 3. The STG shows each of the states and the state transitions, with each of the transitions labeled with the necessary input conditions to cause the transitions.

Figure 3: STG for Mead-Conway Traffic Light Controller [11]

The Mead-Conway traffic light controller represents the control system required to control the traffic lights at the crossroads between a field road and a highway. The system comprises a light on the highway (hl) and a light on the field (fl) with a crossing button (c) that is pressed to request the lights to change.

The system would usually be in the HG state where the highway lights are set to green and the field road lights are set to red. On entering this state a timer  $(t_1)$  is started. After this timer has expired and if the cross button (c) is pressed a state change is triggered to state HY.

In state HY a timer  $(t_s)$  is started and the highway light is set to yellow while the field light remains red. After a set time has passed another state transition is triggered to state FG.

In state FG the field road light is set to green and the highway light is set to red, a timer  $(t_1)$  is again set. If the button is released or the timer has finished a state change is triggered to state FY.

In state FY the field road light is set to yellow and the highway light remains red. A timer  $(t_s)$  is again set and the FSM returns to its start state on the expiry of this timer.

### 2.2.3 State Transition Table representation of Finite State Machines

An alternative to the STG is the State Transition Table (STT). The STT of the Mead-Conway traffic light controller is shown in table 1. The table shows each of the required state transitions of the FSM and gives the current state and input conditions required to cause these transitions. In this simple example there are only two possible transitions from each state and the conditions that cause these transitions are listed. The outputs produced by the FSM are listed in the table, it should be noted that it is customary to produce a hardware block responsible for implementing the FSM and a separate block that produces the outputs based on the current state of the FSM.

| current state | Inputs                    | Next State Outputs |                   |

|---------------|---------------------------|--------------------|-------------------|

| HG            | $not(c \text{ and } t_1)$ | $_{ m HG}$         | hl=GREEN; fl=RED  |

| HG            | c and $t_1$               | HY                 | hl=GREEN; fl=RED  |

| HY            | $\mathrm{not}(t_S)$       | HY                 | hl=YELLOW; fl=RED |

| HY            | $t_S$                     | FG                 | hl=YELLOW; fl=RED |

| FG            | $not(not(c) or t_1)$      | FG                 | hl=RED; fl=GREEN  |

| FG            | $not(c) \text{ or } t_1$  | FY                 | hl=RED; fl=GREEN  |

| FY            | $\mathrm{not}(t_S)$       | FY                 | hl=RED; fl=YELLOW |

| FY            | $t_S$                     | HG                 | hl=RED; fl=YELLOW |

Table 1: STT of Mead-Conway Traffic Light Controller

#### 2.2.4 State Labeling

To allow digital logic to implement the FSM it is necessary to perform state encoding. State encoding takes the symbolic representation, i.e. label, of the states and replaces it with a Boolean representation that can be produced using digital logic. Although a number of encoding methods exist, the most commonly used technique is binary encoding.

In binary encoding each state is given a unique binary code and this is associated with the state label as shown in table 2. Using binary encoding a hardware block with only  $log_2(|S|)$  outputs is capable of indicating the next state of an FSM with |S| states. This hardware block is responsible for calculating the next state of the FSM and producing the corresponding binary code at its outputs.

|             | Encoding |       |  |

|-------------|----------|-------|--|

| State Label | $Z_0$    | $Z_1$ |  |

| $_{ m HG}$  | 0        | 0     |  |

| HY          | 0        | 1     |  |

| FY          | 1        | 0     |  |

| FG          | 1        | 1     |  |

Table 2: Binary Encoding of State Labels

By replacing the labels in the STT with their binary equivalents, as given in table 2, it is possible to build a truth table representation of the FSM. Table 3 gives the truth table for the Mead-Conway traffic light controller. From this it can be seen that the STT presented in section 2.2.3 has been expanded to give all of the possible input conditions for each current state  $(Z_o(t), Z_1(t))$  and the next state  $(Z_o(t+1), Z_1(t+1))$  for each of these conditions has been specified.

Using a vector notation

$$\mathbf{Z} = (Z_0, Z_1), \ \mathbf{HG} = (0, 0), etc.$$

and using the shorthand  $(\mathbf{X} = \mathbf{Y})$  for  $\sum_{i} X_{i} \oplus Y$ , the generator expression for this

table can be written as:

$$\begin{split} \mathbf{Z}(t+1) &\triangleq \\ \mathbf{Z}(t) &= \mathbf{HG}.(\overline{c.t_1}.\mathbf{HG} + c.t_1.\mathbf{HY}) + \\ \mathbf{Z}(t) &= \mathbf{HY}.(\overline{t_s}.\mathbf{HY} + t_s.\mathbf{FG}) + \\ \mathbf{Z}(t) &= \mathbf{FG}.(\overline{c} + t_1.\mathbf{FG} + (\overline{c} + t_1).\mathbf{FY}) + \\ \mathbf{Z}(t) &= \mathbf{FY}.(\overline{t_s}.\mathbf{FY} + t_s.\mathbf{HG}) \end{split}$$

### 2.2.5 Transition Expression (TE) Extraction and Optimization

From the truth-table representation it is possible to extract the logic expressions required to implement the behaviour of the FSM. The extracted expressions are termed Transition Expressions (TE) as they calculate the required state transitions based on the primary inputs and the current state.

If the transition expression is expressed in sum-of-products format, each 1 in the output columns of the truth-table results in the addition of a product term to the TE. For the example shown in table 3 the logic expression required to calculate the next state  $Z_0(t+1)$  is

$$\mathbf{Z_0}(t+1) = \mathbf{Z_0}(t).\overline{\mathbf{Z_1}(t).c}.t_1.\overline{t_s} + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.t_1\overline{t_s}$$

$$+ \mathbf{Z_0}(t).\overline{\mathbf{Z_1}(t).c}.t_1.t_s + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.t_1.t_s$$

$$+ \mathbf{Z_0}(t).\overline{\mathbf{Z_1}(t)}.\overline{c}.\overline{t_1.t_s} + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.\overline{t_1t_s}$$

$$+ \mathbf{Z_0}(t).\overline{\mathbf{Z_1}(t)}.\overline{c}.t_1.\overline{t_s} + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.t_1\overline{t_s}$$

$$+ \overline{\mathbf{Z_0}(t)}.\mathbf{Z_1}(t).\overline{c}.t_1.t_s + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.\overline{t_1}.t_s$$

$$+ \overline{\mathbf{Z_0}(t)}.\mathbf{Z_1}(t).\overline{c}.t_1.t_s + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.t_1.t_s$$

$$+ \overline{\mathbf{Z_0}(t)}.\mathbf{Z_1}(t).\overline{c}.t_1.t_s + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.t_1.t_s$$

$$+ \overline{\mathbf{Z_0}(t)}.\mathbf{Z_1}(t).\overline{c}.t_1.t_s + \mathbf{Z_0}(t).\mathbf{Z_1}(t).\overline{c}.t_1.t_s$$

| current  |   | Primary |       |       | Next State |            |

|----------|---|---------|-------|-------|------------|------------|

| state    |   | Input   |       |       |            |            |

| $Z_0(t)$ |   |         | $t_1$ | $t_s$ | $Z_0(t+1)$ | $Z_1(t+1)$ |

| 0        | 0 | 0       | 0     | 0     | 0          | 0          |

| 0        | 0 | 0       | 0     | 1     | 0          | 0          |

| 0        | 0 | 0       | 1     | 0     | 0          | 0          |

| 0        | 0 | 0       | 1     | 1     | 0          | 0          |

| 0        | 0 | 1       | 0     | 0     | 0          | 0          |

| 0        | 0 | 1       | 0     | 1     | 0          | 0          |

| 0        | 0 | 1       | 1     | 0     | 0          | 1          |

| 0        | 0 | 1       | 1     | 1     | 0          | 1          |

| 0        | 1 | 0       | 0     | 0     | 0          | 1          |

| 0        | 1 | 0       | 0     | 1     | 1          | 1          |

| 0        | 1 | 0       | 1     | 0     | 0          | 1          |

| 0        | 1 | 0       | 1     | 1     | 1          | 1          |

| 0        | 1 | 1       | 0     | 0     | 0          | 1          |

| 0        | 1 | 1       | 0     | 1     | 1          | 1          |

| 0        | 1 | 1       | 1     | 0     | 0          | 1          |

| 0        | 1 | 1       | 1     | 1     | 1          | 1          |

| 1        | 0 | 0       | 0     | 0     | 1          | 0          |

| 1        | 0 | 0       | 0     | 1     | 0          | 0          |

| 1        | 0 | 0       | 1     | 0     | 1          | 0          |

| 1        | 0 | 0       | 1     | 1     | 0          | 0          |

| 1        | 0 | 1       | 0     | 0     | 1          | 0          |

| 1        | 0 | 1       | 0     | 1     | 0          | 0          |

| 1        | 0 | 1       | 1     | 0     | 1          | 0          |

| 1        | 0 | 1       | 1     | 1     | 0          | 0          |

| 1        | 1 | 0       | 0     | 0     | 1          | 0          |

| 1        | 1 | 0       | 0     | 1     | 1          | 0          |

| 1        | 1 | 0       | 1     | 0     | 1          | 0          |

| 1        | 1 | 0       | 1     | 1     | 1          | 0          |

| 1        | 1 | 1       | 0     | 0     | 1          | 1          |

| 1        | 1 | 1       | 0     | 1     | 1          | 1          |

| 1        | 1 | 1       | 1     | 0     | 1          | 0          |

| 1        | 1 | 1       | 1     | 1     | 1          | 0          |

Table 3: Truth-Table representation of the Mead-Conway traffic light controller

This expression can be optimized using boolean simplification techniques to remove redundant logic. This simplification process is well established and can be performed by tools such as SIS [5]. Performing boolean simplification on the above transition expression results in

$$\mathbf{Z_0}(t+1) = \mathbf{Z_0}(t)\overline{.t_s} + \mathbf{Z_1}(t).t_s$$

As this shows, the removal of redundant product terms, using boolean minimization techniques vastly reduces the size of the logic block required to implement the transition expressions and hence makes this a vital step in the extraction of the FSM.

### 2.2.6 ASIC implementation of FSMs

This process is commonly known as synthesis as it involves taking a high level description and converting this to a description that can be used to produce an ASIC capable of implementing the required functionality.

The implementation of a FSM in full-custom hardware involves first producing a description of the device in a hardware description language such as Verilog [10]. This is a hardware description language (HDL) that describes the functionality of the required device in a high level programming language that is capable of being used to produce a silicon implementation of the device.

Due to the mature nature of silicon implementation, many of the steps involved are hidden from the device designer and automatically carried out by design tools such as [1]. The tools can be used to perform synthesis of HDL to a format such as GDSII [2] that can be used by manufacturers to produce a silicon implementation.

Synthesis takes the HDL description of the FSM and converts this to a netlist format that expresses the hardware required to implement the HDL as well as the interconnects between these components. Extensive testing is then required to ensure that the device operates correctly prior to manufacture as any errors would be costly to correct if not detected early in the design cycle. The netlist is then further synthesised to produce a layout in GDSII format that is again tested and refined to ensure correct device operation before manufacture.

This project is not concerned with the details of the synthesis of HDL or the silicon implementation of devices and as such this section is not intended to detail this process, further information can be found in a number of texts including [8].

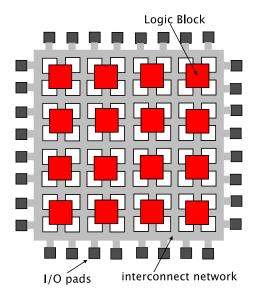

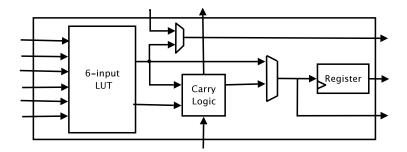

### 2.2.7 FSM implementation on a Reconfigurable Device

The conventional method of implementing an FSM on a reconfigurable device is shown in figure 4. The process outlined here is similar to the design-flow used in full-custom ASIC design of FSMs but, where as in full-custom design flows synthesis results in a description that can be used to produce a silicon implementation of the FSM, synthesis for reconfigurable devices results in a bit-stream capable of configuring the device to implement the FSM.

Figure 4: FSM implementation on a reconfigurable device

#### 2.2.7.1 Hardware selection

The selection of a suitable reconfigurable device is vital to the efficient implementation of the FSM. It is essential to ensure that the device has sufficient hardware resources to implement the FSM but does not introduce excessive redundant hardware. As the reconfigurable device is a generic part it is unlikely that the device will have exactly the correct amount of hardware required to implement a particular application. However, devices are available from device manufacturers in a wide range of sizes and costs, allowing the end-user to select the device most suitable for the chosen application.

Based on the high level description of the FSM it is possible to extract an estimate of the hardware requirements of the device required to implement the FSM. The end-user would then select the device with as close to these parameters as possible to ensure excessive hardware is not introduced that would impact on the cost, area and possibly power of the final implementation.

### 2.2.7.2 HDL Synthesis for reconfigurable devices

After the selection of the appropriate reconfigurable device the high level description of the FSM is then synthesised. Whereas synthesis to ASIC produces a silicon implementation of the FSM, synthesis to a reconfigurable device takes the high level description and produces the bit-stream required to program the device to implement the FSM. As each reconfigurable device has an individual structure and hardware characteristics, synthesis is usually performed by proprietary tools provided by the device manufacture. The results of the synthesis process is a file containing a series of bits that when stored in local memory on the device causes it to implement the required functionality.

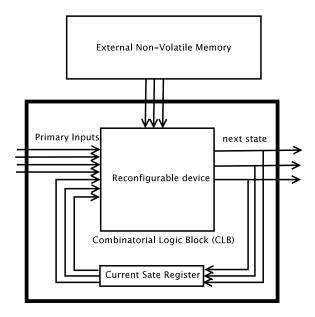

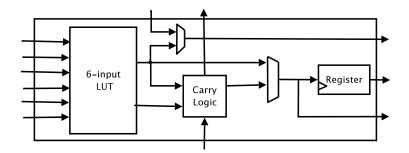

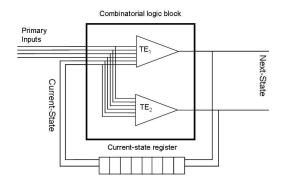

### 2.2.8 FSM operation on a reconfigurable device

The general hardware model of a FSM implemented in hardware is shown in figure 5. As this shows the FSM is implemented by a reconfigurable device, known as the Combinatorial Logic Block (CLB), responsible for implementing the TEs of the FSM and a feed back register used to store the current state of the FSM. The output of

this register is then required to be fed back to the inputs of the CLB as the current state is required to calculate the next state of the FSM.

Figure 5: General Hardware model of FSM using Reconfigurable hardware

On power up the configuration bit-file is loaded into the local memory within the reconfigurable device from non-volatile memory. This configures the reconfigurable device to implement the required transition expressions and the current state register. Although many commercial devices such as FPGAs have the ability to implement feedback within the reconfigurable fabric itself it should be noted that certain reconfigurable devices, such as [3], do not allow feedback, this means an external register is required and feedback must be done out with the actual reconfigurable device.

As algorithm 1 shows, after the required configuration is loaded onto the device the next state would be calculated using the current state, initially this would be a specified *reset* state, and the current inputs. The system would then be clocked and the next state stored as the current state in the current state register, this new current state would then be used to again calculate the next state before the device is again clocked. This means that the clock speed of the device is limited by the time

required for the device to calculate the next state and store it as the current state.

```

Algorithm 1 FSM operation on a reconfigurable device

WHILE{1}

current_state=reset_state

WHILE{reset=no}

next_State=transition_expression(current_sate, primary_inputs)

IF{next_state!= current_state}

current_state=next_state

ENDIF

ENDWHILE

ENDWHILE

```

## 3 Novel representation of FSMs for reconfigurable hardware

As illustrated the main fixed hardware component of the general implementation is the combinatorial logic block (CLB). This block is required to implement the TEs of the FSM. In order to reduce the hardware requirements of the FSM this block was targeted for optimisation to produce a reconfigurable hardware device specifically tailored for the implementation of FSMs.

#### 3.1 Investigation of characteristics of CLB

As the CLB implements the transition expressions (TEs) required to calculate the next state of the FSM from the primary inputs and the current state it is possible to calculate a number of the key characteristics of the block required to perform this function. The first of these is the number of outputs, if binary encoding is assumed, this is simply

$$O = \log_2(|S|)$$

It is also fairly trivial to show that, as feedback is required from the current state register, the total number of inputs to the combinatorial logic block is

$$I = I_p + O = I_p + \log_2(|S|)$$

As these equations show the inputs to the CLB can be divided into two categories. The first of these is the primary inputs; these are the input signals used to determine the next state transition and are necessary to the operation of the FSM. The remaining inputs are the feedback lines from the current state register. Consequently, if this feedback can be removed the total number of inputs to the array can be reduced by a factor of  $\log_2(|S|)$ , this in turn will lead to a reduction in the hardware required due to simplification of the expressions required to calculate the next state of the FSM.

#### 3.2 Removal of current state feedback

As a reconfigurable hardware device has the capability of altering its functionality through programming it is possible to remove the need for the current state to be fed back to the inputs. This can be achieved by using the current configuration of the reconfigurable device to store the current state of the FSM, i.e. creating an individual configuration, or context, for each state of the FSM.

This method relies on the concept of calculating what state the FSM should move to compared to the traditional approach where by each state calculates if the FSM should enter this state. In this way this method directly calculates the next state of the FSM.

As this process calculates which state the FSM should move to, the contexts required to be loaded onto the reconfigurable device are known as FORWARD TRANSITION EXPRESSIONS (FTEs). The following section describes the derivation of these FTEs for the Mead-Conway example shown in figure 3.

#### 3.2.1 Derivation of FTEs for Mead-Conway traffic light FSM

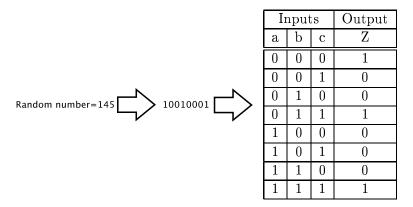

If the example of the Mead-Conway traffic light controller is again considered it can be seen that the truth-table shown in table 3 can be partitioned into sections that define the behaviour of the FSM when the FSM is known to be in a particular state. This is achieved by partitioning the truth-table into sections that contain all transitions *from* a particular state. In this example the truth-table is partitioned into four sub-truth-tables (one for each state) each of three inputs. Tables 4-7 show each of the sub-truth-tables for the Mead-Conway traffic light controller.

If the FSM is assumed to be in the HG state the following expressions can be used to calculate the next state:

$$\mathbf{Z}(\mathbf{t}) = \mathbf{HG} \quad \Rightarrow$$

$$\mathbf{Z}(t+1) \quad \triangleq \quad \overline{c.t_1}.\mathbf{HG} + c.t_1.\mathbf{HY}$$

Substituting the actual state labels yields:

$$Z_0(t+1) = 0; Z_1(t+1) = c.t1$$

If these expressions are analysed it can be seen that the next state is now a function of only the primary inputs. If these expressions are implemented on the reconfigurable device they are capable of indicating the state the FSM should enter at the next state transition.

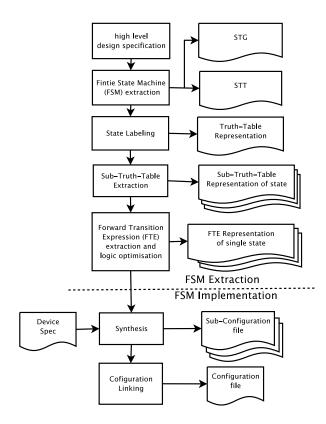

# 4 FSM implementation on a custom reconfigurable architecture

The design flow for the implementation of FSM using the custom method suggested is shown in figure 6. As this shows the derivation of the truth table representation

| Pri | Primary Input |    | Next State |            |

|-----|---------------|----|------------|------------|

| С   | t1            | ts | $Z_0(t+1)$ | $Z_1(t+1)$ |

| 0   | 0             | 0  | 0          | 0          |

| 0   | 0             | 1  | 0          | 0          |

| 0   | 1             | 0  | 0          | 0          |

| 0   | 1             | 1  | 0          | 0          |

| 1   | 0             | 0  | 0          | 0          |

| 1   | 0             | 1  | 0          | 0          |

| 1   | 1             | 0  | 0          | 1          |

| 1   | 1             | 1  | 0          | 1          |

Table 4: Sub-truth-tables for state HG

| Pri | mary | / Input             | Next State |            |

|-----|------|---------------------|------------|------------|

| С   | t1   | $\operatorname{ts}$ | $Z_0(t+1)$ | $Z_1(t+1)$ |

| 0   | 0    | 0                   | 0          | 0          |

| 0   | 0    | 1                   | 1          | 0          |

| 0   | 1    | 0                   | 0          | 0          |

| 0   | 1    | 1                   | 1          | 0          |

| 1   | 0    | 0                   | 0          | 0          |

| 1   | 0    | 1                   | 1          | 0          |

| 1   | 1    | 0                   | 0          | 0          |

| 1   | 1    | 1                   | 1          | 0          |

Table 6: Sub-truth-tables for state FY

| Pri | Primary Input |    | Next State |            |

|-----|---------------|----|------------|------------|

| С   | t1            | ts | $Z_0(t+1)$ | $Z_1(t+1)$ |

| 0   | 0             | 0  | 0          | 1          |

| 0   | 0             | 1  | 1          | 1          |

| 0   | 1             | 0  | 0          | 1          |

| 0   | 1             | 1  | 1          | 1          |

| 1   | 0             | 0  | 0          | 1          |

| 1   | 0             | 1  | 1          | 1          |

| 1   | 1             | 0  | 0          | 1          |

| 1   | 1             | 1  | 1          | 1          |

Table 5: Sub-truth-tables for state HY

| Pri | mary | / Input             | Next State |            |

|-----|------|---------------------|------------|------------|

| С   | t1   | $\operatorname{ts}$ | $Z_0(t+1)$ | $Z_1(t+1)$ |

| 0   | 0    | 0                   | 1          | 0          |

| 0   | 0    | 1                   | 1          | 0          |

| 0   | 1    | 0                   | 1          | 0          |

| 0   | 1    | 1                   | 1          | 0          |

| 1   | 0    | 0                   | 1          | 1          |

| 1   | 0    | 1                   | 1          | 1          |

| 1   | 1    | 0                   | 1          | 0          |

| 1   | 1    | 1                   | 1          | 0          |

Table 7: Sub-truth-tables for state FG

of the FSM from the high level specification of the system is the same as that for the full-custom and conventional reconfigurable implementation shown in figure 1. However, after the truth-table representation is produced the sub-truth-tables are extracted to produce |S| sub-truth-tables. The information contained in each of sub-truth-tables is sufficient to derive the *Forward Transitions Expressions* for each state of the FSM.

FTE extraction is performed to produce a set of boolean expressions capable of calculating the next state of the FSM. This process is similar to the conventional TE extraction process except that, due to the removal of feedback, this process results in simplified boolean expressions that depend only on the primary inputs. As the

Figure 6: Hardware design flow of a FSM for Custom Reconfigurable Device

CLB is required to produce the binary code necessary to indicate the next state, FTE extraction results in  $log_2(|S|)$  boolean expressions for each state of the FSM.

The FTEs would then be synthesised using the appropriate synthesis tool for the family of devices selected by the designer for implementation of the CLB. This synthesis results in a bit-file that is capable of configuring the CLB to calculate the next state of the FSM based on only the primary inputs. At this stage it is then possible to calculate the hardware resources required within the CLB in order to implement the FTEs, this would be the maximum hardware required by any individual context. The device from the family of devices used with the closest hardware resources to this would then be selected in order to reduce the amount of redundant hardware in the final device.

After the final device has been selected it may be necessary to re-synthesis the

FTES in order to produce configuration files specifically for this device. After the configuration files for each state have been produced the final stage is to link these files together into a single bit-file that can be loaded into the local configuration memory of the device.

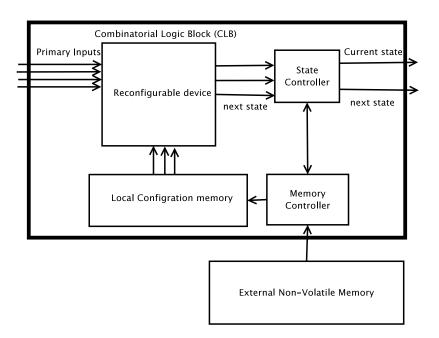

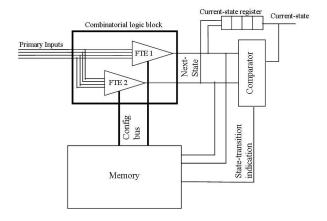

#### 5 Reconfigurable device for the implementation of FTEs

As the device required to implement FSMs using FTEs is required to alter its configuration at each state change the reconfigurable device used to implement the CLB must be rapidly reconfigurable. For this reason a local configuration memory is required to be closely coupled to the CLB.

Figure 7: Custom Reconfigurable device for implementation of FSMs

The overall architecture of the device is shown in figure 7. Similarly to the general model shown in figure 5 this model contains a reconfigurable device used for the implementation of the FTEs. Due to the need to perform rapid run-time reconfiguration a local configuration memory has been added to provide local storage

for the configuration file of the FSM. However, the main difference between this device and the traditional model is the addition of state and memory controllers responsible for detecting if a state change is required to take place and the selection of the configuration required to implement the next state of the FSM. After this new configuration has been loaded the next state would again be calculated at the next state transition based on the new context of the device.

During development of this device the similarity between this and a general purpose processor was noted. It would be possible for an external source to load the local configuration memory during operation of the device. In this way new "states" could be added to the FSM during operation allowing it adapt to the operating conditions of the device. In this way new states would be similar to instructions sent to the processor. The device would then enter one of these new states and determine which should be the next state in a very similar to branch statements on a general purpose processor. The device would then output the next state in a similar way to how a processor would present the result of a calculation and based on this new custom instructions/states could be loaded as required.

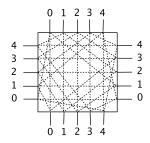

#### 5.0.2 Combinatorial Logic Block (CLB)

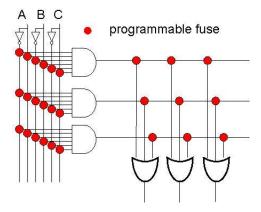

The CLB is a reconfigurable device used to implement the FTEs of the FSM. This fact allows us to determine a number of characteristics of the block required to implement these expressions as discussed in section 3.1. The reconfigurable device must be capable of implementing combinatorial logic expressions and due to the removal of current state feedback the number of inputs to the block is equal to the number of primary inputs (|I|) and the number of outputs required is  $log_2(|S|)$ . Due to the context changes required during state changes the device must also exhibit very low reconfiguration times as this dictates the maximum rate at which state changes can take place.

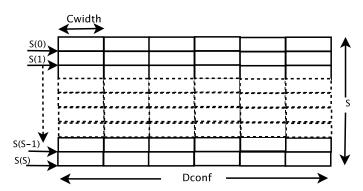

The reconfiguration time  $(C_t)$  of the device is a function of the clock rate  $(C_{rate})$ , configuration bus width  $(C_{width})$  and the amount of data  $(D_{conf})$  required to configure the device. One suggested method of configuring the device is with the aid of scan chains, these are registers chained together in series similar to a shift register used to store configuration data. In the case of memory based reconfigurable devices these registers are the memory components of the reconfigurable devices itself chained together in series. In this way blocks of data blocks equal to the width of the configuration bus  $(C_{width})$  are loaded onto the device in each clock cycle and this data is then shifted through each configuration register until all of the data required to configure the device has been loaded. If it is assumed that a single clock cycle is required to write each block of data to the device it is possible to calculate the reconfiguration time of the device using the expression

$$C_t = \frac{D_{conf}}{C_{width} * C_{rate}}$$

Based on this expression it can be seen that, as the clock rate of the configuration bus is dependent on the technology used to implement the device and is hence out with the control of the device designer, the designer can control the configuration times of the device in one of two ways, either the size of the configuration bus can be altered or the amount of data can be adjusted.

By varying the width of the configuration bus the size of the data chunks written to the device in each clock cycle can be adjusted and hence adjust the overall configuration time of the device. In order to reduce the configuration time it is suggested that as wide a bus as possible be used to program the configuration memory of the reconfigurable device but it should be noted that this increase in bus width will lead to an increase in the overall size of the device. This means the design of a suitable device becomes a trade off between the reconfiguration time of the device and the overall size of the device.

The amount of data required to configure the device is dependent on the size of the device or the amount of configurable elements in the reconfigurable array. This means it is important to ensure that the smallest array possible be used to implement the FTEs as this not only affects the configuration time of the device but also the area and possibly power of the resultant device. Due to the use of FTEs the array required to implement FSMs is far smaller than would be required using the TE approach. This is due to the fact that, using the FTE approach, only the expressions for a *single* state are required to be implemented concurrently where as for the TE approach the expressions of *each* state must be implemented concurrently. In this way it is hoped that the reduction in hardware will result in reduced configuration times.

Figure 8: Configuration Memory Structure

#### 5.0.3 Configuration memory

The configuration memory is responsible for storage of the configuration file required to implement an FSM using the FTE based approach. The memory must thus be capable of storing |S| distinct configurations each of  $D_{conf}$  bits in length, where  $D_{conf}$  is the number of bits of data required to program the CLB. Using this it is possible to calculate the overall size of the memory block  $(M_{size})$  required to implement an FSM using the identity

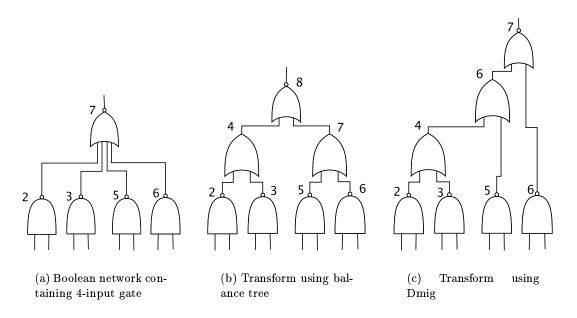

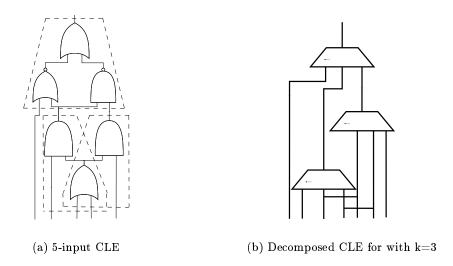

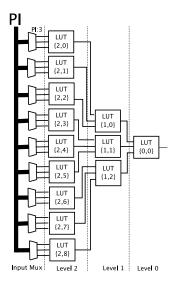

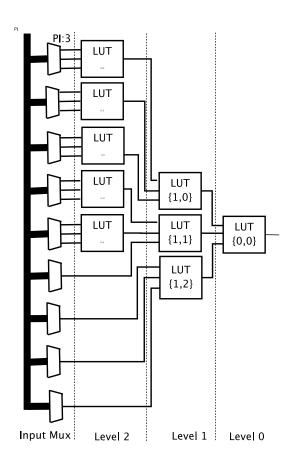

$$M_{size} = D_{conf} * |S|$$