Wang, Jue (2014) Monolithic microwave/millimetrewave integrated circuit resonant tunnelling diode dources with around a milliwatt output power. PhD thesis.

http://theses.gla.ac.uk/5149/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# $\label{lem:monolithic Microwave/Millimetrewave Integrated Circuit} \\ Resonant Tunnelling Diode Sources with around a \\ \\ Milliwatt Output Power \\ \\$

Jue Wang

School of Engineering

University of Glasgow

A thesis submitted in fulfilment of the requirements

for the degree of

**Doctor of Philosophy**

February, 2014

©Jue Wang, 2014

This thesis is dedicated to my loving parents Jian Yang Wang and  ${\it Chang Jiang~Wang}.$

献给我的父亲(王建阳)&母亲(王长江)

### Acknowledgements

I would like to express great appreciation to my supervisor, Dr. Edward Wasige, who offered me this precious opportunity to do research on the project three years ago. The way of scientific researching is full of challenges but as my research advisor, his positive attitude, valuable advice and great patience encouraged me going through any difficulties in both research and life.

I would like to thank Dr. Liquan Wang. With his great preceding work and very wise ideas, my research achieved fruitful results. Discussions with him clarified many questions that puzzled me. Special thanks to Dr. Chong Li for benefiting from his expertise in millimeter-wave engineering. He was very supportive whenever help was needed, and his experience in RF measurement helped me through complicated measurements and sorted out practical problems no matter how small.

I also would like to thank the James Watt Nanofabrication Centre (JWNC) staff: Linda Pollock, David Gourlay, Robert Harkins, Douglas Lang, Helen McLeland, Haiping Zhou, Xu Li, etc for their valuable advice on fabrication processes.

I wish to thank Prof. John Davies for the discussions on quantum physics and great thanks to my colleagues in the High Frequency Electronics Group: Salah Sharabi, Afesomeh Ofiare, Abdullah Al-Khalidi, Raphael Brown and Dr. Douglas Macfarlane. Also to Khalid Alharbi, Dr. Stephen Russell and Dr. Ata Khalid for reviewing this thesis and providing precious suggestions.

Last but definitely not least, special thanks go to my parents JianYang Wang and ChangJiang Wang and my girl friend ZiHui Wu, without their consistent support, I would not walk so far on this researching road.

### Abstract

Resonant tunnelling diode (RTD) oscillators are considered to be one of the most promising solid-state terahertz sources which can operate at room temperature. The main limitation of RTD oscillators up to now is their low output power. For the published terahertz (THz) RTD oscillators, the output power is in the range of micro-Watts ( $\mu$ W). This thesis describes systematic work on RTD device modelling, and on the design, fabrication and measurement of high power monolithic microwave integrated circuit (MMIC) RTD oscillators.

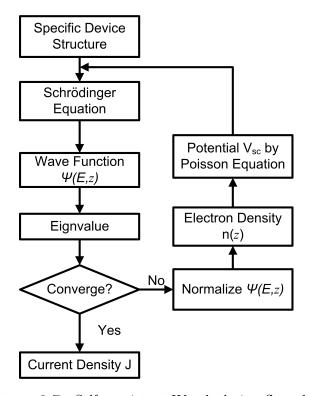

The RTD device consists of a narrow bandgap layer (quantum well) sandwiched between two thin wide bandgap layers (barriers). When the device is biased, electrons with kinetic energy lower than the barriers may tunnel through the double barrier-quantum well (DBQW) structure, and the device exhibits a negative differential resistance (NDR) in this case. To investigate this phenomenon, a new numerical model based on quantum mechanics was developed. The model involves self-consistent solving of the Schrödinger equation until the quasi-eigen energy state converges. This model is expected to serve to optimize the RTD device structure for millimetre-wave and terahertz applications.

Besides RTD device modelling, the fabrication process for single devices and for MMIC RTD oscillator circuits was developed and optimized on this project. Optical lithography, wet/dry etching and metallization were the main fabrication techniques utilized. For device sizes of a few square microns, the fabrication process required the development of new steps, i.e, via opening through polyimide. The fabrication process was optimized and high yield was obtained.

On this project, one of the challenges was to realize RTD oscillators in the form of MMICs, aiming at about 100 GHz with milli-Watts output power, in accordance with a recently proposed power combining circuit topology. To accomplish such an oscillator, proper design of passive components was essential. On this project, these components included  $50\Omega$  coplanar waveguides (CPW), shorted CPW stubs, metal-insulator-metal (MIM) capacitors and thin film resistors. The design procedure for these components is described, and their performance characterized by DC or scattering parameter measurements as appropriate. Two types of MMIC RTD oscillator layouts were designed, fabricated and characterized. Details are described in this thesis. Measurement results showed that for the fabricated 75 GHz oscillator, the output power obtained was -0.2 dBm (0.96 mW), and for the 86 GHz oscillator, the measured output power was  $-4.6 \ dBm$ (0.35 mW), both of which, to the author's knowledge, were the highest power for published indium phosphide (InP)-based RTD oscillators operating in the W-band frequency range.

### **Publications**

- [1] **J. Wang** and E. Wasige, "Self-consistent Analysis of the IV characteristics of Resonant Tunnelling Diodes," *Terahertz Science and Technology*, Vol.5, No.4, pp. 153-162, Dec. 2012.

- [2] **J. Wang**, L. Wang, C. Li, B. Romeira and E. Wasige, "28 GHz MMIC Resonant Tunneling Diode Oscillator of around 1mW Output Power," *Electronics letters*, vol. 49, No.13, pp. 816-818, Jun.2013.

- [3] **J. Wang**, L. Wang, C. Li, D. Cumming and E. Wasige, "Novel Resonant Tunnelling Diode Oscillator with High Output Power," *UK Semiconductor conference 2013*, Sheffield Hallam University, Jul. 2013.

- [4] **J. Wang** and E. Wasige, "IV characteristics of Resonant Tunnelling Diodes investigated by a numerical model based on semiconductor physics," *HETECH (Heterostructure Technology) 2013*, University of Glasgow, Sep.2013.

- [5] J. Wang, L. Wang, C. Li, K. Alharbi, A. Khalid and E. Wasige, "W-band InP-based Resonant Tunnelling Diode Oscillator with Milliwatt Output Power," The 26th International Conference on Indium Phosphide and Related Materials, Montpellier, France, May, 2014.

- [6] L. Chong, J. Grant, **J. Wang** and D. Cumming, "A Nipkow disk integrated with Fresnel lenses for terahertz single pixel imaging," *Optics Express*, vol 21, No. 21, pp. 24452-24459, Oct.2013.

# Contents

| C  | Contents |                                                |    |  |

|----|----------|------------------------------------------------|----|--|

| Li | st of    | Figures                                        | xi |  |

| 1  | TH       | z Technology: Sources                          | 1  |  |

|    | 1.1      | Introduction                                   | 1  |  |

|    | 1.2      | THz Sources                                    | 3  |  |

|    | 1.3      | State of the Art                               | 10 |  |

|    | 1.4      | Project Organization and Aim                   | 13 |  |

| 2  | Self     | C-Consistent RTD Numerical Model               | 16 |  |

|    | 2.1      | Introduction                                   | 16 |  |

|    | 2.2      | Heterojunction                                 | 19 |  |

|    | 2.3      | RTD Material Systems                           | 20 |  |

|    |          | 2.3.1 III-V Based RTDs                         | 21 |  |

|    |          | 2.3.2 Silicon-based RTDs                       | 25 |  |

|    | 2.4      | Operating Principle of RTD                     | 26 |  |

|    | 2.5      | Self-Consistent RTD Numerical Model            | 29 |  |

|    |          | 2.5.1 Finite Quantum Well Schrödinger Equation | 30 |  |

|   |     | 2.5.2   | Normalized Wave Function                | 42 |

|---|-----|---------|-----------------------------------------|----|

|   |     | 2.5.3   | Electron Density and Poisson's Equation | 42 |

|   |     | 2.5.4   | Simulation Results and Discussion       | 46 |

|   |     | 2.5.5   | Summary                                 | 50 |

| 3 | Fab | ricatio | on Processes and RTD MMIC Technology    | 51 |

|   | 3.1 | Introd  | luction                                 | 51 |

|   | 3.2 | Gener   | al Fabrication Steps                    | 52 |

|   |     | 3.2.1   | Optical Lithography                     | 55 |

|   |     | 3.2.2   | Metallisation and Lift-off              | 58 |

|   |     | 3.2.3   | Dielectric Deposition                   | 62 |

|   |     | 3.2.4   | Wet Etching and Dry Etching             | 63 |

|   | 3.3 | Proces  | ss Module Development                   | 64 |

|   |     | 3.3.1   | Via Opening Process                     | 65 |

|   |     | 3.3.2   | Fabricated RTD Devices                  | 70 |

|   | 3.4 | RTD (   | Oscillator MMIC Processes               | 71 |

|   | 3.5 | Summ    | ary                                     | 73 |

| 4 | Pas | sive C  | omponents and Ohmic Contacts            | 74 |

|   | 4.1 | Introd  | uction                                  | 74 |

|   | 4.2 | Design  | n of Passive Components                 | 75 |

|   |     | 4.2.1   | Coplanar Waveguide (CPW)                | 75 |

|   |     | 4.2.2   | Metal-Insulator-Metal (MIM) Capacitor   | 80 |

|   |     | 4.2.3   | Thin Film Resistor                      | 81 |

|   | 4.3 | Chara   | cterisation of Passive Components       | 84 |

|   |     | 4 3 1   | Coplanar Waveguide                      | 85 |

### CONTENTS

|   |     | 4.3.2 MIM Capacitors                                    |

|---|-----|---------------------------------------------------------|

|   |     | 4.3.3 Thin Film Resistor (NiCr)                         |

|   | 4.4 | Metal-Semiconductor Ohmic Contact                       |

|   | 4.5 | Summary                                                 |

| 5 | MN  | MIC RTD Oscillator Design 95                            |

|   | 5.1 | Introduction                                            |

|   | 5.2 | Characteristics of RTD                                  |

|   | 5.3 | DC Stability and Device Sizing                          |

|   | 5.4 | Single RTD Oscillators                                  |

|   | 5.5 | Double RTD Oscillator Circuits and Layouts              |

|   |     | 5.5.1 Double RTD Oscillator Layout (Type I)             |

|   |     | 5.5.2 Double RTD Oscillator Layout (Type II)            |

|   | 5.6 | Summary                                                 |

| 6 | Dev | vice/Oscillator Measurement and Characterisation 116    |

|   | 6.1 | Introduction                                            |

|   | 6.2 | DC Measurement                                          |

|   |     | 6.2.1 Measured and Simulated RTD I-V Characteristic 119 |

|   |     | 6.2.2 RTD Large Signal Model                            |

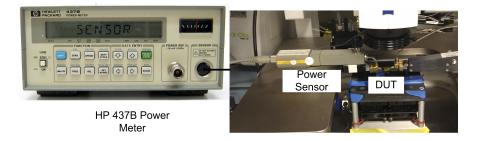

|   | 6.3 | Frequency and Power Measurement                         |

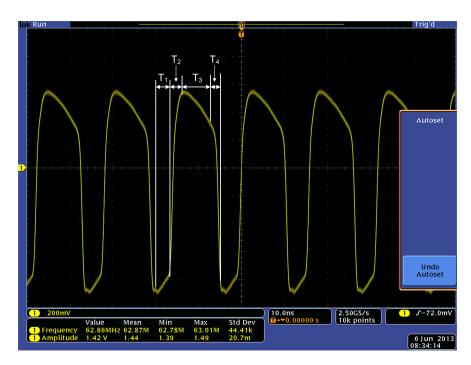

|   |     | 6.3.1 Type I Oscillator Measurement                     |

|   |     | 6.3.2 Type II Oscillator Measurement                    |

|   |     | 6.3.3 Discussion                                        |

|   | 6.4 | Summary 129                                             |

### CONTENTS

| 7                         | Con                               | clusion | as and Future Work                         | 135 |  |

|---------------------------|-----------------------------------|---------|--------------------------------------------|-----|--|

|                           | 7.1                               | Conclu  | sions                                      | 135 |  |

|                           | 7.2                               | Future  | Work                                       | 137 |  |

|                           |                                   | 7.2.1   | Higher Frequency with High Power           | 137 |  |

|                           |                                   | 7.2.2   | Device Fabrication                         | 137 |  |

|                           |                                   | 7.2.3   | Device Characterisation                    | 138 |  |

| $\mathbf{A}_{\mathbf{l}}$ | Appendix A. Fabrication Process 1 |         |                                            |     |  |

| Aı                        | pen                               | dix B.  | Relaxation Oscillations                    | 147 |  |

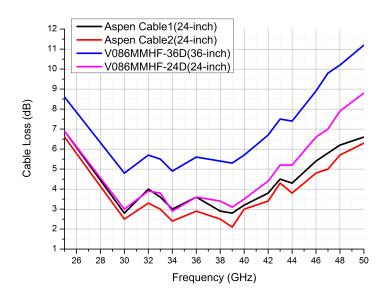

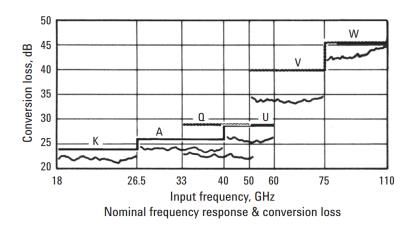

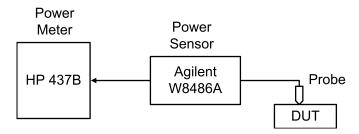

| Aı                        | ppen                              | dix C.  | Oscillator Frequency and Power Measurement | 151 |  |

| Aı                        | ppen                              | dix D.  | List of Symbols                            | 158 |  |

| $_{ m Bi}$                | bliog                             | raphy   |                                            | 163 |  |

# List of Figures

| 1.1  | Frequency and wavelength spectra of electromagnetic waves                   | 1  |

|------|-----------------------------------------------------------------------------|----|

| 1.2  | Simplified schematic diagram of typical laser                               | 4  |

| 1.3  | Schematic diagram of a far-infrared (FIR) $\mathrm{CO}_2$ laser             | 5  |

| 1.4  | Schematic diagram of a gyrotron                                             | 5  |

| 1.5  | Schematic diagram of a backward-wave oscillator (BWO)                       | 6  |

| 1.6  | The schematic circuit of negative differential resistance oscillator.       | 8  |

| 1.7  | Schematic cross-section of a quasi-optical RTD oscillator                   | 10 |

| 1.8  | Schematic diagram of a slot antenna- RTD oscillator                         | 11 |

| 1.9  | Schematic circuit of a RTD slot antenna oscillator                          | 12 |

| 1.10 | State of the art RTD oscillator development                                 | 13 |

| 2.1  | The schematic layer structure of an InP-based RTD device em-                |    |

|      | ployed in this project.                                                     | 17 |

| 2.2  | The schematic conduction band diagram of a double barrier quan-             |    |

|      | tum well (DBBQW) RTD device. $E_f^L$ and $E_f^R$ denote the Fermi           |    |

|      | level of the left and right contact layer. $E_{r1}$ and $E_{r2}$ denote the |    |

|      | quantized resonate state in the quantum well                                | 18 |

| 2.3  | The simplified MBE growth system.                                           | 20 |

| 2.4  | Direct $\Gamma(\text{solid line})$ and indirect $X(\text{dashed line})$ band gaps of the |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | alloys of the semiconductor binaries GaAs, AlAs and InAs, plotted                        |     |

|      | versus their lattice parameters for all mole fractions $x$                               | 21  |

| 2.5  | Conduction band diagram of DBQW under different bias voltage<br>(V $_b)$ :               | (a) |

|      | no bias applied (b) threshold bias (c) resonant tunnelling (d) off                       |     |

|      | resonance. $E_f^L$ and $E_f^R$ are the Fermi level of left emitter layer and             |     |

|      | right collector layer respectively. $E_c^L$ and $E_c^R$ are the conduction               |     |

|      | band edge of the emitter and collector. $E_{r1}$ and $E_{r2}$ represent the              |     |

|      | resonant energy state in the quantum well                                                | 27  |

| 2.6  | The schematic current-voltage(I-V) characteristic of a RTD device.                       |     |

|      | $V_p$ is the bias voltage associated with the peak current $I_p$ , while $V_v$           |     |

|      | denotes the bias voltage associated with the valley current $I_v$                        | 28  |

| 2.7  | Self-consistent IV calculation flow chart                                                | 29  |

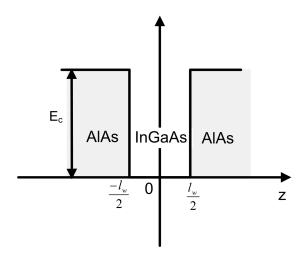

| 2.8  | The schematic conduction band diagram of InGaAs/AlAs with in-                            |     |

|      | finite barriers (AlAs) width. No external bias voltage is applied                        | 31  |

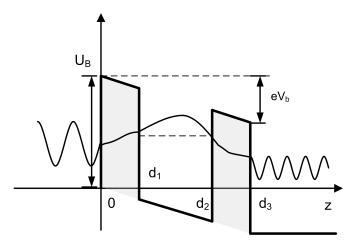

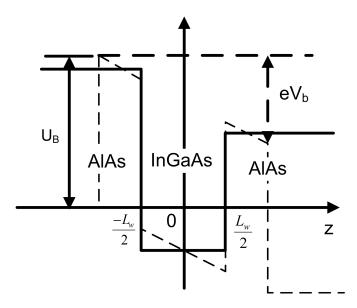

| 2.9  | RTD conduction band diagram under a bias voltage $V_b$ . $U_B$ is the                    |     |

|      | barrier energy height                                                                    | 35  |

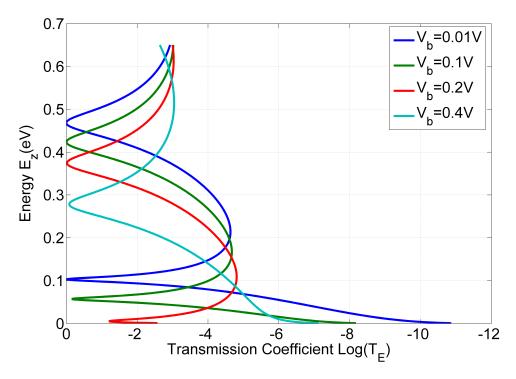

| 2.10 | Calculated transmission coefficient $(T_E)$ as a function of the energy                  |     |

|      | $(E_z)$ with different bias voltage $V_b$ for the DBQW structure shown                   |     |

|      | in Figure 2.1                                                                            | 41  |

| 2.11 | The approximation of an RTD conduction band. The linearly vary-                          |     |

|      | ing energy potential (dotted line) was replaced with a flat constant                     |     |

|      | potential (solid line). The approximation will benefit integrating                       |     |

|      | wave function.                                                                           | 43  |

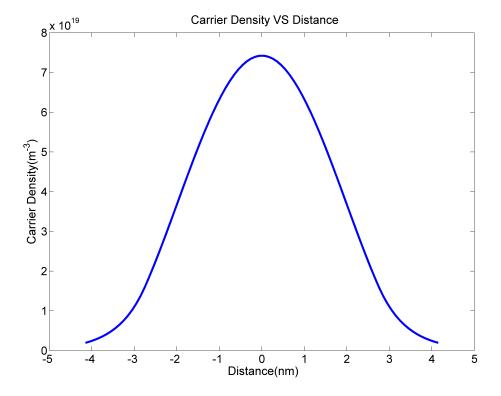

| 2 12 | Calculated distribution of electron density                                              | 44  |

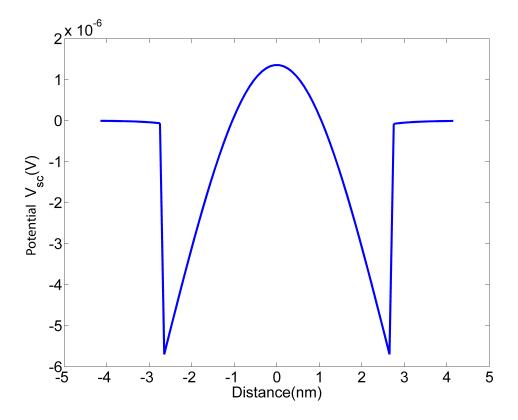

| 2.13 | The calculated potential $(V_{sc})$ due to the electron distribution        | 45    |

|------|-----------------------------------------------------------------------------|-------|

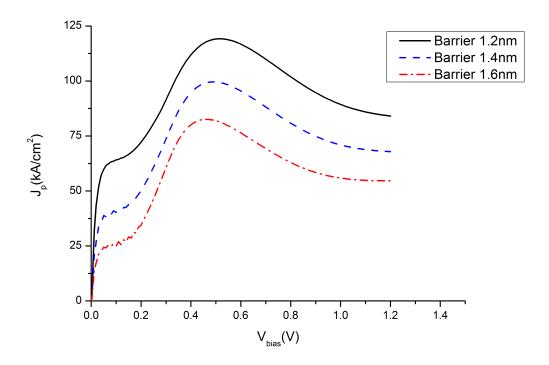

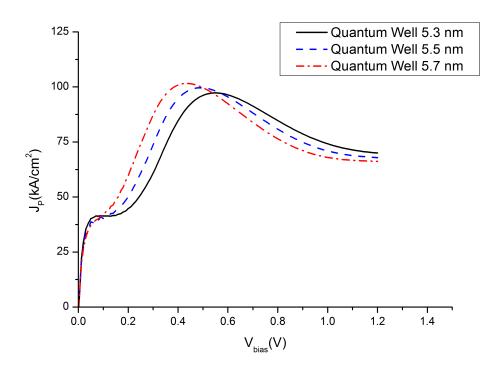

| 2.14 | Simulated current density as a function of bias voltage for differ-         |       |

|      | ent barriers width (1.2 $nm$ , 1.4 $nm$ , 1.6 $nm$ ). The quantum well      |       |

|      | thickness is 5.5 $nm$ . The barrier height is 0.65 $eV$                     | 47    |

| 2.15 | Simulated current density as a function of bias voltage for differ-         |       |

|      | ent quantum well width $(5.3\ nm,\ 5.5\ nm,\ 5.7\ nm)$ . The barrier        |       |

|      | thickness is 1.4 $nm$ . The barrier height is 0.65 $eV$                     | 48    |

| 2.16 | Simulated current density as a function of bias voltage for different       |       |

|      | barrier heights (0.55 $eV$ , 0.60 $eV$ , 0.65 $eV$ ). The barrier thickness |       |

|      | is 1.4 $nm$ . The quantum well is 5.5 $nm$                                  | 49    |

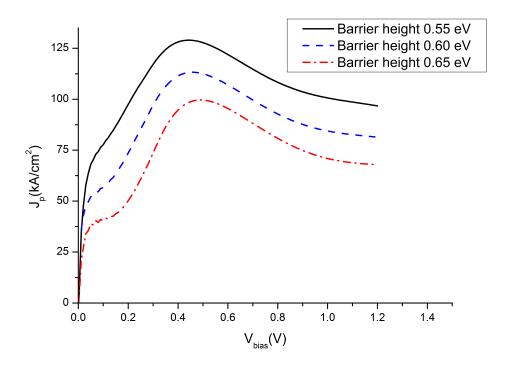

| 2.17 | Calculated I-V characteristics of an InGaAs/AlAs RTD (mesa size $$          |       |

|      | $5\times 5~\mu m^2$ ) with/without considering the contact resistance       | 50    |

| 3.1  | The schematic layer structure of an RTD device (b) with layer               |       |

|      | information (a). $\ldots$                                                   | 53    |

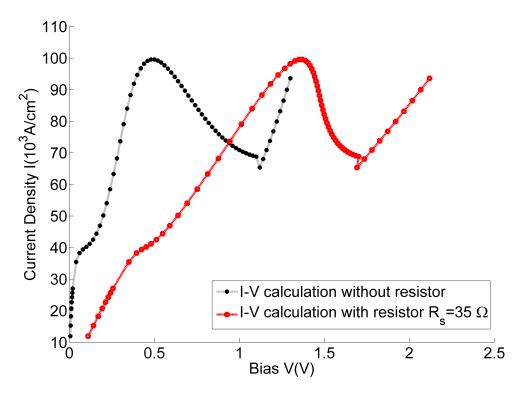

| 3.2  | A single RTD device fabrication flow diagram: (a) Pattern emitter           |       |

|      | metal contact. (b) Wet etch to collector layer. (c) Pattern col-            |       |

|      | lector metal contact. (d) Wet etch to substrate (InP). (e) Deposit          |       |

|      | polymer (PI-2545) and open a via by dry etching. (f) Pattern bond           |       |

|      | metal pads                                                                  | 54    |

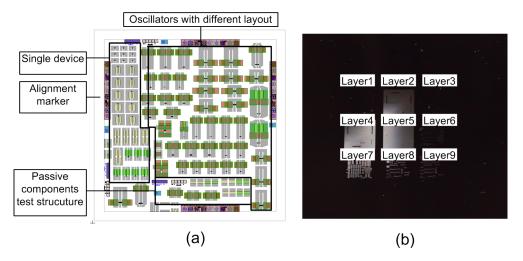

| 3.3  | Optical Mask for RTD oscillators. (a)Mask layout designed by L-             |       |

|      | Edit software. 9 different layers are superimposed on each other.(b)Fir     | ished |

|      | mask plate with 9 layers placed sequentially                                | 57    |

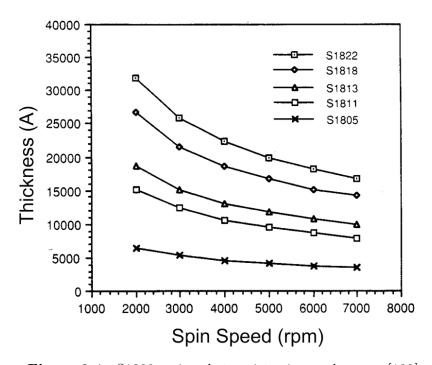

| 3.4  | S1800 series photoresist spin speed curves                                  | 59    |

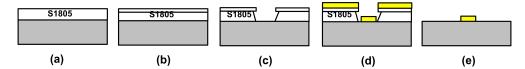

| 3.5  | Single layer lift off process: (a) Coat and prebake photoresist on the                           |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | sample (b) Soak in Chlorobenzene<br>(C $_6{\rm H}_5{\rm Cl})$ (c) Expose and develop             |    |

|      | the photoresist. Due to different dissolving rates, an overhang                                  |    |

|      | profile is ensured (d) Metallisation (e) Lift off                                                | 60 |

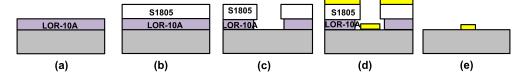

| 3.6  | Dual layer lift off process:(a) Coat and prebake LOR-10A (b) Coat                                |    |

|      | and prebake photoresist over LOR-10A (c) Expose and develop                                      |    |

|      | both photoresist and LOR-10A (d) Metallisation. The re-entrant                                   |    |

|      | profile ensures film discontinuity (e) Lift off                                                  | 61 |

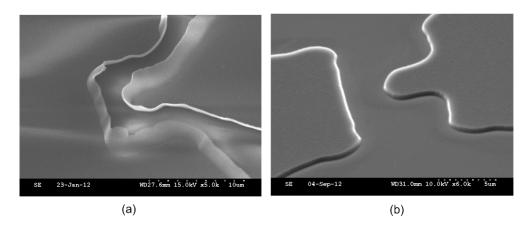

| 3.7  | Metal edge profile comparison between single and dual layer lift off.                            |    |

|      | (a) Single-layer (S1818) lift-off. After coating S1818, the sample                               |    |

|      | was soaked in chlorobenzene for 8 minutes. The thickness of Al                                   |    |

|      | deposited was 200 nm. (b) Dual-layer(LOR10A/S1818) lift-off.                                     |    |

|      | After coating and pre-baking LOR10A, photoresist S1818 was spun                                  |    |

|      | and pre-baked. After exposure and development, the thickness of                                  |    |

|      | Al deposited was 500 nm                                                                          | 62 |

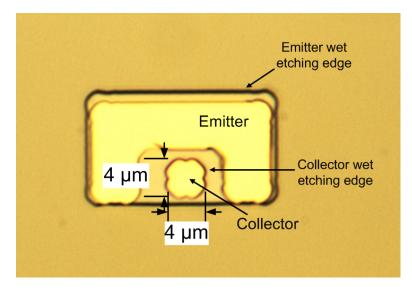

| 3.8  | The micrograph of an RTD device after wet etching. The central                                   |    |

|      | mesa size is about $4 \times 4 \mu m^2$                                                          | 64 |

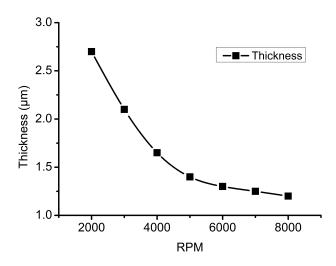

| 3.9  | Spin speed/thickness curve for PI-2545                                                           | 66 |

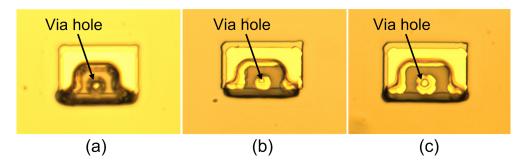

| 3.10 | The micrograph of PI-2545 via opening process developed by wet                                   |    |

|      | etching. (a) The central contact pads size is $3 \times 3 \ \mu m^2$ while the                   |    |

|      | via size is $2 \times 2 \ \mu m^2$ . (b) The central contact pads size is $4 \times 4 \ \mu m^2$ |    |

|      | while the via size is $2.5 \times 2.5 \ \mu m^2$ . (c) The central contact pads                  |    |

|      | size is $5 \times 5 \ \mu m^2$ while the via size is $3 \times 3 \ \mu m^2 \dots \dots$          | 66 |

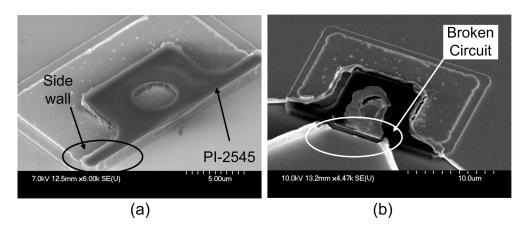

| 3.11 | The micrographs of PI-2545 via opening process developed by $\mathcal{O}_2$          |    |

|------|--------------------------------------------------------------------------------------|----|

|      | plasma dry etching. 75 nm Al was used as etching mask. (a) The                       |    |

|      | after etching profile of PI-2545. The sharp and straight side wall                   |    |

|      | is noticed. (b) After depositing metal bond pads Ti/Pt/Au (15                        |    |

|      | nm/15 nm/200 nm), the circuit is broken at the edge                                  | 68 |

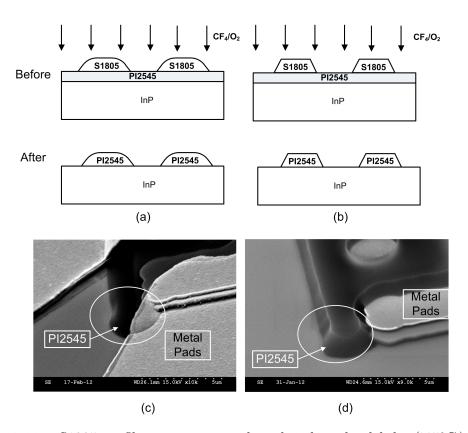

| 3.12 | S1805 profile comparison with and without hard bake (115°C).                         |    |

|      | The profile of PI-2545 was also affected by the mask (S1805). (a)                    |    |

|      | Smooth edge profile due to hard bake. (b) Sharp edge profile with-                   |    |

|      | out hard bake. The SEM pictures of PI-2545 after dry etching (c)                     |    |

|      | with hard bake. (d) without hard bake                                                | 69 |

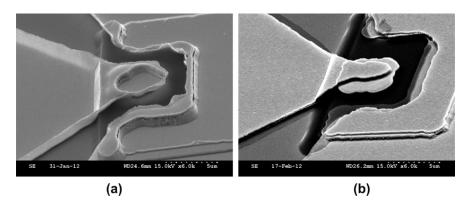

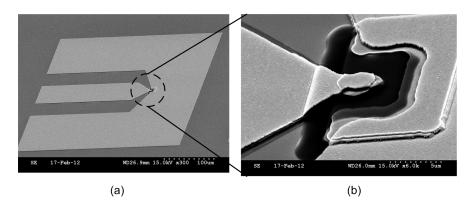

| 3.13 | SEM pictures of the fabricated devices with different polyimide                      |    |

|      | edge profile (PI-2545). (a) Without hard bake, the edge of PI-                       |    |

|      | 2545 is sharp. The crack is noticed on the metal contact, which                      |    |

|      | will lead to circuit failure. (b) With hard bake (115°C), the edge                   |    |

|      | of PI-2545 is smooth. Good metal contact is obtained                                 | 70 |

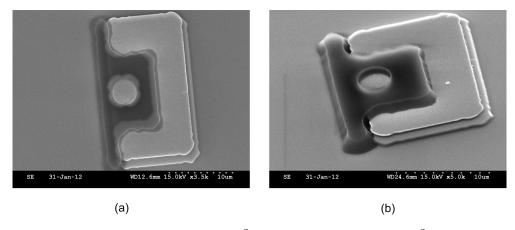

| 3.14 | SEM pictures of $3\times3~\mu m^2$ via opening over $5\times5~\mu m^2$ metal contact |    |

|      | in the centre. (a) Top-view. (b) Side-view                                           | 70 |

| 3.15 | SEM pictures of the fabricated RTD device. (a) The overview of                       |    |

|      | the device. The central area is magnified and shown in (b). The                      |    |

|      | mesa size is $3 \times 3 \mu m^2$ . Good contacts between bond pads and              |    |

|      | electrodes are observed.                                                             | 71 |

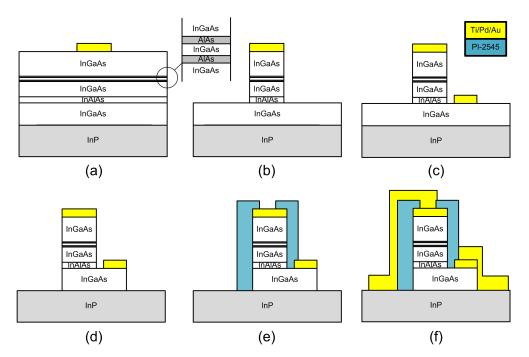

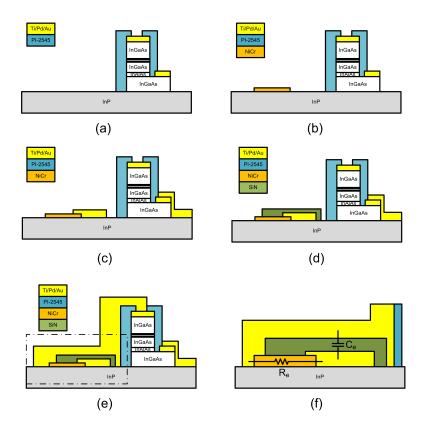

| 3.16 | MMIC RTD oscillator fabrication flow diagram: (a) Fabricated                |    |

|------|-----------------------------------------------------------------------------|----|

|      | RTD device by flowing the process shown in Figure 3.2. (b) De-              |    |

|      | posit NiCr resistor. (c) Pattern emitter metal contact and also the         |    |

|      | MIM capacitor bottom contact. (d) Deposit SiN as MIM capacitor              |    |

|      | insulator. (e) Pattern collector metal contact and also the MIM             |    |

|      | capacitor top contact. (f) The overlapped shunt resistor $(R_e)$ and        |    |

|      | MIM capacitor $(C_e)$ are illustrated with its circuit symbol               | 72 |

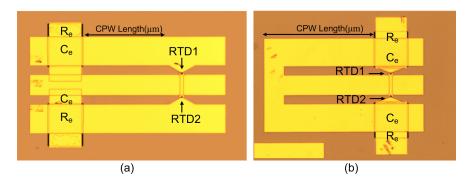

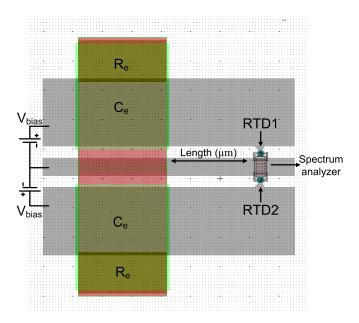

| 3.17 | MMIC RTD oscillator circuits with two different layouts. Both               |    |

|      | employ 2 RTD devices in parallel. Each RTD device is biased                 |    |

|      | individually with its own stabilizing circuit. Locations of the inte-       |    |

|      | grated resistors $(R_e)$ and capacitors $(C_e)$ are also shown              | 73 |

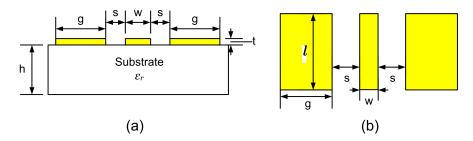

| 4.1  | A CPW structure on a substrate with dielectric constant $\varepsilon_r$ and |    |

| 1.1  | thickness $h$ . The signal line width is $w$ , the gap between the sig-     |    |

|      | nal line and ground plane is $s$ , the width of ground plane is $g$ ,       |    |

|      | the thickness of the conductor is $t$ and the length of the CPW is          |    |

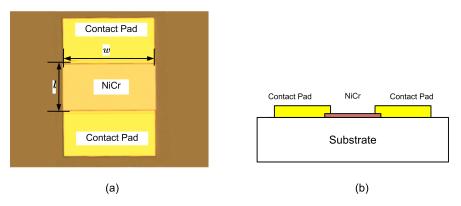

|      | denoted as $l$ . (a) Cross section view. (b)Top view                        | 75 |

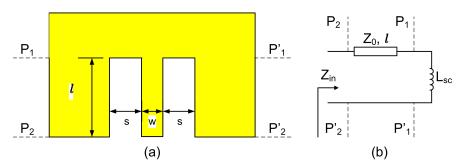

| 4.2  | (a) Physically shorted CPW structure. (b) Shorted CPW equiva-               |    |

|      | lent circuit.                                                               | 78 |

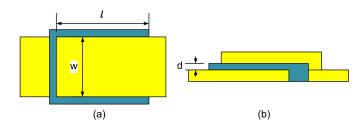

| 4.3  | The layout of MIM capacitor. $w$ is the width of the conductor, $l$ is      |    |

|      | the length of the overlapped conductors. $d$ is the thickness of the        |    |

|      | insulator. (a) Top view. (b) Cross-section view                             | 80 |

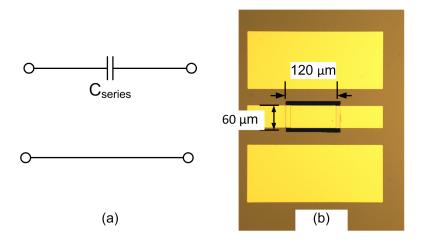

| 4.4  | (a) Coplanar waveguide series MIM capacitor schematic circuit.(b)           |    |

|      | The micrograph of the fabricated series MIM capacitor                       | 82 |

|      |                                                                             |    |

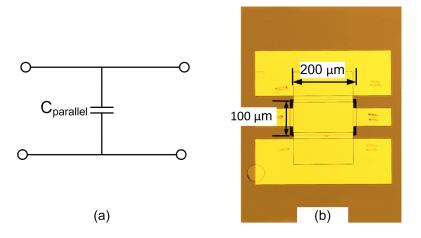

| 4.5  | (a) Coplanar waveguide parallel MIM capacitor schematic circuit.(b)                   |    |

|------|---------------------------------------------------------------------------------------|----|

|      | The micrograph of the fabricated parallel MIM capacitor                               | 82 |

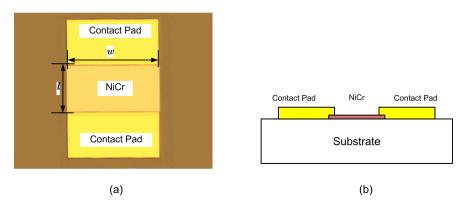

| 4.6  | (a) Micrograph of a NiCr film resistor. (b) Cross section sketch of                   |    |

|      | the resistor                                                                          | 83 |

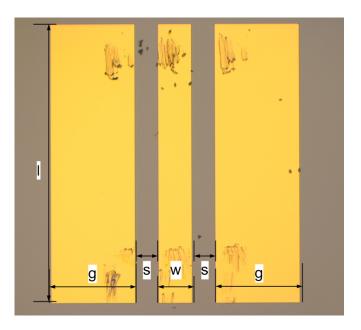

| 4.7  | The micrograph of the design CPW test structure. The centre                           |    |

|      | strip width $w$ is 60 $\mu m$ , the gap width $s$ is 40 $\mu m$ , the ground          |    |

|      | plane width $g$ is 150 $\mu m$ and the length $l$ is 490 $\mu m$                      | 85 |

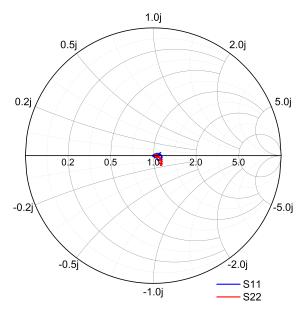

| 4.8  | The S-parameter $(S_{11},S_{22})$ measurement result of the CPW (length               |    |

|      | 490 $\mu m$ ) with designed characteristic impedance $Z_0 = 50~\Omega.$               | 86 |

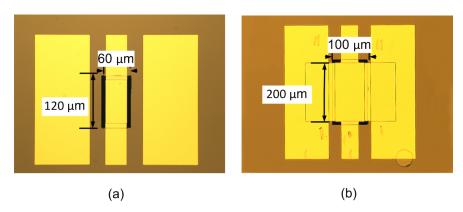

| 4.9  | (a) Fabricated series MIM capacitor with $C_{series} = 5.7  pF$ .(b) Fabricated       | d  |

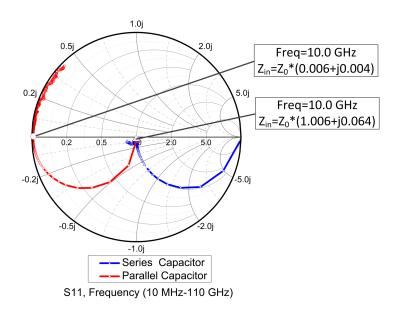

|      | parallel MIM capacitor with $C_{parallel} = 16.1 \ pF. \dots$                         | 87 |

| 4.10 | The S-parameter measurement results, $S_{11}$ , of the series/parallel                |    |

|      | MIM capacitor (blue/red line)                                                         | 88 |

| 4.11 | (a) Micrograph of a NiCr film resistor. (b) Cross section sketch of                   |    |

|      | the resistor                                                                          | 89 |

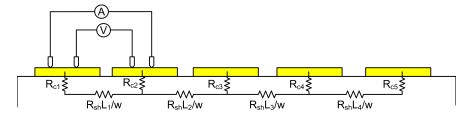

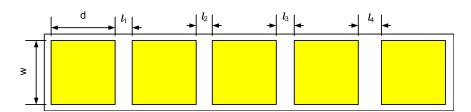

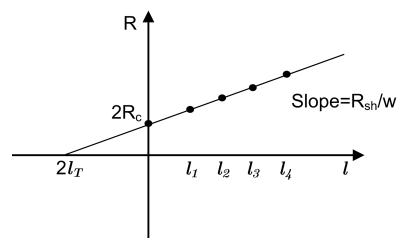

| 4.12 | Four-point probes TLM measurement diagram                                             | 90 |

| 4.13 | The top view of the TLM measurement structure: metal contacts                         |    |

|      | are separated by various distances $l$                                                | 90 |

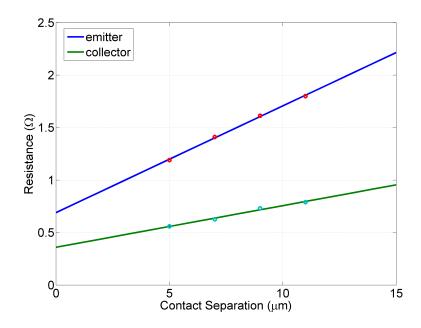

| 4.14 | The plot of measured resistance as a function of contacts separation                  |    |

|      | distance $l$ by TLM method                                                            | 91 |

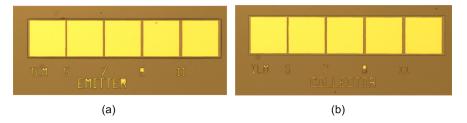

| 4.15 | The micrograph of the TLM test structures for emitter(a) and                          |    |

|      | $\operatorname{collector}(b)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots$ | 92 |

| 4.16 | The plot of total resistance $R_t$ as a function of contacts separation               |    |

|      | distance $l$                                                                          | 93 |

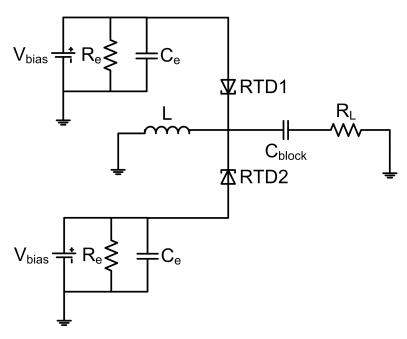

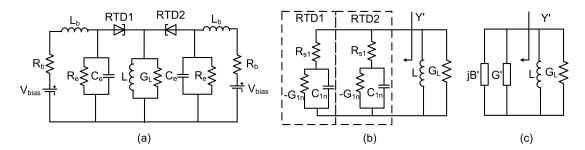

| 5.1 | A two RTD oscillator topology. Each device(RTD1 and RTD2) is                 |     |

|-----|------------------------------------------------------------------------------|-----|

|     | biased individually with shunt resistor $(R_e)$ and decoupling capac-        |     |

|     | itor $(C_e)$ . L, $C_{block}$ and $R_L$ represents the resonator inductance, |     |

|     | the DC block capacitor and the load resistance, respectively                 | 96  |

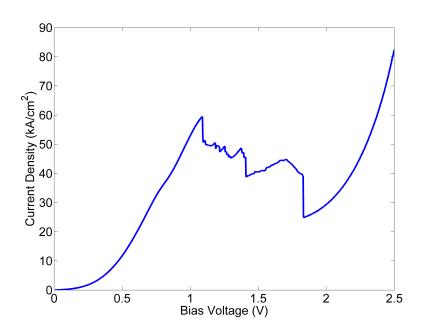

| 5.2 | Measured I-V characteristics of a single $4 \times 4 \mu m^2$ RTD device.    |     |

|     | When the bias voltage is located between 1.1 V and 1.8 V, the de-            |     |

|     | vice exhibits a negative differential resistance (NDR) region. The           |     |

|     | peak current density $J_p = 59.5 \ kA/cm^2 \dots \dots$                      | 97  |

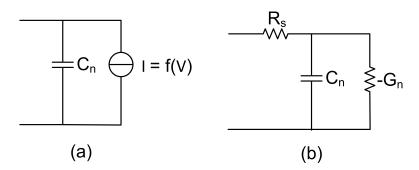

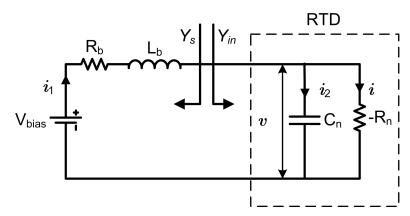

| 5.3 | (a) RTD device large signal model, the device is represented by self-        |     |

|     | capacitance $C_n$ in parallel with voltage controlled current source         |     |

|     | I(V). (b) RTD small signal model. The negative differential con-             |     |

|     | ductance is denoted as $-G_n$ . $R_s$ is the series resistance               | 99  |

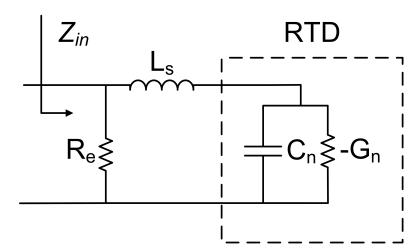

| 5.4 | DC stabilized RTD circuit with shunt resistor $(R_e)$ to suppress the        |     |

|     | bias oscillation. $L_s$ denotes the parasitic inductance. $C_n$ is the       |     |

|     | self-capacitance and $-G_n$ is the negative differential conductance.        | 103 |

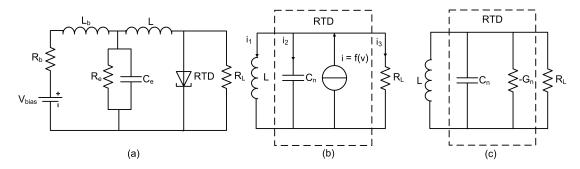

| 5.5 | (a) Single RTD oscillator topology with shunt resistor $R_e$ and de-         |     |

|     | coupling capacitor $C_e$ . $R_b$ and $L_b$ denote the bias cable resistance  |     |

|     | and inductance. $R_L$ is the load resistance and resonator induc-            |     |

|     | tance $L$ . (b) Large signal model. RTD is represented by its self-          |     |

|     | capacitance $C_n$ in parallel with voltage controlled current source         |     |

|     | i(v). (c) Small signal equivalent circuit. RTD is represented by its         |     |

|     | self-capacitance $C_n$ in parallel with the negative conductance $-G_n$ .    | 105 |

|     |                                                                              |     |

| 5.6  | (a) 2 RTDs oscillator circuit topology. 2 RTD devices are employed           |     |

|------|------------------------------------------------------------------------------|-----|

|      | in parallel with each device is biased separately. (b) Small signal          |     |

|      | equivalent circuit. (c) Equivalent circuit where 2 RTDs (parallel)           |     |

|      | are represented by equivalent conductance $G'$ and susceptance $B'$ .        | 110 |

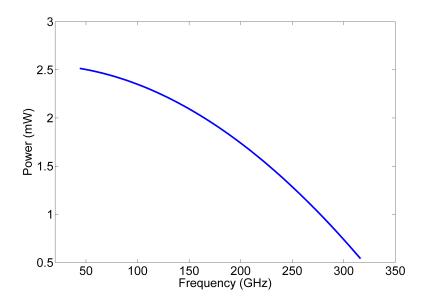

| 5.7  | Calculated two RTD oscillator output power versus frequency. The             |     |

|      | device mesa size is $A=16~\mu m^2,~R_s=11.2~\Omega,~C_n=34.2~fF,$            |     |

|      | $-Gn = -10.89 \ mS, \ G_L = 20 \ mS, \ 4 \ pH < L < 150 \ pH. \dots$         | 112 |

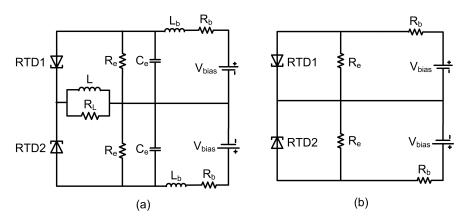

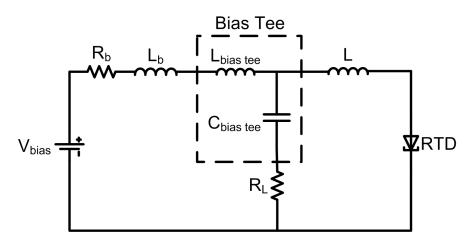

| 5.8  | (a) The schematic circuit of double RTD oscillator layout (type I).          |     |

|      | (b)The DC equivalent circuit                                                 | 112 |

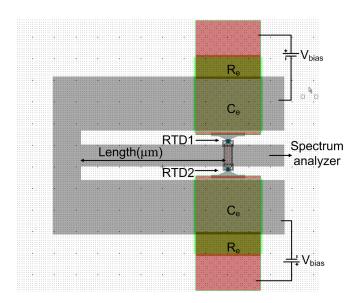

| 5.9  | Double RTD oscillator layout (Type I) drawn by L-Edit software.              | 113 |

| 5.10 | (a) The schematic circuit of double RTD oscillator layout (type              |     |

|      | II). (b)<br>The DC equivalent circuit. Capacitor $C_{block1,2,3}$ blocks the |     |

|      | DC bias reaching the load (spectrum analyser)                                | 114 |

| 5.11 | Double RTD oscillator layout (Type II) drawn by L-Edit software.             | 114 |

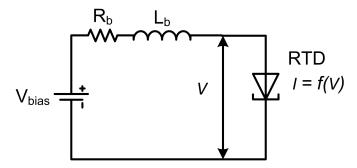

| 6.1  | Direct RTD device I-V measurement circuit. $R_b$ and $L_b$ represents        |     |

|      | the resistance and inductance of the bias cable. The current $I=$            |     |

|      | f(V) exhibits the NDR characteristics of the RTD                             | 117 |

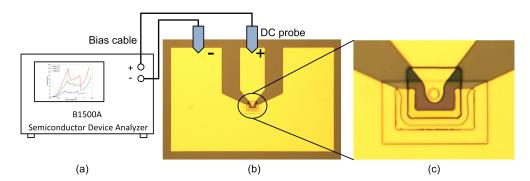

| 6.2  | RTD device DC measurement set up. DC bias was supplied by                    |     |

|      | B1500A semiconductor device parameter analyzer (a). Two DC                   |     |

|      | probes were placed on the contact pads as shown in (b). The top              |     |

|      | view of the device central area is shown in (c)                              | 117 |

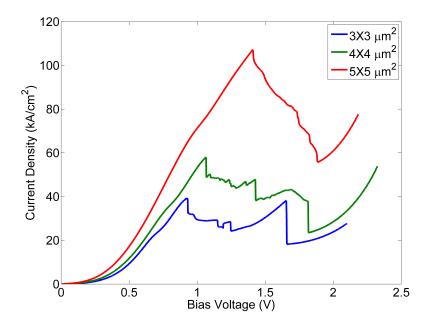

| 6.3  | Measured I-V characteristics of various RTD devices                          | 118 |

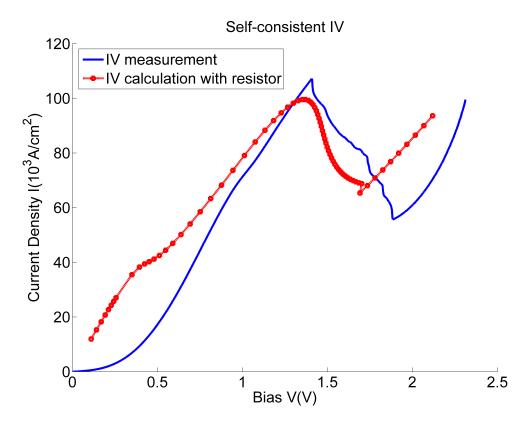

| 6.4  | Comparison between the measurement result of the InGaAs/AlAs                |     |

|------|-----------------------------------------------------------------------------|-----|

|      | RTD $(5 \times 5~\mu m^2)$ and calculated I-V characteristic by using self- |     |

|      | consistent model, of which the parasitic resistance $R_s=35~\Omega$ was     |     |

|      | considered                                                                  | 120 |

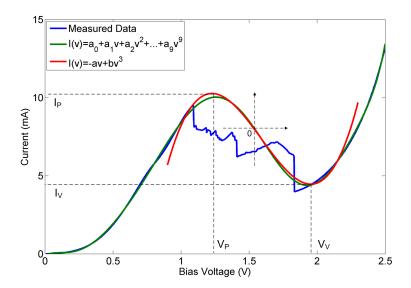

| 6.5  | Measured I-V characteristics compared with polynomial numerical             |     |

|      | fitting (green), including a cubic model for the NDR region (red).          | 122 |

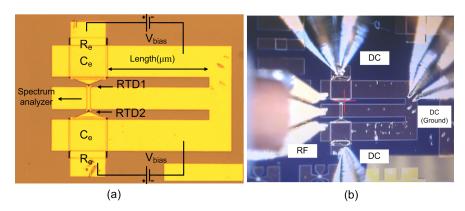

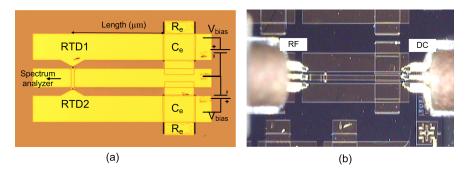

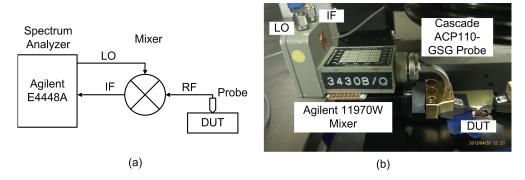

| 6.6  | Type I double RTD oscillator measurement. Three DC probe                    |     |

|      | (one common ground) were landed to bias two RTDs individu-                  |     |

|      | ally. RF signal was extracted from RF probe on the left side.               |     |

|      | (a) The schematic measurement set up. (b) Actual measurement                |     |

|      | with probes landing on the contact pads                                     | 124 |

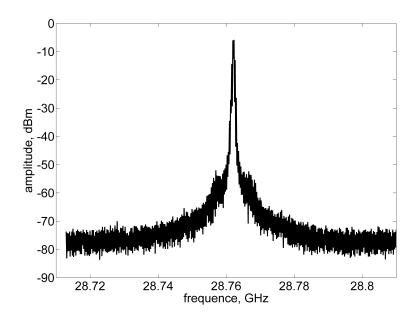

| 6.7  | Measured spectrum of the double RTD oscillator (Type I) when                |     |

|      | $V_{bias} = 1.42 \ V, \ I_{bias} = 203.6 \ mA, \ Span = 100 \ MHz, \ RBW =$ |     |

|      | $300 \ kHz, VBW = 30 \ kHz. \dots \dots \dots \dots \dots$                  | 125 |

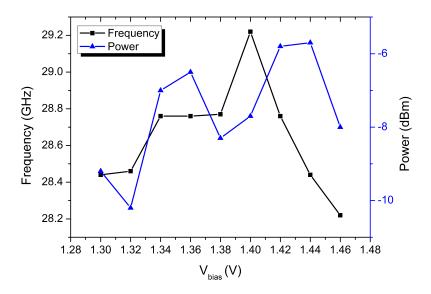

| 6.8  | Measured frequency and RF power of the double RTD oscillator                |     |

|      | (Type I) (VCO) as a function of bias voltage $V_{bias}$                     | 126 |

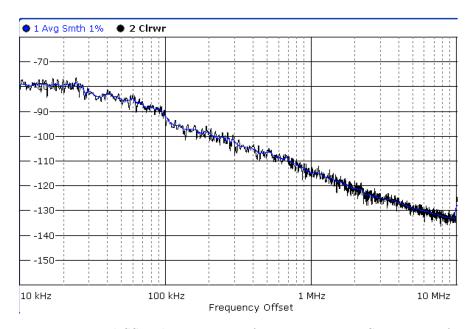

| 6.9  | Measured SSB phase-noise performance at 28.7 GHz carrier fre-               |     |

|      | quency                                                                      | 127 |

| 6.10 | Type II double RTD oscillator measurement. The DC bias was                  |     |

|      | applied through GSG probe on the right side. RF signal was ex-              |     |

|      | tracted from the left side. (a) The schematic measurement set up.           |     |

|      | (b) Actual measurement with probes landing on the contact pads.             | 129 |

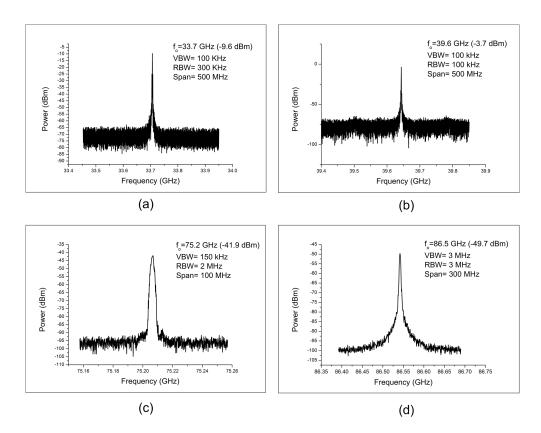

| 6.11 Measured spectru           | m of the double oscillator (type II). (a) 33.7 GHz                    |

|---------------------------------|-----------------------------------------------------------------------|

| (-9.6  dBm)  double             | e RTD $(4 \times 4 \ \mu m^2)$ , $V_{bias} = 1.65 \ V$ , $I_{bias} =$ |

| $172.6 \ mA, \ VBW=$            | =100 kHz, RBW=300 kHz. Span=500 MHz. (b)                              |

| 39.6 GHz (-3.7 dl               | Bm) double RTD $(4 \times 4 \ \mu m^2)$ , $V_{bias} = 1.70 \ V$ ,     |

| $I_{bias} = 216.9 \ mA$         | , VBW=100 kHz, RBW=100 kHz. Span=500                                  |

| MHz. (c) 75.2 (                 | GHz (-41.9 dBm*) double RTD $(4 \times 4 \mu m^2)$ ,                  |

| $V_{bias} = 1.74 \ V, \ I_{bi}$ | $a_{as} = 230.9 \ mA$ , VBW=150 kHz, RBW=2 MHz.                       |

| Span=100 MHz.                   | (d) 86.5 GHz (-49.7 dBm*) double RTD (5 $\times$                      |

| $5 \ \mu m^2$ ), $V_{bias} = 1$ | $58 V, I_{bias} = 200.2 mA, VBW=3 MHz, RBW=3$                         |

| MHz. Span=300                   | MHz. *Note: For frequencies over 50 GHz, mix-                         |

| ers were utilized               | to extend the frequency range of the spectrum                         |

| analyser. As the                | loss of the mixer was not calibrated, the actual                      |

| power were measu                | red by power meter with its value shown in Table                      |

| 6.3                             |                                                                       |

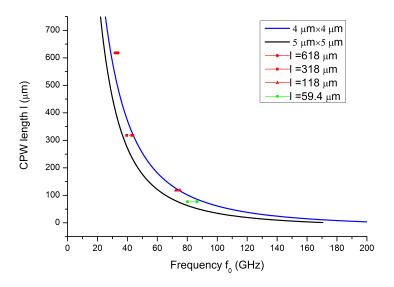

| 6.12 The calculated Cl          | PW length $l$ versus frequency $f_o$ , compared with                  |

| the measurement                 | results                                                               |

## Chapter 1

### THz Technology: Sources

### 1.1 Introduction

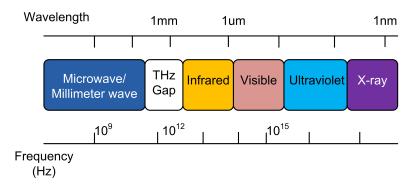

Terahertz (THz) is generally defined as the electromagnetic radiation with frequencies located in the region between 300 GHz–3 THz with corresponding wavelength  $\lambda = 1~mm \sim 100~\mu m$  [1] [2]. In some references [3] [4], it is also referred to as the frequency between 100 GHz–10 THz. This frequency range lies between traditional microwave electronics and infrared photonics, as shown in Figure 1.1.

Figure 1.1: Frequency and wavelength spectra of electromagnetic waves.

Terahertz radiation can penetrate through many materials such as clothing, wood, plastics, etc. as well as organic materials of living organisms without any damage associated with ionizing radiation (such as with X-ray), so terahertz techniques can support promising applications in security systems to reveal undercover weapons, scan sealed packages non-destructively, and also in medical imaging systems. Terahertz techniques can also be utilized in high-resolution radar imaging systems and compact wide-bandwidth wireless-communication systems [2] [5]. However, producing reliable and powerful coherent terahertz signals is a technical challenge.

At the low frequency end, the high electron mobility transistors (HEMTs) and heterojuction bipolar transistors (HBTs) are the electronic devices with current gain cut off frequency  $(f_T)$  approaching 1 THz [6–9]. However the cut-off frequency of the transistors are mostly limited by the carriers drift velocity. The transistor cut-off frequency  $f_T$  can be approximately estimated by  $f_T = 1/(2\pi\tau)$ , where  $\tau$  represents the carriers transit time. For high electron mobility transistor (HEMT),  $\tau$  equals the gate length  $L_q$  divided by the drift velocity v. Under high electric field, v is close to the saturation velocity  $v_s$ , of which typical values for indium gallium arsenide (InGaAs)  $v_s = 4.3 \times 10^7 \ cm/s$  [8], gallium arsenide (GaAs)  $v_s = 2 \times 10^7 \ cm/s$ , silicon (Si)  $v_s = 10^7 \ cm/s$  and graphene  $v_s = 4 \times 10^7 \ cm/s$  [9]. To achieve high frequency, for HEMTs, the gate length  $L_g$  must be scaled down. The highest  $f_T = 610 \ GHz$  (with  $L_g = 15 \ nm$ ) was reported [8] for HEMTs, while for HBTs,  $f_T = 670 \ GHz$  with thin base layer  $(20 \ nm)$  and collector layer (60 nm) was demonstrated [10]. Stringent lighography requirements are therefore required (thin gate length for HEMTs, and thin contacts - base collector parasitic capacitance - for HBTs), which limits the applicability of transistors in THz electronics. In addition, since electronic circuits are typically realised at a quarter or less of the transistor cut-off frequency, the fastest transistors are only useful up to about 200 GHz.

At the high frequency end, the most commonly and commercially available terahertz sources are gas lasers. These sources are able to provide relatively high power in hundreds milli-Watts range, however these sources require large cavities, kilowatt power supply and cryogenic cooling, which impose prohibitive cost and size constraints [1] [4] [11].

The lack of reliable, compact, high power terahertz sources, which can operate at room temperature, has resulted in one of the least tapped regions of the electromagnetic spectrum between the traditional microwave and infrared region. This region is also sometimes termed the "THz gap". In recent years, this gap has been narrowed by high speed microwave electronics devices and the development of long wavelength photonic devices.

### 1.2 THz Sources

As mentioned above, the lack of compact, high power and room-temperature operating THz sources greatly limits the development of modern THz systems, there has been significant research contributing to THz source development. There are many candidates that show great potential for THz applications. In general these THz generation techniques fall into four categories [12].

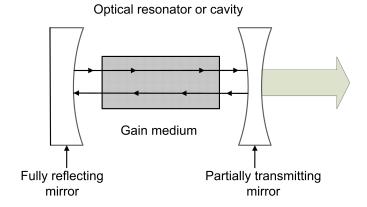

(i) Lasers: A laser is a device based on the stimulated emission of electromagnetic radiation. The process involves an electron that transits from a high energy state to a low energy state with associated photon emission with the same

phase and frequency [13]. The simplest laser system as shown in Figure 1.2 includes a gain medium where stimulated emission occurs and a set of mirrors to reflect the beam passing though the gain medium and being amplified [14]. The frequencies of most lasers are located at the high end of the THz range with

Figure 1.2: Simplified schematic of typical laser [14].

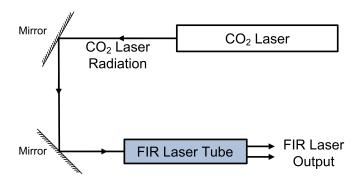

several hundreds of nanometers wavelength. At the low end of THz range, there are several laser devices developed to bridge the THz gap, such as far-infrared (FIR) gas laser [15], quantum cascade lasers (QCL) [16], etc. The schematic representation of FIR laser is shown in Figure 1.3. One of the most widely used FIR laser consists of an external carbon dioxide (CO<sub>2</sub>) laser to stimulate methanol (CH<sub>3</sub>OH) gas molecules which is filled in the FIR gas tube to emit FIR radiation [17] [18]. As FIR gas laser requires cryogenic cooling, the whole system is bulky and costly, however it is a powerful THz source which can provide 100 mW at 118  $\mu m$  wavelength [11].

QCL is an alternative to an FIR laser, and was first demonstrated in 1994 [16]. Different from the FIR gas laser, QCL is a solid-state semiconductor laser, which consists of multiple quantum well heterostructures. The published lowest frequency of QCL is 2.1 THz with 1.2 mW power in continuous-wave (CW) mode

Figure 1.3: Schematic diagram of a far-infrared (FIR) CO<sub>2</sub> laser.

operating at 17K temperature [19]. The performance of QCL degrades sharply with rising temperature. No lasing was observed in CW mode of this QCL for temperature over 40K [19]. The requirement of bulk cryogenic cooling system limits its practical applications which require portability.

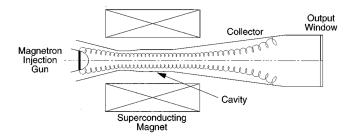

(ii) Free electron sources: Free electron sources such as gyrotron, backward-wave oscillators (BWOs), etc. generate THz radiation by spiralling electrical charges in strong magnetic fields [1]. The gyrotron is a cyclotron resonance maser (CRM) in which an intense flow of electrons (injected by a magnetron injection gun) gyrates at high speed in a strong magnetic field (introduced by symmetrical superconducting magnet) and emits electromagnetic wave as illustrated in Figure 1.4. The gyrotron is generally designed to obtain high power, killowatts (kW),

Figure 1.4: Schematic diagram of a gyrotron [20].

with frequency ranging around several hundred GHz [20] [21].

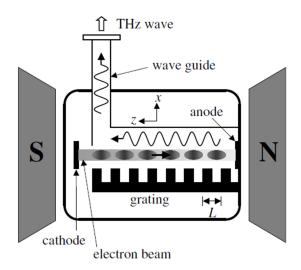

The backward-wave oscillator (BWO) is an another free electron vacuum tube device as shown in Figure 1.5. The electrons are emitted from a heated cathode and collimated by a strong magnetic field. The metallic grating structure induces periodic perturbation of electrons and excites surface wave on the periodic structure. If the electron beam velocity matches the phase velocity of the surface wave, the kinetic energy of the electrons is transferred to the electromagnetic wave [22]. The term "backward-wave" refers to the opposite propagation direction between the group velocity and phase velocity of the surface wave. The typical size of

Figure 1.5: Schematic diagram of a backward-wave oscillator (BWO) [22].

BWO is about  $30cm \times 30cm \times 30cm$ . The bias voltage ranges from 1 kV to 10 kV while the magnetic field is about 1 T. BWOs cover the frequencies ranging from 0.03-1 THz. The output power decreases sharply with increasing frequency. At about 1 THz, the obtained power is about 1 mW [22]. The free electron systems suffer from bulk physical size, metallic wall losses and the requirement for high magnetic and electric fields [11].

(iii) Frequency multiplication: THz radiation is also produced by up-

converting microwave frequencies by using a chain of diode multipliers. As non-linear element can generate harmonics of an input RF signal, a frequency multiplier makes use of such nonlinear circuits to multiply an input frequency. In THz range, the dominant technology is based on gallium arsenide (GaAs) Schottky diodes [23] [24] [25]. In order to produce sufficient output power at terahertz frequency, a high power local oscillator is required to pump the multipliers. Frequencies of up to 1.9 THz with 0.5  $\mu$ W output power were realized by using planar Schottky diodes (GaAs) frequency tripler while a 600 GHz (3 mW) BWO source was utilized in the case of [25]. One disadvantage of frequency multipliers is that noise levels are increased by the multiplication factors because noise variations get multiplied the same way as the frequency is multiplied. Also low power efficiency and short device lifetime are the main limitations of the frequency multipliers [26] [27].

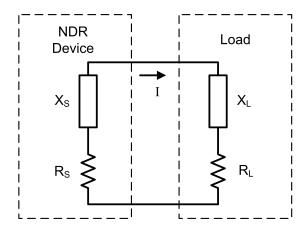

(iv) Negative differential resistance (NDR) devices: The schematic circuit of NDR oscillator is shown in Figure 1.6. The impedance of the NDR device is represented by  $Z_S = R_S + jX_S$ , where  $R_S$  is the negative resistance. The load impedance is represented by  $Z_L = R_L + jX_L$ . To start oscillation, the whole circuit must be unstable which means that the total circuit resistance is negative, i.e.  $R_S + R_L < 0$ . Depending on the nonlinear characteristic of the NDR device, at frequency  $w_0$ , the oscillator will operate in a stable state such that

$$R_S(V_0, w_0) + R_L = 0 (1.1)$$

$$X_S(V_0, w_0) + X_L(V_0, w_0) = 0 (1.2)$$

where  $V_0$  is the bias voltage, and the oscillating frequency  $w_0$  is determined by Equation 1.2. The NDR device in a resonant circuit will compensate the positive resistance loss, so the oscillation will be sustained [26] [28].

Figure 1.6: The schematic circuit of negative differential resistance oscillator.

Two terminal solid state devices such as Gunn diodes, impact ionization transit time (IMPATT) diodes, tunnel injection transit time (TUNNETT) diodes and RTD devices are common NDR devices. A Gunn diode is also known as a transferred electron device (TED) and is based on bulk properties of semiconductors. It only consists of N-doped semiconductor materials (e.g. GaAs, GaN, InP) [29–31]. As the electrons effective mass and mobility are different along different conduction band valley ( $\Gamma$ -valley and L-valley), Gunn diodes exhibit NDR with bias voltage. Gunn diode oscillators with fundamental frequency up to 162 GHz (25 mW) were achieved with devices on diamond heat sinks [32]. The IMPATT diode is basically a p-n junction diode, which is heavily reverse biased to the threshold voltage so that avalanche breakdown happens. Negative resistance characteristics of an IMPATT diode is produced by a combination of impact avalanche breakdown and charge-carrier transit time effects. The main

advantage of IMPATT diode is its high power capability, e.g. 25 mW at 217 GHz [33]. However, the maximum frequency of IMPATT diode is limited to low end frequencies of THz gap and IMPATT diodes suffer from high phase noise [12]. Another high frequency diode is the tunnel injection transit time (TUNNETT) diode. The concept of this diode was introduced by analysis of high frequency performance of the IMPATT diode. When the transit-time-negative resistance (TTNR) region is reduced to realize a high frequency oscillation of an IMPATT diode, electron tunnelling injection becomes dominant instead of the avalanche mechanism. Compared with the IMPATT diode, the advantages of TUNNETT diode are its low noise and high frequency [34]. At 706 GHz, the TUNNETT diode was demonstrated with output power of -67 dBm [35]. All the diode oscillators mentioned above were realized with rectangular waveguide (WR6-WR1.0) cavity technique, which is not compatible with MMICs, and their DC-RF conversion efficiency is normally low (<3 %) [32, 33, 35].

Resonant tunnelling diode (RTD), which make use of resonant tunnelling (through a quantum well) mechanism, is the fastest electronic device [1, 5, 12]. RTD oscillators were estimated to be able to operate up to 2.5 THz at room temperature [36]. Up to date, the highest reported frequency of a single RTD oscillator was 1.1 THz with 0.1  $\mu$ W output power [37]. For RTD oscillators, the DC-RF conversion efficiency can also reach as high as 20% theoretically [38]. Therefore, the RTD device shows great potential for bridging the THz gap, especially for frequencies greater than 300 GHz, where other electronic devices are difficult to implement. At the moment, the main limitation of RTD sources is the low output power. This project aims to raise the power level of RTD oscillators in W-band frequency range (75-110 GHz).

### 1.3 State of the Art

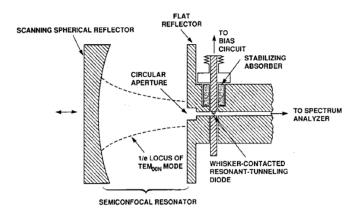

For the first two decades of RTD device development from 1980s, RTD oscillators were realized using a quasi-optical resonator [39–43] as shown in Figure 1.7. A single RTD was mounted in a rectangular waveguide. The resonator was made

Figure 1.7: Schematic cross-section of a quasi-optical RTD oscillator [39] [42].

of a metallic plate acting as a semi-confocal resonator. Spurious bias oscillations were suppressed by a very lossy transmission line. Due to the large contact inductance (whisker contact) and series resistance, it was impractical to stabilize the DC bias circuit and a large portion of power was dissipated over the series resistance. The highest frequency of this quasi-optical RTD oscillator was 720 GHz with only 0.3  $\mu W$  output power [41], and the highest power obtained was 50  $\mu W$  for a single RTD oscillator operating at 210 GHz [43].

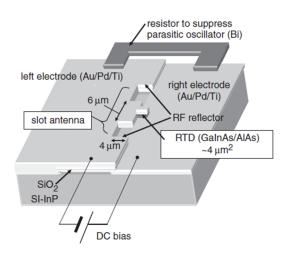

To overcome limitations of quasi-optical RTD oscillators, planar waveguide RTD oscillators were proposed with a single RTD device mounted within a slot metal film as described in [44–49]. This slot performs as a resonator sustaining a standing wave of electromagnetic field and also an antenna to radiate RF power at the same time [50]. The highest frequency of the single RTD slot antenna

Figure 1.8: Schematic diagram of a slot antenna- RTD oscillator [39] [42].

oscillator published is 1.3 THz with 10  $\mu W$  output power [51]. Due to the limited output power of such single oscillator, spatial power combining techniques by employing several oscillators as an antenna array were demonstrated [37] [45] [52]. The highest power obtained to date is 5 mW at 1.18 GHz, when 25 single RTD slot antenna oscillators were employed in parallel [53].

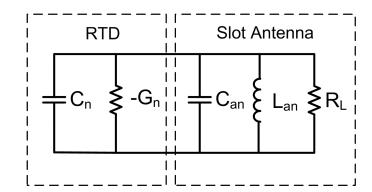

The schematic circuit of an RTD slot antenna (Figure 1.8) is shown in Figure 1.9, where  $-G_n$  and  $C_n$  represent the negative conductance and self-capacitance of RTD device.  $L_{an}$  and  $C_{an}$  represent the inductance and capacitance of the slot antenna.  $R_L$  represent the radiation resistance.  $C_n$ ,  $C_{an}$  and  $L_{an}$  determine the oscillation frequency. For a slot antenna, the impedance varies from infinity at the centre of the slot to zero at the edge of the slot. When an RTD is located at the center of the slot, the oscillator suffers from severe impedance mismatching, and the output power is low. To address this problem, the off-set slot antenna was developed to increase the output power. Published experimental results showed increased power by placing the RTD at different locations in a slot [46,48,49,54].

Figure 1.9: Schematic circuit of a RTD slot antenna oscillator.

However, the physical layout limits the impedance matching improvement of such offset slot antennas. For example, for the 650 GHz oscillator, the length of a slot antenna is only 30  $\mu m$  [50]. For even higher frequency (1.02 THz), the slot length becames shorter (20  $\mu m$ ) [55]. The slot length is comparable to the geometry size of the RTD device (2 – 4  $\mu m^2$ ) which makes the offset difficult to control.

Efforts have also been devoted to develop the RTD slot antenna oscillator array, where several oscillators were placed close to each other [47] [56]. But no procedure has been developed to realize power combining in a specific direction in space. The locations of individual oscillators was not uniquely defined, therefore the power can be combined or cancelled in unexpected directions.

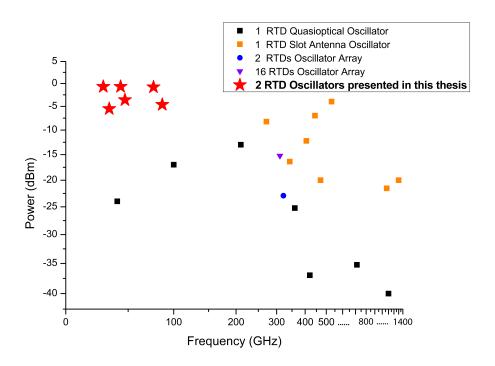

The performance of RTD quasi-optical oscillators, slot antenna oscillators and the oscillators presented in this project are compared in Figure 1.10 in terms of frequencies versus power. It shows at the low frequency end (W-band), the output power of the oscillators in this project (red star) is much higher than other RTD oscillators operating in the similar frequency range. The details of the RTD oscillators designed and realised on this project will be described in the following chapters.

**Figure 1.10:** State of the art RTD oscillator development [37, 39–43, 45, 47–50, 52, 54, 55, 57].

### 1.4 Project Organization and Aim

This thesis is organized as follows: Chapter 1 is the introduction, and reviews THz sources in general and the development of RTD oscillator research. Chapter 2 describes a new self-consistent numerical model, which is based on quantum physics to simulate the current-voltage (I-V) characteristic of an RTD device, in particular the negative differential resistance (NDR) region. Chapter 3 explains the device and oscillator monolithic microwave integrated circuit (MMIC) fabrication techniques including photo lithography, dry/wet etching, metallization, lift-off and especially the new via opening process through polyimide developed in this project. Chapter 4 describes the passive components, including coplanar waveguide (CPW), metal-insulator-metal (MIM) capacitor, and thin film resistor

(NiCr). The description covers their design and experimental characterisation. These components were characterized using DC and scattering parameters (S-parameter) measurements. The ohmic contact resistance of the RTD, which plays an important role in oscillator performance, was also analysed using the transmission line model (TLM) method. The results of this analysis are presented in Chapter 4. Chapter 5 describes the design procedure of MMIC RTD oscillators employing two RTDs in parallel. There are two different double RTD oscillator layouts (type I and type II) designed in this project. Both layouts employed the same power combining topology. In Chapter 6, the frequency and output power measurement of these double RTD oscillators with two different layouts are described. These oscillators operated at 28.7 GHz, 33.7 GHz, 39.6 GHz, 75.2 GHz and 86.5 GHz, and most of them presented relatively high out power (around 1 mW). Finally, conclusions and future work are discussed in Chapter 7.

The aim of this PhD project was to realize monolithic microwave/millimetre wave integrated circuit (MMIC) RTD oscillator with operating frequencies up to 100 GHz with around a milli-Watt output power. The work is based on a power combining circuit topology, in which multiple RTD devices could be employed in a single oscillator circuit [38]. The key was to bias each device individually in the NDR region with shunt resistors to keep the device stable, and also to maximize the device size according to the stability criteria. Details about this circuit topology will be given in Chapter 5. The power combining circuit was proposed by Liquan Wang [38]. A hybrid oscillator prototype using 2 tunnel diodes was realized in his work. The measured output power was 0.22 mW at 437 MHz with DC to RF conversion efficiency over 50% [58]. In this project, the hybrid circuit has been scaled up to realise MMIC RTD oscillators with milli-

Watt output power. 75.2 GHz and 86.5 GHz MMIC RTD oscillators with output power -0.2 dBm (0.96 mW) and -4.6 dBm (0.35 mW), respectively, have been achieved so far, which to the author's knowledge are the highest output power published for RTD oscillators in W-band (75-110 GHz) frequencies.

# Chapter 2

# Self-Consistent RTD Numerical

# Model

## 2.1 Introduction

Resonant tunnelling theory was first proposed by Tsu and Esaki in 1973 [59] and the I-V characteristics with peak tunnelling current at resonant energy were observed experimentally on double barrier heterostructure (GaAs/Al<sub>0.7</sub>Ga<sub>0.3</sub>As) in 1974 [60]. The development of epitaxial crystal growth techniques such as molecular beam epitaxy (MBE) in the 1970s led to a great improvement in high quality RTD heterostructure materials growth. Extensive research has been devoted to resonant tunnelling devices since then.

In this chapter, the content is organized as follows: The first section has introduced the RTD heterostructure. The next two sections introduce the development of RTD heterostructures including those based on III-V materials and on Silicon. The fourth section describes the operating principle of the RTD device.

In section five, a new self-consistent model is developed to simulate the I-V characteristics of a single RTD device for a given layer structure. The final section discusses the simulation results.

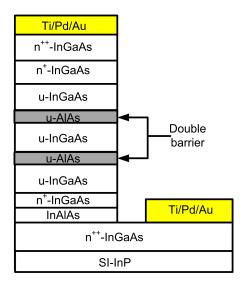

The resonant tunnelling diode (RTD) is a two terminal electronic device that consists of a narrow band gap layer (quantum well) sandwiched between two thin wide band gap layers (barriers). The schematic layer structure of the RTD employed in this project is shown in Figure 2.1. It is noted that the undoped in-

**Figure 2.1:** The schematic layer structure of an InP-based RTD device employed in this project.

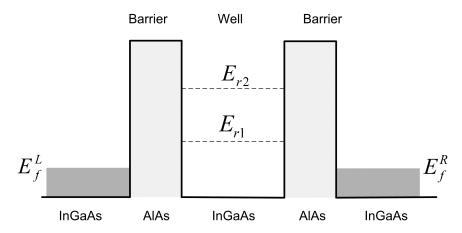

dium gallium arsenide (InGaAs) is sandwiched between two thin un-doped indium aluminium (AlAs) layer. Because of the difference of these two semiconductor material bandgaps, a double barrier quantum well (DBQW) is formed. The band diagram of the DBQW is shown in Figure 2.2. There are several quantized energy states ( $E_{r1}$  and  $E_{r2}$ ) existing in the well according to quantum mechanical theory. The term "resonant" in the name of resonant tunnelling diode refers to the behaviour of electrons with kinetic energy lower than the barrier potential

**Figure 2.2:** The schematic conduction band diagram of a double barrier quantum well (DBBQW) RTD device.  $E_f^L$  and  $E_f^R$  denote the Fermi level of the left and right contact layer.  $E_{r1}$  and  $E_{r2}$  denote the quantized resonate state in the quantum well.

but that still are able to travel though the double barriers. The possibility of electrons tunnelling through the barriers is defined by the transmission coefficient. At the resonant state, the transmission coefficient is close to unity. As the transmission coefficient of electrons tunnelling through the DBQW changes with the bias voltage, the I-V characteristic of resonant tunnelling devices exhibits negative differential resistance (NDR) [61–63].

RTD device is an attractive device, not only because it provides an insight into quantum mechanics theory, but also it shows broadband negative differential resistance from DC up to THz [36], which makes it a very promising electronic device for THz applications. Up to now, RTD oscillators with fundamental frequencies over 1 THz have been reported [37] [55]. However, the output power of the reported THz RTD oscillators is very low. The strategies to raise the power level of RTD oscillators has involved optimizing RTD layer structure to obtain a large peak-valley bias voltage difference ( $\Delta V$ ) and peak-valley bias current difference ( $\Delta I$ ), details of which will be explained in Chapter 3.

In order to engineer the RTD layer structure, a new numerical RTD model based on the resonant tunnelling mechanism was developed on this project. This computational model is different from other published works [62] [64]. Details will be explained in this chapter. It is expected that this model will support the design and optimization of RTD layer structures in high power THz RTD oscillator design.

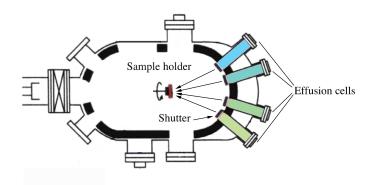

# 2.2 Heterojunction

A heterojunction is a junction between two dissimilar semiconductor materials where the crystal structure is continuous across the interface [65]. A heterostructure normally consists of several thin heterojunction layers. Semiconductor film growth has benefited from modern epitaxial layer growth techniques such as molecular beam epitaxy (MBE) or metal organic chemical vapour deposition (MOCVD). Both techniques provide high quality semiconductor materials growth with precise composition and thickness control. As in this project the indium phosphide (InP) based RTD wafers were grown by MBE, MBE will be introduced briefly. Figure 2.3 shows the basic components of an MBE system. The sample is held in an ultra high vacuum chamber ( $\sim 10^{-11}$  torr vacuum when fully pumped down). In each effusion cell high purity elements such as Si, Ga, Al, As, In and P are heated to generate atomic or molecular beams. Atoms of the elements travel in a straight line to imping on a heated substrate. A shutter is placed in front of each effusion cell to control the composition of the material grown. Selecting a slow growth rate, allows for monolayer ( $\sim 0.3$  nm) growth. It is possible to grow high quality crystals while making abrupt changes in doping

Figure 2.3: The simplified MBE growth system.

and crystal composition [61].

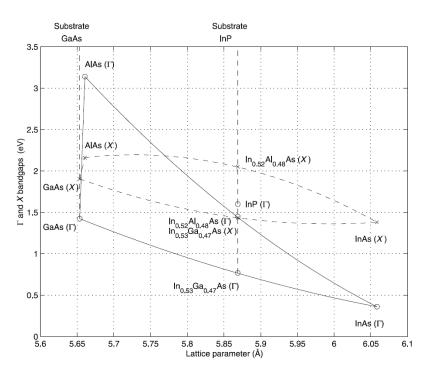

The epitaxial growth of two different semiconductor materials requires that they have a similar lattice constant to minimize the material stress. The stress will prevent thick epitaxial layer growth. The  $In_xGa_{1-x}As/InP$  system lattice constant with different mole fraction x is shown in Figure 2.4 [61]. It is noted that when x=0.53,  $In_xGa_{1-x}As$  has the same lattice parameter with InP which indicates that  $In_{0.53}Ga_{0.47}As$  can be grown epitaxially on an InP substrate. Figure 2.4 shows the band gaps of different alloys. The band diagram can be engineered to improve the performance of resonant tunnelling devices by employing large band gap material with consistent lattice parameters.

# 2.3 RTD Material Systems

With the development of modern epitaxial growth techniques, high quality nano-scale heterostructure is attainable. RTD devices based on III-V semicon-

**Figure 2.4:** Direct  $\Gamma(solid\ line)$  and indirect  $X(dashed\ line)$  band gaps of the alloys of the semiconductor binaries GaAs, AlAs and InAs, plotted versus their lattice parameters for all mole fractions x [61].

ductor materials have been published with record high peak current density  $J_p = 2.4 \times 10^3 \ kA/cm^2$ , and oscillators with record oscillation frequencies over 1 THz [37] [55]. Meanwhile, due to the requirement for compatibility with silicon CMOS processing, Silicon-based RTDs are also being investigated by researchers [66–70].

#### 2.3.1 III-V Based RTDs

RTD devices realized in III-V materials show attractive characteristics, such as THz intrinsic cut-off frequency, high peak current density and high peak valley current ratio (PVCR) performance [37, 41, 55, 71, 72]. The parameters of commonly used III-V semiconductor materials for RTDs are shown in Table 2.1,

in which the effective mass  $(m^*)$ , band gap  $(E_g)$ , relative dielectric constant  $(\epsilon_r)$  and conduction band offset  $(\Delta E_c)$  of the different RTD material systems are compared. In general, small electron effective mass leads to high mobility and improved transport properties, and high conduction band offset will improve the PVCR by suppressing the thermal electron current [73].

**Table 2.1:** III-V RTD material parameters (at room temperature (300K)) [62] [63] [74]

| Material               | $m^*$                 | $E_g(eV)$      | $\epsilon_r$    | $\Delta E_c(eV)$ |

|------------------------|-----------------------|----------------|-----------------|------------------|

| GaAs                   | $0.067m_0$            | 1.42           | 12.9            | 0.28             |

| AlAs                   | $0.1m_0$              | 2.16           | 10.1            | 0.20             |

| $In_{0.53}Ga_{0.47}As$ | $0.042m_0$            | 0.71           | 12.9            | 0.65             |

| AlAs                   | $0.1m_0$              | 2.16           | 10.1            | 0.05             |

| InAs                   | $0.027m_0$            | 0.36           | 14.6            | 1.35             |

| AlSb                   | $0.12m_0$             | 1.61           | 12.04           | 1.55             |

| $Al_xGa_{1-x}As$       | $(0.067 + 0.083x)m_0$ | 1.424 + 1.247x | (12.90 - 2.84x) | N/A              |

| $Al_{0.48}In_{0.52}As$ | $0.084m_0$            | 1.51           | 12.45           | N/A              |

Note:  $m_0 = 9.11 \times 10^{-31} kg$  is the electron rest mass.

#### Gallium Arsenide Based RTDs: $GaAs/Al_xGa_{1-x}As$ Material System

After the resonant tunnelling phenomenon was first demonstrated in 1973 [59], extensive research contributed to the first prototype RTD device based on the  $GaAs/Al_xGa_{1-x}As$  material system [71] [72]. GaAs (low band gap) was sandwiched between  $Al_xGa_{1-x}As$  barriers (high band gap). By changing the composition (mole fraction x) of Al and Ga, when x = 0.42, high PVCR=3.9 at room temperature with  $J_p = 7.7 \ kA/cm^2$  were reported by Huang et al in 1987 [71]. Oscillator frequency up to 420 GHz (0.2  $\mu$ W) was reported based on a GaAs/AlAs material system [39].

The conduction band offset between GaAs and  $Al_xGa_{1-x}As$  is estimated by

Equation 2.1 [62].

$$\Delta E_c(x) = \begin{cases} 0.748x & (0 < x < 0.45) \\ 0.6[1.247x + 1.147(x - 0.45)^2] & (0.45 < x) \end{cases}$$

(2.1)

The electron effective mass  $m^* = (0.067 + 0.083x)m_0$  for  $Al_xGa_{1-x}As$  and  $m^* = 0.067m_0$  for GaAs. The typical specific contact resistance  $(\rho_C)$  reported was about  $10^{-6} \Omega cm^2$  and the saturation velocity of electrons in n<sup>+</sup>-GaAs layer was less than  $1 \times 10^7 \ cm/s$  [62] [75]. Due to low barrier potential and high effective mass, as shown in Table 2.1, compared to InGaAs/AlAs, the PVCR and  $J_p$  of  $GaAs/Al_xGa_{1-x}As$  material RTD is lower.

#### Indium Phosphide Based RTDs: $InGaAs/Al_xIn_{1-x}As$ Material System

Effort has been devoted to develop low effective mass and high conduction band offset semiconductor materials. The effective mass of  $In_{0.53}Ga_{0.47}As$  is  $0.044m_0$  which is much smaller than  $0.067m_0$  for GaAs and the conduction band offset  $\Delta E_C = 0.65~eV$  higher than GaAs/AlGaAs system [62]. A specific contact resistance ( $\rho_C$ ) less than  $10^{-9}~\Omega cm^2$  with a saturation velocity more than  $1.5 \times 10^7~cm/s$  is attainable in  $InGaAs/Al_xIn_{1-x}As$  system [76]. Impressive results have been achieved in InGaAs/AlAs system. Better RTD performance with large  $J_p = 2.4 \times 10^3~kA/cm^2$  and  $PVCR \approx 2$  was reported [55]. And the highest published RTD oscillator frequency is 1.3 THz (10  $\mu$ W) [51] which was realised in the InGaAs/AlAs material system.

The RTD device utilized in this project is InGaAs/AlAs RTD. The details of each layer are shown in Table 2.2. Specifically, from the top layer to the bottom

**Table 2.2:** The specific layer structure of the RTD device used in this project.

| Layer | Thickness (Å)           | Composition            | Doping Level(cm <sup>-3</sup> ):Dopant | Description       |  |

|-------|-------------------------|------------------------|----------------------------------------|-------------------|--|

| 1     | 400                     | $In_{0.53}Ga_{0.47}As$ | $3 \times 10^{19}$ :Si                 | Contact layer     |  |

| 2     | 800                     | $In_{0.53}Ga_{0.47}As$ | $2 \times 10^{18}$ :Si                 | Emitter/Collector |  |

| 3     | 500                     | $In_{0.53}Ga_{0.47}As$ | $2 \times 10^{16}$ :Si                 | Spacer layer      |  |

| 4     | 14                      | AlAs                   | Un-doped                               | Barrier           |  |

| 5     | 55                      | $In_{0.53}Ga_{0.47}As$ | Un-doped                               | Well              |  |

| 6     | 14                      | AlAs                   | Un-doped                               | Barrier           |  |

| 7     | 500                     | $In_{0.53}Ga_{0.47}As$ | $2 \times 10^{16}$ :Si                 | Spacer layer      |  |

| 8     | 800                     | $In_{0.53}Ga_{0.47}As$ | $2 \times 10^{18}$ :Si                 | Collector/Emitter |  |

| 9     | 100                     | $In_{0.52}Al_{0.48}As$ | $1 \times 10^{19}$ :Si                 | Etch stop layer   |  |

| 10    | 2000                    | $In_{0.53}Ga_{0.47}As$ | $3 \times 10^{19}$ :Si                 | Contact layer     |  |

| 11    | 2000                    | $In_{0.53}Ga_{0.47}As$ | $2 \times 10^{19}$ :Si                 | Buffer layer      |  |

| 12    | SI: InP $(635 \ \mu m)$ |                        | Substrate                              |                   |  |

layer, the device consists of: a highly n-type doped contact layer (In<sub>0.53</sub>Ga<sub>0.47</sub>As); a collector/emitter layer (In<sub>0.53</sub>Ga<sub>0.47</sub>As), depending on the bias polarity; a spacer layer (In<sub>0.53</sub>Ga<sub>0.47</sub>As); a 1.4 nm un-doped barrier layer (AlAs); a 5.5 nm undoped quantum well layer (In<sub>0.53</sub>Ga<sub>0.47</sub>As); another 1.4 nm un-doped barrier layer (AlAs); followed by a spacer layer (In<sub>0.53</sub>Ga<sub>0.47</sub>As); an emitter/collector layer (In<sub>0.53</sub>Ga<sub>0.47</sub>As); an etching stop layer (In<sub>0.52</sub>Al<sub>0.48</sub>As); a highly n-doped contact layer and the bottom layer is 200 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As buffer layer which is lattice matched and grown on the substrate (InP). The unintentional doping spacer layers (In<sub>0.53</sub>Ga<sub>0.47</sub>As) delivers two main advantages. One is to reduce the diffusion of impurities from the high doping layer to the barrier layer. The other is that they improve the device high frequency performance by reducing the junction capacitance [77] [61].

#### Gallium Arsenide Based RTDs: InAs/AlSb Material System

The InAs/AlSb system has several advantages over GaAs/AlGaAs and In-GaAs/AlAs system such as low effective mass and high conduction band offset.

The effective mass of InAs is  $0.023m_0$  and the conduction band offset is about 1.35 eV [78] [79]. The low specific contact resistance  $(10^{-9} \Omega \text{ cm}^2)$ , high saturation velocity of electrons  $(5 \times 10^7 \text{ cm/s})$  benefit InAs/AlSb material system over other materials. The published highest single RTD oscillator frequency based on InAs/AlSb material system was 712 GHz with  $0.3 \mu W$  power [41]. However InAs/AlSb system may suffer from impact ionization because of the low band gap of InAs  $(E_g=0.36 \text{ eV})$ . At relatively high electric fields, an electron with energy slightly large than the band gap could collide with an electron in the valence band and knock it out into the conduction band. In the final state, two electrons exists in the conduction band and one hole in the valence band. The number of current carriers are therefore multiplied. This process places an important limitation on the power of devices because once the impact ionization starts, the current increases rapidly due to carrier multiplication. This phenomenon is also referred to as avalanche breakdown. Large band gap semiconductor devices are therefore preferred for high power applications [74].

#### 2.3.2 Silicon-based RTDs

Attempts have been made to integrate an RTD into a complementary metal oxide semiconductor (CMOS) process with different silicon-based material systems such as Si/SiGe [66] [67], Si/CaF<sub>2</sub> [68], Si/SiO<sub>2</sub> [69], Si/ $\gamma$ -Al<sub>2</sub>O<sub>3</sub> [70]. Successful integration will simplify logic circuit design by reducing the device size and number, improve the high frequency response and reduce the power consumption for present Si-based technologies [80]. Due to the difficulty in obtaining high quality interfaces on the Si-based approaches, most Si-based RTDs exhibit poor

performance with low peak current density  $(J_p)$  and peak to valley current ratio (PVCR) compared to III-V RTDs. It should be mentioned that improved n-type SiGe RTD shows comparable performances to III-V RTDs with  $J_p = 282 \, kA/cm^2$ , PVCR=2.4 at room temperature, however the heating effects (due to the poor thermal conductivity of SiGe) lead to strongly area-dependent  $J_p$  [67]. Applications utilizing SiGe heterostructure have not been demonstrated at present.

Comparing III-V RTDs and silicon RTDs, for III-V RTDs, especially with InGaAs/AlAs material, the growth and fabrication technique is more mature. High  $J_p$  and PVCR are obtainable due to the small effective mass, high barrier conduction band discontinuity and low contact resistance. In this project, RTDs based on InGaAs/AlAs material system were utilized.

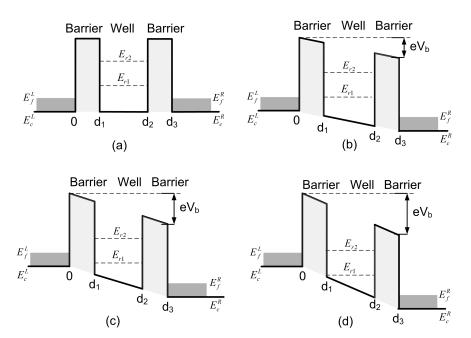

# 2.4 Operating Principle of RTD

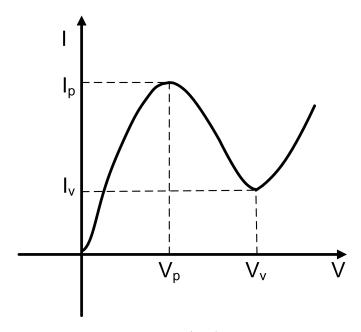

The operating principle of RTD can be illustrated with the conduction band diagram shown in Figure 2.5 [61] [62]. When no bias voltage is applied (Figure 2.5 (a)), no current is observed due to thermal equilibrium. When bias voltage increases from zero, the conduction band profile of the double barrier quantum well (DBQW) shifts as shown in Figure 2.5 (b). Electrons obtain kinetic energy under an electric field. The probability of electrons tunnelling through the barriers (tunnelling current) increases in accordance with the bias voltage. This corresponds to the first positive differential resistance (PDR) region on the device's current-voltage (I-V) characteristic (Figure 2.6). When the energy of electrons corresponding to the increased bias voltage reaches the resonant energy state, the transmission coefficient is unity, which means a large amount of electrons

**Figure 2.5:** Conduction band diagram of DBQW under different bias  $voltage(V_b)$ :(a) no bias applied (b) threshold bias (c) resonant tunnelling (d) off resonance.  $E_f^L$  and  $E_f^R$  are the Fermi level of left emitter layer and right collector layer respectively.  $E_c^L$  and  $E_c^R$  are the conduction band edge of the emitter and collector.  $E_{r1}$  and  $E_{r2}$  represent the resonant energy state in the quantum well.

will tunnel though the DBQW structure without being reflected. The peak DC current  $(I_p)$  is observed in the I-V plot (Figure 2.6). With further increase of the bias voltage, the transmission coefficient reduces drastically, so the current reduces with the increase of bias voltage. This region between  $V_p$  and  $V_v$  is also referred to as the negative differential resistance (NDR). The current is reduced due to the low transmission coefficient. When a larger bias voltage is applied, thermal emission of electrons contributes to most of the current [61] [62], so the current increases with the bias proportionally. The behaviour of electrons tunnelling is characterized by the wave function and the quantized state energy is defined by the Schrödinger equation. In quantum mechanics, the Schrödinger equation describes how the quantum state of particles changes in the form of