Papageorgiou, Vasileios (2014) *Integration of planar Gunn diodes and HEMTs for high-power MMIC oscillators*. PhD thesis.

http://theses.gla.ac.uk/5701/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# INTEGRATION OF PLANAR GUNN DIODES AND HEMTS FOR HIGH-POWER MMIC OSCILLATORS

A THESIS SUBMITTED TO

THE DEPARTMENT OF ELECTRONICS AND ELECTRICAL ENGINEERING

SCHOOL OF ENGINEERING

UNIVERSITY OF GLASGOW

IN FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

By Vasileios Papageorgiou July 2014

© Vasileios Papageorgiou 2014 All Rights Reserved

### **Abstract**

This work has as main objective the integration of planar Gunn diodes and high electron mobility transistors (HEMTs) on the same chip for the realisation of high-power oscillators in the millimeter-wave regime. By integrating the two devices, we can reinforce the high frequency oscillations generated by the diode using a transistor-based amplifier.

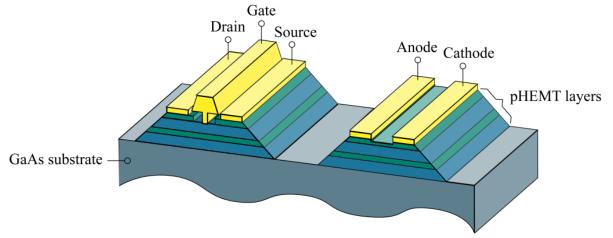

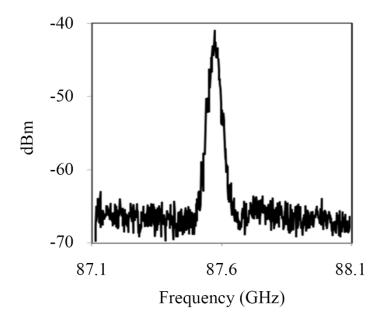

The integration of the planar Gunn diode and the pseudomorphic HEMT was initially attempted on a combined gallium arsenide (GaAs) wafer. In this approach, the active layers of the two devices were separated by a thick buffer layer. A second technique was examined afterwards where both devices were fabricated on the same wafer that included AlGaAs/InGaAs/GaAs heterostructures optimised for the fabrication of pHEMTs. The second approach demonstrated the successful implementation of both devices on the same substrate. Planar Gunn diodes with 1.3  $\mu$ m anode-to-cathode separation ( $L_{ac}$ ) presented oscillations up to 87.6 GHz with a maximum power equal to -40 dBm. A new technique was developed for the fabrication of 70 nm long T-gates, improving the gain and the high frequency performance of the transistor. The pHEMT presented cut-off frequency ( $f_T$ ) equal to 90 GHz and 200 GHz maximum frequency of oscillation ( $f_{max}$ ).

The same side-by-side approach was applied afterwards for the implementation of both devices on an indium phosphide (InP) HEMT wafer for the first time. Planar Gunn diodes with  $L_{ac}$  equal to 1  $\mu$ m generated oscillations up to 204 GHz with -7.1 dBm maximum power. The developed 70 nm T-gate technology was applied for the fabrication of HEMTs with  $f_T$  equal to 220 GHz and  $f_{max}$  equal to 330 GHz.

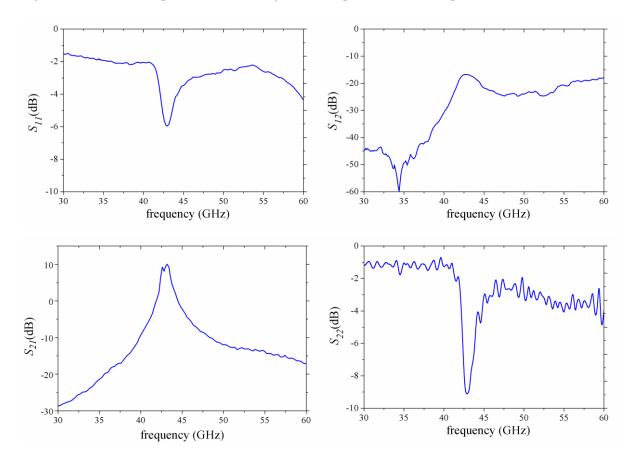

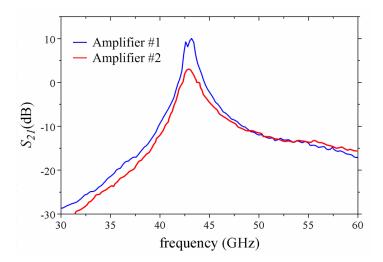

In the end of this work, the two devices were combined in the same monolithic microwave integrated circuit (MMIC), where the diode was connected to the transistor based amplifier. The amplifier demonstrated a very promising performance with 10 dB of stable gain at 43 GHz. However, imperfections of the material caused large variations at the current density of the devices. As a consequence, no signals were detected at the output of the complete MMIC oscillators.

# Acknowledgements

First of all, I would like to heartily thank my supervisor Professor David Cumming for giving me the opportunity to work on this excellent project. He always gave me the confidence that I needed in order to manage the various issues arising during this PhD. He also gave me the mentoring input and his priceless guidance when needed.

I would also like to thank my second supervisor Dr. Ata-ul-Habib Khalid for his valuable guidance during these years. He shared with me his remarkable expertise in nanofabrication, giving me at the same time the mental strength to move on when things went wrong.

Special thanks to Dr. Li Chong who shared with me his tremendous knowledge in millimeterwave electronics. I would still have been "lost in space" without his help. Li Chong became a good friend and one of the greatest people I met in Glasgow.

I was very lucky to share my office with Dr. James Grant (AKA JPG), Iain McCrindle (AKA Zeke Man) and Dr. Kirsty Walls. I am very grateful to them for the quality chatting brakes between work, their advisory on nanofabrication and their kind willingness to proof read this thesis. All of them are great friends and excellent representatives of the Scottish hospitality.

I am indebted to Dr. David Moran for helping me to fabricate functional transistors at a critical point when I had reached a dead end.

My heart full thanks to my good friend, colleague and flat mate Angelos Streklas who suffered my PhD madness all these years. I would have been very grumpy in the mornings without listening to his guitar tunes.

Special thanks to my good friend Dr. Lourdes Ferre Llin for the endless psychoanalysis during our walks in the park. Being cheerful and optimistic, she always had a unique ability to make me see things positive.

I would also like to thank my good friend Dr. Fatemeh Aghamoradi who was big inspiration for hard work and ambitious way of thinking.

Every single member of the James Watt Nanofabrication Centre deserves thanks, because I wouldn't have achieved anything without their continuous support. Helen McLelland, Susan Ferguson, Elizabeth Wyllie, Linda Pollock, Eve Aitkenhead, Vanda Brash, Margaret McCann, Lesley Donaldson, Mark Dragsnen, Douglas Lang, Ronnie Roger, William Monaghan, Robert Harkins, Donald Nicolson, Stephen Thoms and David Gourlay thank you all.

Special thanks to Kirsty Forsythe for her endless support and encouragement that helped me to overcome the difficulties during these years.

Heartfelt thanks to my mentor and good friend, Associate Professor Spyros Vlassis for helping to get where I am.

I would also like to thank George Skotis, Mohammed Al-Rawhani, Salah Sharabi, Sankar Peralagu, Abdullah Al-Khalidi and Thomas O'Hara for helping me with the one or the other way all these years.

I wish to express my sincere appreciation to the Engineering and Physical Sciences Research Council (EPSRC) and to e2v Technologies for the financial support of this project.

Finally, I deeply thank my parents George and Maria as well as my sister Dora for giving me the endless love and support at every stage of my life. Thanks to all my friends in Greece who are too many to name. Thank you all!

### **Associated Publications**

- V. Papageorgiou, A. Khalid, C. Li, M. J. Steer, and D. R. S. Cumming, "Integration Techniques of pHEMTs and Planar Gunn Diodes on GaAs substrates," *Solid-State Electronics* (in press).

- V. Papageorgiou, A. Khalid, C. Li, and D. R. S. Cumming, "Cofabrication of Planar Gunn Diode and HEMT on InP substrate," *IEEE Transactions on Electron Devices*, vol. 61, no. 8, pp. 2779-2784, 2014.

- V. Papageorgiou, A. Khalid, C. Li, and D. R. S. Cumming, "The Development of Planar Gunn Diodes for the realisation of MMIC oscillators," *Proceeding of the 1<sup>st</sup> Annual Active and Passive RF Devices Seminar*, Glasgow, UK, Oct. 2013.

- V. Papageorgiou, A. Khalid, M. J. Steer, C. Li, and D. R. S. Cumming, "Monolithic Fabrication of a Planar Gunn Diode and a pHEMT side-by-side," *Proc.43rd European Solid-State Device Research Conference*, pp. 111-114, Bucharest, Romania, Sep. 2013.

- V. Papageorgiou, A. Khalid, J. Grant, C. Li, and D. R. S. Cumming, "One-step air bridge fabrication technique using 3D e-beam lithography," *Proceedings of the 39th International Conference on Micro and Nano Engineering*, London, UK, Sep. 2013.

- V. Papageorgiou, A. Khalid, C. Li, M. J. Steer, and D. R. S. Cumming, "Monolithic Implementation of a Planar Gunn Diode and a pHEMT," *Proceedings of the 22<sup>nd</sup> European Workshop on Heterostructure Technology (HETECH)*, Glasgow, UK, Sep. 2013.

- V. Papageorgiou, A. Khalid, C. Li, and D. R. S. Cumming, "Simulation and fabrication of InGaAs Planar Gunn Diode on InP Substrate," *Proceedings of the 25th International Conference on Indium Phosphide and Related Materials*, pp. 1-2, Kobe, Japan, May 2013.

- V. Papageorgiou, A. Khalid, and D. R. S. Cumming, "Integration of planar Gunn diodes with High Electron Mobility Transistors," *Proceeding of the 12th Millietre-wave Users Group meeting*, Birmingham, 19 March 2013.

- Khalid, G. M. Dunn, R. F. Macpherson, S. Thoms, D. Macintyre, C. Li, M. J. Steer, V. Papageorgiou, I. G. Thayne, M. Kuball, C. H. Oxley, M. Montes Bajo, A. Stephen, J. Glover, and D. R. S. Cumming, "Terahertz oscillations in an In0.53Ga0.47As submicron planar Gunn diode," Journal of Applied Physics, vol. 115, no. 11, pp. 114502 114502-6, Mar 2014.

- C. Li, L. B. Lok, A. Khalid, V. Papageorgiou, J. Grant, and D. R. S. Cumming, "Millimeter-wave coplanar stripline power dividers," *International Journal of Microwave and Wireless Technologies*, vol. 5, no. 3, pp. 205-212, June 2013.

- Khalid, J. Glover, R. Hopper, V. Papageorgiou, M. Montes, M. Kuball, G. Dunn, A. Stephen, C. Oxley, and D. R. S. Cumming, "Fabrication of integrated planar gunn diode and micro-cooler on GaAs substrate," Proceedings of the 40th International Symposium on Compound Semiconductors, Kobe, Japan, 19-23 May 2013.

- Khalid, C. Li, V. Papageorgiou, N. J. Pilgrim, G. M. Dunn, and D. R. S. Cumming, "A 218-GHz second-harmonic multiquantum well GaAs-based planar Gunn diodes," Microwave and Optical Technology Letters, vol. 55, no. 3, pp. 686-688, Mar. 2013.

- M. I. Maricar, J. Glover, G. Evans, A. Khalid, V. Papageorgiou, D. R. S. Cumming, and C. Oxley, "Planar Gunn Diode and resonators," *Proceedings of the 4th Annual Seminar on Passive RF and Microwave Components*, Birmingham, 18 March 2013.

- Khalid, C. Li, V. Papageogiou, G. M. Dunn, M. J. Steer, I. G. Thayne, M. Kuball, C. H. Oxley, M. Montes Bajo, A. Stephen, J. Glover, D. R. S. Cumming, "Planar Gunn Diodes Operating at a Fundamental Frequency of 164 GHz," *IEEE Electron Device Letters*, vol. 34, no. 1, pp. 39-41, Jan. 2013.

- C. Li, A. Khalid, V. Papageorgiou, L. B. Lok, and D. R. S. Cumming, "A wideband CPW ring power combiner with low insertion loss and high port isolation," *IEEE Microwave and Wireless Components Letters*, vol. 22, no. 11, pp. 580-582, Nov. 2012.

- C. Li, L. B. Lok, A. Khalid, V. Papageorgiou, J. Grant, and D. R. S. Cumming, "A coplanar ring power divider with high isolation for V-band and W-band applications" Proceedings of the European Microwave Conference, Amsterdam, The Netherlands, Nov. 2012.

### **Contents**

| 1. | In  | trod  | luction                                  | 1    |

|----|-----|-------|------------------------------------------|------|

| 2. | Pl  | hysic | es & Devices                             | 4    |

| 2  | 2.1 | Intr  | oduction                                 | 4    |

| 2  | 2.2 | Mat   | terials and properties                   | 4    |

| 2  | 2.3 | Cur   | rent transport                           | . 10 |

| 2  | 2.4 | Het   | erojunctions                             | . 16 |

| 2  | 2.5 | Met   | tal-semiconductor contacts               | . 21 |

|    | 2.5 | .1    | The Schottky contact                     | . 21 |

|    | 2.5 | .2    | Current transport across barriers        | . 23 |

|    | 2.5 | .3    | The Ohmic contact                        | . 25 |

| 2  | 2.6 | The   | high electron mobility transistor (HEMT) | . 26 |

|    | 2.6 | .1    | Device structure                         | . 26 |

|    | 2.6 | .2    | Device operation                         | . 28 |

| 2  | 2.7 | The   | Gunn diode                               | . 35 |

|    | 2.7 | .1    | Material requirements                    | . 35 |

|    | 2.7 | .2    | Operation principles                     | . 36 |

|    | 2.7 | .3    | Devices                                  | . 40 |

|    | 2.7 | .4    | Applications                             | . 44 |

| 2  | 2.8 | Cha   | pter summary                             | . 44 |

| 3. | Pa  | assiv | e components                             | . 45 |

| 3  | 3.1 | Intr  | oduction                                 | . 45 |

|   | 3.2   | Coplanar waveguides                                  | 45 |

|---|-------|------------------------------------------------------|----|

|   | 3.3   | Air bridges                                          | 48 |

|   | 3.4   | Metal-insulator-metal capacitors                     | 50 |

|   | 3.5   | Spiral inductors                                     | 51 |

|   | 3.6   | Matching networks                                    | 54 |

|   | 3.7   | Chapter summary                                      | 60 |

| • | 4. Fa | abrication & characterisation                        | 62 |

|   | 4.1   | Fabrication                                          | 62 |

|   | 4.1   | 1 Material growth                                    | 62 |

|   | 4.1   | 2 Lithography                                        | 63 |

|   | 4.1   | 3 Metallisation                                      | 70 |

|   | 4.1.  | 4 Etching techniques                                 | 70 |

|   | 4.1   | 5 Cleaning and passivation                           | 74 |

|   | 4.2   | Characterisation techniques                          | 75 |

|   | 4.2   | 1 Contact resistivity characterisation               | 75 |

|   | 4.2   | 2 Vector network analyser characterisation           | 77 |

|   | 4.2   | 3 Oscillation detection using the spectrum analyser  | 81 |

|   | 4.3   | Chapter summary                                      | 82 |

| : | 5. To | echnology review                                     | 83 |

|   | 5.1   | Gunn diodes                                          | 83 |

|   | 5.2   | HEMTs and MMIC amplifiers                            | 86 |

| ( | 6. In | dividual fabrication of planar Gunn diodes and HEMTs | 92 |

|   | 6.1   | Introduction                                         | 92 |

| 6.2 Fal  | orication of planar Gunn diodes on single GaAs wafers | 92  |

|----------|-------------------------------------------------------|-----|

| 6.2.1    | Layer structure of the Gunn diode wafers              | 92  |

| 6.2.2    | Fabrication of Ohmic contacts                         | 93  |

| 6.2.3    | Mesa isolation                                        | 96  |

| 6.2.4    | CPW pads and composite contacts                       | 96  |

| 6.2.5    | Recess etching processing                             | 98  |

| 6.2.6    | Results                                               | 104 |

| 6.3 Fal  | brication of pseudomorphic HEMTs on GaAs              | 106 |

| 6.3.1    | Layer structure of the pHEMT wafer                    | 106 |

| 6.3.2    | Ohmic contacts                                        | 107 |

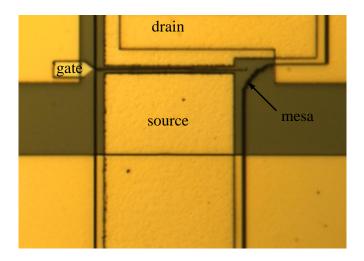

| 6.3.3    | Mesa etching                                          | 108 |

| 6.3.4    | Fabrication of conventional 250 nm gate devices       | 109 |

| 6.3.5    | Development of 70 nm T-gate technology                | 114 |

| 6.3.6    | Fabrication of 70 nm T-gate pHEMTs                    | 119 |

| 6.3.7    | Geometry aspects of transistor design                 | 122 |

| 6.4 Ch   | apter summary                                         | 125 |

| 7. Co-fa | brication of planar Gunn diodes and HEMTs             | 126 |

| 7.1 Int  | roduction                                             | 126 |

| 7.2 Co   | -fabrication on a GaAs combined wafer                 | 126 |

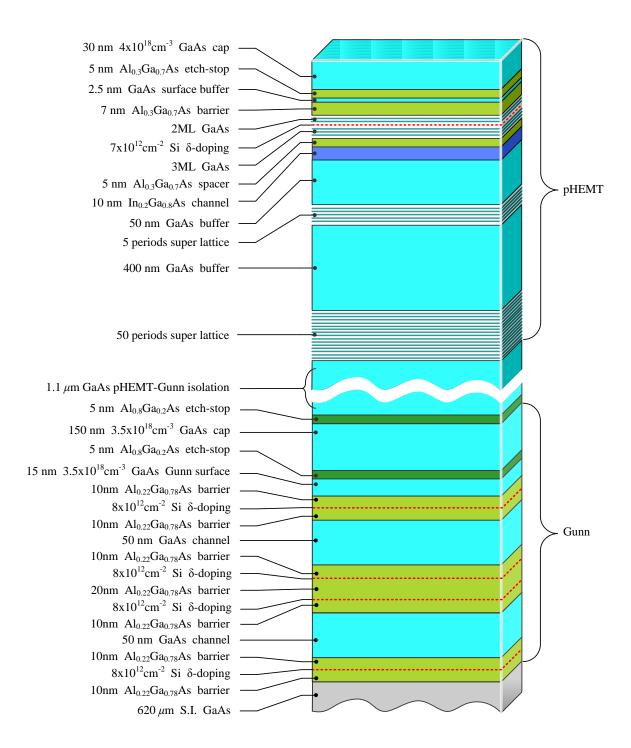

| 7.2.1    | Layer structure                                       | 127 |

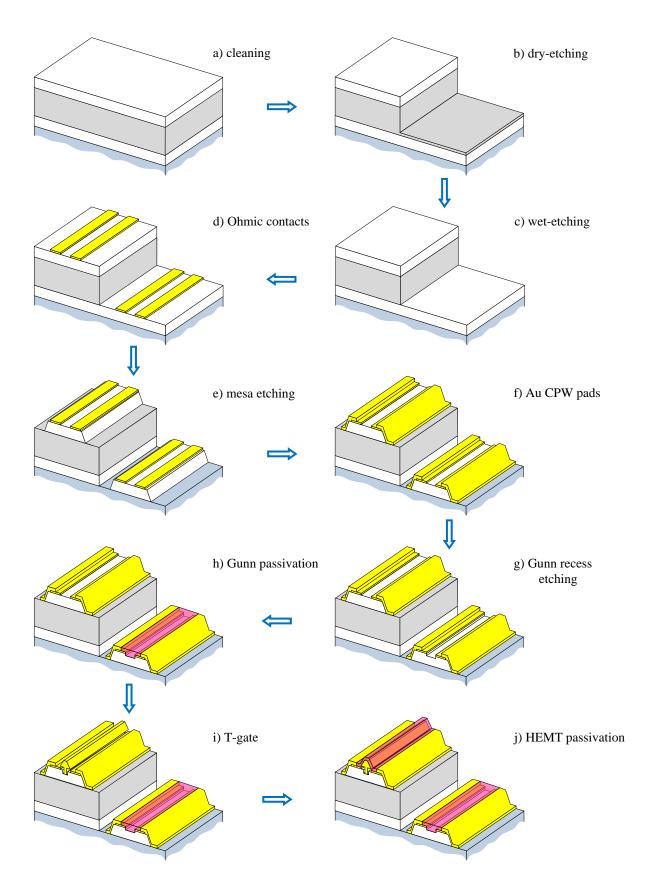

| 7.2.2    | Fabrication process                                   | 129 |

| 7.2.3    | Gunn diode results                                    | 133 |

| 7.3 Sid  | le-by-side implementation on a GaAs pHEMT wafer       | 136 |

| 7.4   | Side-by    | r-side implementation on the InP HEMT wafer | 139 |

|-------|------------|---------------------------------------------|-----|

| 7.4   | 4.1 La     | yer structure and fabrication process       | 139 |

| 7.4   | 4.2 Re     | sults                                       | 142 |

| 7.5   | Chapter    | summary                                     | 148 |

| 8. I  | esign an   | d fabrication of MMIC oscillator            | 150 |

| 8.1   | Introdu    | ction                                       | 150 |

| 8.2   | Circuit    | design                                      | 150 |

| 8.3   | Implem     | entation of MIM capacitors                  | 157 |

| 8.4   | NiCr re    | sistors                                     | 158 |

| 8.5   | Air brid   | lge technology                              | 159 |

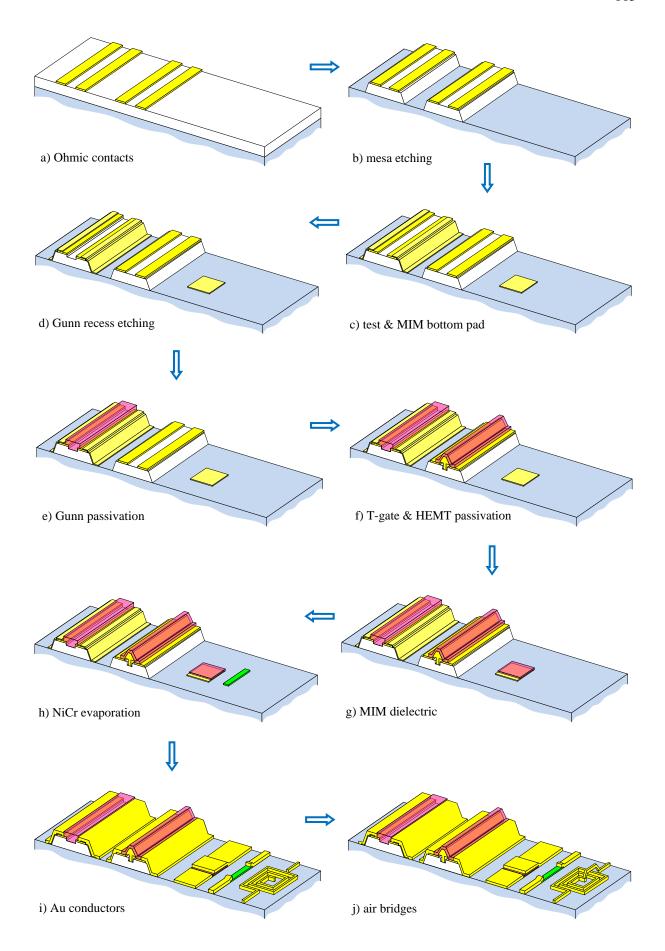

| 8.6   | Fabrica    | tion process of the complete MMIC           | 164 |

| 8.7   | Results    |                                             | 167 |

| 8.8   | Chapter    | r summary                                   | 174 |

| 9. (  | Conclusio  | ns and future work                          | 176 |

| Appen | dix A      |                                             | 180 |

| Appen | dix B      |                                             | 183 |

| B I.  | Planar (   | Gunn diode on C230 GaAs substrate           | 183 |

| B II. | рНЕМП      | Γ on GaAs with conventional 250 nm gates    | 185 |

| B III | . рНЕМТ    | Γ on GaAs with 70 nm T-gates                | 187 |

| B IV  | . Planar ( | Gunn diode on GaAs combined wafer           | 189 |

| BV.   | Side by    | side implementation on GaAs pHEMT wafer     | 191 |

| B VI  | . Side by  | side implementation on InP HEMT wafer       | 193 |

| B VI  | L3D EBI    | air bridge technology                       | 195 |

| B VIII. MMIC oscillator | 196 |

|-------------------------|-----|

| References              | 200 |

### **List of Tables**

| Table 2.1 | Basic parameters of GaAs [19],[20], InP [20],[21], GaN [22],[23] and Si [17].                  |     |

|-----------|------------------------------------------------------------------------------------------------|-----|

|           |                                                                                                | 9   |

| Table 2.2 | Semiconductor material characteristics of GaAs and InP for TEDs (at 300 K                      |     |

|           | temperature unless noted) [16]                                                                 | 40  |

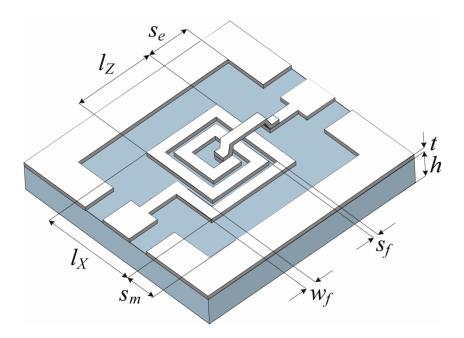

| Table 3.1 | Different design approaches for the implementation of spiral inductors on a                    |     |

|           | GaAs substrate ( $\varepsilon_r = 12.9$ , $t = 3 \mu \text{m}$ , $h = 400 \mu \text{m}$ ) [59] | 53  |

| Table 6.1 | Contact resistance values obtained from TLM measurements.                                      | 108 |

| Table 7.1 | Results obtained from the TLM tests. The recessed resistance is referred to                    |     |

|           | the resistance between two TLM pads with $150 \times 150 \mu\text{m}^2$ geometry and           |     |

|           | 2.5 μm separation.                                                                             | 135 |

|           |                                                                                                |     |

## **List of Figures**

| 2.1  | The zinc-blende lattice (a) [13] and the relative positioning of the two fcc                                                                                       |   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|      | structures (b) [14].                                                                                                                                               | 5 |

| 2.2  | Some crystallographic directions.                                                                                                                                  | 5 |

| 2.3  | The atomic bonding in GaAs (a) and in n-type GaAs (b) [15]                                                                                                         | ó |

| 2.4  | The continuous $E_d$ energy states, the Fermi level $E_F$ and the intrinsic Fermi level $E_i$ [13], [15]                                                           | 7 |

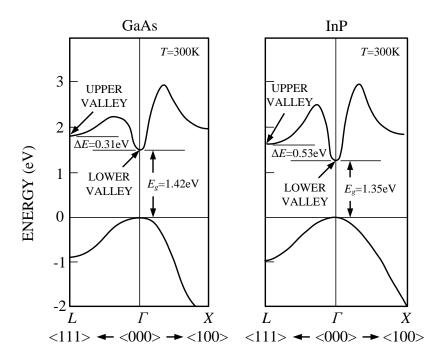

| 2.5  | The simplified energy diagram of GaAs and InP [16].                                                                                                                | 3 |

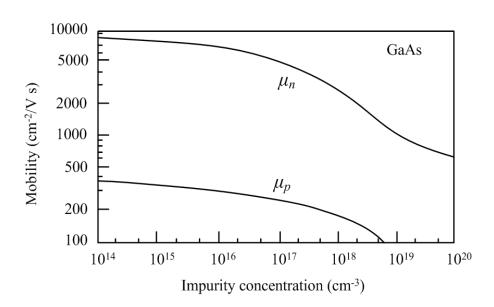

| 2.6  | Mobility of GaAs at 300 K as a function of impurity concentration [24]                                                                                             | Ĺ |

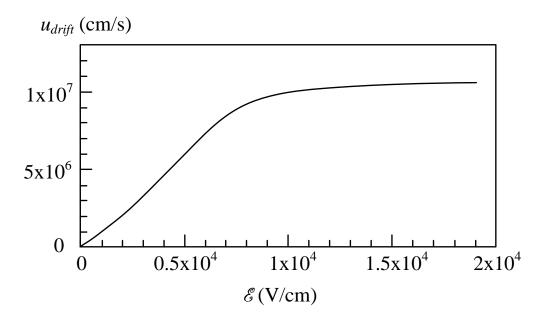

| 2.7  | Electron drift velocity as a function of the external applied field for heavily doped (5·1018 cm-3) GaAs [15].                                                     | 1 |

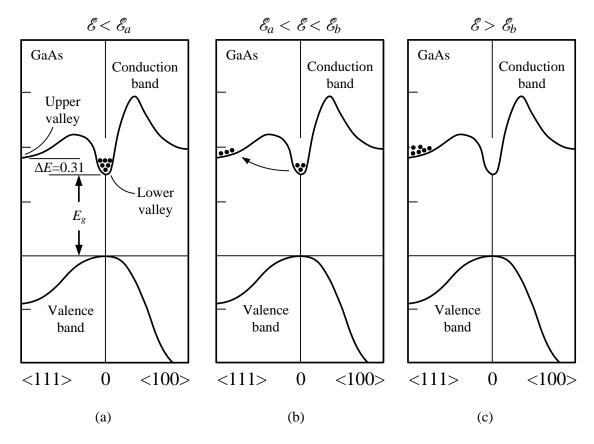

| 2.8  | Electron distributions at the conduction valleys under various applied electric fields for multi-valley semiconductors [24].                                       | 5 |

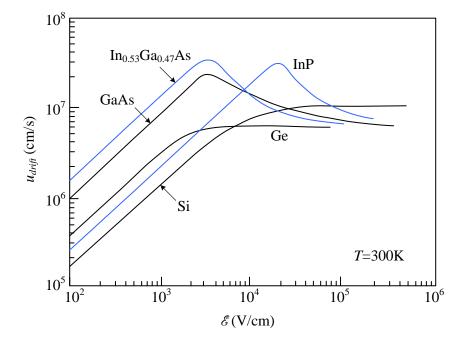

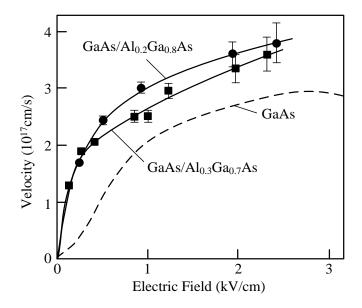

| 2.9  | Drift velocity as a function of the external applied field for various semiconductors  [26]                                                                        | 5 |

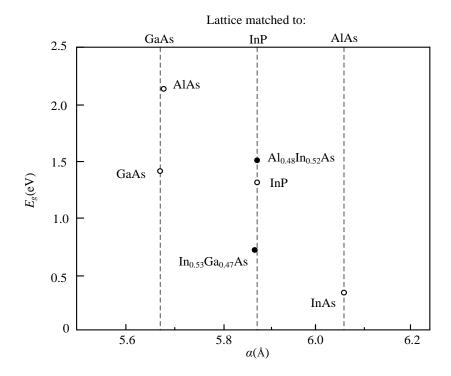

| 2.10 | The lattice constant and the band gap for some III-V compounds                                                                                                     | 7 |

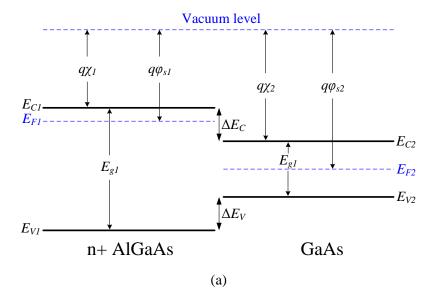

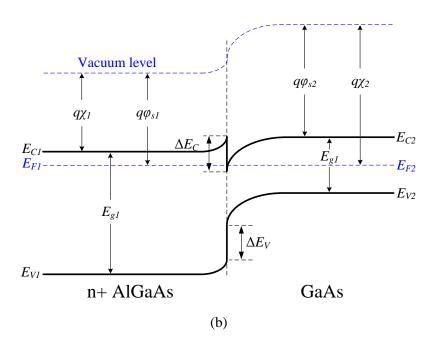

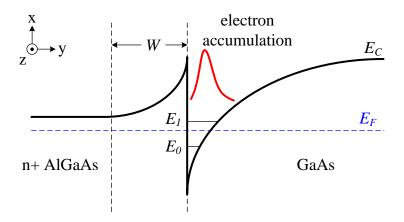

| 2.11 | The individual energy diagrams of the isolated n+ AlGaAs and GaAs (a) and the resulted band diagram after the formation of the AlGaAs / GaAs heterojunction (b) 18 | 3 |

| 2.12 | Band diagram at the AlGaAs/GaAs interface [30]                                                                                                                     | ) |

| 2.13 | Velocity versus electric field dependences for electrons in the 2-DEGs and for n-type GaAs at 4.2 K [29]                                                           | ) |

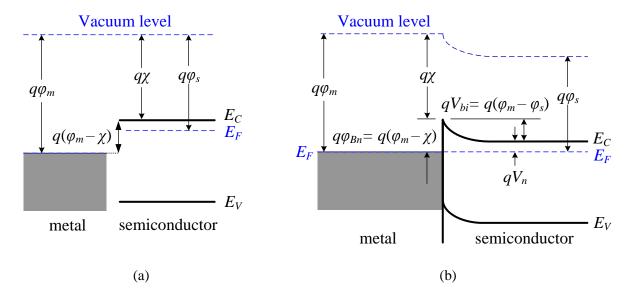

| 2.14 | The energy diagrams of the isolated metal and the n-type semiconductor (a) and the energy diagram of a metal-semiconductor contact (b)                             | 2 |

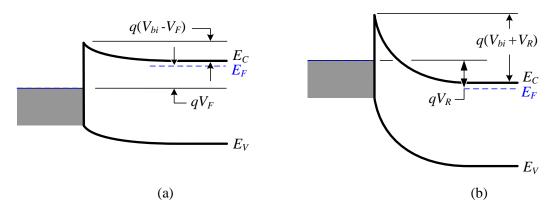

|      | The energy diagrams of the metal-semiconductor interface under forward (a) and reverse (b) biasing conditions                                                      | 3 |

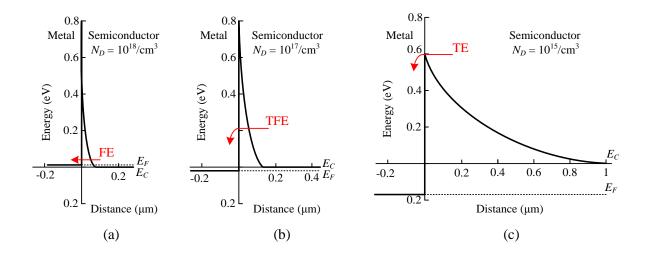

| 2.1 | 6 The main mechanisms for current transport across a metal-semiconductor junction.<br>The junctions are forward biased with $N_{D1} > N_{D2} > N_{D3}$ . The arrows indicate the      |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | electron transfer mechanism [31]                                                                                                                                                      |

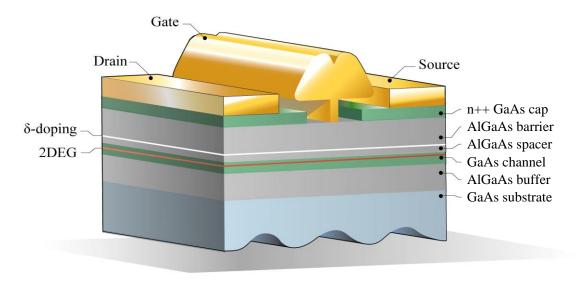

| 2.1 | 7 The basic structure of the HEMT                                                                                                                                                     |

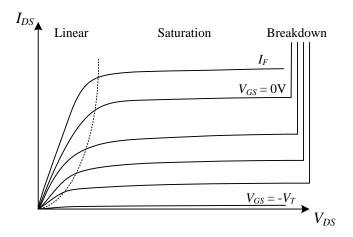

| 2.1 | 8 Typical $I_{DS}$ - $V_{DS}$ characteristics as a function of the gate voltage $V_{GS}$                                                                                              |

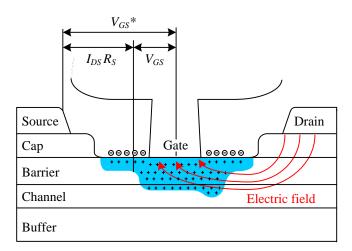

| 2.1 | 9 The voltage drops and the depletion layer in the device [35]                                                                                                                        |

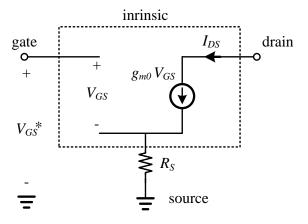

| 2.2 | 0 The simplified equivalent circuit representing the FET for the calculation of the extrinsic transconductance                                                                        |

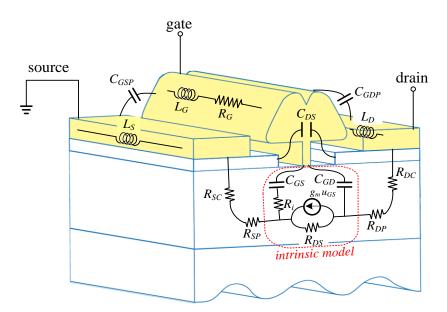

| 2.2 | 1 The detailed equivalent circuit for high frequency operation                                                                                                                        |

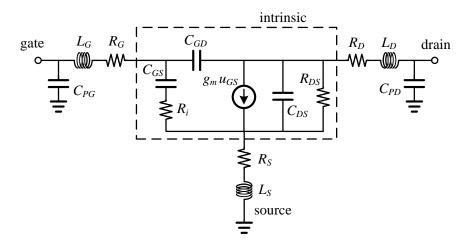

| 2.2 | 2 Lumped-element equivalent circuit of the transistor [38]                                                                                                                            |

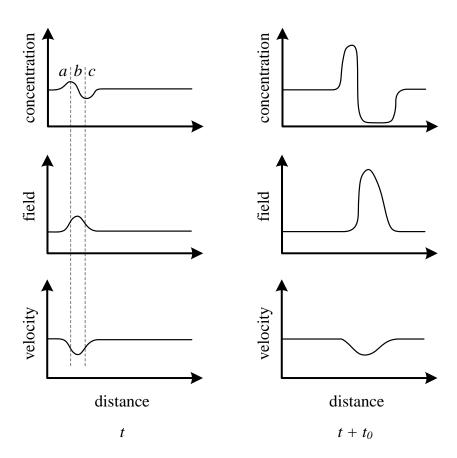

| 2.2 | 3 The formation of the Gunn domain                                                                                                                                                    |

| 2.2 | 4 The equal-area rule for transferred electron devices                                                                                                                                |

| 2.2 | 5 Layer structure of the conventional vertical Gunn diode                                                                                                                             |

| 2.2 | 6 Schematic of oscillator with a vertical Gunn diode placed in a rectangular waveguide cavity [3]                                                                                     |

| 2.2 | 7 Schematic view of the MMIC-compatible vertical Gunn diode (a) [8] and SEM                                                                                                           |

|     | picture of the CPW configuration [3]                                                                                                                                                  |

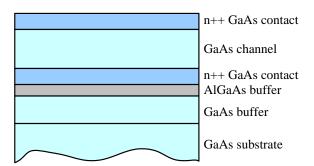

| 2.2 | 8 The layer structure of the first planar Gunn diode oscillating above 100 GHz [9] 43                                                                                                 |

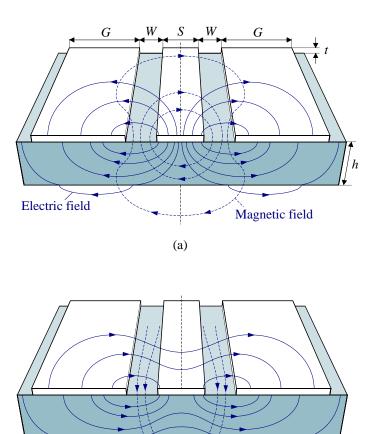

| 3.1 | The coplanar waveguide configuration with finite substrate thickness and finite width of the ground strips. The even mode of propagation is presented in (a) and the odd mode in (b). |

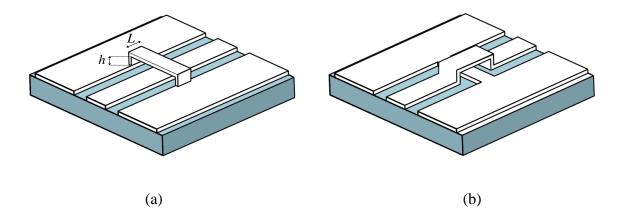

| 3.2 | Type A (a) and type B (b) air bridge configurations                                                                                                                                   |

| 3.3 | The surface current density distribution in the cross section of a symmetrical                                                                                                        |

|     | coplanar waveguide with finite metallization thickness [51]                                                                                                                           |

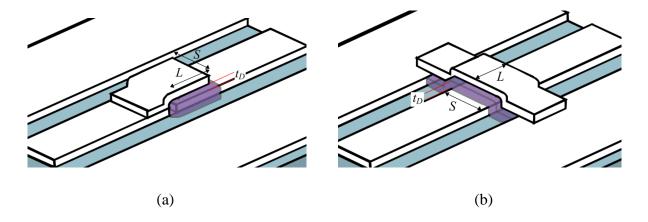

| 3.4 | The MIM capacitor in series (a) and shunt (b) configurations                                                                                                                          |

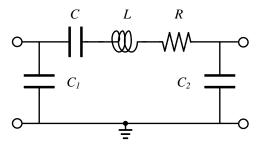

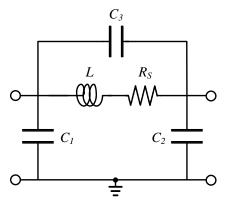

| 3.5  | The equivalent circuit of the MIM capacitor [58]                                                                                                             | 51 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6  | Spiral inductor connected with CPW feed lines.                                                                                                               | 52 |

| 3.7  | The equivalent circuit of the spiral inductor [60]                                                                                                           | 53 |

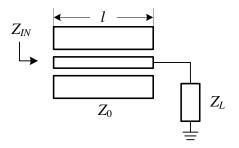

| 3.8  | A CPW line terminated with load $Z_L$                                                                                                                        | 55 |

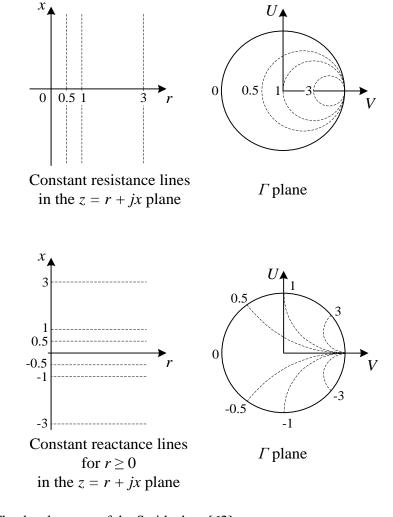

| 3.9  | The development of the Smith chart [62]                                                                                                                      | 55 |

| 3.10 | Basic termination configurations of the transmission line.                                                                                                   | 56 |

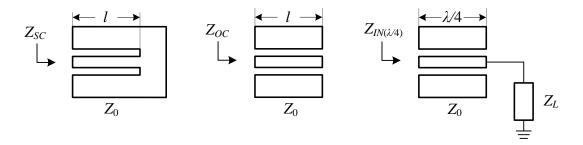

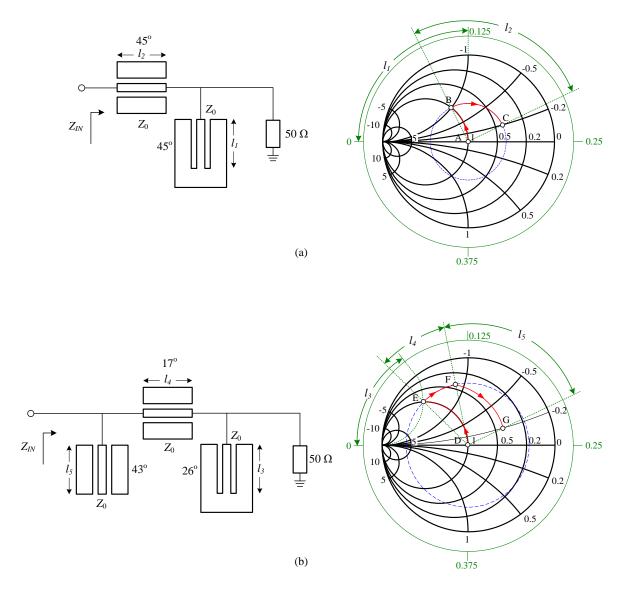

| 3.11 | The L (a) and the Pi (b) matching network approaches.                                                                                                        | 57 |

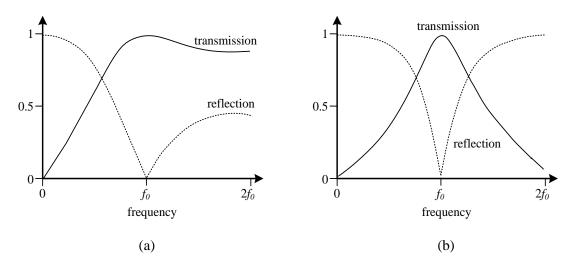

| 3.12 | The frequency response of the L (a) and the Pi (b) matching networks of Figure 3.11                                                                          | 59 |

| 3.13 | The balanced version of the Pi matching network of Figure 3.11(b)                                                                                            | 60 |

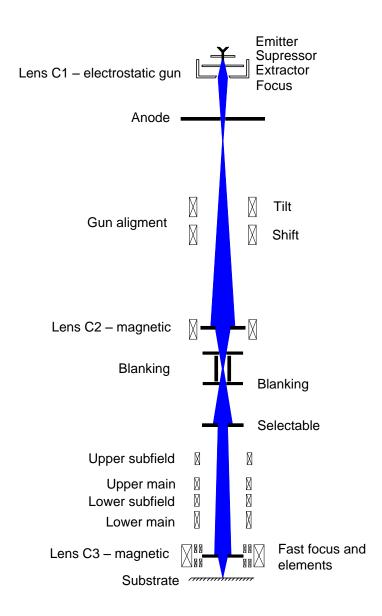

| 4.1  | Ultra high resolution (UHR) column optics [71].                                                                                                              | 66 |

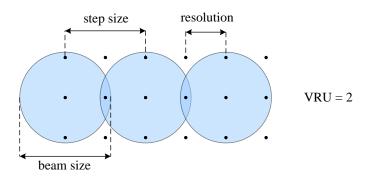

| 4.2  | Pattern writing by stepping the spot. The beam step size is equal to $VRU \times resolution. \\$                                                             | 67 |

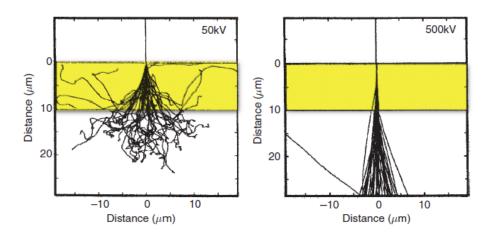

| 4.3  | Electron trajectories for different acceleration voltages [72]. The yellow area indicates the resist layer and the white area bellow indicates the substrate | 68 |

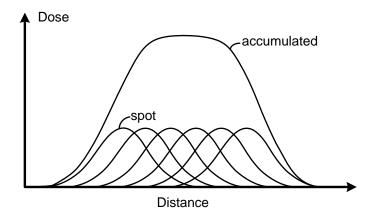

| 4.4  | The electron dose accumulation mechanism.                                                                                                                    | 69 |

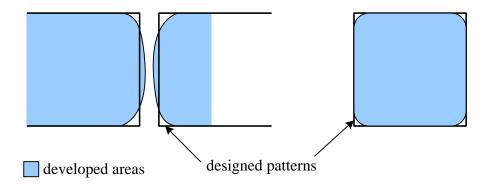

| 4.5  | Distortion caused by the proximity error effect.                                                                                                             | 69 |

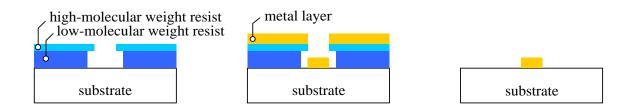

| 4.6  | The conventional process of development, metallisation and lift-off                                                                                          | 70 |

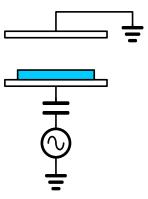

| 4.7  | Basic structure of RIE etcher with the sample placed on the powered electrode [75]                                                                           | 71 |

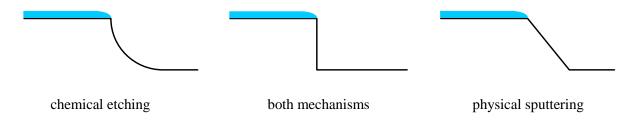

| 4.8  | Cross-sectional profiles depending on the contribution of chemical and physical etching.                                                                     | 72 |

| 4.9  | Cross-sectional profiles for various crystallographic orientations of GaAs                                                                                   | 73 |

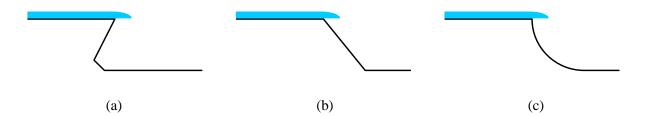

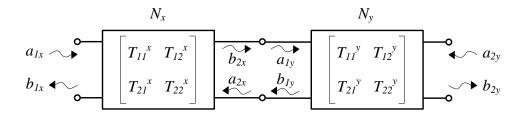

| 4.10 | Fabricated TLM pattern with 1.5 - 5.5 $\mu$ m pad distance.                                                                                                  | 76 |

| 4.11 | Resistance over distance characteristic for the extraction of the contact and the                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | sheet resistance by the TLM method                                                                                                                                                                             |

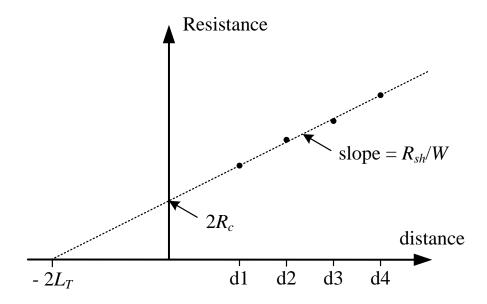

| 4.12 | Calculation of the scattering parameters from a two-port network                                                                                                                                               |

| 4.13 | Cascade connection of the two networks                                                                                                                                                                         |

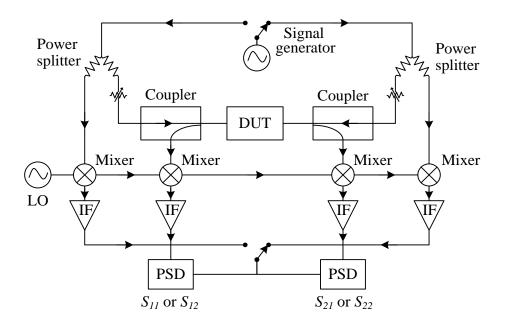

| 4.14 | General block diagram of a vector network analyser [84]                                                                                                                                                        |

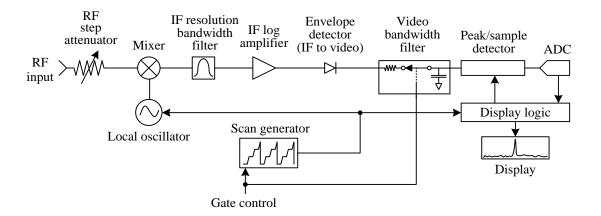

| 4.15 | General block diagram of the spectrum analyser with gate control [89]                                                                                                                                          |

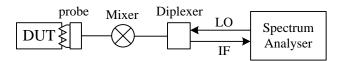

| 4.16 | Simplified block diagram for measurements above the limit of the spectrum analyser                                                                                                                             |

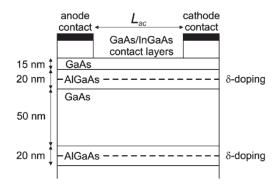

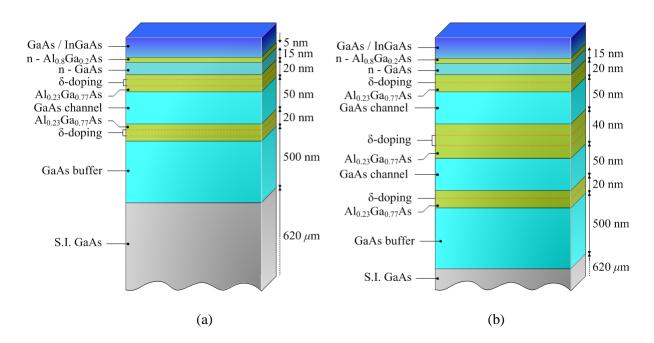

| 6.1  | The layer structure of the single-channel wafer with 4 $\delta$ -doping layers per channel (a) and the double-channel wafer with 2 $\delta$ -doping layers per channel (b) (not to scale) 93                   |

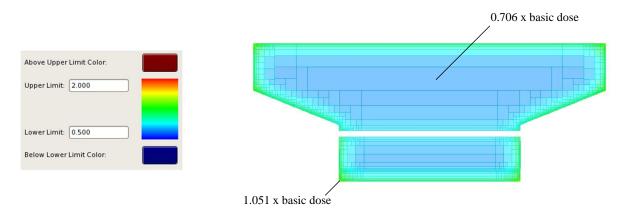

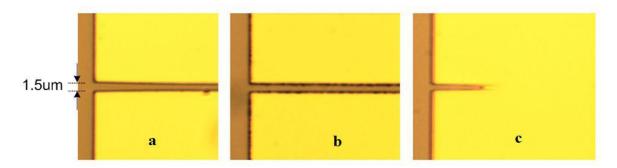

| 6.2  | Generated areas with variable factors for the proximity error correction                                                                                                                                       |

| 6.3  | Metalised patterns using the proximity error correction and variable basic doses (a: $200 \mu\text{C/cm}^2$ , b: $350 \mu\text{C/cm}^2$ , c: $800 \mu\text{C/cm}^2$ ) for a 1.5 $\mu$ m designed separation 95 |

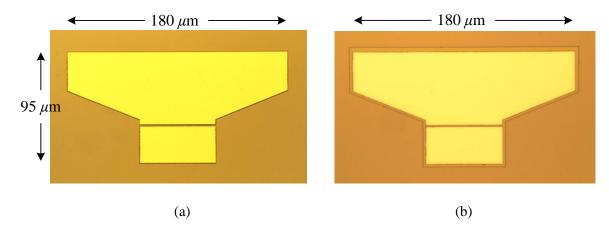

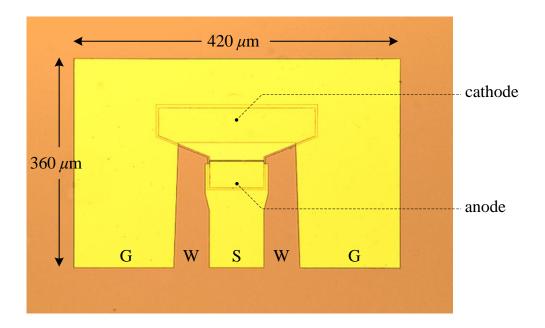

| 6.4  | Fabricated Ohmic contacts (a) and mesa isolation (b) for a device with 1.3 $\mu$ m $L_{ac}$ and 60 $\mu$ m width.                                                                                              |

| 6.5  | Optical picture of the 1.3 $\mu m$ / 60 $\mu m$ device after the evaporation of the CPW pads 97                                                                                                                |

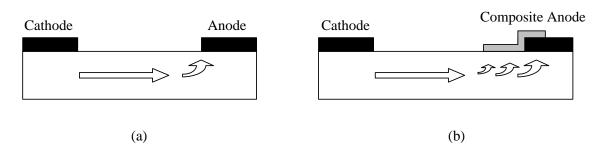

| 6.6  | Schematic representation of the conventional Ohmic contacts (a) and the composite  Schottky anode contact (b) [98]                                                                                             |

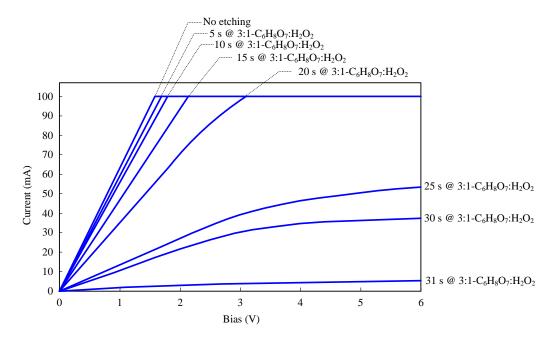

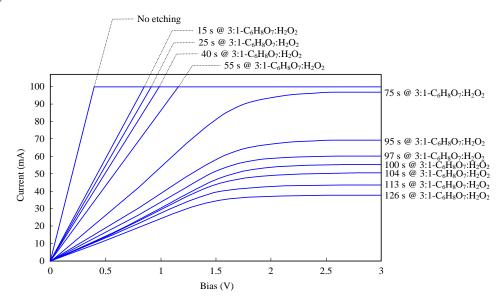

| 6.7  | Results of the first test wafer showing the reduction of the device current for a $4 \mu m / 60 \mu m$ diode after applying a stepped recess etching treatment                                                 |

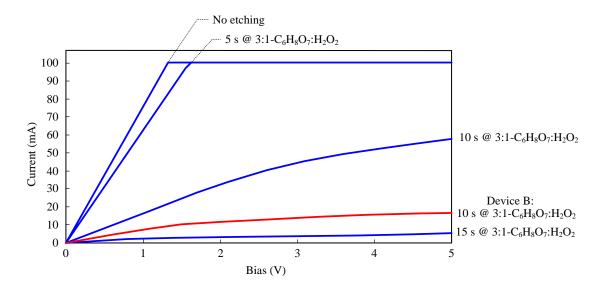

| 6.8  | Results of the second test wafer presenting the reduction of the device current for two different 4 $\mu$ m / 60 $\mu$ m diodes                                                                                |

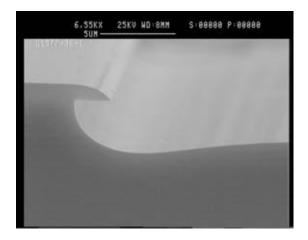

| 6.9  | Trench profile appearing close to mask edges [136]                                                                                                                                                             |

| 6.10 | Reduction of device current for a 1.3 $\mu m$ / 60 $\mu m$ diode after applying a stepped recess etching treatment using succinic acid                                                                         |

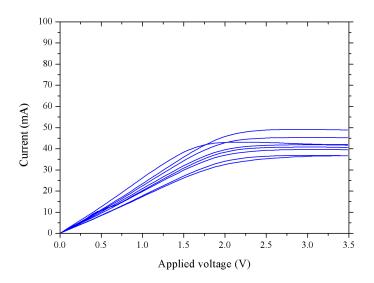

| 6.11 Current - voltage characteristics for a group of eight devices with the same geometry (1.3 $\mu$ m / 60 $\mu$ m).                                             | . 104 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

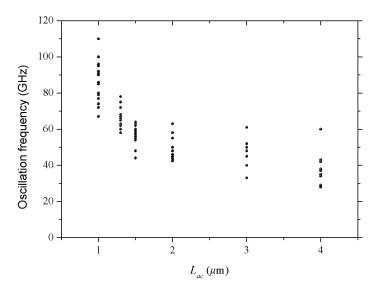

| 6.12 Oscillation frequency as a function of $L_{ac}$ for devices fabricated using succinic acid on the C230 wafer.                                                 |       |

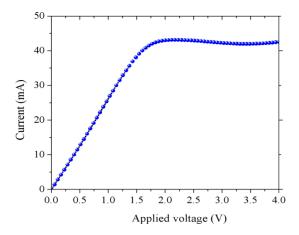

| 6.13 Current-voltage characteristic for planar Gunn diode with 1.3 $\mu$ m $L_{ac}$ and 60 $\mu$ m width.                                                          | . 105 |

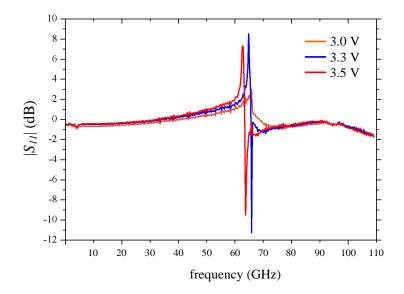

| 6.14 $ S_{II} $ response for a planar Gunn diode with 1.3 $\mu$ m $L_{ac}$ and 60 $\mu$ m width, under various biasing conditions.                                 | . 106 |

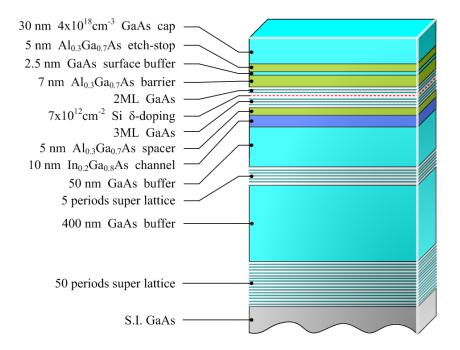

| 6.15 Layer structure of the GaAs-based pHEMT wafer                                                                                                                 | . 107 |

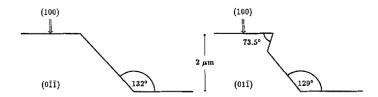

| 6.17 Etching profiles of GaAs after etching with 5 : 1 - Citric Acid : H <sub>2</sub> O <sub>2</sub> [76]                                                          | . 109 |

| 6.18 The resulting mesa island after etching with 10 : 1 - Citric Acid : H <sub>2</sub> O <sub>2</sub>                                                             | . 109 |

| 6.19 Closing of the gate window during the recess etching.                                                                                                         | . 110 |

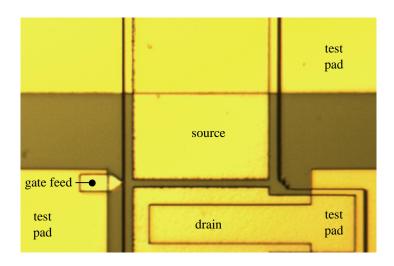

| 6.20 Reduction of the drain current for the 50 $\mu$ m wide test transistors with 250 nm gate length.                                                              | . 111 |

| 6.21 SEM image of a complete pHEMT with 50 μm width, 250 nm gate length and 0.8 μm drain-to-source separation.                                                     | . 112 |

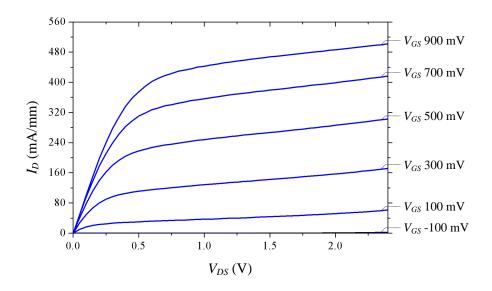

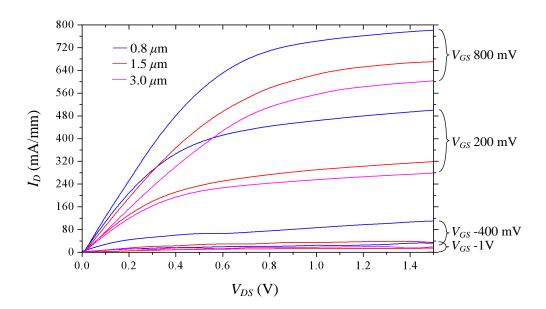

| 6.22 $I_D$ - $V_{DS}$ characteristics under variable gate biasing for a pHEMT with 25 $\mu$ m width, 250 nm gate length and 0.8 $\mu$ m drain-to-source separation | . 112 |

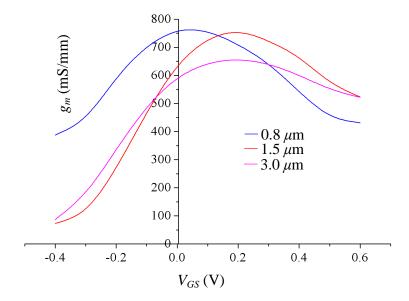

| 6.23 Transconductance performance over $V_{GS}$ for variable drain biasing. The dimensions of the pHEMT are the same as in Figure 6.21                             |       |

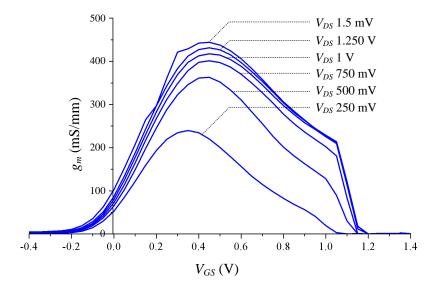

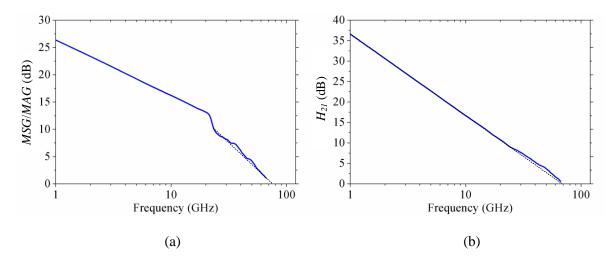

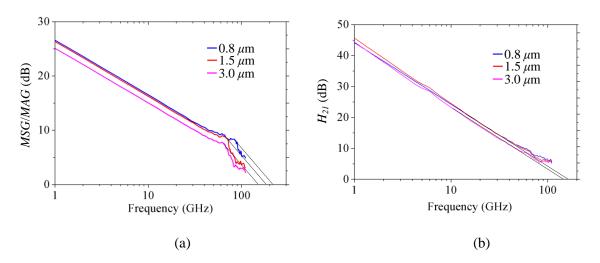

| 6.24 <i>MAG / MSG</i> (a) and current gain (b) as a function of frequency for 250 nm-gate HEMTs.                                                                   | . 114 |

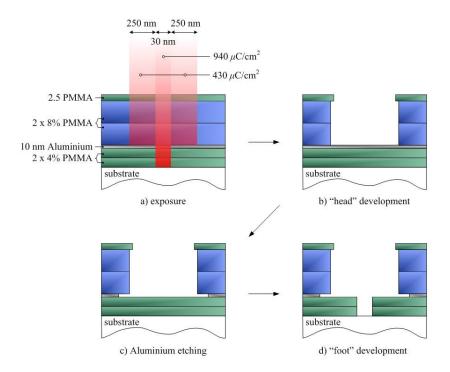

| 6.25 Schematic diagram of the PMMA/Al based T-gate technique                                                                                                       | . 115 |

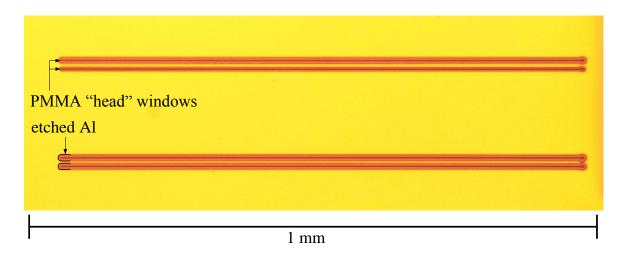

| 6.26 Optical image after etching the Al layer.                                                                                                                     | . 116 |

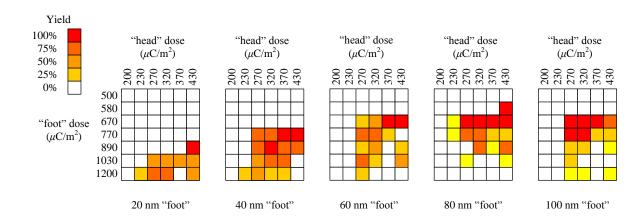

| 6.27 Measured yield of the T-gates for various doses and designs.                                                                                                  | . 117 |

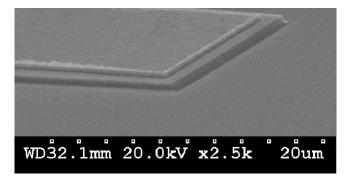

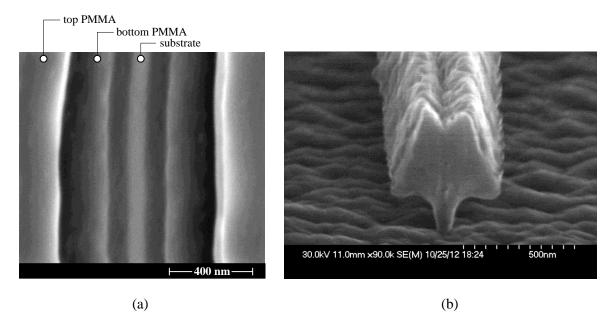

| 6.28 Resist profile (a) and metallised T-gate (b).                                                                                                                 | . 118 |

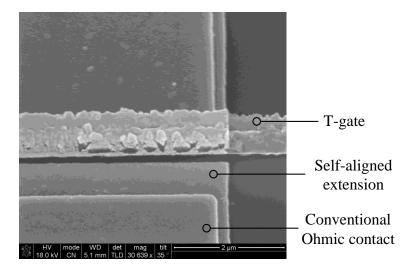

| 6.29 | Fabricated T-gate with self-aligned extensions of the Ohmic contacts                                                                                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

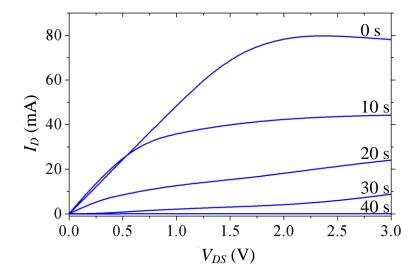

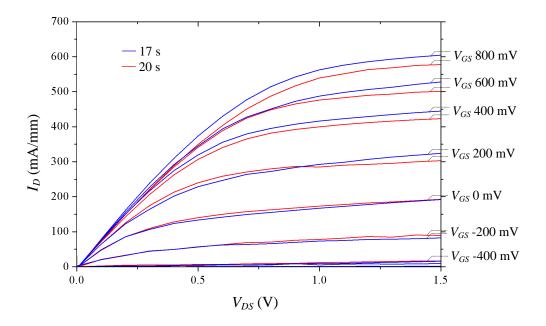

| 6.30 | Comparison of $I_D$ - $V_{DS}$ characteristics for the 17 s (blue curves) and the 20 s                                                                                                                          |

|      | treatment (red curves) for different gate biasing. The 70 nm T-gate devices are $25~\mu m$ - wide with $1.5~\mu m$ drain-to-source separation                                                                   |

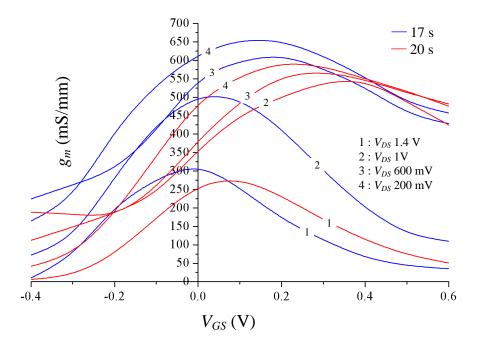

| 6.31 | Comparison of $g_m$ - $V_{GS}$ characteristics for various drain biasing of the devices etched for 17 s and 20 s. The geometry of the devices is the same as in Figure 6.30                                     |

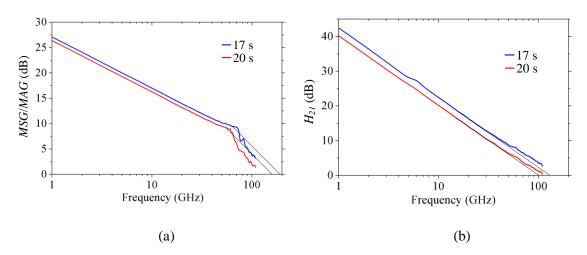

| 6.32 | Device performance; <i>MAG / MSG</i> (a) and current gain (b) as a function of frequency for devices etched for different periods                                                                               |

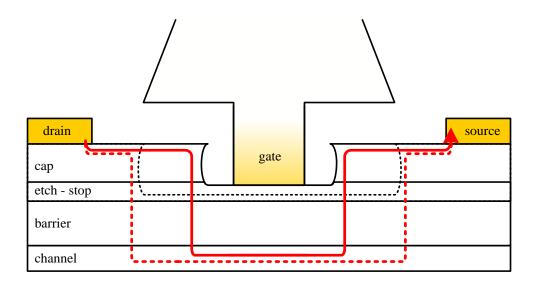

| 6.33 | The extended etched profile and the different current path for devices etched for a longer period (dashed lines)                                                                                                |

| 6.34 | Comparison of $I_D$ - $V_{DS}$ characteristics for 0.8 $\mu$ m (blue curves), 1.5 $\mu$ m (red curves) and 3.0 $\mu$ m (pink curves) drain-source separation. The 70 nm T-gate devices are 12.5 $\mu$ m - wide. |

| 6.35 | Comparison of $g_m$ performance for devices with $L_{DS}$ . The devices are biased at 1.2 V $V_{DS}$ .                                                                                                          |

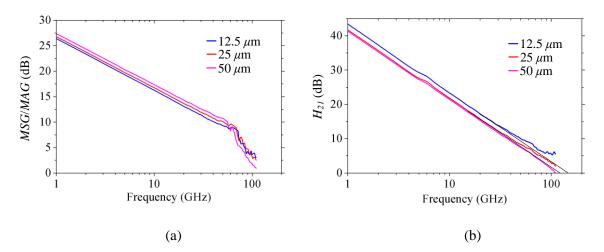

| 6.36 | Device performance; $MAG / MSG$ (a) and current gain (b) as a function of frequency for devices different $L_{DS}$ .                                                                                            |

| 6.37 | Device performance; <i>MAG / MSG</i> (a) and current gain (b) as a function of frequency for devices different width                                                                                            |

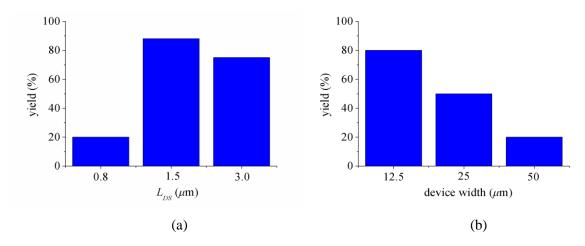

| 6.38 | Fabrication yield as a function of the $L_{DS}$ (a) and the device width (b)                                                                                                                                    |

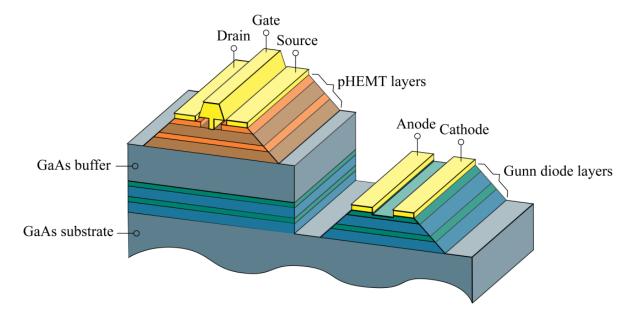

| 7.1  | The general layer structure of the combined wafer approach (not to scale) [151] 127                                                                                                                             |

| 7.2  | The detailed layer structure of the combined wafer (not to scale)                                                                                                                                               |

| 7.3  | The fabrication process flow for the combined wafer                                                                                                                                                             |

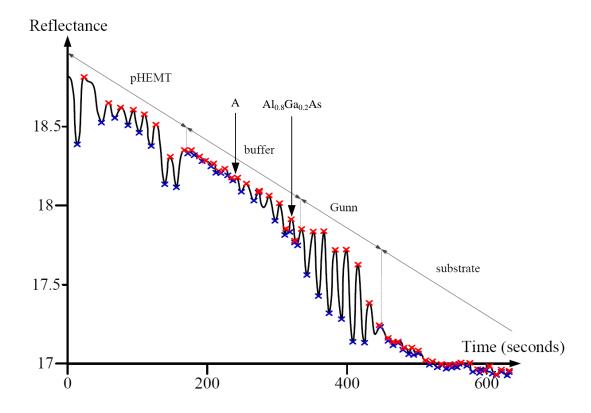

| 7.4  | The interferometer response for the test run where the layer structure is completely etched                                                                                                                     |

| 7.5  | Bad surface morphology caused by the transfer of As at the surface after annealing at 400°C.                                                                                                                    |

| 7.6  | Current-voltage characteristic for a planar Gunn diode with 2 $\mu$ m $L_{ac}$ and 60 $\mu$ m                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------|

|      | width [151]                                                                                                                    |

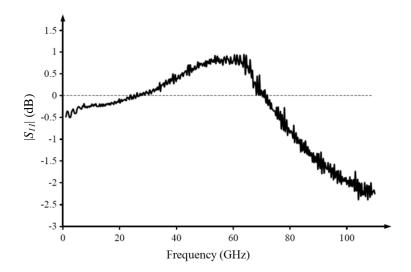

| 7.7  | The $ S_{II} $ response versus frequency for the diode of Figure 7.6 [151]                                                     |

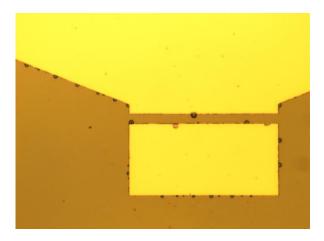

| 7.8  | The side-by-side implementation of the transistor and the diode on the pHEMT substrate.                                        |

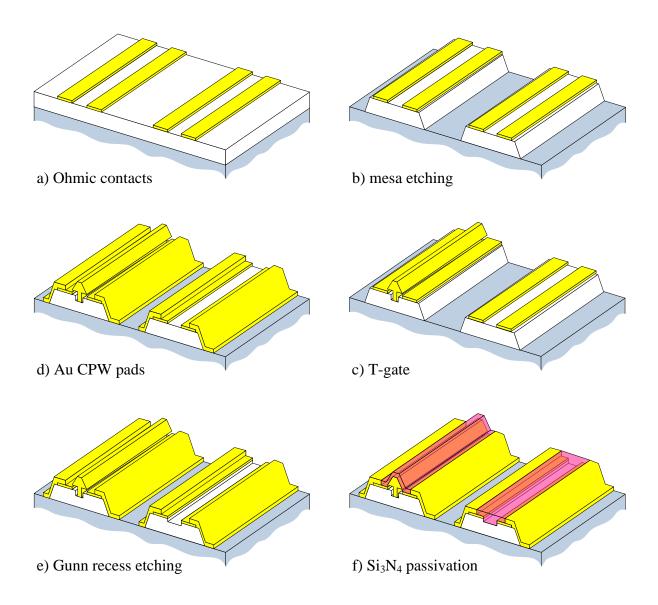

| 7.9  | The fabrication process flow for the side-by-side approach                                                                     |

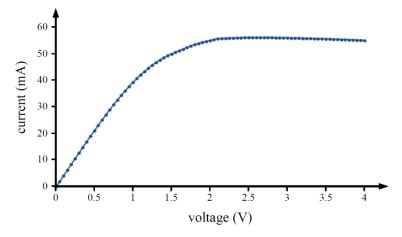

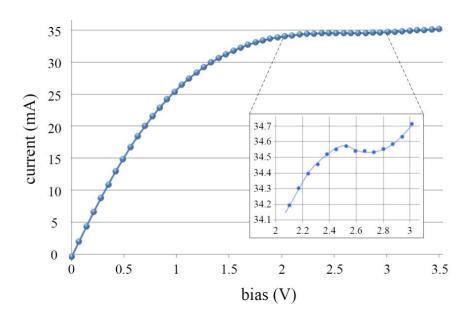

| 7.10 | Current - voltage characteristic for planar Gunn diode with 1.3 $\mu$ m $L_{ac}$                                               |

|      | implemented on the pHEMT wafer [156]                                                                                           |

| 7.11 | Measured spectrum of a planar Gunn diode with 1.3 $\mu$ m $L_{ac}$ implemented on the pHEMT substrate [156]                    |

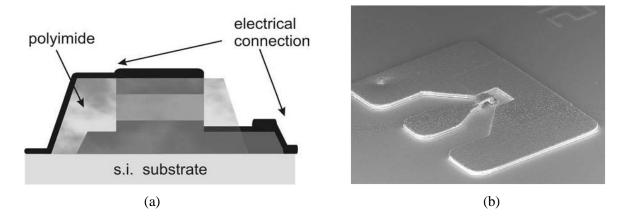

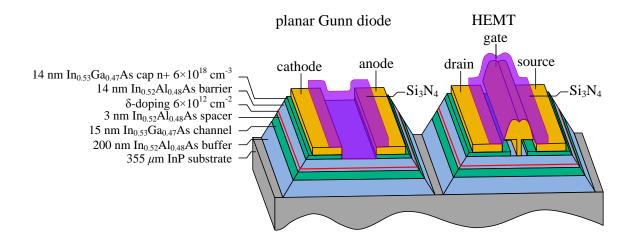

| 7.12 | Cross-section illustration of the integrated planar Gunn diode and the HEMT 140                                                |

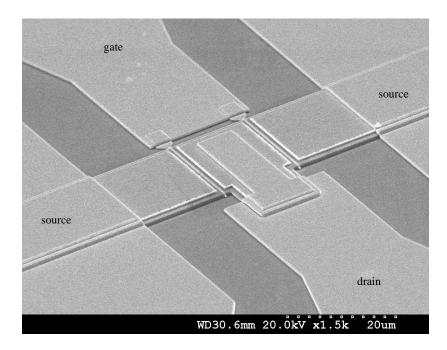

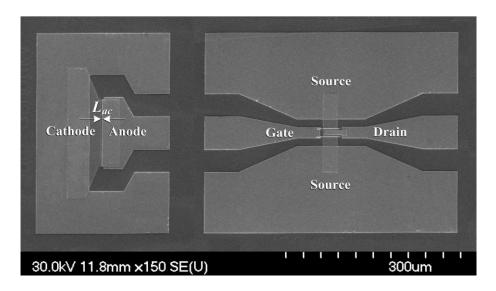

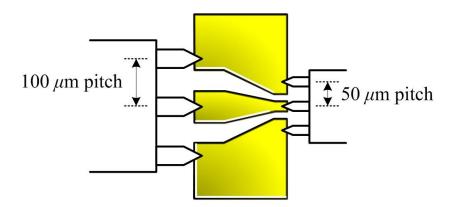

| 7.13 | SEM picture of the two devices fabricated side by side on the InP HEMT substrate.                                              |

|      | The $L_{ac}$ of the planar Gunn diode is equal to 1.3 $\mu$ m and the width is 120 $\mu$ m. The                                |

|      | 70 nm T-gate HEMT is 12.5 $\mu$ m wide with 1.5 $\mu$ m drain to source separation 141                                         |

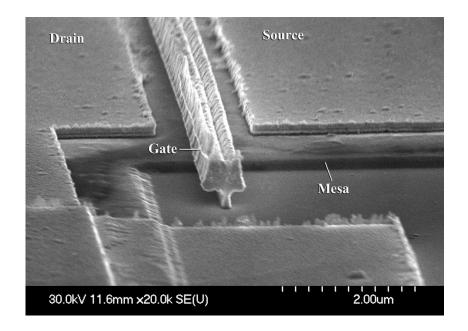

| 7.14 | Detailed image of the 70 nm T-gate HEMT with 1.5 $\mu$ m drain to source separation 142                                        |

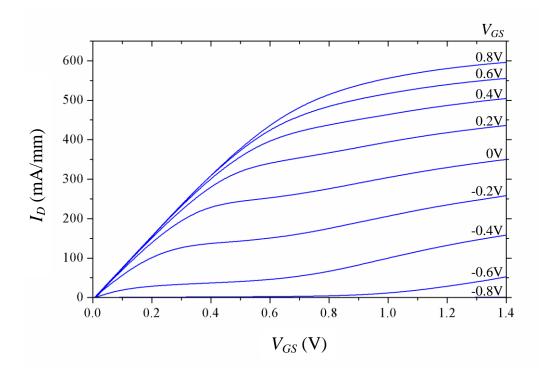

| 7.15 | $I_D$ - $V_{DS}$ characteristics for a 70 nm T-gate device with 12.5 $\mu$ m width and 1.5 $\mu$ m drain-to-source separation. |

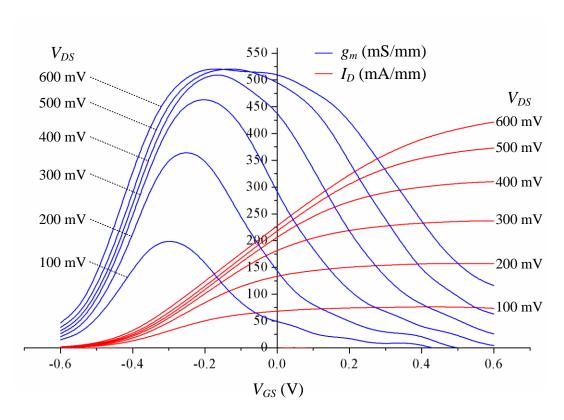

| 7.16 | Resulted $g_m$ - $V_{GS}$ and $I_D$ - $V_{GS}$ characteristics for various drain biasing. The geometry                         |

|      | of the device is the same as in Figure 8.4.                                                                                    |

| 7.17 | Characterisation of the transition pads for post-processing de-embedding 144                                                   |

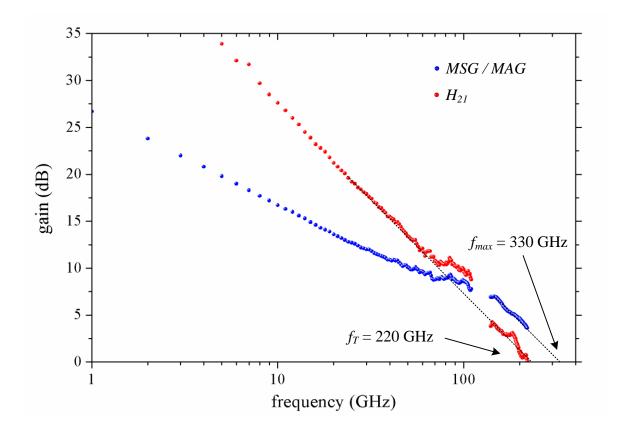

| 7.18 | $MSG/MAG$ and $H_{21}$ gain after de-embedding the transition pads                                                             |

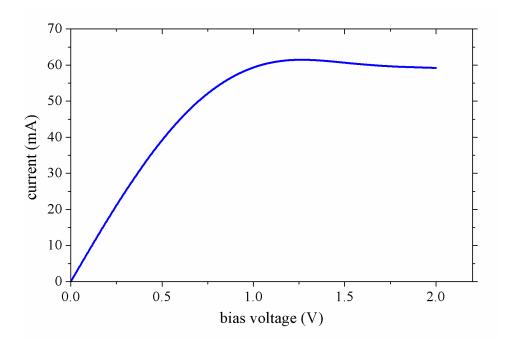

| 7.19 | Current-voltage characteristic for planar Gunn diode with 1.0 $\mu$ m $L_{ac}$ and 120 $\mu$ m width                           |

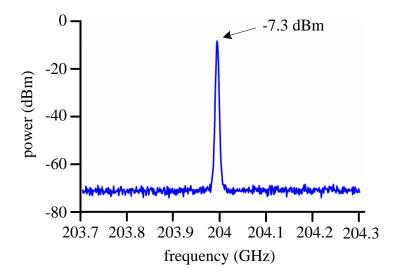

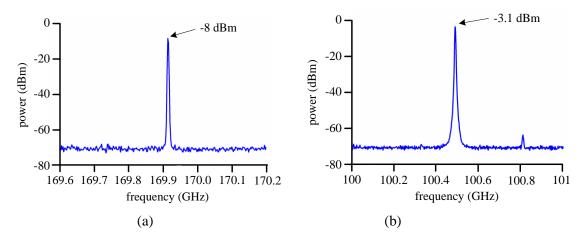

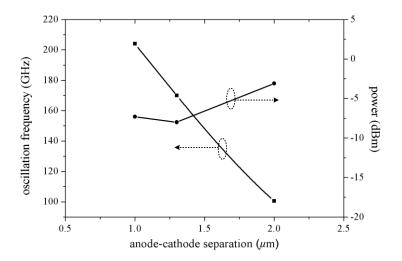

| 7.20 | The measured spectrum of a planar Gunn diode with 1.0 $\mu$ m $L_{ac}$ and 120 $\mu$ m width 146                               |

| 7.21 | The measured spectrum of planar Gunn diodes with 1.3 $\mu$ m (a) and 2.0 $\mu$ m (b) $L_{ac}$ 146                              |

| 7.22 | The oscillation frequency and the generated power as a function of $L_{ac}$                                                    |

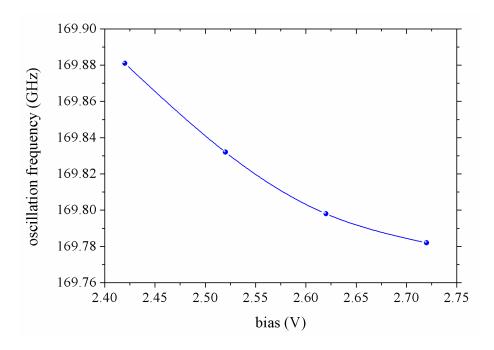

| 7.23 | Tuning of the oscillation frequency of the 1.3 $\mu$ m diode for variable bias voltages 1                                                                                                                       | 47 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

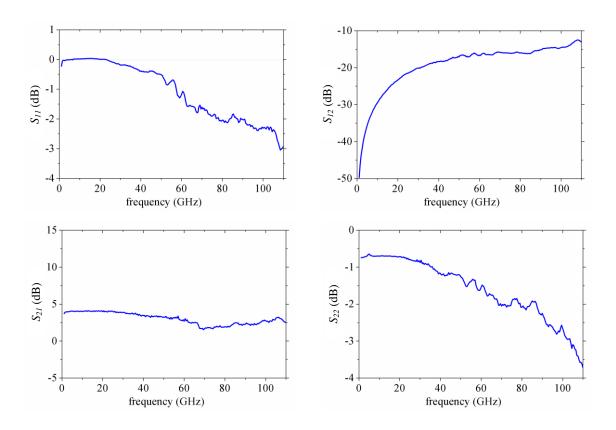

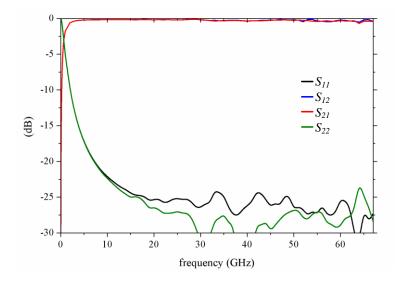

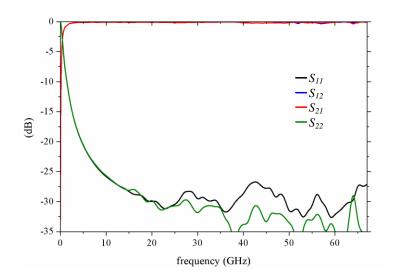

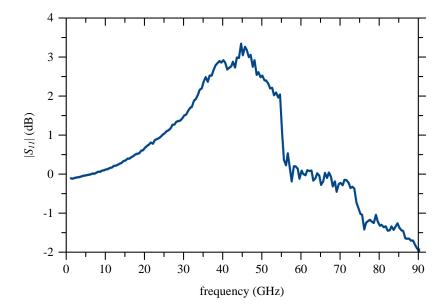

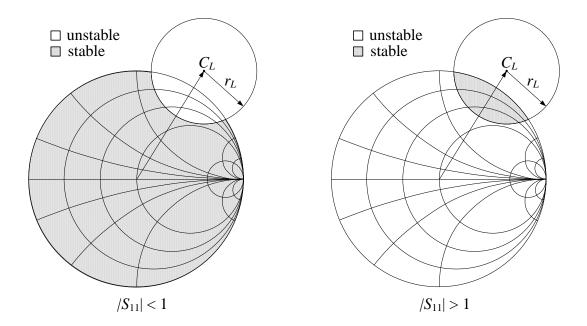

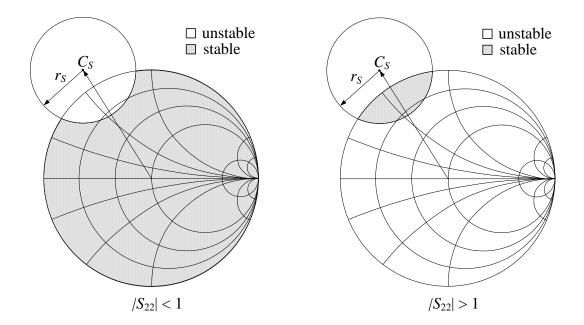

| 8.1  | S-parameters of the $In_{0.53}Ga_{0.47}As\ HEMT.$ 1                                                                                                                                                             | 51 |

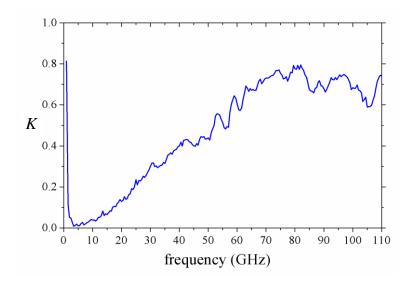

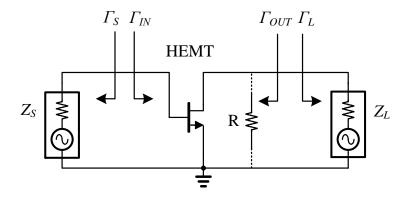

| 8.2  | Stability factor of the $In_{0.53}Ga_{0.47}As$ HEMT as a function of frequency                                                                                                                                  | 51 |

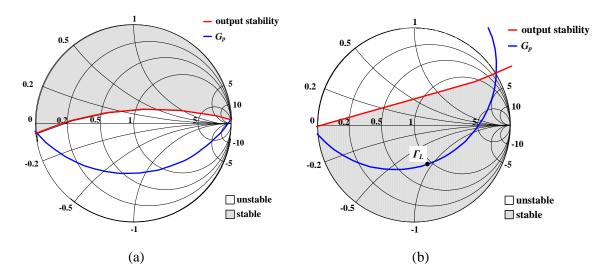

| 8.3  | The transistor as a two-port network and the addition of a parallel transistor for increased stability                                                                                                          | 52 |

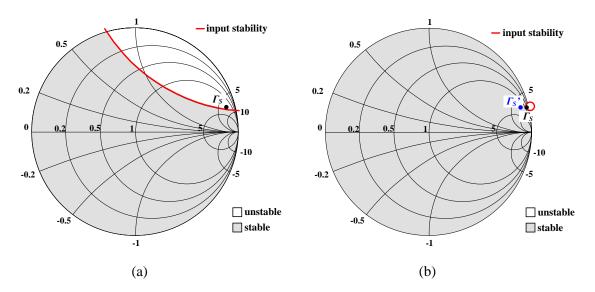

| 8.4  | Normalised impedance Smith charts of the output of the transistor before (a) and after (b) the connection of the parallel resistor                                                                              | 54 |

| 8.5  | Normalized impedance Smith charts of the input of the transistor before (a) and after (b) the connection of the parallel resistor                                                                               | 54 |

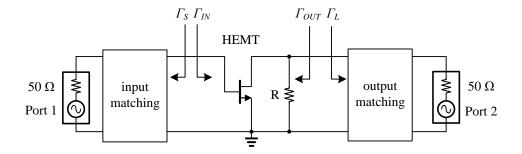

| 8.6  | The two-port network after the addition of the input and the output matching networks.                                                                                                                          | 55 |

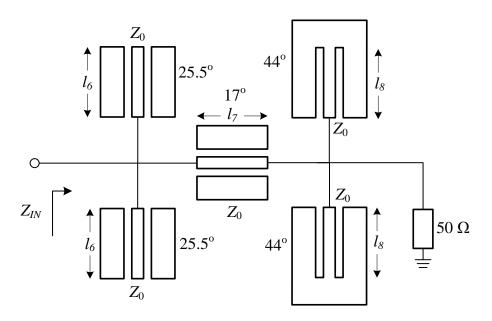

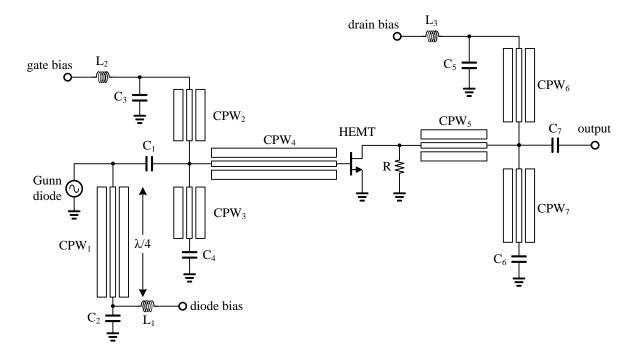

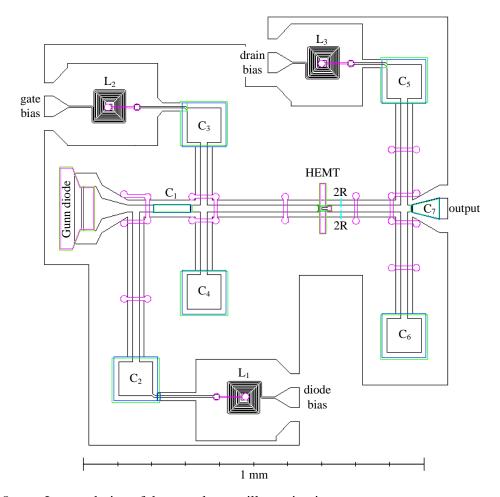

| 8.7  | Schematic representation of the complete oscillator circuit                                                                                                                                                     | 56 |

| 8.8  | Layout design of the complete oscillator circuit                                                                                                                                                                | 56 |

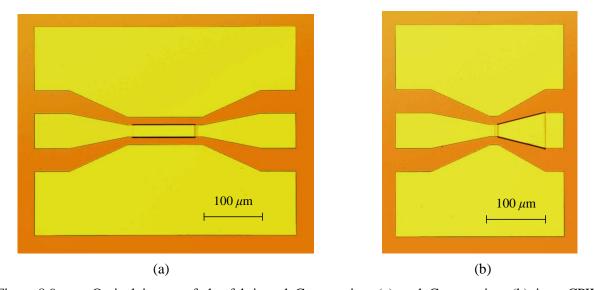

| 8.9  | Optical image of the fabricated C <sub>1</sub> capacitor (a) and C <sub>7</sub> capacitor (b) in a CPW configuration                                                                                            | 57 |

| 8.10 | Detailed SEM image of the fabricated MIM capacitor                                                                                                                                                              | 58 |

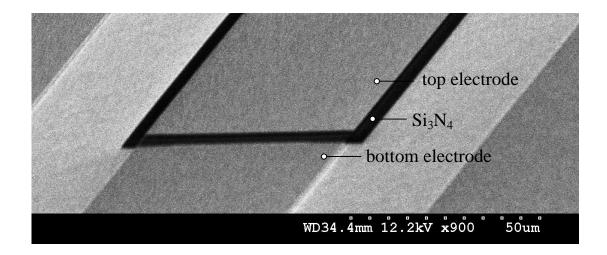

| 8.11 | Test shunt resistor in CPW configuration (a) and measured resistance at 45 GHz as a function of $W_R$ for $L_R$ equal to 15 $\mu$ m.                                                                            | 59 |

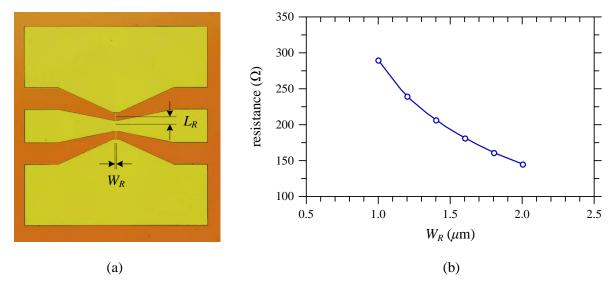

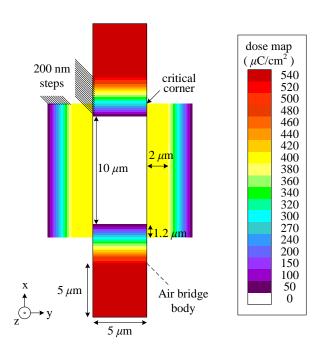

| 8.12 | Process flow of the polyimide/UVIII/PMMA technique [169]                                                                                                                                                        | 61 |

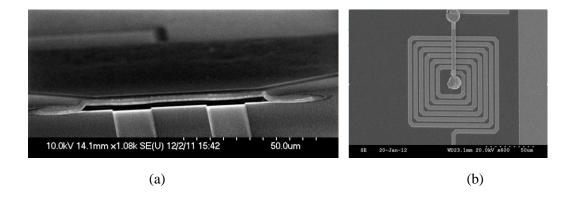

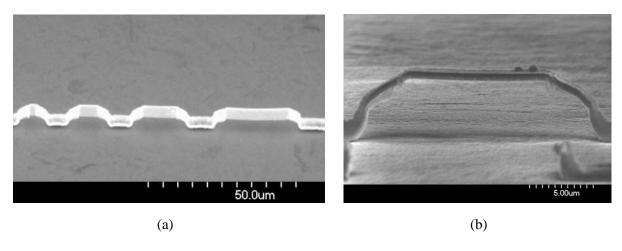

| 8.13 | Fabricated air bridges interconnecting the ground planes of the CPW transmission line (a) and the center with the second terminal of the spiral inductor (b)                                                    | 61 |

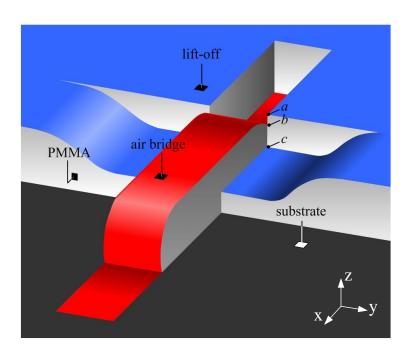

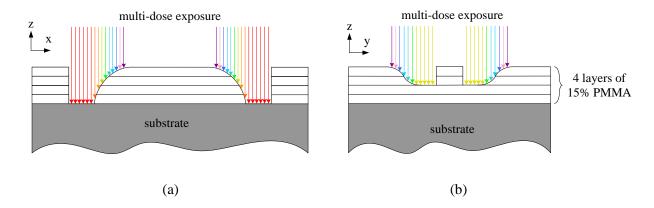

| 8.14 | The desirable 3D profile created on PMMA. Levels <i>a</i> , <i>b</i> and <i>c</i> indicate the level of the metal to be lifted-off, the level of the air bridge and the intermediate level, respectively [171]. | 62 |

| 8.15 | The multi-dose exposure of the 4-layer resist stack with respect to the x-axis (a) and the y-axis (b)                                                                                                           | 63 |

| 8.16 | Design example of air bridge. The doses corresponding to the colours of the design are illustrated at the dose map                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 8.17 | Fabricated air bridges with 20 $\mu$ m width and various lengths [171]                                                               |

| 8.18 | Process flow for the fabrication of the complete MMIC (not to scale)                                                                 |

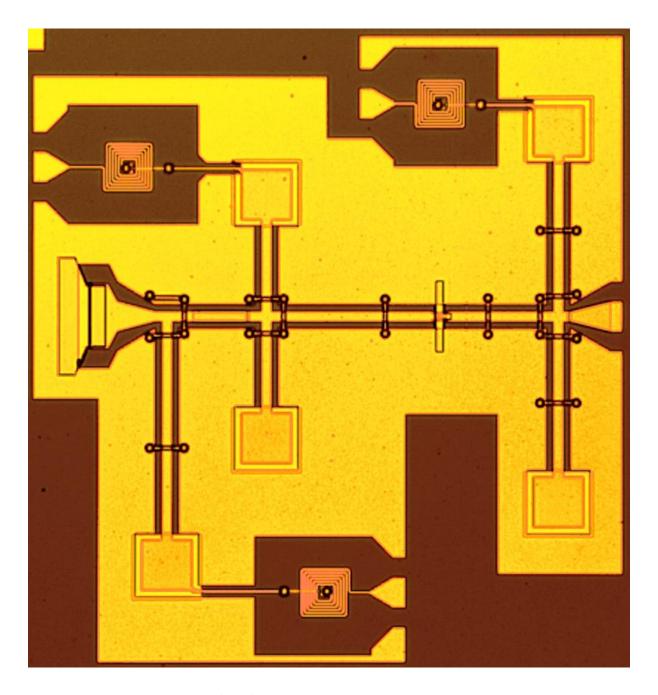

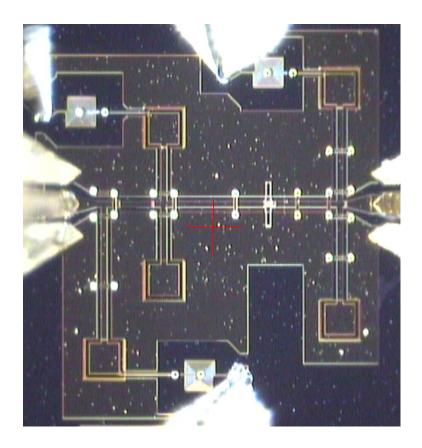

| 8.19 | Optical image of the fabricated MMIC oscillator                                                                                      |

| 8.20 | Measured S-parameters for the C <sub>1</sub> series capacitor                                                                        |

| 8.21 | Measured S-parameters for the C <sub>7</sub> series capacitor                                                                        |

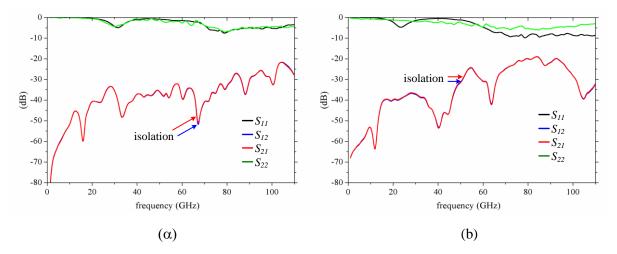

| 8.22 | Isolation between diode bias pad - gate bias pad (a) and drain bias pad - output pad (b)                                             |

| 8.23 | The amplifier circuit during the on-chip characterisation process                                                                    |

| 8.24 | S-parameter performance of the amplifier designed at 45 GHz                                                                          |

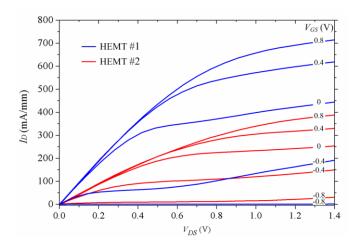

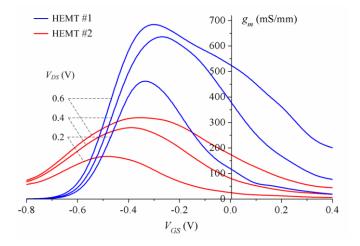

| 8.25 | Comparison of performance for two identical amplifiers fabricated on the same chip                                                   |

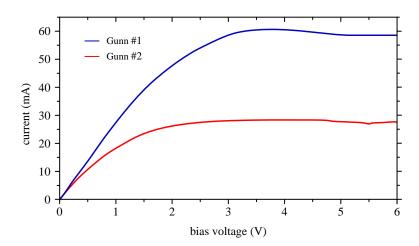

| 8.26 | Comparison of current density for two identical HEMTs fabricated on the same chip                                                    |

|      | Comparison of transconductance performance for two identical HEMTs fabricated on the same chip                                       |

| 8.28 | Comparison of current level for two identical Gunn diodes with 8 $\mu$ m $L_{ac}$ and 120 $\mu$ m width, fabricated on the same chip |

| 8.29 | The $ S_{II} $ response versus frequency for a planar Gunn diode with 8 $\mu$ m $L_{ac}$ and 120 $\mu$ m width                       |

# 1. Introduction

The first Gunn diode oscillators were demonstrated in 1963 by J. B. Gunn, on gallium arsenide (GaAs) and indium phosphide (InP) substrates [1]. Significant development of the Gunn diode technology was conducted in the subsequent years, making Gunn oscillators widely used for millimeter-wave (mm-wave, 30 - 300 GHz) applications. Currently, there is a growing interest for the mm-wave and terahertz (THz, 300 GHz - 30 THz) range of the electromagnetic spectrum. Numerous mm-wave and THz applications have been presented, such as security systems [2], anti-collision radars [3, 4], telecommunication systems [5] and astronomy instrumentation [6]. Modern Gunn diodes are required to present high output power and high frequency oscillations in the upper mm-wave (above 100 GHz) and the THz regime, in order to meet the requirements for the above applications.

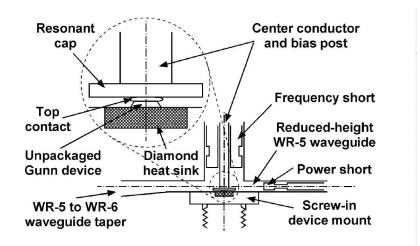

The oscillation frequency of Gunn diodes is strongly dependent on the separation between the anode and the cathode electrodes. Conventional Gunn oscillators are implemented in vertical configuration where the channel layer is sandwiched between the two contact layers. The active layer structure is typically separated from the substrate and mounted in a rectangular waveguide. Vertical devices have presented oscillations up to 77 GHz and 150 GHz for GaAs and InP based systems, respectively [3, 7]. Advanced vertical Gunn diodes compatible with coplanar waveguides (CPWs) were recently demonstrated [8], presenting reduced complexity and implementation cost. However, the maximum oscillation frequency of the vertical devices is limited by the epitaxial thickness of the channel layer.

The frequency performance of the Gunn diode was significantly improved after the introduction of the first planar Gunn diodes operating above 100 GHz by Khalid et al [9]. The anode and the cathode of the planar devices are placed on the top of the structure, similarly to the electrodes of field effect transistors (FETs). Thus, the oscillation frequency can be easily determined by the adjustment of the anode-to-cathode separation ( $L_{ac}$ ) through the lithographic design, and oscillations at various frequencies can be generated from the same chip. State of the art planar Gunn diodes based on InP reached the THz regime, were devices with  $L_{ac}$  as small as 0.6  $\mu$ m presented oscillations up to 307.5 GHz [10].

Despite the high frequency performance, planar Gunn diodes present oscillations with limited generated power. The maximum output power reported was equal to -4 dBm for operation in fundamental mode at 109 GHz, resulted from devices with 7 channel layers [11]. However, the number of the channels that contributed to current conduction was equal to 5. Therefore, there is limited number of channel layers that can be included in the layer structure and additional layers cannot further improve the power performance.

The main objective of this project is the integration of planar Gunn diodes and high electron mobility transistors (HEMTs) on the same substrate. HEMTs are well known amplifying elements with low noise characteristics that recently demonstrated power gain for frequencies above 1 THz [12]. The Gunn oscillator can benefit from a transistor based amplifier for the reinforcement of the signal power, while the low phase noise characteristics of the diode can be retained. The successful implementation of the two devices on the same chip can also lead to the implementation of more sophisticated monolithic microwave integrated circuits (MMICs).

In this work, the integration of the two devices was investigated by following two different approaches. In the first technique the individual layers of the two devices were combined in a single wafer, separated by a thick buffer layer. In the second technique, the implementation of both devices was examined using the same layer structure that was optimised for the realisation of HEMTs. Following the successful realisation of both devices on the same substrate, complete MMIC oscillators were designed and fabricated. The signals generated by planar Gunn diodes were delivered to HEMT amplifiers for the enhancement of the power characteristics.

Following this brief introduction, Chapter 2 presents the basic physical principles and the properties of the materials used in this work, such as GaAs, InP and the In<sub>x</sub>Ga<sub>1-x</sub>As ternaries. The operation of HEMTs and Gunn diodes is also described in the same chapter, based on the formation of semiconductor/semiconductor and metal/semiconductor interfaces. Chapter 3 focuses on the passive elements used in modern MMICs, such as CPWs, capacitors and inductors. In the end of the chapter, the general methodology for the design of transmission line matching networks is described. Chapter 4 presents the fabrication and characterisation techniques used in this project and Chapter 5 conducts an overview of the technology development related to Gunn diodes, HEMTs and MMIC amplifiers. The first experimental

results resulted from GaAs based substrates, are presented in Chapter 6 where both the combined wafer and the single wafer approaches are described in detail. The results from the devices fabricated on InP substrates are given in Chapter 7. In the same chapter we present details of the design procedure of the HEMT amplifier and the complete MMIC oscillator. Finally, Chapter 8 gives a conclusion of this work with the discussion of the results and the proposal of future developments.

# 2. Physics & devices

#### 2.1 Introduction

III-V semiconductor compounds have been the main choice for the implementation of devices for high frequency applications due to their superior electron mobility over silicon (Si). Heterojunction bipolar transistors (HBTs), metal-semiconductor field-effect transistors (MESFETs), high electron mobility transistors (HEMTs), Gunn diodes and resonant tunnelling diodes (RTDs), are some examples of devices based on III-V compounds. The above components have demonstrated operation at the frequency range between several tens of GHz and THz. GaAs and InP are the most studied materials for the fabrication of Gunn diodes while GaAs and InP based HEMTs demonstrate excellent characteristics at high frequencies.

In the next sections, the structure and the basic physical properties of III-V compounds is presented, with the main focus on GaAs and InP. The interfaces between semiconductors with different band gaps, known as heterojunctions, and metal - semiconductor interfaces are also described as the fundamental structures for the realisation of the active devices. The current transport properties are described afterwards. Based on the above principles, the operation of the HEMT and the Gunn diode are described in the last sections of this chapter.

#### 2.2 Materials and properties

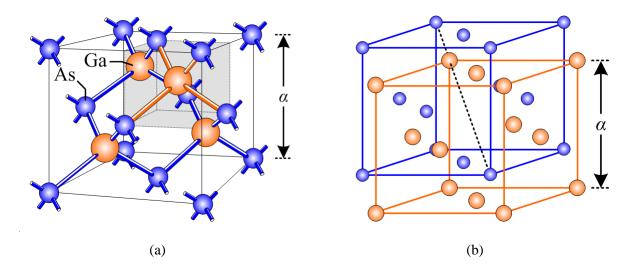

III-V compounds consist of one element from group III of the periodic table (i.e. gallium, indium) and one element from group IV (i.e. arsenic, phosphorus) in 1:1 stoichiometry. GaAs and InP are structured with the zinc-blende lattice which is shown in Figure 2.1(a). The zinc-blende structure is formed by two face-centred cubic (fcc) structures where the second one is shifted by one quarter of the cubic diagonal, placed along the diagonal of the first element (Figure 2.1(b)). The zinc-blende structure can also be considered as an fcc lattice, where two atoms (one of each group) are placed at each point of the lattice. The edge distance of the cubic unit cell determines the lattice constant  $\alpha$  of the crystal.

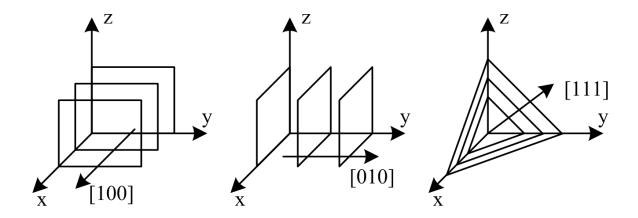

It is important to note that some crystallographic planes in the zinc-blende lattice structure can be viewed as pure monolayers consisting of single elements placed periodically. For example, the Ga atoms are alternated with the As atoms along the [100] and the [111] directions. On the contrary, equal Ga and As atoms form monolayers along the [110] direction. The geometric characteristics of the structure are taken into account during the epitaxial process for the growth of the compound at a specific crystallographic direction. The effect of etching is also dependent on the direction of the crystal as described later in Chapter 4.

Figure 2.1 The zinc-blende lattice (a) [13] and the relative positioning of the two fcc structures (b) [14].

Figure 2.2 Some crystallographic directions.

The main bonding force for the formation of the III-V compound materials is provided by the so-called covalent bond. The bond results from the outer electrons of the atoms which lie in

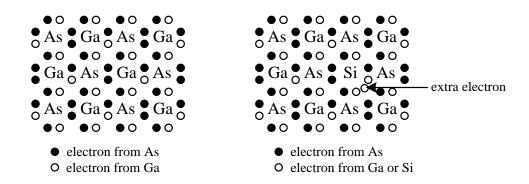

the valence band at 0 K. As an example, each atom of Ga and As provides three and five electrons respectively (Figure 2.3(a)). These eight electrons create four covalent bonds where each one is formed by two electrons with opposite spins due to the Pauli principle. When the electrons get enough thermal energy they can be excited to the conduction band and they are no longer bond electrons and instead contribute to the intrinsic carrier concentration. Practically, the number of the conducting electrons is very small in comparison with the bond electrons [15].

Doping is the effective method to significantly increase the carrier concentration in the material. Si, which belongs to group IV of the periodic table, is commonly used as an n-type dopant to increase the amount of conducting electrons. When Si replaces an atom of Ga at the crystal lattice, four electrons are introduced to the material instead of three. The three electrons are used to form the covalent bonds and the additional electron can move in the crystal (Figure 2.3(b)).

Figure 2.3 The atomic bonding in GaAs (a) and in n-type GaAs (b) [15].

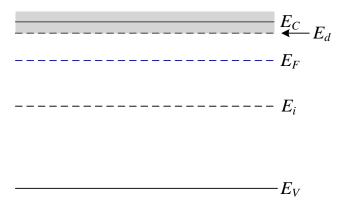

As a result of doping the material, additional energy states  $E_d$  are introduced in the forbidden energy gap. The energy difference between the  $E_d$  level and the conduction band is a few kT. Thus, at room temperature the electrons introduced by the donor have sufficient energy to transfer to the conduction band. When the level of the doping concentration is comparable to the effective density of states of the semiconductor, the interactions between the closely spaced doping atoms are increased. The discrete  $E_d$  energy state turns to a continuous band which reaches and overlaps with the minimum of the conduction band. Therefore, the gap between the valence and the conduction band effectively decreases. The decrement of the band gap is proportional to the donor concentration, while the Fermi level moves closer to the minimum of the conduction band, as illustrated in Figure 2.4 [13, 15].

The Fermi level results from the Fermi-Dirac distribution function, which provides the probability that an electron occupies an energy state at specific temperature T. The Fermi level represents the energy level that has 50% probability to be occupied and it is usually placed in the middle of the band gap for undoped materials. As mentioned above, the Fermi level moves towards the lower edge of the conduction band, for n-type doping and the energy gap between the two bands is given by:

$$E_C - E_F = kT \ln \left( \frac{N_C}{N_D} \right) \tag{2.1}$$

were k is the Boltzmann constant, T is the absolute temperature,  $N_C$  is the effective density of states in the conduction band and  $N_D$  is the donor concentration.

Figure 2.4 The continuous  $E_d$  energy states, the Fermi level  $E_F$  and the intrinsic Fermi level  $E_i$  [13, 15].

The general energy diagram illustrated in Figure 2.4 represents the energy levels when the wave vector  $\mathbf{k}$  of the electron wave function is <000>. A more informative band diagram is presented in Figure 2.5 where the conduction and the valence bands of GaAs are plotted as a function of the wave vector  $\mathbf{k}$ . It can be seen from the band diagram that GaAs is a direct band gap material, as the maximum of the valence band is aligned with the minimum of the conduction band in the <000> direction of the wave vector. Apart from the centre conduction valley, which is called the  $\Gamma$  valley, two more conduction valleys appear in the <111> and the <100> directions. These are the satellite L and X conduction valleys. The existence of the

satellite valleys is fundamental for the generation of the Gunn oscillations, as explained in Section 2.6 where the operation of the Gunn diode is analysed.

Figure 2.5 The simplified energy diagram of GaAs and InP [16].

The energy diagram of the material also provides information of the effective mass of the electrons. When electrons travel in free space they only experience the effect of the applied fields. However, electrons travelling inside crystals are affected additionally by the periodic potential caused by the atoms in the lattice. Effectively, the mass of these electrons, which is called the effective mass  $m_e^*$ , is a smaller fraction of the mass for electrons travelling in free space. Taking the assumption that the conduction valleys have a parabolic shape, the effective mass can be calculated by:

$$m_e^* = \hbar^2 \left(\frac{d^2 E}{dk^2}\right)^{-1}$$

(2.2)

Thus, the curvature of the conduction valley is inversely proportional to the effective mass. As an example, the L and X valleys are more flat than the  $\Gamma$  valley and the electrons lying there have higher effective masses than the ones in the centre conduction valley.

The energy diagrams are characteristic of the materials, depending on the periodic potentials in the crystal. Due to these potentials the effective mass of electrons in the centre conduction valley of GaAs is equal to 0.063 times the electron mass in free space [17]. As the effective mass strongly determines the mobility of the carriers, GaAs has a high electron mobility equal to approximately 9200 cm<sup>2</sup>/V·s and for this reason it is selected for high-frequency applications. For comparison purposes, it is noted that the effective mass of electrons in Si is equal to 0.26 times the free space electron mass and the electron mobility is equal to 1450 cm<sup>2</sup>/V·s.

Table 2.1 summarises some of the basic parameters for GaAs and InP. Gallium nitride (GaN) is also presented here as the material which currently attracts lot of attention for high-power applications. The ability of GaN devices to deliver high amounts of power results from the high break down field due to the large band gap of the material. The parameter values of GaN presented in Table 2.1 correspond to the zinc-blende version of the crystal which is more suitable for high frequency applications over the wurtzite crystal structure [18]. The basic parameters of Si are also presented as a reference to a more conventional technology. All the parameters are referred to room temperature conditions.

| Parameter                                                          | GaAs                 | InP                  | GaN                  | Si                   |

|--------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|

| Crystal structure                                                  | zinc-blende          | zinc-blende          | zinc-blende          | diamond              |

| Lattice constant (Å)                                               | 5.65                 | 5.86                 | 4.52                 | 5.43                 |

| Band gap (eV)                                                      | 1.42                 | 1.34                 | 3.2                  | 1.12                 |

| Effective mass $m_e^*/m_0$ at central valley                       | 0.063                | 0.079                | 0.13                 | 0.26                 |

| Low field mobility (cm <sup>2</sup> /V·s)                          | 9200                 | 5900                 | 1000                 | 1450                 |

| Breakdown field (V/cm)                                             | ~4.105               | ~5.105               | ~5·10 <sup>6</sup>   | ~3.105               |

| Effective density of states in conduction band (cm <sup>-3</sup> ) | 4.7·10 <sup>17</sup> | 5.8·10 <sup>17</sup> | 1.2·10 <sup>18</sup> | 2.8·10 <sup>19</sup> |

Table 2.1 Basic parameters of GaAs [19, 20], InP [20, 21], GaN [22, 23] and Si [17].

#### 2.3 Current transport

When no external electric field is applied to the semiconductor, conducting electrons move randomly in every direction due to their thermal energy. The kinetic energy of the electrons is equal to their thermal energy as:

$$\frac{1}{2}m_e^* u_{th}^2 = \frac{3}{2}kT \tag{2.3}$$

where  $u_{th}$  is the average thermal velocity [24]. If the crystal structure is uniform, there is an equal possibility for the electron to move in every direction. Therefore, the total shift of the electron inside the material is zero. During the random thermal movement, electrons undergo various kinds of scattering interactions inside the crystal. The collisions mainly occur with the atoms of the crystal and the dopants. The former is known as lattice scattering and the latter as impurity scattering.

Lattice scattering is generally referred to collisions between the electrons and the lattice. At finite temperatures, the molecules of the crystal vibrate around their central positions. As the temperature of the material increases, the vibrations become more intense affecting the periodicity of the crystal potential. As a result, lattice scattering becomes more important at high temperatures where carrier mobility degrades significantly. The out-of-phase vibrations of the atoms, which are known as optical phonon modes, result in high frequency oscillations and have relatively high associated energy. The in-phase vibrations of the atoms, known as acoustic phonon modes, occur at low frequencies over a wide spectrum. Both modes of vibration increase the interaction with the electrons in the crystal, which is known as phonon scattering. Since optical phonons have relatively high energy, optical phonon scattering can cause significant changes in the momentum of the electrons. Due to the large change of momentum, electrons can scatter to different energy valleys and the phenomenon is known as inter-valley scattering [25].

Impurity scattering is caused by the ionised donors (for the n-type example) where the impurities cause perturbations to the travelling electrons, due to the additional Coulomb interactions. Consequently, the impurity scattering effect becomes dominant at high doping concentrations. The correlation between the impurity concentration and the mobility in GaAs at room temperature in depicted in Figure 2.6 [24]. For impurity concentrations up to  $10^{16} \, \text{cm}^{-3}$  the material can be considered as lightly-doped and the mobility does not degrade

significantly. In this region, the mobility is limited by lattice scattering. When doping exceeds the value of  $10^{18}$  cm<sup>-3</sup> the mobility decreases by one order of magnitude. The hole mobility appears lower than the electron mobility, because of the higher effective mass of the holes. One significant difference between lattice and impurity scattering is that the latter is less effective at high temperatures. In that case, the carriers gain higher thermal velocity and they are less affected by the Coulomb forces as they travel faster through the lattice.

The mean free time  $\tau_c$  shows how often a carrier is expected to scatter and is equal to the average time between the occurring collisions. The total probability of a possible collision is equal to the sum of the probabilities for collisions due to the individual scattering mechanisms. Thus:

$$\frac{1}{\tau_c} = \frac{1}{\tau_{c,lattice}} + \frac{1}{\tau_{c,impurity}}$$

(2.4)

Figure 2.6 Mobility of GaAs at 300 K as a function of impurity concentration [24].

As described above, the average velocity, caused by the random thermal movement of the electrons, is zero. When an external electric field is applied to the material, electrons gain an additional velocity which is called drift velocity  $u_{drift}$ . Then, a force equal to  $-q\mathcal{E}$  causes the acceleration of the electrons to the opposite direction of the electric field  $\mathcal{E}$ . Therefore, the momentum of the electrons is given by [24]:

$$m_e^* u_{drift} = -q \mathcal{E} \tau_c \tag{2.5}$$

After solving with respect to the drift velocity:

$$u_{drift} = -\mu_n \mathcal{E} \tag{2.6}$$

where  $\mu_n$  is the electron mobility equal to:

$$\mu_n = \frac{q\tau_c}{m_e^*} \tag{2.7}$$

The drift current density is given by:

$$J_{drift} = qnu_{drift} \tag{2.8}$$

As described in Section 2.2, mobility is a characteristic property of the material which is determined by the periodic potentials in the crystal. Here, mobility shows how strongly the electron transport is affected when an external electric field is applied to the semiconductor.

Charge transport occurs even if no external electric field is applied, when the electron concentration inside the semiconductor is not uniform. Electrons flow from the areas with high concentration towards the areas with low concentration until the non-uniformity is compensated. The so-called diffusion current, can also result from the placement of two different materials together. The existence of the diffusion current can be explained as a result of the non-uniform thermal movement of the electrons. Examining the cross section of a uniform material, the electrons arriving from the left and from the right side are equal. Consequently, the individual currents cancel each other and the total current is zero. Assuming that the electron concentration is higher at the right side of a semiconductor, the carriers arriving at the cross section from the left side are less than the ones arriving from the right side. Thus, the diffusion current is created while electrons are moving towards the side of the semiconductor with lower concentration. The diffusion current density  $J_n$  is proportional to the gradient of the carrier concentration as [24]:

$$J_n = qD_n \frac{dn}{dx} \tag{2.9}$$

where  $D_n$  is the diffusivity of the material which is related to the mobility through the

Einstein relation [24]:

$$D_n = \frac{kT}{q} \mu_n \tag{2.10}$$

#### High field phenomena

Equation 2.6 indicates that the drift velocity is proportional to the external electric field. However, this assumption is valid only for a relatively low electric field, where the drift velocity is significantly lower than the thermal velocity  $(1\cdot10^7 \text{ V/cm})$  at room temperature for semiconductors [15]). Under these conditions, the drift velocity and the thermal velocity can be considered as independent. When  $\mathcal{E}$  increases and  $u_{drift}$  approaches the value of  $u_{th}$ , the relation between  $u_{drift}$  and  $\mathcal{E}$  diverges from the linear Equation 2.6. Figure 2.7 presents the drift velocity versus the electric field for a heavily doped sample of GaAs with  $5\cdot10^{18} \text{ cm}^{-3}$  n-type doping concentration. As  $\mathcal{E}$  increases and  $u_{drift}$  becomes comparable to  $u_{th}$ , the scattering effects play a significant role to the electron transport. The energy given by the field is no longer transformed to an additional kinetic energy of the carriers but is consumed through the various scattering mechanisms. For highly doped materials, impurity scattering becomes dominant and the drift velocity reaches a saturation value  $u_{sat}$  as depicted in Figure 2.7 [15].

For lightly doped materials, the drift velocity also increases in a linear fashion at low electric fields but the slope and the  $u_{sat}$  are higher due to the reduced impurity scattering. However, when exceeding a critical electric field the behaviour of the drift velocity is different for materials like GaAs and InP in comparison with Si. As described in Section 2.2, the energy diagrams of GaAs and InP present more than one conduction valley in contrast with Si which is a single-conduction valley material. The curvatures of the conduction valley determines the effective mass and as a consequence the mobility of the electrons lying there.

When a small electric field is applied to the semiconductor, electrons gain sufficient energy and transfer from the valence band to the centre conduction valley  $\Gamma$ , as depicted in Figure 2.8(a). Therefore,  $u_{drift}$  increases monotonically with  $\mathcal{E}$ . If  $\mathcal{E}$  is higher than a critical value, electrons have enough energy to overcome the energy gap between the centre conduction valley  $\Gamma$  and the satellite valley L transferring to the latter. The threshold field is equal to 3.5 kV/cm and 10.5 kV/cm and the energy separation between the two valleys is 0.31 eV and 0.53 eV for GaAs and InP, respectively [16].

The overall mobility of the system is equal to the average mobility of the carriers as [24]:

$$\overline{\mu} = \frac{\mu_{\Gamma} n_{\Gamma} + \mu_{L} n_{L}}{n_{\Gamma} + n_{L}} \tag{2.11}$$

The drift velocity is given by:

$$u_{drift} = -\overline{\mu}\mathscr{E} \tag{2.12}$$

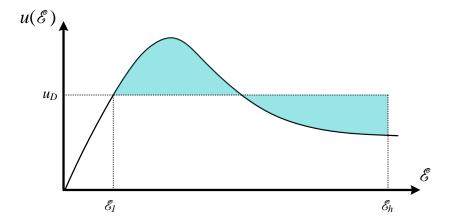

where  $\mu_{\Gamma}$  and  $\mu_{L}$  represent the mobilities and  $n_{\Gamma}$  and  $n_{L}$  are the number of carriers at the two conduction valleys. For both GaAs and InP, electrons transferred to the L valley have a lower mobility as the new valley has a smaller curvature (Figure 2.8). As a result, the overall mobility of the carriers decreases and so does the drift velocity. Under these conditions, the material shows a negative differential resistance (NDR). The phenomenon is also known as the Gunn effect and it is fundamental for the formation of Gunn oscillations as presented in Section 2.6. The NDR appears only when the material is lightly doped otherwise the drift velocity degradation starts from lower electric fields due to the impurity scattering as depicted in Figure 2.7. Figure 2.9 illustrates the drift velocity versus the electric field for GaAs, InP and Si [26]. GaAs and InP show an NDR after the critical electric field which is higher for InP which presents a higher energy difference between the  $\Gamma$  and the L valley. As Si is a single-conduction valley material, the Gunn effect does not exist.

Figure 2.7 Electron drift velocity as a function of the external applied field for heavily doped  $(5\cdot10^{18} \text{ cm}-3) \text{ GaAs } [15].$

Figure 2.8 Electron distributions at the conduction valleys under various applied electric fields for multi-valley semiconductors [24].

Figure 2.9 Drift velocity as a function of the external applied field for various semiconductors [26].

For very high electric fields, exceeding the NDR region, the current starts increasing again as a result of the impact ionisation effect which is also known as the avalanche process. This is caused by the electron-hole pairs that are generated after the interaction of high-energy carriers with the lattice. If the accelerated electrons get enough energy from the applied field, they can break valence bonds after colliding with the lattice. In this way, an electron-hole pair is produced as the bond electron is ionised to the conduction valley leaving an empty space behind. The ionised electron gets highly accelerated before the next collision where a new electron-hole pair is generated. As a consequence, the current of the semiconductor starts rising again as more electrons transfer to the conduction valley.

# 2.4 Heterojunctions

Heterojunctions are formed when two materials with similar lattice constants and different band gaps are brought together to form a contact which is also known as heterostructure. The deployment of modern epitaxial growth techniques as metal organic chemical vapour deposition (MOCVD) and molecular beam epitaxy (MBE) was essential for the realisation of heterojunctions. Modern optoelectronic and microwave active devices resulted from the development of band gap engineering.