https://theses.gla.ac.uk/

Theses Digitisation:

https://www.gla.ac.uk/myglasgow/research/enlighten/theses/digitisation/

This is a digitised version of the original print thesis.

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses <u>https://theses.gla.ac.uk/</u> research-enlighten@glasgow.ac.uk

# Next Generation Automotive Embedded Systems-on-Chip and Their Applications

# **Executive Summary**

Mohamed Anas

A portfolio submitted to

The Universities of

Edinburgh

Glasgow

Heriot Watt

Strathclyde

for the Degree of

# Doctor of Engineering in System Level Integration

© Mohamed Anas

March 2005

This copy of the portfolio has been supplied on condition that anyone who consults it is understood to recognise that the copyright rests with its author and that no quotation from this themed portfolio and no information derived from it may be published without the prior written consent of the author or the University (as may be appropriate). ProQuest Number: 10800629

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10800629

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

Portfoho I

### Abstract

It is a well known fact in the automotive industry that critical and costly delays in the development cycle of powertrain<sup>1</sup> controllers are unavoidable due to the complex nature of the systems-on-chip used in them. The primary goal of this portfolio is to show the development of new methodologies for the fast and efficient implementation of next generation powertrain applications and the associated automotive qualified systems-on-chip. A general guideline for rapid automotive applications development, promoting the integration of state-of-the-art tools and techniques necessary, is presented. The methods developed in this portfolio demonstrate a new and better approach to co-design of automotive systems that also raises the level of design abstraction.

An integrated business plan for the development of a camless engine controller platform is presented. The plan provides details for the marketing plan, management and financial data.

A comprehensive real-time system level development methodology for the implementation of an electromagnetic actuator based camless internal combustion engine is developed. The proposed development platform enables developers to complete complex software and hardware development before moving to silicon, significantly shortening the development cycle and improving confidence in the design.

A novel high performance internal combustion engine knock processing strategy using the next generation automotive system-on-chip, particularly highlighting the capabilities of the first-of-its-kind single-instruction-multiple-data micro-architecture is presented. A patent application has been filed for the methodology and the details of the invention are also presented.

Enhancements required for the performance optimisation of several resource properties such as memory accesses, energy consumption and execution time of embedded powertrain applications running on the developed system-on-chip and its next generation of devices is proposed. The approach used allows the replacement of various software segments by hardware units to speed up processing.

<sup>&</sup>lt;sup>1</sup> *Powertrain:* A name applied to the group of components used to transmit engine power to the driving wheels. It can consist of engine, clutch, transmission, universal joints, drive shaft, differential gear, and axle shafts.

#### Acknowledgements

I would like to thank my supervisors Professor David R. S. Cumming and Dr. Bill Nailon for their guidance and advice. I am very grateful to David and Bill for providing the intellectual stimulation for the projects carried out in this area and their consistently well focused, yet nonetheless visionary, critique of my work.

I would also like to thank Dr. Franz Fink, vice president and general manager, Freescale Semiconductors, formerly Motorola Semiconductor Products Sector, for many discussions at the outset of my EngD to strategically define various aspects of my industrial projects. Various cross functional team members, particularly my industrial supervisor Robin Paling, 32-bit Embedded Controller Division, has provided much encouragement and support together with an unerring desire to meet all my goals, create real-time demonstrator platform to prove the usefulness of next generation automotive advanced single instruction multiple data systems-on-achip – one of the greatest strengths of this department. I would also like to give special thanks to the systems engineering team members with whom I have worked closely throughout my EngD and who provided an excellent intellectual "sparing partner".

A very large number of people within the universities of Edinburgh, Glasgow, Heriot-Watt and Strathclyde, and particularly from the Institute for System Level Integration, have contributed to the development of various demonstration platforms. I would like to thank the 32-bit Embedded Controller Division of Freescale Semiconductors for their technical and financial support.

And last but not least, for their support and understanding over the years, I thank my family and friends.

## Preface

This portfolio presents work undertaken by the author while working in the 32-bit Embedded Controller Division of Motorola SPS, presently known as Freescale Semiconductors. A writing style has been chosen that is fairly explanatory and, it is hoped, easy to read. The aim throughout has been to take a reader, who may not be an expert in the field of automotive systems-on-a-chip and their applications, through the work carried out in such a manner that at the end he or she may have gained a good understanding of what has been done and glimpsed the future possibilities of this exciting area. The author is *convinced* of both the usefulness and practicality of the basic idea of advanced single instruction multiple data system-on-chip and their applications with tightly coupled digital signal processing functionality: it is hoped that some of this enthusiasm for the work has been captured in the contents of this portfolio and imparted to its readers.

## **Journal Publications and Conference Proceedings**

- Mohamed Anas, D. R. S. Cumming, W. H. Nailon and R. J. Paling, "Fast Internal Combustion Knock Processing Algorithm Using an Automotive PowerPC System-on-Chip," IEEE *Transaction on Vehicular Technology*, accepted for publication, manuscript ID VT-2004-00099, (November 2004).

- Mohamed Anas, D. R. S. Cumming, W. H. Nailon and R. J. Paling, "Fast Internal Combustion Knock Processing Algorithm Using an Automotive PowerPC System-on-Chip," proceedings of the 5<sup>th</sup> Australasian Control Conference, Automotive Applications, Melbourne, Australia, vol. 1, pp. 30 – 38, (July 19-23 2005).

- 3. Mohamed Anas, D. R. S. Cumming and W. H. Nailon, "System Level Design of a Controller Platform for a Camless, Electromagnetic Actuator Driven Next Generation Car Engine," IEEE *Transaction on Vehicular Technology*, submitted for review.

# System-on-Chip Book Chapter

Next Generation Automotive PowerPC Von-Neumann Cache Memory: An Architectural Overview and Efficient Use in Fast Time Critical Applications Development, November 22, 2002.

# **Key Awards and Achievements**

- 1. International IEE Research and Best Presentation Medal and Award for the value of £5000 May 2003

- Best conference presentation award, 5<sup>th</sup> Australasian Control Conference, Melbourne, Australia, July 2005.

## **Industrial and Academic Conference Presentations**

- Mohamed Anas, Next Generation Automotive SoCs and their Application, IEE International Hudswell Research Conference, Overall Best Presentation Award and Winner of £ 5000 Scholarship, Savoy Place, London, (May 2002).

- 2. Mohamed Anas, Distributed Camless Engine Controller Platform, SAE TOPTEC Congress 2002, Ann Arbour, USA, (September 23-26, 2002).

- Mohamed Anas, Next Generation Automotive Powertrain Systems-on-a-Chip and Their Applications, Motorola TechTalk, East Kilbride, Scotland, (February 21, 2003).

- Mohamed Anas, Next Generation Automotive Powertrain Systems-on-a-Chip and Their Applications, Motorola Smart Networks Developer Forum, Hyatt Regency Hotel, Dallas, Texas, USA, (March 20-23, 2003).

- 5. Mohamed Anas, Fast Internal Combustion Engine Knock Processing using an Automotive Qualified SoC, Automotive TechTalk, East Kilbride, Scotland, (August 21, 2003).

- Mohamed Anas, Fast Internal Combustion Engine Knock Processing, 5<sup>th</sup> Australasian Control Conference, Automotive Applications, Melbourne, Australia, (July 19-23 2004).

- 4. Mohamed Anas, Various Major Customer Presentations and Seminars

## **Patents Pending**

- Mohamed Anas, "Distributed Electromagnetic Actuator Driven Camless Engine Controller Platform," US Patent Pending

- 2. Mohamed Anas, "Fast Internal Combustion Engine Knock Processing Methodology," US Patent Pending

## **Glossary of Products Used**

- 1. Metrowerks CodeWarrior Development Suite -Compiler v1.5 (MW v1.5)

- 2. Greenhills Compiler, Functional Simulator and Debugger v4.0.1 (GHS v4.0.1)

- 3. WindRiver Diab Compiler and Functional Simulator v5.0

- 4. MATLAB, Simulink and Stateflow Release 12 and Release 13

- 5. Microsoft Office Professional Suite 2000 and XP

- 6. LAUTERBACH TRACE32 BDM Debugger for PowerPC

- 7. SIMD SoC Core Cycle Accurate Architectural Modelling Environment

- 8. Various MPC5xx automotive qualified evaluation boards

- 9. MPC5554 automotive qualified evaluation board

- 10. HiWare Functional Simulator v2.0

- 11. Microsoft Project 2000

# **Table of Contents**

| Abstract      | ü                                                                  |

|---------------|--------------------------------------------------------------------|

| Preface       | iv                                                                 |

| Journal Publ  | ications and Conference Proceedingsv                               |

| System-on-C   | hip Book Chapterv                                                  |

| Key Awards    | and Achievementsv                                                  |

| Industrial an | d Academic Conference Presentationsvi                              |

| Patents Pend  | lingvi                                                             |

| Glossary of I | Products Usedvii                                                   |

|               | action11                                                           |

| 1.1           | Systems-on-Chip in Modern Cars11                                   |

| 1.2           | Portfolio Structure and Original Contributions14                   |

| 2 Industr     | ial Context                                                        |

| 2.1           | SoCs in Embedded Automotive Applications18                         |

| 2             | .1.1 Automotive Powertrain Controllers                             |

| 2             | .1.2 Development of Powertrain Controllers                         |

| 3 EngD        | Research Contribution22                                            |

| 3.1           | Integrated Business Plan22                                         |

| 3.2           | An Overview of the SoC Developed24                                 |

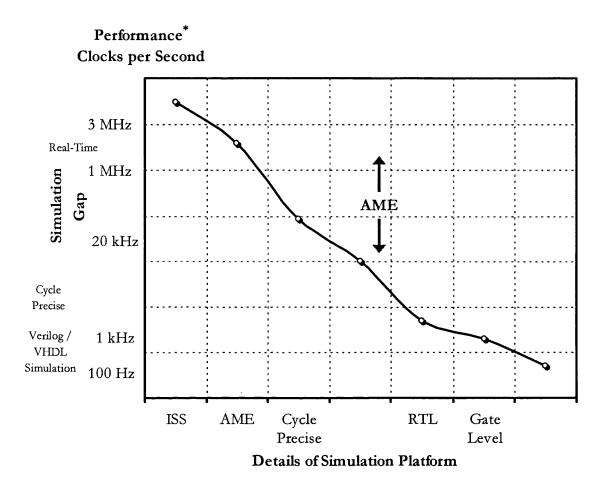

| 3.3           | An Architectural Modelling Environment for the PowerPC SoC26       |

| 3.4           | Electromagnetic Actuator Driven Camless Engines                    |

| 3             | .4.1 Introduction                                                  |

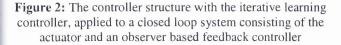

| 3             | .4.2 Construction and Operation of the Electromechanical Actuator  |

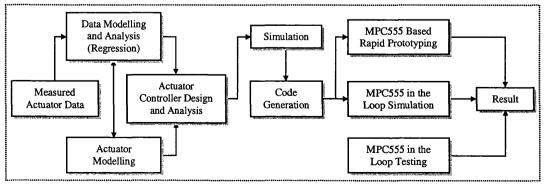

| 3             | .4.3 Design and Implementation of the Actuator Controller Platform |

| 3             | .4.4 The Camless Engine Actuator Controller Platform               |

| 3             | .4.5 Results and Concluding Remarks                                |

| 3.5           | Embedded Von-Neumann On-Chip SoC Cache35                           |

| 3.6           | Fast Internal Combustion Engine Knock Processing                   |

| 3             | .6.1 Introduction                                                  |

| 3             | .6.2 Impact of Knock and its Real-Time Processing                  |

| 3             | .6.3 Modelling the Pre-Silicon Knock Processing Platform           |

| 3.                                                         | 6.4                                              | SoC Based Hardware Knock Evaluation Platform                  | 39  |

|------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------|-----|

| 3.                                                         | 6.5                                              | Knock Processing Methodology – Data and Algorithmic Flow      | 40  |

| 3.                                                         | 6.6                                              | Measured Results and conclusions                              | 41  |

| 3.7                                                        | ]                                                | Next Generation Powertrain SoCs and Their Applications        | 43  |

| 3.                                                         | 7.1                                              | Introduction                                                  | 43  |

| 3.                                                         | 7.2                                              | Methodology and Challenges Faced                              | 44  |

| 3.                                                         | 7.3                                              | Suggestions and Conclusions                                   | 45  |

| 3.8                                                        | ]                                                | Portfolio Conclusions and Future Direction                    | 46  |

| 3.                                                         | 8.1                                              | Summary of Industrial Research Undertaken                     | 46  |

|                                                            | Bus                                              | siness Plan for the SoC Development of Camless Engine Control | .46 |

| An Architectural Modelling Environment for the PowerPC SoC |                                                  |                                                               |     |

| Development of a Camless Engine Controller Platform        |                                                  |                                                               |     |

| Fast Internal Combustion Engine Knock Processing           |                                                  |                                                               |     |

|                                                            | Embedded Von-Neumann On-Chip PowerPC SoC Cache51 |                                                               |     |

| Next Generation Powertrain SoC Performance Requirements    |                                                  | .51                                                           |     |

|                                                            | Fut                                              | ture Work                                                     | .52 |

| 3.9                                                        | ]                                                | References                                                    | 55  |

# List of Figures and Tables

| Figure 1.1: Performance Demanding SoC Controlled Modules in a Modern Car?                 | 12 |

|-------------------------------------------------------------------------------------------|----|

| Figure 1.2: Synopsis of Themed Portfolio                                                  | 17 |

| Figure 2.1: Powertrain Controller Software V Development Cycle                            | 20 |

| Figure 3.1: Camless Project – Financial Summary                                           | 23 |

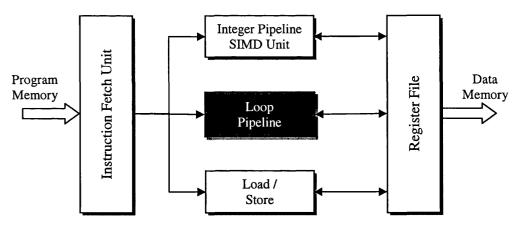

| Figure 3.2: An Overview of the SIMD SoC Developed                                         | 25 |

| Figure 3.3: Application Binary Characterisation Process Using the AME                     | 28 |

| Figure 3.4: The Electromechanical Actuator                                                | 30 |

| Figure 3.5: Configuration of the Actuator Iterative Learning Controller                   | 31 |

| Figure 3.6: Experimental Set-up of the Actuator Controller Platform                       | 33 |

| Figure 3.7: Valve Position Control Results based on the ILC (k $\varepsilon$ [1, 13, 24]) | 34 |

| Figure 3.8: Torque Production with Mechanical Cam and Camless Engine                      | 34 |

| Figure 3.9: Cylinder Pressure versus Crank Angle (CA)                                     | 37 |

| Figure 3.10: Pre-Silicon Knock Functional and Behavioural Simulation Platform             | 38 |

| Figure 3.11: Photograph of fully populated knock hardware evaluation board                | 39 |

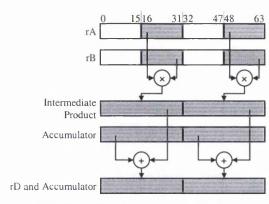

| Figure 3.12: Data and Algorithmic Flow of the Developed SIMD Knock Kernel                 | 40 |

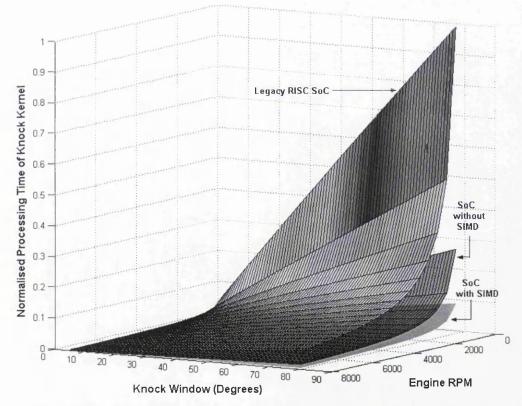

| Figure 3.13: Knock Kernel Processing Time with and without SIMD                           | 42 |

# **1** Introduction

#### 1.1 Systems-on-Chip in Modern Cars

The automobile has proven to be the ultimate "vehicle" for integrating new electronic technologies. Its average consumption level, variety of semiconductors and growth rate, from 10% in 1998 and projected to be 40% in 2009 according to leading global automotive manufacturers continues to be impressive [1, 2, 3, 4, 5, 6, 7, 8, 9, 10]. Today's premier vehicles use over 70 microcontrollers [1, 2, 6, 11]. In fact, the term "system-on-chip" (SoC) is often used to describe this class of powerful microcontrollers. In the automotive world, the transition from 4, 8 and 16-bit micro controller units (MCUs) to powerful 32 and 64-bit SoCs is not without some important considerations. It often means learning a new central processing unit (CPU) architecture, investing in new development tools, and importantly porting existing software. While there is a significant investment, there is also significant payback in the long term, if correct decisions are made.

Traditionally, advancements in microprocessor speed have been gained by increasing clock speed, which is a measurement of how fast a microprocessor can execute instructions [12]. However, recent design efforts have focused upon increasing the number of instructions that can be executed simultaneously [12, 13, 14, 15, 16]. When more instructions can be executed at the same time, an SoC's speed increases without requiring an increase in clock speed [12]. To increase speed without increasing the clock speed, various single instruction multiple data (SIMD) technologies are being designed to allow SoCs apply a single computation to many pieces of data at the same time [13, 16]. Additionally, modern embedded SoC based automotive systems are used in complex powertrain control, antilock braking systems and airbag systems. These applications require the manipulation of large pieces of data and particularly perform complex calculations.

More limited applications such as near obstacle detection, integral cellular phones, advanced body computers, telematics and vehicle mobile Internet access products taking vehicular SoCs to a new level. High performance SoCs is providing a growing list of feature differentiators for many vehicles - cars, trucks and all the emerging classifications in between.

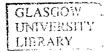

Figure 1.1: Performance Demanding SoC Controlled Modules in a Modern Car

Where,

- CVT Continuous Variable Transmission

- DFI Digital Fuel Injection

- EACC Electric Air Conditioning Control

- EAPS Electric Power Assisted Steering

Many vehicle applications use several semiconductor technologies to meet the performance and cost targets of the system. Figure 1.1 illustrates some of the existing and next generation processor bandwidth intensive embedded automotive applications.

Increasingly sophisticated automotive and transportation infrastructure requirements are defining navigation, collision avoidance, automatic toll collection, night vision and even auto-pilot type systems for future automobiles. The proof-of-concept-technologies in many of these systems continue to trace their roots to military or aerospace [17, 18, 19, 20].

New technologies will most likely be required to attract broad consumer acceptance. Computing technology adapted for automotive applications is providing the initial Internet connectivity for vehicles.

With the SoC technology poised to radically change the automotive electronic industry landscape, it is essential to understand the future SoC trends and the performance requirements of the applications to be run on them. As a result, research was conducted on various architectural elements of the next generation embedded automotive PowerPC SoC and its applications incorporating a mix of hardware and software. The proposed approach responds to the requirements for new design and development technology, driven by the automotive market demand for high performance and particularly cost-effective SoCs.

#### **1.2 Portfolio Structure and Original Contributions**

The key aspects of the research undertaken are as follows:

- To set-up a viable business plan for the next generation automotive qualified advanced single-instruction-multiple-data (SIMD) PowerPC SoCs with tightly coupled digital signal processing (DSP) functionality

- To assist the rapid development of processor bandwidth intensive embedded automotive applications and their SoCs

- To evaluate and solidify various core architectural enhancements as per performance requirements of such applications

- Introduction and implementation of first-of-its-kind single-instruction-multipledata (SIMD) based real-time embedded automotive algorithms

- To facilitate the simulation and prototyping of heterogeneous automotive systems, by supporting specification, the co-existence and interaction of different models of computation, mixed-mode system simulation, design and generation of automatic code from a block diagram description of the applications and its algorithms.

- To promote the reuse of intellectual property (IP)

These aspects are encapsulated in the themed portfolio. In particular, embedded automotive applications are developed; demonstrating the capabilities of the next generation embedded SIMD PowerPC SoC. This section of the executive summary insets the historical background to the current slow transformation from legacy microcontrollers to advanced SoCs and the motivating forces behind it.

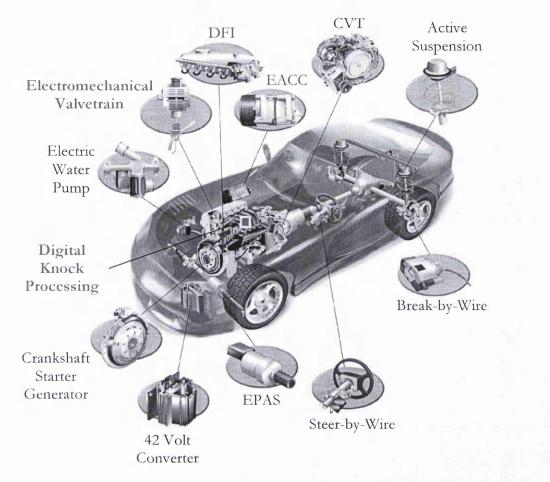

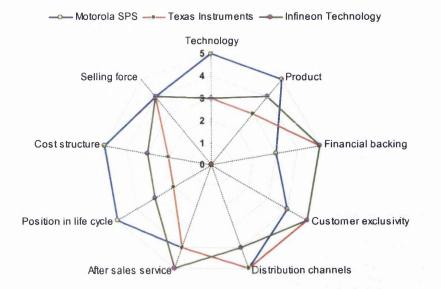

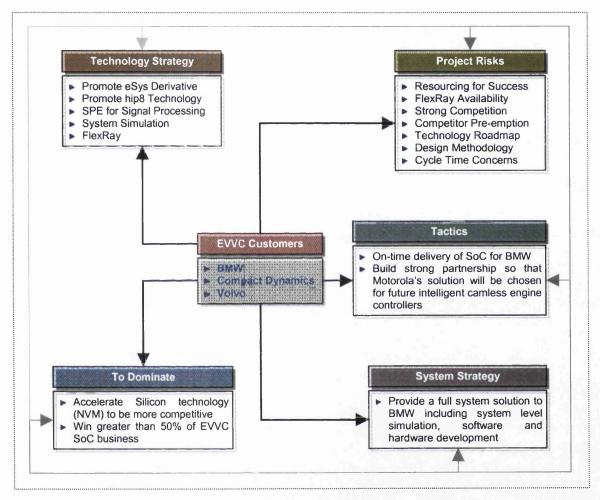

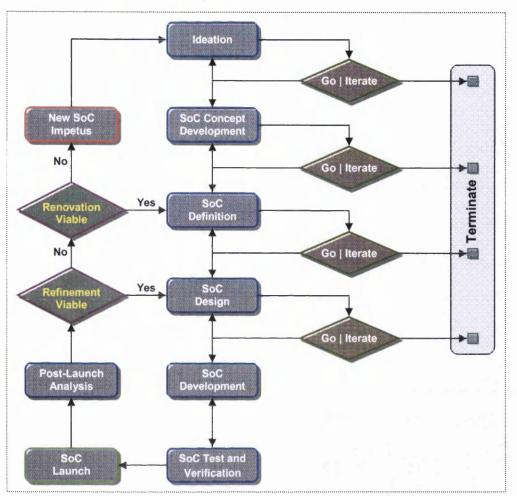

Portfolio I, Integrated Business Plan for the SoC Development of Camless Engine Platform, discusses the business plan put forward to raise necessary funds from the Motorola Semiconductor Products Sector (SPS) funding body for the design and development of the distributed SoC controller platform for the control of electromagnetic actuator driven camless engines. This portfolio lays emphasis on the overall industrial and commercial relevance of the industrial EngD research undertaken.

Portfolio II, System Level Design of a Controller Platform for a Camless, Electromagnetic Actuator Driven Car Engine, discusses the design of a patent-pending rapid development methodology of a controller platform and the associated algorithm, for an electromagnetic actuator driven camless engine, based on the developed PowerPC SoC. This portfolio also reviews the current state of camless engines. This work was presented at a number of international automotive conferences and permission has been granted for the publication of the attached journal paper.

Portfolio III, Fast Internal Combustion Engine Knock Processing Using an Automotive PowerPC System-on-Chip, introduces a patent-pending, journal published, novel high performance knock detection strategy using the next generation automotive PowerPC SoC, particularly highlighting the capabilities of the SIMD micro architecture implemented. The developed SIMD knock processing algorithm is based on autonomous on-chip modules and a custom designed auxiliary signal processing extension tightly coupled to the main SoC core. The author has also presented various software development techniques with an advanced software circular buffer implementation for processing the streaming knock sensor data.

The SoC Book Chapter, *Embedded Von-Neumann On-Chip PowerPC SoC Cache*, introduces the design and efficient use of the on-chip first-of-its-kind Von-Neumann cache of the automotive SoC. This document also introduces various cache control hardware instructions developed, particularly, addressing the optimal handling of time-critical segments of applications.

Next Generation Powertrain SoC Performance Requirements, is a discussion of author evaluated key SoC architectural enhancements and additions required in the natural successor to the abovementioned single-issue SoC, based on a number of next generation powertrain applications. This investigation was done by profiling author and automotive customer developed applications. This document also discusses the model based control approach taken with the development of some of the profiled applications.

15

The document, Architectural Modelling Environment for the PowerPC SoC, discusses the various fully-functional and cycle-accurate SoC core specific simulation modules developed by the author for pre-silicon evaluation. This simulation platform is primarily used for performance analysis of applications which in turn solidifies the pre-silicon SoC core requirements to be implemented in real-time. Particularly architectural trade-offs at the processor, cache, and memory interface level of system design, also known as core-complex for embedded SoC designs is investigated.

Figure 1.2 overleaf shows a synopsis of the above themed portfolio plan.

Figure 1.2: Synopsis of Themed Portfolio

# 2 Industrial Context

#### 2.1 SoCs in Embedded Automotive Applications

The automobile as a self-contained microcosm is undergoing radical changes due to the advancements in automotive SoC technology. The relative part of electronics in the automobile is increasing dramatically whilst the future of new electronic systems based around SoCs is extremely promising. Beginning with electronic controlled ignition in the early sixties [23], past two decades have witnessed a tremendous change in vehicle electronics [21, 22, 23, 24, 25, 26]. New applications such as mobile multimedia, control-by-wire systems, advanced safety interiors, and collision avoidance highlights a portion of the significantly more electronic control the automobile of the future. SoCs are now essential to control the movements of the automobile, of the chemical and electrical processes taking place in it, to entertain the passengers, to establish connectivity with the rest of the world, and importantly to ensure safety. Of particular importance is the development of automotive SoC technologies necessary to offer timely, reliable, and cost effective products to the consumer.

#### 2.1.1 Automotive Powertrain Controllers

Automotive powertrain controllers generally satisfy diverse and often conflicting requirements [27, 28, 29, 30, 31]. Such robust controllers in and around the engine room require high reliability, advanced performance, high voltage (>35V) and high temperature (>125 °C) characteristics [32, 33, 34, 35, 36, 37, 38]. Dense integration of complex sub-controllers is also key to providing expanded functions without increasing the size of the overall controller or the number of devices on it. By adopting high performance SoCs, such expanded functions can be provided in smaller and more lightweight packages with high reliability [39, 40].

In high performance engines, the number of application to be controlled and the associated control actions have been increasing in order to achieve better driveability, higher power, lower fuel consumption and particularly lower emissions. Therefore, in addition to being adaptive and self-diagnostic, the powertrain control systems have to control many applications such as,

- Fuel Injection

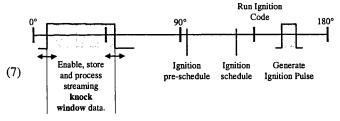

- Ignition Timing

- Idle Speed

- Exhaust Gas Recirculation (EGR)

- Knock Control

- Electronic Controlled Transmission (ECT)

- Camless Engine Control (CEC)

Additionally, such application need to interact with safety critical applications such as antilock braking and traction control, necessitating the need to for the integration of time and event driven high performance fault-tolerant communications protocols such as CAN [23], the time triggered protocol (TTP) [41] and FlexRay [11].

#### 2.1.2 Development of Powertrain Controllers

Development of powertrain controllers describes techniques, tools, roles, deliverables, standards and activities [21, 22, 23, 24, 25, 26, 28, 29, 30, 32, 33, 34, 35, 36]. With the advent of the new low-cost complex automotive qualified high performance SoCs, there are unique challenges and trade-offs for development engineers and associated tool vendors [42, 43, 44, 45, 46, 81, 89, 90, 88].

Ever increasing performance needs of advanced powertrain applications have led the development of sophisticated embedded development tool chains, SoCs with complex cores, various types of on-chip memories and autonomous peripherals, particularly supporting single cycle on-chip instruction and data buses [81, 86, 87, 88, 89, 90]. Designers of such SoCs strive to provide the visibilities needed by logic analysers, processor emulation and calibration systems, while not compromising performance and cost saving. It is evident that there is less support for the development of powertrain controllers based on advanced SoCs introducing critical and costly delays in the development cycle [22, 23, 24, 25, 26, 47]. Additionally, based on industrial trend, it can simply be stated that powertrain SoCs would soon be based on superscalar<sup>2</sup> or multiple-issue cores, magnifying the complexities already present with the application development process [81, 86, 87, 88, 89, 90]. Thus it is vital to establish a strategy early enough in the development process to avoid costly business disruptions.

As with other industries, a new powertrain controller concept originates in research and development and once this new concept is proven, it makes its way into the appropriate automotive platform.

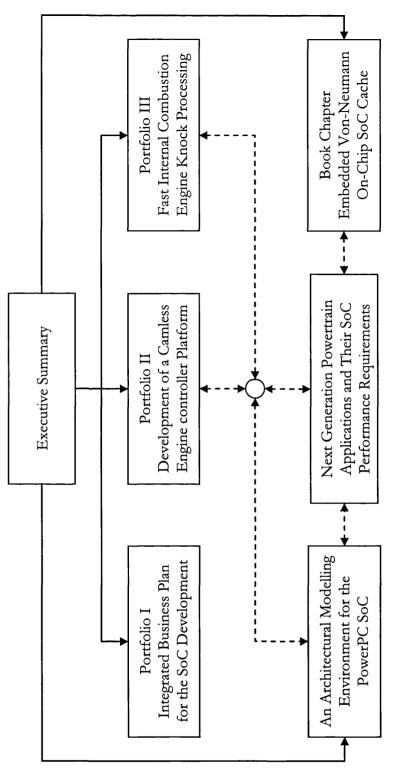

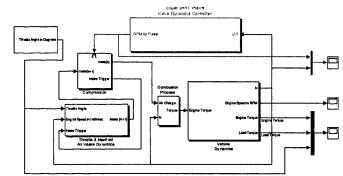

A systematic approach, outlined in Figure 2.1 is generally used to translate the concept into an embedded powertrain controller [22, 23, 24, 25, 26, 47]. A number of steps in the illustrated development process require a model of the powertrain system for which the controller is being developed.

Figure 2.1: Powertrain Controller Software V Development Cycle

<sup>&</sup>lt;sup>2</sup> A microprocessor architecture that contains more than one execution unit or pipeline, allowing the processor to execute more than one instruction per clock cycle.

Figure 2.1 also demonstrates the complexity and expansiveness of the overall powertrain controller development process, and how different skills and organisations are involved. As shown above, once the sub-systems are solidified, they are then qualified and calibrated to verify conformance with the initial requirements.

# **3 EngD Research Contribution**

### 3.1 Integrated Business Plan

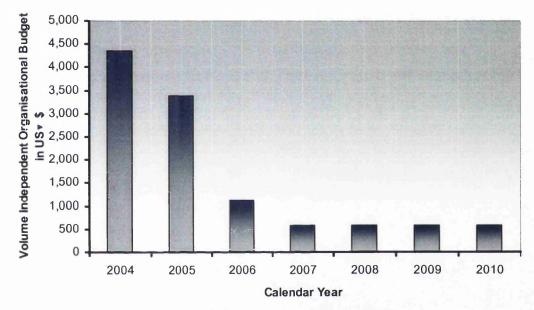

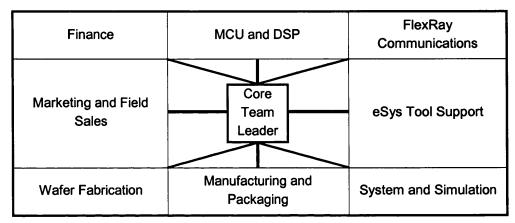

This portfolio encapsulates a comprehensive business plan developed by the author for the camless engine controller platform business based on the PowerPC SoC. The overall plan enclosed is divided into four distinct sections:

- 1. The offer, summarising the funds required and the benefits

- 2. Marketing plan

- 3. Financial plan

- 4. Organisational plan

This plan was used for the allocation of required resources, handle unforeseen complications, and make good business decisions. Specifically, organised information about the company and proposal as to how the repayment of the invested money is to be made is highlighted. Additionally, it informs sales personnel, suppliers, and others about all the project operations and goals.

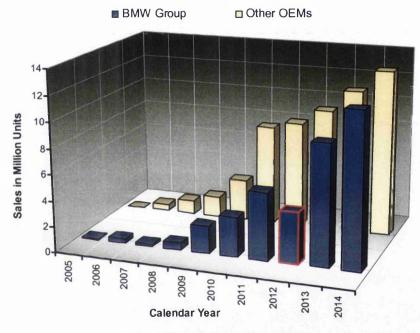

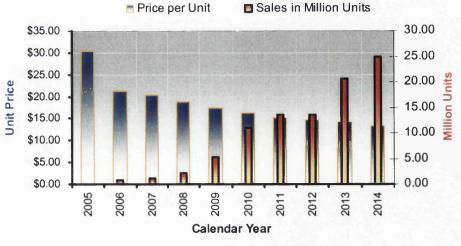

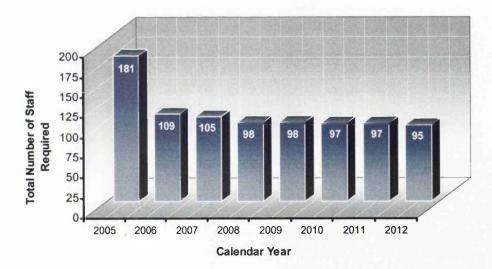

Of particular importance to the overall plan is the principle agreement with BMW Group and various other OEMs and Tier Is to supply 138 million valve control SoCs over a 10 year period starting in 2006. This provides the venture with a reliable income stream through highly reputed premier automotive engine technologist and manufacturers.

During the process, the biggest challenge faced was the understanding of the technology and business risks, in order to establish methodologies to manage those risks and rewards, and to develop the business models to fairly allocate those risks and rewards to the appropriate business players.

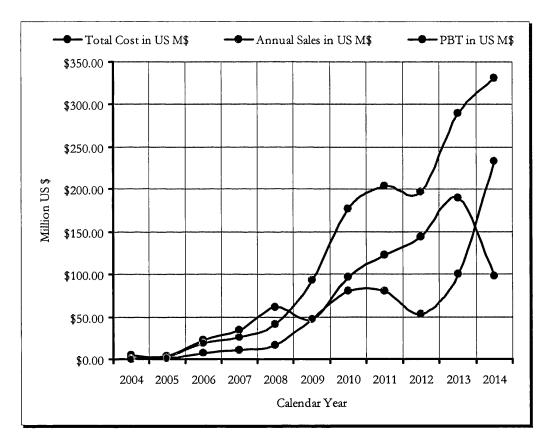

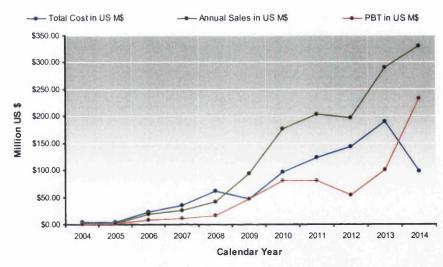

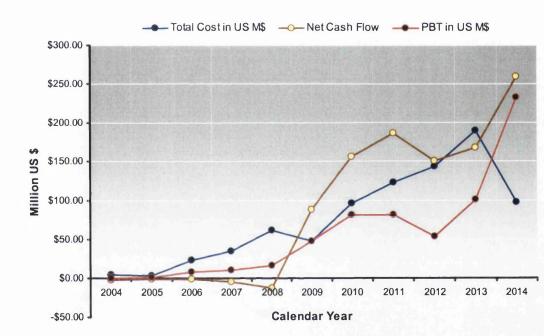

Figure 3.1 overleaf shows the overall financial summary of the camless engine controller business.

Figure 3.1: Camless Project – Financial Summary

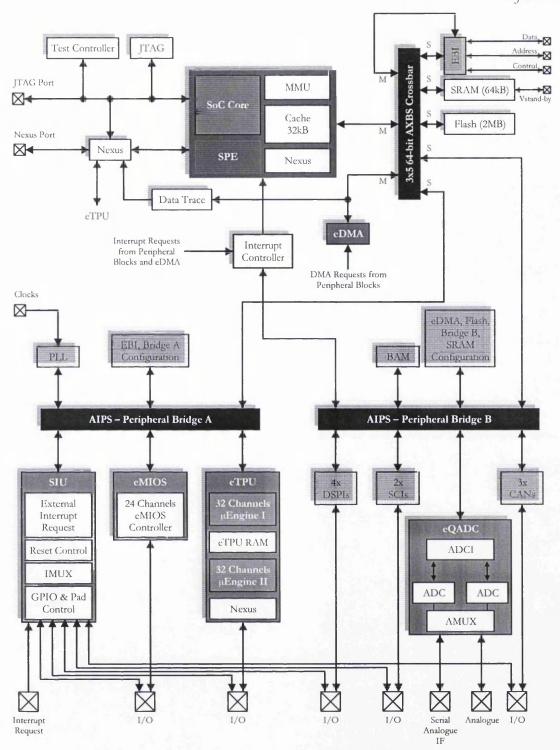

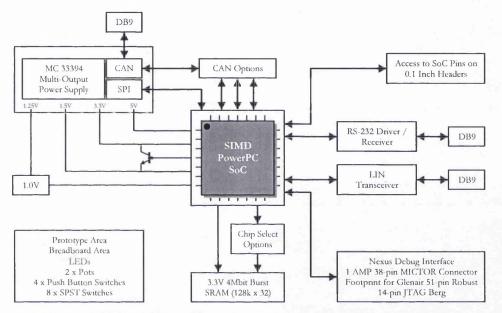

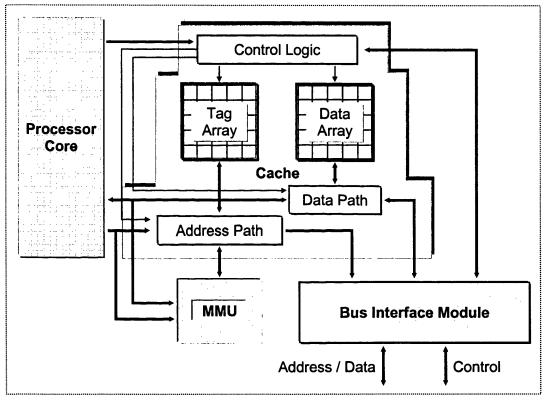

#### 3.2 An Overview of the SoC Developed

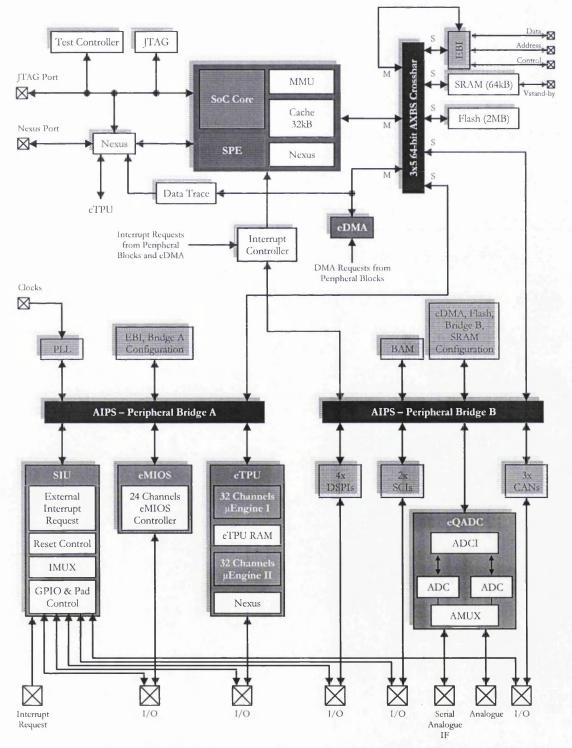

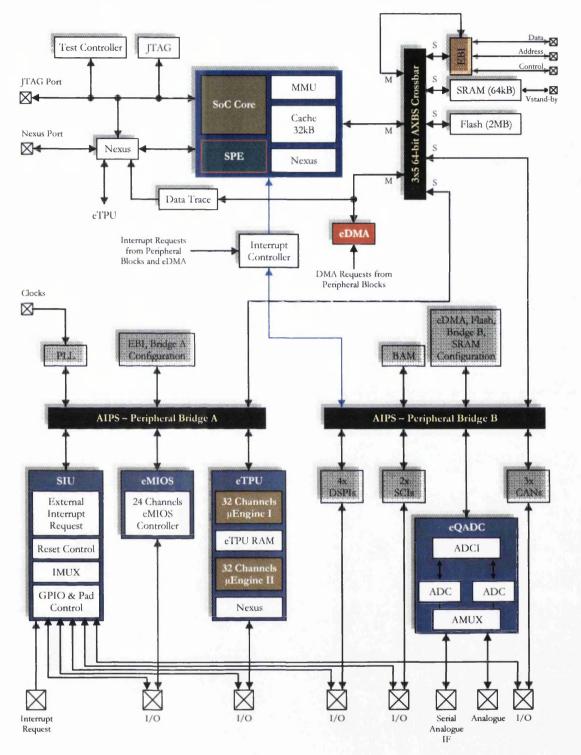

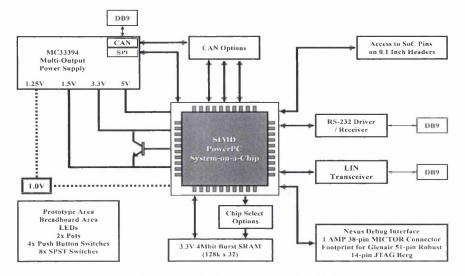

The SoC developed, as per the outcome of the business plan highlighted in section 3.1, is the first member of a family of next generation powertrain SoCs based on the PowerPC Book E architecture, containing many new features coupled with high performance complementary metal oxide semiconductor (CMOS) technology to provide substantial reduction of cost per feature and significant performance improvement over the legacy devices, particularly the presently used MPC565 [81]. This SoC is targeted toward middle to high-end powertrain applications, such as camless engine controller platforms and digital knock processing.

The host processor core of the SoC complies with the PowerPC Book E architecture. It is 100% user mode compatible with the classic PowerPC instruction set including the floating point library. The Book E architecture has enhancements that improve the PowerPC architecture's fit in embedded applications. This core also has additional instructions, including DSP instructions, supported by the signal processing extension (SPE), beyond the classic PowerPC instruction set.

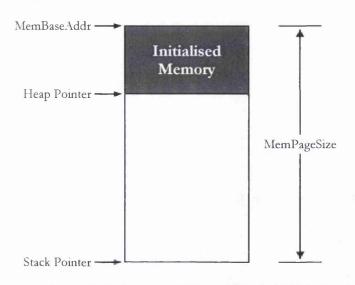

The SoC has two levels of memory hierarchy. The fastest accesses are to the 32kB unified, aka von Neumann cache. The next level in the hierarchy contains the 64kB on-chip static random access memory (SRAM) and the 2 MB internal flash memory. Both the SRAM and the flash memory can hold instructions and data. The External Bus Interface has been designed to support most of the standard embedded memories widely available.

The complex I/O timer functions of SoC are performed by two Enhanced Time Processor Unit engines (eTPU). Each eTPU micro-engine controls 32 hardware channels. The eTPU consists of 24-bit timers, double action hardware channels, variable number of parameters per channel, angle clock hardware, and additional control and arithmetic instructions. The eTPU can be programmed using a high-level programming language.

The less complex timer functions required are performed by the Modular Timer System (eMIOS/MTS). The eMIOS' 24 hardware channels are capable of single action, double action, Pulse Width Modulation (PWM) and modulus counter operation. Off-chip communication is performed by a suite of serial protocols including controller area networks (CAN), enhanced serial peripheral interface (SPI) and serial communication interfaces (SCI).

Additionally the SoC has an on-chip 40-channel Enhanced Queued dual Analogue-to-Digital Converter (eQADC). The System Integration Unit (SIU) performs several chip-wide configuration functions. Pad configuration and General-Purpose Input and Output (GPIO) are controlled from the SIU. External interrupts and reset control are also found in the SIU. The Internal Multiplexer sub-block (IMUX) provides multiplexing of eQADC trigger sources, daisy chaining the DSPIs and external interrupt signal multiplexing.

Figure 3.2: An Overview of the SIMD SoC Developed

# 3.3 An Architectural Modelling Environment for the PowerPC SoC

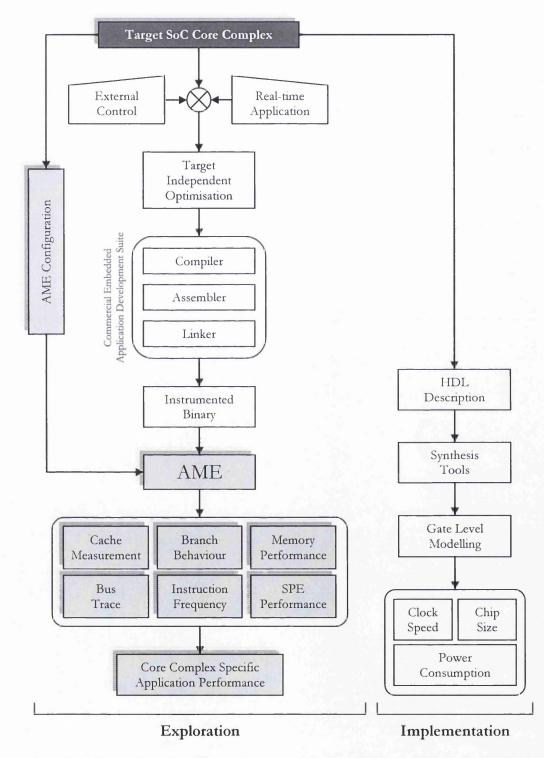

Over the years, core architectural simulation models have migrated to either fully functional models or to cycle accurate models [42, 43, 44, 45, 48]. Fully functional models are characterised by modelling system features without regard to hardware timing. Functional models are typically preferred by software developers since they tend to be the highest performance models available for developing application code. The drawback is that they offer very little information for performance evaluation. On the other hand, cycle accurate models provide very precise behaviour in regards to timing but tend to be relatively slow in performance due to the extreme detailed nature of the model [48, 81, 88]. The area of performance evaluation is in a middle ground; requiring the simulation performance of a functional model but needing the information provided by a cycle accurate model. Ideally, performance evaluation studies would like to simulate proposed system architectures over a wide range of benchmarks to determine system level performance, then adjust the system architecture and re-evaluate the performance.

The Architectural Modelling Environment (AME) targets the middle ground simulation requirements of performance evaluation by recognising that typical benchmark code does not require a fully functional model to run and that only a vital few key architectural elements determine a systems throughput [45, 48, 88, 12]. Typical benchmark code does not target a specific architecture which allows the benchmark to run across many different system implementations. Therefore, every *nook and cranny* of a fully functional simulation model is never used due to the generalised nature of benchmarks. Development time devoted to functional features which are never used by a benchmark is thus wasted effort in regards to performance evaluation. Similarly, most of the development time associated with creating a very precise, cycle accurate model is lost since a system's throughput is generally controlled by a very few architectural elements or bottlenecks.

While AME allows both fully functional and cycle accurate models to be developed, the intent of AME is to target the specific requirements of performance evaluation. The current area of study that AME is being used for is in architectural trade-off studies at the processor, cache, and memory interface level of system design or what is being called the core-complex for embedded SoC designs.

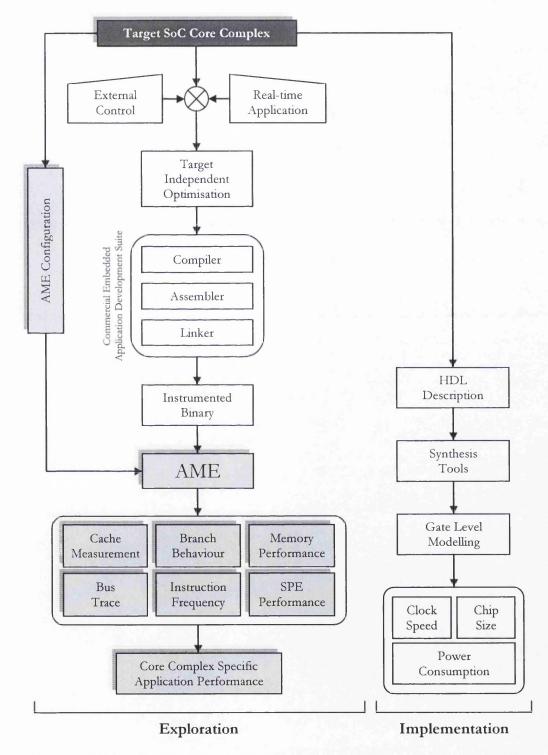

As shown in Figure 3.3 overleaf, in order to efficiently performance profile an application using the AME, the modules around it require the designer to work in two fields; on the one hand, the development of the software part including compiler, assembler, linker, and simulator and, on the other hand, the development of the target architecture itself. The AME produces the characteristics of the core architecture specific application binary performance and, thus, may answer questions concerning the instruction set, the performance of an algorithm, and the required size of memory and registers. The required silicon area or power consumption can only be determined in conjunction with a synthesisable hardware description language (HDL) model.

Core architectural analysis using the AME provides a unique opportunity to develop system metric estimation methodologies for power, area and performance in conjunction with low-level RT-synthesisable HDL for soft cores, netlist for firm cores and layout for hard cores. As an example, consider a UART (universal asynchronous receiver/transmitter) core implemented in synthesisable HDL, having its buffer size as a parameter. By performing gate-level simulation of UARTs with different buffer sizes, one can obtain area and toggle switch information for different parameter settings; likewise, after simulation of a core-based design at system-level, one can use low-level toggle data to accumulate total toggle counts and estimate power consumption of the design for a given technology.

Figure 3.3: Application Binary Characterisation Process Using the AME

#### 3.4 Electromagnetic Actuator Driven Camless Engines

#### 3.4.1 Introduction

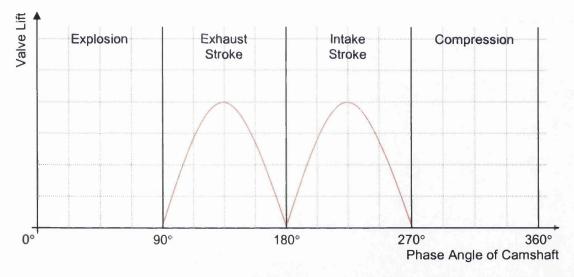

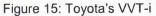

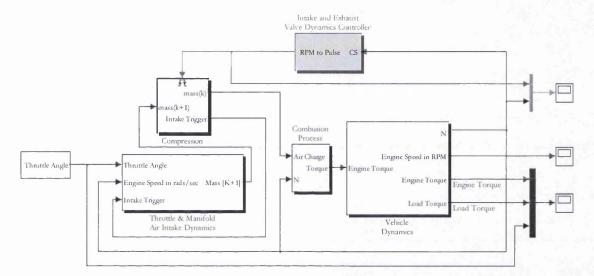

Conventional internal combustion engines use mechanically driven camshafts to actuate intake and exhaust valves. Like a very simple software program that contains only one set of instructions, such mechanical cams always open and close the valves at the same precise moment in each cylinder's constantly repeated cycle of fuel-air intake, compression, combustion, and exhaust [49]. They do so regardless of whether the engine is idling or spinning at maximum rpm. While this system is convenient and reliable, the fixed timing of the valve events with respect to the piston motion is typically selected as a compromise among fuel economy, emissions, maximum torque output, valvetrain noise, vibration and harshness [49, 50].

The growing need to improve fuel economy and particularly reduce emissions led to the introduction of an alternative valvetrain technology, namely a camless valvetrain [51]. Camless engines, employing electrohydraulic, electromagnetic or hydromechanical control of the valves, offer the next step in engine flexibility. Such engines allow independent control of valve timing and lift without mechanical linkage to the crankshaft [50, 51]. Various studies have shown that a camless valvetrain can alleviate many otherwise necessary engine design tradeoffs by supplying extra degrees of freedom to the overall powertrain system [50].

Automotive engines equipped with electromagnetic camless valvetrains have been studied for over thirty years but production worthy vehicles with engines of this type are still not available due to difficulties in ensuring adequate and reliable electromagnetic valve performance [1, 7, 50, 52, 53]. For an electromagnetic camless valvetrain (EMCV), the actuator noise caused by high contact velocities of the moving parts has been identified as a key problem [50, 52, 53].

Critical to the successful implementation of such a camless engine is the electromagnetic valve control strategy, its real-time software and hardware, satisfying performance and cost targets of the overall platform in a timely manner.

29

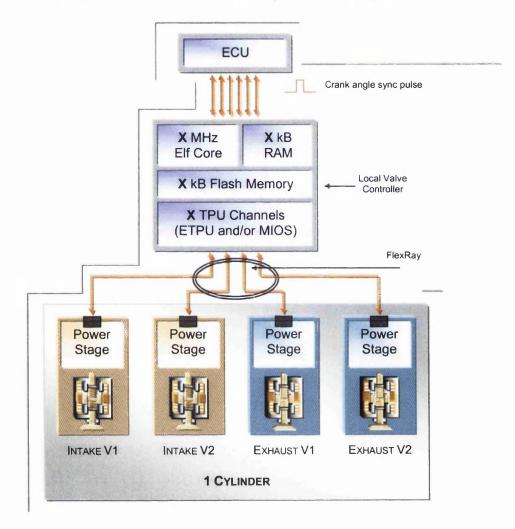

#### *3.4.2 Construction and Operation of the Electromechanical Actuator*

Figure 3.4: The Electromechanical Actuator

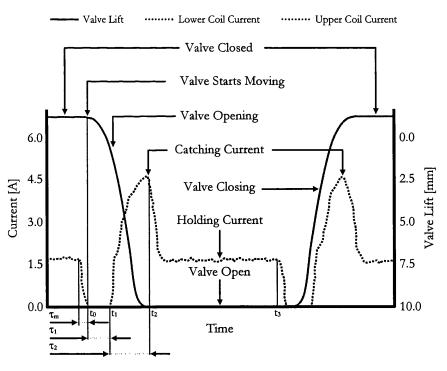

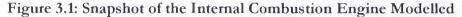

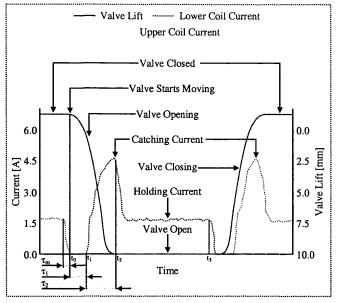

Figure 3.4 illustrates the actuator at open, neutral and closed positions. There are two magnets, two springs and an armature in the actuator. The two magnets are coil wound on ferromagnetic material. The coils are driven by currents generated by an electronic system, driven by a pulse-width modulated voltage. The activated coil generates a magnetic field applying a force on the armature. The two springs are adjusted such that both are always compressed for any position of the armature. The actuator uses the spring force to accelerate the masses, then uses the electromagnetic force to attract and dwell the valve. When there is no current on coils, the spring-mass system stays at the neutral position. Voltage applied on the upper coil closes the valve generating a holding current, which depends on the spring force and the pressure difference between the cylinder and the exhaust/intake manifold. Because of the symmetry, analysis is done only on the valve-opening event.

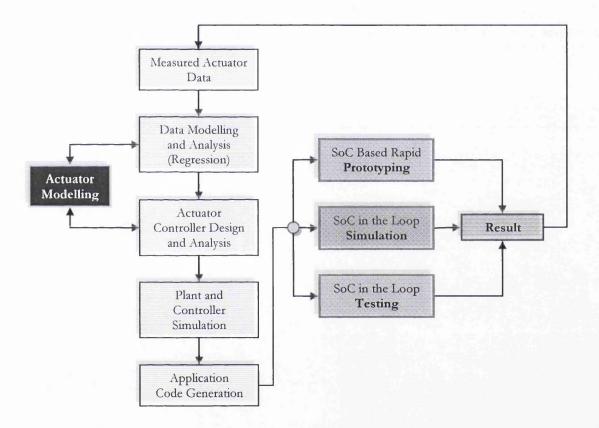

#### 3.4.3 Design and Implementation of the Actuator Controller Platform

The PowerPC SoC based actuator control system is required to ensure accurate valve closing and opening events (timing). The engine management system deploys the timing strategy on the drivers torque demand and other vehicle variables [51, 52, 53]. One of the key objectives of the controller platform is to reduce the armature-coil and valve-cylinder contact velocities, the so called *soft-landing*, which in turn reduce noise and component wear [50, 51, 52, 53, 54]. Modern engine manufacturers design camshafts to achieve a low 0.04 m/s contact velocity at low engine speeds and in conventionally driven engines, this velocity increase linearly with engine speed [1, 3, 6, 9, 54, 55].

The electromechanical actuator operating in the harsh engine room is a highly nonlinear drive system but it is greatly welcome in high-speed and high accuracy applications such as camless engine control [50, 51, 52]. One of the most commonly used controller techniques for such actuator position control is the linear PI/PID<sup>3</sup> controller. For set point regulation, PID controller provides satisfactory performance. However under time-varying trajectory reference such as the one in the camless engine, the performance of the PID controller degrades due to its linearity characteristic [56].

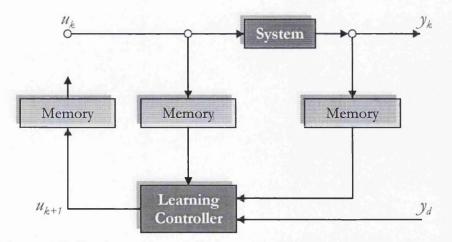

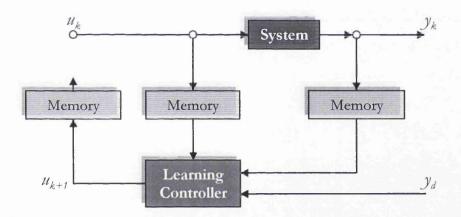

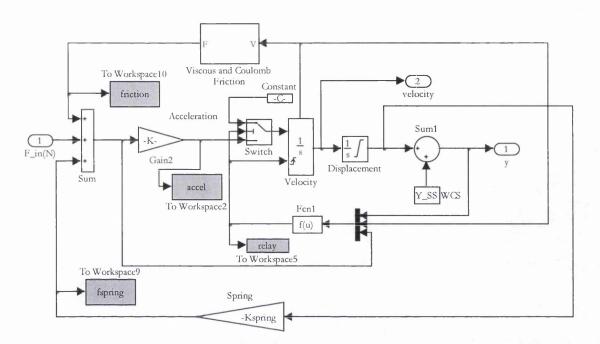

In order to achieve better tracking of the desired valve position, an iterative learning controller (ILC) is implemented as it is a proven technique for improving the transient response of systems following the same trajectory motion or operation over and over [57, 58, 59, 60, 61, 62, 63, 64, 65, 66, 67].

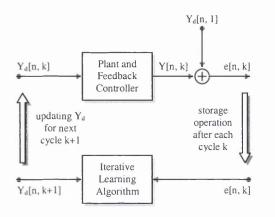

Figure 3.5: Configuration of the Actuator Iterative Learning Controller

<sup>&</sup>lt;sup>3</sup> PID - Proportional, Integral, Derivative - A three mode control action where the controller has time proportioning, integral (auto reset) and derivative rate action.

The basic idea of the ILC implemented is illustrated in Figure 3.5. All the signals shown are assumed to be defined on a finite interval. The subscript k indicates the number of full armature travel cycles. During the  $k^{th}$  cycle, the input armature position  $u_k(t)$  is applied to the system, producing the output  $y_k(t)$ . These signals are stored in the memory units until the trial is over, at which time they are processed by the ILC algorithm. Based on the error  $(e_k(t) = y_d(t) - y_k(t))$  that is observed between the actual output and the desired output, the ILC algorithm computes a modified input signal  $u_{k+1}(t)$  upon full armature travel that will be stored in memory until the next time the system operates, at which time this new input signal is applied to the system. This new input produces smaller error than the previous input.

The overall controller is modelled and implemented using Matlab<sup>®</sup>, Simulink<sup>®</sup> and Stateflow<sup>®</sup>. MathWorks' Real-Time Workshop is then used to generate executable stand-alone C code of the algorithm modelled in Simulink [68]. The resulting code is then hand optimised before generating the binary executable for the PowerPC SoC.

Primarily, the approach taken enables the use of the actuator controller:

- 1. As an embedded model within a control algorithm or observer

- 2. As a real-time engine model for hardware-in-the-loop testing

- 3. As a system model for evaluating engine sensor and actuator models

- 4. As a subsystem in a powertrain or vehicle dynamics model

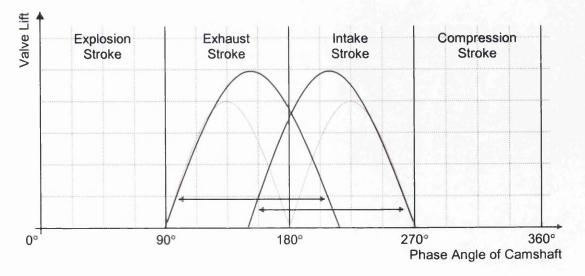

#### 3.4.4 The Camless Engine Actuator Controller Platform

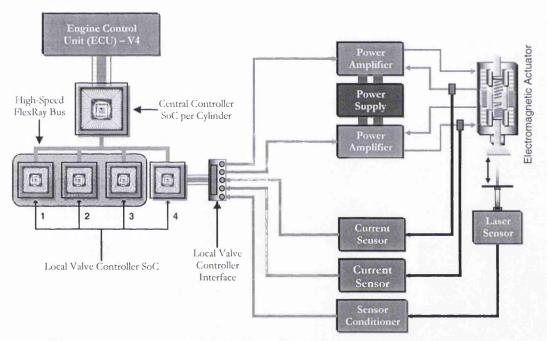

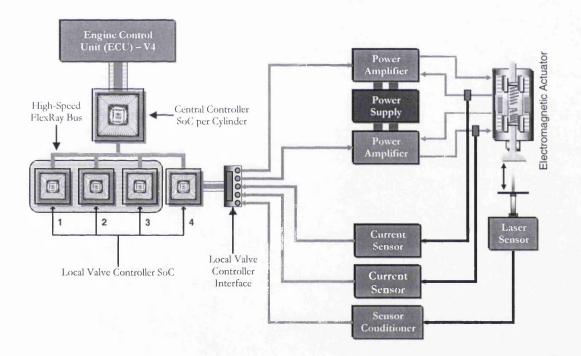

Figure 3.6 illustrates the real-time system level development platform implemented for the evaluation of the electromechanical valvetrain. First of all, the maximum supply voltage is limited to 42-Volts to simulate the available voltage on a future vehicle. Two power amplifiers driven by the power supply drive the magnetic coils of the actuator. The SoC designed controls the voltage across the coil through a custom designed I/O board. A laser sensor is used to measure the actual valve position with a 5µm resolution. Coil current is also monitored for diagnostic purposes.

Figure 3.6: Experimental Set-up of the Actuator Controller Platform

This central controller SoC shown above receives its drive cycle information from the existing engine control unit (ECU). The local valve controller SoC is used for the execution of control algorithms and to drive the power stages. Other inputs to this controller include position of the actuators. Data transfer to actuator occurs at 25µs (40kHz) intervals.

## 3.4.5 Results and Concluding Remarks

An electromechanical camless valvetrain controller platform is realised based on the PowerPC SoC developed. Simulations and real-time measurements confirm the functional ability of the electromechanical actuator to vary valve timing, lift, velocity and event duration, as well as to perform cylinder deactivation in a fourvalve multi-cylinder engine.

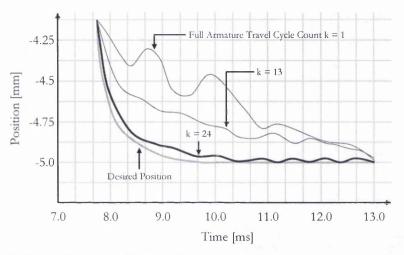

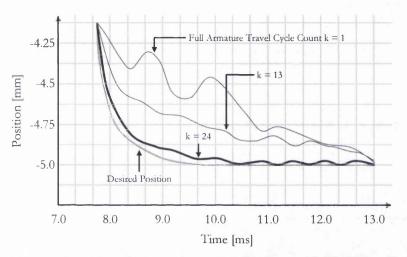

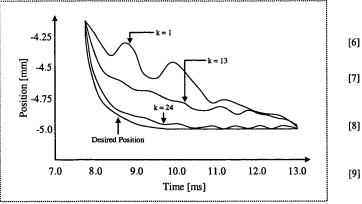

Figure 3.7: Valve Position Control Results based on the ILC (k  $\varepsilon$  [1, 13, 24])

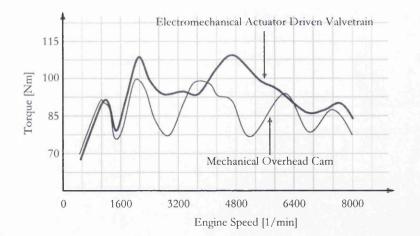

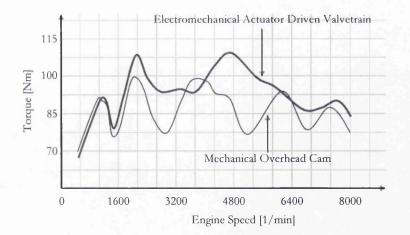

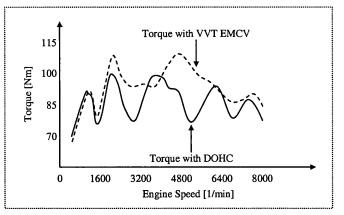

Figure 3.8: Torque Production with Mechanical Cam and Camless Engine

As shown in Figure 3.7, employing an ILC reduces the valve contact velocity as the armature cycles are increased. Measured results from [69] in Figure 3.8 confirms that the torque produced by the four cylinder engine, driven by an electromechanically driven valvetrain is 13% better than that of a classic dual overhead camshaft (DOHC) arrangement.

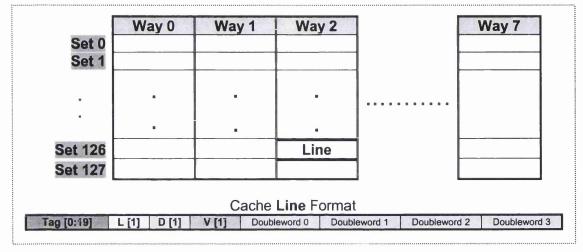

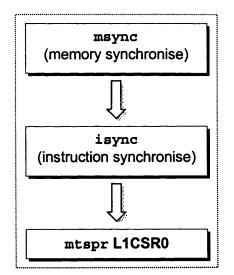

## 3.5 Embedded Von-Neumann On-Chip SoC Cache

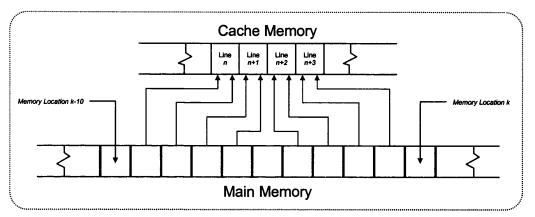

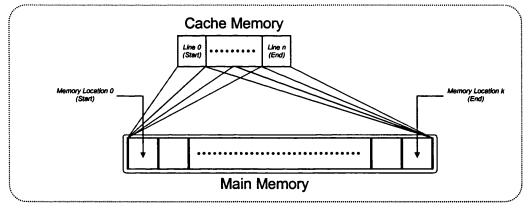

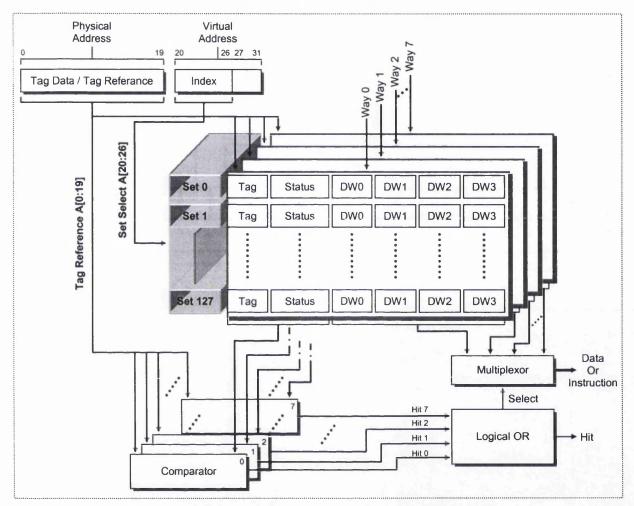

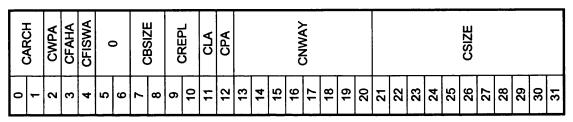

A high performance, 32-kilobyte, 8-way set-associative, unified, aka von Neumann (instruction and data) cache with a 32-byte line size has been developed for the SoC. The enclosed SoC cache book chapter examines the new cache control instructions and provides the user with sample routines to invalidate the cache and relocate object code in memory using the cache. Most applications only use these cache control instructions during power-on initialisation and when necessary to flush cache contents to system memory. However, in time-critical code segments these instructions can often improve throughput via preloading of required cache contents and by reducing unnecessary transfers between external memory and the unified cache.

Measured results using author and customer developed powertrain applications confirm the developed cache improves system performance by providing low-latency data to the SoC core's instruction and data pipelines, which decouples processor performance from system memory performance. The cache is virtually indexed and physically tagged.

Due to areal overhead, the cache developed does not consist of dedicated hardware for enforcing coherency, and a software technique to accomplish this task is also proposed in the document.

This book chapter also discusses a technique as to how the cache can be used as local memory with minimal reconfiguration overhead using software. Particularly, inability to reuse data and under utilisation of cache capacity are responsible for poor cache performance on various commonly used automotive applications is highlighted.

35

## 3.6 Fast Internal Combustion Engine Knock Processing

## 3.6.1 Introduction

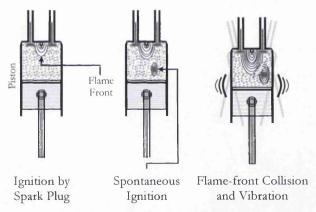

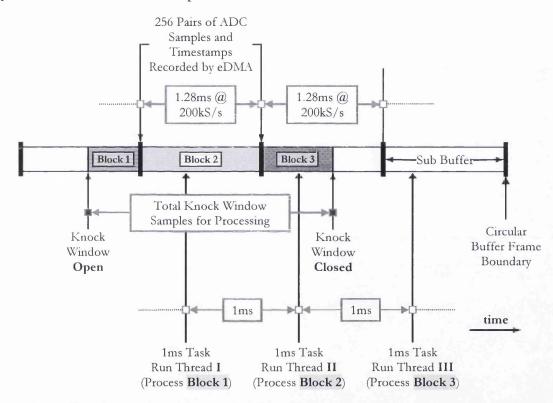

Knock in internal combustion engines (ICE) refer to the premature *self or auto* ignition of the air-fuel mixture in the engine when the unburnt mixture's temperature and pressure have exceeded a critical point. Frequent occurrence of this knock phenomenon causes permanent damage to the ICE and should be avoided. However, in order to obtain maximum power, modern engines are run at their borderline limit of incipient knock using closed-loop control of spark timing based on knock sensor feedback [49, 70, 71, 72].

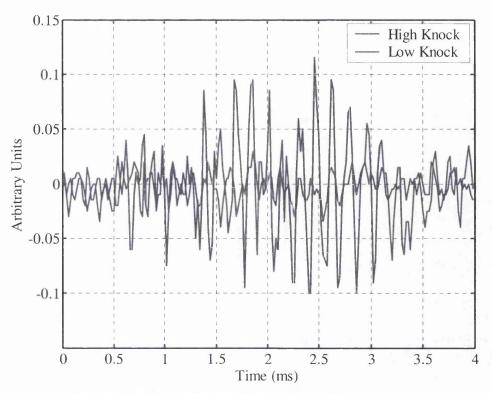

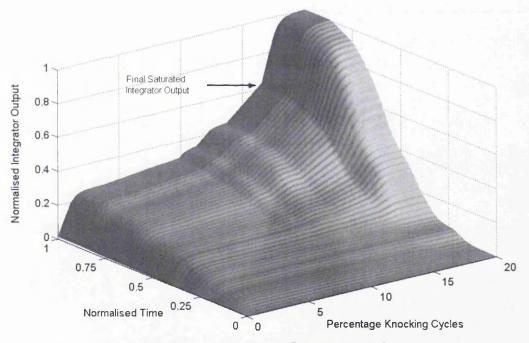

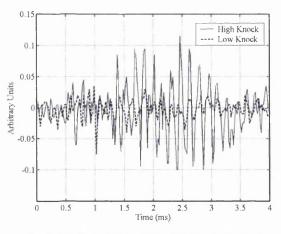

The developed knock processing strategy is based on autonomous on-chip modules and an auxiliary signal processing extension to the main SoC core. Realtime software development techniques with an advanced software circular buffer implementation for processing the streaming knock sensor data have been developed. Various SIMD software optimisation techniques are employed to reduce the real-time knock algorithmic execution time. Real-time and simulation results are presented for the detection of knock on a four cylinder internal combustion engine, but, the approach is widely applicable.

## 3.6.2 Impact of Knock and its Real-Time Processing

Impact of knocking in an engine depends on its intensity and duration [72]. Trace knock has no significant effect on engine performance or durability. Heavy knock can lead to extensive engine damage [49, 70, 71]. The engine can be damaged by knock in different ways: piston ring sticking; breakage of the piston rings and lands; failure of the cylinder head gasket; cylinder head erosion; piston crown and top land erosion; piston melting and holing. Knocking is one important factor limiting the efficiency of an engine and is therefore of great importance to the engine manufacturers [49, 70, 71, 72, 73].

Portfolio I

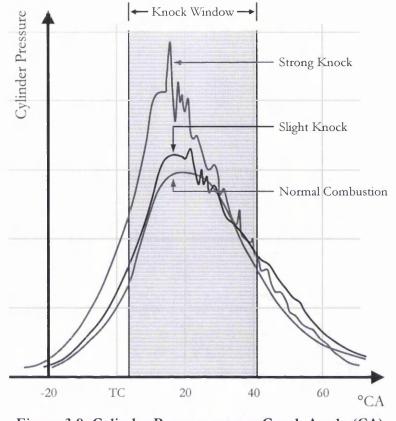

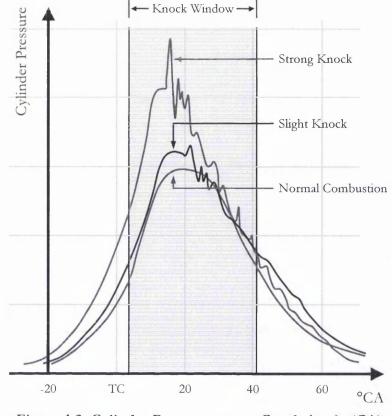

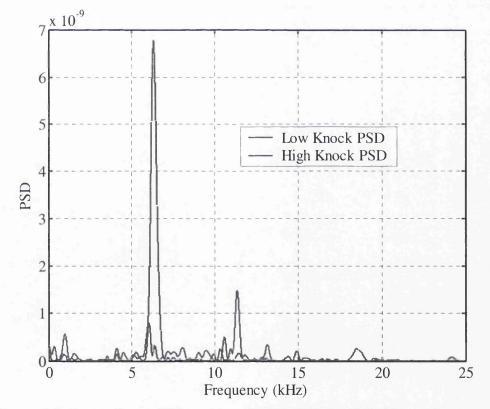

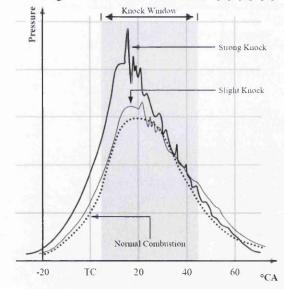

Figure 3.9: Cylinder Pressure versus Crank Angle (CA)

In severe cases, the piston may still be moving upwards to compress the airfuel mixture. As such, it cannot move away to ease the build up of pressure wave. This results in severe stress on the engine and should be prevented as permanent engine damage can occur [49]. Figure 3.9 shows three plots of cylinder pressure against crank angle of a single cylinder engine with ignition timing three degrees apart between each trace.

There are several different approaches to detect the presence of knock in engines, see e.g. [73, 74, 75, 76, 77, 78, 79, 80]. One of the classic techniques presently used in production engines is based on application specific integrated circuits (ASIC) with limited programmability, such as the ProSAK<sup>TM</sup> knock control ASIC [81] and The HIP9011 ASIC [82].

Due to the high cost of direct knock sensors, most of the current knock detection systems are based on structural vibration signals obtained using an accelerometer [78].

#### 3.6.3 Modelling the Pre-Silicon Knock Processing Platform

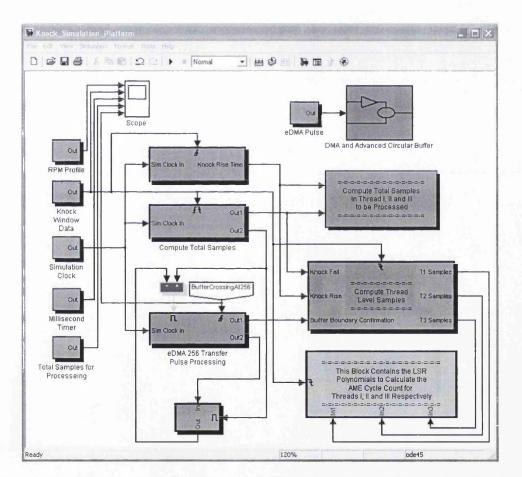

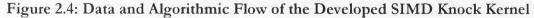

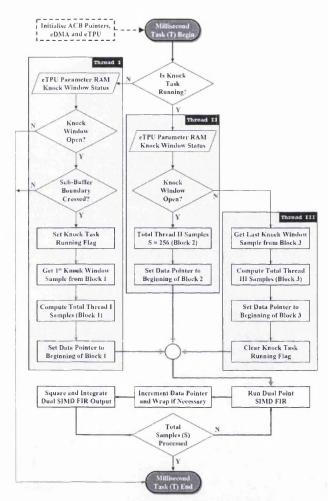

Functional and behavioural modelling of the overall knock processing strategy was carried out using the AME, Matlab, Simulink and Stateflow simulation platforms [68, 83], which was initially used as the primary demonstrator to customers before the development of the SoC based real-time environment. A topdown, modular design approach was taken with the overall implementation. The knock simulation platform is divided into hierarchical subsystems, making it more generic by separating engine and knock control system specific parameters.

Figure 3.10: Pre-Silicon Knock Functional and Behavioural Simulation Platform

AME based linear and non-linear regressed performance analysis tables of the developed SIMD knock signal processing kernels are also incorporated in order to simulate different knock signal acquisition windows as shown in Figure 3.9. As a result, performance optimisation of the entire system, eliminating laborious programming and delivering substantial time was achieved.

Portfolio I

## 3.6.4 SoC Based Hardware Knock Evaluation Platform

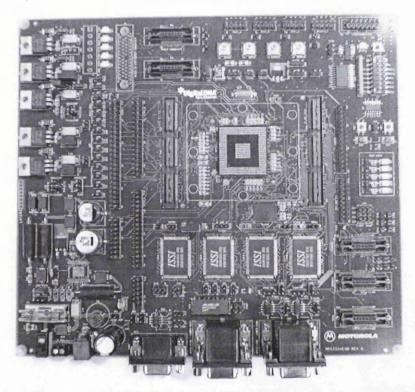

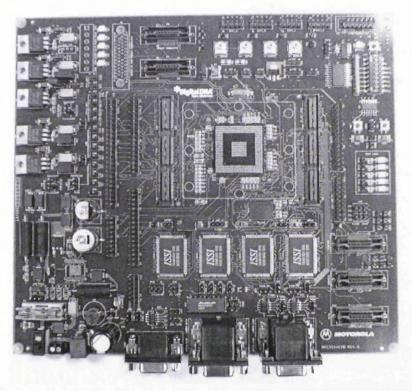

The following figure shows the fully populated printed circuit board (PCB), partly designed by the author, used for the real-time evaluation of the overall knock processing strategy developed. It employs an MC33394 Power Supply IC [81] and connectivity to other basic optional communication protocols available on the SoC as shown in Figure 3.2.

#### Figure 3.11: Photograph of fully populated knock hardware evaluation board

Where possible, components mounted on the PCB are automotive qualified to allow system evaluation over the full automotive temperature range (-40  $^{\circ}$ C to 125  $^{\circ}$ C).

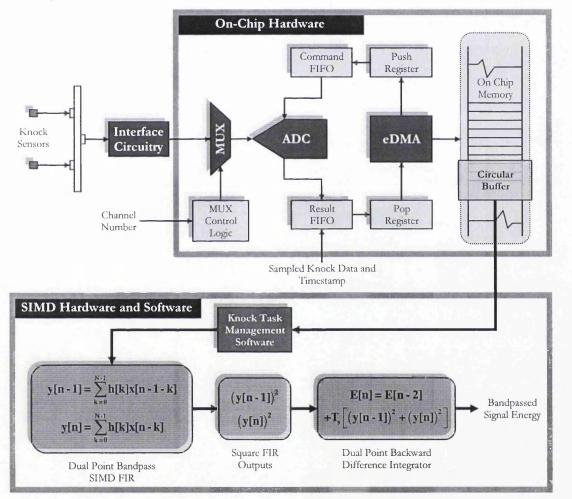

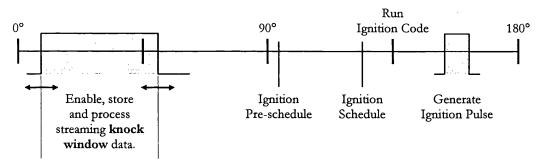

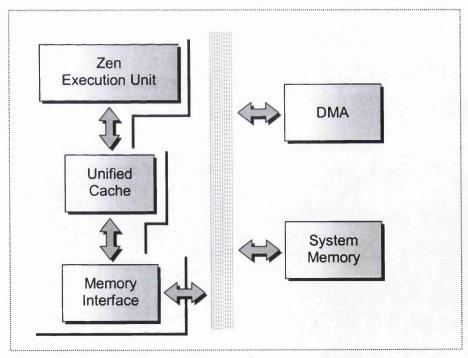

## 3.6.5 Knock Processing Methodology – Data and Algorithmic Flow

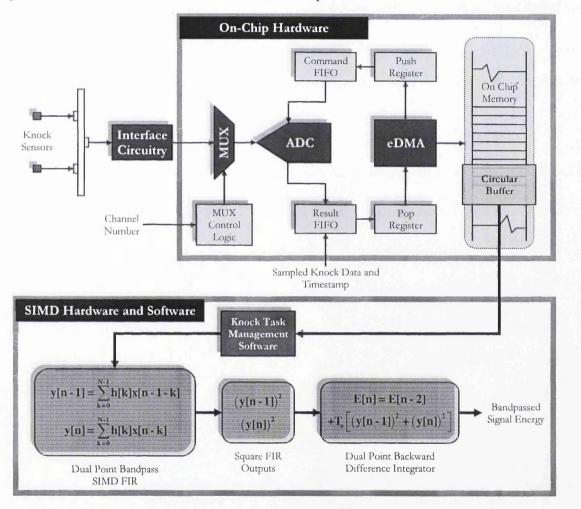

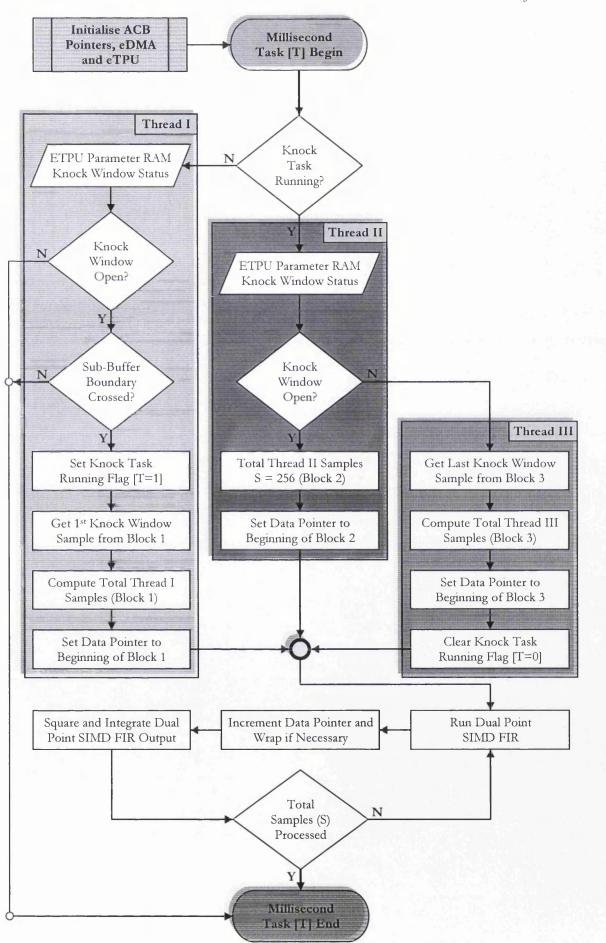

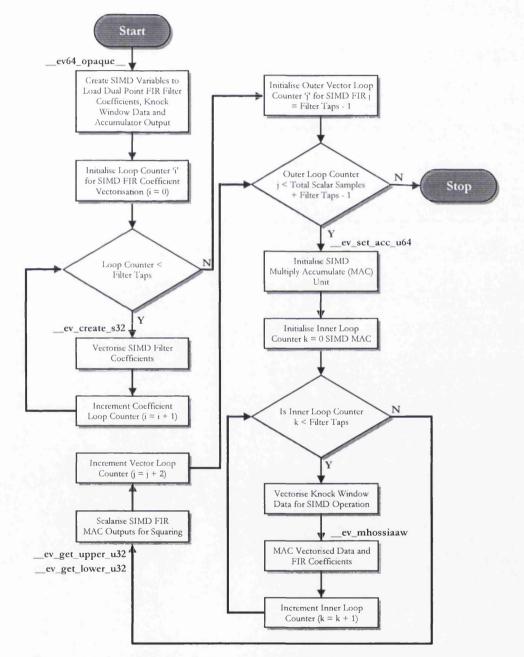

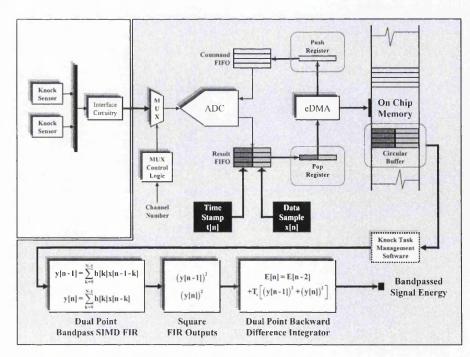

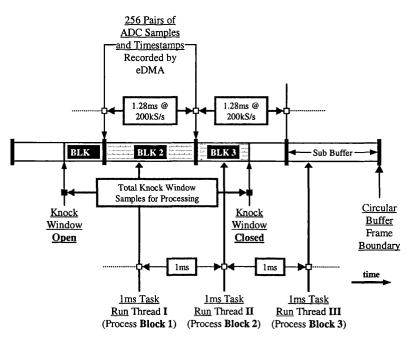

Figure 3.12 illustrates the developed knock sensor data and the algorithmic flow. User programmed eQADC commands are contained in the on-chip memory in a user defined data structure. The eQADC command data is moved from the command queue to the command FIFO buffer by either the host CPU or by the enhanced Direct Memory Access (eDMA) controller. Once the command FIFO is triggered and is transferred into the ADCs on chip, the ADC executes the command, and the result, i.e. a pair of time stamp and data is moved through the result FIFO by the eDMA or the host CPU in to the circular buffer in the on chip memory.

The data in the circular buffer is then processed and presented by the knock task management software threads to the key SIMD knock signal energy extraction elements. The streaming data is then subjected to various SIMD signal processing elements in order to extract the signal of interest [84, 85].

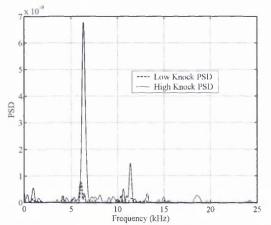

## 3.6.6 Measured Results and conclusions

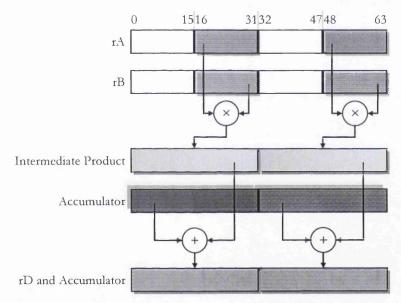

Streaming knock processing constitutes a significant part of current day average microprocessor workloads. To address this, a SoC combining SIMD DSP functionality with a classic microprocessor core has been developed. Peripherals on this SoC designed use fast register and memory based communication and synchronisation mechanisms to deliver high performance. Memory based communication and synchronization is realised using the eDMA module. Parallelism in this application is exploited using a combination of orthogonal parallel processing techniques, namely instruction and data level parallelism (ILP and DLP).

It has been shown that using a common architecture for both RISC and DSP instructions, in combination with autonomous on-chip peripherals, allows complex systems to be built around a single SoC platform, where previously two or more different processors would have been used together [78, 79, 80]. Based on the overall development strategy, it is also evident that real SIMD computers need to have a mixture of single instruction single data (SISD) and SIMD instructions. Importance of SISD elements in the micro-core to perform operations such as branches and address calculations that do not need parallel operation is also highlighted. It is also worth nothing that for efficient dynamic power management and flexibility, unused individual execution units of the SoC are disabled during algorithmic execution.

Thorough experimental analysis of the developed knock control platform confirms that SIMD works best in dealing with arrays of streaming data. Additionally, in the proposed architecture, sustained MAC instructions are executed in a single CPU cycle. In contrast, in a typical fixed-point microprocessor used in an engine control environment, a multiply and an add typically executes in 15 to 20 CPU cycles [81, 86, 87, 88, 89, 90].

The SIMD unit implemented also significantly increases execution speed by performing multiple operations in parallel. For instance, in the same instruction cycle that a MAC operation is performed, a parallel data move is carried out. SIMD enhancements in the SoC supplement the computational speed of present generation real-time processors used and make them ideal for high-performance real-time applications.

41

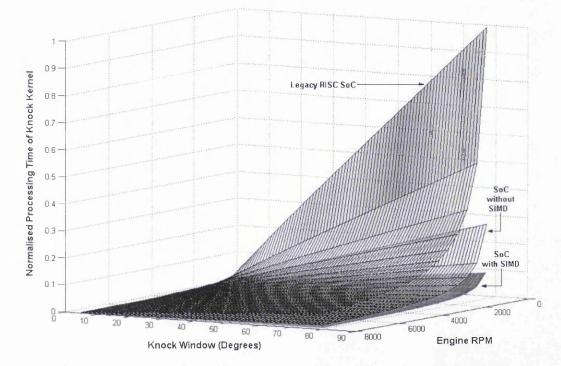

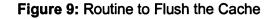

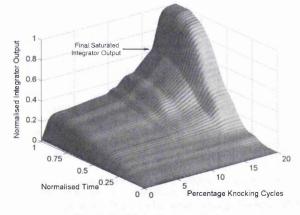

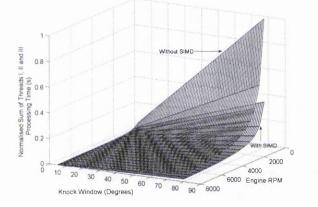

As shown in Figure 3.13, computational bandwidth is what separates the SIMD based core from the classic CPU – the ability to process an abundance of data, consistently, in an uninterrupted stream.

Measured performance results shown in Figure 3.13 confirms that the efficient coding and optimisation techniques used for the SIMD implementation of the knock kernel have improved performance by a minimum of x1.8.

Figure 3.13: Knock Kernel Processing Time with and without SIMD

## 3.7 Next Generation Powertrain SoCs and Their Applications

## 3.7.1 Introduction

Ever increasing performance and increased on-chip memory requirements from various automotive powertrain applications radically increase the demand on powertrain controller overhead and the bandwidth required to run such applications [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 21, 22, 23, 24, 25, 26].

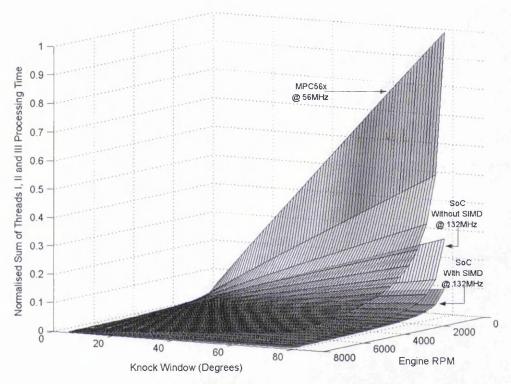

Powertrain applications not only take cost, performance and issues of realtime deterministic operation into account when choosing an SoC, but also lay emphasis on devices with sufficient flexibility and scalability to cope with complex, and modern development methodologies being employed. This document summarises the studies and benchmarking evaluations of customer and author developed application requirements for the natural successor to the developed SoC core.

In general, powertrain applications are driven by two main goals:

- Reduced fuel consumption

- Reduced emissions

These goals are to be achieved at the same or even higher engine power and, of course, at the same system cost level [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 21, 22, 23, 24, 25, 26].

Analysis done on the present customer applications and general trends confirm that new software development techniques presently being employed in powertrain applications increases the code size and requires higher processor bandwidth. Rapidly growing performance requirements are being primarily driven by applications developed with auto code generation using embedded real-time targets [1, 4, 6, 24, 25, 26], enhanced DSP functionality, model fitting to automatically generate calibration tables [24, 25], frequent use of specialist math functions, especially in areas like model based development [1, 4, 6, 22, 24, 26], along with ever increasing quality, reliability and safety.

## 3.7.2 Methodology and Challenges Faced

It is a very well known fact that implementing various number crunching and signal processing algorithms on a general-purpose powertrain CPU core can be very challenging [81, 87, 90]. Issues such as numeric formats and precision, type conversion, cache behaviour, dynamic instruction scheduling, and data-dependent instruction execution times pose hazards for high throughput powertrain applications, especially those running with tight real-time constraints [50, 51, 54, 55, 58, 70, 74, 81, 84, 85, 90,]. An appraisal of such application requirements is done by profiling the critical computational blocks within them using the real-time hardware evaluation board and the AME.

This report summarises the performance requirements of the natural successor core to the one already developed and appraises on the benchmarked and analysed wide range of author and customer developed real-time powertrain applications. Both automotive OEM and Tier I [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 22, 23, 24, 25, 26] application signatures profiled include:

- Table manipulation mechanisms that allows powertrain calibrations system to its most robust operating conditions

- Use of torque-spark curve to model port fuel injection (PFI)

- Fixed and floating point FIR filtering

- Fixed and floating point IIR filtering

- Various adaptive filters

- Fixed and floating point FFT including fast vector magnitude calculation

- Vector dot product

- Advanced motor control for x-by-wire

- Linear regression and radial basis function techniques

## 3.7.3 Suggestions and Conclusions

Based on the analysis done, it is evident that the applications evaluated require various enhancements to present SoC core in order to meet performance targets. Granular profiling of the applications signatures confirm that the features listed in the report are required to performance accelerate *fixed* and *single precision floating* point number crunching algorithms including DSP functionality without sacrificing a clean, intuitive programming model. The following summarises the minimum "standard" features required by the natural successor powertrain SoC platform:

- < ~70% of code density of present SoC to meet customer requirements and to particularly beat competition

- Zero-overhead looping mechanism supporting a minimum of 4K iterations

- Hardware cache coherency mechanism

- An enhanced branch target address and instruction cache (BTAC/BTIC) unit supporting speculative execution and branch prediction.

- Reasonably low capacity, on chip tightly coupled SRAM memory, aka scratch pad memory is required to place and manipulate frequently used data. This memory will be used to create circular buffers as developed in the SIMD based streaming knock processing methodology.

- Multiple hardware single precision floating point multiply accumulate (SPFPMAC) operations per cycle

- Modulo addressing mode supporting circular buffer management

- Misaligned load store support in SIMD

- Fast hardware math functions, particularly single precision squareroot

- Enhanced memory management unit (MMU) granularity

- 100% binary compatibility with the existing core

- Faster bit reversing hardware for FFT

- Wider issue mechanism

- Most of all it would be ideal to have a super compiler to vectorise and exploit full potential of SIMD

- Multithreading and Multiprocessing If the required performance can be met with wider issue, this would obviously be the successor to present core

## 3.8 Portfolio Conclusions and Future Direction

The themed portfolio has examined and proposed strategies for the rapid and efficient development of high-performance automotive powertrain SoCs and their applications. It has been shown how to employ the first-of-its-kind SIMD based SoC micro-architecture to design and develop applications consisting of complex algorithmic control structures and strategies depending on the desired performance, flexibility and particularly cost. The portfolio developed two main novel implementation strategies to support camless engine control and advanced knock processing based on the SIMD SoC. Various next generation SoC core elements required have also been proposed based on thorough profiling of advanced powertrain applications, allowing SoC designers to make hardware and software trade-offs without having to enter the detail design process.

## 3.8.1 Summary of Industrial Research Undertaken

#### Business Plan for the SoC Development of Camless Engine Control

Automotive powertrain controllers are undergoing a drastic transition, from the traditional RISC based microcontrollers to technologically advanced SoCs with increased DSP functionality tightly coupled to the micro-architecture in order to support advanced applications requirements. As the SoCs being introduced are challenged to continue this evolution, the business model established by the author implements the necessary changes to remain a competitive, and to execute the proposed strategies in a manner that ensures continued and improved support and profitability. All efforts required by the proposed business are closely managed to ensure technological advances are not sacrificed and responsibilities are not compromised.

The SoC developed uses heterogeneous computational fabrics to meet conflicting requirements with respect to cost, performance and flexibility related to the camless engine controller market. Two variants of the SoC, targeting two types of camless engine controller platform have already been introduced to the market. Seven patents are initially incorporated. In year three, \$26 million in sales with approximately \$11 million gross profit is projected. It is expected that the gross profit after year six would be approximately \$81 million. The camless market segments are clearly defined and all are subject to a high growth trend. Close collaboration with engine technologist in the field has improved upon the overall marketing strategy significantly. A new, particularly low-cost and innovative design has been created to answer the needs of the ubiquitous low-end camless market. This market should begin at \$61 million but could expand to several hundred million as soon as the technology is fully accepted. The SoC business becomes mature in year four with gross margins of approximately 50% producing \$47 million in gross earnings.

The keys to success for the camless engine controller SoC business are as follows:

- Initial capitalisation obtained

- SoC for the high-end camless engine controllers have been introduced

- All patent applications filed

- The ability to generate early revenue from the low-end market is established

- Top-notch team is in place for successful market roll-out

- Successful implementation of sales and marketing plan to the leading automotive markets in Asia, Europe and the U.S

- Increased product development with technological breakthroughs and continued market share gains to produce a \$47 million revenue by year five

#### An Architectural Modelling Environment for the PowerPC SoC

The diversity of powertrain applications coupled with the radically decreasing time to market is creating the need for new tools to support rapid SoC design at a level of abstraction above the register-transfer level. The architectural modelling environment developed consists of a library of author developed reusable performance models that correspond to the core architectural elements of the powertrain SoC roadmap plus a facility to rapidly assemble these elements into a complete performance model for a new SoC design. The environment helps the successful introduction of advanced powertrain SoCs facilitating the trade-offs between hardware and software elements of all applications targeted.

All application binaries are profiled and their performance metrics on the SoC are collected during simulation by the author. On the AME, the user can always trade simulation performance against depth of profiling by selecting only the relevant parameters, for example the wait states and branching mechanisms. Tight integration of bus and software analysis with the core complex lets the tracing of the segment of application currently executed and what bus transactions are initiated.

These powerful profiling capabilities introduced in the AME enables the determination of exact SoC core complex requirements. The complex UNIX based APIs encapsulated allows complete control over the SIMD micro-architecture efficiently.

#### **Development of a Camless Engine Controller Platform**

Based on the extensive research and development undertaken by the author and engine technology trends, it is evident that camless technology is the future for internal combustion engines. It has been shown by the author that electronic control of engine valves independently using electromagnetic actuation yields benefits such as improving torque production and driveability, increasing fuel economy, reducing weight and decreasing emissions. For example, first-of-its-kind, Honda's mechanical cam based *limited* "variable valve timing and electronic lift control" (VTEC) module first came out in 1991 and was used in the NSX model [3]. This VTEC module is still being incorporated in various Honda engines due to its successful demonstration of the increased engine torque production with lower emissions.

A low cost, automotive qualified SoC based distributed camless engine controller platform, meeting all performance requirements has been developed. The complexity problem of inter SoC communications has also been addressed using FlexRay [11] in order to cope with high data traffic that cannot be supported by existing communications protocols such as CAN [23]. An electromechanical valve actuator model was developed and experiments were used to identify unknown model parameters and functions and to validate the model predictions.

Actuators are programmed to do the same task repeatedly which enables the observation of the control error in successive iterations. An ILC has been developed by the author in order to compensate for and, hence, remove this repetitive error. It has been shown that using such an ILC algorithm, allows the valve motion to approximately converge to a desired trajectory achieving a landing velocity of 0.065m/s in twenty four cycles, potentially eliminating undesired valve landing transients, the so called *soft-landing*.

Overall, the principal emphasis was laid on the modelling, analysis, and SoC hardware linkable real-time simulation for the camless engine controller platform. Such a hardware-in-the-loop environment deployed enables the cost-effective evaluation of new SoC technologies and control strategies. Use of such a camless engine controller development platform promises shorter development time and concomitant reduction of system cost.

#### Fast Internal Combustion Engine Knock Processing

It has been shown that frequent occurrence of the knock phenomenon in an internal combustion engine causes permanent damage. However, in order to obtain maximum power, modern engines are run at their borderline limit of incipient knock using closed-loop control of spark timing based on knock sensor feedback.

Streaming knock processing constitutes a significant part of current day average powertrain microprocessor workloads. To address this, an automotive SoC combining tightly coupled DSP functionality with SIMD has been developed. Peripherals on this SoC designed use fast register and memory based communication and synchronisation mechanisms to deliver high performance. Memory based communication and synchronisation is realised using the eDMA module.

A novel high performance knock detection strategy based on this SoC has been developed by the author encapsulating the optimal use of relevant autonomous on-chip modules.

In the developed SoC micro-architecture, it has been experimentally shown by the author that SIMD works best in dealing with arrays of streaming data. Hence, to have the opportunity for massive parallelism in SIMD there must be massive amounts of data, or data parallelism. It was shown that the performance of the SIMD based knock processing kernel is higher than 80% compared to that of hand optimised classic RISC/non-SIMD based approach.

The C/C++ interface introduce by the author to access the SIMD elements of the SoC micro-architecture eliminates the issues associated with writing code at the assembly level: register allocation, scheduling, stack management and conformance to the underlying application binary interface (ABI). It has been shown that the intrinsic interface developed enables the embedded compiler to optimise the instruction scheduling.

Overall, for the automotive powertrain environment, the change from standard scalar 32-bit to SIMD vector 64-bit register based cores has been established, allowing the implementation of advanced algorithms with minimal processing time.

#### Embedded Von-Neumann On-Chip PowerPC SoC Cache

It has been shown by the author that the performance of the unified cache module incorporated on the SoC is critical to alleviate the increasing gap between the SoC core and on-chip memory speed. The first-of-its-kind cache implemented on the SoC improves overall system performance by providing low-latency data to the core instruction and data pipelines. However, it was confirmed that poor reuse of data, conflicts between various references and underutilisation of cache capacity lead to poor cache performance for various commonly used applications.

Software techniques have been introduced by the author to explicitly accomplish cache coherency as the cache does not have dedicated hardware enforcing coherency. In conjunction with the compiler, with no changes to existing instruction set, it has been shown by the author that cache can be used as local memory with minimal overhead. Data pre-fetching, blocking, and data copying techniques have been also been introduced to improve overall cache performance.

It was established by the author that the best general approach to making good use of the cache module is to keep the performance critical elements of applications as small as possible so that it can completely be loaded onto the cache module. Particularly, linked lists intensive applications are bad for the cache due to the widely spread out memory accesses.

Hardware configurable, load and lock mechanism has also been implemented on the cache in order to guarantee the availability of instruction and data. This feature is particularly useful for critical interrupt handler routines in order to provide fast and guaranteed interrupt performance.

#### Next Generation Powertrain SoC Performance Requirements

It has been established by the author that performance evaluation of the developed powertrain SIMD SoC core is more complex than the classic RISC machines. The overall performance of powertrain applications profiled by the author depends on a number of performance metrics such as the average instruction length, cache configuration, branching mechanisms and the number of memory references per instruction. The analysis conducted by the author is used for the solidification of future powertrain SoC core architecture and their embedded compilers.

#### Future Work

- 1. The first step is to establish a stronger and particularly a realistic vision for the SoC business targeting the *low-end* engine market for both camless engine controllers and knock processing platforms.