https://theses.gla.ac.uk/

#### Theses Digitisation:

https://www.gla.ac.uk/myglasgow/research/enlighten/theses/digitisation/

This is a digitised version of the original print thesis.

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses

<a href="https://theses.gla.ac.uk/">https://theses.gla.ac.uk/</a>

research-enlighten@glasgow.ac.uk

### AN INTEGRATED ENVIRONMENT FOR ELECTRO-MECHANICAL SYSTEMS DESIGN AND ANALYSIS

by

Azeddin Mohamed Shaeb Margani (B.Eng., MSc)

Thesis presented for the Degree of Doctor of Philosophy under general regulations

Department of Mechanical Engineering

Faculty of Engineering

University of Glasgow

ProQuest Number: 10391393

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10391393

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

Thesis 10957 Cony 2

GLASGOW UNIVERSITY LIBRARY

## **Synopsis**

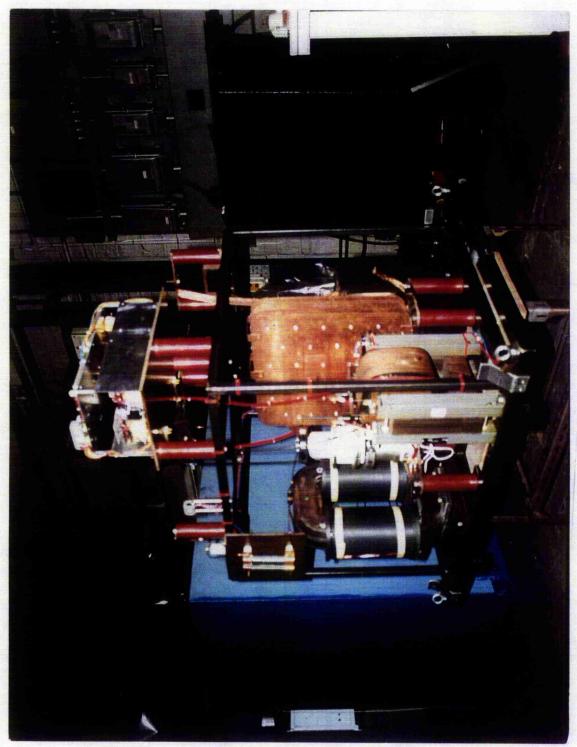

The purpose of this research was to examine current methodology and design tools for concurrent engineering of complex systems. A prime objective of the work was to develop an integrated CAE system for concurrent engineering and to investigate performance issues, including: Design management, productivity, modelling and simulation. The main aspects that are important in achieving total design integration have been considered and extensively studied, including: System functionality requirements, design flow, system integration, applications design, and data management. An integrated design environment has been developed utilising open architecture, commercial CAD systems and databases. An extensive range of design tools have been developed which facilitate the process of design and design management.

Issues relating to transfer of data across domains (or disciplines) are addressed specifically. A "netlist" generating systems has been designed to facilitate data transfer between domains and from design to simulation. Several techniques have been assessed and fully functional system developed utilising database extraction.

A database was used to assist in many areas, in particular, the strong need for efficient design data management. Various tools have been designed and developed to ensure that integration between the different environments is achieved and also to accommodate the needs of profile interchange between tools. The development of these tools comprises three major parts. In part 1, methods of design reports generation are described. Part 2 concerned with the design and development of data update tools. Part 3 is concerned with data manipulation. Design examples are used to demonstrate the performance of these tools.

#### Synopsis

The work on implementing the graphical user interface (GUI) has produced a large variety of design tools and utilities. This work describes the design and development of these tools and their applications to perform design, modelling and simulation.

Evaluation and performance of the software have been demonstrated based on a coupled example of electro-mechanical design. A set of design issues involving graphics constructions of both 2D schematics and 3D modelling, design tool capabilities, and design simulation was considered and performed.

The results of this work have produced many specific design tools. In a broader sense, the research has examined key issues of design management in concurrent engineering and drawn important conclusions.

### Acknowledgment

I would like to express my gratitude to Dr. D. McDonald for his encouragement and guidance during this research, and for his useful discussions and ideas.

Particular thanks are due to the technicians: Gordon Hicks and Bernard Hoey for their assistance and useful suggestions. I would also like to thank Ian Peden for the invaluable assistance with computer hardware.

Finally, I would like to thank my family for their encouragement and continuous support during my study.

| SYNOPS | SIS                                           | ii   |

|--------|-----------------------------------------------|------|

| ACKNO  | WLEDGEMENT                                    | iv   |

|        |                                               | xi   |

| LIST O | FFIGURES                                      | XI   |

| LIST O | F TABLES                                      | XX   |

| NOMEN  | NCLATURE                                      | xxii |

| СНАРТ  | ER 1. INTRODUCTION.                           |      |

| 1.1    | BACKGROUND.                                   | 1    |

| 1.2    | DESIGN PRACTICE.                              | 1    |

| 1.3    | DESIGN SYSTEMS.                               | 5    |

| 1.4    | MARKET FOR MECHANICAL DESIGN SOFTWARE.        | 6    |

| 1.5    | DESIGN SYSTEMS AND METHODOLOGY.               | 8    |

|        | 1.5.1 Product Design Approach                 | 8    |

| 1.6    | DETAILED DESIGN PROCESSES.                    | 10   |

|        | 1.6.1 Electronics Schematics and PCB Layout   | 10   |

|        | 1.6.2 Circuit Simulation and Analysis         | 11   |

|        | 1.6.3 Thermal Analysis                        | 13   |

|        | 1.6.4 Mechanical Drafting and Solid Modelling | 14   |

|        | 1.6.5 Mechanical Dynamics                     | 14   |

|        | 1.6.6 Finite Element Analysis                 | 15   |

| 1.7    | CONCLUSIONS.                                  | 15   |

| 1.8    | SCOPE OF PRESENT WORK.                        | 16   |

|        | 1.8.1 Outline of Thesis                       | 16   |

| RE     | FERENCES.                                     | 18   |

| СНАРТ  | TER 2. SYSTEM DESIGN AND DEVELOPMENT.         |      |

| 2.1    | INTRODUCTION.                                 | 21   |

| 2.2    | DESIGN CONSIDERATIONS.                        | 24   |

| 2.3    | SYSTEM DESIGN ARCHITECTURE.                   | 25   |

|        | 2.3.1 Graphical User Interface (GUI)          | 25   |

|        | 2.3.2 Cells Libraries                         | 27   |

|      | 2.3.3    | Design Activities                         | 27         |

|------|----------|-------------------------------------------|------------|

| 2.   | 4 SYSTE  | EM IMPLEMENTATION.                        | 28         |

|      | 2.4.1    | Hardware Considerations                   | 29         |

|      | 2.4.2    | System Design Software                    | 29         |

|      | 2.4.3    | System Functionality                      | 32         |

|      | 2.4.4    | System Integration                        | 33         |

|      | 2.4.5    | Design Flow                               | 34         |

|      | 2.4.6    | Design Data Management                    | 34         |

| 2    | .5 SPECI | FIC SOFTWARE REQUIREMENTS.                | 19         |

|      | 2.5.1    | Physical Design Aids                      | 40         |

|      | 2.5.2    | Design Connectivity and Testability       | 40         |

|      | 2.5.3    | Integration With Standard Database        | 41         |

|      | 2.5.4    | Circuit Documentation and Data Extraction | 42         |

| 2    | .6 CONC  | CLUSION.                                  | 56         |

| R    | REFEREN  | CES.                                      | 56         |

|      |          |                                           | <b>~</b> 0 |

| СНАН | TER 3.   | COMPONENT DESIGN AND MODELLING.           | 59         |

| 3    | .1 INTRO | ODUCTION.                                 | 59         |

| 3    | .2 COM   | PONENT MODELLING.                         | 60         |

|      | 3.2.1    | Modelling Objective                       | 60         |

|      | 3.2.2    | Fundamental Modelling Concepts            |            |

|      | 3.2.3    | PSPICE and Parts Models                   | 60         |

|      | 3.2.4    | Circuit Modelling Languages               | 61         |

| 3    | .3 ELEC  | TRO-MECHANICAL DESIGN.                    | 63         |

|      | 3.3.1    | Electro-mechanical relational Design      | 64         |

|      | 3.3.2    | Parametric Design                         | 65         |

|      | 3.3.3    | Parts and Attributes                      | 66         |

| 3    | .4 DESIG | GN AND MODELLING PROCEDURE.               | 69         |

|      | 3.4.1    | The Procedure Requirements                | 70         |

| 3    | .5 COMI  | PONENTS DESIGN ENVIRONMENT.               | 71         |

|      | 3.5.1    | Integration of Tool sets                  | 71         |

|      | 3.5.2    | Libraries Cells Design                    | 72         |

|      | 3.5.3    | Interaction with Database                 | 72         |

| 3    | 3.6 COMI | PONENT DESIGN EXAMPLES.                   | 73         |

|  | 114 |

|--|-----|

|  |     |

|  |     |

|  |     |

|  | 100 |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  | 1   |

|  |     |

|  |     |

|  |     |

|  | -5  |

|       | 3.6.1   | Charging Inductor Design                     | 73  |

|-------|---------|----------------------------------------------|-----|

|       | 3.6.2   | Problem Definition                           | 75  |

|       | 3.6.3   | Theoretical Calculations                     | 76  |

|       | 3.6.4   | Design Optimisation                          | 78  |

|       | 3.6.5   | Software Program Development                 | 80  |

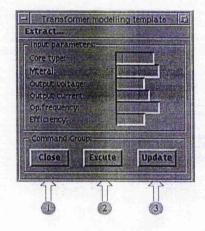

|       | 3.6.6   | Design of a High Frequency Transformer       | 84  |

|       | 3.6.7   | Transformer Theory                           | 85  |

|       | 3.6.8   | Problem Definition                           | 87  |

|       | 3.6.9   | Transformer Theoretical Calculations         | 88  |

| 3.7   | DESIG   | SN SIMULATION                                | 94  |

|       | 3.7.1   | Simulation Results using PSPICE              | 94  |

|       | 3.7.2   | Simulation Results using TK solver           | 96  |

| 3.    | 8 CONC  | CLUSION.                                     | 99  |

| R     | EFEREN  | NCES.                                        | 99  |

| CHAP' | TER 4.  | AUTOMATIC NETLIST GENERATION.                | 102 |

| 4.3   | 1 INTRO | DDUCTION.                                    | 102 |

| 4.2   | 2 THE I | MPORTANCE OF CIRCUIT NETLISTS.               | 103 |

| 4.3   | 3 RELA  | TED WORK.                                    | 103 |

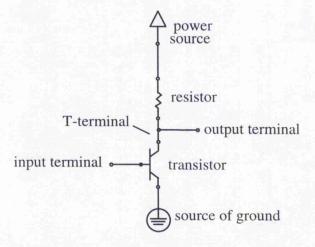

|       | 4.3.1   | The need for Computer Aided Circuit Analysis | 107 |

|       | 4.3.2   | PSPICE Background Information                | 108 |

|       | 4.3.3   | Circuit Definition in PSPICE                 | 108 |

|       | 4.3.4   | Process for Using PSPICE in Electronic CAD   | 109 |

| 4.4   |         | IST DESIGN DEVELOPMENT.                      | 111 |

|       |         | Problem Definition                           | 112 |

|       |         | General Development Rules                    | 113 |

|       | 4.4.3   | Connectivity Establishment                   | 114 |

| 4.    |         | RENT TECHNIQUES USED FOR NETLIST GENERATION. | 115 |

|       | 4.5.1   | Matrix Comparison Technique                  | 115 |

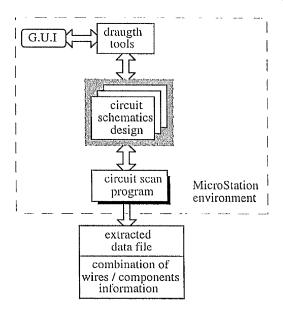

|       |         | Circuit Data Extraction                      | 118 |

|       |         | Software Program Description                 | 119 |

|       |         | The use of Database                          | 127 |

|       |         | User Defined Netlist                         | 128 |

| 4.    | 6 CONC  | CLUSIONS.                                    | 134 |

| R     | EFEREN  | ICES.                                        | 135 |

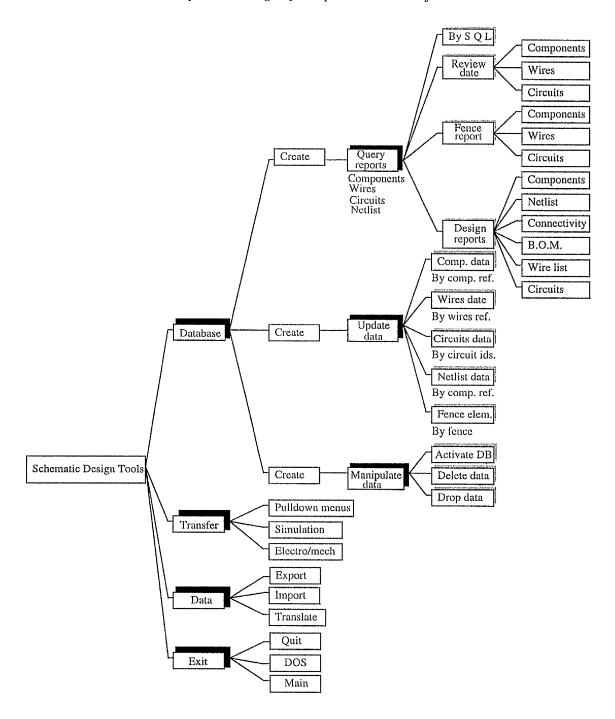

| CHAPTER 5. DESIGN FOR DATABASE AUTO LINK.           | 137 |

|-----------------------------------------------------|-----|

| 5.1 INTRODUCTION.                                   | 137 |

| 5.2 A HISTORY AND EVALUATION OF DATABASE SYSTEMS.   | 139 |

| 5.3 THE ROLE OF DATABASE IN CAD.                    | 139 |

| 5.4 INTERFACING WITH SOFTWARE ENGINEERING.          | 141 |

| 5.5 COMMERCIAL DATABASE SYSTEMS.                    | 141 |

| 5.6 RELATIONAL DATABASE CONCEPTS.                   | 142 |

| 5.6.1 Data Relational Model                         | 143 |

| 5.6.2 Relationships Determination                   | 145 |

| 5.6.3 The use of Structural Query Language          | 145 |

| 5.7 DESIGN DEVELOPMENT.                             | 146 |

| 5.7.1 Applications Design Methodology               | 149 |

| 5.7.2 Database Editing Interface                    | 152 |

| 5.7.3 Setting up and Accessing the Database         | 152 |

| 5.7.4 Linking Circuit Elements to Database Records  | 153 |

| 5.7.5 Data Tables Design                            | 153 |

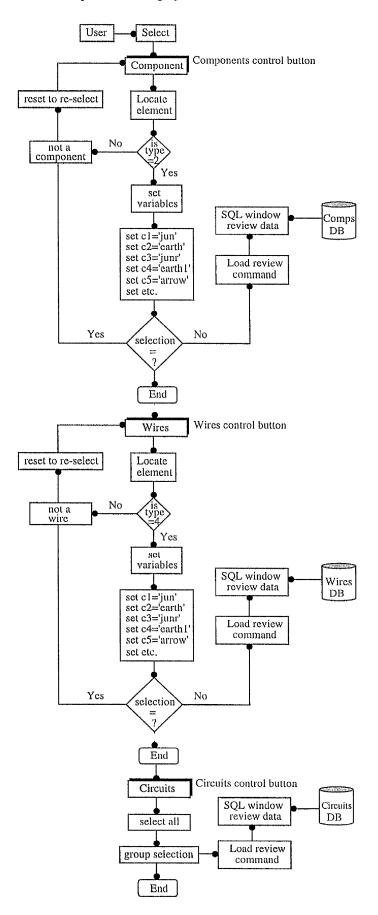

| 5.7.6 Automatic Element Recognition                 | 154 |

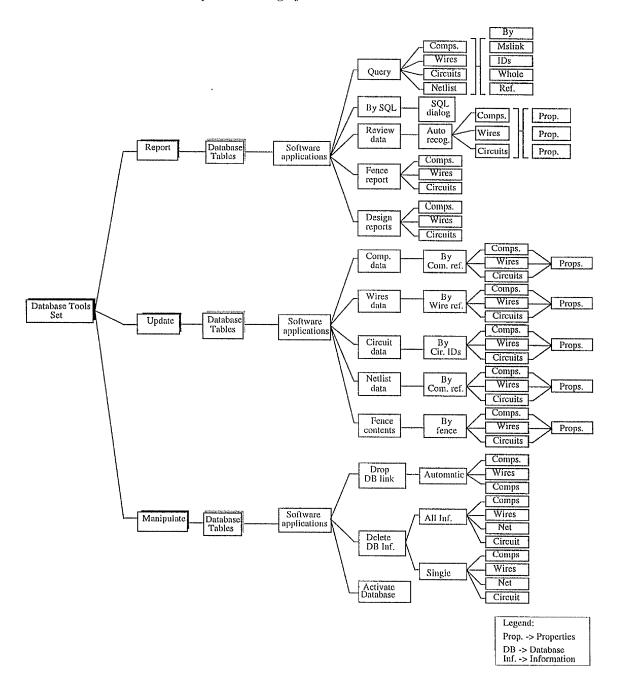

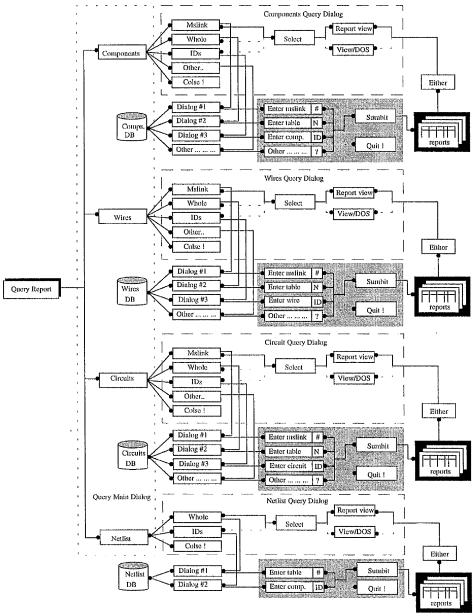

| 5.8 DATA QUERIES AND REPORTS GENERATION.            | 154 |

| 5.8.1 Design for Data Query                         | 155 |

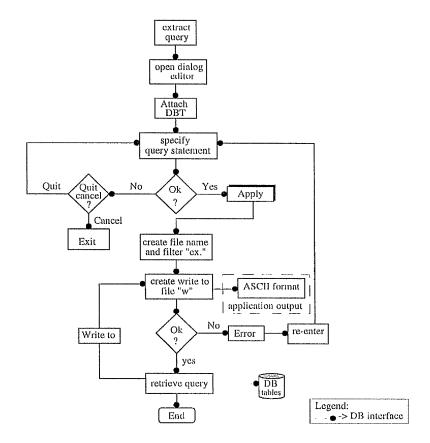

| 5.8.2 Design for Data retrieval                     | 157 |

| 5.8.3 Design for Reports Generation                 | 161 |

| 5.8.4 Design for Fence Reporting                    | 162 |

| 5.9 DESIGN FOR DATA UPDATE.                         | 163 |

| 5.9.1 Update by Fence Design                        | 166 |

| 5.10 DESIGN FOR DATA MANIPULATION.                  | 167 |

| 5.10.1 Data Deletion                                | 167 |

| 5.10.2 Automatic Data Linkage Dropping              | 168 |

| 5.11 CONCLUSION.                                    | 170 |

| REFERENCES.                                         | 170 |

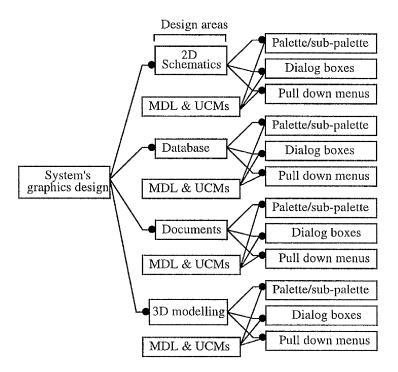

| CHAPTER 6. DESIGN OF GRAPHICS USER INTERFACE (GUI). | 173 |

| 6.1 INTRODUCTION.                                   | 173 |

| 6.2 REVIEW OF GRAPHICS SYSTEMS.                     | 174 |

| 6.3 GRAPHICS DESIGN AND ENGINEERING CONSIDERATION. | 174 |

|----------------------------------------------------|-----|

| 6.4 GRAPHICS AND TOOL CUSTOMISATION.               | 175 |

| 6.5 GRAPHICS MODELLING METHODS.                    | 176 |

| 6.5.1 Graphic Model Representation                 | 176 |

| 6.5.2 Symbol hierarchies                           | 177 |

| 6.6 GRAPHICS DESIGN AND DEVELOPMENT.               | 177 |

| 6.6.1 Design Methodology                           | 177 |

| 6.7 DESIGN OF USER INTERFACE.                      | 178 |

| 6.7.1 Review of User Interface Generators          | 179 |

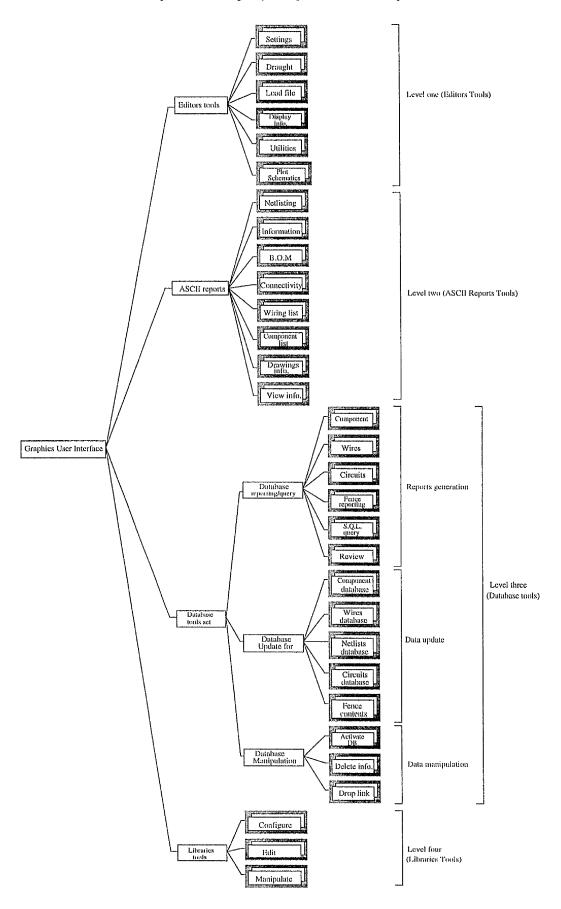

| 6.7.2 User Interface Design Levels                 | 181 |

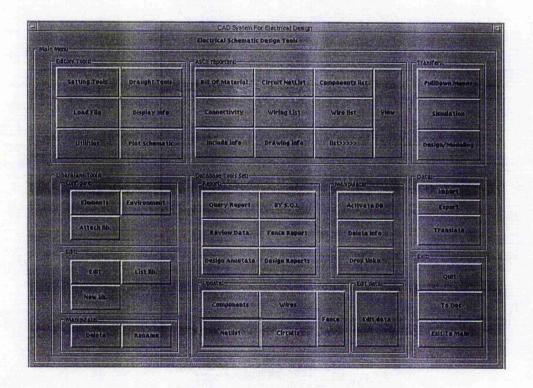

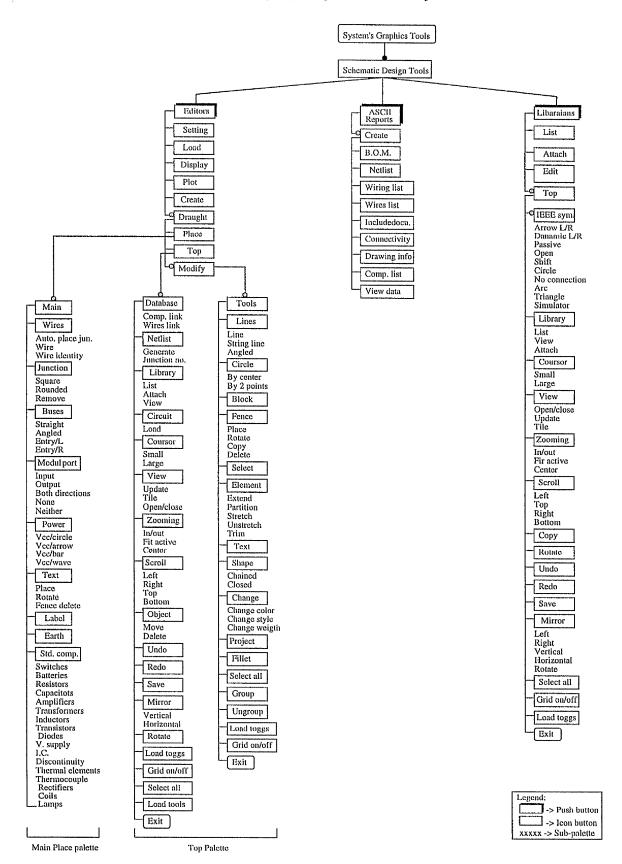

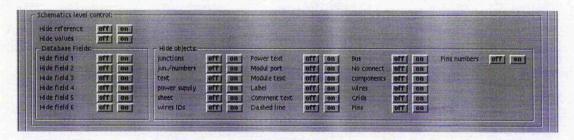

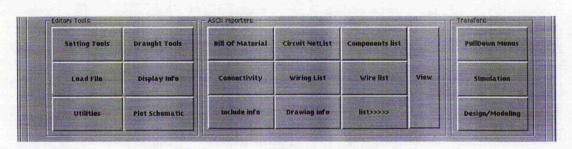

| 6.8 ELECTRICAL SCHEMATIC DESIGN TOOLS              | 184 |

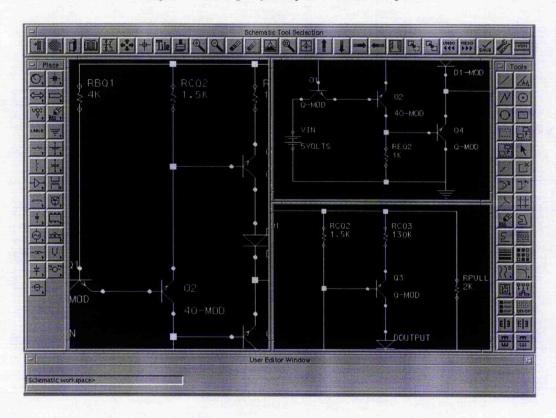

| 6.8.1 Schematics Workspace Design                  | 184 |

| 6.8.2 Editors Tools Design                         | 185 |

| 6.8.2.1 Design of Drafting Tools                   | 186 |

| 6.8.2.2 Design of Schematics Palettes              | 188 |

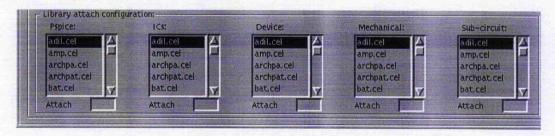

| 6.8.2.3 Design of Configuration Tools              | 202 |

| 6.8.3 Design By Levels                             | 207 |

| 6.9 DESIGN OF ASCII REPORTS TOOLS.                 | 209 |

| 6.10 DESIGN OF TRANSFER TOOLS.                     | 210 |

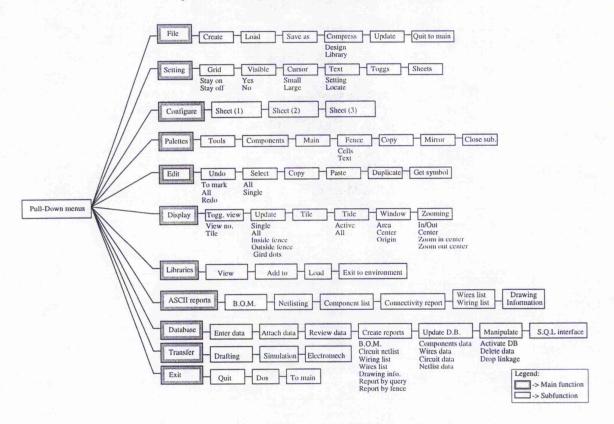

| 6.10.1 Pull-Down Menus Environment Design          | 210 |

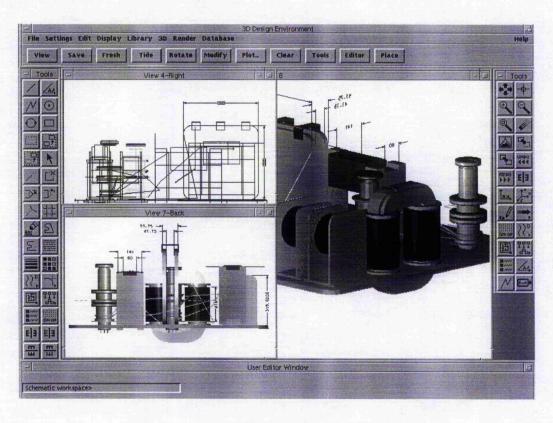

| 6.10.2 3D Environment Design                       | 214 |

| 6.11 DESIGN OF LIBRARIES TOOLS.                    | 215 |

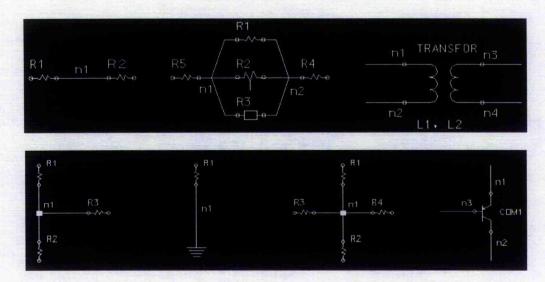

| 6.11.1 Symbols Creation                            | 218 |

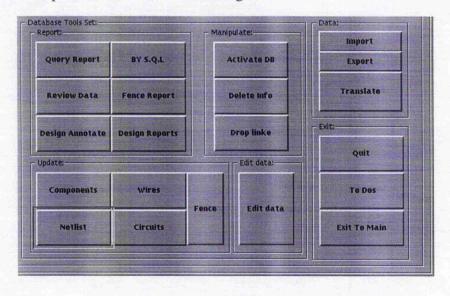

| 6.12 DESIGN OF DATABASE TOOLS SET.                 | 221 |

| 6.13 DESIGN OF DATA TOOLS.                         | 229 |

| 6.14 DESIGN OF EXIT TOOLS.                         | 229 |

| 6.15 CONCLUSION.                                   | 229 |

| REFERENCES.                                        | 229 |

| CHAPTER 7. SOFTWARE PERFORMANCE AND EVALUATION.    | 231 |

| 7.1 INTRODUCTION.                                  | 231 |

| 7.2 DEDECOMANCE EVALUATION                         | 221 |

| 7.3   | A DESIGN E  | XAMPLE.                             | 232 |

|-------|-------------|-------------------------------------|-----|

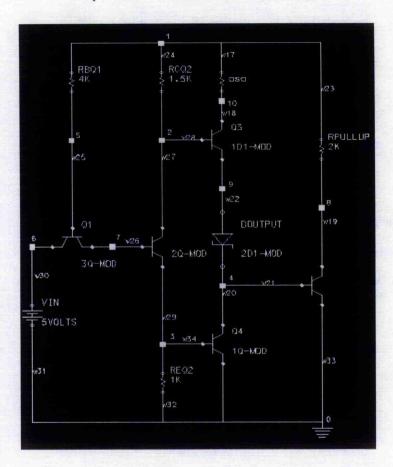

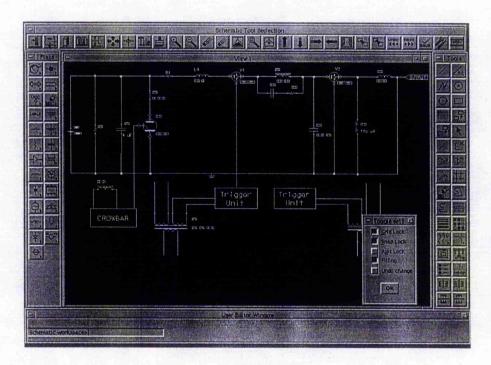

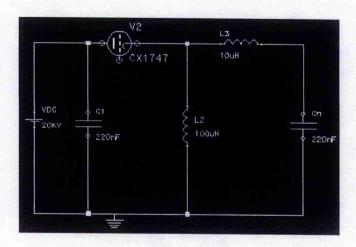

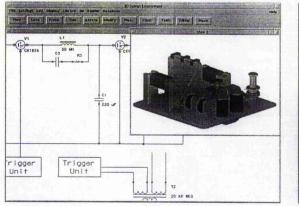

|       | 7.3.1 Circu | uit General Description             | 232 |

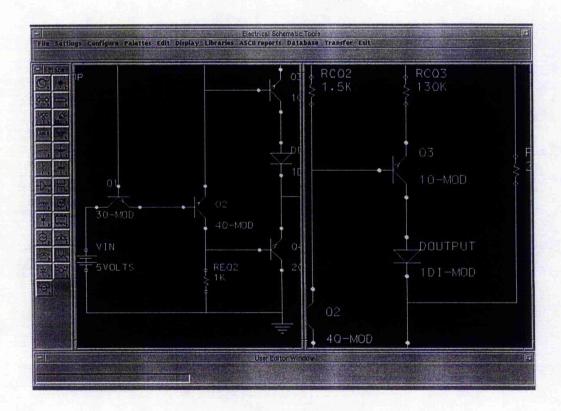

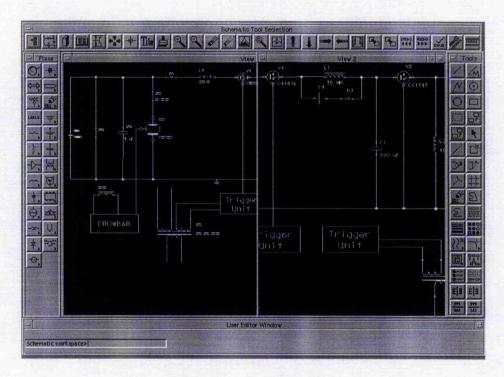

|       | 7.3.2 2D C  | Circuit Representation              | 233 |

| 7.4   | CIRCUIT DI  | ESIGN AND ANALYSIS.                 | 234 |

|       | 7.4.1 Desi  | gn of First stage                   | 234 |

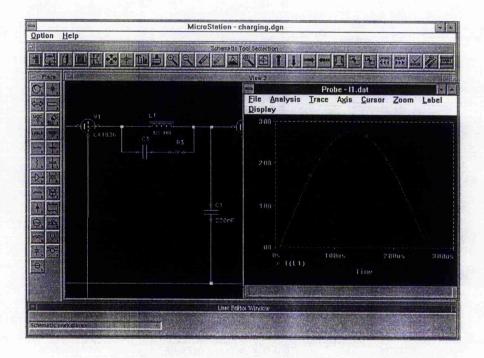

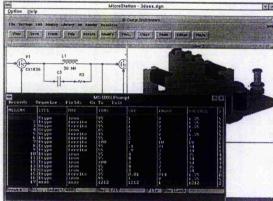

|       | 7.4.2 Sim   | ulation of First Stage              | 238 |

|       | 7.4.3 Desi  | gn Optimisation and Performance     | 241 |

|       | 7.4.4 Desi  | gn of the Second Stage              | 241 |

|       | 7.4.5 Sim   | ulation of Second Stage             | 244 |

| 7.5   | MECHANIC    | CAL DESIGN.                         | 246 |

|       | 7.5.1 Com   | nponents Design Description         | 246 |

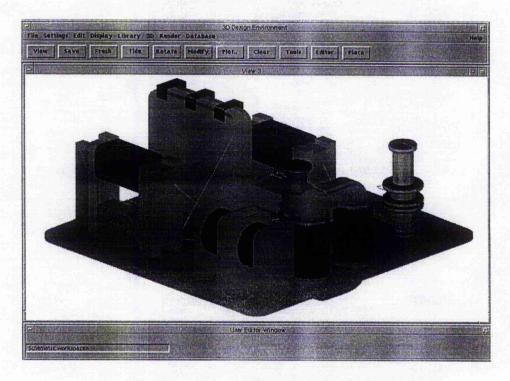

|       | 7.5.2 3D I  | Layout Representation               | 249 |

|       | 7.5.3 The   | Assembly Wiring Connections         | 251 |

| 7.6   | ENVIRONM    | MENT INTEGRATION.                   | 254 |

|       | 7.6.1 The   | Interface between 2D and 3D layouts | 255 |

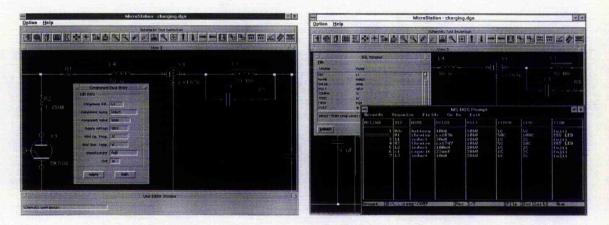

|       | 7.6.2 Cor   | nponents Modelling Procedure        | 255 |

|       | 7.6.3 Inte  | egration with the Common Database   | 256 |

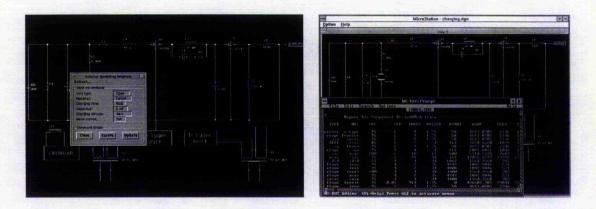

| 7.7   | DESIGN CO   | FIGURATION.                         | 259 |

| 7.8   | DESIGN DO   | CUMENTATION.                        | 260 |

| 7.9   | CONCLUSIO   | ONS.                                | 261 |

| RE    | FERENCES.   |                                     | 262 |

|       |             |                                     |     |

| CHAPT | ER 8. GENE  | RAL CONCLUSIONS AND FUTURE WORK.    | 263 |

| 8.1   | GENERAL (   | CONCLUSION.                         | 263 |

| 8.2   | FUTURE W    | ORK.                                | 268 |

### CHAPTER 1.

| Section | on 1.5                                                    |    |

|---------|-----------------------------------------------------------|----|

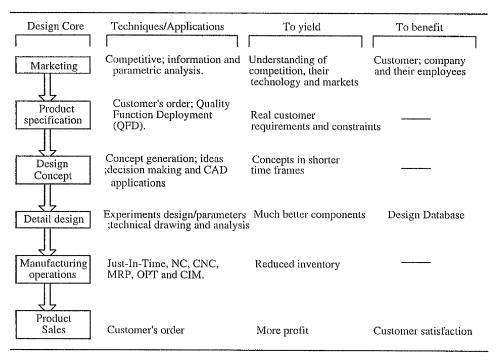

| 1.1     | Product-design process supported by CAD applications.     | 9  |

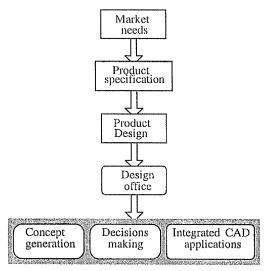

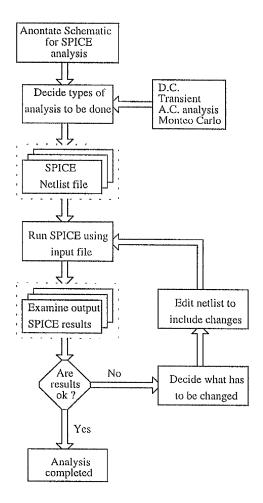

| 1.2     | Customer requirements and product characteristics matrix. | 10 |

| Section | on 1.6                                                    |    |

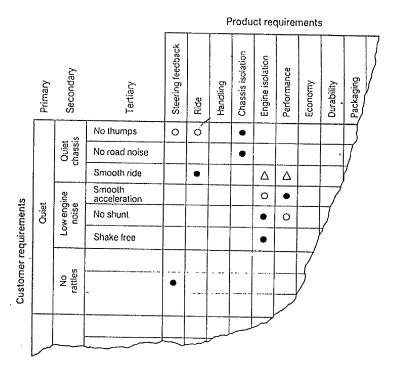

| 1.3     | Flowchart of SPICE general analysis process.              | 11 |

| СНА     | PTER 2.                                                   |    |

| Section | on 2.1                                                    |    |

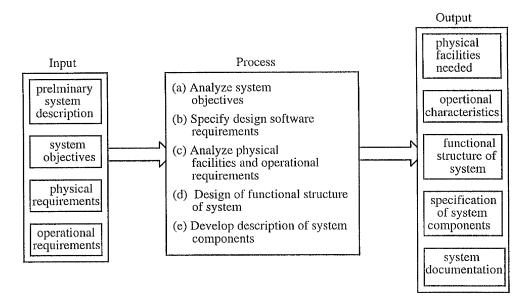

| 2.1     | Overview of system design life cycle.                     | 22 |

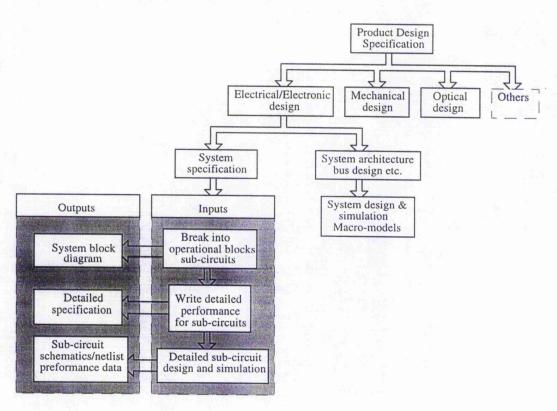

| 2.2     | Breakdown for electronics products systems.               | 23 |

| Section | on 2.2                                                    |    |

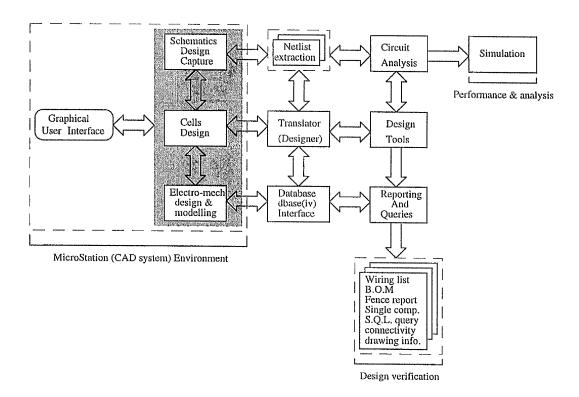

| 2.3     | The system components block diagram.                      | 25 |

| Section | on 2.3                                                    |    |

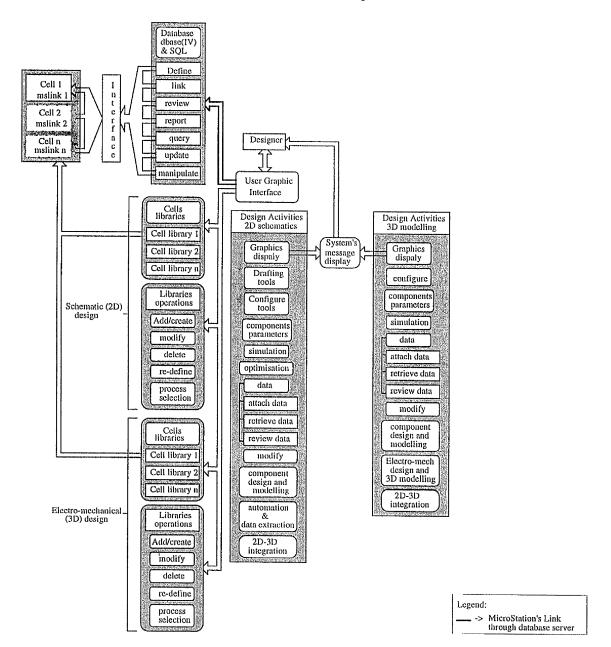

| 2.4     | Illustration of the design detailed structure.            | 26 |

| Section | on 2.4                                                    |    |

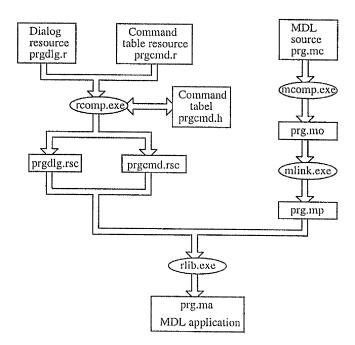

| 2.5     | Applications development procedure.                       | 30 |

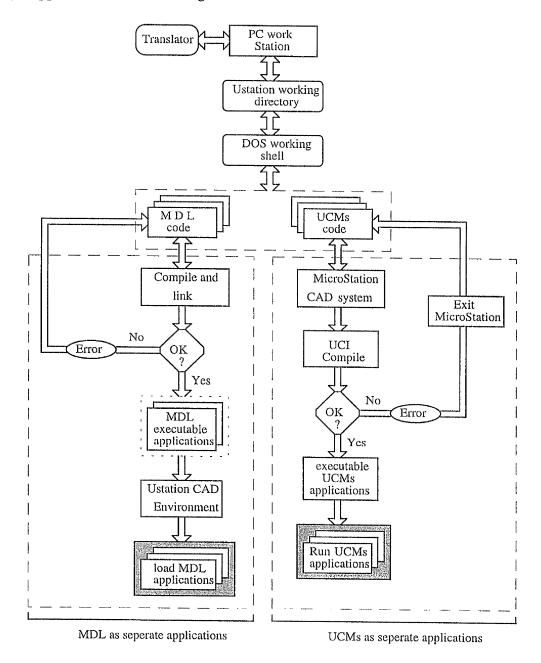

| 2.6     | Programming of MDL and UCMs as separate applications.     | 31 |

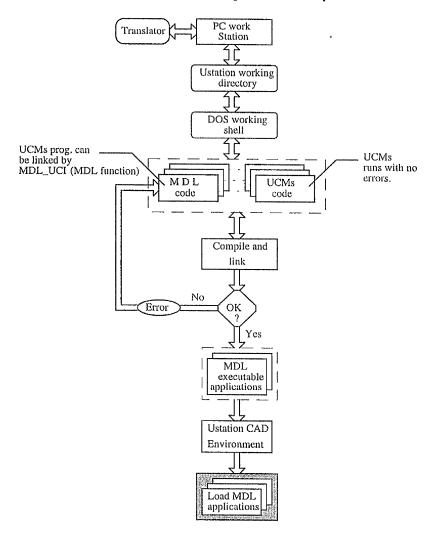

| 2.7     | MDL and UCMs combined as single application.              | 32 |

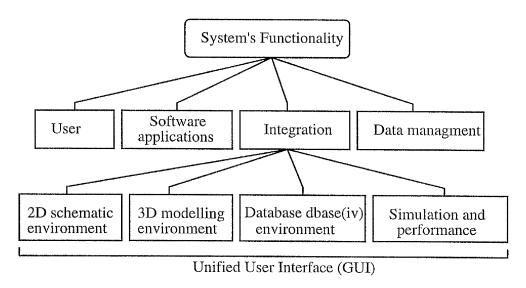

| 2.8     | Concept of system functionality levels.                   | 33 |

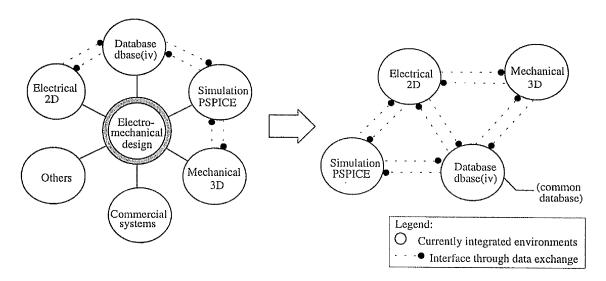

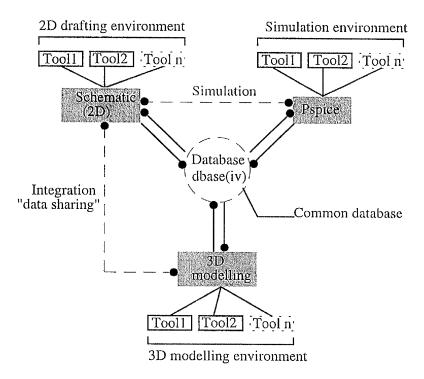

| 2.9     | The system integrated environments.                       | 34 |

| 2.10    | Design flow proceeds towards complete integration.        | 35 |

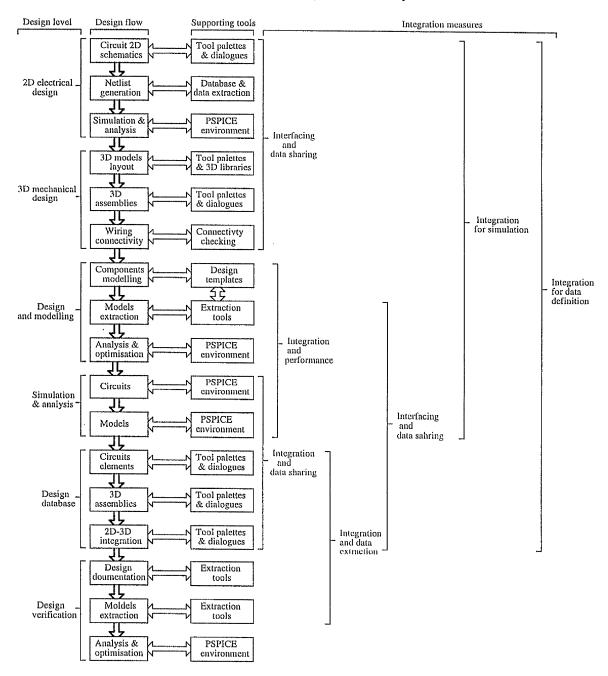

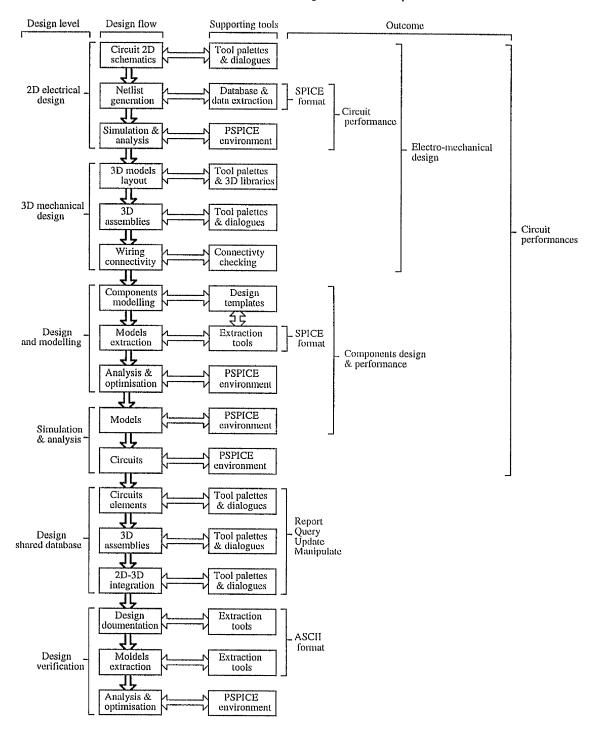

| 2.11    | Design flow and supporting tools.                         | 36 |

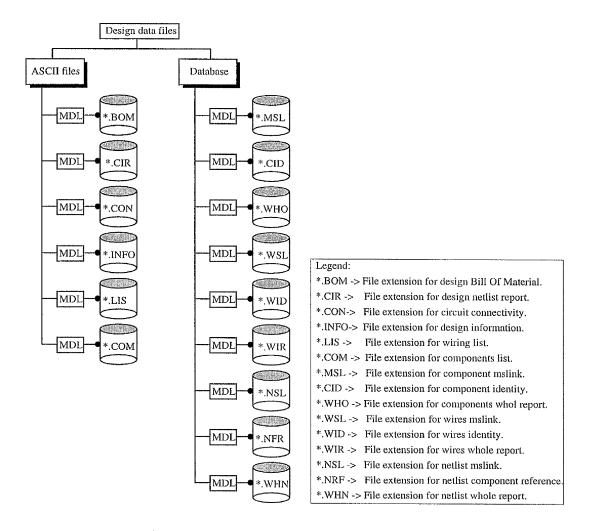

| 2.12    | Extracted data and files extensions.                      | 38 |

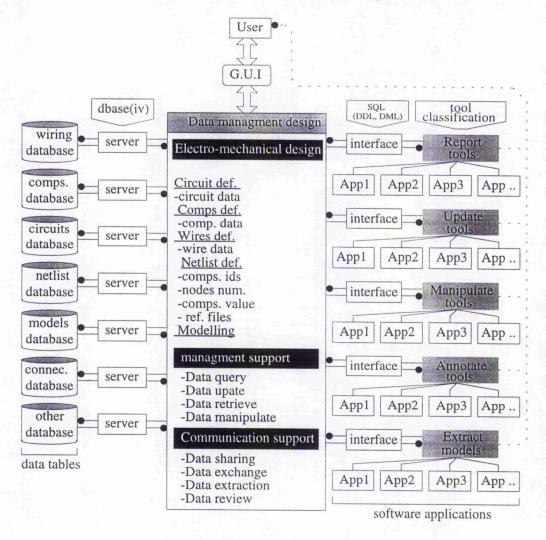

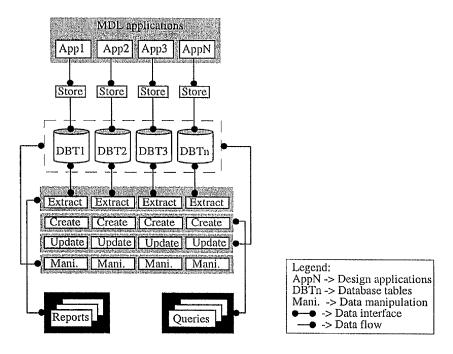

| 2.13    | Overall architecture of data management design.           | 39 |

| Section | on 2.5                                                    |    |

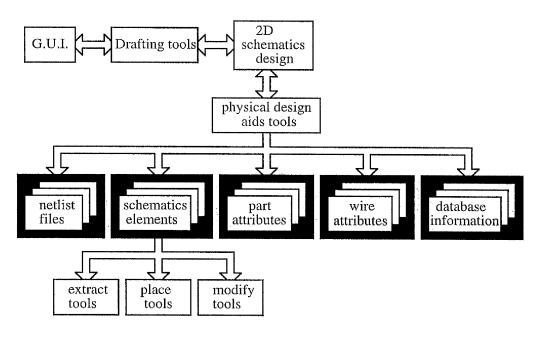

| 2.14    | Design of circuit design tools.                           | 40 |

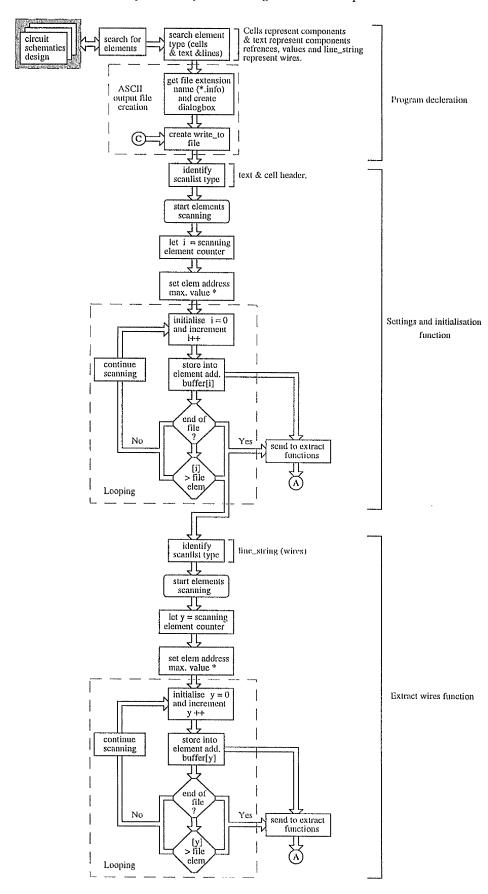

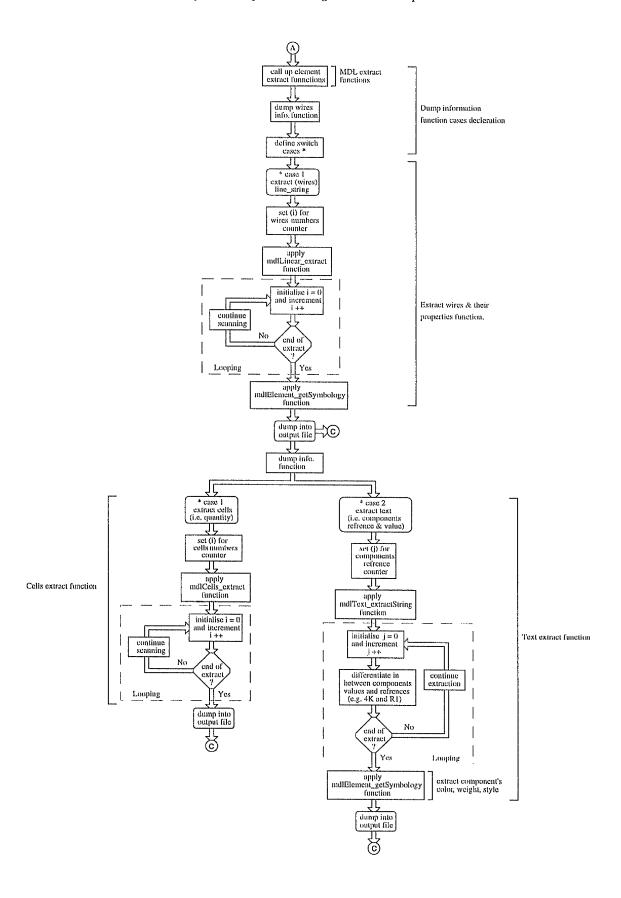

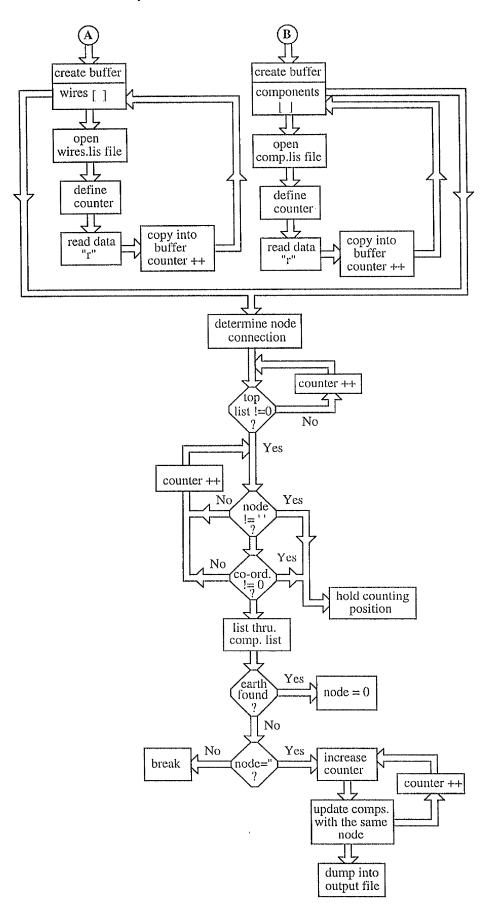

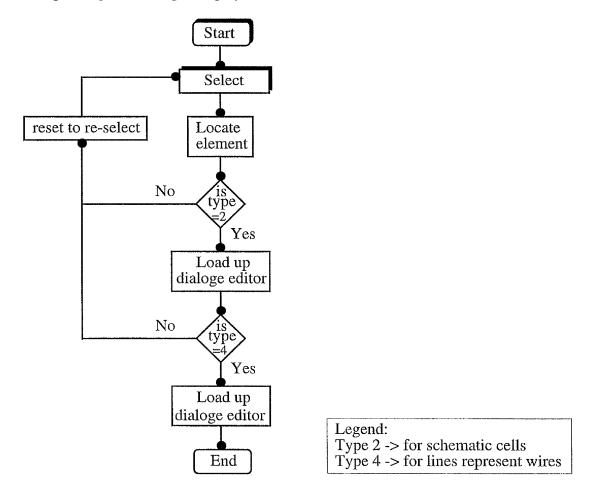

| 2.15    | Flowchart of circuit connectivity program.                | 46 |

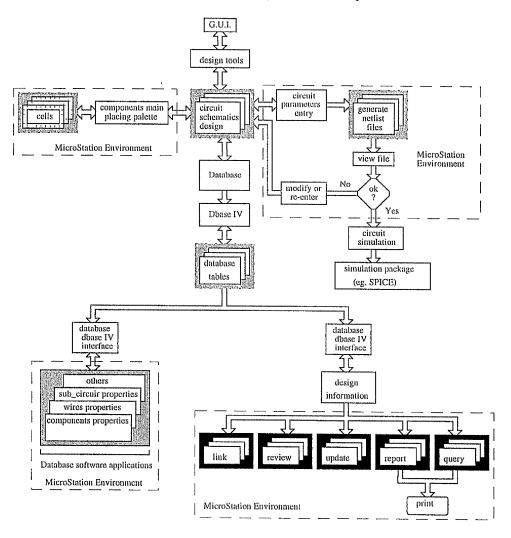

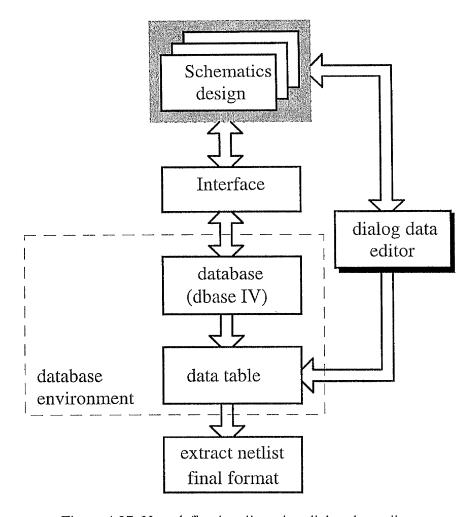

| 2.16    | Circuit information flow and database linkage.            | 42 |

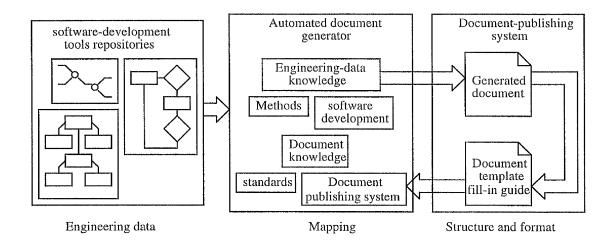

| 2.17    | Flow of information in an automated document generator.   | 43 |

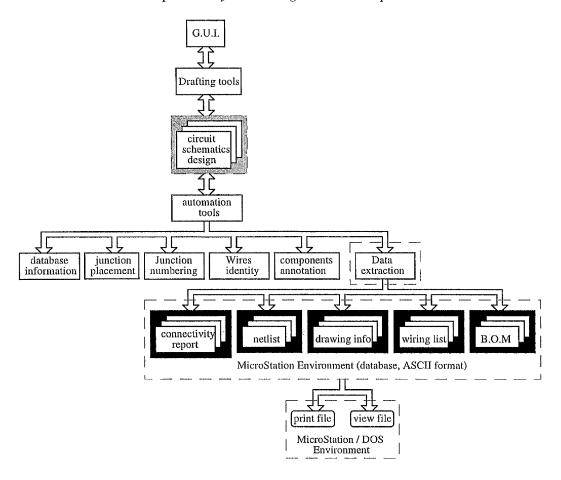

| 2.18    | Circuit automation tools and data extraction.             | 44 |

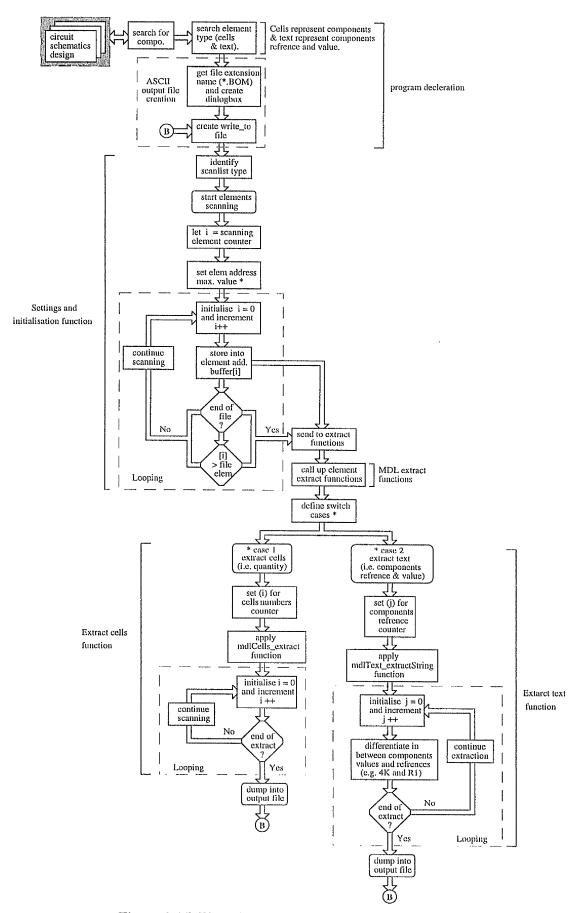

| 2.19    | Flowchart of circuit Bill Of Material extraction program. | 47 |

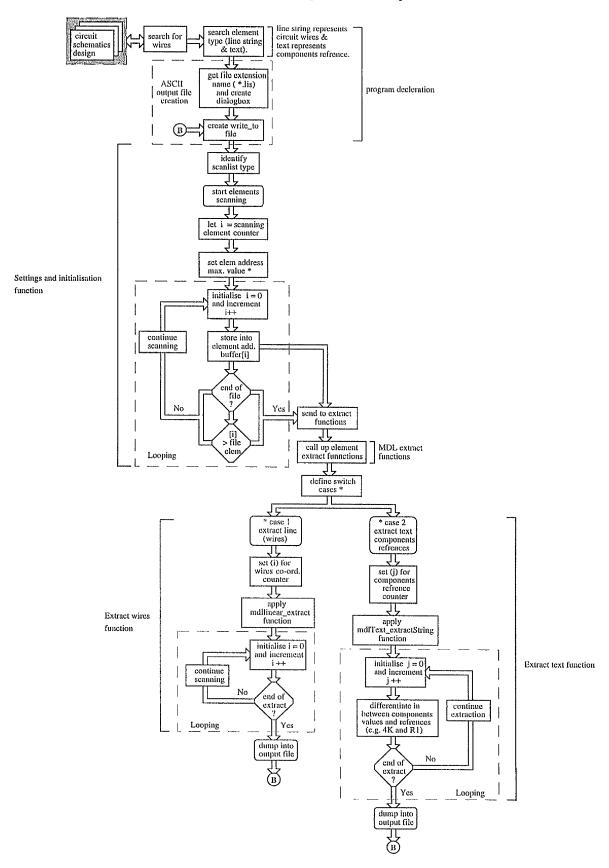

| 2.20    | Flowchart of wiring list extraction program.              | 49 |

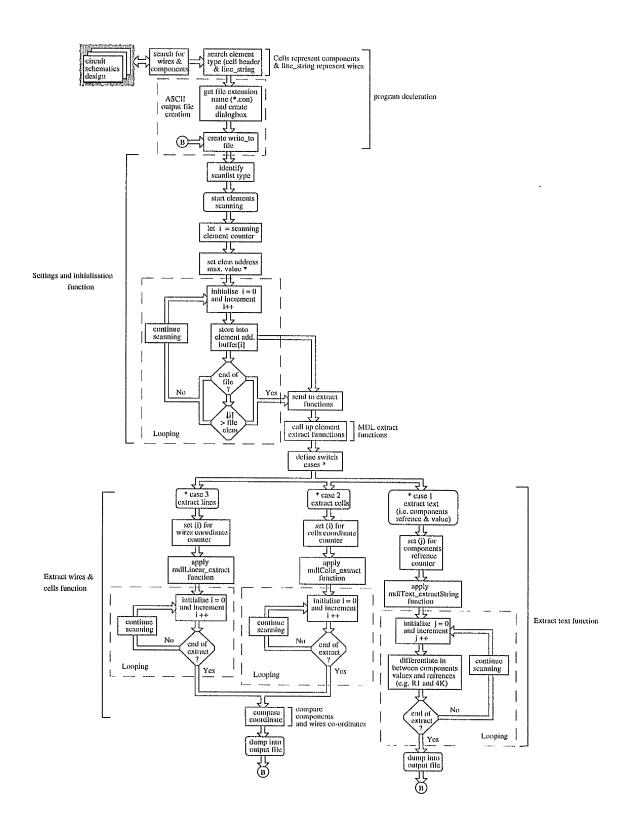

| 2.21a   | Flowchart of drawing information extraction program part (1).  | 50 |

|---------|----------------------------------------------------------------|----|

| 2.21b   | Flowchart of drawing information extraction program part (2).  | 51 |

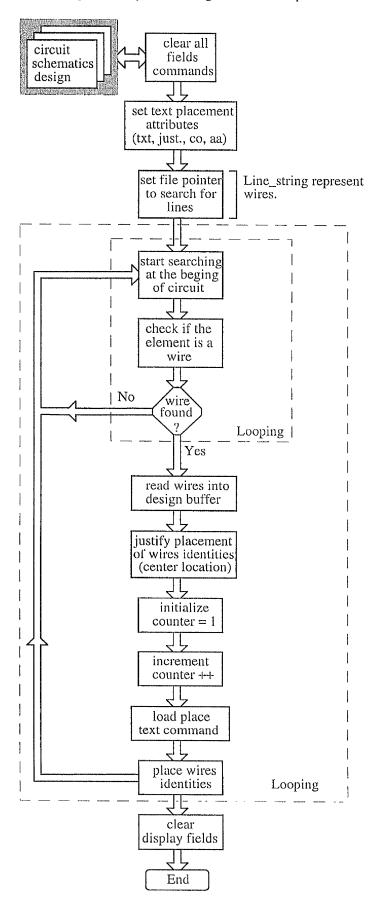

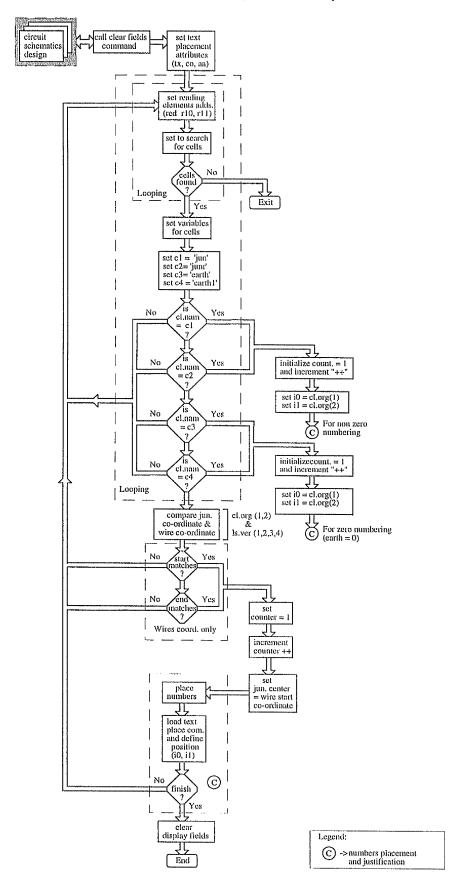

| 2.22    | Flowchart of automatic wires identity placement program.       | 53 |

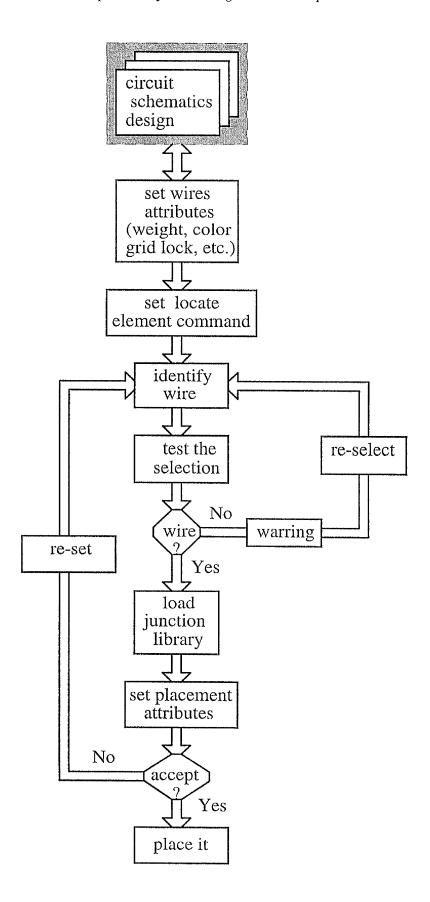

| 2.23    | Flowchart of automatic junction placement program.             | 54 |

| 2.24    | Flowchart of automatic junction numbering program.             | 55 |

| CHA     | PTER 3.                                                        |    |

| Section | on 3.2                                                         |    |

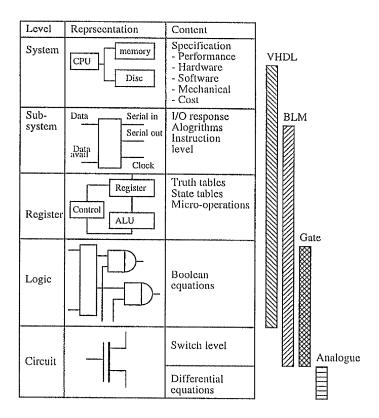

| 3.1     | The scope of VHDL compared to some other modelling techniques. | 62 |

| Section | on 3.3                                                         |    |

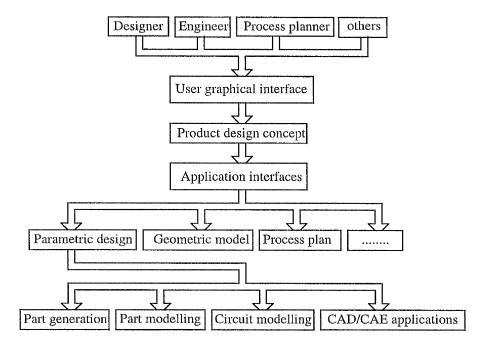

| 3.2     | Parametric design supports different applications.             | 65 |

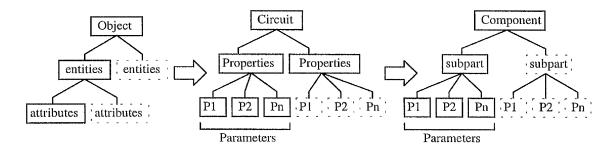

| 3.3     | Part-attributes relationship translation.                      | 67 |

| 3.4     | The concept of mechanical part-attributes definition.          | 67 |

| 3.5     | Inductor part-attributes description.                          | 68 |

| 3.6     | Transformer part-attributes description.                       | 69 |

| Section | on 3.4                                                         |    |

| 3.7     | Design and modelling general concept.                          | 70 |

| Section | on 3.5                                                         |    |

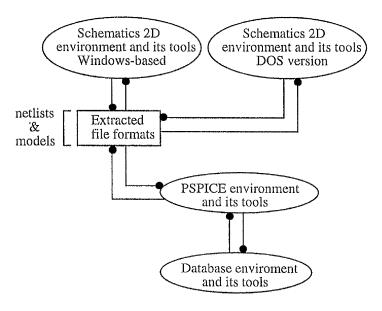

| 3.8     | Illustration of the integrated environments and their tools.   | 72 |

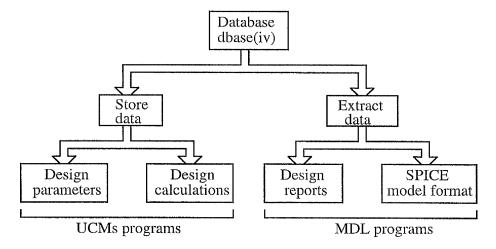

| 3.9     | Block diagram illustrates the use of database.                 | 73 |

| Section | on 3.6                                                         |    |

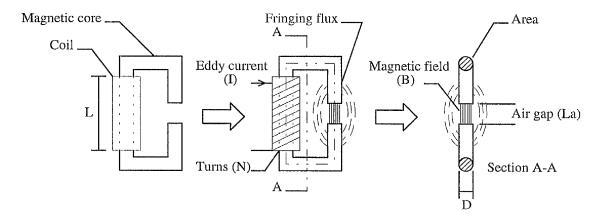

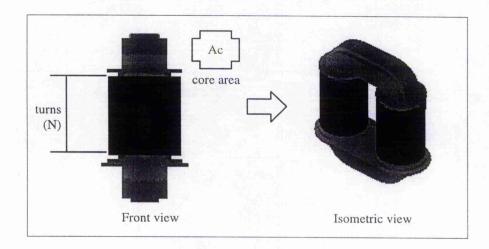

| 3.10    | Inductor detailed description.                                 | 74 |

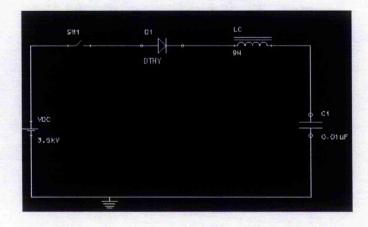

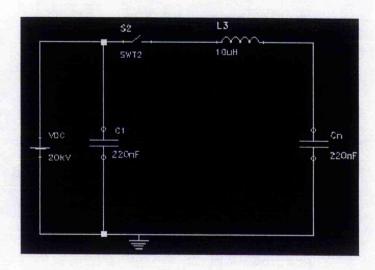

| 3.11    | Charging inductor design circuit.                              | 75 |

| 3.12    | The equivalent design model of $L_c$                           | 75 |

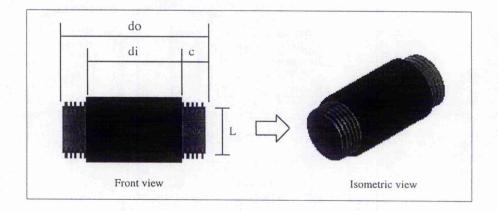

| 3.13    | Inductor with detailed dimensions.                             | 76 |

| 3.14    | Wave forms of charging current and voltage.                    | 79 |

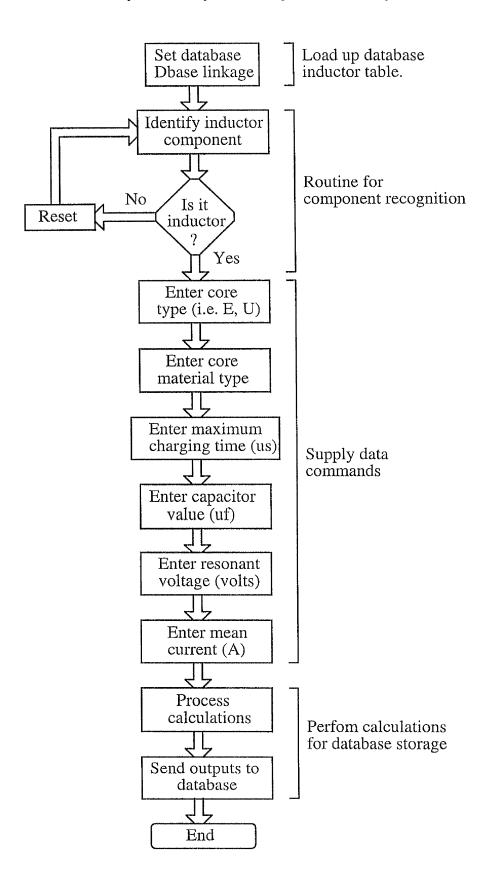

| 3.15    | Flowchart of inductor design program.                          | 81 |

| 3.16    | Inductor parameters calculations part.                         | 81 |

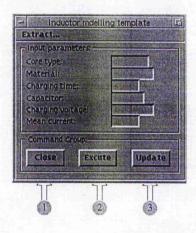

| 3.17    | Inductor design template.                                      | 83 |

| 3.18    | Database retrieved information using SQL.                      | 83 |

| 3.19    | The inductor extracted model.                                  | 83 |

| 3.20    | The usage of transformer.                                      | 84 |

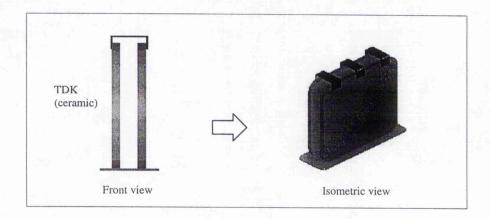

| 3.21    | Transformer detailed description.                              | 85 |

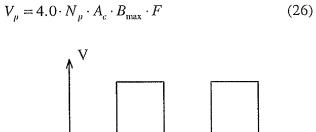

| 3.22    | Voltage square wave excitation.                                | 86 |

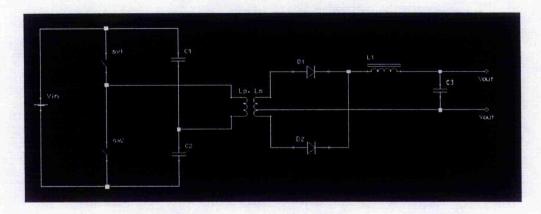

| 3.23    | Half bridge forward converter design circuit.                  | 87 |

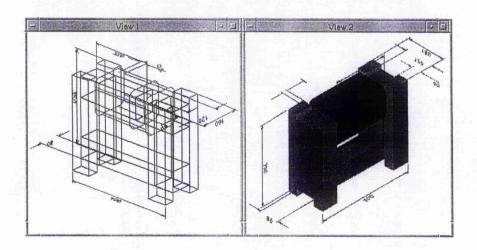

| 3.24    | Transformer with detailed dimensions.                          | 87 |

| Section | n 3.7                                                                    |     |

|---------|--------------------------------------------------------------------------|-----|

| 3.25    | Flowchart of transformer design program.                                 | 93  |

| 3.26    | Transformer parameters calculations part.                                | 94  |

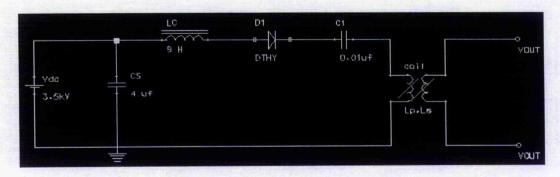

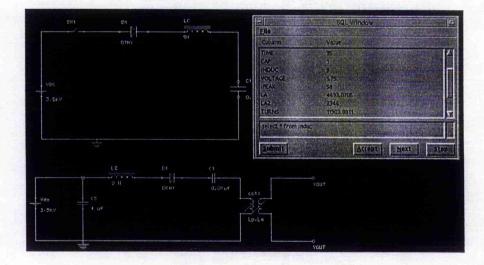

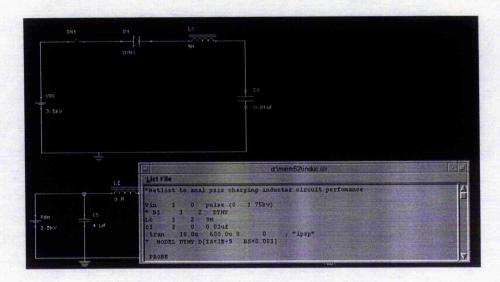

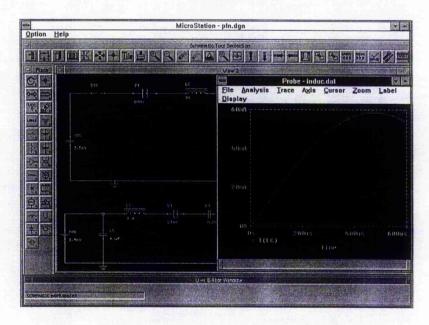

| 3.27    | Display of PFL circuit and PSPICE.                                       | 95  |

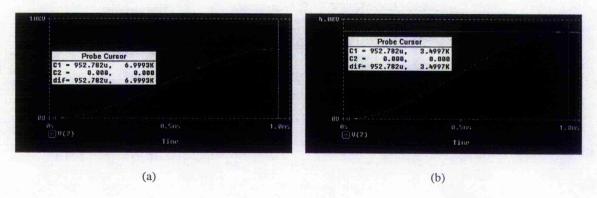

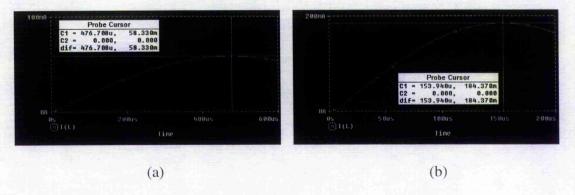

| 3.28a   | Transient analysis response of V(0) when $V_{DC}$ =3.5V.                 | 95  |

| 3.28b   | Transient analysis response of V(0) when $V_{DC}=1.75$ kV.               | 95  |

| 3.29a   | Peak current response when $L_c = 9H$ .                                  | 96  |

| 3.29b   | Peak current response when $L_c = 0.9$ H.                                | 96  |

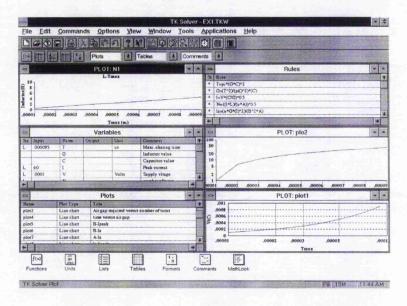

| 3.30    | A display of TK solver interface.                                        | 96  |

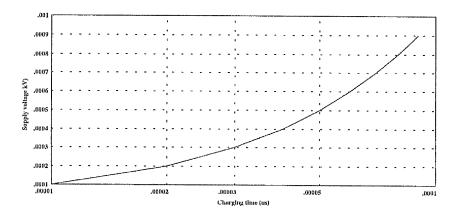

| 3.31    | Voltage versus maximum charging time.                                    | 97  |

| 3.32    | Peak current versus maximum charging time.                               | 97  |

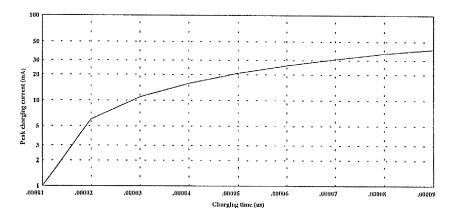

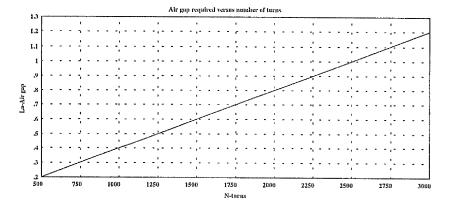

| 3.33    | Air gap required versus number of turns.                                 | 97  |

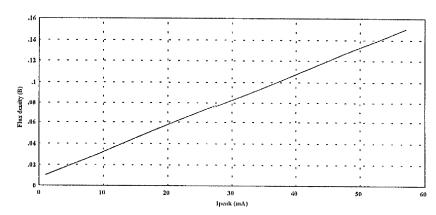

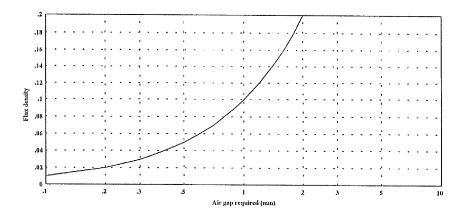

| 3.34    | Flux density versus peak current.                                        | 98  |

| 3.35    | Flux density versus air gap required.                                    | 98  |

| СНАР    | TER 4.                                                                   |     |

| Section |                                                                          |     |

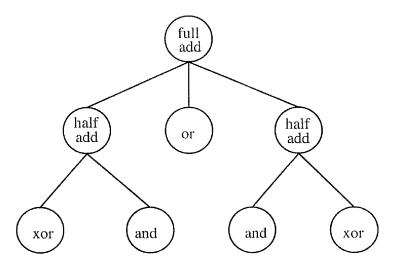

| 4.1     | Design tree of a full adder.                                             | 104 |

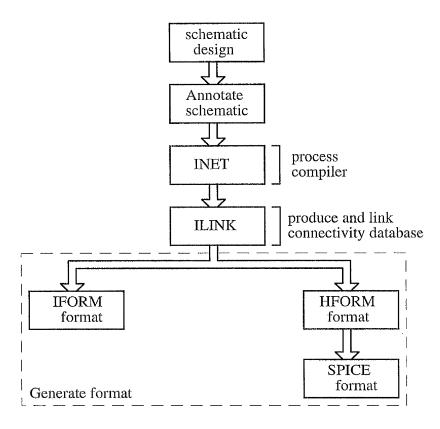

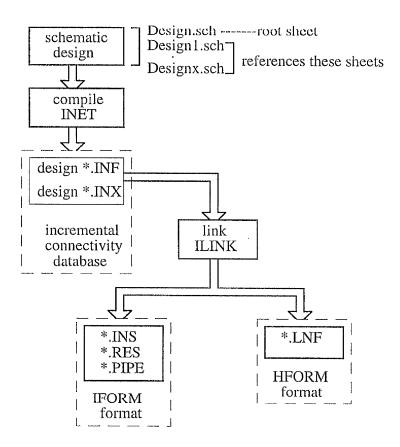

| 4.2     | 3-steps process of netlist creation using OrCAD system.                  | 105 |

| 4.3     | Files generated by both compiler and linker.                             | 106 |

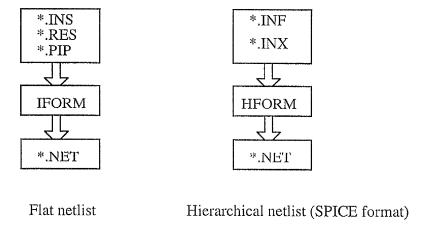

| 4.4     | Final stage of netlist format files (flat, hierarchical netlist).        | 106 |

| 4.5     | Creating a netlist in sabre system.                                      | 107 |

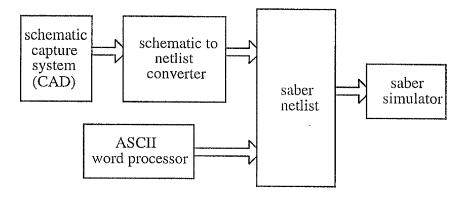

| 4.6     | Generic PSPICE input file format.                                        | 109 |

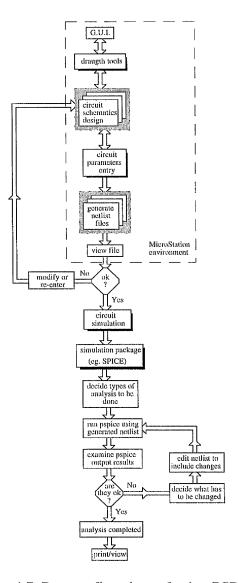

| 4.7     | Process flowchart of using PSPICE.                                       | 110 |

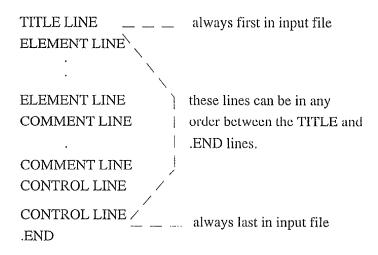

| 4.8     | The link between system environments and PSPICE.                         | 111 |

| Section | on 4.4                                                                   |     |

| 4.9     | Illustration of circuit connection possibilities for netlist generation. | 114 |

| 4.10    | A circuit as connected components.                                       | 114 |

| Section | on 4.5                                                                   |     |

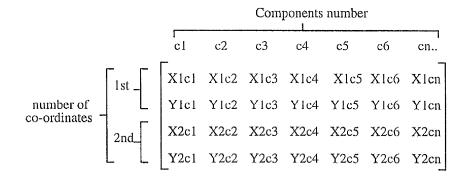

| 4.11    | Components matrix form of four co-ordinates.                             | 116 |

| 4.12    | Components matrix form of six co-ordinates.                              | 116 |

| 4.13    | Components matrix form of eight co-ordinates.                            | 117 |

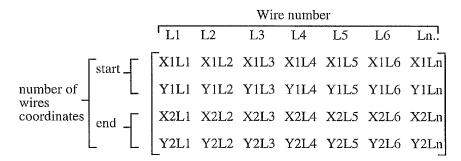

| 4.14    | Wires matrix form.                                                       | 117 |

| 4.15    | Matrices comparison (components versus wires).                           | 118 |

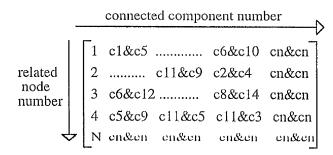

| 4.16    | Resultant node connection matrix.                                        | 118 |

| 4.17    | General procedure for data extraction.                                   | 119 |

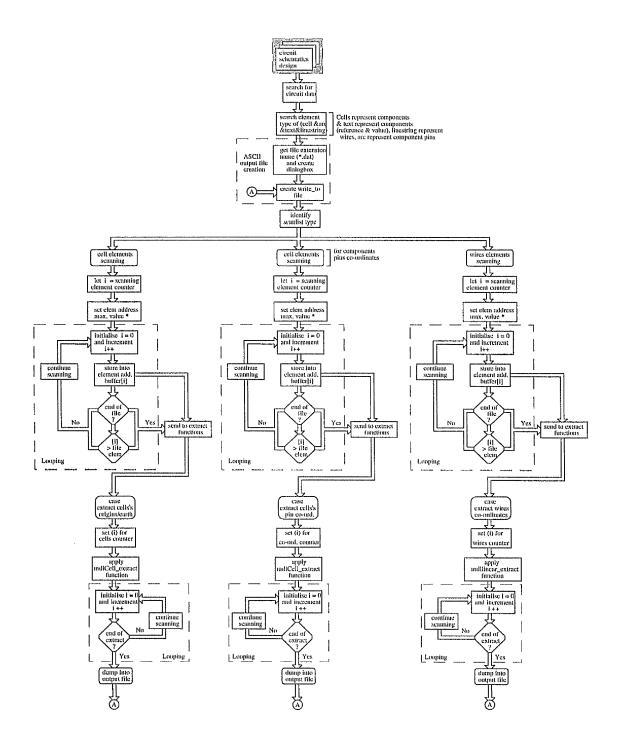

| 4.18    | Flowchart of circuit input data extraction program.                      | 120 |

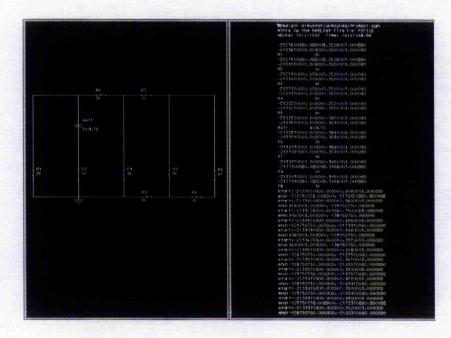

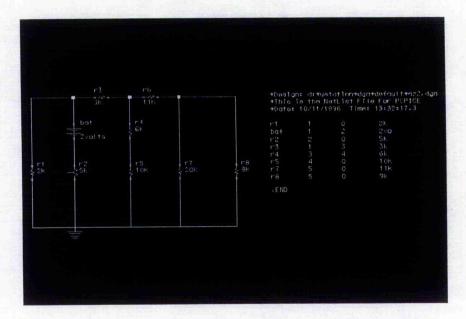

| 4.19    | A circuit and its extracted data.                                        | 121 |

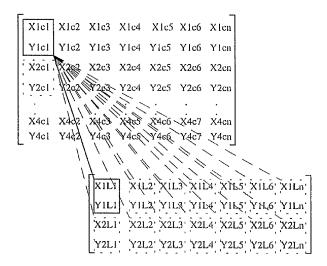

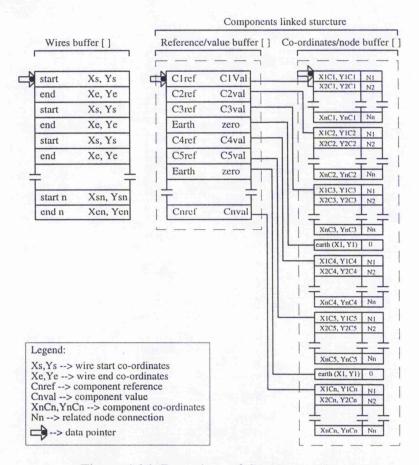

| 4.20    | Wires, components, and components co-ordinates/nodes matrices forms.     | 122   |

|---------|--------------------------------------------------------------------------|-------|

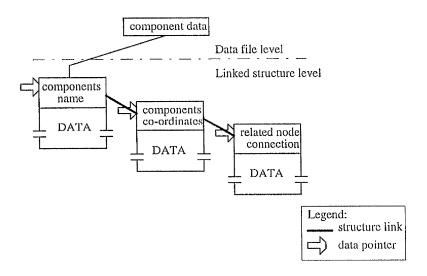

| 4.21    | Illustration of the basic structure of one way linked list.              | 123   |

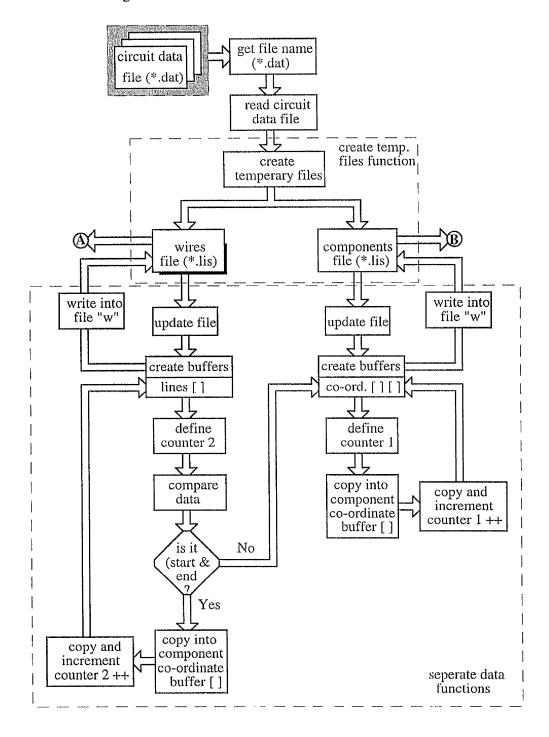

| 4.22    | Flowchart of read data file program.                                     | 124   |

| 4.23    | Flowchart of node determination program.                                 | 125   |

| 4.24    | Procedure of data processing.                                            | 126   |

| 4.25    | MDL debugger during data separation.                                     | 126   |

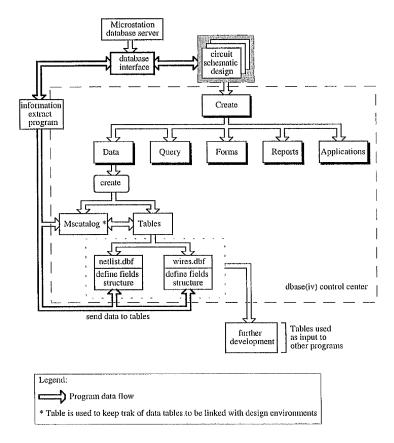

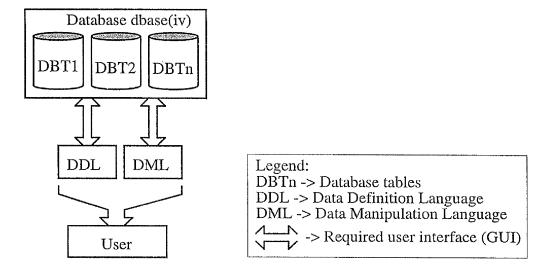

| 4.26    | The use of database dbase(iv).                                           | 127   |

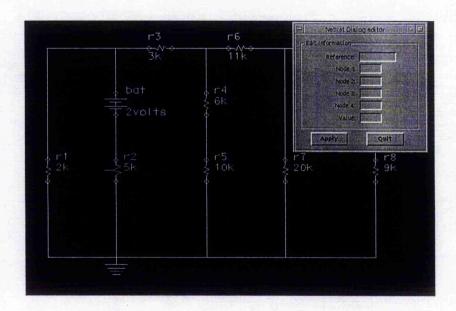

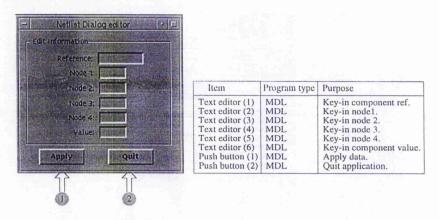

| 4.27    | User defined netlist using dialog editor.                                | 128   |

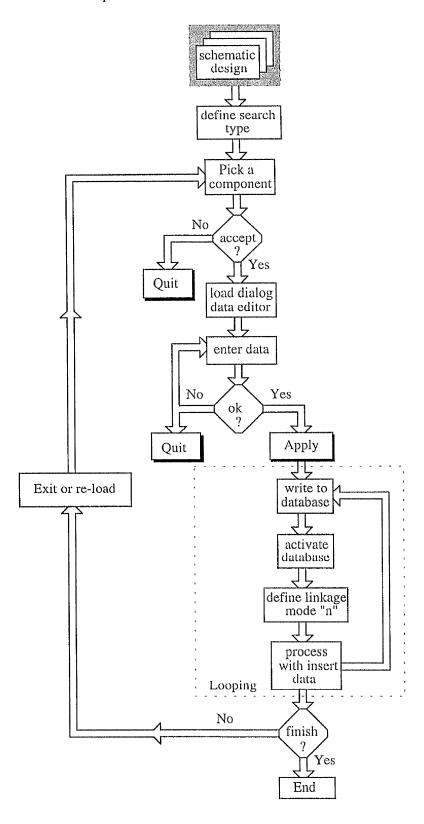

| 4.28    | Flowchart of dialog data editor program.                                 | 129   |

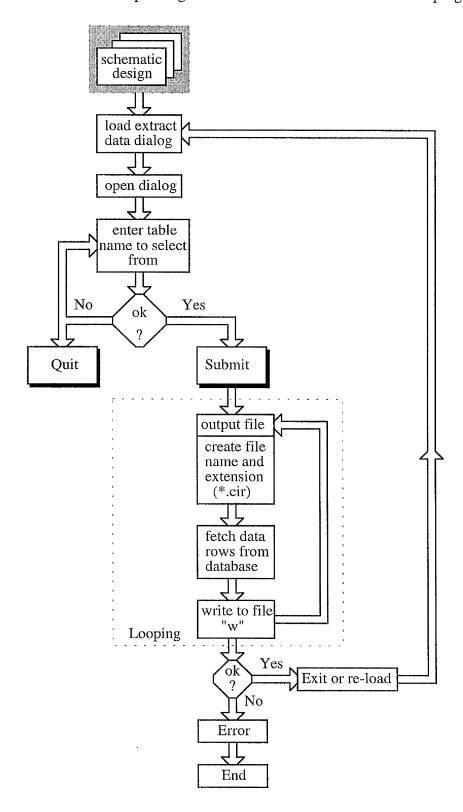

| 4.29    | Flowchart of netlist final format extraction.                            | 130   |

| 4.30    | Example of generating netlist using dialog editor.                       | 131   |

| 4.31    | Generated netlist file.                                                  | 132   |

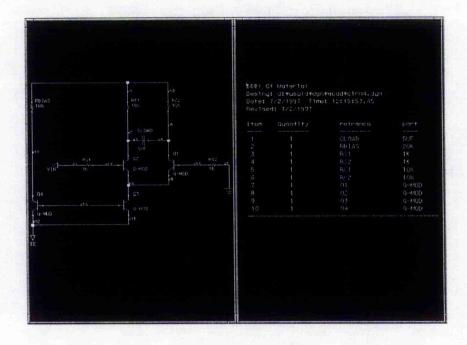

| 4.32    | Circuit Bill Of Material extraction.                                     | 132   |

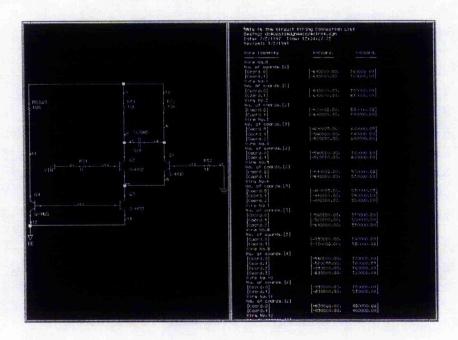

| 4.33    | Circuit wiring list extraction.                                          | 133   |

| 4.34    | Circuit drawing information extraction.                                  | 133   |

| 4.35    | Automatic nodes-wires identity placement.                                | 134   |

| CHAI    | PTER 5.                                                                  |       |

|         | on 5.1                                                                   |       |

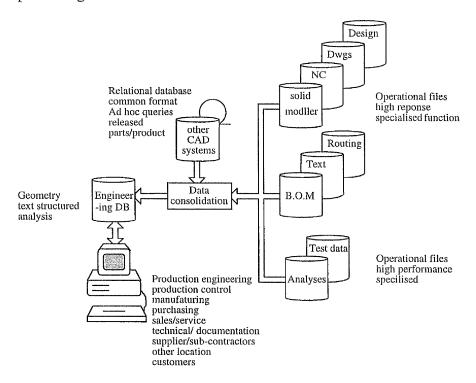

| 5.1     | Engineering database (towards integration-engineering database).         | 138   |

|         | on 5.5                                                                   | 1.40  |

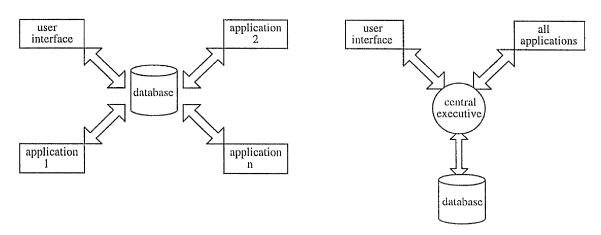

| 5.2     | Database-centred and executive systems.                                  | 142   |

| 5.3     | Database-centred and executive systems.                                  | 142   |

| Section | on 5.6                                                                   |       |

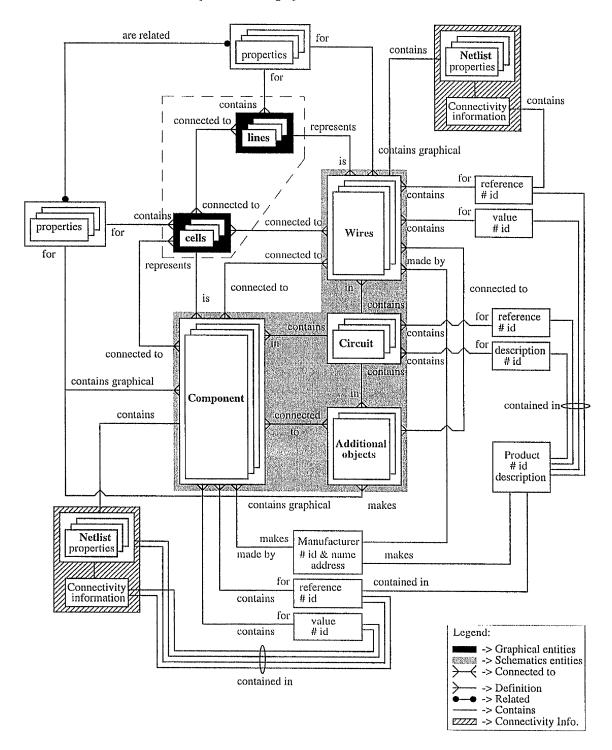

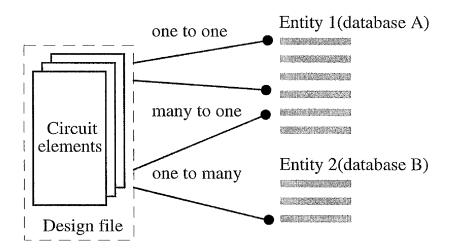

| 5.4     | Illustration of entities-relationship conceptual model.                  | 144   |

| 5.5     | Organisation of database.                                                | 146   |

|         | on 5.7                                                                   |       |

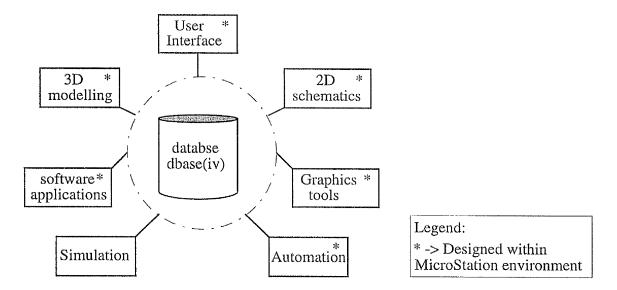

| 5.6     | Database dbase(iv) used for different design applications.               | 147   |

| 5.7     | Illustration of the link between MicroStation and dbase(iv) environment. | 148   |

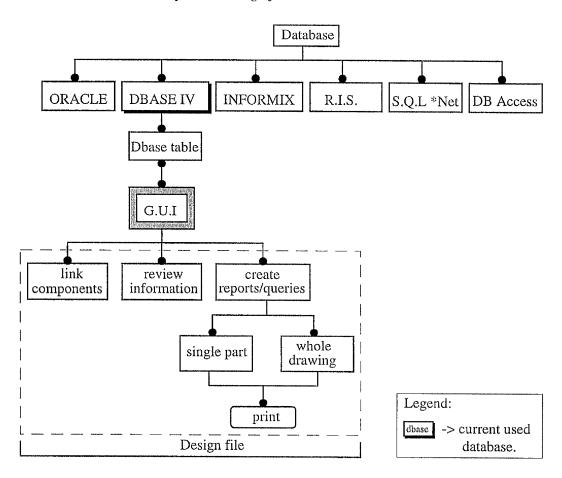

| 5.8     | Illustration of database tools design plan.                              | 149   |

| 5.9     | Applications design organisation.                                        | 151   |

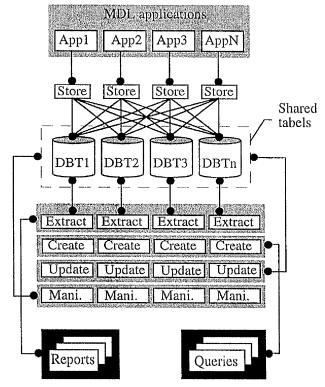

| 5.10    | Tables are shared between applications.                                  | 151   |

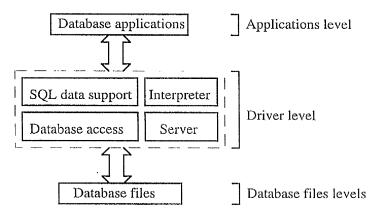

| 5.11    | General architecture of database communication link.                     | 152   |

| 5.12    | Element to record linkage.                                               | 153   |

| 5.13    | Flowchart of element recognition for data editing program.               | 154   |

|         | on 5.8  Illustration of data guery design.                               | 155   |

|         | THUSTIALION OF HALA HUCLY ACSIER.                                        | [.7.] |

| 5.15    | Flowchart of query extraction program.                       | 156 |

|---------|--------------------------------------------------------------|-----|

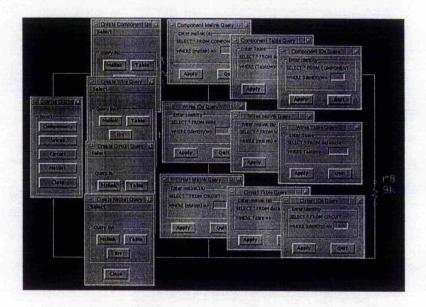

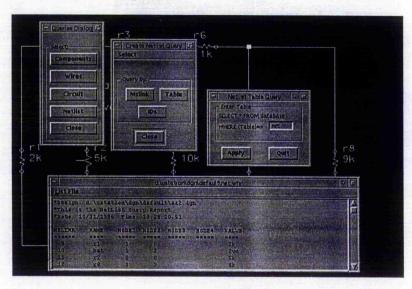

| 5.16    | Different user dialog boxes used for design data query.      | 157 |

| 5.17    | Demonstration of components-netlist queries.                 | 157 |

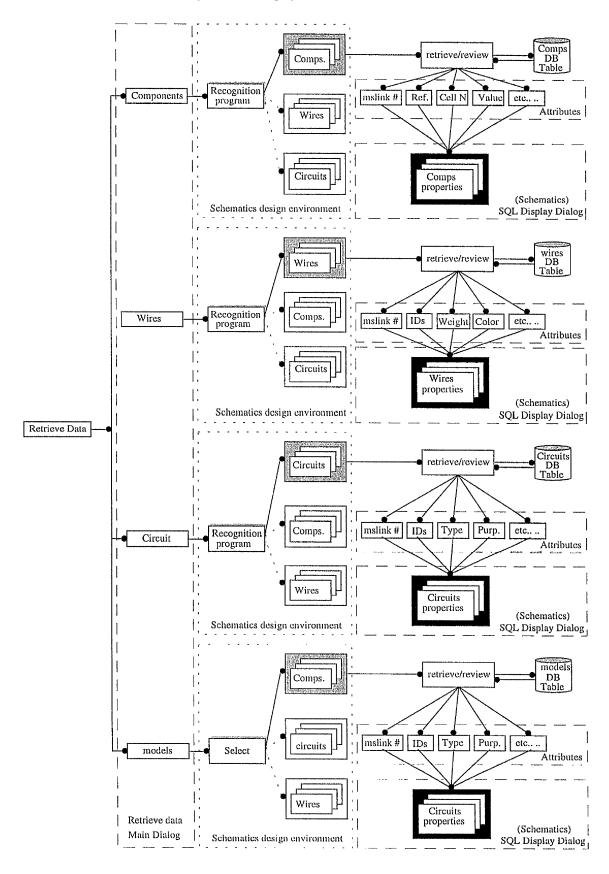

| 5.18    | Illustration of data retrieval design.                       | 158 |

| 5.19    | Flowchart of element recognition for data retrieval program. | 159 |

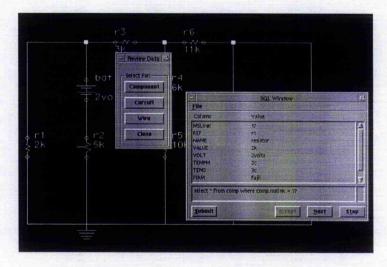

| 5.20    | Demonstration of design data retrieval.                      | 160 |

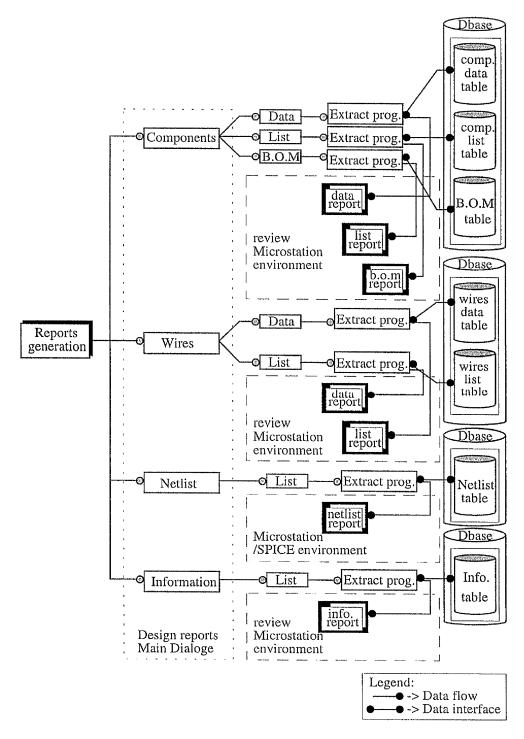

| 5.21    | Illustration of reports generation design.                   | 161 |

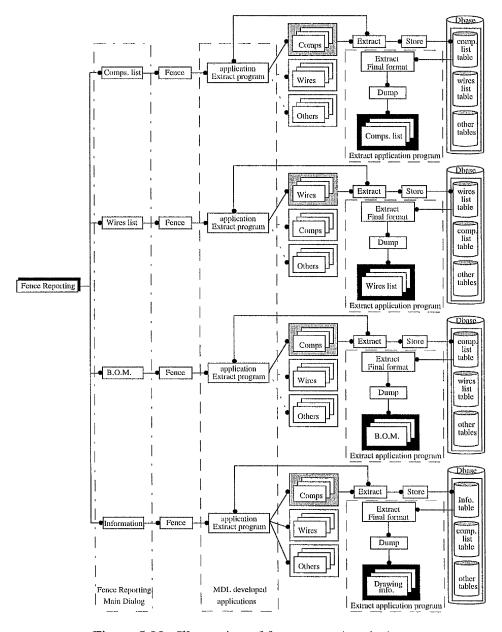

| 5.22    | Illustration of fence reporting design.                      | 162 |

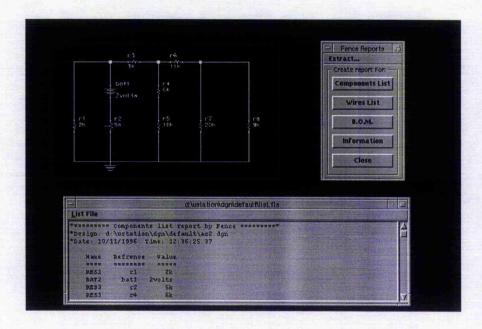

| 5.23    | Dialog boxes used for fence report generation.               | 163 |

| Section | on 5.9                                                       |     |

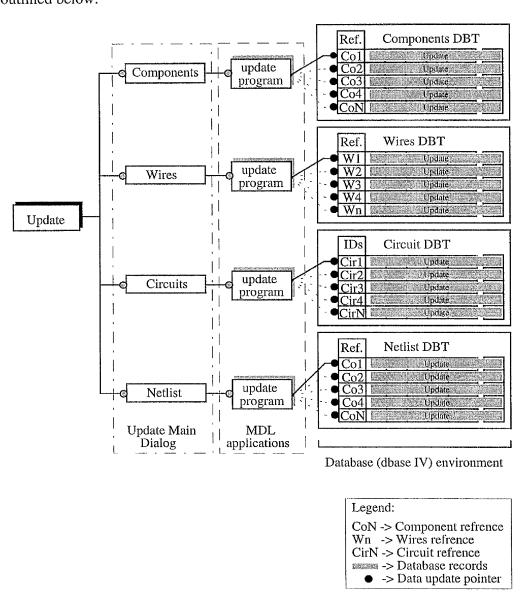

| 5.24    | Illustration of data update design.                          | 164 |

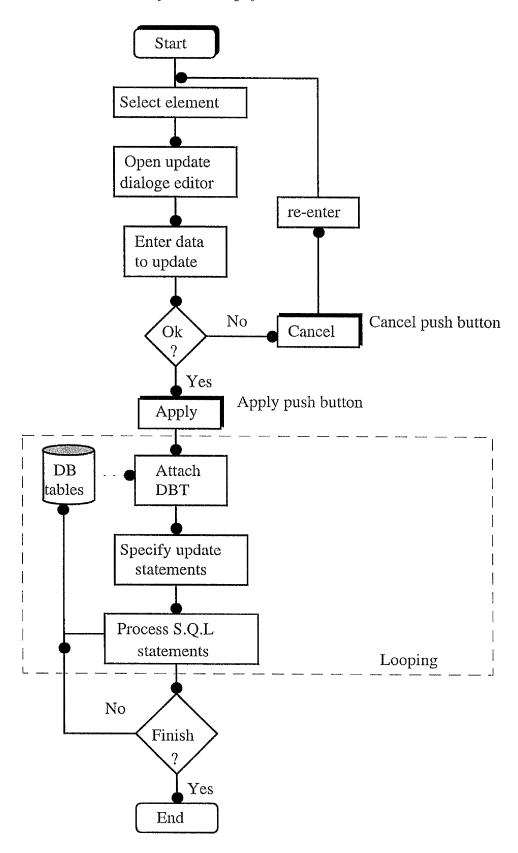

| 5.25    | Flowchart of data update program.                            | 165 |

| 5.26    | Demonstration of design data update.                         | 166 |

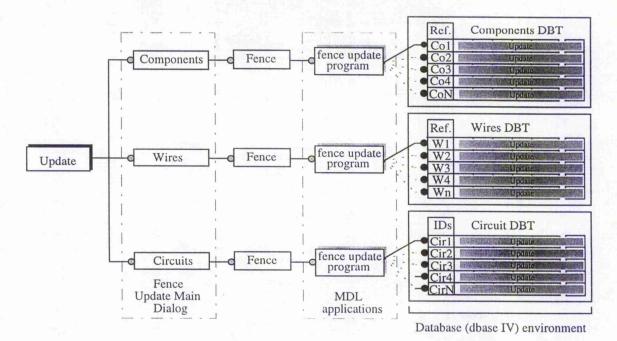

| 5.27    | Illustration of fence updating design.                       | 166 |

| 5.28    | Demonstration of fence update design.                        | 167 |

| Secti   | on 5.10                                                      |     |

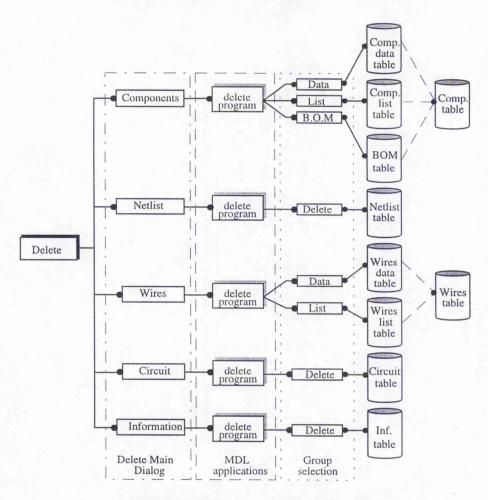

| 5.29    | Illustration of delete data design.                          | 168 |

| 5.30    | Dialog for data deletion.                                    | 168 |

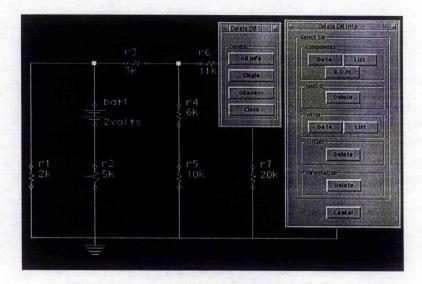

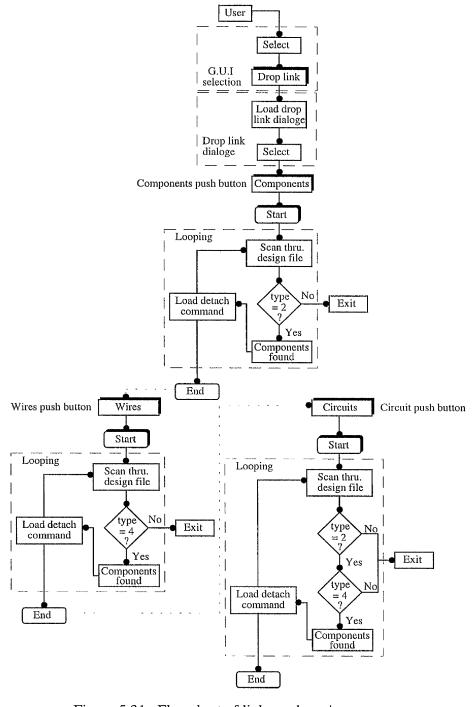

| 5.31    | Flowchart of linkage dropping program.                       | 169 |

| СНА     | PTER 6.                                                      |     |

| Secti   | on 6.6                                                       |     |

| 6.1     | Illustration of graphics design general concept.             | 178 |

| Secti   | on 6.7                                                       |     |

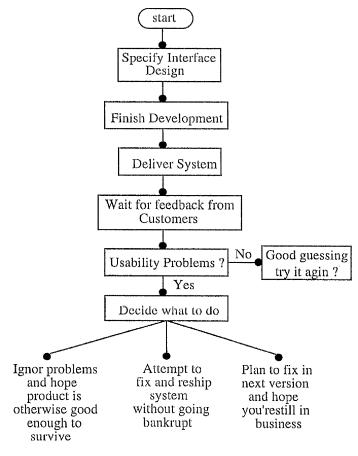

| 6.2     | Common industrial development process flowchart.             | 179 |

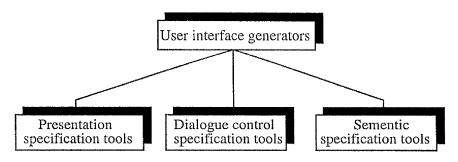

| 6.3     | Different types of user interface generators.                | 180 |

| 6.4     | Illustration of GUI design levels.                           | 182 |

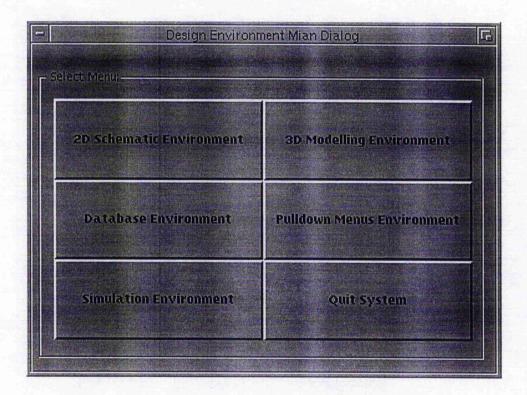

| 6.5     | User interface main dialog.                                  | 183 |

| 6.6     | 2D schematics interface main dialog.                         | 183 |

| Secti   | on 6.8                                                       |     |

| 6.7     | Display of schematics workspace environment.                 | 185 |

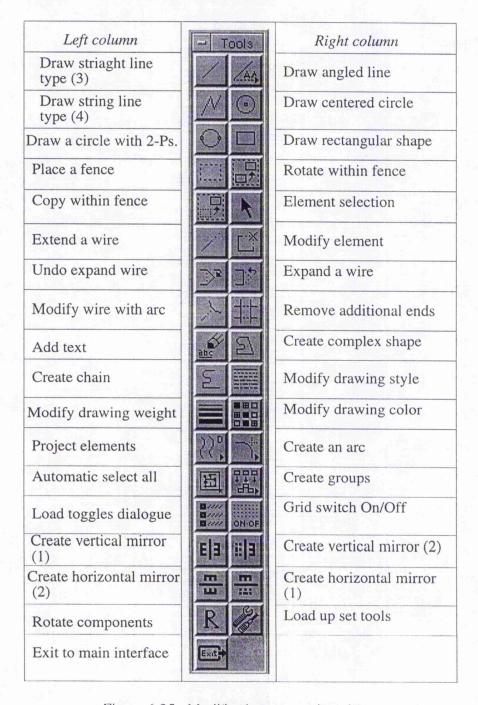

| 6.8a    | Schematics design tools part (1).                            | 187 |

| 6.8b    | Schematic design tools part (2).                             | 188 |

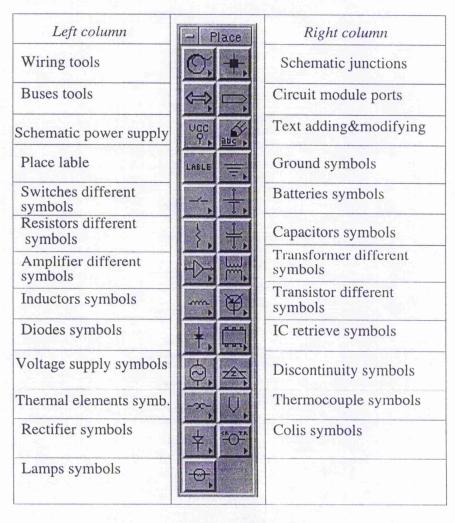

| 6.9     | Place main palette.                                          | 189 |

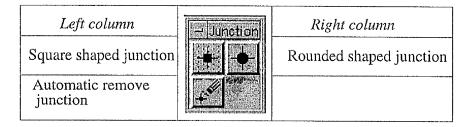

| 6.10    | Schematic junctions sub-palette.                             | 190 |

| 6.11    | Place wires sub-palette.                                     | 190 |

| 6.12  | Bus symbols sub-palette.                      | 190 |

|-------|-----------------------------------------------|-----|

| 6.13  | Ground symbols sub-palette.                   | 190 |

| 6.14  | Power supply symbols sub-palette.             | 190 |

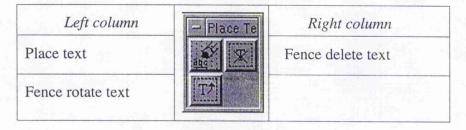

| 6.15  | Schematic place text sub-palette.             | 191 |

| 6.16  | Module ports symbols sub-palette.             | 191 |

| 6.17  | Amplifiers symbols sub-palette.               | 191 |

| 6.18  | Batteries symbols sub-palette.                | 191 |

| 6.19  | Transformers symbols sub-palette.             | 191 |

| 6.20  | Capacitors symbols sub-palette.               | 192 |

| 6.21  | Diodes symbols sub-palette.                   | 192 |

| 6.22  | Inductors symbols sub-palette.                | 192 |

| 6.23  | Resistors symbols sub-palette.                | 192 |

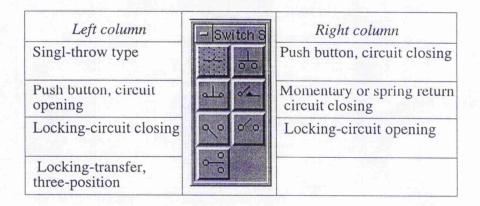

| 6.24  | Switches symbols sub-palette.                 | 193 |

| 6.25  | Voltage supply symbols sub-palette.           | 193 |

| 6.26  | Transistors symbols sub-palette.              | 193 |

| 6.27  | IC symbols sub-palette.                       | 193 |

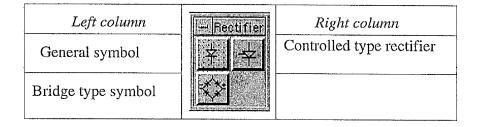

| 6.28  | Rectifiers symbols sub-palette.               | 194 |

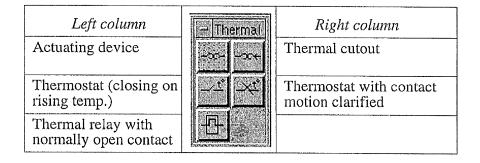

| 6.29  | Thermal elements symbols sub-palette.         | 194 |

| 6.30  | Thermocouple symbols sub-palette.             | 194 |

| 6.31  | Lamps and visual devices symbols sub-palette. | 194 |

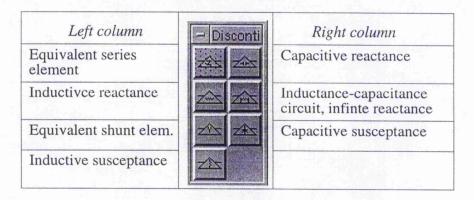

| 6.32  | Discontinuity symbols sub-palette.            | 195 |

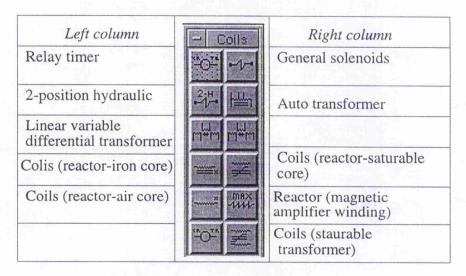

| 6.33  | Coils symbols sub-palette.                    | 195 |

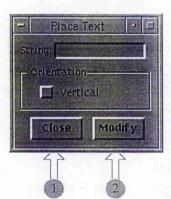

| 6.34  | Place text dialog.                            | 195 |

| 6.35  | Modify elements main palette.                 | 196 |

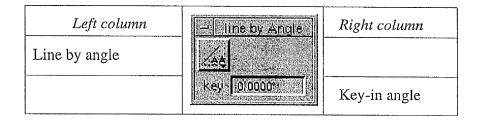

| 6.36  | Angled line sub-palette.                      | 197 |

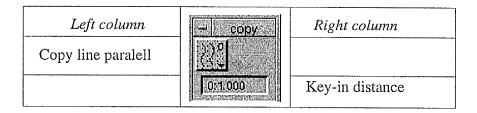

| 6.37  | Copy line parallel sub-palette.               | 197 |

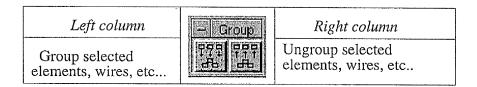

| 6.38  | Group-ungroup elements sub-palette.           | 197 |

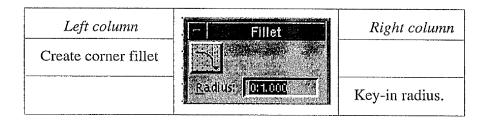

| 6.39  | Place fillet sub-palette.                     | 197 |

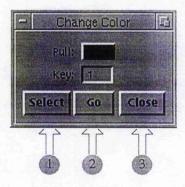

| 6.40  | Change colour dialog.                         | 198 |

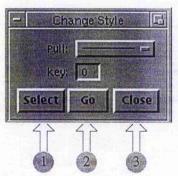

| 6.41  | Change style dialog.                          | 198 |

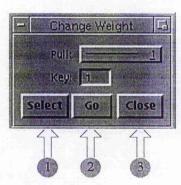

| 6.42  | Change weight dialog.                         | 198 |

| 6.43  | Workspace top main palette.                   | 199 |

| 6.44  | Netlist-wire sub-palette.                     | 199 |

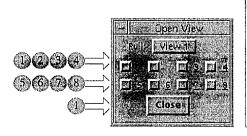

| 6.45  | Open view main dialog.                        | 200 |

| 6.46  | 3D modelling main palette.                    | 200 |

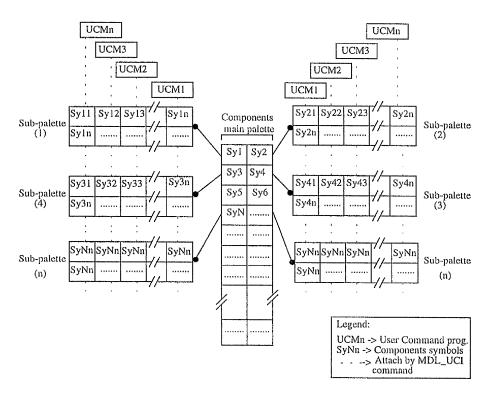

| 6.47  | Components UCMs program attachment.           | 201 |

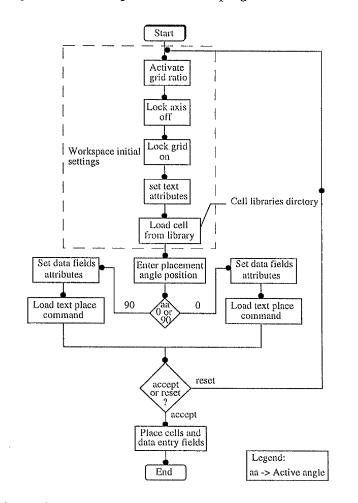

| 6.48  | Flowchart of component placement program.     | 201 |

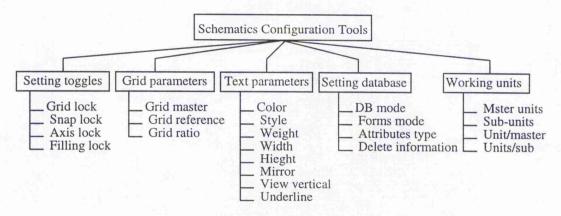

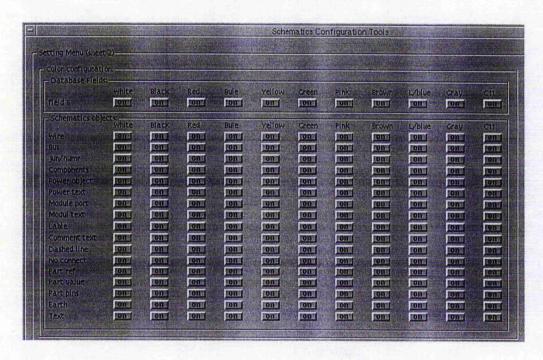

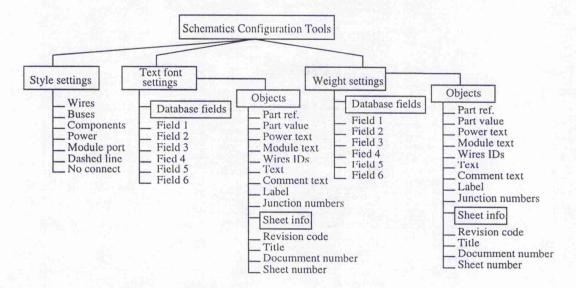

| 6.49a | Configuration tools hierarchy part (1).       | 203 |

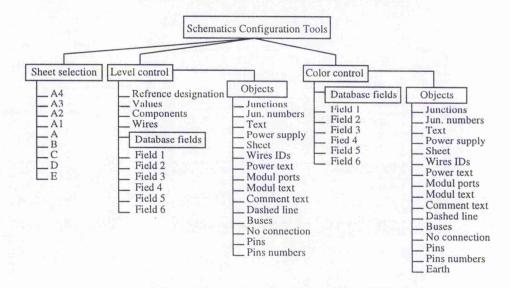

| 6.49b | Configuration tools hierarchy part (2).       | 203 |

| 6.49c | Configuration tools hierarchy part (3).       | 204 |

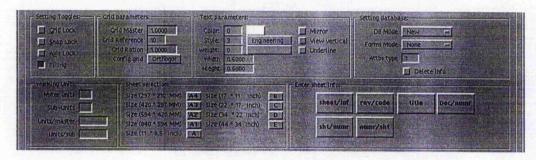

| 6.50    | Settings tools dialog of sheet (1).              | 203 |

|---------|--------------------------------------------------|-----|

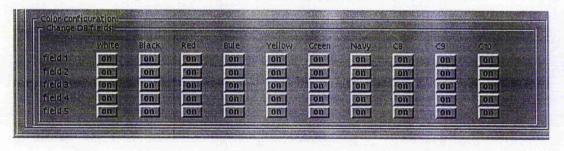

| 6.51    | Automatic colours configuration dialog part (1). | 203 |

| 6.52    | Automatic colours configuration dialog part (2). | 204 |

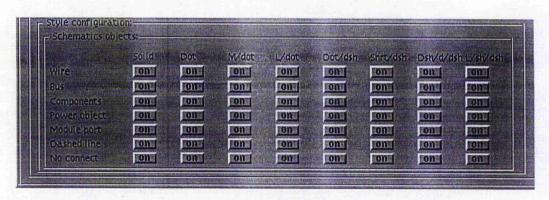

| 6.53    | Automatic style configuration dialog.            | 204 |

| 6.54    | Automatic font-weight configuration dialog.      | 205 |

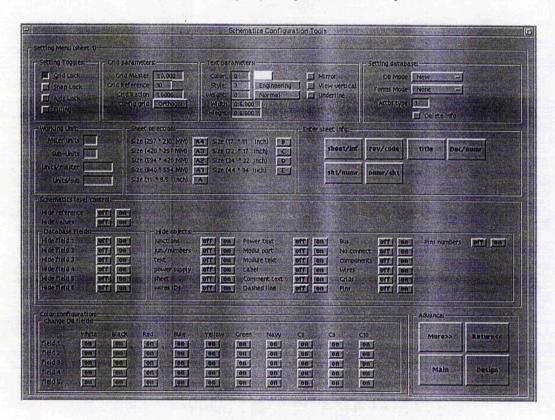

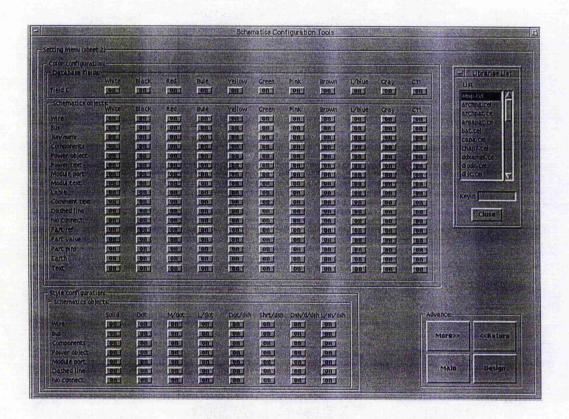

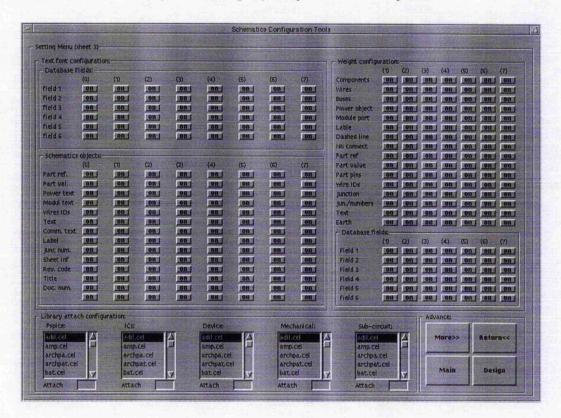

| 6.55    | Schematics configuration tools sheet (1).        | 206 |

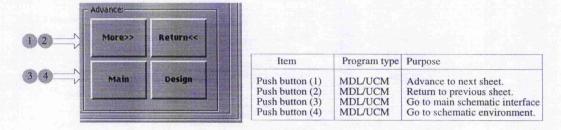

| 6.56    | Sheet advance group.                             | 205 |

| 6.57    | Schematics configuration tools sheet (2).        | 206 |

| 6.58    | Schematics configuration tools sheet (3).        | 207 |

| 6.59    | Toggle settings dialog.                          | 207 |

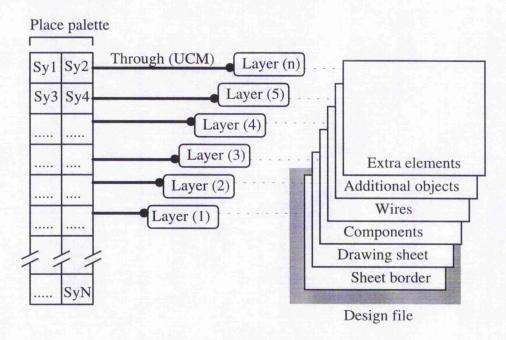

| 6.60    | The concept of design by levels.                 | 208 |

| 6.61    | Schematics levels control dialog.                | 208 |

| Section | on 6.9                                           |     |

| 6.62    | ASCII reports dialog.                            | 209 |

| Section | on 6.10                                          |     |

| 6.63    | Pull-down menus tools design hierarchy.          | 211 |

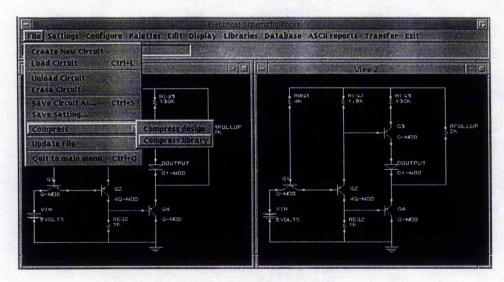

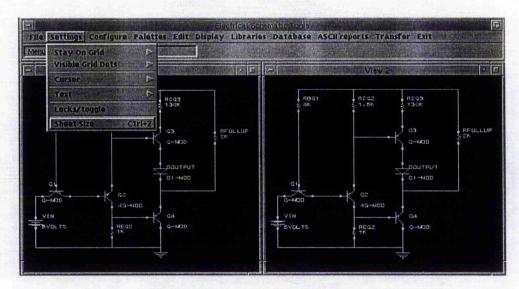

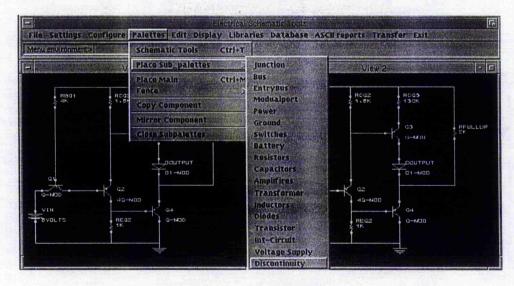

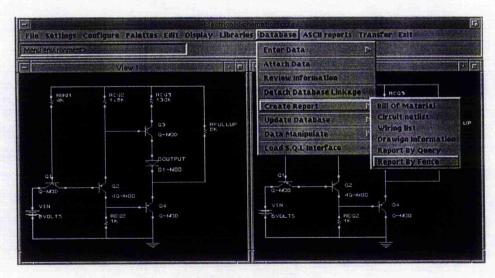

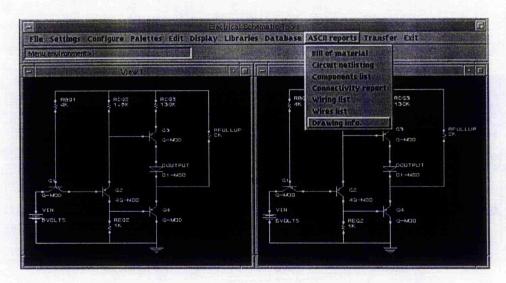

| 6.64    | Pull-down menus environment.                     | 211 |

| 6.65    | File tools submenus.                             | 212 |

| 6.66    | Settings tools submenus.                         | 212 |

| 6.67    | Palettes submenus.                               | 212 |

| 6.68    | Database submenus.                               | 213 |

| 6.69    | ASCII reports submenus.                          | 213 |

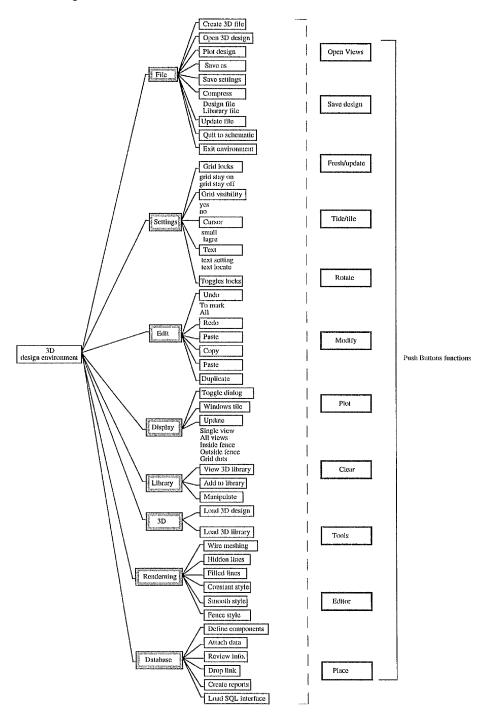

| 6.70    | 3D environment design hierarchy.                 | 214 |

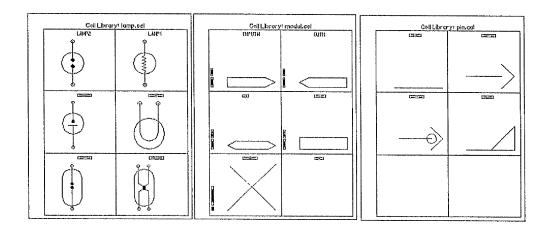

| Section | on 6.11                                          |     |

| 6.71    | The 3D modelling environment.                    | 215 |

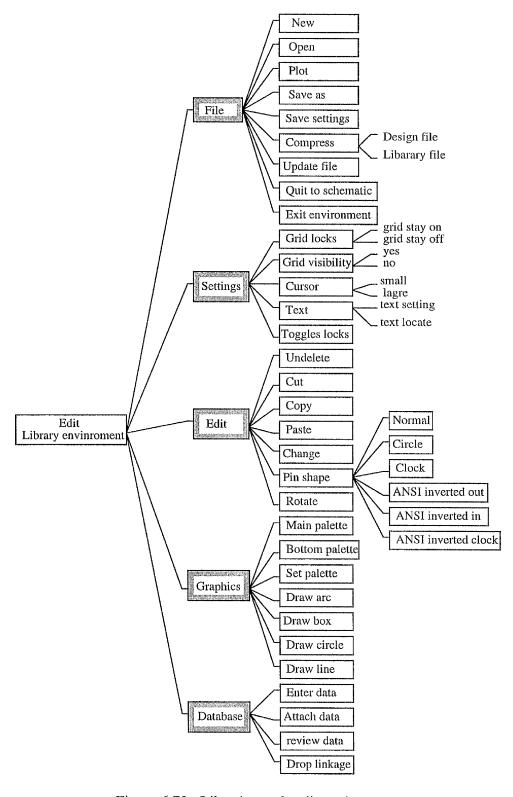

| 6.72    | Libraries tools edit environment.                | 216 |

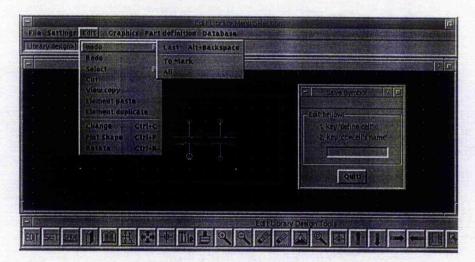

| 6.73    | Library design tools (Edit submenus).            | 217 |

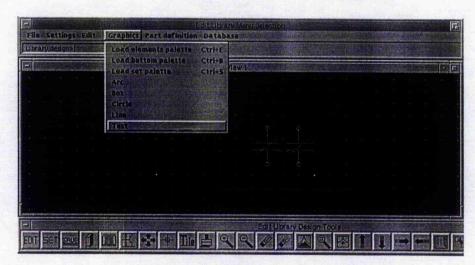

| 6.74    | Library design tools (graphics submenus).        | 217 |

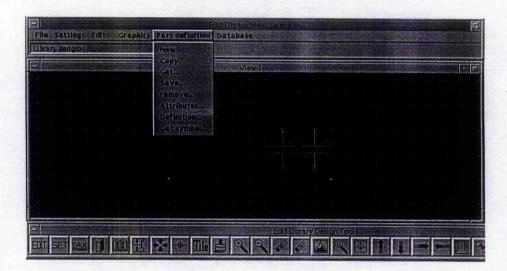

| 6.75    | Library design tools (part definition submenus). | 217 |

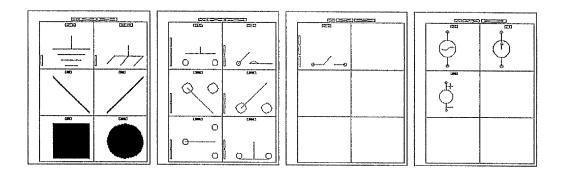

| 6.76    | Components libraries classification.             | 218 |

| 6.77    | An example of transformer symbol design.         | 218 |

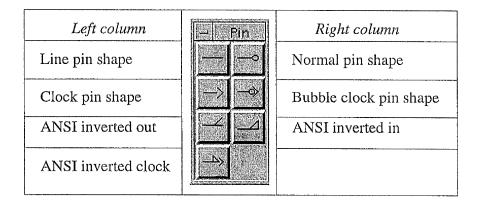

| 6.78    | Palette of components different pins.            | 219 |

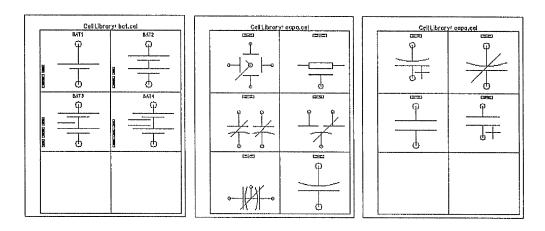

| 6.79    | Batteries-capacitors symbols.                    | 219 |

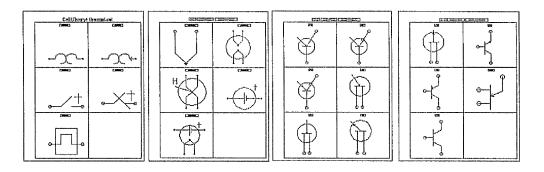

| 6.80    | Thermal elements-transistors symbols.            | 219 |

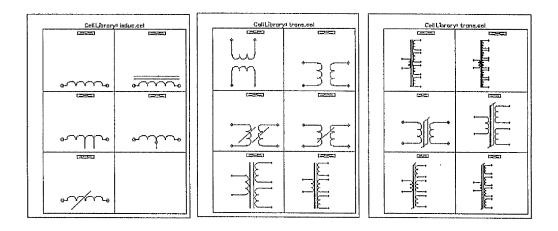

| 6.81    | Inductors-transformers symbols.                  | 220 |

| 6.82    | Schematic objects-switches symbols.              | 220 |

| 6.83    | Module ports-pins symbols.                       | 220 |

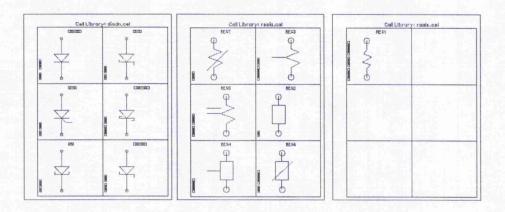

| 6.84    | Diodes-resistors symbols.                        | 221 |

| Sectio | n 6.12                                                         |     |

|--------|----------------------------------------------------------------|-----|

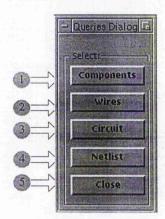

| 6.85   | Database tools dialog.                                         | 221 |

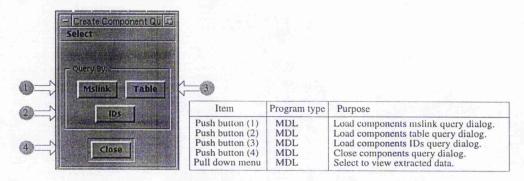

| 6.86   | Database query main dialog.                                    | 222 |

| 6.87   | Components query main dialog.                                  | 222 |

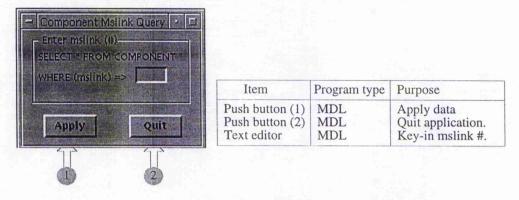

| 6.88   | Components mslink query dialog.                                | 222 |

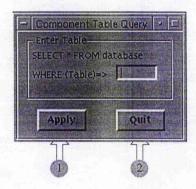

| 6.89   | Components table query dialog.                                 | 223 |

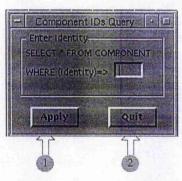

| 6.90   | Components IDs query dialog.                                   | 223 |

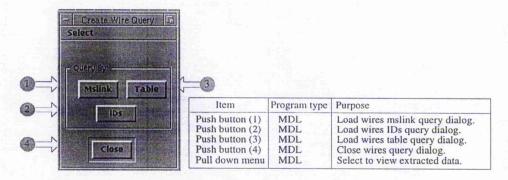

| 6.91   | Wires query main dialog.                                       | 223 |

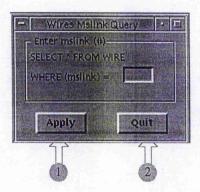

| 6.92   | Wires mslink query dialog.                                     | 223 |

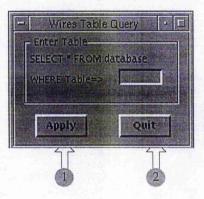

| 6.93   | Wires table query dialog.                                      | 224 |

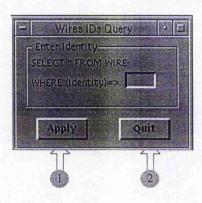

| 6.94   | Wires IDs query dialog.                                        | 224 |

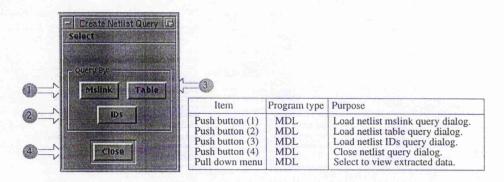

| 6.95   | Netlist query main dialog.                                     | 224 |

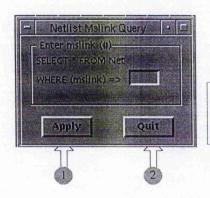

| 6.96   | Netlist mslink query dialog.                                   | 224 |

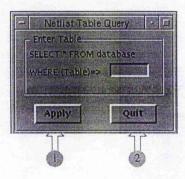

| 6.97   | Netlist tables query dialog.                                   | 224 |

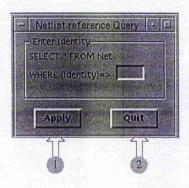

| 6.98   | Netlist reference query dialog.                                | 225 |

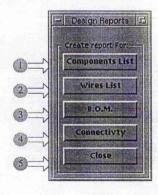

| 6.99   | Reports creation main dialog.                                  | 225 |

| 6.100  | Data retrieval main dialog.                                    | 225 |

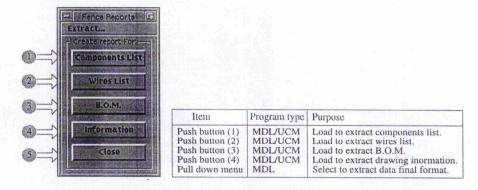

| 6.101  | Fence report generation dialog.                                | 226 |

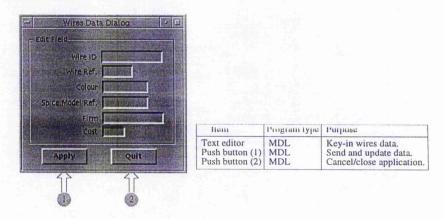

| 6.102  | Wires data editing dialog.                                     | 226 |

| 6.103  | Netlist editor dialog.                                         | 226 |

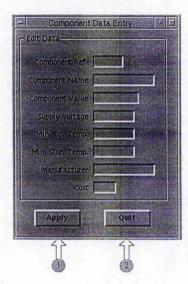

| 6.104  | Components data editing dialog.                                | 227 |

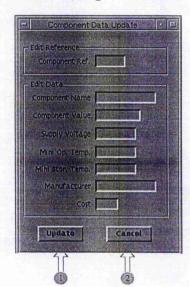

| 6.105  | Components data update dialog.                                 | 227 |

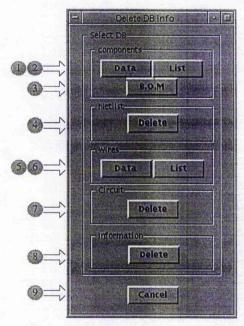

| 6.106  | Clear database records main dialog.                            | 227 |

| 6.107  | Clear database main dialog.                                    | 228 |

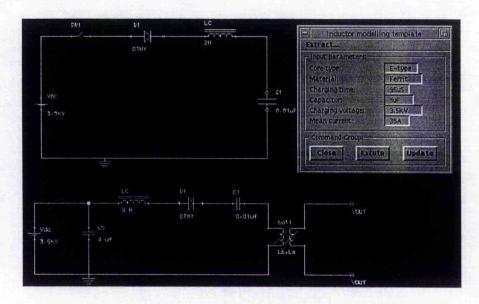

| 6.108  | Inductor modelling template.                                   | 228 |

| 6.109  | Transformer modelling template.                                | 228 |

| СНАН   | TER 7.                                                         |     |

|        | on 7.3                                                         |     |

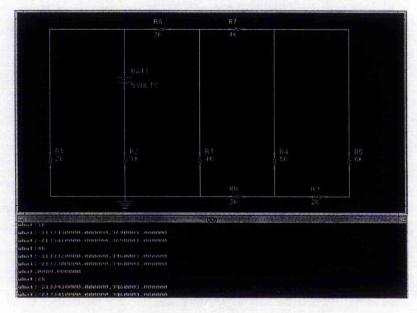

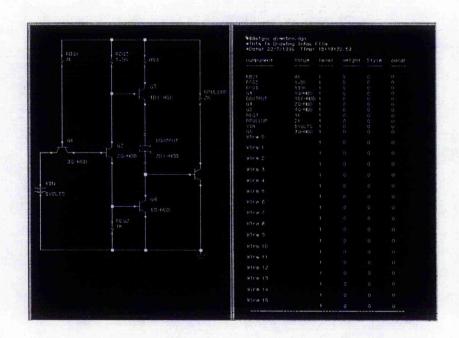

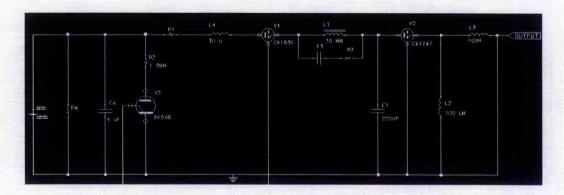

| 7.1    | Resonant charging circuit drawing on 2D schematic environment. | 223 |

| 7.2    | 2D schematic different views.                                  | 234 |

| 7.3    | The 2D schematic of charging circuit.                          | 234 |

|        | on 7.4                                                         |     |

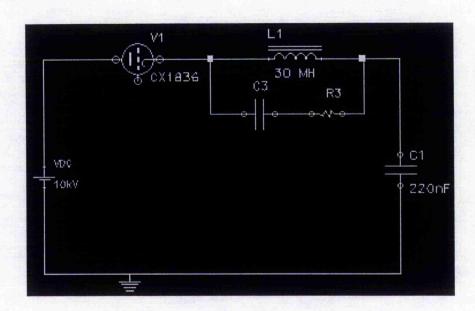

| 7.4    | Schematic design of the first stage.                           | 235 |

| 7.5    | The equivalent design model of L1.                             | 235 |

| 7.6    | Netlist file generated for the first stage.                    | 239 |

| 7.7    | A display of the 2D schematic environment and PSPICE.          | 239 |

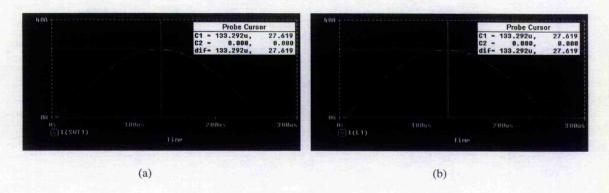

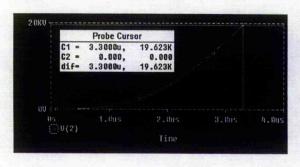

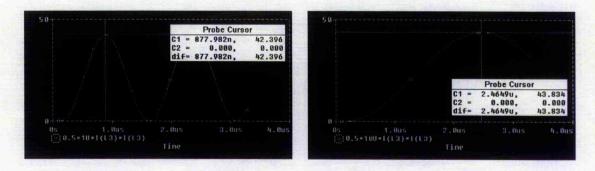

| 7.8a   | Peak current $I$ through swt1.                                 | 240 |

| 7.8b   | Peak current I through L1.                                     | 240 |

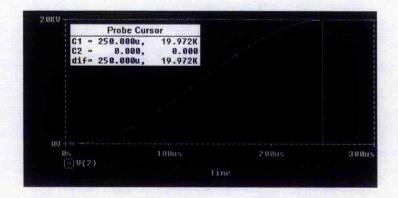

| 7.9     | Output voltage $V(0)$ through inductor L1.                      | 240 |

|---------|-----------------------------------------------------------------|-----|

| 7.10    | Energy stored in L1.                                            | 241 |

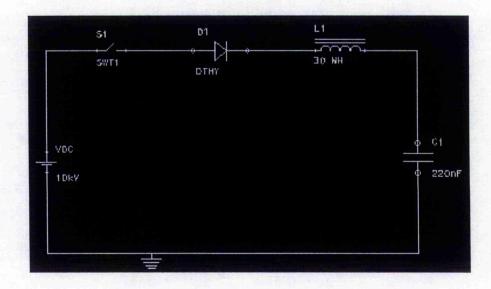

| 7.11    | Schematic design of the second stage.                           | 241 |

| 7.12    | The equivalent design model of L3.                              | 242 |

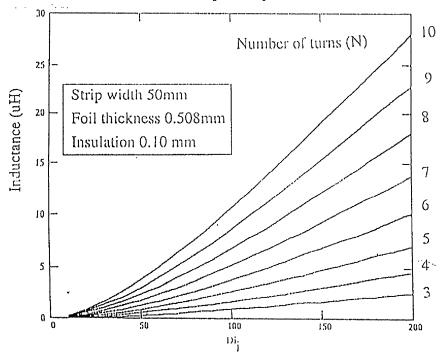

| 7.13    | Graph of inductance versus former diameter and number of turns. | 244 |

| 7.14    | Netlist generated for the second stage.                         | 244 |

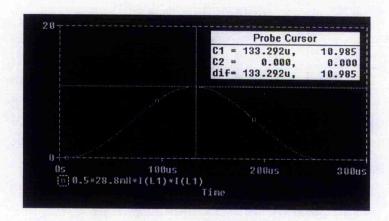

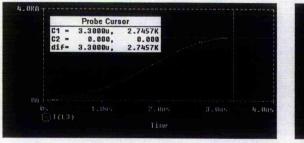

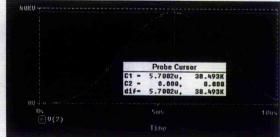

| 7.15    | Peak current $\hat{I}$ when L3=10 $\mu$ H.                      | 245 |

| 7.16    | Output voltage V(0) when L3=10μH.                               | 245 |

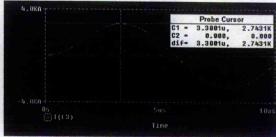

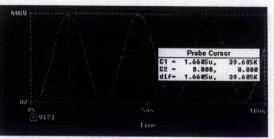

| 7.17    | Peak current $\hat{I}$ when L3=1 $\mu$ H.                       | 245 |

| 7.18    | Output voltage V(0) when L3=1µH.                                | 245 |

| 7.19    | Energy stored in L3 when L3=10μH and 1μH.                       | 246 |

| Section | on 7.5                                                          |     |

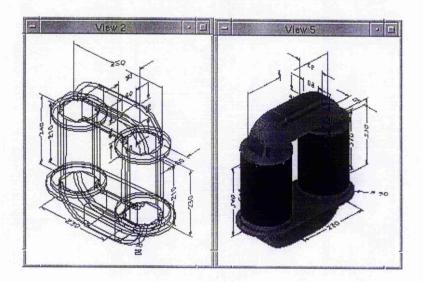

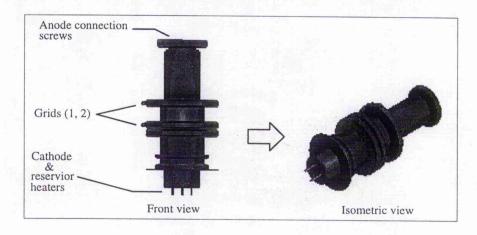

| 7.20    | Inductor L1 design.                                             | 247 |

| 7.21    | Spiral inductors (L1, L3) design.                               | 247 |

| 7.22    | Capacitor (C1) design.                                          | 248 |

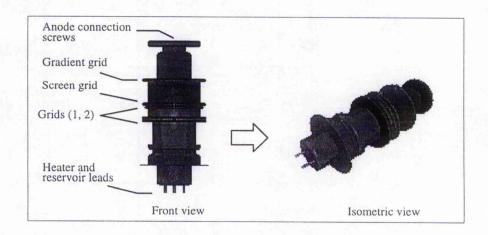

| 7.23    | Thyratron CX1836 design.                                        | 248 |

| 7.24    | Thyratron CX1747 design.                                        | 249 |

| 7.25    | 3D model components stored as libraries cells.                  | 249 |

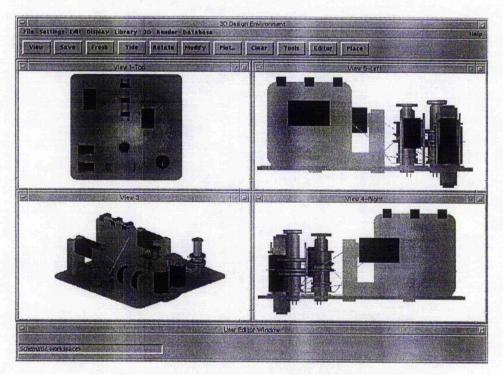

| 7.26    | 3D different views representation.                              | 250 |

| 7.27    | Isometric representation of the 3D model.                       | 250 |

| Secti   | on 7.6                                                          |     |

| 7.28    | Illustration of environments integration.                       | 254 |

| 7.29    | The interface between 2D and 3D using common database.          | 255 |

| 7.30    | Dialog editor and L1 extracted model.                           | 256 |

| 7.31    | Components data editing and data retrieval.                     | 257 |

| 7.32    | Components data updating.                                       | 258 |

| 7.33    | Display of inductor database storage.                           | 258 |

| 7.34    | Display of first stage netlist stored in database.              | 259 |

| Secti   | on 7.7                                                          |     |

| 7.35    | Display of graphics configuration tools for (2D and 3D).        | 259 |

| 7.36    | Display of settings and levels control tools.                   | 260 |

| Secti   | on 7.8                                                          |     |

| 3.37    | Display of Documents generation tools.                          | 260 |

| 7.38    | Circuit B.O.M. and wiring list extraction.                      | 260 |

# List of Tables

| СНА   | PTER 1.                                                                   |     |

|-------|---------------------------------------------------------------------------|-----|

| Secti | ion 1.2                                                                   |     |

| 1.1   | Product design and its techniques.                                        | 3   |

| Secti | ion 1.3                                                                   |     |

| 1.2   | List of ECAD systems and tools integration approaches.                    | 6   |

| Secti | ion 1.6                                                                   |     |

| 1.3   | List of existing programs for circuit simulation.                         | 13  |

| СНА   | PTER 2.                                                                   |     |

| Secti | ion 2.5                                                                   |     |

| 2.1   | Connectivity testing utilities and its development functions.             | 48  |

| 2.2   | Bill Of Material utilities and its development functions.                 | 48  |

| 2.3   | Wiring list utilities and its development functions.                      | 52  |

| 2.4   | Drawing information utilities and its development functions.              | 52  |

| СНА   | PTER 3.                                                                   |     |

| Secti | ion 3.6                                                                   |     |

| 3.1   | Circuit design specification.                                             | 75  |

| 3.2   | Component output parameters.                                              | 78  |

| 3.3   | The database structure for inductor design.                               | 82  |

| 3.4   | Transformer input data.                                                   | 87  |

| 3.5   | Transformer output data.                                                  | 92  |

| СНА   | PTER 4.                                                                   |     |

| Secti | ion 4.5                                                                   |     |

| 4.1   | Summary of utilities, functions and their operations.                     | 121 |

| 4.2   | Summary of database extraction utilities, functions and their operations. | 131 |

| СНА   | PTER 5.                                                                   |     |

| Secti | ion 5.3                                                                   |     |

| 5.1   | Database comparison.                                                      | 140 |

### List of Tables

| Sect | ion 5.6                                                   |     |

|------|-----------------------------------------------------------|-----|

| 5.2  | A summary of SQL statements.                              | 146 |

| СНА  | APTER 6.                                                  |     |

| Sect | ion 6.9                                                   |     |

| 6.1  | Workspace initial settings commands and their operations. | 202 |

| 6.2  | Schematics level assignment.                              | 209 |

| Sect | ion 6.10                                                  |     |

| 6.3  | Commands and their functions keys.                        | 213 |

| CHA  | APTER 7.                                                  |     |

| Sect | ion 7.3                                                   |     |

| 7.1  | Circuit general parameters.                               | 232 |

| Sect | ion 7.4                                                   |     |

| 7.2  | First stage input parameters.                             | 238 |

| 7.3  | Second stage input parameters.                            | 242 |

| 7.4  | Second stage design parameters.                           | 243 |

| List | of photographs                                            |     |

| СНА  | APTER 7.                                                  |     |

| Sect | ion 7.5                                                   |     |

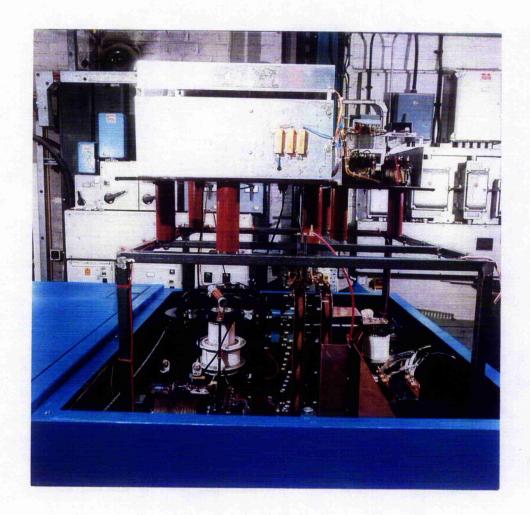

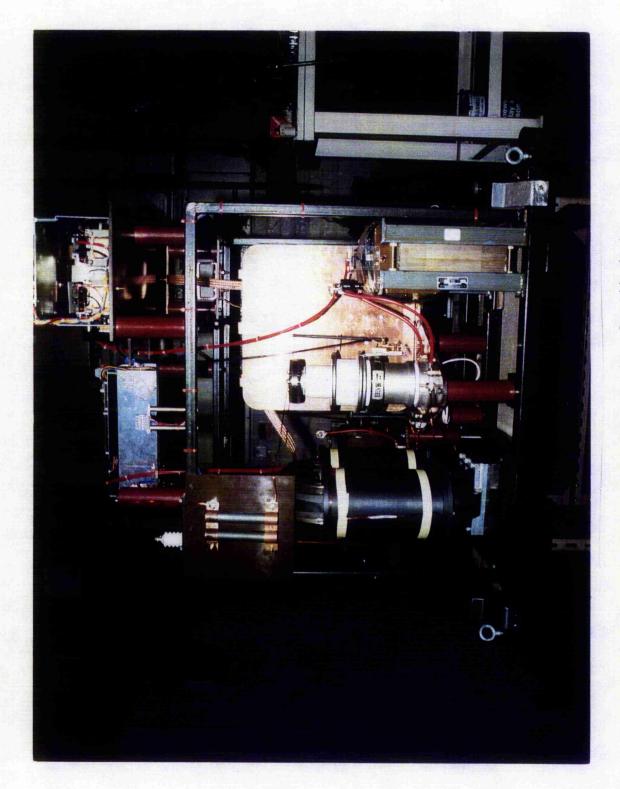

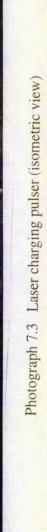

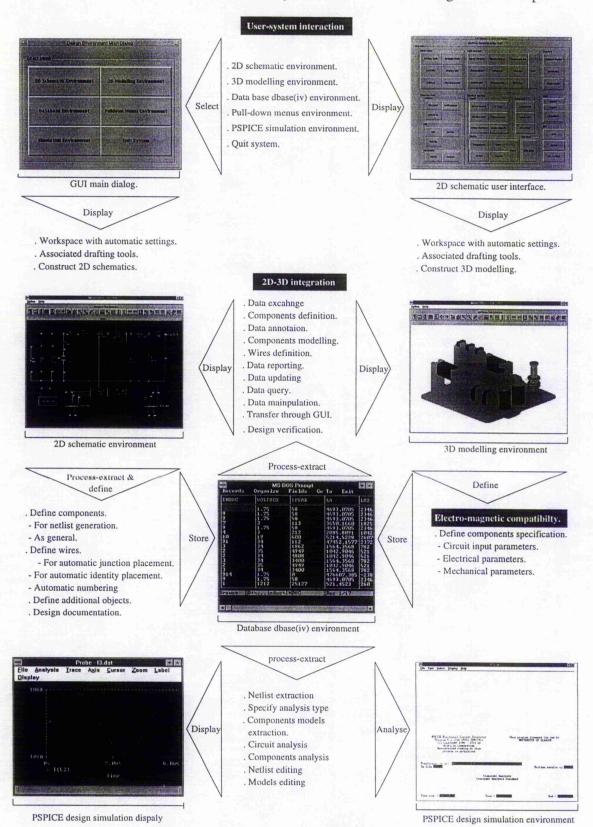

| 7.1  | Laser charging pulser.                                    | 251 |

| 7.2  | Laser charging pulser (side view).                        | 252 |

| 73   | Laser charging pulser (isometric view)                    | 253 |

# Nomenclature

| Symbol                        | Quantity                    | Units            |

|-------------------------------|-----------------------------|------------------|

| A                             | Area                        | $m^2$            |

| $A_c$                         | Effective iron area         | $cm^2$           |

| $A_{p}$                       | Area product                | $cm^4$           |

| $B_m$                         | Magnetic flux density       | T                |

| B                             | Flux density                | T                |

| C                             | Capacitor                   | F                |

| $C_1$                         | Intermediate capacitor      | nF               |

| $C_s$                         | Smoothing capacitance       | F                |

| $C_n$                         | Network capacitor           | nF               |

| D                             | Diode                       |                  |

| c                             | Thread length               | m                |

| d                             | Mean diameter               | m                |

| $d_o$                         | Total length                | m                |

| $d_{i}$                       | Winding length              | m                |

| E                             | Magnetic energy             | J                |

| F                             | Frequency                   | Hz               |

| G                             | The length of the core limb | mm               |

| $\tilde{I}_{_{\Lambda}}$      | Peak charging current       | $\boldsymbol{A}$ |

|                               | Normal peak current         | A                |

| $\stackrel{\smallfrown}{I_F}$ | Peak fault current          | A                |

| $ar{I}_t$                     | Mean current                | $\boldsymbol{A}$ |

| $I_s$                         | Secondary current           | $\boldsymbol{A}$ |

| $I_p$                         | Primary current             | $\boldsymbol{A}$ |

| $K_f$                         | Wave form coefficient       | Square           |

| $K_{j}$                       | Current density coefficient |                  |

| $K_u$                         | Window utilisation factor   | Ratio            |

| L                             | Inductor                    | H                |

| $L_{\mathrm{i}}$              | Charging inductor           | $\mu H$          |

| $L_2$                         | Inductor                    | $\mu H$          |

| $L_3$                         | Inductor                    | $\mu H$          |

| $L_c$                         | Charging inductor           | H                |

| $l_a$                         | Air gap length              | mm               |

| $l_p$                         | Primary linear dimension    | m                |

| $l_m$                         | Core magnetic length        | mm               |

| $l_s$                         | Secondary linear dimension  | m                |

| MTL                           | Mean length turn            | ст               |

#### Nomenclature

| N                           | Number of turns          |       |

|-----------------------------|--------------------------|-------|

| $N_s$                       | Secondary turns          |       |

| $N_{p}$                     | Primary turns            |       |

| $P_o$                       | Transformer output power | W     |

| $P_t$                       | Apparent power           | W     |

| $P_{fe}$                    | Core loss                | W     |

| $P_{g}$                     | Air gap loss             | W     |

| $P_p$                       | Primary loss             | W     |

| $P_{\scriptscriptstyle S}$  | Secondary loss           | W     |

| $P_{cu}$                    | Total copper loss        | W     |

| $R_p$                       | Primary resistance       | Ω     |

| $R_s$                       | Secondary resistance     | Ω     |

| $V_{\scriptscriptstyle NL}$ | Voltage with no load     | V     |

| $V_{\scriptscriptstyle FL}$ | Voltage with full load   | V     |

| $V_r$                       | Ripple voltage           | V     |

| $V_{DC}$                    | DC voltage               | V     |

| $V_p$                       | Primary voltage          | V     |

| $V_{\stackrel{\circ}{s}}$   | Supply voltage           | V     |

| $\stackrel{\circ}{V_p}$     | Peak primary voltage     | V     |

| $W\!f_e$                    | Core weight              | g     |

| $W_a$                       | Window area              | $m^2$ |

### **Greek letters**

| $	au_{ m max}$                    | Maximum charging time    | $\mu s$ |

|-----------------------------------|--------------------------|---------|

| $	au_c$                           | Charging duration cycle  | $\mu s$ |

| $\mu_{\scriptscriptstyle 0}$      | Absolute permeability    |         |

| $\mu_{\scriptscriptstyle \Delta}$ | Incremental permeability |         |

| $\alpha$                          | Regulation               | % Reg.  |

| $\eta$                            | Efficiency               | _       |

| $\phi_{ m max}$                   | Maximum magnetic flux    |         |

| $\phi$                            | Magnetic flux            |         |

| ξ                                 | Electro-magnetic field   |         |

# 1 Introduction

#### 1.1 BACKGROUND

Design of all but the simplest products now generally involves multi-disciplinary teams of engineers working in close tandem. For example, the design of a medical diagnostic product may involve: biochemists, optics designers, analogue designers, mechanical engineers, digital designers, software engineers and production engineers. Obviously, it is critical on such projects to manage design information during both the concept phase and detailed design phase. The objectives of each project is primarily the creation of a competitive product or system and communication is arguably the most critical factor governing success of any project.

In the context of design in general, the purpose of this work is to examine current methodology for "concurrent engineering" and to develop a user-friendly environment for engineering multi-disciplinary products and systems. Before going on to detail the full scope of this work, it is worthwhile considering current design practice.

#### 1.2 DESIGN PRACTICE

During the last decade major advances have taken place in computer-aided design (CAD) systems for assisting the rapid and efficient design of electronic circuits. This has been made possible by the advent of low-cost, powerful and easily accessible microcomputers. The market today for printed circuit board (PCB) design is very competitive with many suppliers offering fully integrated systems at comparatively low cost. Common tools provided include: Digital and Mixed Signal analysis, logic synthesis, Programmable

Array Logic, thermal analysis and latterly electro-magnetic compatibility (EMC) analysis. Tools for the implementation of application specific integrated circuits (ASICs) are now readily available and offer a custom alternative to discrete designs. The market for products specifically for PCB design and layout is now quite mature, with new tools and features evolving at a much slower pace than during the eighties.

There is a wide spectrum of systems's design which involves more detailed engineering analysis than simple schematic design and PCB layout, which may span a range of disciplines. For example, the design of switched-mode power supplies involves not only the design of drive and conditioning circuits, but also a very iterative design cycle for magnetic components, which is closely coupled to mechanical layout of cores and windings. It is therefore necessary for the designer to iterate between mechanical and electronics designs in order to optimise circuit performance. There are many examples of this type of design particularly in power electronics. Although computer-aided engineering (CAE) systems are available for each distinct aspect of the design (e.g. mechanical CAD, electronics, control simulation) a fully integrated environment for system engineering is not available commercially; at best each organisation must develop their own integrated, bespoke, system from available software products.

In the mechanical domain, CAD systems have developed along two paths: 2D draughting and 3D solid modelling. In 2D draughting, tools have evolved which automate the draughting process with standard libraries of components (e.g. fasteners). However, it is still reliant on the user to generate the engineering views of the components. Many vendors have added on 3D modelling with some solid modelling features to enhance the product but their main application is still primarily in 2D draughting. On the other hand, advanced modelling packages have been developed using solid modelling techniques and surface modelling to provide true 3D mathematical representations of components. Coupled with parameteric dimension driven design capability, such tools provide on unparalleled approach for mechanical design. 2D drawings can be generated automatically from the 3D models and models transferred to rapid prototyping systems such as stereolithography. Such systems are generally UNIX based and systems are currently evolving rapidly. Advanced PC-based systems (Windows NT) are now appearing, which is predicted to dominate the market.

It is apparent that between the extremes of electronics circuit tools and mechanical modelling that there is an opportunity to provide an integrated environment for design, aimed at the problems which fall into both electronic and mechanical domains, and wider disciplinary projects. Power electronics is one area but there are many more, including: mechatronics, building services and electro-magnetics. What is required is a design

#### Chapter 1: Introduction

environment that combines the best of both worlds so that the designers can transfer between electronics and mechanical layouts (or domains) rather like a PCB designer transfers between schematics and layout. Even within PCB design this may of significant advantage given the requirements of packaging; the display of full 3D circuit models would give the designer a greater appreciation of layout, particularly when mechanical component such as heat sinks and connectors need to be added, and PCB's interfaced in complex assemblies.

The growing market for design software tools indicates an increase in the use of computers throughout the product design process [1.1]. In addition, there is a demand for full product models (digital mock-ups) and links to simulators. These advances contribute to a more efficient design process and facilitate innovative design. Product models play an important role for the designer: by using product models, the designer is able to store, retrieve, and modify data, as well as the data on design methodology itself. Table [1.1] shows the core procedure employed in the design process and the methods used to achieve a final product.

Table [1.1]. Product design and its techniques.

Requirements of modern markets in electronics are distinguished by dramatically decreasing prices, higher demands for flexibility, reduced "time-to-market" and growing product complexity. Only well designed products with high performance and quality are able to ensure a company's competitiveness. The application of CAD systems is now vital for competitiveness. Design departments are responsible for product quality, product cost, and for planning and forecasting the innovation potential of each product

[1.1]. Therefore, there has been a great deal of effort to improve the design process itself, and the systems employed. The application of engineering design methodology and its integration with CAD have contributed greatly to the speed with which competitive products can be developed.

Reducing the "time-to-market" is one of the greatest challenges facing industry today, Sadiq et al. [1.2]. The total development time includes the time to design, prototype, test and certify new products. In comparison to mechanical design, studies have shown that in a typical electronic product development cycle, 85 per cent of development costs are committed in the first 5 per cent of the design cycle. In this early (conceptual) design stage, important decisions are made regarding fundamental product technology, materials and manufacturing processes [1.3].

The management of the conceptual phase is critical to the success of the project. Organisations must look closely at the tools available to designers and the sharing of information amongst project teams, particularly when a project encompasses a wide range of technologies (e.g. mechanics, optics, sensors, digital, analogue and power electronics). The optimisation of designs and the requirements for reporting vary considerably depending on the project and demarcations within the projects teams. Obviously, a common engineering environment where data is available to all project engineers, irrespective of discipline would be of major advantage.

Today, there are examples of large organisations that have developed integrated engineering environments (e.g. Boeing, Ford), however, the systems employed have been of high cost and generally out of each the normal capital expenditure of most companies. The benefits to any organisation implementing concurrent engineering and managing design on an integrated basis are manifold. What is required, therefore, is the availability of such a system at a realistic cost.

The market for CAE systems is becoming more resistant to change, particularly as products become established. In mechanical design, for example, AutoCad is now widely used with a large, loyal, user base. There are other examples of this and it is vital for new systems to capitalise on the existing user base. As a result, many mainstrain companies now offer an open architecture which permits third party vendors to supply add-on utilities, which can greatly enhance productivity in particular applications. For AutoCad, there are probably more than 1000 third party enhancements available in practically every application area.

#### 1.3 DESIGN SYSTEMS

It is now well recognised that CAD tools can be used to speed up electronic circuit design. Jain et al. [1.4] describes a designed package called AJITA, used for rapidly producing electronic circuit design, in printed circuit form, from direct specification in terms of functional building blocks. It provides a library of prototype building blocks that are dimensioned by user interaction for each application (i.e. inputs, outputs and power supply availability). The appropriate circuit, component values and circuit board are then automatically generated. However, AJITA provides a full printed circuit board (PCB) design, given a tool to speed up their design process. With the advent to high-speed digital computers, some of the pioneering work of Kron [1.5], [1.6] was applied to the simultaneous solution of network equations. This formulation was used in part by computer codes such as network analysis program (NET-1) by Malmberg [1.7] and electronic circuit analysis program (ECAP) [1.8].

With the availability of workstations with high resolution graphics, a further step in the evolution of integrated design system becomes possible. Simulated profiles from the layout design interface for x-windows (SIMPL-DIX) [1.9], is an integrated system that utilise graphical interfaces. It provide process design, rather than device design, environments, but it employs an open architecture combined with workstation-based graphics to aid the user interface.

CAD systems have also evolved from electrical-electronic (ECAD) or computer integrated manufacture (CIM) systems [1.10]. The distinction between advanced ECAD, extended CIM, and dictated technology computer-aided design (TCAD) systems is sometimes not trivial [1.11]. Nevertheless, a summary of a designed ECAD systems shown in table [1.2], where each of the systems listed exhibits a different architecture and emphasis certain aspects of TCAD.

New capabilities are provided within the methodology of developing these systems by, for example, extending existing applications, or by integrating additional existing applications which implement the required functionality. From the table shown above, these system are compared using technology CAD (TCAD) levels (i.e. a term which correspond to different views of integrated multi-tool systems): The data level is the process representation which provides the database for tool coupling. The tool level is where the simulation functions are stored. The task level a control environment where operations and flows are defined and executed. Finally, the representation level is the interface through which the user interacts. Additional, comparison schemes can be employed such as the methods of integration used and overall performances. In this table also:

- internal means that the system is not used outside the institution.

- Production means that the system is known to be in use somewhere.

- Commercial means that the system is commercially available.

- Blank fields indicate lack of reliable infuriation.

Table [1.2]. List of ECAD systems and tools integration approaches [1.11]

| Name             | Institution              | Stauts                  | Data level            | Task level               | Presentation level |

|------------------|--------------------------|-------------------------|-----------------------|--------------------------|--------------------|

| MECCA            | AT&T                     | int. prod.              | awk/sed, c++          | UNIX, Shell              | Tk                 |

| PREDITOR         | CMU                      | experim.&<br>commercial | CDB/HCDB              | Tel                      | Tk, Motif          |

| EASE             | Intel                    | int. prod.              | PIF derivate.         | UNIX Shell,<br>FASST/TEL | Motif              |

| CAFE             | MIT                      | internal                | BPIF/Gestalt          | MIT PFR                  |                    |

| P&D<br>Workbench | NEC                      | int. prod.              |                       | MEDLEY+<br>ESCORT        | DAIJOBDA           |

| UNISAS           | Oki                      | int. prod.              | GCOS                  | UNICOL                   |                    |

| IDDE             | Philips UK               | int. prod.              | ASCII PIF derivative. | none                     | Apollo<br>DIALOGUE |

| PROSE            | UC Berkeley              | internal                | BPIF, SWR             | Tcl                      | Tk + VEM           |

| SIMPL-IPX        | UC Berkeley              | internal                | Converter<br>(BTU)    | none                     | SIMPL-DIX          |

| OrCAD/VST        | OrCAD sys. corporation   | commercial              | PASCAL or<br>C        | IBM PC<br>AT / XT        | OrCAD/VST          |

| eCAD plus        | Microdata<br>systems SrL | commercial              | EFORM                 | IBM PC<br>AT-286, 486    | eCAD<br>OrCAD/STD  |

#### 1.4 MARKET FOR MECHANICAL DESIGN SOFTWARE

Generally, revenues in the 90's for CAD computer-aided manufacturing (CAM) and CAE rose, according to market researcher Dataquest [1.12]. The leading applications area are mechanical, electronic CAE, integrated circuits (ICs) layout, PCB layout. Dataquest's top vendors in total factory revenues were IBM, SunMicrosystems, Hewlett-Packcard, Intergraph, Digital, Computer vision, and AutoDesk. In mechanical software, IBM, AutoDesk and parametric technology (PTC) lead. In the top 10 companies, total growth was almost double that of the market as a whole. AutoDesk and Intergraph are setting the pace in ECAD software applications, with respective market shares of 21.7 and 13.8 per cent.

The growth of the use of CAD software has climbed rapidly each time computer hardware crossed a threshold; first minicomputer, then UNIX workstation to PC's [1.13]. Mechanical CAD software is one tool that is widely used on these platforms. As they vary in their structure and use, many of these software incorporates advanced features like unified parametric geometry which facilitates 3D wireframe, surfaces and feature-

based solid modelling, into a single associative data structure with combined parametric modelling. Market research carried for mechanical CAD systems show a high level of competitions between world leading companies. According to Dataquest's market statistic, CAD continues to dominate the world-wide CAD software market comparing to its competitor IBM. For example, in the mechanical vendor community, 1995 software market leader AutoDesk was replaced by IBM, which moved to the top position world-wide, followed by parametric technology (PT).

Mechanical system developed by AutoDesk has carved a solid position as the price-performance leader in mechanical design. Its comprehensive application programming interface available that can deliver graphic performance under Windows or DOS. In addition, AutoDesk have developed the new software in combination with programs developed by other industrial leading companies from the mechanical sector to provide complete design. An enhancement version of mechanical CAD was made including additional features: New interactive 3D graphics visualisation capabilities and other customer requested enhancements. Market analysts believe that AutoDesk mechanical DeskTop provides a complete design through manufacturing solution for the mechanical CAD market.

IBM keep improving their CAD products such CATIA. The latest updated versions available in the market contains different products grouped into different engineering areas: Mechanical design; manufacturing; analysis and simulation; architecture. Additional features include the capability to provide custom modelling facilities to suit various different tasks and to update the modelling technology to include parametrics and variational geometry with modern sketching facilities. CATIA is now multi-mode modeller with integrated solids, wireframe and surfaces. For consistency with other systems CATIA has bi-directional associatively between the various modelling technologies. This is very much under the control of the user where data can be updated with the assistance of data management system. The system provides a programming language called interactive user access (IUA), which can be used for developing further software routines and applications of different tasks.

Available on PCs and UNIX workstations, Intergraph's MicroStation is one of the most complete draughting packages currently on the market. The package is now on its fifth version. Design tools enhancement make it flexible system to use. The development language (MDL) enables users to developed third party software of various engineering areas to perform specific tasks. Similarly, AutoCAD is a full featured CAD system, capable of handling most designs duties including mechanical design.

Pro/Engineering is another CAD system used for mechanical design, it provides rapid prototyping to speed up the whole process of design and manufacture in a wide range of industries [1.14]. It contains facilities such as stereolithography which works by taking a 3D model of a component and slicing in into thin layers. These layers are further processed, for example, to ensure an even thickness for each layer of resin.

Despite all the facilities that are available within the system, many improvements have been carried out. At release 16, the definition of geometric tolerances has been much improved. Instead of selecting a series of menus picks, tolerance can be defined in dialog editors, which are windows-based and contain a panel of tolerances symbols so that the selection can be performed graphically. New set of commands have been added concerning general feature creation, to allow creation advanced general shapes (e.g. fillets, chamfers). These facilities have been improved by the addition of a dialog editors, allowing different features to be changed, extended, and redefined. Further improvements have been carried towards the placement conditions in assemblies. As the facility was available but less interactive, a component can be placed dynamically using either, translation or rotation techniques. Further improvement also taken towards the design of GUI including some enhancement to design tools. With these tools assembly files are automatically generated for each component in the assembly, as this saves time and facilitates the individual specification of attributes (i.e. creates assemblies and readily control colour and texture).

#### 1.5 DESIGN SYSTEMS AND METHODOLOGY

Mechanical design and electronics design are typically performed as separate functions in engineering [1.3]. However, the increasing use of electronics in what were once predominately mechanical products and the increasing emphasis on packaging and other mechanical considerations in electronics products, requires the implementation of a concurrent engineering approach.

#### 1.5.1 Product Design Approach

When designing a product, decisions have to be made on what to optimisation, with several consequences on manufacturing costs. These decisions can completely defeat the designer's intentions. Top management, engineering, purchasing, personal, and manufacturing each contribute to the success or failure of a product. The design requires a great deal of analysis, investigation of basic physical processes, experimental verification, difficult decisions and choices. In many cases, the choices become more and more difficult as the design gradually works its way toward acceptability. Figure 1.1

shows the product design process supported by the concept of computer-aided design (CAD).

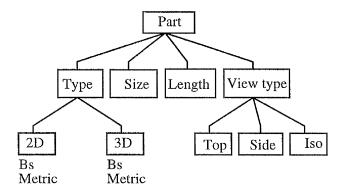

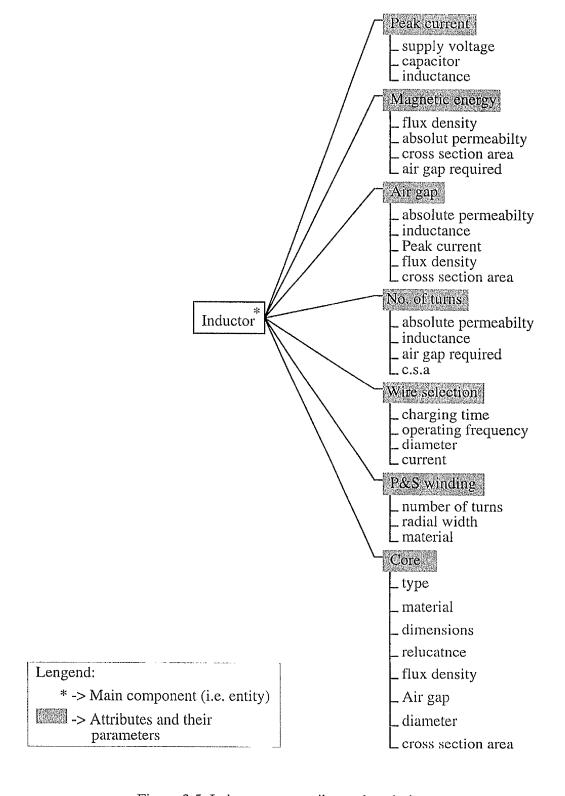

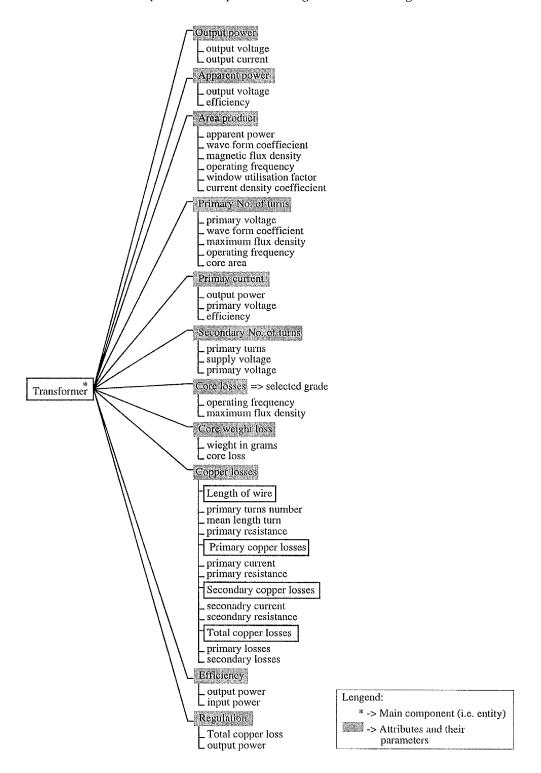

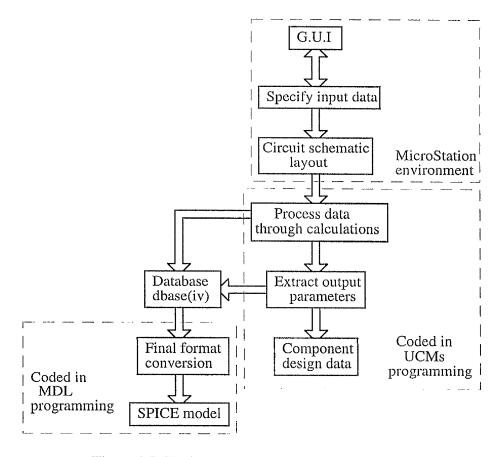

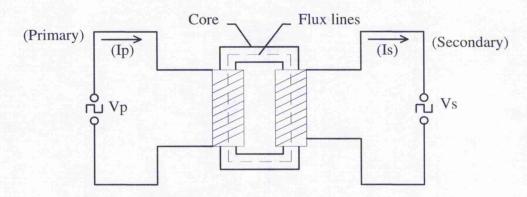

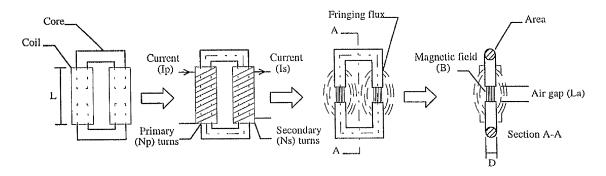

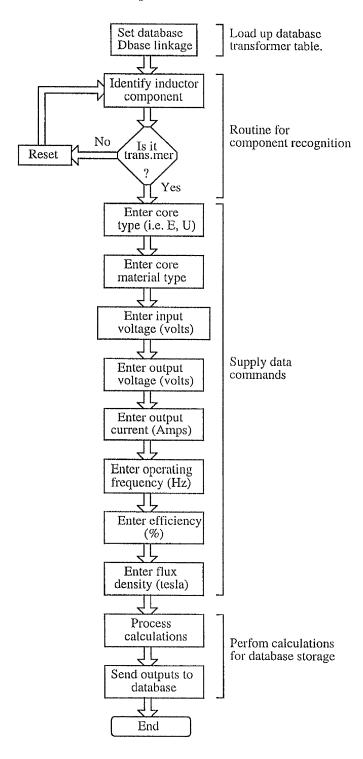

Figure 1.1 Product-design process supported by CAD applications.