# <u>Accelerating Stresses</u> <u>For Life Testing of</u> <u>Switch-Mode Power Supplies</u>

Anne R. Keown

Submitted for the degree of Master of Science

Department of Electronics and Electrical Engineering

University of Glasgow

October 1994

Copyright: Anne R. Keown B.Eng 1994

ProQuest Number: 13831537

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 13831537

Published by ProQuest LLC (2019). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

### Abstract

I.B.M U.K. Ltd procure Switch-Mode Power Supplies to place in the computers they manufacture. These Power Supplies are tested to ensure that they meet a specified reliability target. Due to the high Mean Time To Failure (MTTF) the test duration required to verify the MTTF is in excess of three months. In an attempt to find a way to reduce the time required to ensure this requirement is met it was decided to investigate a selection of stresses from the point of view of their effectiveness as a means of accelerating life tests. Subsequent to a theoretical exploration of the topics of Switch-Mode Power Supplies, Reliability and Accelerated Life Testing the power supplies were subjected to High Temperatures, High Relative Ambient Humidity, Power Cycling, Temperature Cycling and various conditions of electrical Stress. The effectiveness of these stresses was gauged by checking the power supplies' performance after various intervals during which they had been subjected to stress.

It was discovered that high ambient temperatures have a measureable effect on electrolytic capacitors, which is physically related to the amount of energy to which the capacitors are subjected, to the extent that several capacitors failed during the tests without other damage being done to the power supply. It is recommended that further research be undertaken with a view to developing a relationship between capacitor degradation and power supply life test duration because, since the capacitors MTTF is greater than that of the power supply, failure due to degradation would indicate that the power supply had passed its specified MTTF.

Acknowledgements

I would like to thank IBM U.K. Ltd for providing the funding and the resources for this research.

In addition I would like to thank the following members of the Engineering Laboratory, as well as the staff of the Product Quality and Reliability Laboratory, for their invaluable assistance: Mr J. Goodfellow, Mr D. Edgar, Mr G. Guthrie, Mr R. Leonard, Mr R, Pearce, Mr D. Kerr, Dr F. Martin, Mr I. Turner, Mr W. Beer, Mrs S. Kilpatrick, Mr M. Burrows, Mr D Hewitt and especially Mr S. Linning.

I would also like to express my sincere gratitude to Professor J. Barlow and Professor J. Sewell of Glasgow University for their guidance in producing this thesis.

## Page

# Contents Chapter or Section

|    | Acknowledgements                                               |

|----|----------------------------------------------------------------|

|    | List of Figures                                                |

| 1  | Chapter 1 - Introduction                                       |

| 1  | Section 1.1: Linear Power Supplies                             |

| 6  | Section 1.2: Switch Mode Power Supplies                        |

| 12 | Section 1.3: Voltage Doubling Circuitry                        |

| 17 | Section 1.4: Performance Requirements                          |

| 19 | Chapter 2 - Reliability and Accelerated<br>Life Testing        |

| 19 | Section 2.1: Product Reliability                               |

| 23 | Section 2.2: The Life of A Product                             |

| 25 | Section 2.3: Failure Rates and MTTFs                           |

| 31 | Section 2.4: Accelerated Testing                               |

| 41 | Section 2.5: Activation Energy                                 |

| 44 | Section 2.6: Alternative Means of                              |

|    | Reliability Assessment                                         |

| 47 | Chapter 3 - The Effect of Elevated                             |

|    | Ambient Temperatures                                           |

| 47 | Section 3.1: Current Laboratory Practice                       |

| 49 | Section 3.2: Highest Possible Operating<br>Ambient Temperature |

|    |                                                                |

### Page **Chapter or Section** Section 3.3: Temperatures of 52 Individual Components 81 Section 3.4: Analysis by Thermal Imager 82 Section 3.5: The Effect of Elevated Ambient Temperature on Electrolytic Capacitors 101 Chapter 4 – Cycle Based Tests 101 Section 4.1: Power Cycling 118 Section 4.2: The Effect of Increased Humidity Section 4.3: Thermal Cycling 132 144 Chapter 5 - The Effect of Electrical Stresses 145 Section 5.1: The Effect of Varying Input Voltage 159 Section 5.2: Examination By Thermal Imager Section 5.3: The Effect of Varying 163 **Output Load**

- 166 Section 5.4: The Effect of Interfering With Airflow.

- 180 Chapter 6 Conclusions

- 185 References

### List of Figures

| <u>Number</u> | Page       | <u>Title</u>                               |

|---------------|------------|--------------------------------------------|

| 1.1           | 2          | Linear Power Supply                        |

| 1.2           | 4          | Series Regulator                           |

| 1.3           | 7          | Switch Mode Power Supply                   |

| 1.4           | 13         | Commercial Power Supply                    |

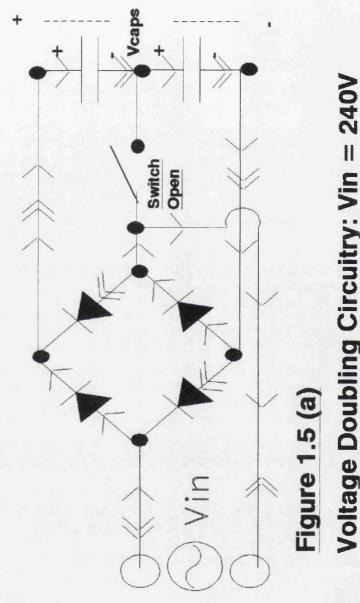

| 1.5(a)        | 14         | Voltage Doubling Circuitry: Vin = 240V     |

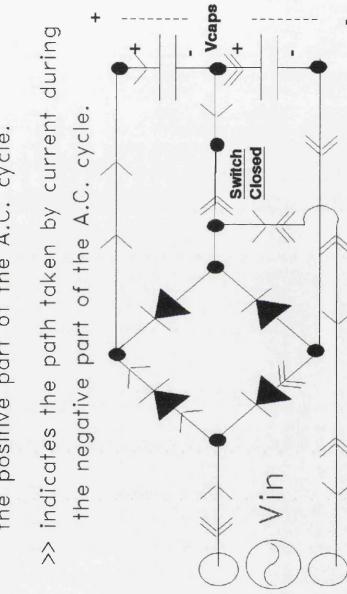

| 1.5(b)        | 15         | Voltage Doubling Circuitry: Vin = 110V     |

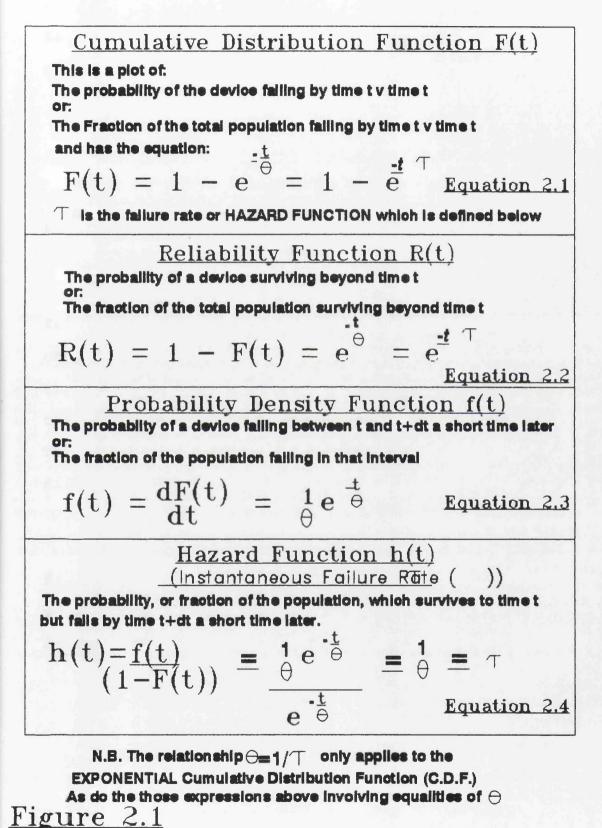

| 2.1           | 22         | Reliability Definitions and Equations      |

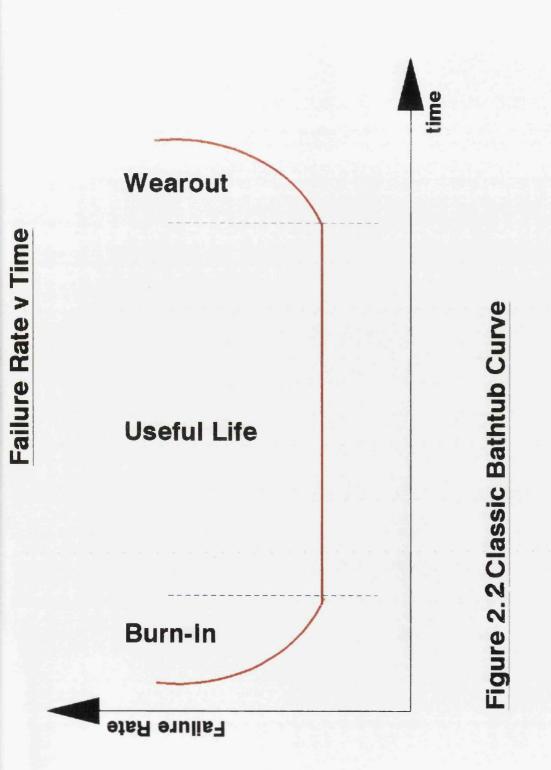

| 2.2           | 24         | Classic Bathtub Curve                      |

| 2.3           | 28         | Chi-Square Values                          |

| 2.4           | 30         | Failure Rate Conversion Factors            |

| 2.5           | 35,36      | 'Failure Rates' Program Listing            |

| 2.6           | 39         | Typical Thermal Cycling Test Profile       |

| 3.1           | 48         | 'Normal' Power Cycling Acceleration Factor |

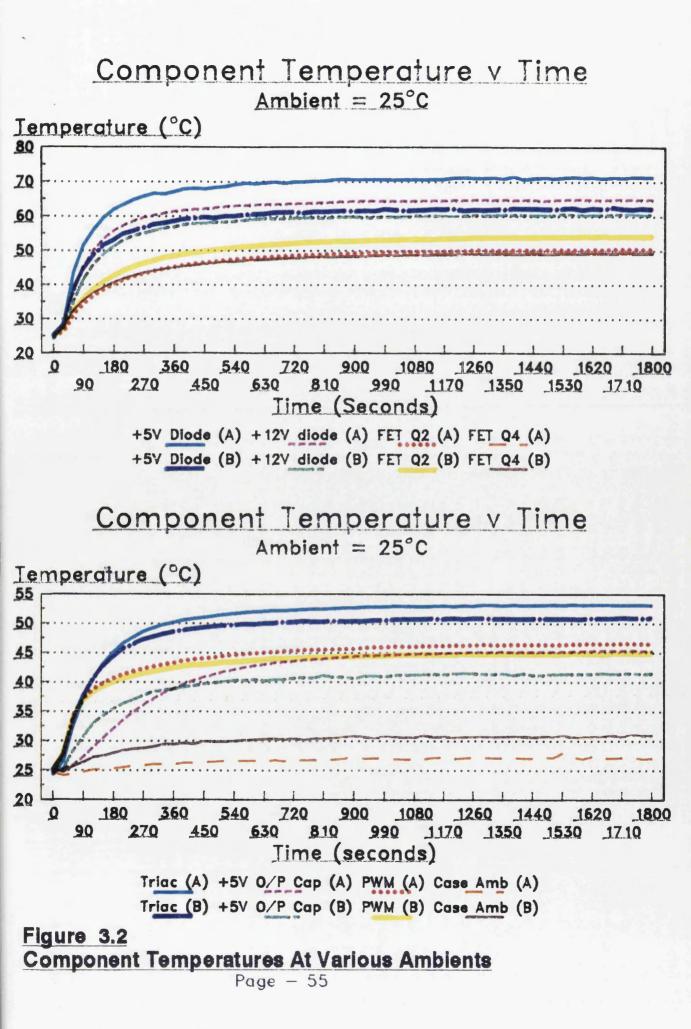

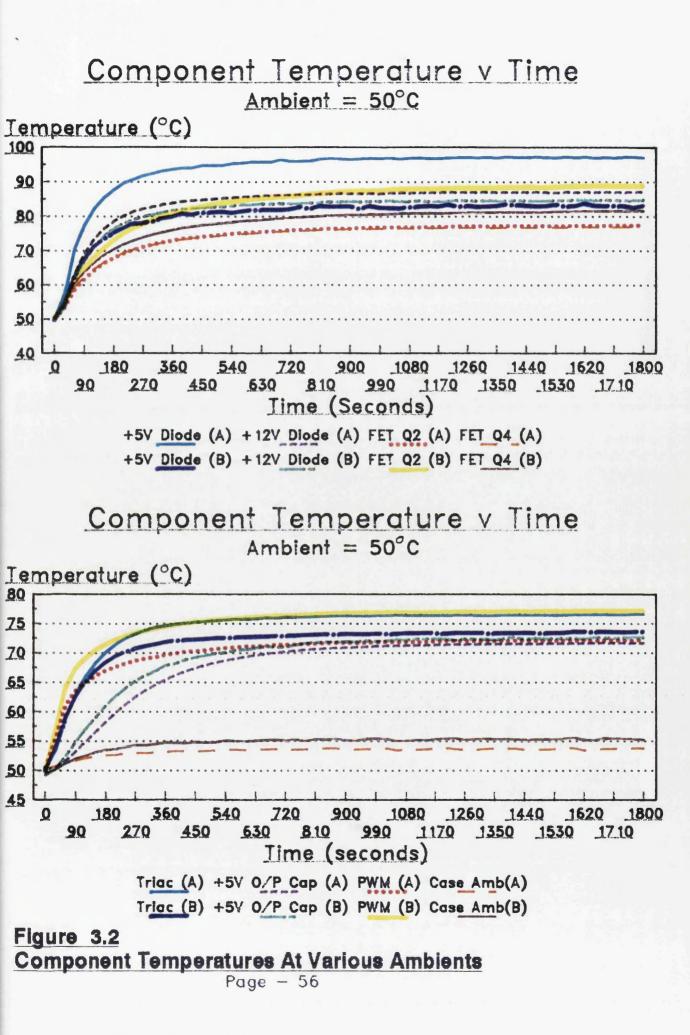

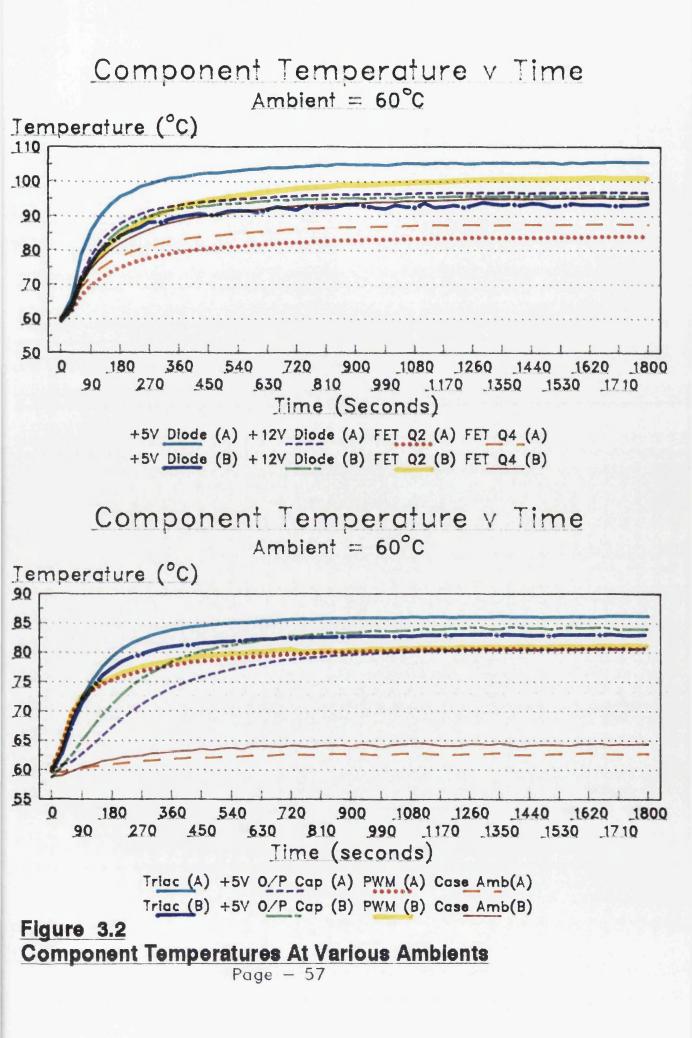

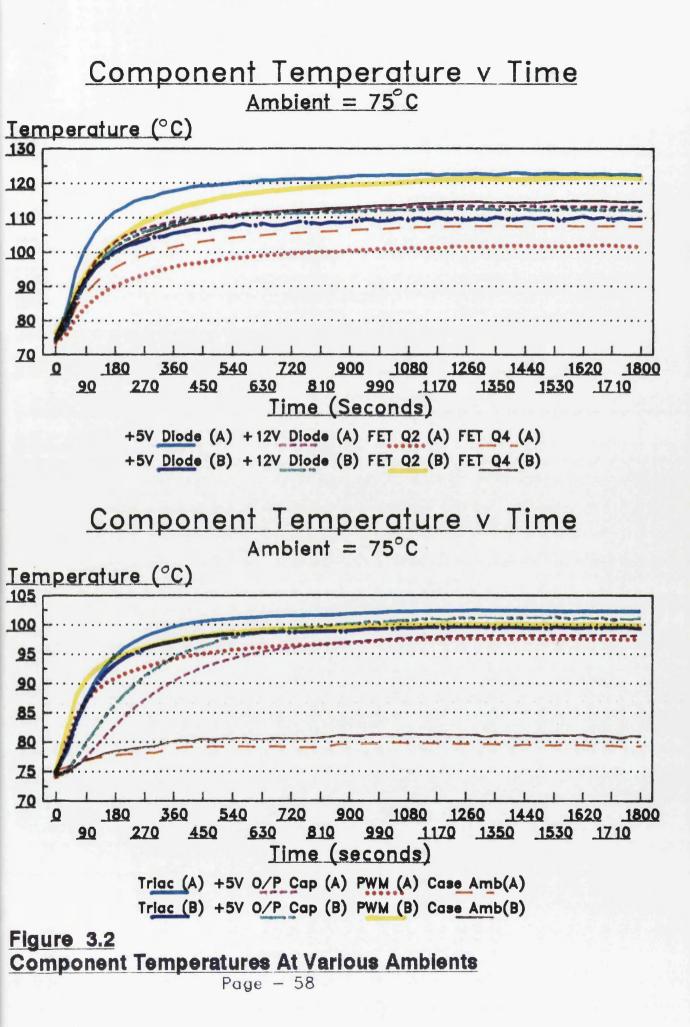

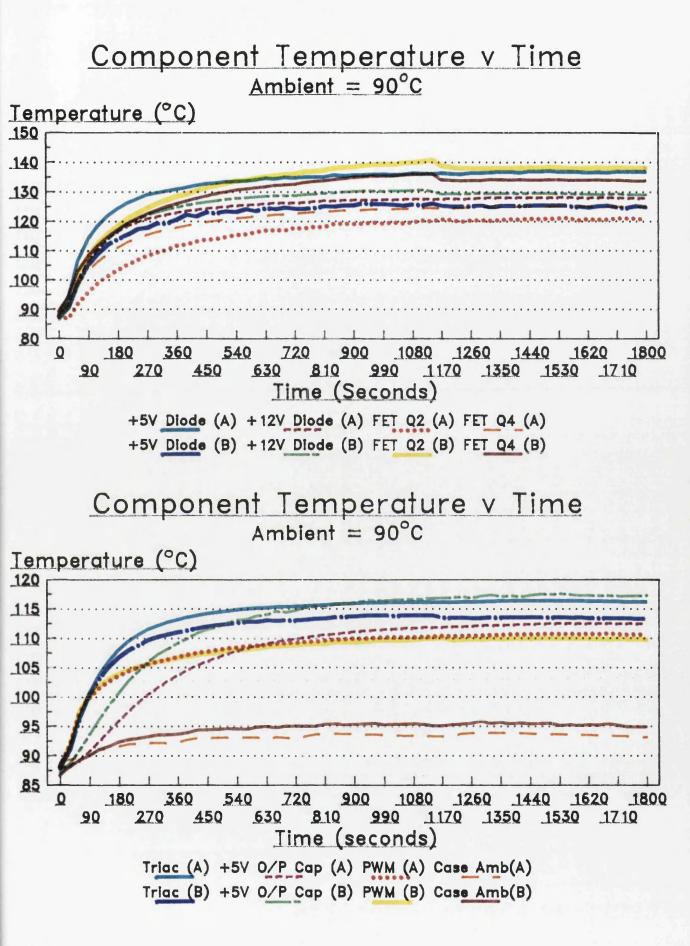

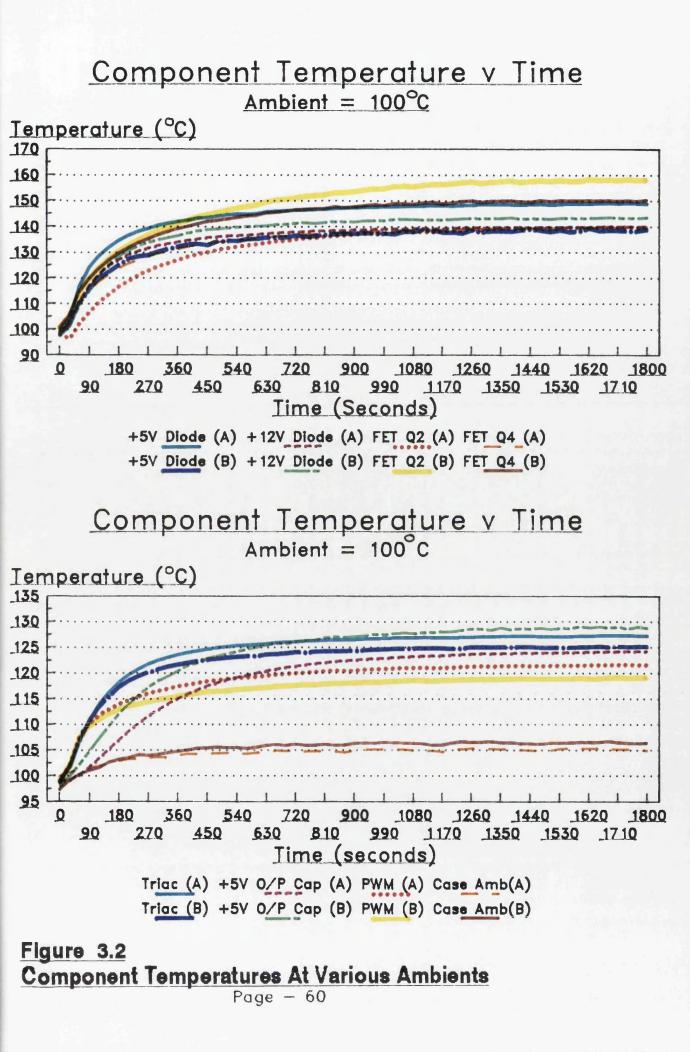

| 3.2           | 55-60      | Component Temperatures at Various Ambients |

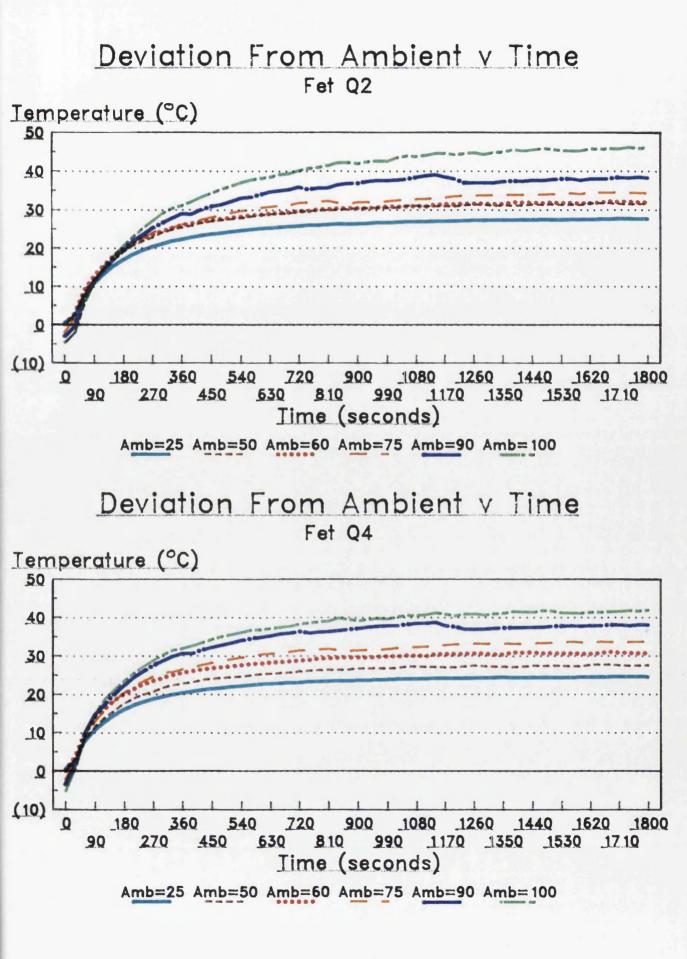

| 3.3           | 62-65      | Deviation of Component Temperature From    |

|               |            | Ambient                                    |

| 3.4           | 68         | FET Q2; Deviations From Ambient            |

|               |            | Temperature                                |

| 3.5           | 70         | FET Q4; Deviations From Ambient            |

|               |            | Temperature                                |

| 3.6(a)        | · · · 72 · | +5V Output Diode; Deviations From Ambient  |

| 3.6(b)  | 73             | +5V Output Capacitor; Deviations From      |

|---------|----------------|--------------------------------------------|

|         |                | Ambient                                    |

| 3.6(c)  | 74             | +12V Output Diode; Deviations From Ambient |

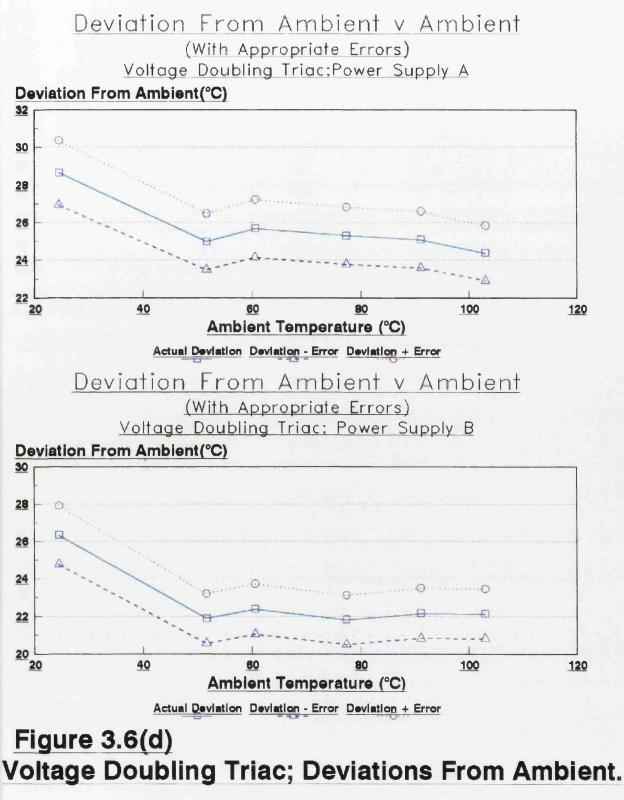

| 3.6(d)  | 75             | Voltage Doubling Triac: Deviations From    |

|         |                | Ambient                                    |

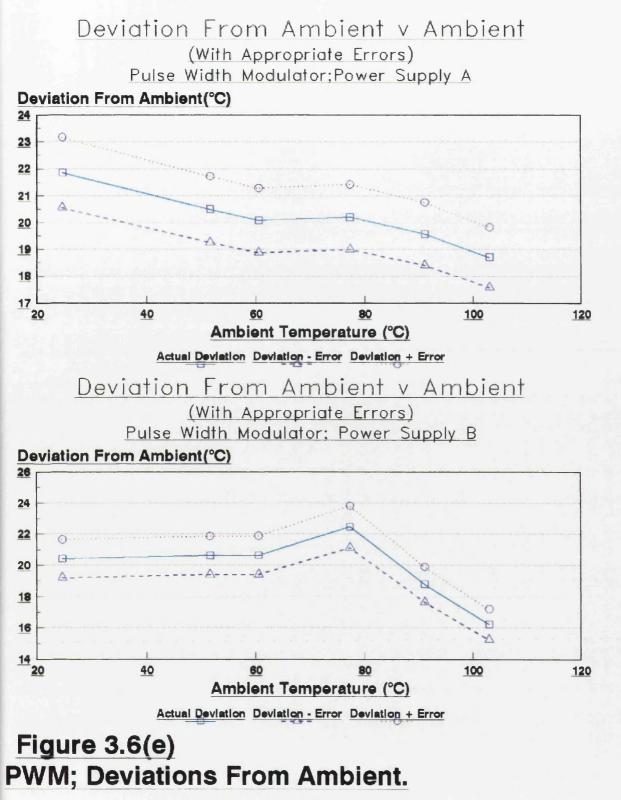

| 3.6(e)  | 76             | PWM; Deviations From Ambient               |

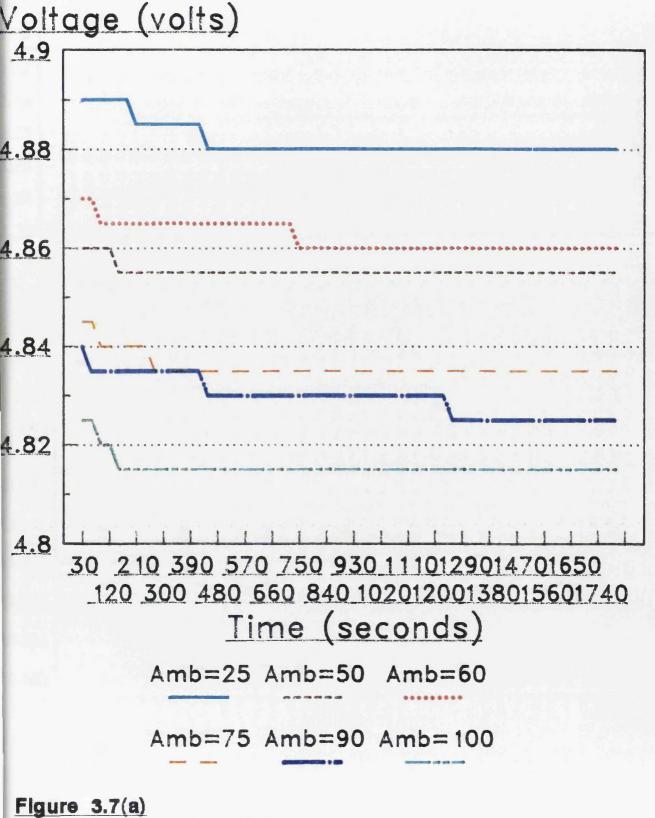

| 3.7(a)  | 78             | Averaged +5V Output Voltages               |

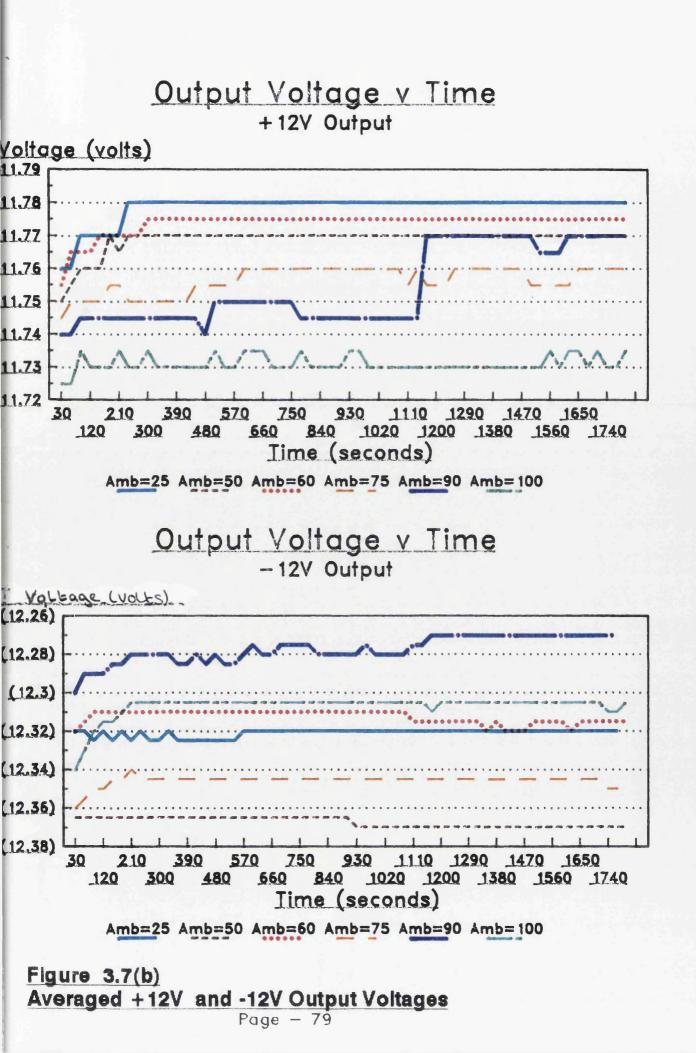

| 3.7(Ь)  | 7 <del>9</del> | Averaged +12V and $-12V$ Output Voltages   |

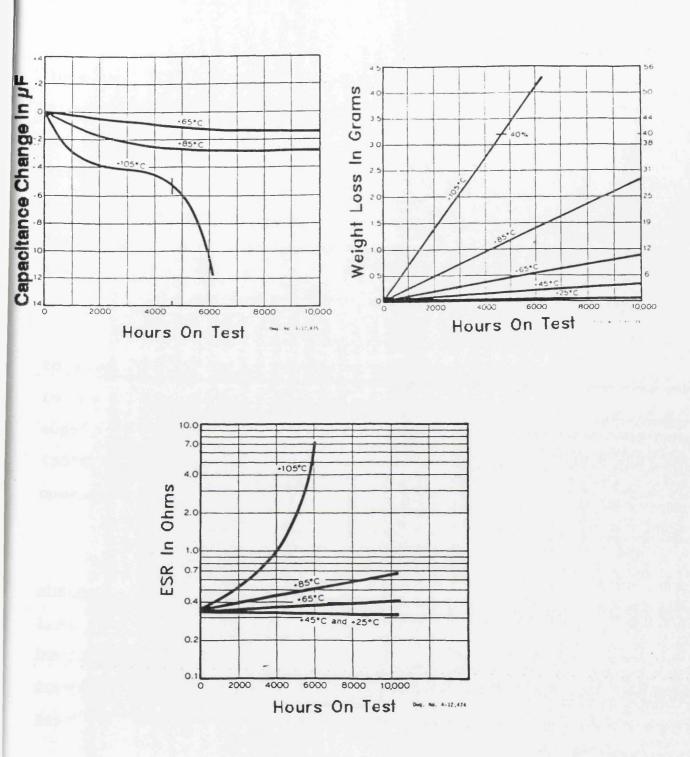

| 3.8     | 83             | Manufacturers' Capacitor Degradation Data  |

| 3.9     | 85             | Capacitor Activation Energy Calculation    |

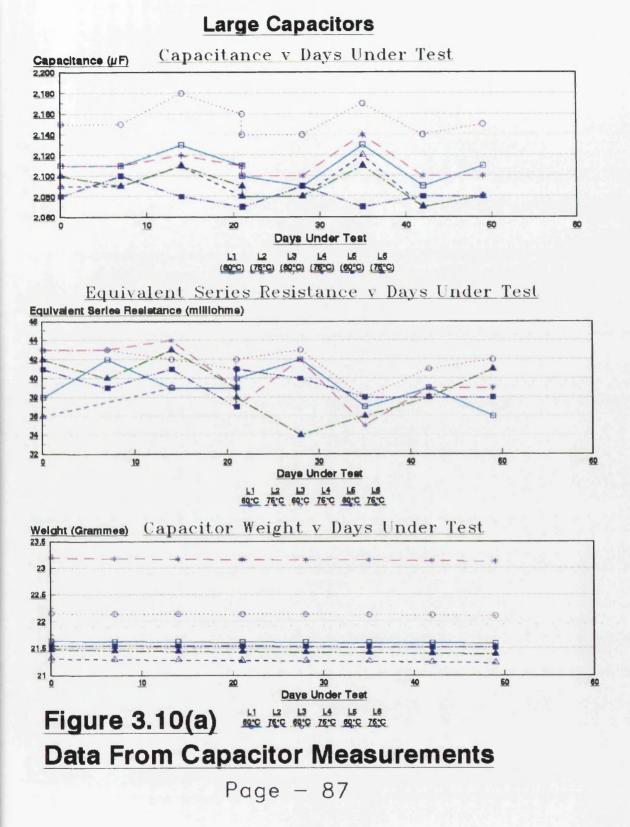

| 3.10(a) | 87             | Data From Capacitor Measurements           |

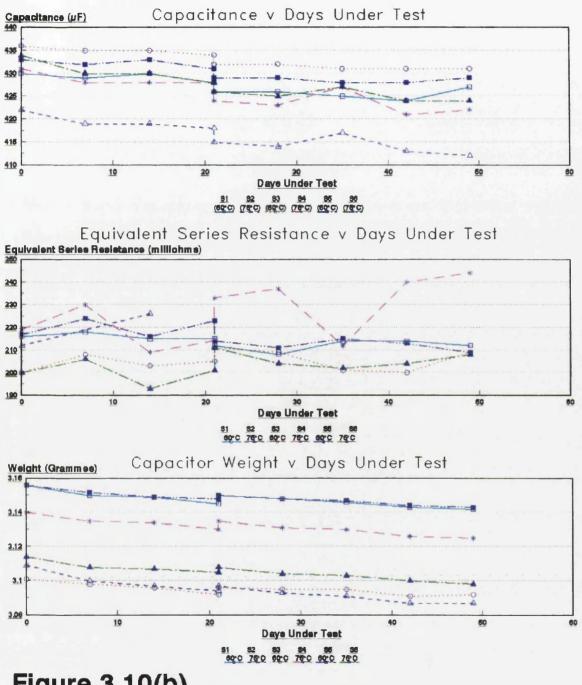

| 3.10(Ь) | 88             | Data From Capacitor Measurements           |

| 3.11    | 90             | High Ambient Test Regulation and Ripple    |

|         |                | Results                                    |

| 3.12    | 91             | High Ambient power Cycling Regulation and  |

|         |                | Ripple Checks                              |

| 3.13    | 93             | Good and Degraded Electrolytic Capacitors  |

| 3.14    | 95             | Characteristics of Stressed and Unstressed |

|         |                | Capacitors                                 |

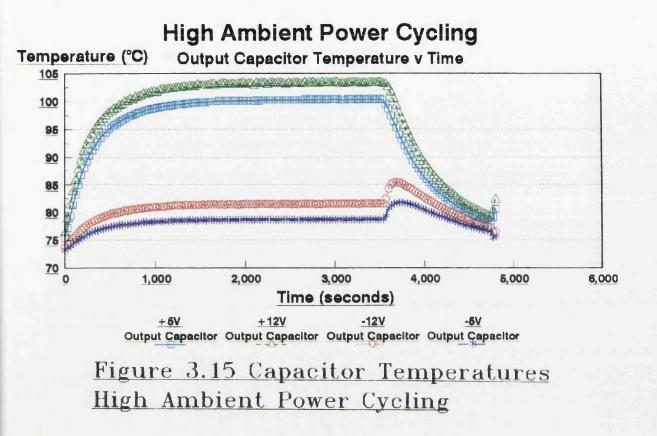

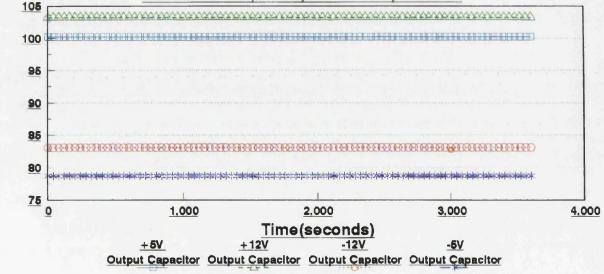

| 3.15    | 97             | Capacitor Temperatures: High Ambient Power |

|         |                | Cycling                                    |

| 3.16    | 97             | Estimated Capacitor Temperatures High      |

|         |                | Ambient Test                               |

| 3.17    | 98             | High Ambient Power Cycling Acceleration    |

|         |                | Factor                                     |

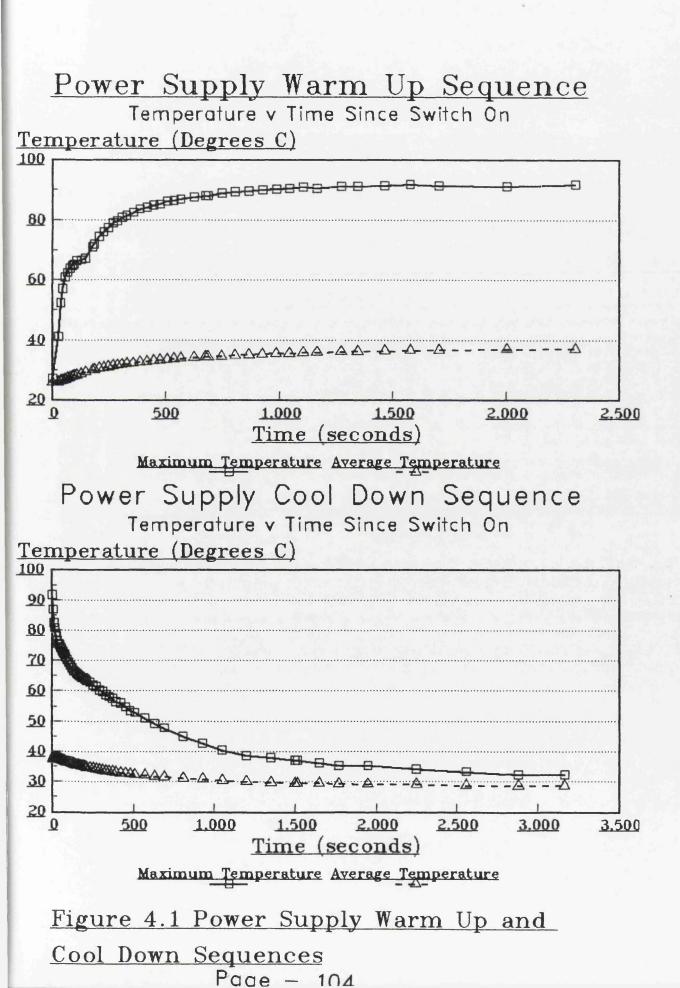

| 4.1   | 104     | Power Supply Warm Up and Cool Down         |

|-------|---------|--------------------------------------------|

|       |         | Sequences                                  |

| 4.2   | 108     | Coffin-Manson Acceleration Factor For      |

|       |         | Power Cycling                              |

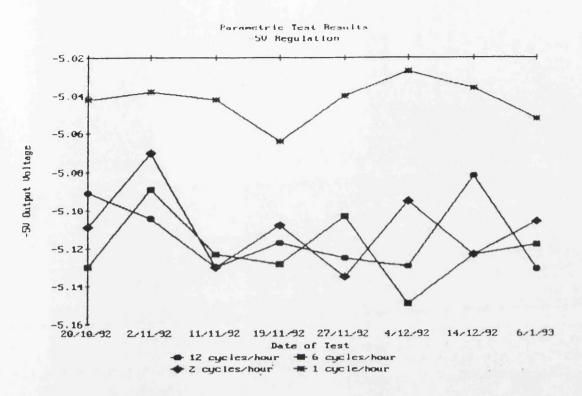

| 4.3   | 110     | Power Cycling Tests typical Database Entry |

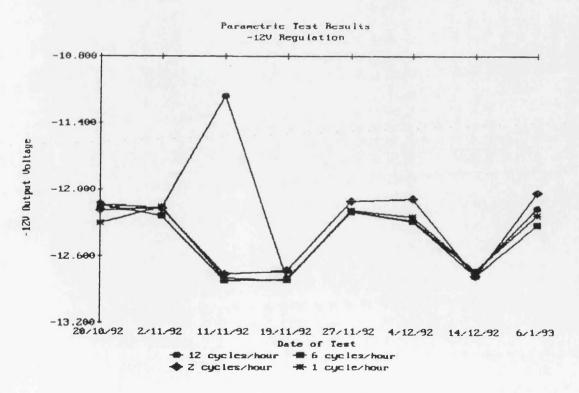

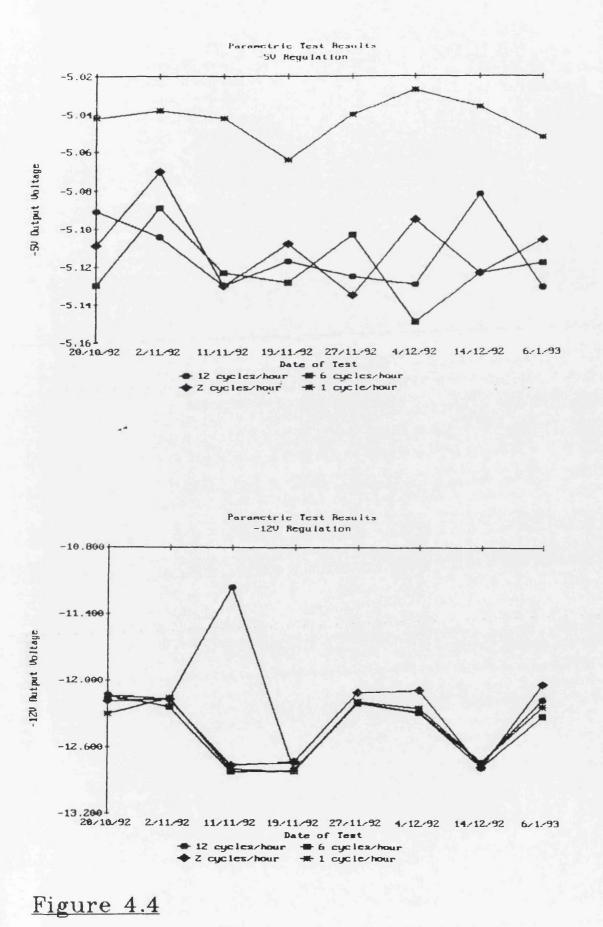

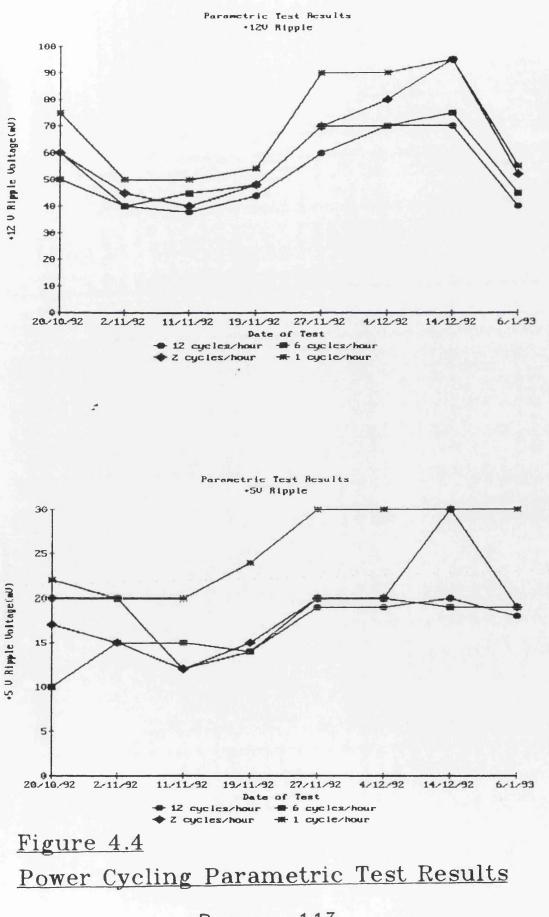

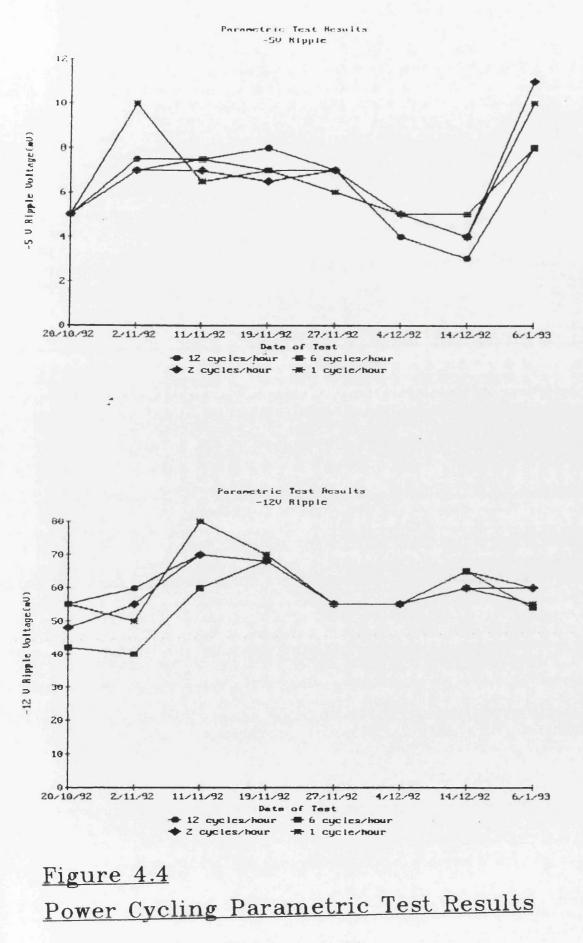

| 4.4   | 111-114 | Power Cycling Parametric Test Results      |

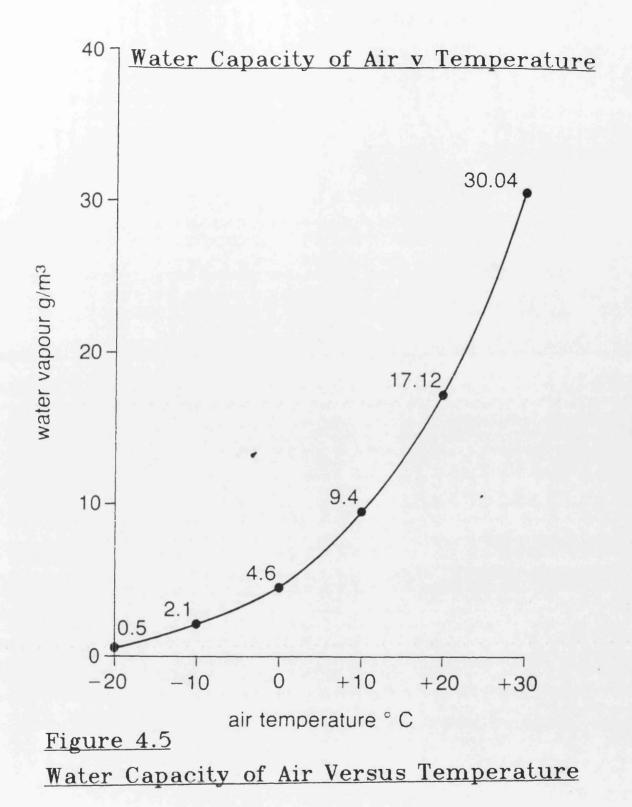

| 4.5   | 120     | Water Capacity of Air Versus Temperature   |

| 4.6   | 122     | Humidity Acceleration Factor               |

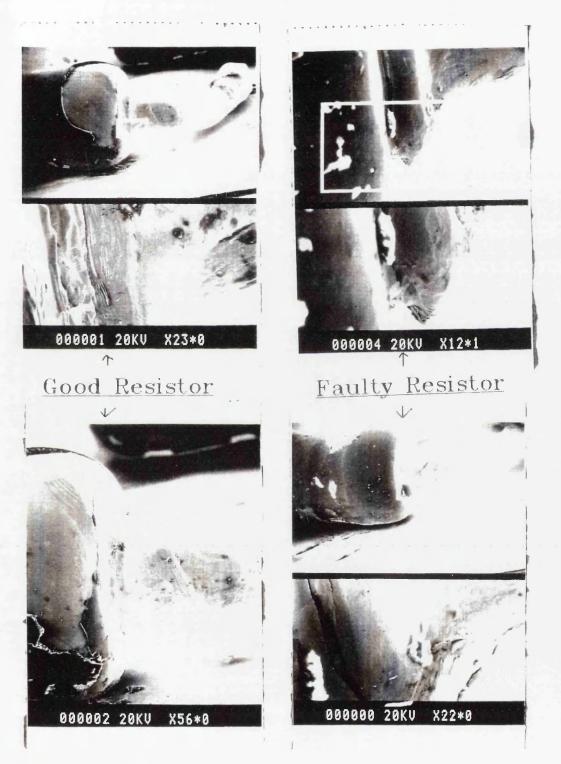

| 4.7   | 128     | Good and Damaged Resistors                 |

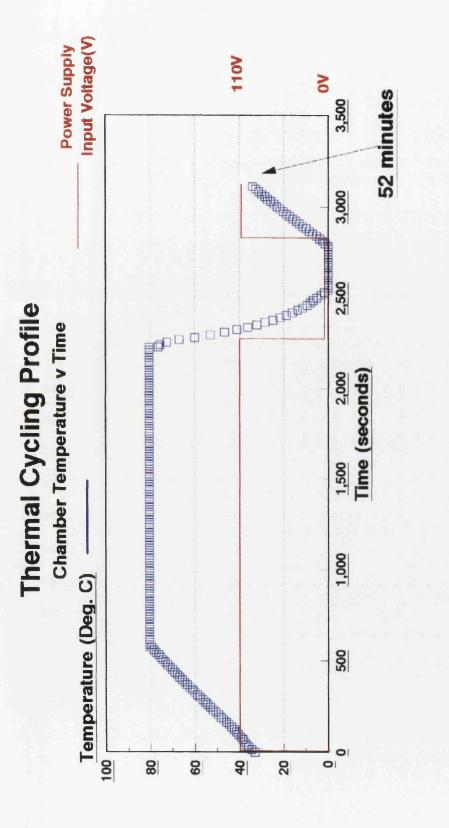

| 4.8   | 135     | Thermal Cycling Chamber Temperature        |

|       |         | Profile                                    |

| 4.9   | 137     | Thermal Cycling Capacitor Comparisons      |

| 4.10  | 138     | Results of Regulation and Ripple           |

|       |         | Measurements                               |

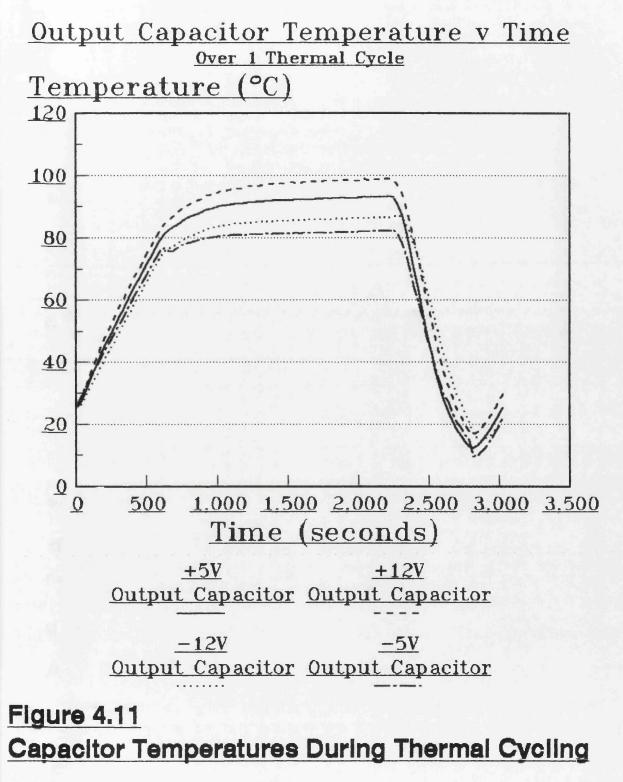

| 4.11  | 140     | Capacitor Temperatures During Thermal      |

|       |         | Cycling                                    |

| 4.12  | 141     | Thermal Cycling Acceleration Factors       |

| 4.13  | 142     | Capacitor Degradation During Thermal       |

|       |         | Cycling                                    |

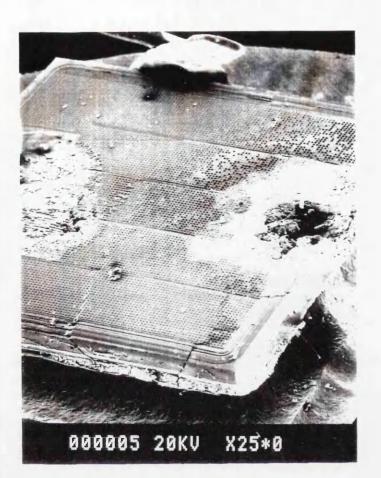

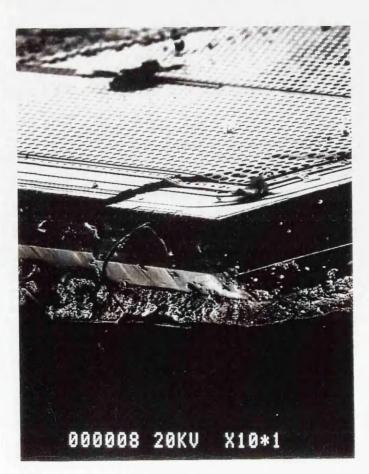

| 5.1(a | ) 147   | Undamaged FET                              |

| 5.1(b | ) 148   | Electrically Damaged FET                   |

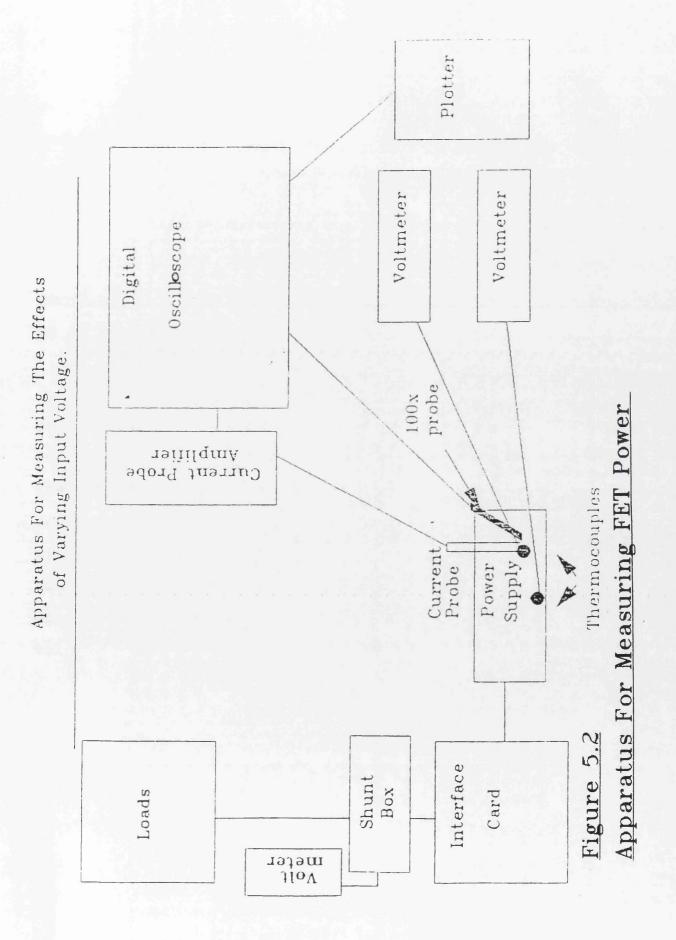

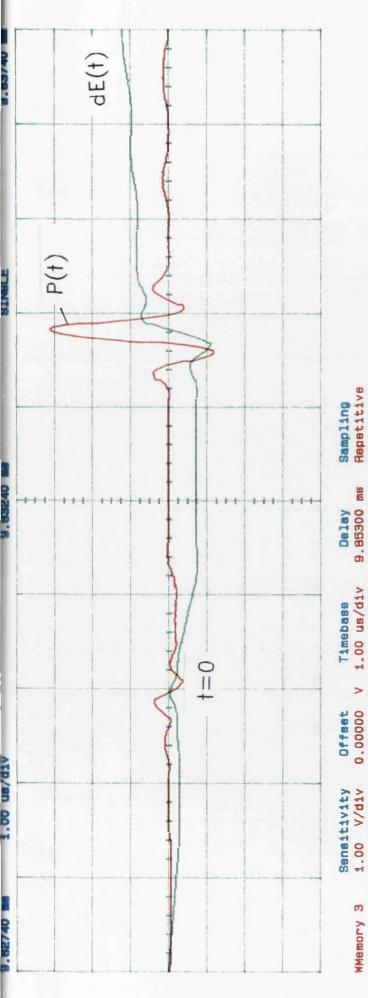

| 5.2   | 151     | Apparatus For Calculating FET Power        |

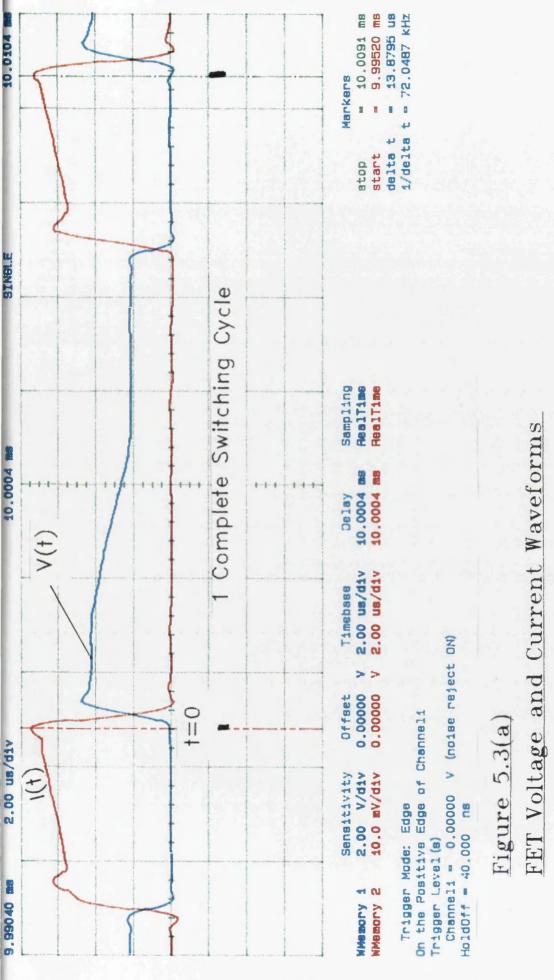

| 5.3(a | ) 153   | FET Voltage and Current Waveforms          |

| 5.3(b | ) 154   | FET Power and Energy Waveforms             |

| 5.3(c | ) 155   | Explanation of FET Power Calculations      |

.

| 5.4  | 157     | Triac Temperature v Input Voltage    |

|------|---------|--------------------------------------|

| 5.5  | 157     | FET Temperature v Input Voltage      |

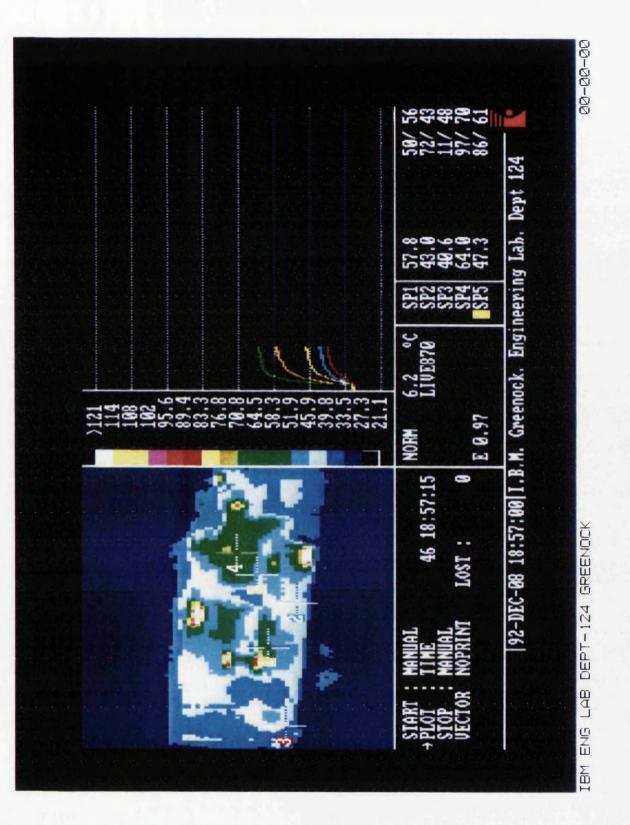

| 5.6  | 161     | Thermal Imaging Data                 |

| 5.7  | 162     | Thermal Imager Temperature Plot      |

| 5.8  | 164     | Component Temperature v Load         |

| 5.9  | 168     | Power Supply Ventilation System      |

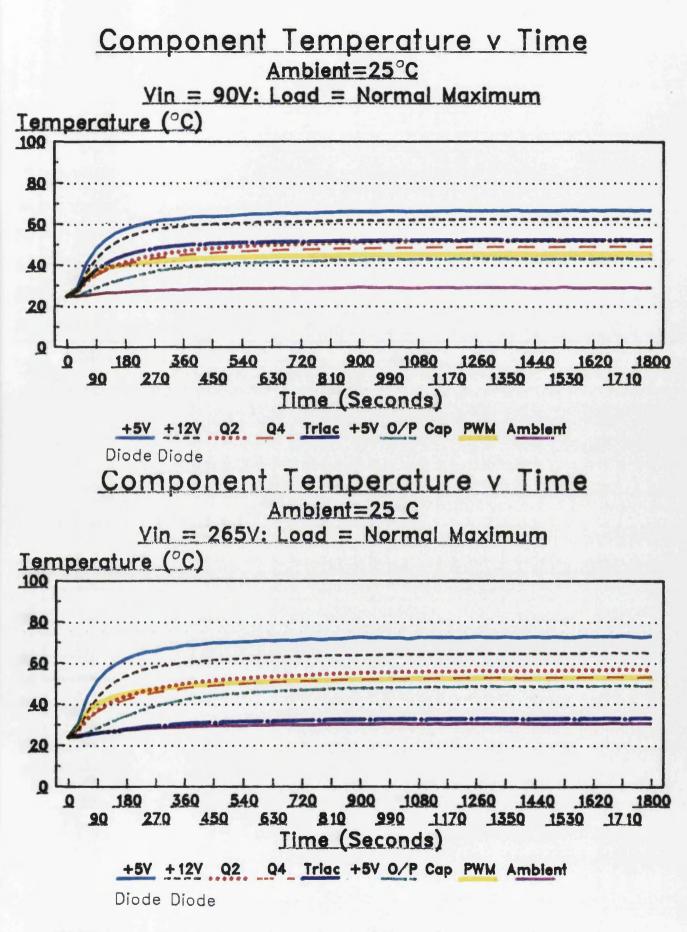

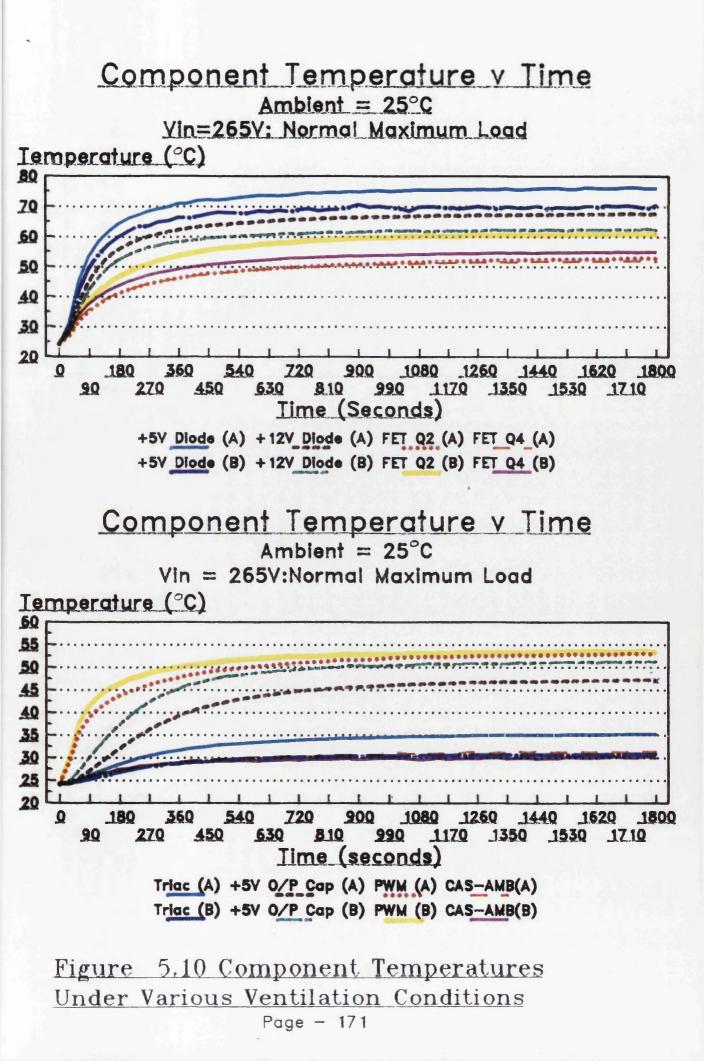

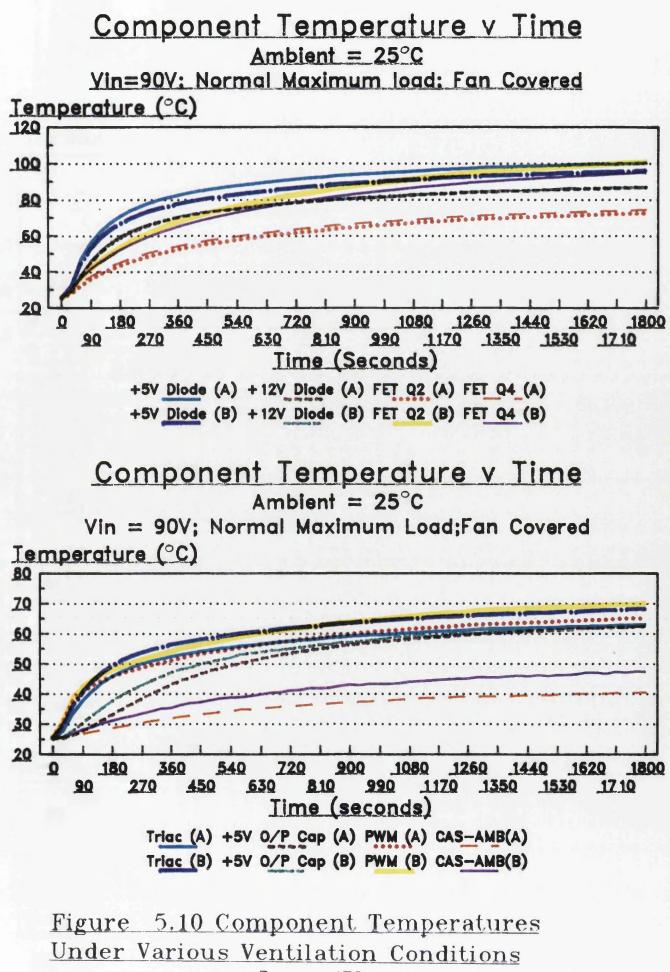

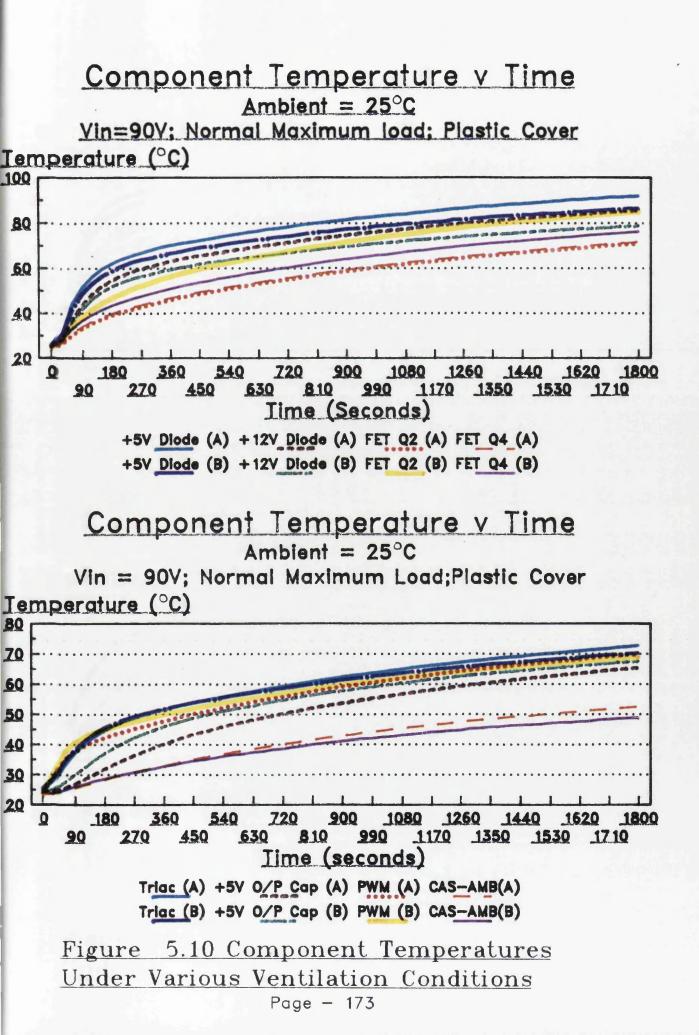

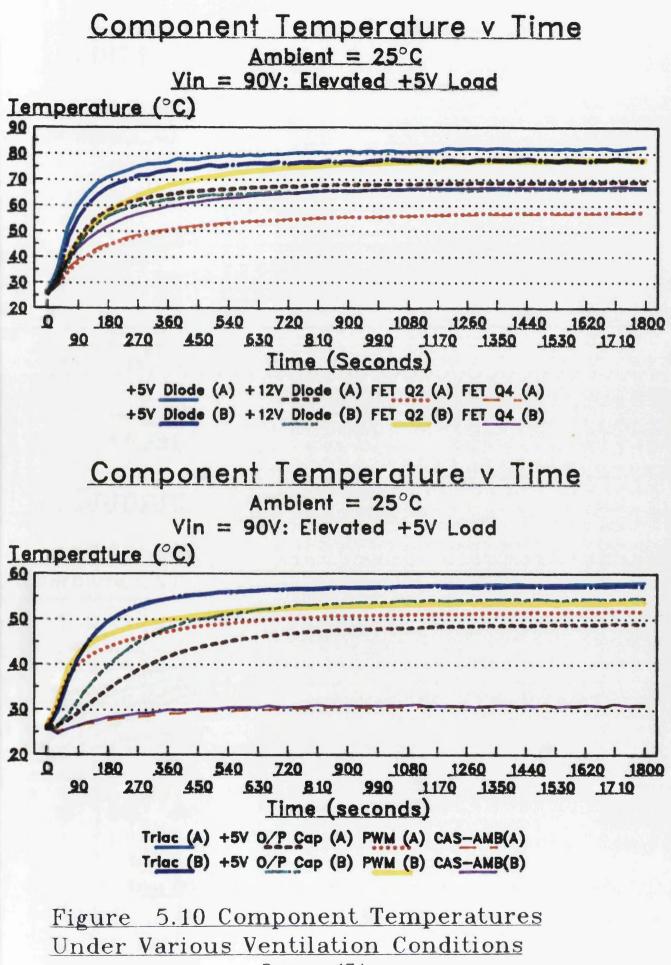

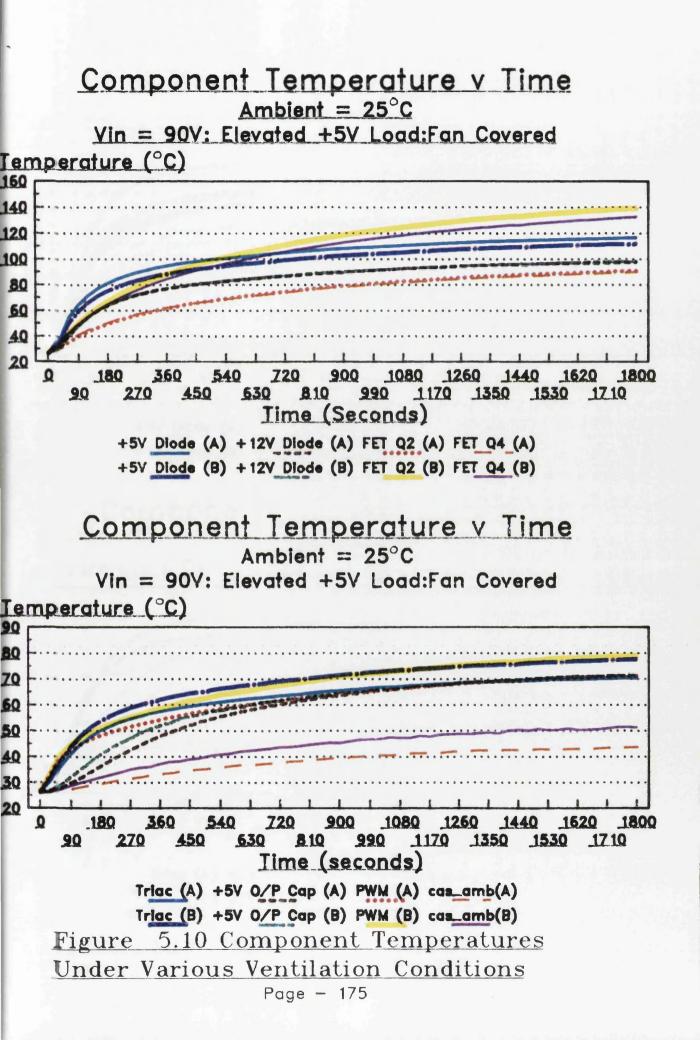

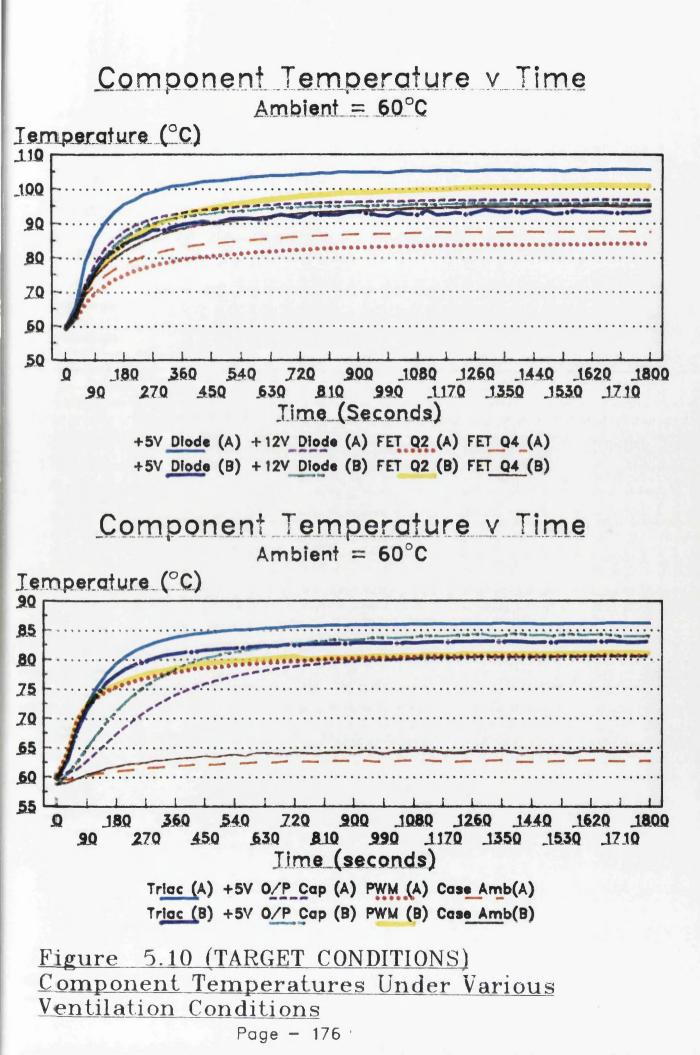

| 5.10 | 170-176 | Component Temperatures Under Various |

|      |         | Ventilation Conditions.              |

| 5.11 | 178     | Heat Damaged FET                     |

.

### Chapter 1: Introduction

### Section 1.1:Linear Power Supplies

Electronic equipment which is powered by connection to the mains supply usually requires circuitry to convert the high voltage A.C. into low voltage D.C.

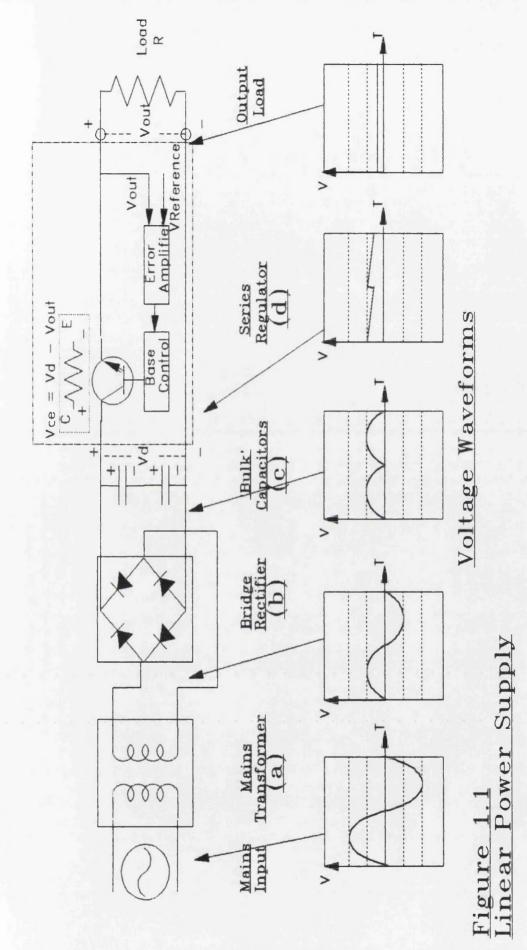

Traditionally this circuitry took the form of what is referred to as a linear power supply. Figure 1.1. is a block diagram of such a power supply.

The A.C. from the mains is passed through a step-down transformer (a). This reduces the voltage level from 240V to below 50V which is closer to the level required by devices such as transistors and integrated circuits, and is the region of 12-15V.

In some instances the equipment being powered will require voltages which are higher than that supplied by the mains e.g. D.C. voltages in the kilovolt range. In these cases a step-up transformer replaces the step-down transformer mentioned above.

The A.C. output of the transformer is made unidirectional, usually by a bridge rectifier (b). This, however, is still by no means the steady D.C. level required. The next stage of the circuit consists of large electrolytic capacitors (c) which smooth the output of the bridge rectifier and provide D.C. of an almost constant level. There is inevitably a degree of ripple voltage because it is unlikely that the capacitors will completely smooth the waveform.

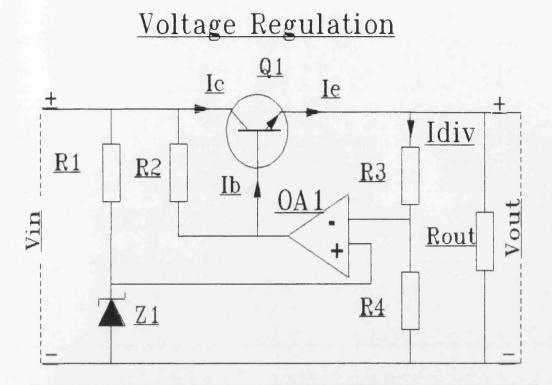

Transformers cannot be guaranteed to produce the correct voltage level at their outputs. This can be due either to variations in the mains supply or to the fact that the transformer may not be custom built to the application for which it is specific beina hazu Additionally the output of the power supply can fluctuate changes in the electronic circuitry due to being supplied. Such changes can be caused by, for example, resistors changing value as they heat up. It is therefore necessary to regulate the D.C. output. This is acheived by a regulator circuit (d) such as that in Figure 1.2. The regulator can take this discrete form or appear as a single Integrated Circuit (I.C.).

**Q: Transistor** Z: Zener Dlode **R: Resistor OA: Amplifier** Vin: Input Voltage **Vout: Output Voltage** Ic: Collector Current **Ib: Base Current B: Transistor Current Gain** le: Emitter Current Idly: Current through Voltage Divider

$IC = \beta x Ib$ le = lb + lcVout = (le-Idiv) x Rout Figure 1.2

Equation 1.1 Equation 1.2 Equation 1.3

Series Regulator

A fraction of the regulator's output voltage at the inverting input of a differential appears amplifier. The non-inverting input of the amplifier is supplied with a reference voltage at the level required by the electronic circuitry being supplied at the output; i.e. the load circuitry. The reference voltage is usually held at the correct level by a zener diode. The output of the amplifier is fed to the base of the transistor; the collector of which is supplied with the smoothed D.C. voltage. When the regulator output is too high the amplifier output falls and reduces the base current of the transistor, thereby reducing the collector current (equation 1.1), the emitter current (equation 1.2) and the output voltage (equation 1.3). When the output voltage level is too low the base current is increased.

In many cases the input voltage of the regulator can be more than 10V higher than the output. The excess created by this voltage and the current through the transistor can only be dissipated as heat and is therefore wasted energy. This, combined with losses in the large 50Hz mains transformer, make the linear power supply very inefficient. Typically the efficiency of a linear power supply is in the 30% to 60% range.

Additionally, due to the low frequency of the mains supply, the transformer and smoothing capacitors are very large which causes the linear power supply to be very bulky.

#### Section 1.2 Switch-Mode Power Supplies

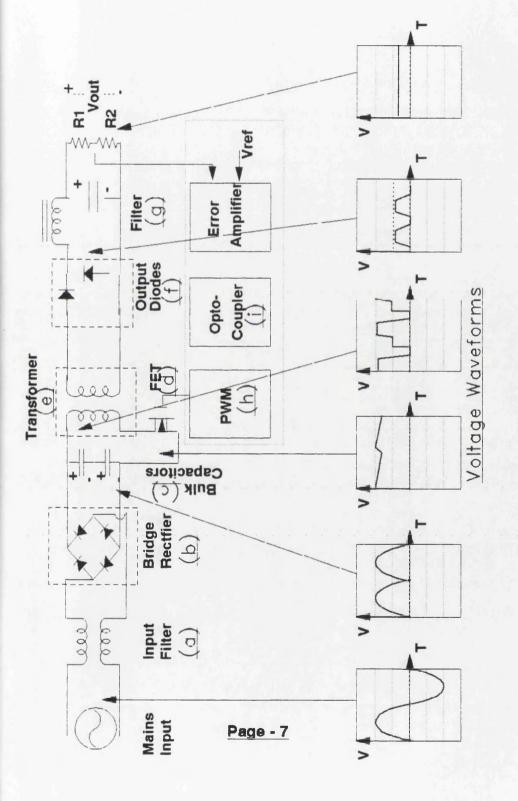

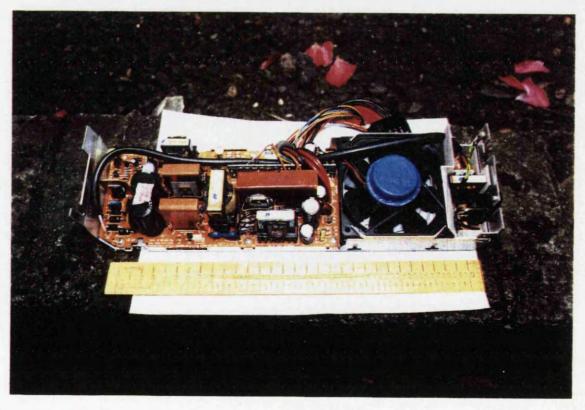

For the above reasons the linear power supply has been superseded by the Switch-Mode Power Supply(S-MPS) in the majority of mains powered electronic products. Figure 1.3 is a block diagram of this lighter and more compact type of power supply which uses a small, high frequency transformer but no mains transformer and is more than 60% efficient.

The input passes through a filter (a) to prevent any high frequency noise present in the mains voltage entering the power supply. This filter also removes the possibility of any noise from the power supply polluting the mains. The filtered voltage is then converted into unregulated D.C. using components (b), a bridge rectifier, and (c) two large capacitors which are commonly referred to as the 'bulk caps'. The voltage output of the capacitors is approximately 400V D.C.

# Figure 1.3 Switch-Mode Power Supply

Two capacitors are used because this allows the power supply to be used with different values of mains voltage. An explanation of how this is accomplished appears below in the section concerning the 'voltage doubling' circuitry.

This D.C. is then passed to a Field Effect Transistor (FET), component (d). This FET is the first component in the section of circuitry known as the DC to DC converter. There are several types of D.C. to D.C. converter. Each type operates in a similar manner to that described below but there are subtle differences in the way electrical energy is transferred from the input of the converter to its output. The D.C. to D.C. converter depicted in Figure 1.3 is known as a 'Forward Converter'. Other varieties of converter, i.e. converter topologies, include the Flyback and Cuk converters.

The FET acts as a switch and is controlled by component (h), a pulse width modulator (PWM). When the PWM output is high the FET is switched on and the switch is closed. This causes the D.C. level to appear at the primary of the step-down transformer, component (e). When the PWM output is low the FET is off and the switch is open. In this case OV appears at the transformer input. The FET is switched on and off at a frequency of 50kHz or above which is the frequency of the voltage waveform which appears at the primary of the transformer.

If this waveform were allowed to reach the mains there is a possibility that it could affect other equipment being powered by that mains supply. The aforementioned input filter (a) must prevent this signal from coming in contact with the mains waveform entering the power supply.

The inductive nature of the transformer changes the 'chopped' D.C. which appears at its input into high frequency A.C., with a magnitude of approximately 50V, which appears at its output. This is rectified by what are referred to as the output diodes, components (f), and smoothed by the filter (g) which consists of an inductor and capacitor(s). The inductor serves as the main energy storage device during the switching cycle because its very nature prevents rapid changes in the direction, and size, of the current flowing through it.

The regulation of the output voltage involves feeding back that output voltage to the Pulse Width Modulator. In order to maintain the primary:secondary isolation across the transformer , which is required to avoid the possibility of lethal voltage levels appearing at the outputs , this feedback is usually via an optocoupler. The level of output voltage will determine the voltage level at both sides of the optocoupler which will in turn determine the voltage measured by the PWM. If the output voltage level is too high, compared with the internal reference voltage of the PWM, the PWM decreases the duty cycle of the FET, i.e. the ratio of On Time:Total Switching Period. This results in a lower voltage at the output. If the output voltage is too low the duty cycle is increased.

If more than one D.C. output level is required, as is the case when the power supplies are used in computers where different voltages are needed for circuitry, disc drives and cooling fans, then the transformer used is one with multiple secondary windings. In some cases it is also necessary to provide series regulators, the same as those used in linear power supplies, to regulate the additional outputs. The need for these extra regulators is due to the fact that the PWM will be controlled by one output and will adjust the duty cycle according to the needs of that output. Even with different windings ratios on the transformer secondaries it will not be possible to achieve precisely all the various output voltages required and the extra regulators will ensure that all series supplementary output voltages are at the correct levels.

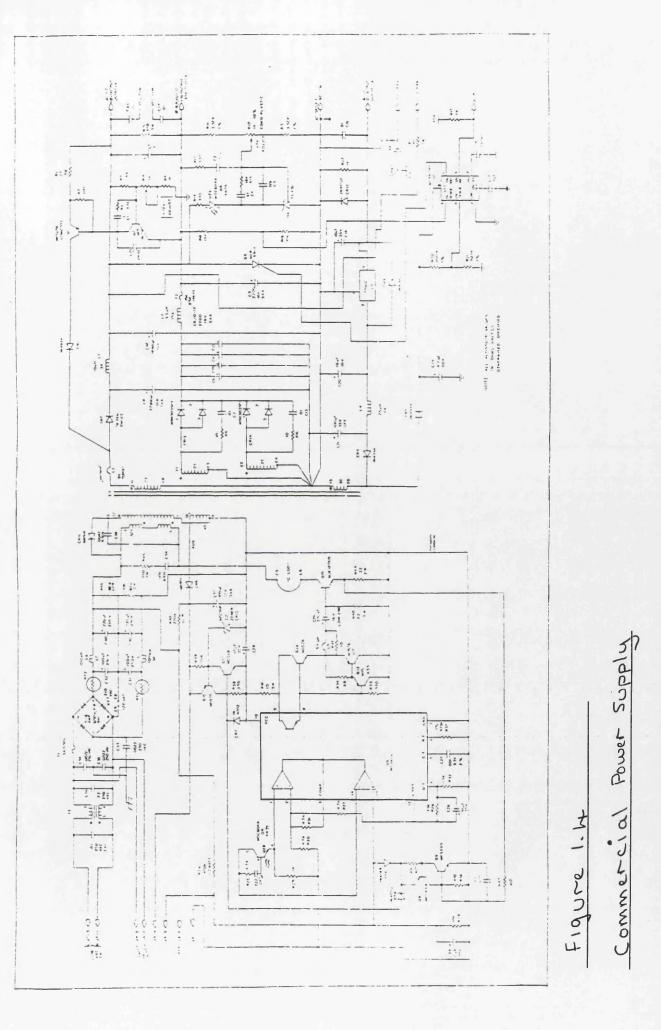

Figure 1.4 shows a circuit diagram of a commercial SMPS. The D.C. to D.C. converter, i.e. the circuitry described above, forms only a small part of the complete circuit. The other components serve, among other things, to protect the power supply from damage if a fault occurs at either the mains input , e.g. an excessive level of mains voltage, or at one of the outputs e.g. a short circuit.

### Section 1.3 Voltage Doubling Circuitry

In order to allow manufacturers of power supplies, or those of products which include power supplies, to export to a variety of countries commercial power supplies include components which allow the power supply to operate whether the input voltage is the 240V used in this country or the 110V used in The United States, France etc. This set of components is referred to as the 'voltage doubling' circuitry and forms the basis of Figures 1.5(a) and 1.5(b)

> indicates the path taken by current during the positive part of the A.C. cycle.

>> indicates the path taken by current during the negative part of the A.C. cycle.

> indicates the path taken by current during the positive part of the A.C. cycle.

# Figure 1.5 (b) Voltage Doubling Circuitry: Vin = 110V

In cases where the power supply can detect the level of input voltage being supplied the switch takes the form of a triac which conducts only if the mains voltage is above a certain level. In other cases the user is required to set an actual physical switch depending on whether the input voltage lies in the range which includes 110V, or that which contains 240V.

When the power supply is operating from 240V the bridge rectifier operates normally and all of the rectifed 240V is shared equally by the two bulk caps at all times. This situation is depicted by Figure 1.5(a).

If the input voltage lies in the lower range the switch is closed which causes one capacitor to be charged during the positive half of the a.c. cycle and the other to be charged during the negative half. This is the case in Figure 1.5(b). In both cases the combined voltage across the capacitors is in the region of 300V.

### Section 1.4: Performance Requirements

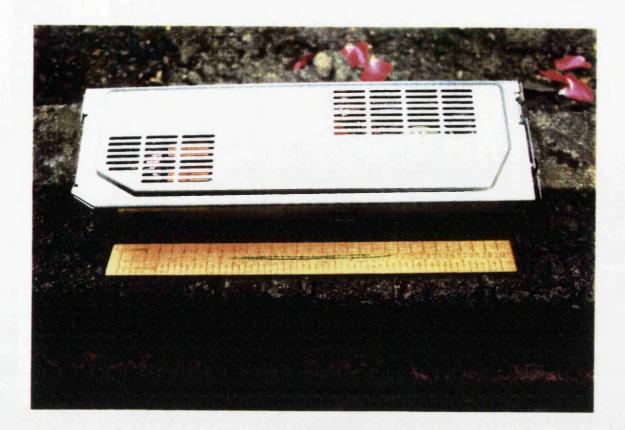

The power supplies which form the subject of this thesis are those used by IBM in computers. Most of the power supplies investigated were 118W power supplies i.e. a total of 118W could be supplied at the outputs for normal use. Samples are submitted for test, before power supplies are purchased from various vendors, to ensure that they meet the rigorous IBM specifications. Such a test can take twelve weeks. During that time the power supply is checked to ensure, for example, that it can shut down during a brief transient in the mains voltage.

An individual specification exists for every size and type of power supply IBM uses and, as well as stating the physical dimensions and performance crtieria of the power supply, contains precise details of tests which must be carried out on the power supplies together with acceptable quantatative results for these tests.

For the purposes of checking the effects of the processes documented in this thesis tests detailed in the relevant power supply specification were used. There are two areas of operation where any faults would be immediately obvious and most likely to affect the day to day operation of the equipment being supplied. The first of these is referred to as 'Regulation' and is the requirement that the voltage levels at the power supply outputs lie within the allowed ranges. The second parameter is the ripple voltage at the outputs. If the output voltage fluctuates too much due to the switching nature of the power supply then the equipment could fail to operate properly. It is the task of the filter capacitors to remove voltage ripple but there will always be a certain amount which will tend to increase as the capacitors age. Checks of regulation and ripple voltage, among other checks, formed an integral part of each of the tests documented in the pages which follow.

# Chapter 2- Reliability and Accelerated Life Testing

### (Relevant Background Theory)

### Section 2.1 Product Reliability

It is becoming increasingly important that equipment, both mechanical<sup>4</sup> and electronic, can be trusted to operate at all times under all conditions in which it is used. At one extreme the consequences of equipment failure could merely be inconvenient; in contrasting situations such failures could be fatal e.g. Failures in the control system of a nuclear reactor.

In addition to the safety aspect there are also cost considerations. There are two major instances in which unreliable equipment can incur considerable expense for the owner:

The first concerns equipment situated where the cost of access for repair or servicing is prohibitive e.g. underwater cables or satellites.

The second, and that which is probably more relevant to the subject matter dealt with in this thesis, is in manufactured goods which are covered by a warranty. If a company's product breaks down within the period covered by the warranty then the company must bear the expense of repairing or replacing that product. Obviously when large numbers of the particular product are being sold the cost involved can be considerable. Additionally if that company sells products which are inclined to fail after a relatively short period their reputation, and consequently their sales figures will suffer. Customers and will continue to, expect ever have come to, increasing ever increasing operational lifetimes for the products they buy.

For these reasons a great deal of industry time and money has been put towards the investigation of equipment reliability in an attempt to find ways of predicting and lengthening the life time of manufactured goods. In the course of these investigations certain parameters have been defined. The parameter most usually quoted in connection with the reliablilty of a device is the Mean Time To Failure (MTTF). This is a statistical measurement which is calculated by measuring the time to failure of as many samples of the device as possible and then calculating the average or mean of these.

Where a device or item of equipment is repairable the expression becomes Mean Time Between Failures (MTBF).

Regardless of which expression is used this parameter is usually represented by  $\theta$ . The expression population refers to the collection of sample devices used in the test.

It is common practice when investigating the reliability of a device to plot what is known as the 'Cumulative Distribution Function' (F(t) v t). Figure 2.1 gives a list of definitions. There are a variety of common cumulative distribution functions such as the Exponential, Normal and Weibull Functions.

Reliability Definitions and Equations

The model usually used with electronic assemblies, of which Switch-Mode Power Supplies are an example, is the Exponential function the equations for which are also given in Figure 2.1.

### Section 2.2: The Life of a Product.

It is a plot of h(t) v t which yields that which is probably the best known reliability curve, i.e. the 'Bathtub' Curve, which is shown in Figure 2.2.

The high initial failure rate is due to failure of products with manufacturing defects. It is common practice to age, or 'burn-in', products before they are sold in order that these failures occur while the product is still in the hands of the manufacturer. This all but eliminates the failures which occur in the field . i.e. when the product is with the customer.

As a result of burn-in the failure rate in the field should be constant, this is represented by the flat section in the middle of the curve. This period is known as the 'useful life'.

The final section of the curve is known as the wearout interval. As the products pass their useful life the number of failures starts to increase as the products literally wear out. This could be caused by, for example, corrosion of metal parts.

#### Section 2.3: Failure Rates and MTTFs

What a life test sets out to do is indicate the likelihood of a sufficiently high MTTF. The population undergoing life test will have passed through the burn-in process and should therefore have the constant failure rate of the 'useful life' section of the bathtub curve.

A typical MTTF for an S-MPS would be 50,000 hours, slightly over five years, but this requirement is increasing and it is not uncommon for a specification to demand an MTTF of 100,000 hours. Fortunately, because the failure rate is assumed to constant:

$$Ttotal = N * T$$

#### (Equation 2.5)

#### Where:

Ttotal = total test duration = total power-on Hours. N = number of units being tested. T = actual test duration = power-on hours per unit

This assumption of a constant failure rate has a very important consequence. It means for example, <u>that</u> <u>instead of testing 1 unit for 1000 hours it is possible</u> to test 10 units for 100 hours and make the same <u>statements about MTTF etc.</u>

It is customary when quoting failure rates/ MTTFs for a product to also give an associated confidence level. This is an indication of how accurate the MTTF figure is. i.e. the confidence levels give an indication of the uncertainty associated with the figure quoted for the MTTF. If an MTTF is stated with a confidence of 60% then this is equivalent to saying that 60% of the time the MTTF will lie within what is known as the confidence interval, a range of values surrounding the MTTF. The Chi-Square equation relates the number of units being tested to the confidence figure, the test duration and the failure rate.

$\tau = [chi-square(a, 2n+2)]/(2*N*T)$

(Equation 2.6)

The Chi-Square distribution gives a numerical value for each combination of confidence level and failures. A table of these values, such as that in Figure 2.3, can be found in most statistical and reliability texts. In certain cases the actual confidence level percentages or fractions are used for each column, in other cases (1-confidence level) is quoted. It is important to establish which is the case for individual tables.

|         |   |        |    | 0.5                 | 0.6    | 0.7   | 0.8   | 0.9   | 0.95  |

|---------|---|--------|----|---------------------|--------|-------|-------|-------|-------|

|         |   |        |    | % Confidence Levels |        |       |       |       |       |

|         |   |        |    | 50%                 | 60%    | 70%   | 80%   | 90%   | 95%   |

|         | 0 |        | 1  | 0.455               | 0.708  | 1.07  | 1.64  | 2.71  | 3.84  |

|         |   |        | 2  | 1.390               | 1.830  | 2.41  | 3.22  | 4.61  | 5.99  |

|         | 1 |        | 3  | 2.370               | 2.950  | 3.67  | 4.64  | 6.25  | 7.81  |

| -       |   |        | 4  | 3.360               | 4.040  | 4.88  | 5.99  | 7.78  | 9.49  |

|         | 2 |        | 5  | 4.350               | 5.130  | 6.06  | 7.29  | 9.24  | 11.10 |

| 3       |   |        | 6  | 5.350               | 6.210  | 7.23  | 8.56  | 10.60 | 12.60 |

|         | 3 | -      | 7  | 6.350               | 7.280  | 8.38  | 9.80  | 12.00 | 14.10 |

| 0       |   | La     | 8  | 7.340               | 8.350  | 9.52  | 11.00 | 13.40 | 15.50 |

|         | 4 | pa     | 9  | 8.340               | 9.410  | 10.70 | 12.20 | 14.70 | 16.90 |

| Salures |   | reedom | 10 | 9.340               | 10.500 | 11.80 | 13.40 | 16.00 | 18.30 |

| Ľ       |   | LL     | 11 | 10.300              | 11.500 | 12.90 | 14.60 | 17.30 | 19.70 |

| 5       | 5 | of     | 12 | 11.300              | 12.600 | 14.00 | 15.80 | 18.50 | 21.00 |

| La la   |   | rees   | 13 | 12.300              | 13.600 | 15.10 | 17.00 | 19.80 | 22.40 |

| Ō.      | 6 |        | 14 | 13.300              | 14.700 | 16.20 | 18.20 | 21.10 | 23.70 |

| Nurnber | 7 | 6ð     | 15 | 14.300              | 15.700 | 17.30 | 19.30 | 22.30 | 25.00 |

|         |   | 0      | 16 | 15.300              | 16.800 | 18.40 | 20.50 | 23.50 | 26.30 |

|         |   |        | 17 | 16.300              | 17.800 | 19.50 | 21.60 | 24.80 | 27.60 |

|         | 8 |        | 18 | 17.300              | 18.900 | 20.60 | 22.80 | 26.00 | 28.90 |

|         | 9 |        | 19 | 18.300              | 19.900 | 21.70 | 23.90 | 27.20 | 30.10 |

|         |   |        | 20 | 19.300              | 21.000 | 22.80 | 25.00 | 28.40 | 31.40 |

|         |   |        | 21 | 20.300              | 22.000 | 23.90 | 26.20 | 29.60 | 32.70 |

| 1       | 0 |        | 22 | 21.300              | 23.000 | 24.90 | 27.30 | 30.80 | 33.90 |

|         |   |        | 23 | 22.300              | 24.100 | 26.00 | 28.40 | 32.00 | 35.20 |

| 11      |   |        | 24 | 23.300              | 25.100 | 27.10 | 29.60 | 33.20 | 36.40 |

## **Chi-Square Values**

Figure 2.3 Chi-Square Values

Instead of looking along the row for the actual number of failures, it is necessary to check the row for the corresponding degrees of freedom (D.O.F) using the relationship:

$$D.O.F. = 2(n+1)$$

(Equation 2.7)

Where n = number of actual failures

Note that n+1 is used instead of n because it is customary to assume the worst case i.e. if the test had gone on any longer another failure would have occurred immediately.

Figure 2.4 lists the various ways in which failure rate figures can appear and indicates how one converts a failure rate given in one form into the equivalent figure in another form.

## **Failure Rate Conversion Factors**

| = F.R. * 10E+05 |

|-----------------|

| = F.R. * 10E+09 |

| = F.R. * 10E+12 |

|                 |

<u>Key</u> F.R. = Base Fallure Rate = 1/MTTF

%/K = Percentage failures per 1000 Hours\*

PPM/K = Parts per million failing per 1000 hours

PPB/K = Parts per billion failing per 1000 hours

FITS = PPM/K

MTTF = Mean Time to Failure

\*1000 hours of test Figure 2.4 Failure Rate Conversion Factors

#### Sample Calculation

<u>Target</u>: To calculate the time required to verify a failure rate of 0.2% per 1000 hours, with zero failures, 60% confidence and a population of 100 units.

From Figure 2.3 the chi-square value for this combination is 1.83.

The failure rate/P.O.H (F.R.) is 0.02/100000 = 2E-07T = <u>Chi-square (2,60)</u> = <u>(1.83)</u> = <u>4575 hours</u> (F.R \* N \* 2) (2E-06 \* 100 \* 2) <u>4575 hours = 190 days. (Approximately 6 months)</u>

#### Section 2.4: Accelerated Testing

The purpose of accelerated testing is to enable manufacturers to shorten the time required to test the MTTF of their products. This is achieved by subjecting the items being tested to stress levels higher than those they would experience while being used normally. e.g. if a resistor has a temperature of 30°C under normal use conditions then it could be tested at 50°C by placing it in an oven . Other parameters which could be raised include the voltage across a device and the current through it.

It is also possible to subject the products to stresses which change over a set period of time. e.g. The oven mentioned above could have a cycle which included higher and lower temperatures than a device would normally experience. A number of equations exist<sup>5</sup> which relate the failure rate at one level of stress to the failure rate at another. This allows failure data from units which are operated at a higher than normal stress to be used when calculating the MTTF of units operating at the levels of stress they would experience when being used normally.

N.B. Those stresses which are applied to a product for this purpose are known as Accelerating Stresses because they accelerate the life of the products subjected to them.

The failure rates at the two stress levels are related by:

F.R. (high stress) = A.F. \* F.R. (Normal Stress) (Equation 2.8)

Where F.R. stands for failure rate and A.F. for the value of acceleration caused by the stress used. This value is referred to as the Acceleration Factor.

Probably the most commonly used of these equations is the Arrhenius Equation, as given by Jensen<sup>5</sup>, which relates the MTTF/Failure Rate at one temperature to the MTTF/Failure Rate at another:

$t = A \exp[Ea/kT]$

(Equation 2.9)

Where: t = time to failure (Hours)

A = a constant relating to the cause of failure

Ea = activation energy i.e. The energy required

to cause failure (e.v.)

k = Boltzmann's constant.

T = absolute temperature (K)

The Arrhenius equation is used in conjunction with failures caused by chemical processes which can include corrosion, evaporation etc.

The Arrhenius acceleration factor<sup>5</sup>,  $K_{Arrhenius}$ , is calculated by dividing  $t_{low}$ , the time to failure at operating temperature  $(T_{low})$ , by  $t_{high}$ , the time to failure at high temperature  $(T_{high})$  Therefore:

K<sub>Arrhenius</sub> = t<sub>low</sub>/t<sub>high</sub> = exp(Ea/k)((1/T<sub>low</sub>)-(1/T<sub>high</sub>)) (Equation 2.10)

The other symbols are as defined above.

This value of acceleration factor can then be used to relate the failure rates, as in Equation 2.8, using the fact that.

F.R.(Tlow) = F.R.(THigh)/Karrhenius

The consequence of the above equations is that the Chi-square Equation can be applied to the results of a test carried out at high temperature to reveal the failure rate at that temperature. This failure rate can then be divided by the relevant acceleration factor yielding the true failure rate i.e. that which would occur in the field. Figure 2.5 shows a program which carries out all of the above process.

There are documented equations<sup>6</sup> for the other types of accelerating stresses which perform the same function for those stresses as the Arrhenius equation does for temperature stress.

10 'program to calculate actual failure rates 20 'based on Arrhenius 25 'COLLECT CHI-SQUARE DATA 30 DIM CHISQ(10,10) 40 FOR FAILS= 1 TO 10 50 FOR LEVEL = 1 TO 1060 READ X 70 CHISO(FAILS, LEVEL) =X 80 NEXT LEVEL 90 NEXT FAILS 95 COLOR 14,1 100 CLS 110 LOCATE 5,5: PRINT "Please Enter the desired confidence Level" 115 LDCATE 6,5:PRINT "(CHODSE FROM 10,20,30,40,50,60,70,80,90,95)" 120 LOCATE 7,5:INPUT "(Type the NUMBER and 'RETURN')";CONF% 130 LOCATE 10,5: INPUT "Please enter the number of failures which ocurred"; DEAD % 140 LOCATE 15,5: INPUT "Please enter the Total number of units on test "FOPLN% 150 LOCATE 20,5: INPUT "Please enter the Test Duration in hours"; TSTTM% 200 IF CONFX=95 THEN CONFX=CONFX+5 210 ALPHA=INT(CONF%/10):FREE=DEAD%+1 220 UPPER=CHISQ(FREE, ALPHA) 230 ACCFAIL=UPPER/(2\*POPLN/\*TSTTM/) 235 COLOR 11,4 240 CLS 300 LOCATE 5,5:INPUT "Please enter the stress temperature level (°C)";TSTRESS 310 LOCATE 10,5:INPUT "Please enter the operating temperature level (°C)";TNORMA L 320 LOCATE 15,5:INPUT "Please enter the activation energy (eV)";EACT 330 BRACKET=((1/(TNORMAL+273.15))-(1/(TSTRESS+273.15))) 340 INDPO=(EACT/8.617E-05)\*BRACKET 350 ACCFACT=EXP(INDPD) 360 OPFAIL=ACCFAIL/ACCFACT 365 COLOR 7,4 366 CLS 367 COLOR 14.3 370 LOCATE 7,5:PRINT "The failure rate under stress is: ";ACCFAIL; " per POH" 375 COLOR 15,1 380 LOCATE 14,5:PRINT "The actual failure rate is: ";OPFAIL; " per POH" 385 KPOH = OPFAIL\*100000!:FITS=OPFAIL\*1E+09 386 COLOR 14,2 390 LOCATE 16,5:PRINT "Which corresponds to ";KPOH;"%/1000 hours" 391 COLOR 14,5 395 LOCATE 18,5:PRINT "Which corresponds to ";FITS;" FITS" 396 COLOR 4,4 400 COLOR 1,4:LOCATE 20,5:PRINT "Do you wish to do another calculation (Y/N)?" 415 A\$=INKEY\$:IF A\$="" THEN GOTO 415 420 IF A\$="Y" OR A\$="y" THEN GOTO 95 ELSE GOTO 500 500 COLOR 7,0:CLS:SYSTEM

, Figure 2.5 (Programming Language: BASIC) Failure Rates Program Listing (Part 1)

Page - 35

- 1000 DATA 0.211, 0.446, 0.713, 0.102, 1.39, 1.83, 2.41, 3.22, 4.61, 5.99

- 1010 DATA 1.06,1.65,2.19,2.75,3.36,4.04,4.88,5.99,7.78,9.49

- 1020 DATA 2.2,3.07,3.83,4.57,5.35,6.21,7.23,8.56,10.6,12.6

- 1030 DATA 3.49,4.59,5.53,6.42,7.34,8.35,9.52,11.0,13.4,15.5

- 1040 DATA 4.87,6.18,7.27,8.3,9.34,10.5,11.8,13.4,16,18.3

- 1050 DATA 6.3,7.81,9.03,10.2,11.3,12.6,14,15.8,18.5,21

- 1060 DATA 7.79,9.47,10.8,12.1,13.3,14.7,16.2,18.2,21.1,23.7

- 1070 DATA 9.31,11.2,12.6,14,15.3,16.8,18.4,20.5,23.5,26.3

- 1080 DATA 10.9,12.9,14.4,15.9,17.3,18.9,20.6,22.8,26,28.9

- 1090 DATA 12.4,14.6,16.3,17.8,19.3,21,22.8,25,28.4,31.4

## Figure 2.5 Failure Rates' Program Listing (Part 2)

#### Voltage Acceleration Factor<sup>6</sup>

Kvoltage = <u>Voltage during Stress Test</u> Voltage when in use

(Equation 2.11)

$\frac{\text{Humidity Acceleration Factor}}{\text{K}_{\text{humidity}}} = \exp(0.00044) (\text{Rh}_{\text{stress}}^2 - \text{Rh}_{\text{use}}^2)$ (Equation 2.12) Where:  $\text{Rh}_{\text{stress}} = \%$  Stress Level of relative humidity  $\text{R}_{\text{huse}} = \%$  Normal/Use level of relative humidity (This is known as the 'Sim-Larson' Equation)<sup>6</sup>

#### Temperature Cycling

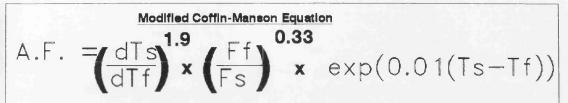

In the course of the project two possible equations have been found for an acceleraion factor for thermal cycling. The first of these is the Modified Coffin-Manson Equation<sup>6</sup>

$$K_{\text{Thcyc}} (dTs/dTf)^{1.9} * (Ff/Fs)^{0.333} * exp(0.01*(Ts-Tf))$$

(Equation 2.13)

#### Where:

dTs = Temperature Range of Laboratory Stress cycle

| dTf | = | Temperature Range in Field          |

|-----|---|-------------------------------------|

| Ff  | = | Cycle Frequency in Laboratory       |

| Fs  | = | Cycle frequency in Field            |

| Ts  | ÷ | Max Temperature of Laboratory Cycle |

| Tf  | = | Max Temperature of Field cycle      |

The Thermal cycling test is the main test for checking solder joints and is a standard part of the burn-in process along with vibration testing. Another possible equation for thermal cycling was that proposed by Nachlas<sup>7</sup> based on a cycle such as that in Figure 3.6 which includes separate integrated factors for the high temperature section and the ramps and has the form:

A.F. =

$$\frac{1}{t_3} \begin{cases} t_3 \\ [exp{[EaT(t)/K][(1/To)-1/T(t)]-\phi{DT(t)/dt}] \\ 0 \end{cases} \end{cases}$$

(Equation 2.13)

Where  $\phi$  is a constant relating to the ramp stress and DT(t)/dt is the ramp rate of change of temperature.

To = temperature at the start of the temperature ramp T(t) = temperature at time t Ea = activation energy

K = Boltzmann's Constant

DT(t)/dt = rate of change of temperature at time t.

Ta = Temperature During High Temperature Dwell

# Figure 2.6

**Typical Thermal Cycling Test Profile**

#### Section 2.5: Activation Energy

Several of the equations above, in which the accelerating stress is temperature based, make reference to what is known as the Activation Energy i.e. the energy required to initiate the process which causes failure.

Obviously different processes have different activation energies this means that one must talk about the activation energy of a process rather than that of a component which could have a number of chemical processes associated with it. e.g. One quotes the activation energy of corrosion of a capacitors leads rather than the activation energy of a capacitor which could also fail, in the case of an electrolytic capacitor, through evaporation of the electrolyte. This is a different process with a different activation energy.

In order to arrive at a value for activation energy for a process it would be necessary to compare failure rates at different temperatures but with the same failure mechanism.

It is for this reason that stress levels have to be carefully controlled. There is nothing to be gained in placing the samples in a temperature of 200°C if they fail due to a process which could never have occurred in the range of temperatures they would be expected to deal with when in normal use. It is even possible that if a very high temperature causes one such unrealistic failure mode to manifest itself in a relatively short period this could hide a failure mode which happens at operating stress but had not yet caused failure at the higher stress. When an activation energy is quoted for a component it will be the activation energy of the most likely cause of failure.

In the case of electronic assemblies which contain a multitude of different components with various failure modes it is not always possible to know the relevant activation energy in advance. This is especially true when dealing with a wide variety of different samples. (a range of power supplies from a variety of manufacturers are tested in the laboratory. The MTTF's are so large that it would be impractical to derive an activation energy using the method described above. It is important to point out that a power supply will fail because one or more components fail. Apart from electrolytic capacitors which can dry out components fail for one of two reasons:

(1) The component is faulty. ( The fault may take years to cause failure)

(2) The component is overstressed (The wrong component has been used for a particular application. i.e. failure is due to a design fault.)

When dealing with electronic assemblies it is common practice to work with an average activation energy. The value used in the laboratory is 0.6 eV which emerged from work done by another laboratory , namely the Product Quality and Reliability Laboratory, on electronic assemblies. Values commonly quoted for assemblies range from 0.4eV to 1.00eV. Obviously if a test was started and some failures occurred due to one process with a known activation energy that value could be substituted in place of the 0.6 eV. Jensen<sup>5</sup> suggests 0.4eV and some manufacturers prefer this more pessimistic value.

#### Section 2.6: Alternative Means of Reliability Assessment.

Another means of arriving at an MTTF for a device is by working out a weighted average based on the number of each type of component and the activation energy of the failure mode usually associated with that component.

Many companies, instead of checking assembly reliability by means of life testing, use the published failure rates for each component, muliplied by the number of components of that type, to arrive at an overall failure rate for that component. All of these failure rates are then added together to give a failure rate for the complete assembly.

The above approach is that documented in Mil-Hdbk 217<sup>8</sup>, a system developed to give reliability guidance for usage of components in military equipment from the point of view of maintainance and spares. The main problem with this system is that the published failure rates are not always accurate and this inaccuracy during multiplication the increases process. Additionally, the failure rates are quoted for particular levels of voltage, temperature etc. so in order to use them in a real situation the actual values of voltage and temperature would have to be measured and the failure rates adjusted accordingly. In a complicated device this could prove impractically time consuming. However one of the main advantages of this Mil-Hdbk method is that it allows manufacturers to compare like with like and, in the event of field failure, gives an indication of which component is most likely to have failed. This knowledge can lead to a reduction in repair time.

Manufacturers now tend to prefer life testing for reliability verification. Not only is it a practical test of the actual products involved it can also reveal potential problem areas. For example if a component fails during a life test at a temperature only slightly above that at which it is expected to operate then that component is one that could cause problems in the field and the manufacturer would be wise to replace it with a component which gives a wider safety margin for the particular application involved.

Perhaps the essence of Reliability and Life Testing is best captured in that statement from Dummer and Winton<sup>4</sup> which reads "Very often the goal is to show that a device is reliable enough to meet some mission requirement; this is somewhat different from needing to know, with maximum precision, the device reliability."

#### Chapter 3-The Effect of Elevated Ambient Temperatures

Section 3.1: Current Laboratory Practice

The method currently used for testing S-MPS in the Engineering Laboratory at IBM consists of running the power supplies for three months in an environment where the air temperature is 60°C i.e. the power supplies are operated in a 60°C ambient. In normal use the power supplies would operate in a 25°C to 35°C ambient. The power supplies spend 45 minutes of each hour switched on and the other 15 minutes switched off. This cycle also ensures that the power supply can endure the requisite number of on/off cycles. The MTTF for the power supplies is \*500,000 hours at an operating temperature of 35°C.

Figure 3.1 shows how this figure is converted to calculate the time required to test 20 power supplies at 60°C.

This part of the thesis deals with the tests that were performed in an attempt to discover whether these life tests currently conducted at 60°C could be carried out at a higher ambient temperature. A higher Temperature would bring a higher acceleration factor and therefore a reduced test time.

\* SPECIFIED AS

Sample Acceleration Factor Calculations <u>60 C Power Cycling</u> (Assume 60% Confidence) Number of Units Tested = 20 MTTF = 500000 hours Failure Rate = 2e-06 Number of Failures = 0 Chi-Square = Chi-Square(2,60%) = 1.830  $T = (Chi-Square(2,60\%)) = \frac{1.83}{0.00004}$

Test Length at Ambient Temperature = 22875 hours

Arrhenius Equation A.F. = exp{(Ea/k)((1/Tf)-(1/Ts))} Tf = Tfield = Tlow; Ts = Tstress = Thigh

### Ea = 0.6eV; k= 8.617e-05

Tfield = 35°C = 308.15K; Tstress = 60°C = 333.15K

$A.F. = \exp\{(0.6/8.617e-05)((1/308.15)-(1/333.15))\}$

$= \exp((6963) * (2.435e-04)) = \exp(1.69) = 5.42$

Test Length at  $60^{\circ}C = \frac{22875}{5.42}$  hours

Test Length at 60°C = 4220 hours = 175 days

Figure 3.1 'Normal' Power Cycling Acceleration Factor

#### Section 3.2

#### Highest Possible Operating Ambient Temperature

In order to obtain some idea of the maximum ambient temperature in which the power supplies would actually function it was decided to place four power supplies in an environmental chamber and gradually increase the ambient temperature until the power supplies stopped operating, either by shutting themselves down or by failure through actual damage.

The ambient temperature was increased in 10°C steps from 50°C. At each stage the power supply was powered on for 30 minutes. This allowed the various parts of the power supply to reach the temperature of the surroundings and ensured, in each case, that the power supply would run at that level of ambient temperature.

The power supplies operated for the full 30 minute period at temperatures of up to and including 100°C but when the temperature was increased to 110°C the power supplies shut down 5 to 10 minutes after they were switched on. A similar shut down ocurred at 105°C. This seemed to suggest that the power supplies involved would operate in temperatures of up to and including 100°C.

N.B. Although the power supplies shut down after a few minutes operation at temperatures above 100°C that shutdown was due to the power supplies' self-protection circuitry rather than being a result of damage. This is supported by the fact that the power supplies ran for an indefinite time when the ambient temperature was reduced which would not have been the case if the high temperatures had resulted in damage.

The operating specification for the 118W power supplies used demands that they operate normally in temperatures of up to 50°C. When the above test was being planned it was with a view to carrying out long term tests which would involve operating the power supplies for a prolonged period at 10°C below the maximum temperature at which they would function. At that time it was expected that the maximum temperature would be in the region of 80°C - 90°C. Since the tests documented in this thesis were being carried out with the ultimate aim of using them on a large scale it was necessary to take into account the thermal chamber which would be used if a large number of power supplies were to be tested simultaneously. Since the maximum temperature attainable by that chamber is 75°C It was decided to run the aforementioned long term tests at 75°C rather than the 90°C which was suggested by the fact that the power supplies would function in an ambient of 100°C. 75°C allowed for an adequate safety margin between the actual ambient for the test and the maximum abmbient in which the power supplies had operated.

#### Section 3.3: Temperatures of Individual Components

A power supply consists of a series of discrete electronic components all with different actual and maximum operating temperatures. The designer of a power supply will choose components which not only fulfill the required function for their position in the power supply but do so without exceeding their maximum rated values for voltage, current, power and temperature.

If a life test resulted in the components operating at temperatures which exceded their maximum rated values the result could be unrealistic failure modes due to components being overheated.

For this reason it was decided to measure the temperature of various components within the power supply at various values of ambient temperature and compare the operating temperatures at each value of ambient temperature.

These measurements were carried out with three main objectives in mind.

1) To discover the operating temperatures of the principal components of a S-MPS.

2) To establish the existence, or lack thereof, of a connection between the temperatures of the individual components and the ambient temperature of the power supply's operating environment.

3) To find out if it is possible to predict the maximum temperature in which the power supply can operate, without the internal components exceding their maximum temperature, by measuring the temperatures of these components while the power supply is operating at room temperature. The components used for these checks were as follows:

The two switching FETs The Voltage Doubling Triac The +5V and +12V Channel Output Diodes. (The above components are all mounted on heatsinks)

The Pulse Width Modulator chip. One +5V channel Output/Filter Capacitor The Air Temperature inside the power supply case.

Two power supplies were chosen and thermocouples were attached to these components in each power supply. The power supplies were switched on in an ambient temperature of 25°C ,i.e. on the bench, for 30 minutes and during this time the thermocouple outputs were stored at 30 second intervals by a data logger. The ambient temperature of the air surrounding the power supplies was logged along with the other temperatures.

These measurements were repeated in ambient temperatures of 50°C, 60°C, 75°C, 90°C and 100°C and the resultant plots of the logged thermcouple temperatures appear in Diagram 3.2.

Figure 3.2 Component Temperatures At Various Ambients

Between each of the elevated temperature stages the power supply was checked for damage by measuring the regulation and ripple voltages of each output channel. This was to ensure that temperature changes were authentic and not due to component damage. The voltages of several of the power supply outputs were also logged, by the datalogger, throughout the test

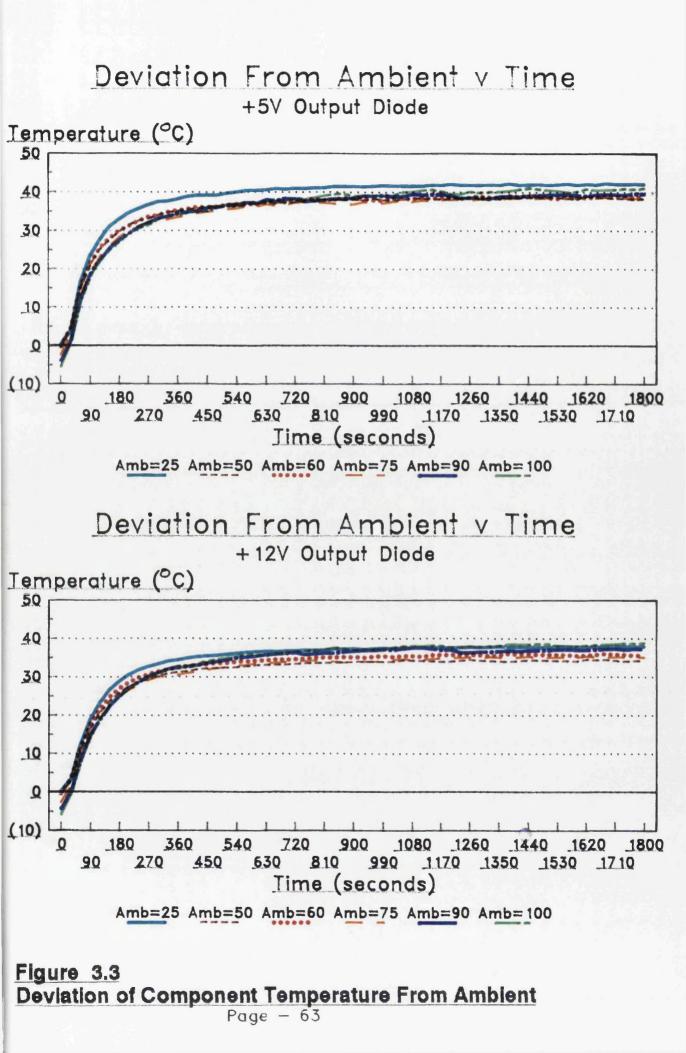

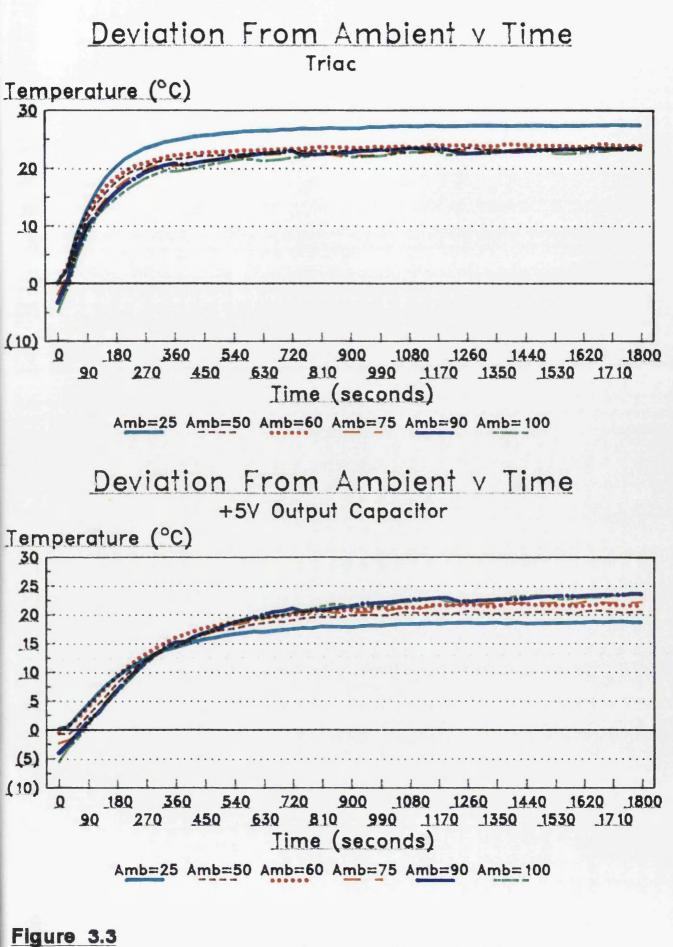

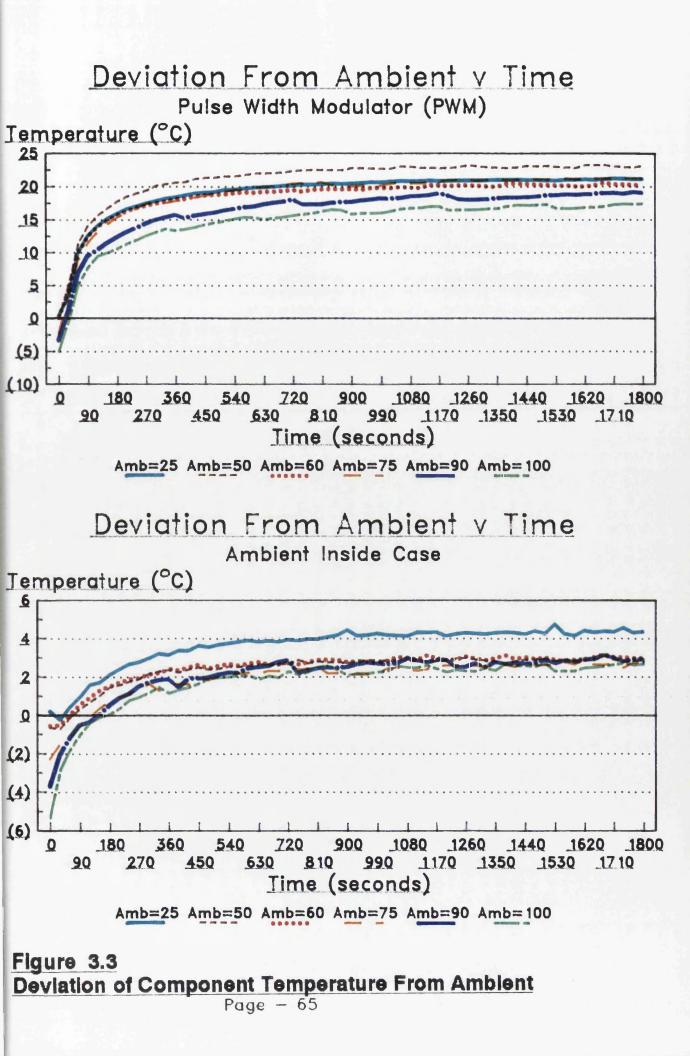

In order to examine the possibility of a relationship between component temperature and ambient temperature plots were also made of average deviation of component Temperature from ambient temperature versus time. These were produced using the temperatures logged for the previous section and form the basis of Figure 3.3. The graphs indicate whether the deviation of component temperature from ambient temperature is dependent on the ambient temperature.

Figure 3.3 Deviation of Component Temperature From Ambient Page - 62

is worth noting that this test It was originally carried out with one power supply. On that occasion the temperatures recorded for the components mounted on heatsinks were exceptionally low when compared with those seen during the observations of warm up after the power supply was switched on. It was discovered that this was due to the adhesive which had been used to attach the thermocouples to the components. This adhesive is thermally conductive and the had been applied in such a way that it increased the surface area of the component which was in contact with the heatsink. The consequence of this was that more of the components heat was being lost through conduction than would ordinarily be the case and the component temperature was lower than it would actually be in normal circumstances. For this reason it would seem advisable to work with the worst case, i.e. highest, actual temperatures recorded for each component in the two power supplies.

In these tests the comparisons of the average results are still valid because if there was an error due to this kind of measurement problem it would be present at all the ambient temperatures and therefore cancels out when the deviations from each value of ambient temperature are compared with each other.

On examination of the graphs in Figure 3.3 it would appear that the assumption which has previously been made in the lab. i.e. if the ambient temperature is increased the temperature of the components changes by the same amount, is, on the whole, valid. There are, however, certain points which should be taken into account.

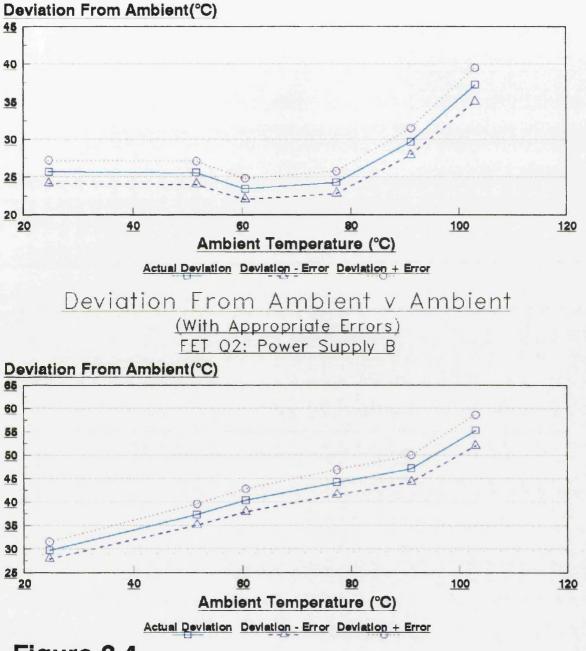

In the case of the FETs it would appear that as the ambient temperature is raised so is the deviation from ambient. For FET Q2 the built in 3% error in the thermocouples causes a 6% error in the deviation from ambient. The graphs in Figure 3.4 show the "Deviation of Average Final Temperature From Ambient Temperature v Ambient Temperature", with associated error. The final temperatures being the temperatures of FET Q2, in power supplies A and B respectively, 30 minutes after the power supplies were switched on.

### Deviation From Ambient v Ambient (With Appropriate Errors) FET Q2: Power Supply A

Figure 3.4 FET Q2; Deviations From Ambient Temperature

As can be seen from the graph for FET Q2 in power supply A when the associated 3% thermocouple errors are taken into account the assumption that the deviation from ambient temperature is constant appears to be true for ambient temperatures up to approximately 70°C. At above 70°C the ambient temperatures deviation of component temperature from ambient temperature increases the ambient temperature increases. Unfortunately, as however, this trend is not reflected in the measurements taken for the corresponding component in power supply b.

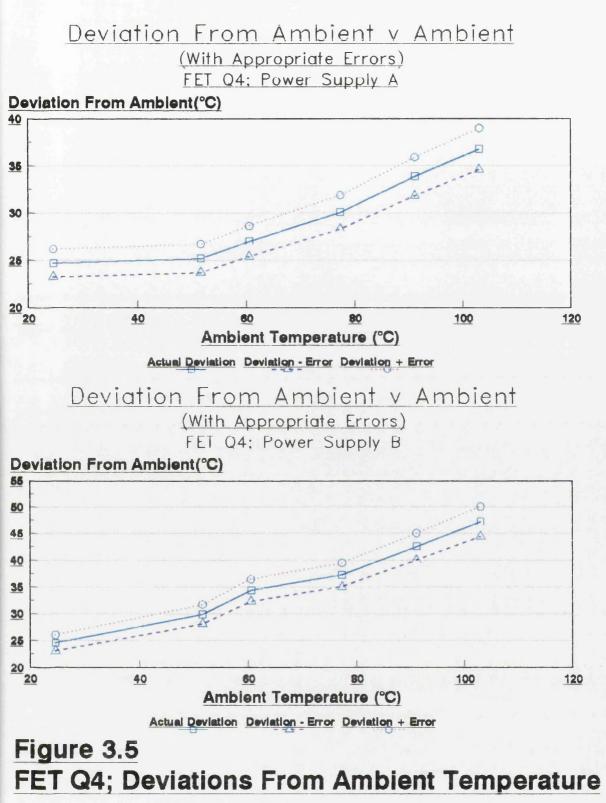

graphs in Figure 3.5 The show the distributions in the case of FET Q4. With this component, even when thermocouple errors are taken into account, the deviation of component temperature from ambient temperature tends to increase with ambient temperature over the complete range of ambient temperatures used. An error of 20% would be required for the assumption to hold at ambient temperatures of up to 75°C.

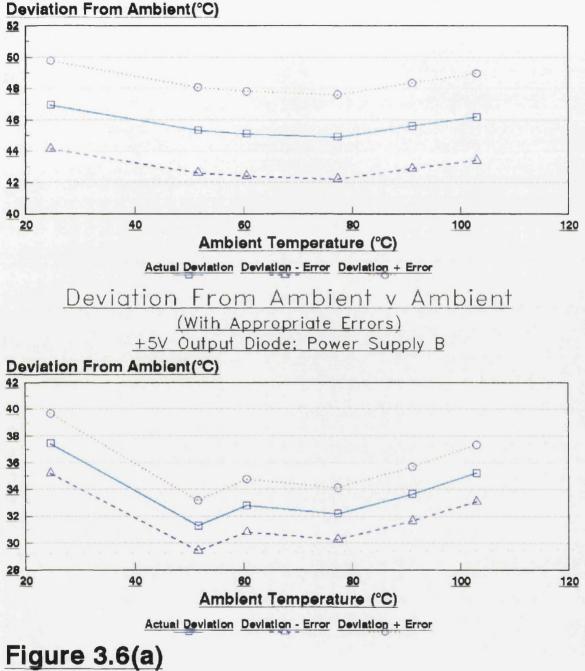

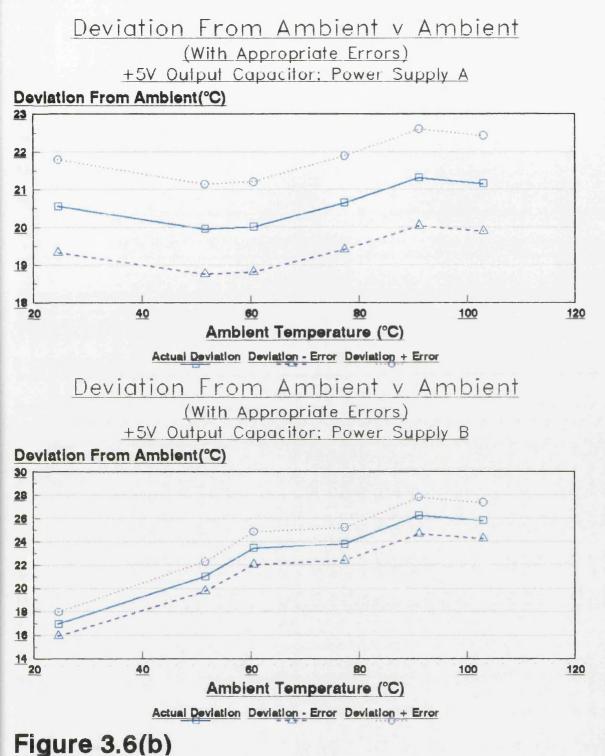

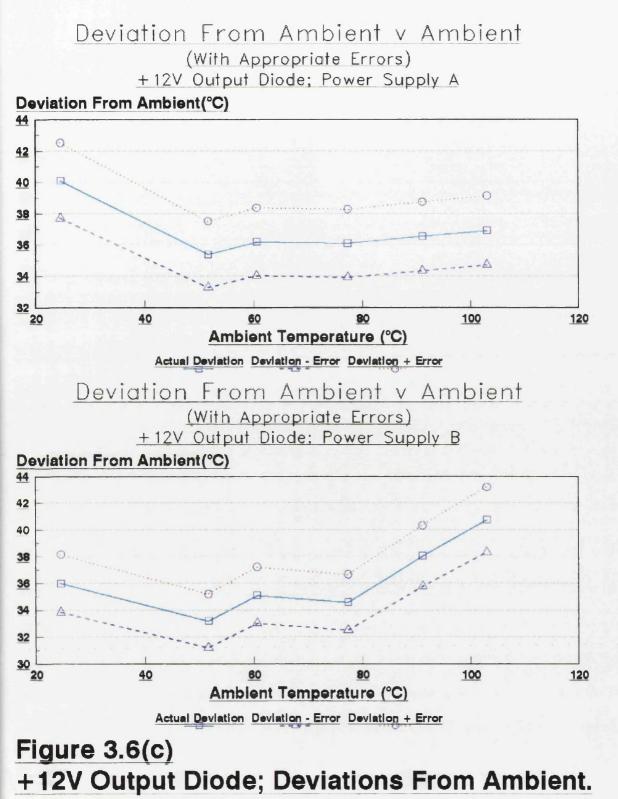

The deviations for the FETs show the widest spread of all the components. On examination of the +5V Output Diode it can be seen that there is almost no change in the deviation from ambient temperature across the 25°C to 100°C range of ambient temperatures. This trend is, on the whole, reflected in the behaviour of the other principal components. The various parts of Figure 3.6 show, with appropriate errors the deviations from ambient, at each of the temperatures used, for the main components tested.

The ambient inside the case was measured mainly to find out its actual value from the point of view of correcting for the plastic cover used during thermal imaging. It would seem that the ambient inside the case is between 2.8°C to 4.2°C above the temperature of the power supply's surroundings.

### Deviation From Ambient v Ambient (With Appropriate Errors) +5V Output Diode: Power Supply A

+5V Output Diode; Deviations From Ambient.

# +5V Output Cap'r; Deviations From Ambient.

Figure 3.7(a) shows the average value of the +5V output of the power supplies during the various high temperature tests. The main purpose of logging the output voltages was to reveal whether the voltages became unstable, or had values outwith the specified limits at any particular value of ambient temperature. Neither phenomenon is apparent in the case of the +5V output. The +12V and -12V outputs, as shown in Figure 3.7(b) showed some fluctuation but remained within their specified limits.

## Output Voltage v Time +5V Output

Averaged +5V Output Voltages Page - 78

#### <u>Conclusions</u>

The initial assumption, which was that a change in the temperature of a power supply's environment causes an equivalent change in the individual component temperatures, would, on the whole, appear to be valid up to an ambient temperature of 75°C for most components provided the measurements include the built-in errors of the thermocouples. The exception to this is the FETs where the deviation from ambient increases with ambient temperature. The worst case is FET Q4 where it would seem that the assumption would hold if the error in the deviation were increased to 17%. Such an assumption would allow component temperatures at higher ambients to be predicted if their values at a 25°C ambient were known. Although this assumption appears to be valid; if it were to be a critical factor in a test further verification would be advisable.

If the failure of the FET temperatures to follow the trend exhibited by the temperatures of the other components were due to a systematic error in the measurement of the FET temperatures; and if this error could be found and eliminated, then it is possible that the FET temperatures would mirror the trend adopted by the temperatures of the other components.

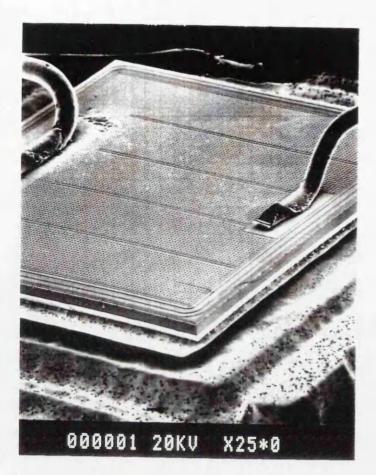

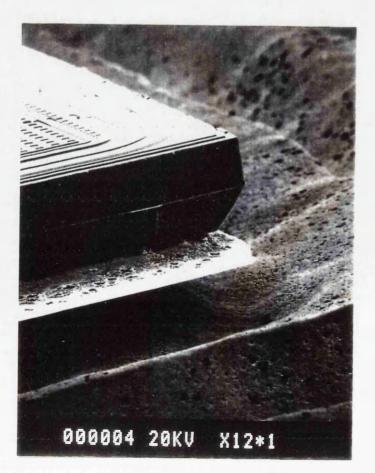

#### Section 3.4: Temperature Analysis By Thermal Imager

If it were decided in the future to make use of the aforementioned trends to establish the maximum, safe operating ambient temperature for a previously untested power supply then it would perhaps be worth investigating the accuracy with which the temperatures of individual components could be measured using a thermal imager.

Each power supply which comes into the laboratory undergoes thermal analysis as a matter of course and if the relevant temperatures could be determined with sufficient accuracy in this manner then there would be no need for the time consuming task of attaching thermocouples to components.

#### Section 3.5: The Effect of Elevated Temperature on

#### Electrolytic Capacitors

This set of tests came about from an interest in the possible use of measurements made on the electrolytic capacitors to give an idea of true test lengths.

The thinking behind this was as follows: If a direct relationship could be found between capacitor weight loss and time under test at different temperatures then it should be possible to use before and after weights from capacitors involved in the life test to give a true idea of the actual life test length by knowing how long it takes for such a weight loss to take place under the conditions experienced by the capacitor both while in test and while in actual use.

Figure 3.8 shows published manufacturer's data in the form of tables relating capacitor weight loss to useful life at various operating temperatures. One of the main purposes of this experiment was to see if those results could be reproduced.

Figure 3.8

<u>Manufacturer's Capacitor Degradation Data</u> Page - 83 Additionally, since the cause of the weight loss is a specific process i.e. evaporation of capacitor electrolyte, the activation energy of this process could be used with the Arrhenius equation to give an acceleration factor for the test used. Figure 3.9 demonstrates how the activation energy can be calculated from the manufacturer's data. In this case the energy is that required to evaporate a certain mass of electrolyte.

There is another possible use of data relating to electrolytic capacitors: A typical capacitor life is in excess of 80,000 hours at 55°C. At present power supply MTTFs are in the region of 50,000 hours at 35°C. (35°C being the ambient temperature inside the case of an operating computer)

If the power supply was tested to the point where the capacitors had undergone 80,000 hours at 35°C, i.e. had demonstrated weight loss corresponding to 80,000 hours at 35°C, or the accelerated equivalent, and the power supply had not failed then The MTTF target would seem to have been satisfied.

### Electrolytic Capacitor Activation Energy

(Activation energies refer to the energy required

per molecule to participate in a reaction)

Weight Loss is directly proportional to reaction

rate as given by the Arrhenius Equation:  $K = A \exp(-E/kT)$

Therefore:  $W(t) = B \exp(-E/kT)$

Where W(t) is the weight loss after t hours at a temperature of TK

W1(t) = B exp(-E/kT1)W2(t) = B exp(-E/kT2)and W1(t) = 2 \* W2(t)

then 2 =  $(\exp(-E/kT1)/\exp(E/kT2)) = \exp(E/k)((1/T2)-(1/T1))$

and  $\ln 2 = E/k((1/T2)-(1/T1))$

E = ln<u>2 \* k ((1/T1)-(1/T2))</u>

Take the following values: T1 =  $105^{\circ}C = 378.15K$ <br/>(See Figure 3.8)T2 =  $85^{\circ}C = 358.15K$ <br/>k = 8.617e-05E = 0.693 \* 8.617e-5<br/>(1.476e-04)

### Capacitor Activation Energy = 0.4eV

Figure 3.9 Capacitor Activation Energy Calculation

The first investigation in this area involved placing three sets of capacitors at each of 25°C, 60°C and 75°C. On a weekly basis the following measurements were made for each capacitor: Weight

Capacitance

Equivalent Series Resistance.

The results of the measurements taken at 60°C and 75°C appear in Figure 3.10. Unfortunately most of the variables did not change appreciably over the test period except, that is, the weights and capacitances of the smaller capacitors which decreased steadily during the test. Their Equivalent Series Resistances, however, did not exhibit the increase which should have accompanied such a trend. However, examination of the manufacturer's data, which was obtained subsequent to the test being carried out reveals that at the temperatures involved no discernible changes could be expected before the test had been running for approximately 2000 hours.

Figure 3.10(b) Data From Capacitor Measurements

Concurrent with this test two other investigations, also related to capacitor degradation and the effects of elevated ambient temperature were taking place.

The first of these involved running two power supplies non-stop in an ambient temperature of 75°C.

The second test cycled four power supplies on and off, with 2 power supplies being cycled at each of 2 different on/off cycles: One cycle switched the Power supplies on for 20 seconds and then off for 20 seconds. The other cycle switched the power supplies on for 60 minutes and off for 15 minutes.

Figure 3.11 contains the regulation and ripple voltage results for the constant high ambient test and Figure 3.12 shows the corresponding results for the units which were cycled. It was discovered during the course of the test that the ambient temperature in which the power supplies were switched on had a significant influence on output ripple voltage measurements. Thereafter steps were taken to ensure as far as possible that the power supplies were always switched on at the same ambient temperature.

Constant High Ambient Test Output Voltage Regulation Results Output Voltage v Hours Under Test

| Unit 1 | Unit 2 | Unit 1 | Unit 2 | Unit 1    | Unit 2 | Unit 1 | Unit 2 |

|--------|--------|--------|--------|-----------|--------|--------|--------|

| +12V   | +12V   | +21    | 191 H  | <u>-9</u> | 20     | -12V   | -12V   |

| 11.88  | 11.95  | 5.04   | 5.04   | -5.07     | -5.09  | -12.21 | -12.33 |

| 11.89  | 12.23  | 5.04   | 5.01   | -5.06     | -5.12  | -12.22 | -12.76 |

| 11.88  | 12.21  | 5.04   | 5.03   | -5.06     | -5.10  | -12.24 | -12.74 |

| 11.88  | 12.23  | 5.02   | 5.00   | -5.07     | -5.09  | -12.20 | -12.70 |

| 11.85  | 12.29  | 5.03   | 5.01   | -5.07     | -5.09  | -12.17 | -12.94 |

| 11.87  | 12.22  | 5.02   | 5.02   | -5.07     | 4.99   | -12.20 | -12.63 |

| 11.83  | 12.20  | 4.98   | 5.01   | -5.08     | -5.08  | -12.22 | -13.02 |

| 11.86  | 12.12  | 5.01   | 5.02   | -5.06     | -5.09  | -12.18 | -12.70 |

|                       |      |     |     | 1    |

|-----------------------|------|-----|-----|------|

| <b>Dutput Channel</b> | +12V | +5V | -5V | -12V |

| Ripple Voltage(mV)    | 80   | 50  | 100 | 100  |

Constant High Ambient Test Output Voltage Ripple Results Ripple Voltage v Hours Under Test

| Unit 1         Unit 2         Unit 2         Unit 1         Unit 2         Unit 1         Unit 2           +5V         +5V         -5V         -5V         -12V         -12V | 7.00 12.00 10.00 39.00 | 6.00 11.00 11.00 35.00 | 12.00 13.00 18.00 42.00 | 10.00 12.00 15.00 34.00 | 10.00 10.00 19.00 38.00 | 8.00 8.00 10.00 28.00 | 10.00 9.00 18.00 40.00 | 900 10.00 17.00 35.00 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|-------------------------|-------------------------|-------------------------|-----------------------|------------------------|-----------------------|

| +12V                                                                                                                                                                         | 38.00                  | 45.00                  | 60.00                   | 40.00                   | 95.00                   | 70.00                 | 90.00                  | 90.00                 |

| +12V                                                                                                                                                                         |                        |                        |                         | 528 24.00               |                         |                       |                        |                       |

Figure 3.11 High Ambient Test Regulation and Ripple Results

High Ambient Power Oycling

| Anti- Anti- Anti- | (12.12) (12.26) (12.20) (12.23) | (12.10) (12.20) (12.20) ( | (1210) (1230) (1220) ( | (12.10) (12.25) (12.20) | (12.07) (12.20) (12.20) (12.10) | 2             |               | (13.12) (12.33) (12.34) 25 C Start | imblent Temperature when PSU Settched on |

|-------------------|---------------------------------|---------------------------|------------------------|-------------------------|---------------------------------|---------------|---------------|------------------------------------|------------------------------------------|

| A PART STAT       | (4.87) (5.02)                   | (4.97) (5.02)             | (4.99) (5.02)          | (4.97) (4.96)           | (44.96) (44.96)                 | (8.01) (8.01) | (4.99) (4.96) | (4.96) 4.95                        | Amhant Tam                               |

| P                 | (\$04) (\$.03)                  | (\$04) (\$.03)            | (8.03) (6.02)          | (5.04) (5.02)           | (5.02) (5.03)                   | (8.04) (8.04) |               | (\$01) (\$.02)                     |                                          |

|                   | \$080 \$'01                     | \$050 \$03                | \$032 \$03             | 5,6 WD 5.03             | R430 8.45                       | 5010 E.0.1    | \$040 S.04    | \$030 2'04                         |                                          |

| The second        | \$03 \$01                       | 5.03 5.05                 | 8.03 8.03              | \$.03 £.05              | 8.01 8.05                       | \$42 \$45     | 5.01 5.07     | 8.00 5.05                          |                                          |

|                   | 1.11 1.                         | 11.94 11.44               | 11.93 11.93            | 11.92 11.62             | 11.11 11.14                     | 10.11 00.     | 14-11 00-1    | 1.46 11.46                         |                                          |

|                   | 11 96.11                        | 11.96                     | 11.94                  | 11.93                   | 1 88.11                         | 11 14.11 7    | 11 1011 8     | 1 00'11                            |                                          |

|                   | 24 11.4                         | 192 11.48                 | 33.6 11.40             | An4 11.40               | 672 11.48                       | 0711 PUP      | B64 11.40     | B64 11.40                          |                                          |

Units 1 and 2: 20 seconds on. 20 seconds off Units 3 and 4: 60 minutes on. 15 minutes Off High Amblent Power Cycling output Repti Vehinge

|           |      |      |      |      |      | 75 C Start | 10 C Start | 25 C Start |                                        |

|-----------|------|------|------|------|------|------------|------------|------------|----------------------------------------|

| 1121-     | 27   | 27   | 28   | 28   | 24   | *          | 2          | 3          | and har                                |

| 5 HAI     | 4    | 95   | 3    | 37   | 3    | 36         | 22         | 47         | U Swite                                |

| -121      | 04   | 04   | 85   | 2    | 30   | 33         | 32         | 9          | then PS                                |

| 112       | 37   | 8    | 94   | 35   | 1    | 2          | 11         | 1          | nMent Tenmershire when PSU Switched on |

| The first | 9    | 7    | •    | 9    | -    | -          | 2          | 7          | Tempe                                  |

| C Hall    |      | 10   | 10   | -    | 8    | 10         | 14         | 13         | mhlent                                 |

|           | 12.0 | 12.0 | 11.5 | 11.0 | 14.0 | 12.0       | 8.0        | 14.0       |                                        |

|           | 15   | 10   | 11   | 11   | 1    | 13         | 15         | 13         |                                        |

|           | =0   | =0   | 6    | 6    | 1    | 10         |            | -          |                                        |

| e Hun     | -    | 8    | 9    | 10   | 0    | 7          | 10         | 12         |                                        |

|           | 10   | 9    | 7    | 9    |      | -          | •          | 7          |                                        |

|           | 12   | 9    | 6    | 10   | 1    | +          | -          | 9          |                                        |

|           | 21   | 30   | 20   | 30   | 31   | 30         | 79         | 20         |                                        |

| 2         | 38   | 36   | 36   | *    | 95   | 36         | 05         | 68         |                                        |

|           | 94   | 25   | 37   | 82   | 95   | 9          | 33         | 3          |                                        |

|           | 28   | 28   | 28   | 82   | ล    | 31         | 67         | 50         |                                        |

|           | 24   | 192  | 335  | 105  | 572  | 192        | 192        | 198        |                                        |

Figure 3.12

High Ambient Power Cycling Regulation and Ripple Checks.

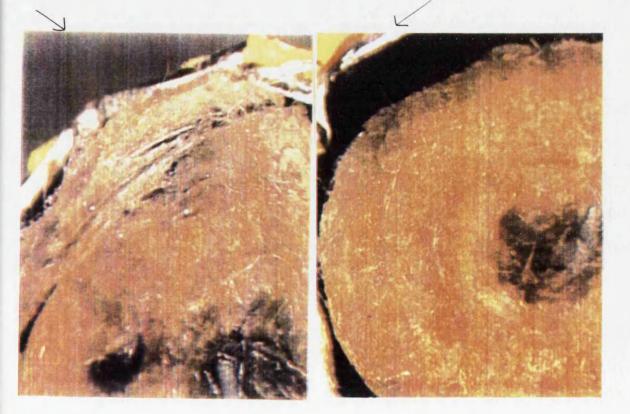

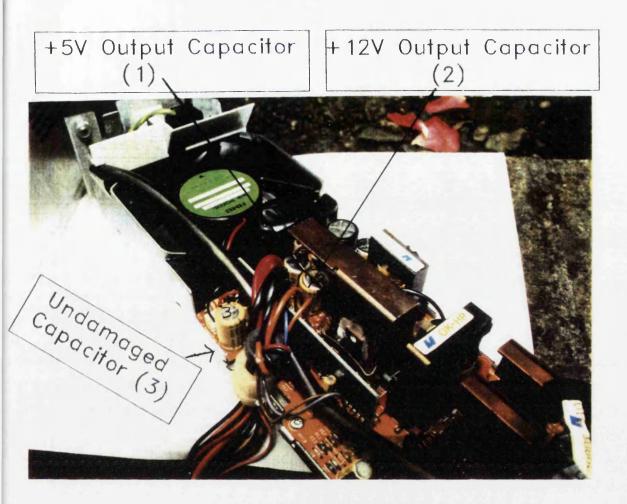

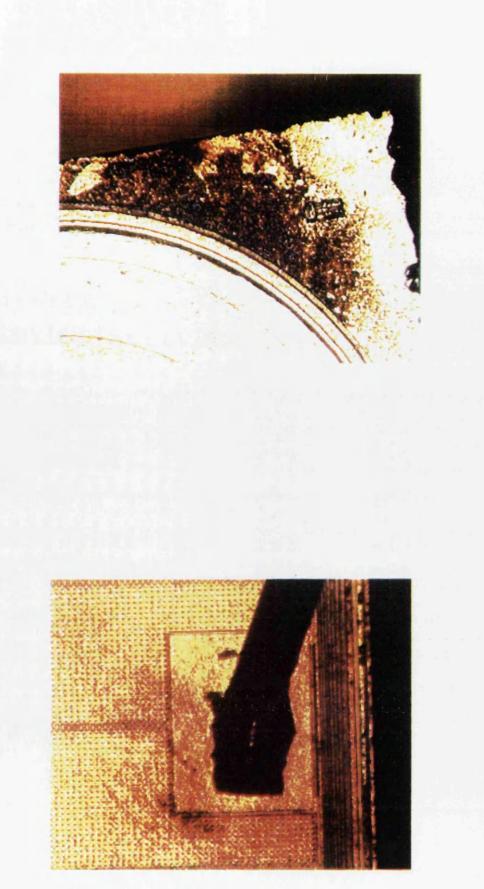

A trial run of one of the tests used revealed that capacitor failure, i.e. where the capacitance drops to approximately 40% of its listed value, is accompanied by a visible change in the appearance of the capacitor. Figure 3.13 shows external and internal photographs of both functional and failed capacitors.

As well as investigating the effects of each of these tests in their own right; by monitoring regulation, ripple voltage and capacitor appearance on a weekly basis; the cycling tests were also compared to each other, and the thermal cycling test in the next chapter, with respect to effectiveness in increasing ripple voltage and capacitor equivalent series resistance and decreasing capacitance.

<u>Good Capacitor</u> Seal intact and unexpanded. Internal filling soaked with electrolyte and occupying full volume of can Degraded Capacitor Seal expanded during evaporation of electrolyte. Filling, dry and shrunken, occupies a decreased volume.

Figure 3.13 Good and Degraded Capacitors