# ON THE PARALLEL IMPLEMENTATION OF THE LEHMAN FACTORING ALGORITHM

### 1 DAVID JOHN PATERSON HARE

1

A Thesis Submitted to the Faculty of Science of the University of Glasgow

> for the degree of Doctor of Philosophy

> > July 1985

ProQuest Number: 13834209

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 13834209

Published by ProQuest LLC (2019). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

## Acknowledgments

It gives me great pleasure to express my gratitude to Professor D. C. Gilles, the Head of the Department of Computing Science, for the opportunity to pursue this research in the first place, and for all his advice and patience when supervising my work.

As co-supervisor of my work, Dr. M. K. N. Nair, of the Mathematics Department, gave generously of his time and proved repeatedly to be both friend and counsellor, as well as having done much to stimulate my interest in this field of study during undergraduate days, and to him I am most grateful for it all.

I would also like to thank Professor W. D. Munn, the Head of the Mathematics Department for all his encouragement and consideration, and to his predecessor, Professor I. N. Sneddon, whose interest went far beyond the bounds of academic duty, and whose friendship has meant more than I can ever express.

In the Department of Computing Science I have many friends, especially the System Manager, Mr. Z. Podolski, who never seemed to tire answering questions; Doctors A. C. Allison and R. R. W. Poet who helped in the initial stages of the work and Doctors M. J. Jamieson and L. M. Mackenzie and Mr. W. Findlay who proof-read parts of the thesis and made some helpful comments. To them all I extend warmest thanks. Without the friend-ship and company of the postgraduate students in both departments, this would have been a lonely struggle. To all of them I say "thank-you", especially Mr. N. Nei, for his specialist knowledge and help with the graphs.

Mrs Anne Donnelly and Mrs Maxine Ramsay made an excellent job of decyphering my handwriting when typing the major part of the thesis. Sincere thanks are due to them also.

Without the generous assistance of the Science and Engineering Research Council this work would not have been possible. Professor D. Parkinson, the Head of the DAP Support Unit at Queen Mary College, London, was most generous with his time, and for several helpful discussions I am very grateful.

Last, but by no means least, to my parents, whose understanding of me made up for their lack of understanding of my research, and whose encouragement and help did much to keep me at it, I wish to express heartfelt thanks.

## Table of Contents

## Chapter

### Page

| 0  | Preface                                         | 1   |

|----|-------------------------------------------------|-----|

| 1  | Parallel Processing : An Historical Survey      | 4   |

| 2  | The ICL DAP                                     | 19  |

| 3  | The Lehman Algorithm                            | 35  |

| 4  | The Serial Implementation                       | 51  |

| 5  | The DAP Implementation                          | 58  |

| 6  | Assessment of Results                           | 89  |

| 7  | The Generalised Lehman Algorithm                | 104 |

| 8  | An Alternative Technique for Detecting Divisors | 128 |

| 9  | Primes and Primality Testing                    | 141 |

| 10 | Conclusions                                     | 149 |

Erratum - page 36, last paragraph, lines 6-9

According to [CACM 1984] it was, in fact, the Quadratic Sieve algorithm which was used by Simmons and his team.

## Note re. page 30, last line

The appropriate reference manual is the ICL Technical Publication 6918 (Third Edition, April 1981), which is entitled "DAP: FORTRAN Language".

# Table of Illustrations

between pages 103 and 104

## Plate

| 1 | Step | 1 |

|---|------|---|

| 1 | r    | 1 |

- 2 Step 2

- 3 VAX DAP comparison for 46-bit prime

between pages 127 and 128

## Plate

| 4 | T = 2589 with 11,111,111,111,111,111          |

|---|-----------------------------------------------|

| 5 | comparison for 11,111,111,111,111,111         |

| 6 | further comparison for 11,111,111,111,111,111 |

| 7 | (k,d) pairs within "easy reach"               |

## Chapter 0 Preface

There must be few people who, ten years ago, could have imagined the tremendous interest now being shown in finding the prime factors of large integers. What used to be just another part of the Mathematics taught in schools that most pupils forgot after entering the outside world, namely that every positive integer (>1) is the product of a unique set of primes, has now become a focus of attention. Several factors have contributed to this, but undoubtedly one reason lies in recent developments in cryptography.

Several years ago a scheme was announced called the RSA Public Key Encryption system [Rivest, Shamir and Adleman 1978]. This is a method for coding information with the advantage that the method by which a message is encoded can be made public (hence the name "Public Key") while only the information necessary for decoding need be kept secret. The mathematics involved centres round a particular congruence modulo N, say, where the integer N is the product of two large primes (each having probably more than 40 decimal digits) chosen beforehand, and at present, the only way known (or at least published!) to crack this is to find these two primes. This is not a simple task. Certainly, the factorisation of very small integers poses few problems, but to find the factors of, say, a 100-digit decimal integer would probably take many years of computer time, even using the fastest algorithm available! Hence the considerable amount of effort now being applied to this problem. In the related area of primality testing, recent theoretical advances have resulted in tests that can ascertain whether a given integer is prime or not in a very short period of time. For example, the work involved for a 100-digit number would typically require less than one minute of cpu processing! Unfortunately this has not happened with factorisation, and the main achievements in the field are now coming from the efficient implementation of existing algorithms on the very fast computers now available.

It has not just been the great progress made in chip technology that has produced these high-speed computers. Much research effort has also been directed to the actual design of machines themselves, and how best to make use of the devices available. Thus, many novel computer architectures have been suggested and built, and it is these that have proved extremely useful to those mathematicians trying to solve the problems associated with integer factorisation. Just three years ago, it was widely believed that numbers with 50 digits represented the limit of computational feasibility. But such is the progress in this area, made possible by the use of these advanced computers, that only last year a team at Sandia National Laboratories managed to factor the 69-digit Mersenne composite  $2^{251} - 1$  in only  $32 \cdot 2$  hours of computer time. This was such a significant achievement, demonstrating as it does, the advances made in numerical computing, that it was the subject of the plaque presented to the IEEE on the occasion of their centenary, by the ACM. In fact, the Sandia team have gone on to larger numbers, factoring, for example, a 71-digit integer in only  $6 \cdot 45$  hours of cpu time. The leader of this group, Gustavus Simmons, is quoted by Kolata [1983] as saying: "I'm convinced now that large-scale computational problems such as factoring depend as much on the architecture of the machine as on its brute-force speed. If you can modify the architecture you can make enormous progress .... The exploitation of machine architecture is a whole new way of doing mathematics."

Simmons' work has been on a CRAY-1 computer, which is typical of one approach to "supercomputer" design. However, there are other possibilities, and these are the subject of Chapter 1. All the designs have one feature in common though, namely, the use of parallelism to increase the speed of the machine. The survey begins by showing how parallelism was first introduced to computer architectures at the bit level, with the development of word-based machines, before the demand for ever faster processors prompted its incorporation into other areas of machine design, with the result that now computers have been built with up to thousands of processing elements working in parallel.

As part of this research has involved the use of one particular supercomputer, namely the ICL Distributed Array Processor (DAP), we then go on to describe this machine in some detail. Mention is also made of the high-level language available on the computer, and examples are given and techniques discussed, to illustrate the problems associated with programming such a processor array. It is interesting to note that, after trying to implement the Continued Fraction factoring algorithm on the DAP in only a couple of months, Wunderlich is on record [Kolata 1983] as saying, "It takes a gigantic effort to put a new algorithm on a large machine."

Chapter 3 begins with an outline of the mathematical idea which underlies most of the modern factoring algorithms along with a brief survey of some of the better-known current work, before the method chosen for consideration in this study, namely the Lehman factoring algorithm, is presented, and proved. During the discussion which follows, various short-cuts that can be incorporated into a computer implementation are mentioned, including one modification to the algorithm which reduces the constant implied in the running time being  $O(N^{1/3})$ .

- 2 -

In Chapter 4 we give a brief description of an implementation of this algorithm on a VAX 11/780, before going on to discuss in detail, the parallel version on the DAP. The problem of performing trial divisions in parallel on a processor array is analysed and we show that, unless just prime divisors are used (which is impractical because of the storage required), the best processor utilisation figure that can be obtained (on the DAP) is only 80%. Also discussed fully is a binary algorithm for finding square roots which is particularly suited to the architecture of the DAP.

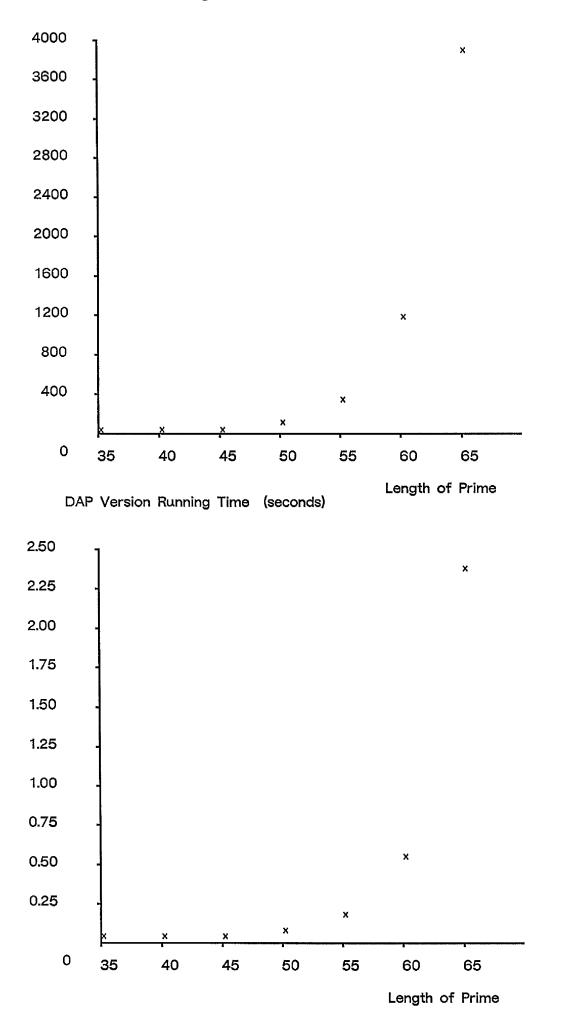

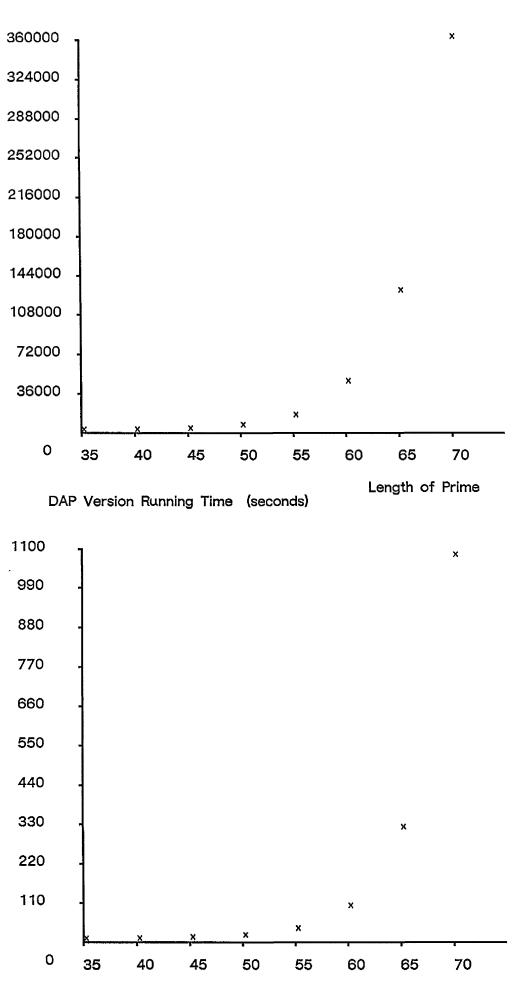

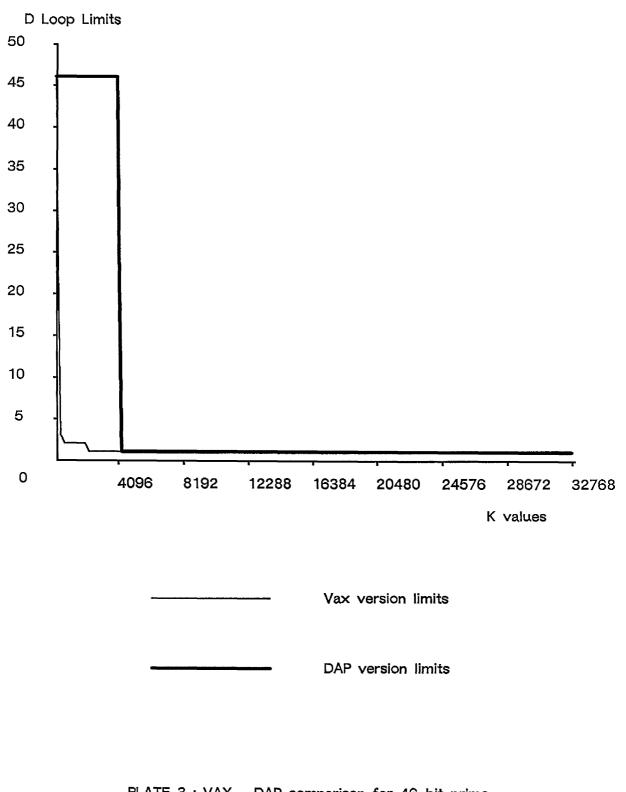

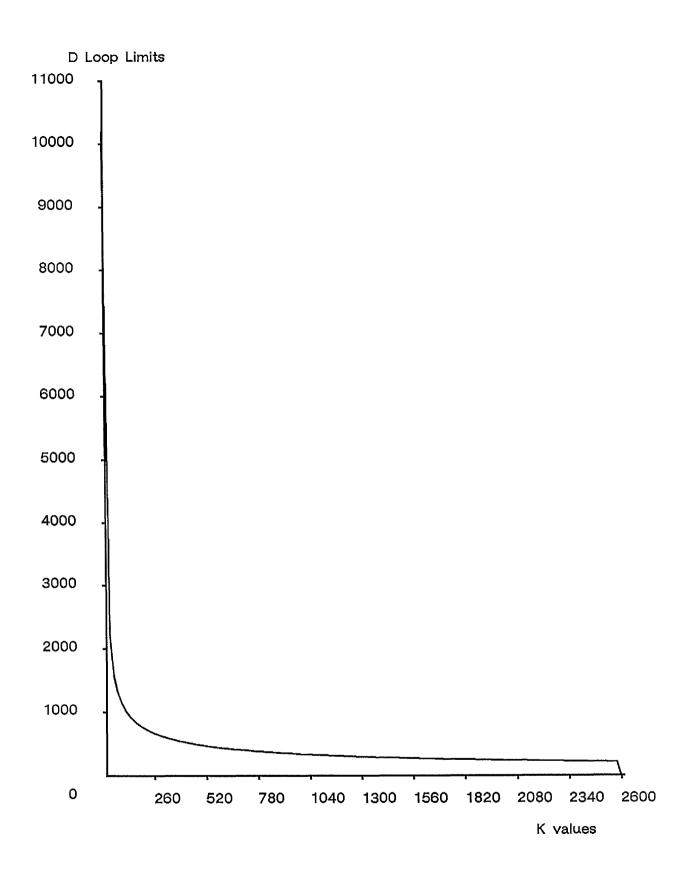

Assessing the relative performance of machines (especially if they have fundamentally different architectures, as here) is very difficult. Thus, the beginning of Chapter 6 is devoted to a brief discussion of this complicated problem, before the results obtained from this research are presented and analysed. For various reasons, which are examined, the speed-ups over the VAX, obtained by using the DAP, are sometimes more than would have been expected.

In Chapter 7 we give an example of when an even greater speed-up was recorded, and show mathematically why this was the case. Further analysis of the algorithm follows, leading up to the statement of a generalisation of the Lehman algorithm. We also discuss how certain extra knowledge can be used to reduce the amount of work required by the algorithm.

An alternative technique to division for identifying divisors of an integer is presented and analysed in Chapter 8 and, in addition to an examination of how one could generate lists of consecutive primes on the DAP, Chapter 9 contains a discussion of a topic related to factorisation, namely primality testing. Two tests suitable for use on the DAP are presented (from the literature), along with a running time analysis which shows that the algorithm concerned runs in polynomial time.

Chapter 10 contains a summary of the conclusions which this research led to, as well as an indication of further work that could be done.

## Chapter 1 Parallel Processing: An Historical Survey

With the advent of electronic computers, scientists found themselves able to do in minutes what had previously taken them days, or even longer. It is surprising to discover, though, that there were those who felt that even faster machines would not be required. In a summary of a talk he gave in 1949, von Neumann [1949] is reported as making the following point.

"A major concern which is frequently voiced in connection with very fast computing machines, particularly in view of the extremely high speeds which may now be hoped for, is that they will out-run the planning and coding which they require and, therefore, run out of work."

Of course, this was not the case. Von Neumann went on to point out, in the same talk, how the size of the problems that had been tackled up till then, had been limited by the speed of the machines available, and how the desire to solve larger problems would bring pressure to bear on designers to produce faster computers. Five years later, when speaking at the first public showing of the IBM Naval Ordnance Research Calculator [von Neumann 1954], he emphasised the importance of following the example of the US Navy and IBM, and "to write specifications simply calling for the most advanced machine which is possible in the present state of the art". As can be seen from what follows, his advice was heeded.

The early electronic computers were "bit-serial" machines (i.e. arithmetic and logical operations, as well as data transfers, were performed serially, one bit at a time) and so were comparatively slow. An example of such a machine was the Pilot ACE (short for Automatic Computing Engine), and its commercial derivative, the English Electric DEUCE [Wilkinson 1953]. An obvious (looking back!) improvement was to process more than one bit of a number or operand simultaneously, and so n-bit machines (where n > 1 is an integer) were born. Bit-parallel arithmetic, as it is called, became possible with the advent (and availability) of static random-access memories from which all the bits of a word could be read in parallel. In 1952, at the Institute of Advanced Studies, the first experimental machine to use such arithmetic was completed, while 1953 saw the appearance of the first commercial computer to employ parallel arithmetic, the IBM 701.

Another feature of early machines which limited their performance was that all input/output operations involved the use of a register in the arithmetic unit, thus halting

arithmetic activity for relatively long periods of time, due to the slowness of the type of I/O equipment being used (e.g. on-line card reader: 150-250 cards per minute; card punch: 100 cards per minute; line printer: 150 lines per minute; and, of course, paper tape reader: up to 1000 characters per second). Even the introduction of magnetic tape drives as the primary I/O medium with the provision of off-line card-to-tape and tape-to-printer facilities via another computer, failed to solve the problem, since even a tape speed of 15,000 characters per second was approximately 1,000 times slower than some processors (e.g. IBM 704).

This problem was at least partially overcome with the use of a separate computer (called a data channel) whose only job was to transfer data to and from (slow) peripherals and the main memory of the computer. Thus, once initiated by the main control unit, data transfers could proceed independently of the main processor, leaving the arithmetic unit free for more useful tasks. Of course, one was not limited to a single channel. In 1958 six data channels were added to the IBM 704, which produced the IBM 709, though this machine had a short life due to the use of "out-dated" technology (i.e. the use of valves when the transistor had become a reliable component).

The use of data channels is an example of what could be called "functional parallelism", which is the provision of several independent units for performing different functions (such as I/O, logic, addition, or multiplication), which are capable of operating simultaneously on different sets of data. This represents one of the four ways of introducing parallelism into the architecture of computers, namely pipelining, functional parallelism, multiprocessing, and processor arrays.

#### 1. Pipelining

This method makes use of the principle of the production line. The assembly of a car, for instance, can be divided into many smaller tasks, each independent of the others, and all capable of being performed simultaneously. There are many tasks in computing that can be similarly split up. For example, the addition of two floating-point numbers could be decomposed into the following three stages:

- prenormalise

- arithmetic operation

- postnormalise

all of which can be carried out at the same time on (obviously) different data, thus forming what would be called a three-stage pipeline.

If pipelining is to be used in the design of a computer, several factors have to be taken into consideration. For one thing, it is desirable that the operation whose execution is to be pipelined be divided into stages that take approximately the same time to complete, otherwise some stages will involve a (comparatively) large amount of waiting for others to finish, resulting in a certain degree of inefficiency. It is also important to keep the pipeline as full as possible (i.e. We want each stage to have operands to process for as much of the time as we can.). Gaps in the pipeline (as stages without operands are called) occur when the sequence of operations is being set up (i.e. in the filling of the pipeline), and when the sequence is being terminated (i.e. when the pipeline is, as they say, being flushed). Unfortunately, there is really nothing one can do about this. However, once the pipeline is full, a certain amount of ingenuity is required on the part of the designer to keep it that way. Such contingencies as conditional branches and operand dependency can, unless properly dealt with, cause a (wasteful) gap in the pipeline.

Despite these problems, this technique has been used effectively to speed up various arithmetic operations. For example, the CRAY-1 [Russell 1978] has twelve functional units, all pipelined, to perform such tasks as floating-point addition, multiplication and reciprocal approximation, as well as logical operations and shifts on vector operands (which are a feature of this very high-speed machine). The CDC 7600 and IBM 360/91 [Anderson et al 1967] also provide pipelined functional units, while in the AMDAHL 470 V/6, the entire processing of instructions is pipelined, with instruction execution divided into twelve suboperations. A new instruction can be taken every two clock cycles (or every 64ns), and so, at any given time, up to six instructions can be in various phases of execution. Thus, to a certain extent, this machine, and the others like it, may be considered parallel processors.

While the CRAY-1 computer, as already noted, features many special-purpose pipelines, other machines, like the CYBER 205 (as Hockney and Jesshope [1981] report) incorporate a number of general-purpose ones. Another such machine was the TIASC [Watson 1972] which had either one, two or four identical general-purpose pipelines.

The efficacy of pipelining was demonstrated in the early 1960s in Manchester, where the ATLAS computer was developed. This was a single processor machine in which pipelining was employed in the executing of instructions. It proved very effective because, for example, in a series of floating-point additions, the average time per operation was reduced from 6.0  $\mu$  s for the sequential execution of the program, to 1.6  $\mu$  s with pipelining [Hockney and Jesshope 1981].

### 2. Functional Parallelism

As already mentioned, the term "functional parallelism" refers to the provision of separate units for performing different tasks, each independent of the others, and all capable of operating simultaneously on different data. One of the earliest computers to include this feature was the pilot ACE [Wilkinson 1953], which permitted one out of each of the following classes of operation to be performed in parallel:

- add, subtract, fetch, store

- multiplication, division

- memory transfer to and from drum

- input, output

The ATLAS computer is another example, since it provided a separate autonomous 24-bit adder for index calculations, in addition to the main fixed- and floating-point arithmetic unit which worked on 48 bits. However, the first computer to employ functional parallelism as a major design feature was the CDC 6600 [Thornton 1964] which had ten separate functional units. The IBM 360 series machines also used this idea in that they had separate execution units for floating-point and integer address calculation which could operate in parallel.

Before discussing multiprocessing and processor arrays, it might be constructive to see where parallel processors fit into the whole spectrum of computer architecture. A useful categorization of machine design was developed by Flynn [1966, 1972]. He classified computers into four groups according to the number of instruction and data streams which can be processed simultaneously, as follows.

- (1) SISD single instruction stream/single data stream. This is the conventional serial von Neumann [von Neumann et al 1946] computer in which there is one processor executing one stream of instructions, using a single stream of data. Whether pipelining is used or not is irrelevant for the purposes of the categorization. Examples of such machines are: CDC 6600 (unpipelined); CDC 7600 (pipelined arithmetic); AMDAHL 470 V/6 (pipelined instruction processing).

- (2) SIMD single instruction stream/multiple data stream. Such a machine could be called a vector processor since each instruction operates on a vector of operands, rather than on a single data item. The individual elements of each vector could be considered members of different data streams hence the classification name. One could argue that this group should contain the pipelined uniprocessors which can process vector instructions (like the CRAY-1), although nowadays the term SIMD is used to refer

to an array of processors working under common control, examples of which will be given later.

- (3) MISD multiple instruction stream/single data stream. In this type of computer, each operand would be operated on by several instructions simultaneously. However, at present, there is no system that is purely MISD, and it is hard to imagine what advantages such a machine would have. Thus, this grouping is only included to make the categorization symmetric.

- (4) MIMDmultiple instruction stream/ multiple data stream. The computer described here is formed from at least two independent processors (independent in the sense that each is capable of operating on its own data stream, using its own instruction stream) connected together in some way. This group will shortly be described under "multiprocessing".

As can be seen, in this classification, nothing is said about the architecture of the processors involved, or about how they are connected together (in the cases of SIMD and MIMD machines), and so, to a certain extent, it is too broad. However, it will suffice for our purposes. (An example of a more detailed categorization is Shore's taxonomy which Hockney and Jesshope [1981] describe, in addition to a very complicated system of their own.)

#### 3. Multiprocessing

As the name implies, a multiprocessor is a computer incorporating more than one processor. Since 1959, when Holland (as Hockney and Jesshope [1981] report) presented what could be considered to be the first large-scale multiprocessor design, several such machines have been produced, and from the standpoint of high-speed computation, the area seems a promising one. Unlike a processor array, which is composed of a large number of identical processors working in lockstep, this type of computer is made up of usually a smaller number of general-purpose processors, each capable of executing different instruction streams. The processors share global memory, and so one of the most important components of the system is the processor-memory interconnection network. In the designs so far produced, many different types of interconnection schemes have been used.

The most popular design has been that of a crossbar switch, which connects every processor to every memory module. It was used by Burroughs in their 5000 series machines, as well as in their D825 command and control computer [Anderson et al 1962]. The C.mmp [Wulf and Bell 1972] developed at Carnegie-Mellon University is another example, as more recently, is the S-1 multiprocessor [Widdoes and Correll 1979]. Developed at the Lawrence

Livermore Laboratory, University of California, under the auspices of the U.S. Navy, this machine was designed to have a performance ten times that of a CRAY-1! The S-1 Mark IIA, as it is called, consists of 16 specially developed single processor machines (called S-1 Uniprocessors), each with about the computational power of a CRAY-1, connected to 16 main memory banks via a crossbar switch which provides high-bandwidth, low-latency interprocessor communication. (There is also a shared bus whose function, among other things, is to transmit interrupts and small data packets from one uniprocessor to any subset of the others.) Early results seem encouraging, and there are plans to (re)implement the whole system using VLSI techniques. (That the idea of connecting together very powerful computers is still current in research, can be seen from a recent paper which describes a distributed system, called LCAP [Clementi et al 1984], being developed by IBM. Designed initially for applications in computational chemistry, it consists of two IBM-4341's and one IBM-4381 as front end processors, and ten FPS-164 attached array processors. This parallel system was claimed, in June of last year, to have a peak performance of 120MFlops (i.e. millions of floating point operations per second), which, it was hoped, would have risen to 550MFlops by the end of 1984).

There is, however, a major snag with the crossbar network. The cost of a such a switch grows as the product of the number of processors and memory modules. So, for a large number of processors with the corresponding memory, the price of the required switch could dominate the cost of the entire system!

A second computer developed at Carnegie-Mellon University, called Cm\* [Swan et al 1977a, b], uses a less expensive interconnection method. The main distinguishing feature of this machine is that, instead of the shared main memory being separated from the processing elements, it is spread throughout the whole system. One processor (in this case an LSI11) and a unit of memory form the basis of what is called a "computer module". Up to 14 of these modules may be grouped together, along with a mapping processor (called a Kmap) to form a "cluster". The Cm\* is basically a collection of such clusters. Communication in the system is performed using a three-tiered bus structure. Within each computer module, communication is via the LSI11 processor's bus. To enable modules in the same cluster to communicate with each other, every cluster contains a bus connected to all the LSI11 buses via a switch (or Slocal) in each module. The Map Bus (as it is called) is also connected to the Kmap which performs the required routing. If, however, a processor wishes to communicate with a processor in a different cluster, then this can be done through an intercluster bus connecting all the Kmaps, which again controls the routing of the data or message. Packet Switching, rather than Circuit Switching, is used in an attempt to achieve good bus utilization while minimising bus contention.

The cost of such a system is roughly linear with respect to the number of computer modules, and this makes possible the inclusion of a large number of processors (Jones [Jones and Schwarz 1980] reports the use of 50.). However, this interconnection scheme is comparatively slow, especially when intercluster communication is required. Thus, a certain amount of planning is required to try and ensure that very rarely does a processor need an operand contained in a memory unit within a different cluster.

A good compromise between the costly crossbar switch and the slow asynchronous bus would seem to be the network used in the Burroughs' design for a Flow Model Processor (FMP) [Lundstrom and Barnes 1980]. This was an architecture designed for NASA, with a planned performance of 1000Mflop/sec, targeted to be the FMP for the Numerical Aerodynamic Simulator. While this machine was not actually built, extensive simulation and analysis showed that, for certain favourable aerodynamic applications, the required performance level would have been achieved. The connection network between the 512 processors and 521 memory modules (Hockney and Jesshope [1981] state that this number was chosen because having a prime number of memory elements which is greater than the number of processors reduces memory conflict.) in the computer was considered an essential element in the design. What was required was a connection scheme that would allow all the processors to request simultaneously, and attend to their needs "fairly" and with little delay. The designers chose what is called the "baseline" network. This has a complexity of O(Plog P) (where P is the number of processors), which compares favourably with the crossbar switch  $(O(P^2)$  complexity) from the point of view of cost, and with the asynchronous bus system with respect to time.

While the design of this class of machines makes them inherently more flexible than processor arrays, there are very real obstacles in the way to achieving high performance. Such problems as allocating tasks to processors, synchronization of computations on different processors, and the sharing of resources, giving precedence to certain processes over others, as well as the design of interprocessor connection networks, are still topics requiring further research. (The Denelcor HEP has an interesting solution to the problem of resource allocation incorporating a queueing system [Snelling 1984].)

It is worth noting that most of the multiprocessors commercially available do not incorporate as many processors as some of the research machines mentioned above. Two or four processors have been the more common numbers to be used. For example, the CRAY XMP has only two processors, but with each of them being equivalent to a CRAY-1, it is one of the most powerful computers ever built.

### 4. Processor Arrays

Here we are referring to the provision of an array of identical processing elements working under common control, designed to perform the same operation simultaneously, but on different data stored in their private memories (i.e. operating in lockstep). These should be distinguished from array processors, since the latter term is used to refer to any computer that has special facilities for the processing of arrays, and so can include pipeline machines as well as processor arrays [Robinson 1979].

Hockney and Jesshope [1981] report that the idea of having a connected array of processors was first developed by von Neumann, who demonstrated that a two-dimensional array of computing elements with 29 states could simulate a Turing machine and so perform all operations. Unger [1958] followed this theoretical work by producing a design for a "spatial computer" consisting of a rectangular array of processing modules under the direction of a single control unit that broadcast instructions to all the modules. The major milestone in the introduction of this type of architecture was the SOLOMON computer, first described in 1962 [Slotnick et al 1962].

The Simultaneous Operation Linked Ordinal Modular Network (or SOLOMON for short) was originally a two-dimensional array of  $32 \times 32$  processing elements (or PE's), each with its own two memory frames, again under the control of a single control unit which processed a single stream of instructions, and an input-output unit. However it appeared from a later paper [Gregory and McReynolds 1963] that it was possible to add or remove modules of 256 PE's, and their associated memory frames, from the system, so that the configuration could vary in size from a minimum of  $32 \times 8$  PE's up to a maximum of  $32 \times 64$ . Each PE had 4096 bits of core storage in addition to a bit-serial arithmetic unit, and was able to communicate with its four nearest neighbours, if they existed. Gregory and McReynolds state that by specifying alternate connections between (only) the edge elements, a number of different geometric configurations were available to the programmer, namely: a horizontal cylinder; a vertical cylinder; a torus; a horizontal circle; and a vertical circle, as well as the normal planar configuration. The network control unit had two major functions: that of decoding and organising the execution of instructions, and controlling memory addressing. In addition, a broadcast option was provided, whereby the control unit could simultaneously supply the same operand (e.g. some required constant) to any (probably large) subset of the PE's, thus acting as a sort of "fifth nearest neighbour".

While this actual design was never implemented, it did "pave the way" for many of the processor arrays so far constructed. Machines like the ILLIAC IV, PEPE, STARAN, DAP, and the MPP all exhibit the influence that the SOLOMON computer had on the architecture of this type of machine. Before discussing these examples more fully, it would be worthwhile to consider some of the main design issues which have to be resolved in the design of a processor array.

Firstly, one has to decide how many processors are required for the array. Or perhaps a better question would be "How many processors can be afforded?"! The answer to this problem will be influenced very much by one's decision on the second point, namely: "How complex should the processors be?". (As mentioned before, all the processors in the array will be identical.) "Do we want a large number of single bit processors (like the DAP), or a smaller number of 64-bit floating-point units (as in the ILLIAC IV), or are we going to try and seek a compromise somewhere in between?" is a question that has to be answered. It is interesting to note that, in terms of a processor array, 64 PE's constitute a small number! The amount and type of memory (i.e. associative or not), and how much of it will be common to all, rather than local to each PE, has also to be considered. Possibly the most important decision to be made concerns how the PE's will be interconnected (if at all - c.f. PEPE, later). It would be very undesirable if the potential increase in computation speed gained from the number of processors was lost, or not fully realised, because of routing delays. There have been several communication networks proposed for processor arrays [see Kuck 1977, Siegel 1979], three of which (namely mesh, cube and perfect shuffle) are described by Dekel and Sahni [1981] as follows.

(1) Mesh Connected Computer (MCC).

Here we consider the PE's to be logically arranged as a k-dimensional array which we will denote by  $A(n_{k-1}, n_{k-2}, \dots, n_0)$ , where there are  $n_i$  processors in the  $i^{th}$  dimension, and the total number of processors is equal to  $n_{k-1}n_{k-2}\cdots n_0$ . The PE at location  $A(i_{k-1}, \dots, i_j, \dots, i_0)$  is connected to the PE's at location  $A(i_{k-1}, \dots, i_j+1, \dots, i_0)$  and  $A(i_{k-1}, \dots, i_j-1, \dots, i_0)$ ,  $0 \leq j < k$ , provided they exist. This interconnection scheme, however, requires (at most) 2k connections per PE ( < 2k for the cases where not all the "neighbours" exist).

(2) Cube Connected Computer (CCC).

This interconnection scheme is only possible if the number of PE's is equal to a power of 2 (i.e.  $p = 2^q$ , say). Using Dekel and Sahni's notation, if we let  $i_{q-1}i_{q-2}\cdots i_0$  be the binary representation of i, for  $i \in [0, p-1]$ , and  $i^{(b)}$  be the number whose binary pattern is  $i_{q-1}\cdots i_{b+1}\overline{i_b} i_{b-1}\cdots i_0$ , where  $\overline{i_b}$  is the complement of  $i_b$ , and  $0 \leq b < q$ , then in this network, PE(i) is connected to PE( $i^{(b)}$ ),  $0 \leq b < q$ . Thus we have a model requiring  $\log_2 p$  connections  $\rho_{2r} \ell \in \mathbb{C}$ .

(3) Perfect Shuffle Computer (PSC).

Let p, q, i and  $i^{(b)}$  be as above, and let  $i_{q-1}i_{q-2}\cdots i_0$  be the binary representation

of *i*. Define SHUFFLE(*i*) and UNSHUFFLE(*i*) to be, respectively, the integers with binary representations  $i_{q-2}i_{q-3}\cdots i_0i_{q-1}$  and  $i_0i_{q-1}\cdots i_1$ . Then, in this scheme, PE(i) is connected to  $PE(i^{(0)})$ , PE(SHUFFLE(i)) and PE(UNSHUFFLE(i)), the three connections being called exchange, shuffle and unshuffle respectively. It is not hard to see that this connection network requires only three connections per PE.

As most communication networks are more suited to certain applications than others (due to requirements for data flow in the algorithms), the choice of interconnection scheme is usually influenced by the proposed uses of the machine. So it is important to decide what one wants the machine for, before building it. Admittedly, it would be preferable if there was a design which was independent of a particular application and efficient in the solution of a wide range of problems. However, this achievement is still a matter for research. Of course, another avenue for investigation is the development of algorithms for many different applications, all suited to a certain type of interconnection network , as is taking place with, for example, the ICL DAP.

As with the previous class of machines, many computers have been built which conform to the basic SIMD pattern - too many for them all to be listed here. Thus, in the descriptions that follow, mention is made only of the more significant or representative machines.

### ILLIAC IV, PEPE, BSP

In 1966 the University of Illinois was awarded a contract by the U.S. Department of Defense's Advanced Research Projects Agency to design a computer based on the SOLOMON proposal. This machine became known as the ILLIAC IV [Slotnick 1967, Barnes et al 1968]. The original design was for a machine made up of four quadrants connected by a highly parallel I/O bus, and using a large disk for secondary storage. Each quadrant was to contain 64 processors (PE's) under the direction of a control unit executing a single stream of instructions, with each PE connected to  $_{\Lambda}^{i6}$  four nearest neighbours. Slotnick reported that each PE was provided with three 64-bit arithmetic registers and high-speed adders for full 64-bit floating- and fixed-point operations, in addition to 2000 64-bit words of thin film memory. Such a machine, it was planned, would achieve a maximum processing rate of 1Gflop/s, and was to be used for the solution of partial differential equations. However, due to many problems, ranging from the too slow development of the intended technology (ECL) to uncertainty over a location for this huge machine (see [Falk 1976] for further details), the

design as planned was never constructed. One quadrant, though, was built by Burroughs and delivered to NASA Ames Research Center, California, in 1972. It took a further three years of testing and replacing of faulty parts (e.g. 110,000 resistors had to be replaced because of unreliability) before it was fully operational. While the performance was not even a tenth of what had been proposed, the ILLIAC IV had a profound influence on the development of computer design, software, and especially technology. It was one of the first machines to use semiconductor memory chips for all its main memory, due to the fact that there was not enough room on the circuit boards for the thin-film memory originally intended. In the excellent historical survey at the beginning of their book , Hockney and Jesshope [1981] mention that the ILLIAC IV also "pioneered the use of 15-layer circuit boards and computer-aided layout methods that proved necessary to wire them".

As already mentioned, Burroughs were the main contractors of the ILLIAC IV (from 1969 - 73). In fact, they were involved with three parallel machines in the 1970's, the second of which was the PEPE computer (Appendix A of [Enslow 1974] ). The Parallel Element Processing Ensemble (PEPE, for short) was a special-purpose machine designed to control a ballistic missile defence system of radar detectors and missile launchers for the U.S. Army. It grew ( Hockney and Jesshope [1981] state ) out of research at Bell Laboratories, Whippany, into content-addressable distributed logic memories combined with floating-point processing. PEPE consisted of 288 PE's working together in lockstep under the direction of three control units. Each PE actually contained three processors (one each for input of radar signals, processing of data, and output of control signals) - hence the need for three control units, one for each type of processor. Hockney and Jesshope report that "When operating, each target that was identified became the responsibility of one PE and, because there were no ordered connections between the targets, no direct connections were provided at all between the PE's. When necessary, communication between the PE's took place via the memories of the control units. The array of processors was then said to be unstructured and the word ensemble was coined for this arrangement.". Theoretically, the maximum computing rate of PEPE was 288Mflop/s (1Mflop/s per PE). However, a more realistic estimate was 100Mflop/s.

The third machine was a commercial venture called the Burroughs Scientific Processor (or BSP) [Stokes 1977]. Its design benefited from the experience gained from the construction of the ILLIAC IV. The aim was to provide a computer using standard technology (rather than pioneering new methods) which was capable of sustaining a high percentage of its maximum performance (in this case, sustain 20-40Mflop/s and have a maximum performance of 50Mflop/s), something the ILLIAC IV failed to do, and be programmed exclusively in a high-level language. The BSP consists of 16 serially organised floating-point processors (each over twice as powerful as those in the ILLIAC IV) connected via a crossbar network to 17 memory banks, under the direction of a central processor. Pipelining is used in the execution of instructions. While the first design principle was not adhered to strictly, since the massive file memory of the BSP was constructed using charge coupled logic (CCL) technology, Hockney and Jesshope [1981] list timings which show that the desired performance was achieved. However, the BSP was withdrawn in 1980 before any had been sold.

### DAP, MPP

This type of machine exemplifies a completely different approach to high-speed computation via arrays of PE's. Rather than the powerful processors used in machines like the BSP, here, large numbers of simple processors are involved in the design. The ICL Distributed Array Processor (DAP) [Flanders et al 1977] is an example of such a machine, and since much of this dissertation concerns it, a more detailed description will follow in the next chapter. But, for the sake of completeness, a brief outline is included here to show where the DAP fits into the spectrum of parallel computers. First delivered in 1980, it is a 64×64 two-dimensional array of single bit processors, each connected to its four nearest neighbours, working under the control of what is called the Master Control Unit. A feature of this machine is that 16 PE's and the associated memory are mounted on the same circuit board, in contrast to the von Neumann concept of a computer in which logic and memory are completely different (both conceptually and materially). Thus the logic could be said to be distributed throughout the memory - hence the name of the computer. Hockney and Jesshope give performance figures for this machine ranging from 15Mflop/s for matrix inversion to 48Mflop/s for Poisson solution which uses a number theoretic transform which optimises the use of the hardware.

The Massively Parallel Processor (MPP) [Batcher 1980] was the result of a contract awarded to Goodyear Aerospace by the NASA Goddard Space Flight Center in December 1979 for a machine capable of the very high-speed image processing required to process satellite photographs. It comprises a two-dimensional array of  $128 \times 128$  PE's, again with nearest neighbour connections, and a single array control unit. (There is also an additional rectangle of  $128 \times 4$  PE's that is used to reconfigure the main PE array in the event of a PE fault.) Single bit processors were chosen to enable the efficient processing of operands of any length. The results achieved are truly astonishing. Batcher gives a table showing speeds of typical operations which range from 216 million operations per second for the multiplication of two 32-bit floating-point numbers to 6553 million operations per second for the addition

#### STARAN, LUCAS

These machines are similar to the DAP and MPP in that they also comprise arrays of single bit processors. The main difference lies in their use of associative memory. In this type of memory, an item is accessed by its contents, rather than by an address (hence its alternative name: Content Addressable memory.). Usually a comparison is performed between a certain part, or field, of each memory word and a given pattern or mask, and the data item is accessed if a match is obtained. (Some associative memories also have a conventional addressing system.) Various machines based on associative memories have been produced [see Thurber and Wald 1975, Yau and Fung 1977], the best known of which is the STARAN [Batcher 1974] processor array produced by Goodyear and completed in 1976. Hockney and Jesshope summarise the features and uses of the computer as follows.

"The STARAN typically comprised four array modules, each with 256 one-bit PE's and between 64Kbits and 64Mbits of total storage, controlled by a sequential PDP-11. Unlike the SOLOMON, however, the storage was not assigned to specific PE's; instead, a flexible 'FLIP' network was interposed between the PE's and the memory. A slice of 256 bits was selected from memory in a pattern specified, under program control, by a 256-bit code. The pattern selected may, for example, have treated the store as a multidimensional array with a varying number of dimensions, or shuffled the data in the manner required by the fast Fourier transform and other important numerical algorithms. Connections between the PE's were achieved by passing the 256-bit slices of data through the FLIP network, thus achieving in minimum time a highly flexible effective interconnection pattern that could be varied from problem to problem by the programmer. The STARAN, like other bit-oriented computers, was most effective when performing logic and short word-length integer arithmetic. A particularly suitable application is the digital processing of pictures, in which the image is divided into millions of pixels (picture elements) each of which is represented by 6 - 12 bits. The first STARAN was delivered to the Rome Air Force base for such an application and it has also been proposed for air-traffic control."

A more recent, if less well known, machine is that developed at the University of Lund in Sweden. LUCAS (Lund University Content Addressable System) [Ohlsson and Svensson 1983] was developed as a research tool to investigate the applicability of associative processors. It consists of an array of 128 identical single bit processors interconnected using the Perfect Shuffle/Exchange network (see above). Apart from STARAN, whose FLIP network can resemble the Perfect Shuffle connection, LUCAS is the only machine at present known to have this network, and so the findings of this research will be especially interesting. Early results seem promising.

It should be said before concluding this section, that all the above machines normally require a host computer, and so act as special-purpose attached processors. For example, the ILLIAC IV was connected to a PDP-10, the PEPE to a CDC-7600, the DAP to an ICL 2980, and the STARAN at Rome Air Development Centre is attached to an I/O channel of a Honeywell HIS-645 computer.

### Other approaches

All the machines mentioned above follow von Neumann's idea of sequential instruction execution. However, architectures are being proposed which do not operate on this principle. One alternative is the data flow concept which Dennis [1979] describes as follows:

"In a data flow computer, an instruction is ready for execution when its operands have arrived - there is no concept of 'control flow', and data flow computers do not have program location counters. A consequence of data-activated instruction execution is that many instructions of a data flow program may be available for execution at once. Thus highly concurrent computation is a natural accompaniment of the data flow idea."

However, the extent to which such potential concurrency can be exploited is limited when only a single processor is being used (although such techniques as pipelining can be employed). Thus, a natural extension is to connect together many data flow processing elements to form what Dennis calls a "data flow multiprocessor system". In fact, he goes on to describe a possible architecture for such a machine, that has been developed at MIT. Various other designs have also been proposed, including a 20 processor system currently under construction at Manchester University [Gurd 1984]. However, this class of computers is still at the development stage, with much more work to be done if this type of machine is to become commercially widely available, and whether they will ever achieve the performance figures quoted for other high-speed machines remains to be seen.

Another approach to high-speed computation, though specifically for use in specialpurpose machines, has been developed recently at Carnegie-Mellon University. Kung [1982] describes the basic idea involved in "systolic architectures", as they are called, as follows.

"A systolic system consists of a set of interconnected cells, each capable of performing some simple operation. Because simple, regular communication and control structures have substantial advantages over complicated ones in design and implementation, cells in a systolic system are typically interconnected to form a systolic array or a systolic tree. Information in a systolic system flows between cells in a pipelined fashion, and communication with the outside world occurs only at the 'boundary cells'. For example, in a systolic array, only those cells on the array boundaries may be I/O ports for the system."

Kung goes on to explain that this class of machine was proposed in order to speed-up those computations where multiple operations are performed on each data item in a repetitive manner (e.g. matrix multiply, convolution problems). By replacing a single processing element with an array of systolic cells, it was envisaged that a higher computation throughput could be achieved, without increasing memory bandwidth. Since the cells used are very simple processing elements, such machines can be implemented in VLSI at relatively low cost. Versions of systolic processors are being designed and built by several industrial and governmental organisations, and it will be interesting to see if, as Kung hopes, they result in "cost-effective, high-performance special-purpose systems for a wide range of problems."

#### Related areas in research

The study of Parallel Processing is not limited to machine architecture. The development of algorithms, and languages to express them, which exploit the potential of these machines is also of great importance. Work has been done in the writing of compilers which can detect parallelism in a serial program. But, for reasons that will be discussed later, for the most part, it is still up to the programmer to identify the possible parallelism beforehand, and to express it using one of the available parallel languages like TRANQUIL, GLYPNIR, ACTUS and CFD FORTRAN, which were all developed for the ILLIAC IV, or DAP FORTRAN, to name but a few. As can be seen, the above languages are specifically designed for certain machines. However, in the interests of even just portability, it would be desirable to have a "universal" language for the writing of programs for parallel machines. It had been hoped that the new language Ada would have proved suitable. However, this seems unlikely to be the case.

It seems certain that this whole area will be the subject of much study in the future, for as Stone says [Stone 1975]:

"To achieve even faster computers in the future we must take new approaches that do not depend on breakthroughs in device technology, but rather on imaginative application of the skills of computer architecture.".

### Chapter 2 The ICL DAP

In the previous chapter we briefly mentioned that the DAP, with its  $64\times64$  array of bit processors operating in lockstep under the control of the Master Control Unit (mcu), is typical of one of the approaches to parallel processing. We start this chapter by giving some of the reasons which motivate the design of this class of machine.

It is well-known that there are many algorithms which require basically the same operation(s) to be performed on many different numbers (e.g. matrix manipulation, finite difference methods for solving Partial Differential Equations, Lattice Gauge Theory). On a serial machine, this involves the use of DO loops (or the equivalent), where the same sequence of instructions has to be repeated over and over again, but on different data. If, however, we were able to allocate a separate processor to each data item, then we could perform all the required operations in parallel. Often, as in the case of finite difference methods, this might require the use of thousands of processors, This, in turn, places certain constraints upon them; for example, the processors would have to be physically small, of low power consumption, and be relatively simple. Conventional 8- or 16-bit processors are not suitable; for one thing, they (rightly) have an instruction decoder. But this facility is unnecessary in an SIMD computer, since all the processors will obey the same instructions which, therefore, need only be decoded once (by the mcu), and not 4096 times. Thus it is not surprising that most of the SIMD machines designed to date, have used specially-designed, bit-organised processing elements.

The DAP is no exception. Its processing elements (PE's) are identical, and have only three registers, each one bit long, together with an arithmetic logic unit, and some memory. Originally, each processor had 4K bits of memory, but in the DAP at Queen Mary College, extra has been added, to bring the total up to 16K bits per processing element. As one would expect, there is an Accumulator (Q), and a Carry register (C).However, the third register is more unusual. Called an Activity bit (and denoted by A), this register provides the ability to effectively "turn off" (and "turn on") processors as we wish. Since the processors work in lockstep, they all obey the same sequence of instructions, broadcast from the mcu. Of course, they will probably not be operating on the same data! However, if for some reason, we only wanted some subset of the PE array to perform a certain task, we are forced to have the necessary work carried out by all the processors. This could cause problems, as will be shown later. But, among other things, the Activity bits allow us to select which processors will actually store the result of such an operation, and which will not. Thus, while all the processors have to do the specified work, not all of them need to record the effect. Hence, we can think of those PE's which do not perform the assignment part of the instruction as being "switched off". This technique (known as masking) is one of the most powerful features of this machine, and so will be described in more detail later.

Normally, (though, of course, it will depend on the application), the processors use data from their own local memories. But there are times when information is needed from "outside", so to speak, and there are two ways in which this can be supplied. As well as telling the processors what to do, the mcu can broadcast a given scalar value to all the processors at once. Although it is not possible for different values to be made available globally simultaneously (instead, several broadcast instructions would need to be used, along with masks to select which processors received which data), this facility can prove very useful. In addition, the processors can communicate with each other by means of the interconnection network. The PE's are connected to their nearest neighbours (i.e. to the processors which are immediately above, below, to the right, or to the left - denoted, in an obvious notation, by NSEW), and data can be passed between them on these row and column highways (as they are called). There is no restriction here that all the values be the same. It is quite possible for each processor to receive a different number. However, there is a limitation; namely, that every processing element receives a value, and that all the values travel the same distance, in the same direction. In other words, it is not possible for one processor to receive a piece of data from the PE which is three rows below it, but in the same column, while another processor is passed a value from the PE to its left. Every processor must receive information from the same corresponding source, with masking used to indicate which processors are not to store the value they receive.

It is because of this interconnection scheme of rows and columns, that we can conceive of the processors as being arranged in an array. Of course, physically, this is not true. The PE's are placed on circuit boards (16 per board) which are, in turn, arranged side by side in cabinets. Nevertheless, the conceptual idea of an array is a useful one to have, as it can help us visualize the parallel activity that we are trying to arrange. It also means that we can refer to a certain processor easily, by stating which row and column it is in. Thus PE(i, j)will lie at the intersection of row i and column j, where both i and j take values between 1 and 64 inclusive.

The hardware also provides connections between the elements at the edge of the array. The processors on the left edge (i.e. in the first column) take as their left neighbour, the element in the same row in the last column, while the PE's in the first row are connected to the corresponding elements of the last row. Thus the array can be thought of as both a vertical, and a horizontal cylinder. A more unusual system of edge connections, supported by software, provides a link between the bottom elements of the first 63 columns with the top elements of the successive columns. Thus, for example, PE(1,64) is (conceptually) joined to PE(2,1), PE(2,64) is connected to PE(3,1), and so on. How such a scheme can prove useful will be seen later in this chapter.

Since the processors are capable of receiving information only one bit at a time, the connections described above are just one bit wide. Thus, a 64-bit register could supply data to all the row or column highways simultaneously. The mcu has 8 such registers attached to the row and column highways, which can be used, not only to transmit data to all the processors in a given row or column, but also to receive data from selected processors.

As has already been mentioned, the DAP does not stand alone, but requires a host computer, through which all communication with "the outside world" takes place. The DAP itself has no input or output facilities, and so any required data must be read in by the host, which must also write out any necessary results. Programming the DAP is done in a specially-designed high-level language called DAP-FORTRAN, and the instructions are executed after a call of the DAP from a main program in the host. Thus there are two distinct parts to any job that requires the use of the DAP: a host section, written in FORTRAN IV or FORTRAN 77, consisting of a main program, and possibly some host subroutines; and the DAP code, which is a collection of subroutines, written in DAP-FORTRAN. At least one of these subroutines must be, what is called, an "entry subroutine".

The entry subroutine is a parameter-less subroutine which is called by the host program as if it were written in normal FORTRAN. However, all its instructions are for execution on the DAP, and so, on its call, control is passed from the host to the DAP mcu, which then takes over the running of the program. If the programmer wishes, further subroutines may be called once the DAP has been entered. These will be internal to the DAP section of the job, and can have parameters, if required, which will be passed by address, rather than by value. It is only the entry subroutine which must have no parameters. Instead, values of variables are passed in and out of the DAP by means of FORTRAN named COMMON blocks. The way data is stored in the host is not the same as in the DAP, and so, before any values in a COMMON block can be used, they have to be converted to the DAP format (There are routines supplied for doing this, which have only to be called, usually from the entry subroutine, with the appropriate names as parameters.). Similarly, any output from the DAP must be converted to the host mode (again using standard routines) before the DAP section can be completed, and control passed back to the host. The DAP may be entered (and left) as many times during the running of a job as the programmer wishes, provided that one is prepared to accept the overhead in time that this will require. But, in the interests of speed of execution, it is better to limit leaving and reentering the DAP, to as few occurrences as possible. Indeed, with each of the programs that will be described in this thesis, there is only one entry subroutine, which is just called once. This does not mean, however, that we never re-enter the DAP, as we will now explain.

In a serial machine, a "tried and trusted" way of debugging a program is by tracing, i.e. to insert (possibly many!) "write statements" in the code, to print out the values of relevant variables, so that the programmer can discover if the program does what it was meant to. This technique can sometimes prove vital in finding inconspicuous errors in a piece of code. However, this cannot be done easily on the DAP. Values of variables can only be printed out by the host, and these would normally be passed from the DAP in a COMMON block, once the work of the entry subroutine, and any routines it may call, had been completed. Thus, to find the intermediate values of certain variables, we would be faced with writing a whole series of entry subroutines, each one containing a few more instructions than the previous one, running them in succession, and then comparing the results returned in the COMMON blocks - a very cumbersome procedure!

In order to avoid this, DAP-FORTRAN provides a facility for tracing the intermediate values of variables. Called, not surprisingly, a TRACE statement, it is used in exactly the same way as a "write statement", except that it causes the DAP to be left, the host entered, the required value(s) printed out, and then the DAP to be re-entered, with execution of the DAP program restarted at the instruction immediately following the TRACE statement. While such statements may be inserted anywhere in the DAP code, they have one disadvantage which will be mentioned later. Even so, this feature is extremely useful, as it makes less difficult what is, perhaps, the hardest part of DAP programming, namely, debugging a program and getting it to run! Of course, since TRACE statements necessitate leaving the DAP, they should be used sparingly in programs which are known to work correctly.

When a machine has such a definite structure as the DAP, this must be taken into account when producing programs for it, otherwise the computer's potential will, almost certainly, not be realised. Certainly, this is nothing new. For example, optimising compilers are written for a specific machine so that advantage can be taken of the features of its design, without the programmer having to know about them. Programming bit processors in parallel is not that simple, however. The problem lies in there being two different areas that must be considered before optimal performance can be reached, or even approached. The first concerns the parallelism of the machine, to make use of which normally involves the re-ordering or unrolling (or both) of loops, so that blocks of iterations can be performed in parallel. For many years now, such problems and their solutions have been discussed in the literature [Kuck 1980], and compilers have been written to detect pieces of code which could be performed in parallel, and then arrange for this to be done, with varying degrees of success. For example, an optimising compiler (called CFT) has been written for the CRAY-1 computer, which "vectorizes" innermost DO loops to take advantage of this particular machine's vector registers [Russell 1978].

However, it is in the second area that real problems stand in the way of compiler-based solutions. As we will discuss more fully later, one of the consequences of performing many tasks in parallel using bit-processors is that all the arithmetic involved must be done bitserially, which opens up a whole new field for optimisation and improvement. Certainly one could just perform in parallel exactly the same sequence of instructions as would be used on a conventional word-based machine. But this would mean ignoring much of the potential of the DAP. There are many algorithms which, while being relatively timeconsuming on word-based computers are relatively quick on the DAP (finding square roots is an example of this which will be discussed later). In addition, an array of bit processors provides the programmer with the scope for using bit-manipulating algorithms, which as we will also show later, can prove very effective. Such a simple approach to parallel programming as described above, will also mean the neglecting of the interconnection network, and the possibilities it makes available, like the technique of recursive doubling (again, see later). From the above, it should be clear that to get the best out of a machine like the DAP will certainly require much careful thought and planning, and probably involve different algorithms and techniques to those employed on a word-based machine. For this reason, at the present time, it is not practical to write a compiler which would produce from an existing serial program, very efficient code for the DAP, and the programmer has to decide how to organise the performing of the required tasks in a way that will capitalise on the DAP's form. To do this, one must be able to express the parallelism required.

To meet this need in a high-level language, a version of FORTRAN has been written specifically for the DAP, namely DAP-FORTRAN. One of the advantages in using a highlevel language is that, while the programmer will be aware of the general architecture of the computer (e.g. that it has 4096 processors), the low-level features of the design (e.g. that the processors are bit-serial, and are connected in an array) can be hidden. Of course, to use the processors most efficiently will probably require some knowledge of the latter, and even then, as we will describe later, DAP-FORTRAN can be used to express low-level concepts. The decision to extend an existing language (in this case, FORTRAN IV) rather than design a new one, was made because it was envisaged that most of the users of the DAP would be members of the scientific computing community, where in the past, FORTRAN has been the most popular language and that it would be easier for them to adapt to the new machine if they did not have to learn a completely new language.

The main extension provided by DAP-FORTRAN is in the data modes. Conventional FORTRAN has only one : namely, scalar mode. DAP-FORTRAN has, in addition to this, two new modes: vector and matrix. A vector, of a certain type, is the same as a 64-element array of scalars of that type, except that all the elements of the former will be operated on simultaneously. Similarly, a matrix is equivalent to a two-dimensional array (with 64 elements in each dimension) of scalars of the same type, where, again, all 4096 elements of the matrix can be processed at the same time. Thus, instead of using the following loops:

DO 10 I = 1,64DO 10 J = 1,6410 C(I,J) = A(I,J) + B(I,J)

to add the contents of corresponding locations of two 2-dimensional arrays (each of size  $64 \times 64$ ), we can simply say

$$C = A + B$$

where A, B, C are declared to be matrices of the desired type. This could also be written as

$$C(,) = A(,) + B(,)$$

where the two dimensions of each operand have been left empty, showing that they are what are called "constrained dimensions", and to be operated on in parallel. The inclusion of the constrained dimensions is optional, unless one is dealing with an array of matrices, in which case they must be included. For example, an array of INTEGER matrices, with 3 components, TEMP say, would be declared as

## INTEGER TEMP(,,3)

(The same convention applies to vectors, except that there is only one constrained dimension.).

Thus the iterations required can be expressed in terms of a single instruction. The same is true for the other arithmetic operations: subtraction, multiplication and division. It is worth mentioning that when you multiply two DAP-FORTRAN matrices together (using the arithmetic operator \*), what is performed is not the conventional matrix multiplication algorithm, but the forming of the product of the corresponding elements of the two operands. The other arithmetic operations : +, - and /, are similarly performed pointwise.

It is through the use of these two data modes that the programmer controls the parallelism of the machine. A matrix of type, say INTEGER, refers to 4096 scalars of that type, each one lying in the memory of a different processor, but all at the same address. The same is true for matrices of the two other numerical types in the language: REAL and LOGICAL. The fact that all the elements have the same address (in different memories) is very important, as will now be shown.

We have already mentioned how we imagine the processors to be arranged in a  $64 \times 64$  array. Let us imagine further, that all of the 16K bits of memory local to PE(1,1) are placed one on top of the other, resulting in a column, as it were, rising out of the processor. If we were to do this for every PE, then we could consider the DAP to be the shape of a cuboid, with the processors at the bottom, and the memory arranged in planes (each 1 bit deep) above them. Now, since all the elements of a matrix have the same address (but lie in different memories, and hence, columns in our analogy), we can imagine a matrix to be stored as a contiguous set of these store planes (hence the use of the term "vertical storage" to describe the representation of matrices).

The DAP can process only one store plane at a time, and so all arithmetic has to be performed by system-supplied software routines. One consequence of this is that we can choose the precision to which we work, and similarly, we can choose how many store planes each matrix will be allocated. However, as we have already remarked, if we require some processors to perform a task, then all the PE's have got to do it : we can only be selective about the storing of results. This is because the DAP cannot process just part of a store plane. It is a case of "all or nothing". So, if we had a matrix of integers, one of which had 33 bits in its binary representation, while all the others had less, then all the elements would have to be allocated 33 bits (i.e. the matrix would require 33 planes of the DAP store). In fact, in a DAP-FORTRAN program, we would need to set aside 40 bit planes for storing such a matrix because there is a (software) limit to the variety of precisions that DAP-FORTRAN INTEGER variables can have.

Normal FORTRAN supports at most two precisions: single and double, which, on a machine with a word size of 32 bits, would correspond to 32 and 64 bits, respectively, being allocated to integer variables. In addition to these lengths, DAP-FORTRAN offers the choice of 16, 24, 40, 48 and 56 bit integers (denoted by INTEGER n, where the integer is to be allocated n bits). A similar situation exists with the type REAL, but not with LOGICAL variables.

It is one of the important features of DAP-FORTRAN that LOGICAL variables only occupy a single bit of memory. This is far more efficient than the method often used in computers with word lengths of more than one bit, where up to 32 binary digits (i.e. one machine word) are used to store either a .TRUE. or a .FALSE. (Of course, having a machine word larger than one bit does have certain advantages when performing arithmetic operations, as will be mentioned later.) The DAP's storage arrangement means that a LOGICAL matrix will only require one bit plane to hold its values. Hence, a onedimensional array of LOGICAL matrices, with 32 components will be stored in 32 contiguous store planes, and thus be indistinguishable from a matrix of type INTEGER \* 4. From this we see that the EQUIVALENCE statement of normal FORTRAN can take on a whole new significance here. By making an array of LOGICAL matrices (of the right size) equivalent to, say, an INTEGER matrix, we can gain access to the bit patterns of the latter's elements.

The same is true for scalars and vectors. Scalars are stored horizontally (i.e. in a single plane), with the bit pattern (of length up to 64 bits) spread across consecutive processors in the same row, with the least significant bit stored in the rightmost processor. A LOGICAL vector is also stored in a single row, and so, by means of an EQUIVALENCE statement, the bits of the scalar's binary pattern can be manipulated in terms of the elements of the LOGICAL vector. (If the scalar is not of 8-byte precision, then it should be converted to this length, to match the size of the vector.) INTEGER or REAL vectors, however, are stored one element per row (as scalars above), and so require a whole store plane (since each has 64 elements). Thus, for a vector of type INTEGER, the  $64^{th}$  column of the plane will contain the least-significant bits of all 64 elements. Access to the binary digits can be obtained via a LOGICAL matrix, after any necessary length change, and the appropriate EQUIVALENCE statement.

Thus, by means of an EQUIVALENCE statement, we can have access to the binary patterns of numbers (although they are expressed in terms of the logical values .TRUE. and .FALSE. rather than the digits 1 and 0) directly from our high-level language. This allows the programmer to implement bit-manipulating algorithms (which are, of course, very suited to an array of bit processors) without having to resort to the complications of assembly code programming. As we will illustrate later, this feature has been made use of in the implementation of the Lehman algorithm on the DAP.

Returning to our analogy of the cuboid, we can see another use for LOGICAL matrices. We have considered the DAP to be 16,384 bit planes, stacked on top of the array of processing elements. But, since each PE contains 3 bit registers, we could think of there being 16,387 bit planes, with the lowest 3 planes containing the contents of the 3 registers, one register per plane. Thus all 4096 Activity bits (designated the A plane) could be assigned by means of a LOGICAL matrix. This is indeed possible; how it can be done is shown in the following short piece of a program to obtain the square roots of those elements of the real matrix NUMBERS which are positive.

LOGICAL MASK(,) REAL\*5 NUMBERS(,) REAL\*3 ROOTS(,)

MASK = NUMBERS.GE.0 ROOTS(MASK) = SQRT(NUMBERS) ROOTS(.NOT. MASK) = 0

We require the square roots of the elements of the real matrix NUMBERS, but have no guarantee that the latter are all non-negative. Trying to find the square root of a negative real number (even just one out of 4096) will cause a machine error; but only if an assignment of the "bogus" root is attempted. Thus, by identifying those processors with negative values (indicated by a .FALSE. in the LOGICAL array MASK), we can block or "mask out", the assignment of the root in these processors, and so avoid trouble. The masking takes place during the instruction

ROOTS(MASK) = SQRT(NUMBERS)

which causes the following course of action to take place: (a) all the elements of the matrix NUMBERS have their square roots taken but (b) only where the corresponding element of the A plane (which holds the matrix MASK) contains a .TRUE. will the value of the root be stored in ROOTS. We can also negate the mask so that all the locations not assigned above may be given some other value; in this case, 0.

This technique is extremely useful as, for instance, it allows us to implement "IF (condition) THEN (task 1) ELSE (task 2)" branches, where a mask would be set with the condition in the IF statement, and used in masked instructions to perform task 1. Then task 2 could be carried out, again using masked assignments, but with the negative of the previous LOGICAL matrix.