https://theses.gla.ac.uk/

Theses Digitisation:

https://www.gla.ac.uk/myglasgow/research/enlighten/theses/digitisation/

This is a digitised version of the original print thesis.

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses <u>https://theses.gla.ac.uk/</u> research-enlighten@glasgow.ac.uk

## The Fabrication of GaAs Membrane and GaAs/GaAlAs Heterostructure Field Effect Transistor Devices

A Thesis submitted to the Faculty of Engineering of the University of Glasgow for the degree of Doctor of Philosophy

by

Kim Yang Lee

16 55

May 1987

© Kim Yang Lee, May 1987

ProQuest Number: 10995585

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10995585

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

#### This thesis is dedicated to my parents.

Andrew weight and the state of the second second

and a second by a barght a barght and a start and a

#### **ACKNOWLEDGEMENTS**

I wish to express my appreciation and gratitude to Professor J. Lamb for the use of laboratory and computing facilities, and to my supervisor Dr. S.P.Beaumont and Professor C.D.W.Wilkinson for their invaluable advice and encouragement throughout this project.

Best of thanks are due to Dr. M. Al-Mudares for providing the simulated MESFET results, to Dr. John Davies for introducing me to the many delights of quantum mechanics, and to my predecessors Dr. W.S.Mackie, Dr. W.Patrick and Dr. S.A.Rishton for their encouragement and patience throughout the early stages of this work.

I also wish to express my thanks to my collaborators at Nottingham University; namely, Dr. D.P.Halliday, Mr. C. Payling and Professor L.Eaves.

support provided A.Stark The excellent technical bv and Ultrasmall Structures Group gratefully D.Gourlay of the is acknowledged. Best of thanks are also due to J.Critchton, J.Clarke, G.Boyle, L.Hobbs, K.Piechowiak and H.Anderson for their technical assistance. I would also wish to thank A.MacKinnon for the use of the GEC 4180 computer.

thanks colleagues office Special go to my and mates V.M.Airaksinen and D.M.Halliday for making my stay in the Department an eye opening experience, and to C.Reeves who shared the joys of thesis writing and numerous excursions to the 'Country Club'. Best of thanks are due to J.Frost, S.Thoms and I.McIntyre for many useful discussions. I would also like to thank Jim (the Cat) Adams and A.Jezierski for keeping me roofed through the final few chapters of this thesis. The occasional proof reading of this thesis (under duress) by J.Turnbull, S.McMeekin, K.Thomas and A.Jennings

is gratefully acknowledged. Thanks are also due to R.M.K.Cheung for providing some results.

I am grateful to the University of Glasgow for sponsorship of this work. Financial contribution from the Lee Foundation, Malaysia, is also acknowledged.

Finally, I wish to express my gratitude to my family for their support and encouragement through the duration of my stay in U.K.

1. A second se

#### Summary

The principal aim of the work presented in this thesis was to develop the techniques for fabricating FET devices on 50 nm thick active  $n^+$ -GaAs membranes. The use of these membranes for electron beam lithography offers the advantage of very high resolution patterning due to the lack of backscattering, and the use of high contrast STEM (Scanning Transmission Electron Microscope) microscopy for very high resolution alignment and analysis.

The electron beam lithographic techniques for fabricating nanostructures on thin substrates (principally thin carbon and  $Si_3N_4$  membranes) are well established in this Department through the effort of previous workers. These techniques were successfully combined with very high resolution alignment to pattern interdigital metal gratings. With 8 nm probe size, alignment accuracy of better than 3 nm was demonstrated and gratings with 24 nm centre—to—centre spacing were fabricated on 60nm thick  $Si_3N_4$  membranes.

The membrane processing techniques were transferred to GaAs and MESFETs successfully fabricated. MESFETs were also fabricated with a fine pitch grating in place of the gate. Electrical characteristics of these devices indicated that surface effects dominated. Comparison between membrane MESFETs and conventional substrated MESFETs permitted an analysis of the effects of the substrate on device operation.

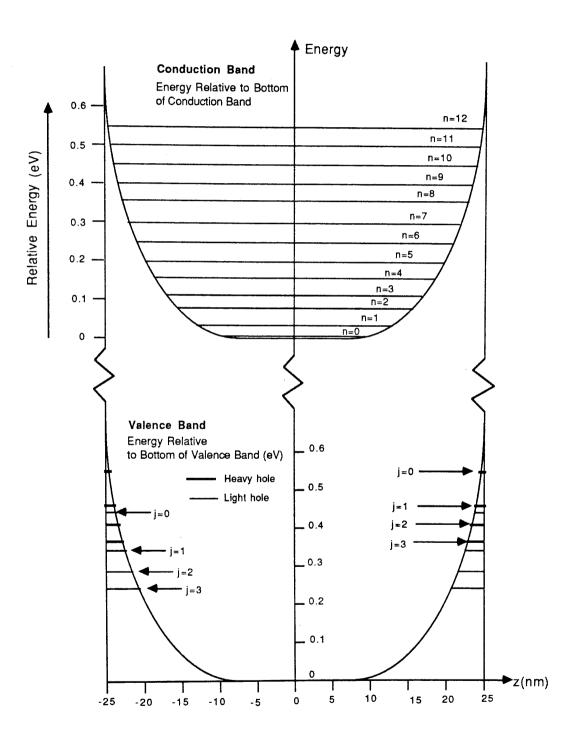

Electrical measurements on membrane devices suggest carriers are confined to a thin layer. A theoretical investigation performed in collaboration with Dr. John Davies of this Department indicates that carrier energies are quantised. In order to substantiate this, GaAs membranes were characterised optically using transmission spectroscopy and photoconductivity. The use of membranes permitted a signal corresponding to the higher energy band—gap (L–L band) of GaAs to be resolved.

Finally, GaAs MESFETs with gate-lengths of between  $0.08 \mu m$ and  $0.2 \mu m$  were fabricated on a MBE grown heterostructure  $(n^+ - GaAs/$  undoped  $Ga_{0.3}Al_{0.7}As)$ . These devices showed excellent d.c. characteristics with very high transconductance and low output conductance. However, interface effects which degrade pinchoff characteristics were observed.

States and Street States and Street and

· 11. 2. 1. 1. 紧张静地走动出力了杂剧。\$P\$ 在心中透着了话

. . .

1. S. A.

e fe - <sup>1</sup> - **Februarie** and see a

a sharing the second second

· 医白白云云 网络夏日

·公司会会 · 神秘的过去式

literezon : fra fabrication de Case Mesterias

President and Article of the Permetican

Note: Filler for the set of the state of the

i de participada de la composición de l

- Elizabeth Borth Children and

#### **CONTENTS**

| Chapter | 1 General Introduction                         |    |

|---------|------------------------------------------------|----|

| 1.1     | Introduction                                   | 1  |

| 1.2     | Project Aims                                   | 1  |

| 1.3     | Thesis Outline                                 | 3  |

|         |                                                |    |

| Chapter | 2 Electron beam Processing                     |    |

| 2.1     | Introduction                                   | 6  |

| 2.2     | Electron Bram Lithography                      | 6  |

| 2.2.1   | Background                                     | 6  |

| 2.2.2   | The EBL System                                 | 6  |

| 2.2.3   | Resist                                         | 8  |

| 2.3     | Alignment Techniques                           | 9  |

| 2.3.1   | Low Resolution Alignment Technique             | 10 |

| 2.3.2   | Very High Resolution Alignment                 | 11 |

| 2.3.2.1 | Alignment Method                               | 12 |

| 2.4     | Fabrication of Interdigital Gratings           | 14 |

| 2.4.1   | Introduction                                   | 14 |

| 2.4.2   | Fabrication Procedure                          | 14 |

| 2.5     | Fabrication of MOP masks                       | 16 |

| 2.5.1   | Fabrication Procedure                          | 16 |

|         |                                                |    |

| Chapter | 3 The Fabrication of GaAs Membranes            |    |

| 3.1     | Introduction                                   | 19 |

| 3.2     | Fabrication of 50nm Thick n <sup>+</sup> -GaAs |    |

|         | Membranes                                      | 19 |

| 3.2.1   | Fabrication Outline                            | 19 |

| 3.2.2   | Material                                       | 20 |

| 3.2.3   | Etches                                         | 20 |

| 3.2.4   | Membrane Fabrication Procedure                 | 21 |

| 3.2.5   | MBE vs MOVPE                                   | 26 |

| 3.3     | Electron Beam Lithography                      | 27 |

| 3.3.1   | Resolution Tests                               | 27 |

| 3.4     | The Fabrication of FET devices on              |    |

|         | GaAs Membranes                                 | 30 |

| 3.4.1   | Requirements for Membrane Device               |    |

|         | Fabrication                                    | 30 |

| 3.4.1.1 | Lithography                       | 30 |

|---------|-----------------------------------|----|

| 3.4.1.2 | Isolation                         | 31 |

| 3.4.1.3 | Ohmic Contacts                    | 32 |

| 3.4.1.4 | Schottky Contacts                 | 34 |

| 3.4.2   | Membrane FET Fabrication Strategy | 35 |

| 3.5     | Discussions and Conclusions       | 35 |

## Chapter 4 The Fabrication of MESFETs and LSSLs on Thin

| Active G | GaAs Membranes                       |    |

|----------|--------------------------------------|----|

| 4.1      | Introduction                         | 39 |

| 4.1.1    | Membrane MESFETs                     | 39 |

| 4.1.2    | LSSL                                 | 40 |

| 4.2      | Fabrication of Membrane FET devices  | 41 |

| 4.2.1    | Device Design and Fabrication        |    |

|          | Outline                              | 41 |

| 4.2.2    | Low Resolution Fabrication Process   |    |

|          | Steps                                | 43 |

| 4.2.2.1  | High Resolution Alignment            | 48 |

| 4.2.3    | Fabrication of MESFETs               | 48 |

| 4.2.3.1  | High Resolution Patterning of        |    |

|          | Drain-Source Contacts                | 48 |

| 4.2.3.2  | Gate Level                           | 49 |

| 4.2.3.3  | Gate Metallisation                   | 49 |

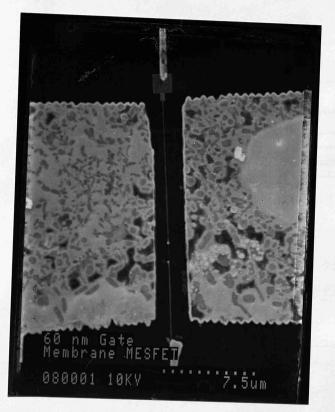

| 4.2.4    | Fabrication of LSSLs                 | 50 |

| 4.2.4.1  | Grating Patterning and Metallisation | 50 |

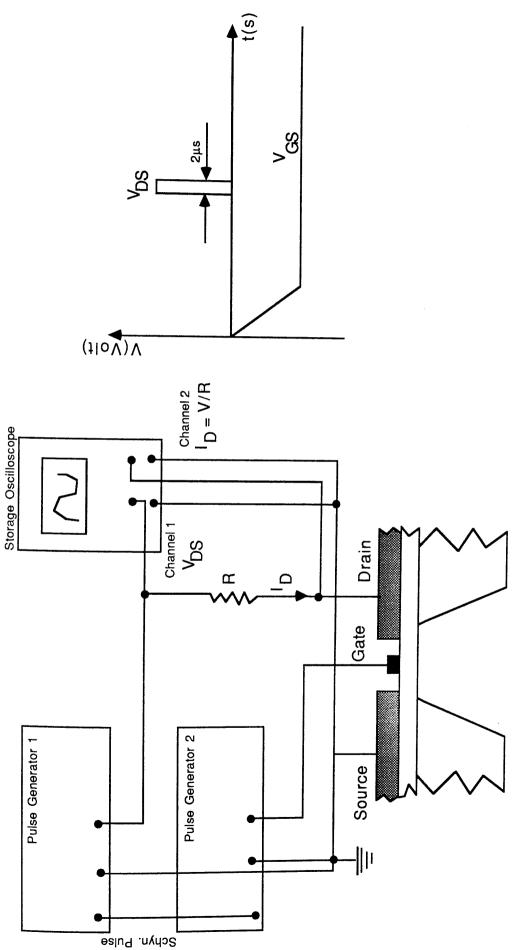

| 4.3      | Electrical Testing                   | 50 |

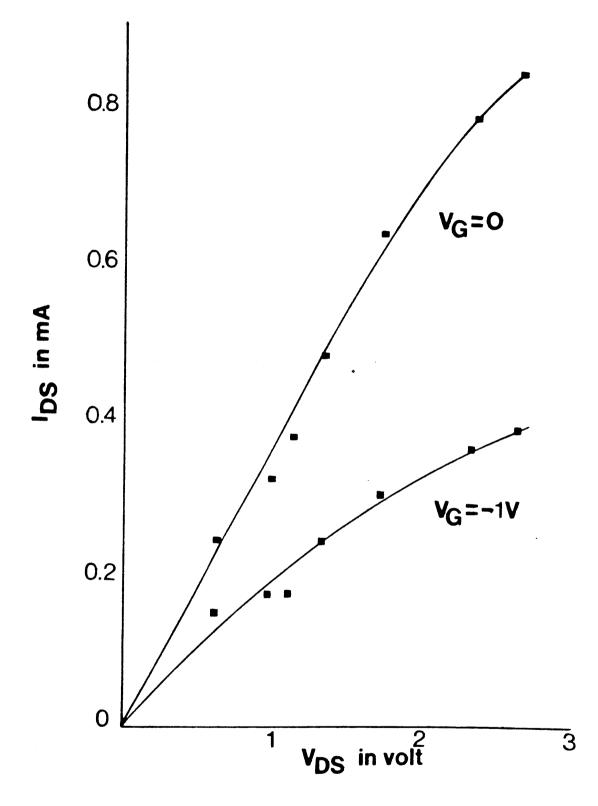

| 4.3.1    | Membrane MESFETs                     | 51 |

| 4.3.2    | LSSLs                                | 51 |

| 4.4      | Alternative Membrane MESFETs         |    |

|          | Fabrication Method                   | 52 |

| 4.4.1    | Fabrication Procedure                | 53 |

| 4.4.2    | Electrical Testing                   | 55 |

| 4.5      | Discussion                           | 57 |

| 4.5.1    | Device Operation and Interface       |    |

|          | Quality                              | 57 |

| 4.5.2    | Comparisons of Device Operation of   |    |

|          | Substrated and Unsubstrated MESFETs  | 58 |

| 4.5.2.1  | Substrate Effects                    | 59 |

|          |                                      |    |

| 4.5.2.2 | Gate-length and Sur | face States | Effect 60 |

|---------|---------------------|-------------|-----------|

| 4.5.3   | LSSLs               |             | 61        |

| 4.6     | Summary             |             | 62        |

## Chapter 5 Characterisation of 50nm Thick Active GaAs Membranes

| 5.1     | Introduction                          | 67 |

|---------|---------------------------------------|----|

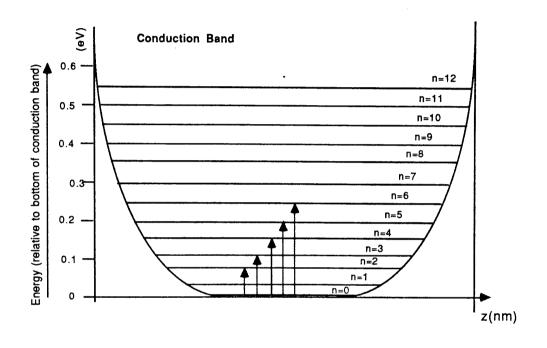

| 5.2     | Calculation of Confined Energy States |    |

|         | in a 50nm Thick GaAs Membrane         | 68 |

| 5.3     | Experimental                          | 75 |

| 5.3.1   | Basic Principles of Photo-absorption  |    |

|         | and Photoconductivity Measurements    | 75 |

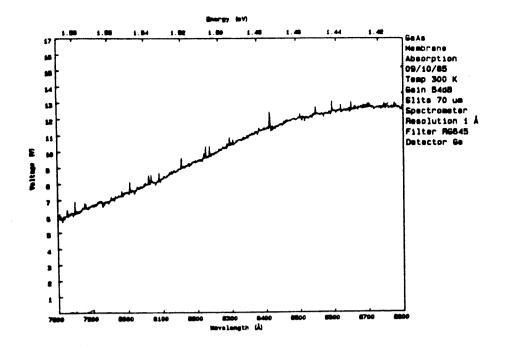

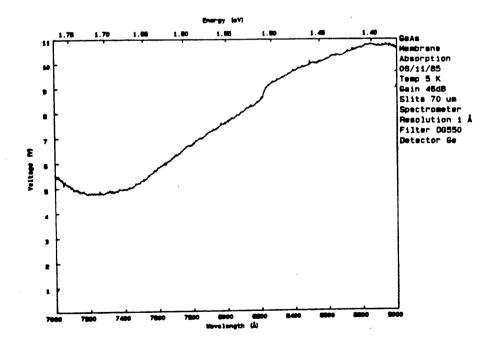

| 5.3.2   | Photo-Absorption Measurements         | 77 |

| 5.3.2.1 | Method                                | 77 |

| 5.3.2.2 | Results                               | 78 |

| 5.3.2.3 | Discussion                            | 79 |

| 5.3.3   | Photoconductivity Measurements        | 83 |

| 5.3.3.1 | Method                                | 83 |

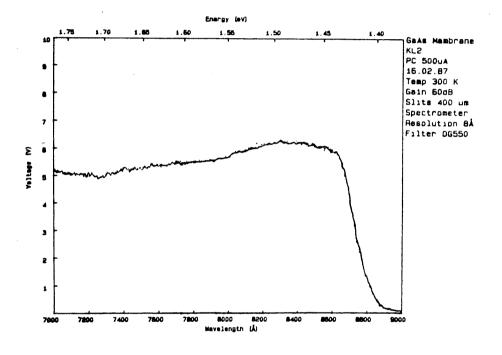

| 5.3.3.2 | Results                               | 84 |

| 5.3.3.3 | Discussion                            | 85 |

| 5.4     | Conclusions                           | 88 |

## Chapter 6 The Fabrication of Very High Transconductance Short Channel GaAs MESFETs with $Ga_{0.3}Al_{0.7}As$ Buffer Layer

| 6.1     | Introduction                                                   | 91  |

|---------|----------------------------------------------------------------|-----|

| 6.2     | Device Operation of Short Gate-length                          |     |

|         | MESFETs                                                        | 92  |

| 6.2.1   | Substrate Effects: Undoped GaAs Buffer                         |     |

|         | Layer vs Undoped Ga <sub>0.3</sub> Al <sub>0.7</sub> As Buffer |     |

|         | Layer                                                          | 94  |

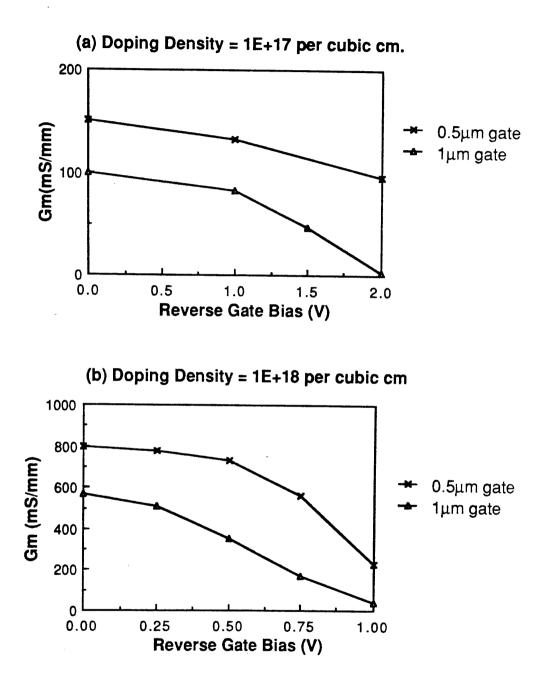

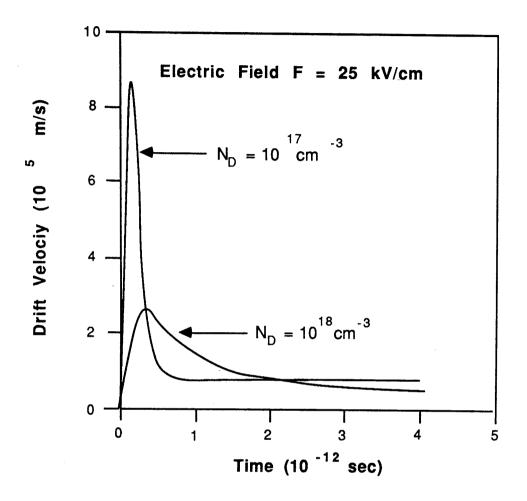

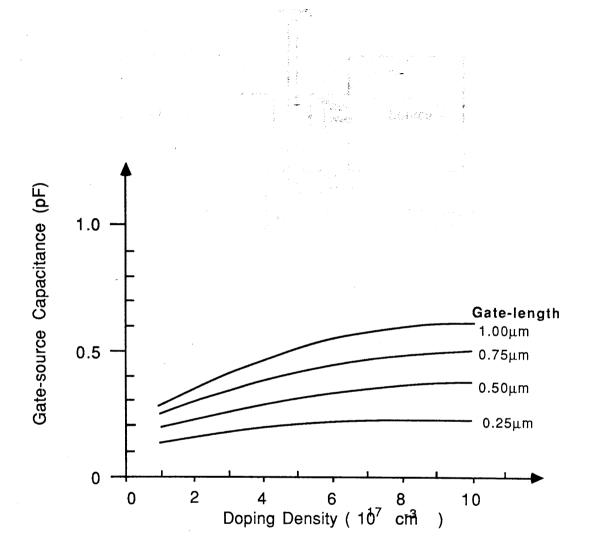

| 6.2.2   | Effect of High Doping Density                                  | 96  |

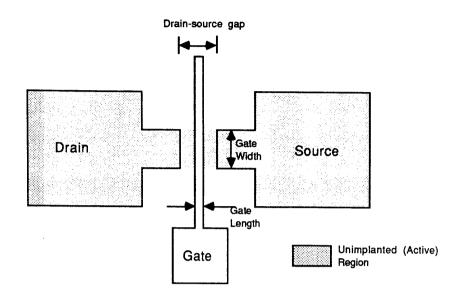

| 6.3     | Experimental: Fabriaction of GaAs MESFETs                      | 98  |

| 6.3.1   | MESFETs Design and Fabrication Outline                         | 98  |

| 6.3.2   | Fabrication Procedure                                          | 100 |

| 6.3.2.1 | Ohmic Level                                                    | 100 |

| 6.3.2.2 | Isolation Level                                                | 100 |

| 6.3.2.3 | Gate Level                                                     | 101 |

| 6.3.2.3.1 | Gate Alignment                         | 101 |

|-----------|----------------------------------------|-----|

| 6.3.2.3.2 | Gate Metallisation                     | 102 |

| 6.3.2.3.3 | Gate Recessing                         | 103 |

| 6.4       | Results and Discussions                | 105 |

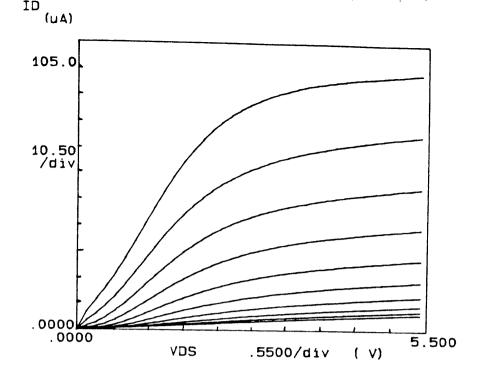

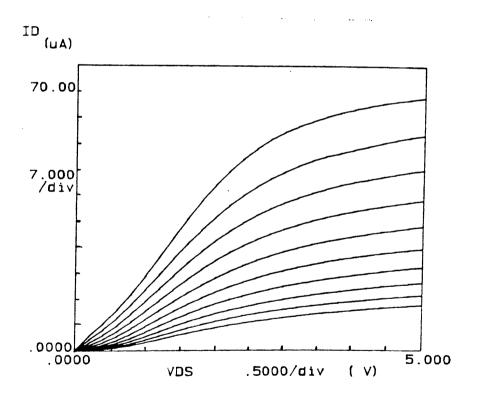

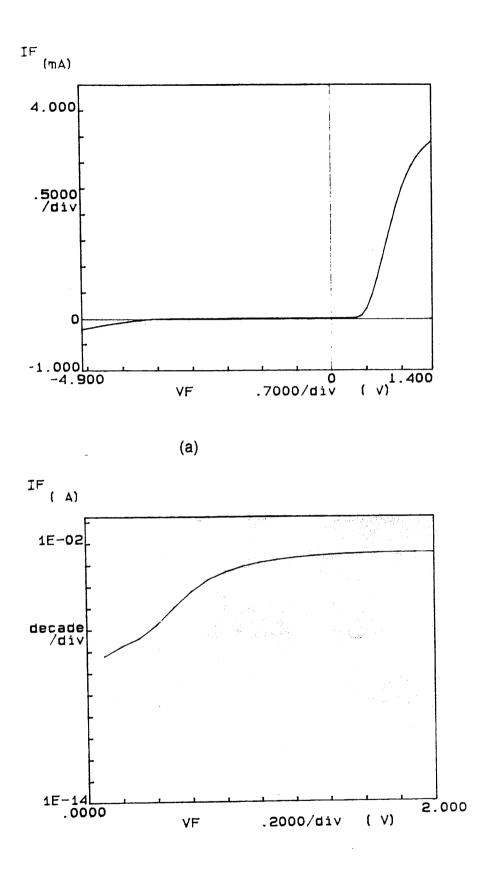

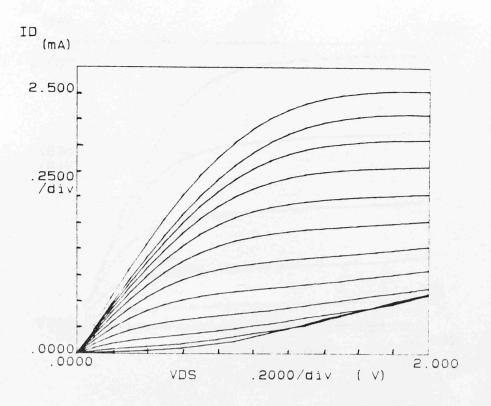

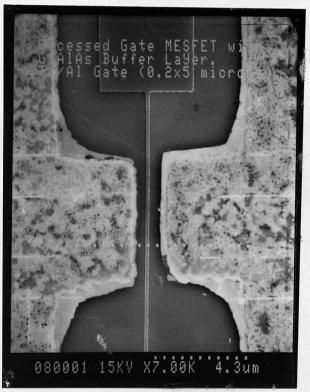

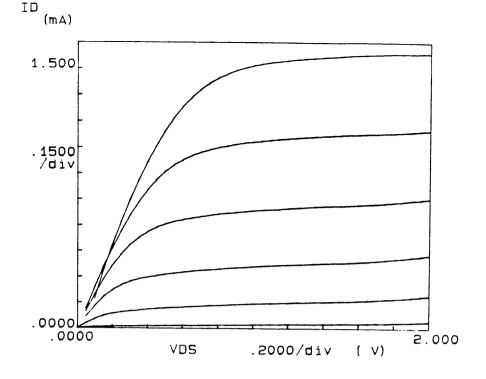

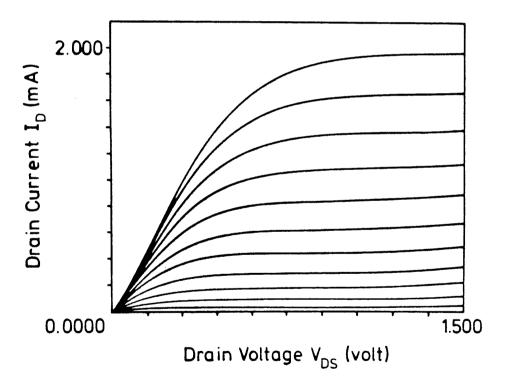

| 6.4.1     | I-V Characteristics                    | 105 |

| 6.4.2     | Effects of Recessed Depth on Device    |     |

|           | Operation                              | 106 |

| 6.4.3     | Quasi Two Dimensional Analytical Model |     |

|           | GaAs MESFETs                           | 109 |

| 6.5       | Conclusions                            | 111 |

|           |                                        |     |

a the application of the second second and the second second second second second second second second second s

- Electron and the stand state of the state

the theory all philling of the stand of the

and accord Representation and a constitution into the second states in the

a an an the second second and the second second

a the state tests description of provide the second second

and a to a serie character and control alors and frequencies for

and a start of the address thereight a stranger that the start of the start of the start of the start of the st

an in the second second subscription and the second second second second second second second second second sec

ing the state of the **Bellin**t of Belling and the state of the

#### Chapter 7 Conclusions

the Paris of Marsh

115

an da ser a tra

#### **1.1 Introduction**

The resolution limiting effect of backscattering in electron beam lithography can be eliminated by the use of thin (or electron transparent) substrates (1.1). The fabrication of 10 nm metal lines and gratings with 40 nm centre-to-centre spacing on 60 nm thick Si<sub>3</sub>N<sub>4</sub> membranes (1.2) represents the highest resolution structures formed by electron beam lithography using polymer resists (1.3). Thin substrates also allow the use of high contrast STEM microscopy for very high resolution alignment. On 60nm thick Si<sub>3</sub>N<sub>4</sub> membranes, alignment accuracy of 3nm has been demonstrated using an 8nm spot size (1.2). Moreover, wide latitude in exposure and process control are available for making nanostructures on thin substrates (1.4). Therefore, from a research point of view, thin semiconductor membranes may be suited the fabrication of experimental structures requiring very high to resolution lithography (i.e. beyond the resolution limits for patterning on solid substrates).

#### 1.2 Project Aims

The principal aim of this project was to develop the techniques for fabricating FET devices at the limit of electron beam lithography on thin active GaAs membranes. Of particular interest to this work were Lateral Surface Superlattices (LSSLs) and very small geometry MESFETs. Such devices may exhibit electronic properties dominated by quantum and ballistic transport phenomena. Interesting effects predicted in superlattices include negative differential resistance (1.5) and Bloch oscillations (1.6) thought to be at above 1000GHz (compared with the maximum achievable of about 100GHz by present devices such as the Gunn diode)(1.7). In MESFETs, ballistic transport **may occur** if the distance electrons have to travel is shorter than their mean free path (1.8-9). This would enable the device to operate at extremely high speed.

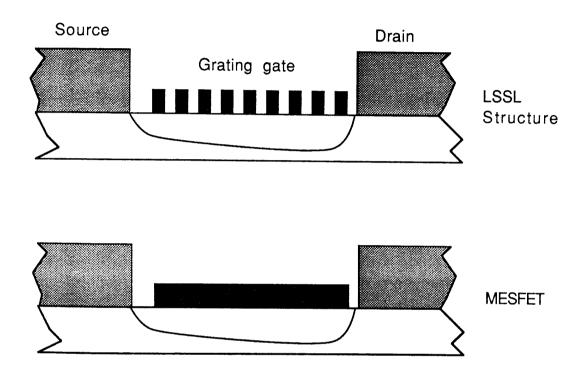

The structure of the LSSL was envisaged to be similar to the membrane MESFET but with a metal grating in place of the gate. In order to observe superlattice effects, the period of the grating has to be comparable to electron scattering length (between few tens to few hundreds of nanometres in GaAs). On thin substrates, such gratings can be fabricated with good reproducibility and reliability using electron beam lithography.

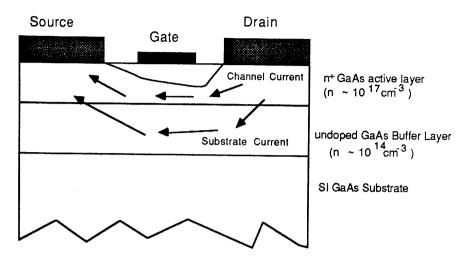

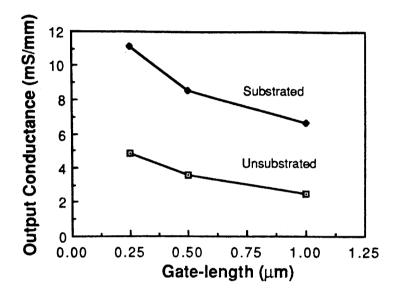

In addition to the lithographic benefits gained, fabricating MESFETs on GaAs membranes also provides a means of directly investigating the effects of the substrates on GaAs MESFETs characteristics. Relevent to this work is the influence of the substrates on the performance of short gate-length MESFETs. Decreasing the gate-length can result in worse d.c. characteristics, typified by increased output conductance and poorer saturation and pinchoff characteristics. This trend is clearly demonstrated experimentally by Jaeckel et al (1.10). Theoretical studies (1.11-12) indicate that the effects are partly due to injection of carriers from the active channel into the substrate. Therefore, a short gate-length MESFET fabricated on a membrane may exhibit superior characteristics to that on solid substrate. This was the subject of investigation in the second part of the thesis.

The electron beam lithographic techniques used throughout this work are reviewed in Chapter 2. In addition, a method for fabricating interdigital gratings on 60nm thick  $Si_3N_4$  membranes is described. This allows patterning of gratings with centre-to-centre spacings smaller than the resolution limits imposed by interproximity and resist effects. The finest gratings fabricated consisted of 16nm lines with 24nm pitch which are the closest spaced gratings reported on any substrates.

50nm thick GaAs membranes with  $3 \times 10^{18}$  cm<sup>-3</sup> doping density were fabricated by selective etching of GaAs/Ga<sub>0.3</sub>Al<sub>0.7</sub>As heterostructures grown by molecular beam epitaxy (MBE) and metal organic vapour phase epitaxy (MOVPE) (Chapter 3). On these membranes, high resolution electron beam patterning was demonstrated together with the formation of ohmic and Schottky contacts. Finally, a strategy for fabricating FET devices was developed

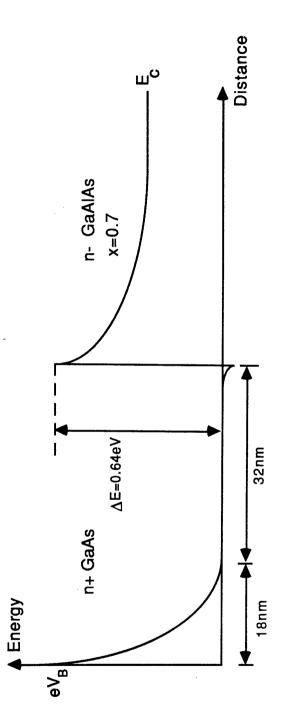

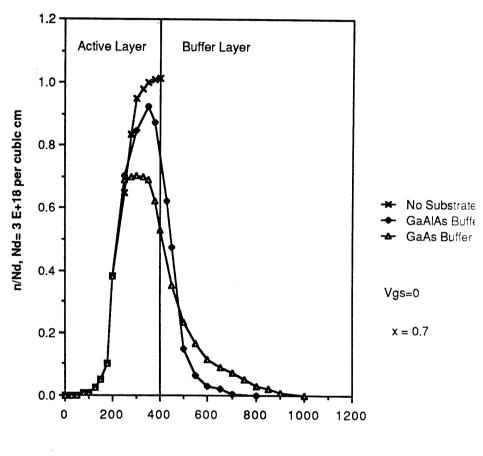

The fabrication of membrane MESFETs and LSSL structures is set out in Chapter 4 along with an alternative method for fabricating membrane MESFETs. Electrical characteristics of the membrane devices were measured which indicated that surface effects dominated. A comparison of the performances of membrane MESFETs to conventional MESFETs on solid substrate was made in order to study substrate effects. In the course of this work, it was discovered that degrades short gate-length **MESFETs** which carrier injection performance as mentioned earlier was suppressed by the use of a Ga<sub>0.3</sub>Al<sub>0.7</sub>As buffer layer.

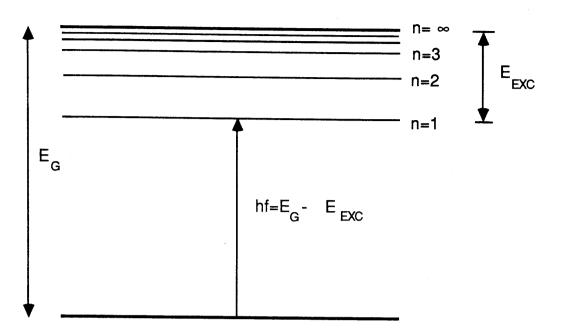

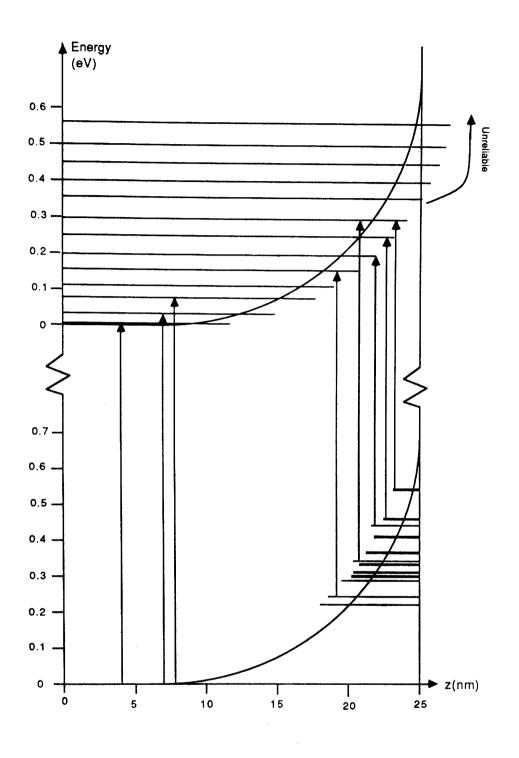

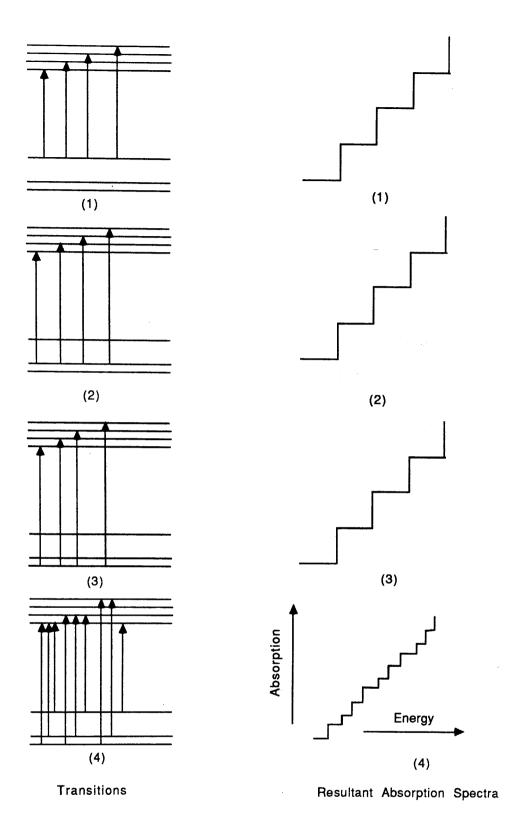

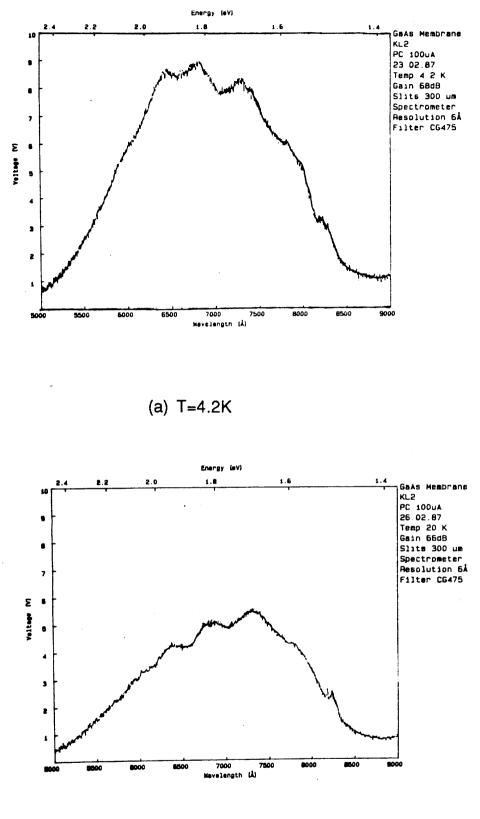

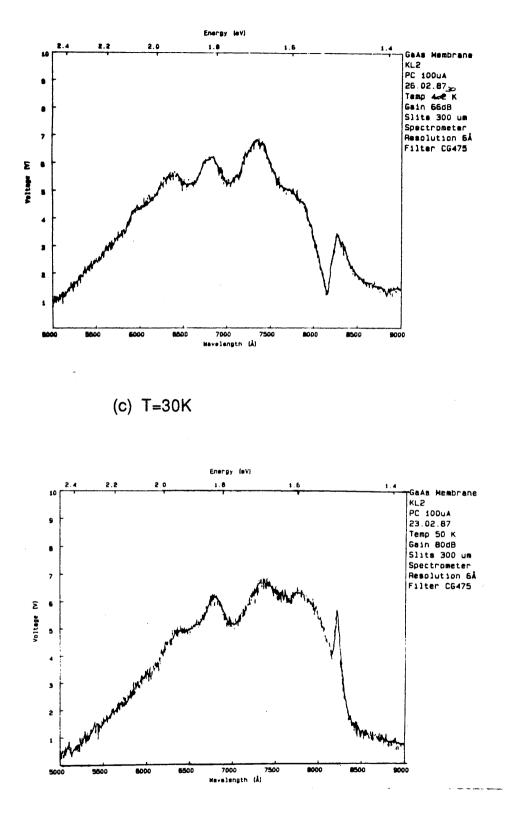

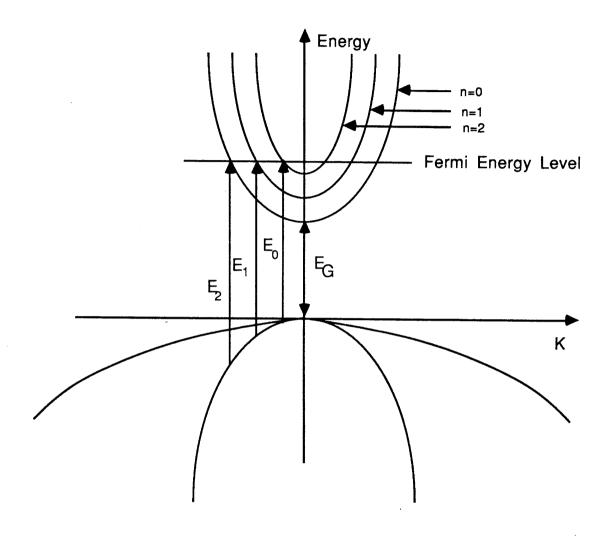

Electrical measurements on membrane devices in Chapter 4 suggest that carriers are confined to a thin layer. A theoretical investigation indicates that the confinement results in quantisation of

page 3

the carrier energies (Chapter 5). Photo-absorption and photoconductivity measurements were performed to probe the calculated quantised energy levels.

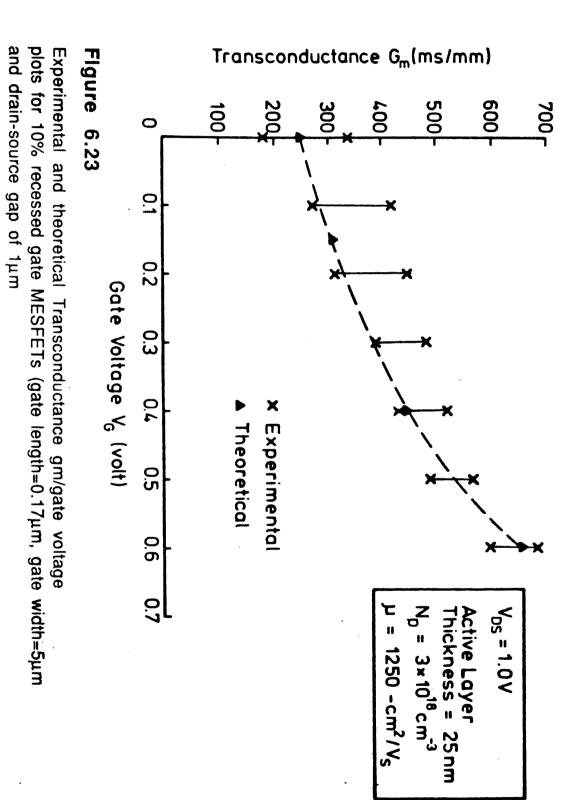

The fabrication and evaluation of GaAs MESFETs with  $Ga_{0.3}Al_{0.7}As$  buffer layer with gate-lengths of between  $0.08 \mu m$  to  $0.2 \mu m$  are described in Chapter 6. These devices exhibit excellent d.c. characteristics with very high transconductance and low output conductance. The performance of the devices was observed to be affected by the GaAs/GaAlAs interface. A discussion of this is given.

Finally, a summary of the major findings of this work and suggestions for future work are given in Chapter 7.

#### **Chapter 1** References

(1.1) S.Mackie and S.P.Beaumont, "Materials and Processes for Nanometer Lithography", Solid State Tech. 28, No. 8, pp117-123, Aug. 1985.

(1.2) W.S.Mackie, PhD Thesis, Glasgow University, 1984.

(1.3) A.N.Broers, "High Resolution Lithography (Some Comments on Limits and Future Possibilities", in The Physics and Fabrication of Microstructures and Microdevices, Edited by M.J.Kelly and C.Weisbuch, Springer Proc. in Physics 13, pp2-14, 1986.

(1.4) W.Patrick, PhD Thesis, Glasgow University, 1986.

(1.5) Esaki and Tsu, "Superlattice and Negative Differential Conductivity in Semiconductors", IBM Res. Dev. Vol.14, pp61-65, 1970.

(1.6) R.K.Reich, R.O.Grondin and D.K.Ferry, "The Bloch FET – A

Lateral Surface Superlattice", IEEE Electron. Dev. Lett., Vol.

EDL-3, No.12, pp381-383, 1982.

page 4

(1.7) T.Sakamoto, "Moving Toward Future Electron Devices", JEE pp28-31, July, 1982.

(1.8) M.S.Shur and L.F.Eastman, "Ballistic Transport in Semiconductors at Low Temperatures for Low Power, High Speed Logic", IEEE Trans. Electron. Dev., Vol. ED-26, pp1677-1683, 1979.

(1.9) L.F.Eastman, R.Still, D.Woodward, N.Nondeker, C.E.C.Wood,

M.Shur and K.Board, "Ballistic Motion in GaAs at Room

Temperature", Elect. Lett., 16, pp524-525, 1980.

(1.10) H.Jaeckel, V.Graf, B.J.Van Zeghbroeck, P.Vettiger, "Scaled GaAs MESFET's with gate-length down to 100nm", IEEE Electron. Dev. Lett., Vol. EDL-7, No.9, pp522-524, 1986.

(1.11) M.Reiser, "Two Dimensional Analysis of Substrate Effects in Junction FETs", Elect. Lett., Vol.6, No.16, pp493-494, 1970.

(1.12) Y.Awano, K.Tomizawa, N.Hashizame, M.Kawashima, "Monte Carlo Particle Simulation of A GaAs Short Channel MESFET", Elect. Lett., Vol. 19, No.1, pp20-21, 1983.

人名法法 精神 化分子

#### 2.1 Introduction

This chapter gives an overview of the technology used in the fabrication of micro- and nano-structures. As detailed reviews of electron beam lithographic processing can be found in the theses of Mackie (2.1), Rishton (2.2) and Binnie (2.3), only brief description of the main processes will be given here.

2.2 Electron Beam Lithography

#### 2.2.1 Background

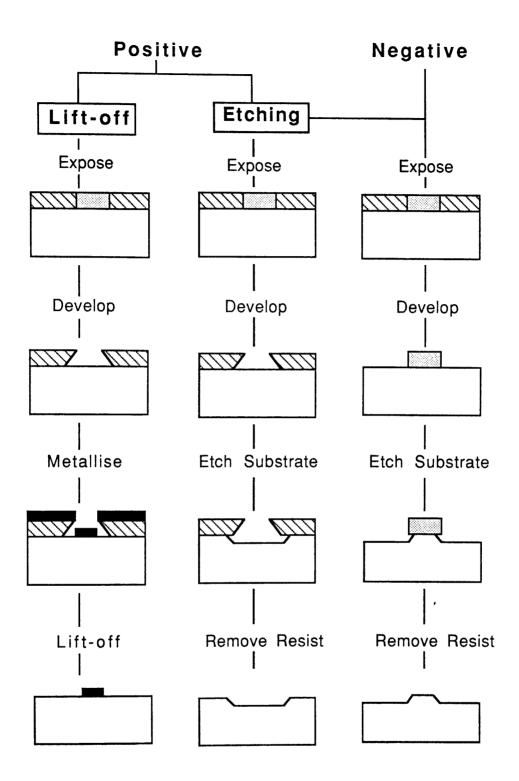

In Electron Beam Lithography (EBL), a focused electron beam is deflected in a controlled manner over an electron sensitive material (usually polymer) known as a resist. The irradiation modifies the resist's molecular structure such that either the exposed or the unexposed resist can be dissolved selectively in a developer. The developed resist layer can then be used either as a stencil to transfer a metallic pattern (liftoff process) or as a mask for etching. The process is illustrated in Figure 2.1.

#### 2.2.2 The EBL System

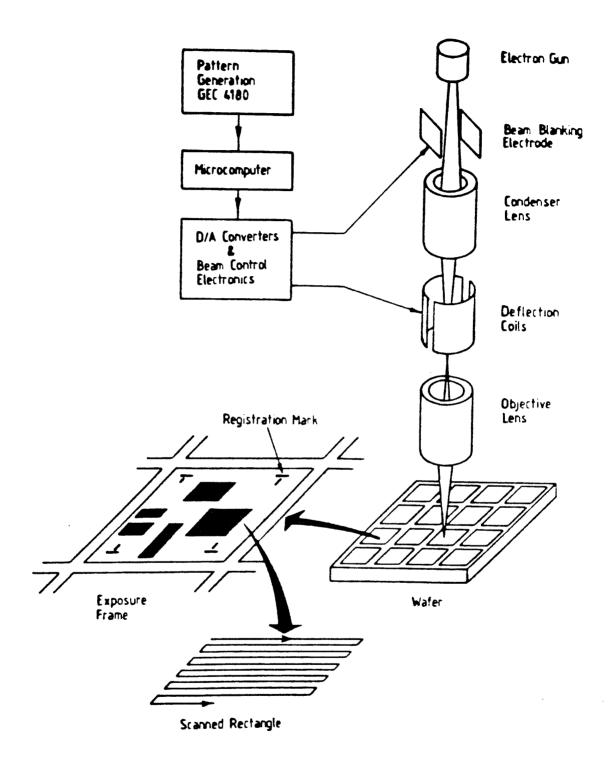

The Glasgow EBL system is shown schematically in Figure 2.2. The key components of the system are: The Philips machine has been modified for electron beam writing. Its essential features are:

a) electron spot sizes ranging from 8 nm to 1 micron

b) variable accelerating voltage from 1.5 to 80 kV

c) a specially fitted transmission detector for Scanning Transmission Microscopy (STEM)

d) a fully eucentric goniometer on which a specimen can be positioned in the X and Y directions in 1  $\mu$ m steps and rotated with an accuracy of 1/68th of a degree

e) X- and Y- electronic beam shifters for fine positioning in the X and Y directions of up to  $\pm 10 \ \mu m$

f) X- and Y- Varymag control which allows the magnification and therefore frame size in the X and Y directions to be increased continuously by a factor between 1 and 2.5

g) beam blank which, when switched on, deflects the beam into an aperture thus avoiding unwanted exposure.

#### GEC 4180 Computer

Pattern files are designed, generated and edited in the GEC 4180 computer using an interactive pattern editor called DESIGN (2.1).

#### ITHACA Microcomputer

This is linked to the GEC 4180 computer and the electron microscope. Pattern files generated by DESIGN are transferred to the microcomputer where they are stored in a disc. When a program (EBSS) is run on the microcomputer, the pattern data is fed into the scan generator which controls the beam deflection via D/A converters connected to the scan coils.

#### 2.2.3 Resist

Resists are classified as either positive or negative, depending on how they respond to exposing radiation (2.1-4). Positive resists are rendered more soluble and is dissolved selectively in a developer. The reverse effect occurs for the negative resists. This distinction is illustrated in Figure 2.1.

The positive resists used were Poly(Methyl Methacryalate) (PMMA) with molecular weights of 185,00 and 350,000. Two resist systems were used:

1) 1  $\mu$ m thick layer 185,000 MW PMMA

2) a bilayer resist system consisting typically of a 20 nm thick layer of 350,000 MW PMMA on a 100 nm thick 185,000 MW PMMA layer.

Resist (1) is obtained by spinning 15% w/w of the PMMA solution (in chlorobenzene) at 5000 rpm for 60s. For resist (2), 4% w/w 185,000MW PMMA solution (in xylene) and then 4% w/w 350,000 MW PMMA (in xylene) are spun for 60s at 6000 rpm and 8000 rpm respectively. The bottom layer is baked at  $180^{\circ}$ C for at least 1 hour before coating on the top resist layer. Both resist systems are hardened by baking at  $180^{\circ}$ C for at least an hour before exposure. It is necessary to bake the resists overnight at  $180^{\circ}$ C if they are to be used as wet etch masks.

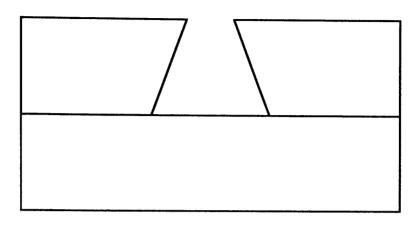

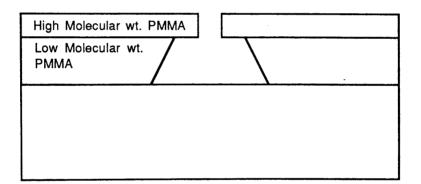

Resist (1) is used for patterning coarse features requiring thick metallisation while the bilayer resist is suitable for defining high resolution patterns. The developers are 1:1 MIBK:IPA and 1:3 MIBK:IPA for the thick resist and the bilayer resist respectively. Both resist systems are thought to develop into undercut profiles (Figure 2.3) which facilitate lift-off. In the case of resist (1), the undercut profile results from the divergence of the electron beam by electron scattering as it passes through the resist film (2.2). The undercut in resist (2) arises because the lower resist layer is more sensitive than the top layer. Therefore, when the resist is developed, more material is dissolved from the bottom layer, leaving an undercut profile as shown in Figure 2.3 (2.5).

#### 2.3 Alignment Techniques

Alignment is necessary for positioning a pattern in one process level accurately with respect to another pattern defined in a previous level. Two alignment techniques were used, one for low resolution work on thick substrates and the other for high resolution alignment on thin substrates. The techniques rely on the fact that the position of an image seen on the screen of the electron microscope corresponds to the position of the electron spot on the specimen.

#### **POSITION**

POSITION (2.1) is a computer program for calculating exposure positions on a wafer in terms of the goniometer coordinates. The positions are aligned to the wafer axes with the bottom left corner taken as the reference point and are spaced at regular intervals in the X and Y directions on the wafer. Therefore, these positions can be located at a subsequent lithographic level using POSITION i.e. the program facilitates approximate positioning required for alignment.

#### 2.3.1 Low Resolution Alignment Technique

This technique was used extensively for alignment of coarse features at X80 magnification (1.5 by 1.2 mm frame size) on thick substrates. An example is in the alignment of isolation and ohmic levels in the fabrication of GaAs MESFETs (Chapter 4).

#### **Registration Marks**

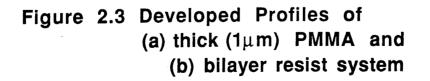

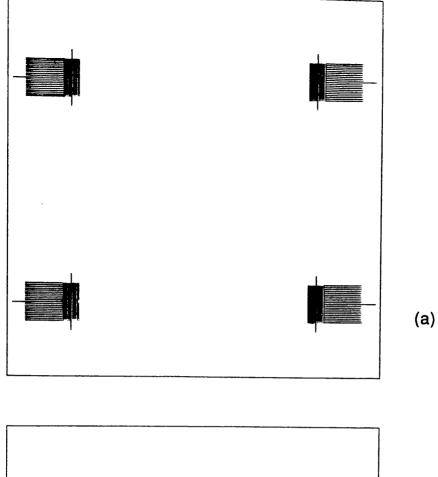

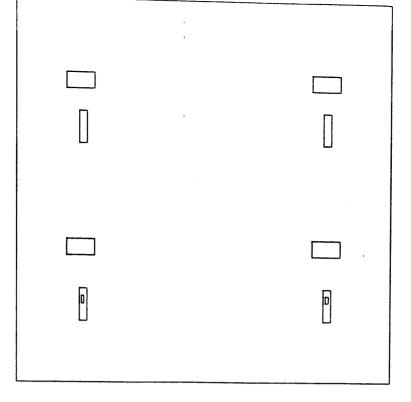

The standard registration mark pattern is shown in Figure 2.4. It consists of a pair of rectangles aligned in the horizontal and vertical directions to form a T- shape near each corner.

#### Coarse Alignment

Using POSITION, the sample is moved approximately to the first exposure site. A coarse alignment pattern which consists of a 20 pixel pitch (horizontal) grating and partial outlines corresponding to the top horizontal rectangles of the alignment marks is scanned at a speed of 2  $\mu$ s per pixel. The scan speed is the fastest that can be driven by the scan generator. The scanned pattern allows the top pair of T-shape rectangles to be viewed thus enabling the operator to determine how the exposure frame is positioned with respect to the registration marks. At this stage, there is usually a significant offset between the scanned partial outlines and the corresponding rectangles

in the X- and Y- directions and in the orientation of the wafer. These offsets are corrected approximately by dead reckoning (i.e. with no image on the SEM screen) and then checked by scanning the alignment pattern for a second time.

#### Fine Alignment

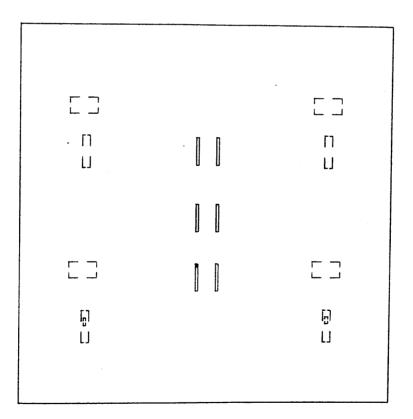

Two fine alignment patterns are scanned, one at a time, over the alignment marks at 2  $\mu$ s/pixel. The first contains partial outlines corresponding to the horizontal rectangles, while the second consists of partial outlines corresponding to the vertical rectangles of the registration marks (Figures 2.5a and b). The exposure frame is deemed to be aligned to the registration marks when either scanned pattern coincides with the corresponding registration marks. This is achieved by adjusting the rotation, the beam shifters and the varymag controls. The main reason for using two sets of scanned patterns is to avoid scanning a particular area more than twice so that unnecessary exposure of the resist is prevented. This alignment technique is accurate to within 0.5  $\mu$ m.

#### 2.3.2 Very High Resolution Alignment

The use of thin substrates for electron beam lithography offers the advantage of high resolution due to the lack of backscattering and the use of high contrast Scanning Transmission Electron Microscopy (STEM) for imaging and analysis (2.1,2.6). A very high resolution alignment technique that exploits the high contrast and high resolution STEM imaging on thin substrates had been developed in this department by Mackie (2.7). The method was modified slightly and

#### 2.3.2.1 Alignment Method

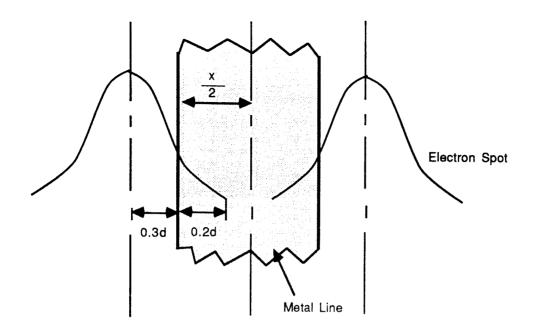

When operating in STEM mode, the contrast achievable in the Philips machine is such that when about 20% of the electron spot is obstructed from the transmission detector, the spot changes from bright to dark on the screen. If an electron beam with diameter d is scanned across a metal line of width x, the change in contrast should just occur when the centre of the spot is at a distance (0.3d+x/2) from the centre of the metal line (Figure 2.6). If the spot is scanned in parallel to the metal line, the whole scanned line will be either bright or dark. The alignment test which involves aligning the scanned line with the metal line should then give an overlay accuracy of about  $\pm(0.3d+x/2)$ .

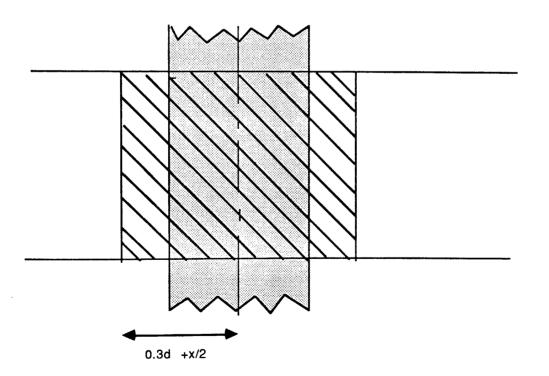

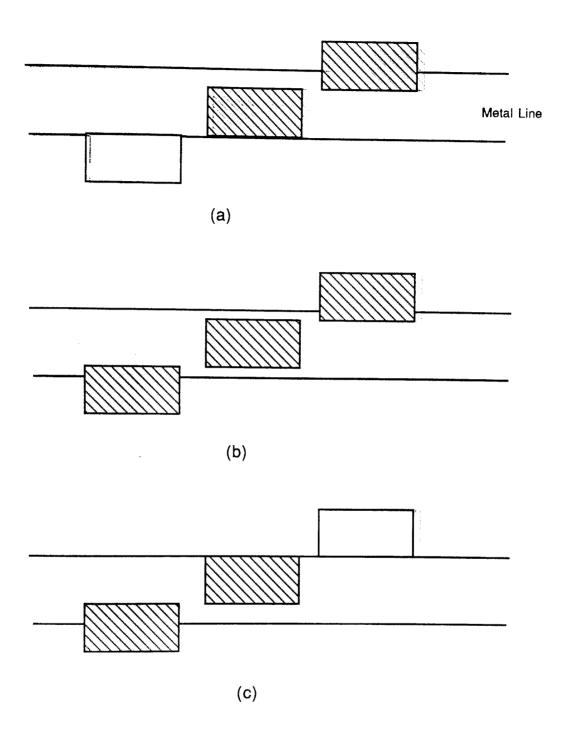

The above alignment method can be improved by using a three segment line scan as shown in Figure 2.7 (2.7). The condition for all 3 segments to appear dark simultaneously is  $0.3d+x/2 \ge p$  (Figure 2.7), where p is the displacement between the centre and the end segments. By increasing the displacement p, there is a point at which the condition is just satisfied i.e. 0.3d+x/2=p. When this happens, the centre segment should be aligned to the metal line such that a slight misalignment results in one of the end segment turning bright as illustrated in Figure 2.8. As the displacement can only be varied by an integral number of pixel, alignment accuracy of within one pixel might be expected. Therefore, the accuracy should improve with smaller frame size i.e. smaller pixel size.

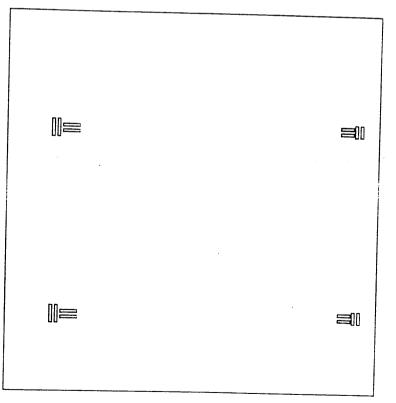

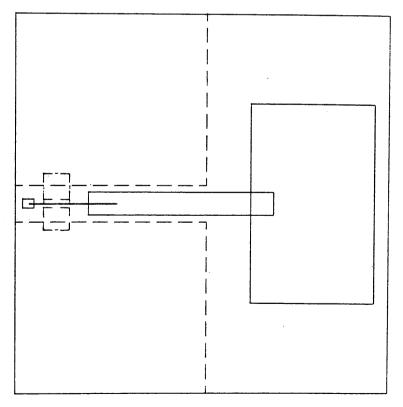

The very high resolution alignment technique exploits the above facts. The method developed by Mackie with one minor change was

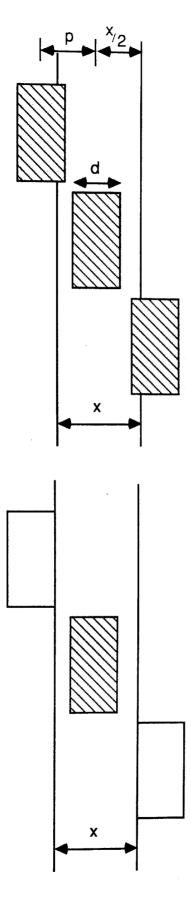

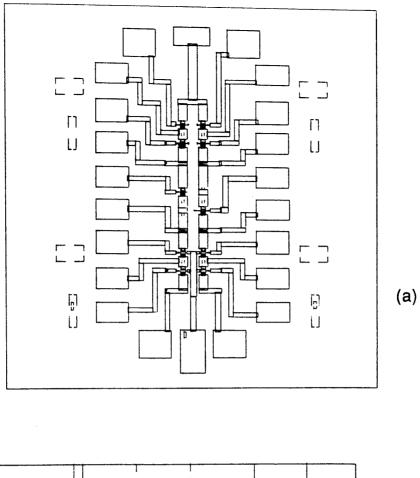

used. The alignment marks are shown in Figure 2.9. The blocks and the T-bars are used for coarse and fine alignment respectively. During alignment, the pattern shown in Figure 2.10a is scanned repeatedly over the alignment marks. A magnified view of one corner of the pattern is shown in Figure 2.10b. It consists of a vertical and a horizontal rasters designed for viewing of alignment marks on the screen. The extended lines are the reference lines corresponding to the positions of the T-bars. Each of these lines is made up of 3 segments, the centre segment having the same X- (or Y-) coordinates as the vertical (or horizontal) line of the T-bar. The displacement between the end segments and the centre segment is 1 pixel.

Coarse alignment is carried out initially by moving the blocks of the alignment marks to either side of the corresponding T-bar using the beam shifters. Fine alignment is then performed by adjusting the stage rotation, X and Y precision magnification (varymag) control and the beam shifters to change the shape and position of the scanned alignment marks until all 3 segments of each reference line appear dark at the same time i.e. until all 4 T-bars are aligned at once.

The fine alignment procedure is repeated using a series of the scanned patterns (Figure 10a) which are identical except that the displacement between the centre and the end sections of the reference lines are increased progressively by a pixel. This is stopped when the displacement is too large for all three sections of the reference lines to turn dark at the same time. When this happens the condition 0.3d+x/2=p is very nearly satisfied.

This high resolution alignment technique was used for fabricating interdigital gratings which is described below.

#### 2.4.1 Introduction

The resolution of a electron beam written grating is limited by interproximity and resist effects (2.1, 2.2, 2.8). These effects can be overcome by using two lithographic stages. The method is outlined below.

- a) Perform resolution tests to find the minimum reproducible pitch

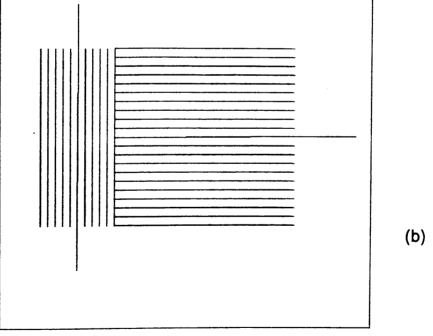

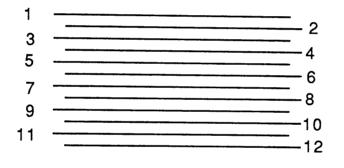

- b) Level 1- write lines 1,3,5,7,....(Figure 2.11)

c) Develop pattern, metallise and lift-off

d) Spin on fresh resist. Align second exposure level to Level 1

d) Level 2- write lines 2,4,6,8,.....(Figure 2.11)

e) process as (c).

The interdigitation technique was developed for fabricating Lateral Surface Superlattices on the 50 nm thick GaAs membranes described in Chapters 3 and 4.  $Si_3N_4$  membranes (60 nm thick) were readily available and initial tests were conducted with these before extending these experiments to the GaAs membranes. The  $Si_3N_4$ experiments are described below.

#### 2.4. Fabrication Procedure

A high resolution 2 layer resist system comprising of 40 nm of 350,000 MW PMMA on 40 nm of 185,000 MW PMMA was used throughout. This was baked (180°C) overnight before exposure.

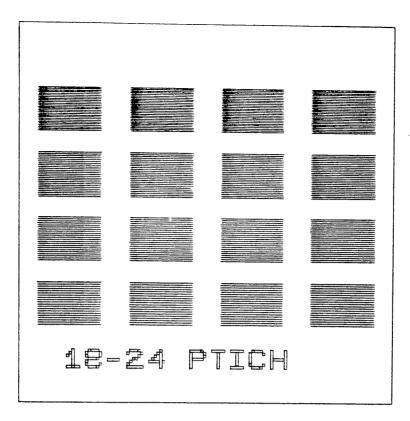

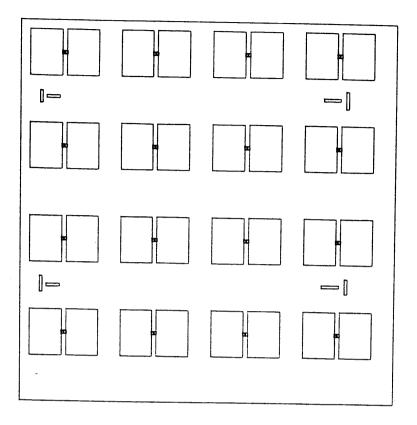

#### **Resolution** Tests

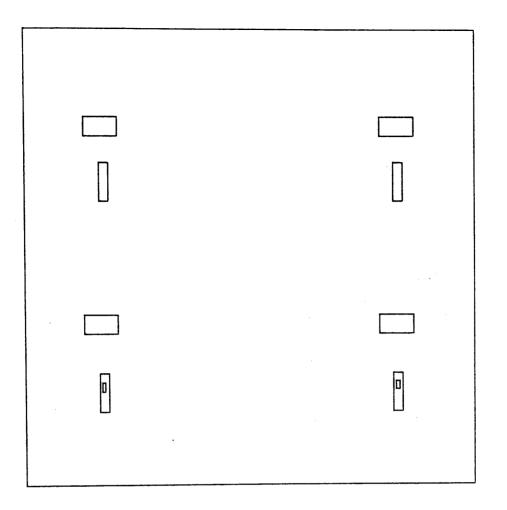

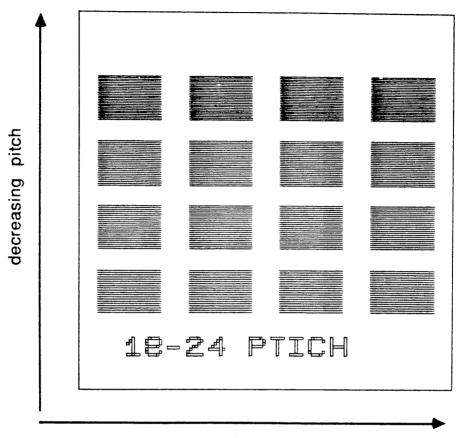

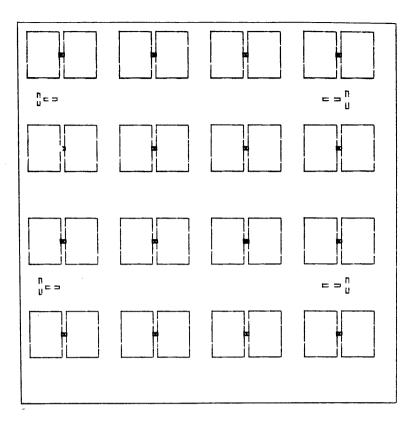

The pattern shown in Figure 2.12 was used for the resolution tests. It contains a matrix of gratings in which exposure dose and pitch are varied along rows and columns respectively. The pattern was written with a 8 nm electron spot of 50 keV energy in a 12.5 X 9.5  $\mu$ m frame. After exposure, the specimen was developed in 1:3 MIBK:IPA at 23°C for 20s followed by a 30s rinse in IPA. 10 nm of Au/Pd was subsequently evaporated onto the specimen and lift-off performed in chlorobenzene using the shooting technique (2.9).

#### Interdigital Gratings

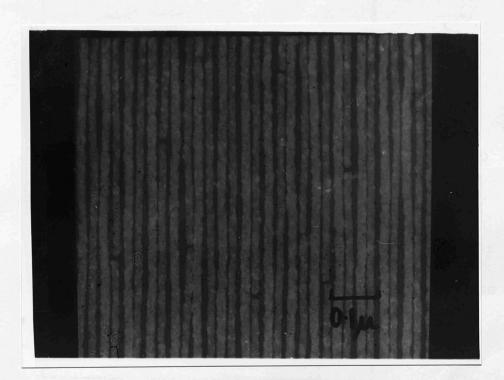

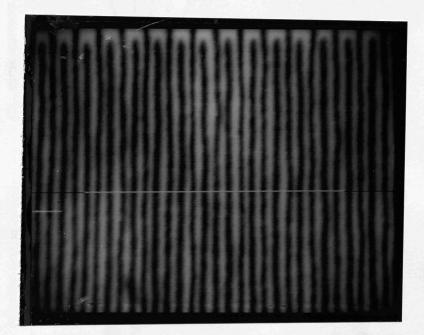

A pattern consisting of gratings with a range of pitches together with the high resolution alignment marks (Figure 2.13) was exposed in a 12.5 X 9.5  $\mu$ m frame. 50 kV electron beam with 8 nm spot size was used. After exposure, the specimen was processed as above. Fresh resist was spun on after liftoff. The second exposure level was aligned to the first using the high resolution technique described earlier. Once aligned, the second set of identical gratings was written between the fingers of the gratings previously exposed. This resulted in interdigital gratings with half the pitch of the original sets. Accuracy of the alignment was better than 3 nm. A TEM micrograph, Figure 2.14, which shows one of the finest grating thus fabricated. The grating consisted of 16 nm lines with 24 nm pitch (i.e. spaced 8 nm apart). This is the finest pitch grating reported to date on any substrate (2.10). Electrical isolation for all FET devices fabricated in this work was achieved by boron implantation. Metal On Polymer (MOP) masks were used to define active areas. The bombardment of epitaxial GaAs with the energetic ions causes formation of deep traps and renders it semi-insulating.

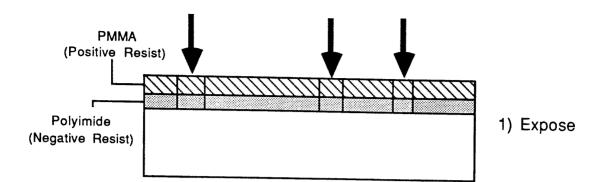

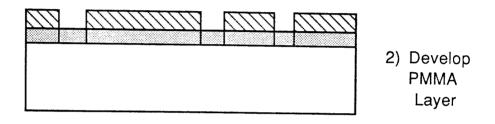

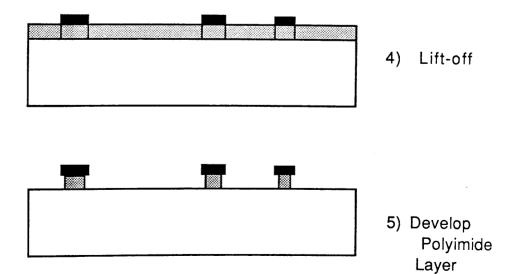

#### 2.5.1 Fabrication Procedure

The MOP mask consists of a 800nm thick Ge layer on a 0.3  $\mu$ m layer of polyimide. This is fabricated using a bilayer resist comprising of a 1 $\mu$ m thick 185,000 PMMA layer on a 0.3  $\mu$ m thick of polyimide.

Procedure (2.11)

A 0.3  $\mu$ m thick polyimide layer is first coated on a wafer by spinning 10% w/w Polyimide solution (solvent 35:65 by volume of acetophenone:xylene) at 5000 rpm for 60s. This is baked at 180°C for an hour before coating the wafer with a 1  $\mu$ m thick PMMA layer (15% w/w solution in chlorobenzene at 5000 rpm for a minute). The bilayer resist is then baked for 2 hours at 180°C before exposure.

Exposed PMMA is developed in 1:1 MIBK:IPA at 23°C for 60s. 10nm of NiCr followed by 800nm of Ge are evaporated, liftoff performed in acetone. The NiCr enhances adhesion of the Ge layer to the polyimide. Finally, unexposed polyimide is developed in 1:1 acetophenone:xylene at room temperature for 2 minutes. The fabrication process is illustrated in Figure 2.15. After implantation, MOP masks were removed by dissolving the polyimide layer in boiling acetophenone.

#### Chapter 2 References

(2.1) W.S.Mackie, PhD Thesis, Glasgow University 1984.

(2.2) S.A.Rishton, PhD Thesis, Glasgow University, 1984.

(2.3) C.E.Binnie, PhD Thesis, Glasgow University, 1985.

(2.4) M.J.Browden, "Electron Irradiation of Polymers and its Application to Resists for Electron Beam Lithography", CRC Critical Reviews in Solid State Sciences, pp223-264, 1979.

(2.5) S.P.Beaumont, T.Tamamura and C.D.W.Wilkinson,"A Two Layer Resist System for Efficient Liftoff in Very High Resolution Electron Beam Lithography", in Proc. International Conference on Microlithography, Amsterdam, Edited by Roel P.Kramer, Delft University Press, 1981.

(2.6) S.P.Beaumont, B.Singh, and C.D.W.Wilkinson,"Very High Resolution Lithography—Thin Films or Solid Substrates", in Proc. 10th International Conference on Electron and Ion Beam Sciences and Technology, Montreal, 1982.

(2.7) W.S.Mackie, S.P.Beaumont, P.G.Bower and

C.D.W.Wilkinson, "Very High Resolution Alignment of E- beam written

Patterns", in Proc. Microcircuit Eng. 82, Grenoble, France, 1982.

(2.8) A.N.Broers, "Resolution Limits of PMMA Resist for Exposure with 50kV Electrons", J.Electrochem. Soc.: Solid-state Science and Technology, **128**(1), pp166-170, 1981.

(2.9) S.P.Beaumont, P.G.Bower, T.Tamamura and C.D.W.Wilkinson, "Sub 20nm wide metal lines by electron beam exposure of thin poly(methylmethacrylate) films anf liftoff", Appl. Phys. Lett., 38(6), pp436-439, 1981. (2.10) K.Y.Lee, J.Frost, C.R.Stanley, W.Patrick, W.S.Mackie, S.P.Beaumont and C.D.W.Wilkinson, "Fabrication of Ultrasmall Devices on Thin Active GaAs Membranes", J.Vac. Sci. and Tech. B, Vol.5, No.1, pp322-324, 1987.

(2.11) W.Patrick, W.S.Mackie, S.P.Beaumont and C.D.W.Wilkinson, "Polyimide as a Negative Electron Resist and its Application in Crossovers and Metal On Polymer Mask Fabrication", J.Vac. Sci. and Tech. B, Vol. 4, No.1, pp390-393, 1986.

(2.12) W.Patrick, PhD Thesis, Glasgow University, 1986.

Figure 2.1 Illustration showing the lift-off and etching techniques.

# Figure 2.2

The Glasgow Electron-beam Lithoraphic System (After Patrick, ref. (2.12)).

(b)

# Figure 2.4 Standard Registration Mark Pattern.

Containe the the state of the second the second second

# Figure 2.5 Scanned Alignment Patterns

Positions of (a) Horizontal and (b) Vertical scanned patterns relative to standard registration marks are shown schematically.

An electron beam with spot size d turns from bright to dark when about 20% of the beam diameter crosses the metal line i.e. when the separation between the centres of the beam and the line is  $0.3d + \frac{x}{2}$

If the beam is scanned in parallel to the metal line, the scanned line turns dark if the centre of the spot is within region

## Figure 2.6

Condition for all 3-segments to turn dark at the same time is  $p \le 0.3d + x_{/2}$

If  $p > 0.3d + \frac{x}{2}$ only one segment can turn dark at a time

Figure 2.7

# Figure 2.8 Very High Resolution Alignment

Using a 3-segment scan, a slight misalignment (a & c) results in one of the end segment turning bright.

# Figure 2.9

Alignment Mark Pattern for Very High: Resolution: Alignment.

# Figure 2.10

- a) Scanned Alignment Pattern for Very High Resolution Alignment

- b) Magnified view of one corner

1) Pattern lines 1,3,5,7,9 & 11

2) Coat fresh layer of resist and pattern lines 2,4,6,8, 10 & 12 between the fingers of the first set of grating

## Figure 2.11 Fabrication of Interdigital Grating

# Figure 2.12

Grating Resolution Test Pattern

| - |  |

|---|--|

|   |  |

# Figure 2.13

Pattern used for exposure in the fabrication of interdigital gratings.

### Figure 2.14

TEM micrograph of a interdigital grating with 24nm centre-to-centre spacing and 16nm linewidth (8nm gaps). The grating was fabricated on 50nm thick Si  $_{3}N_{4}$  membrane using 2 lithographic stages.

Figure 2.15 Fabrication of Metal On Polymer Mask

#### 3.1 Introduction

This chapter is concerned with work carried out to explore the feasibility of fabricating FET devices on 50 nm thick GaAs membranes. The method used for producing the GaAs membranes is first described. Next, the development of the techniques and processes required for making the membrane devices are presented.

#### 3.2 Fabrication of 50 nm Thick $n^+$ – GaAs Membranes

GaAs membranes were initially made from MOVPE (Metal Organic Vapour Phase Epitaxy) wafers using the method developed by Mackie (3.1). The reliability and the reproducibility of the method were later improved by making some modifications. This included using wafers grown by MBE (Molecular Beam Epitaxy).

#### 3.2.1 Fabrication Outline

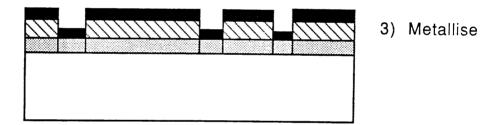

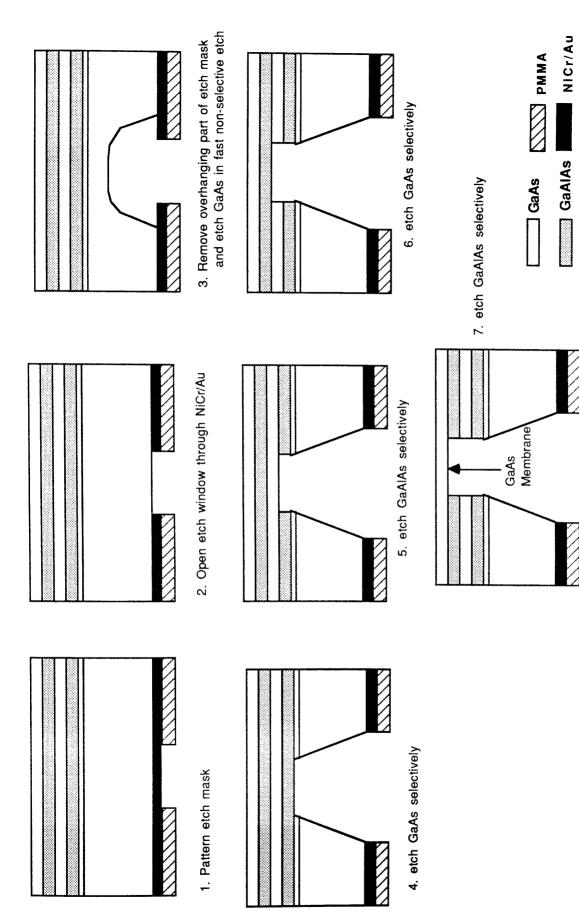

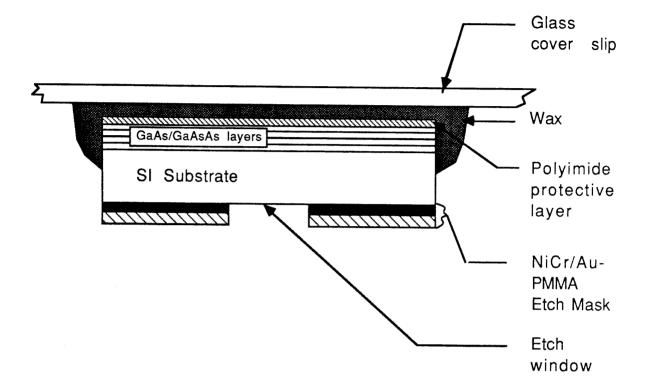

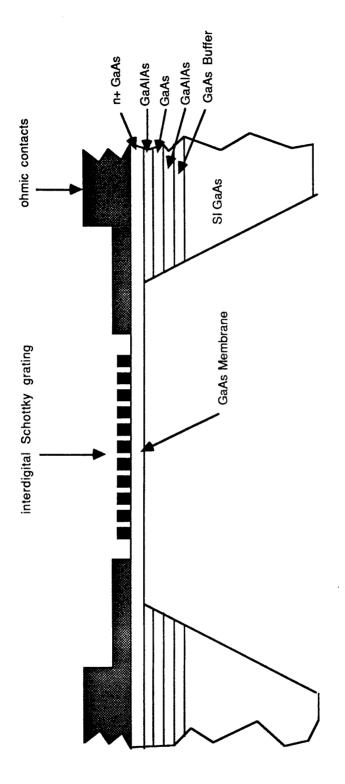

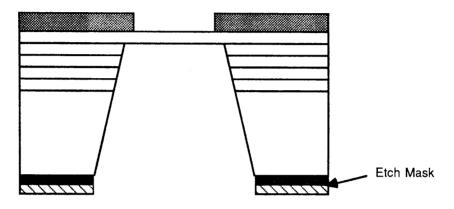

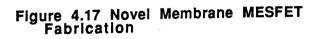

The starting material was a GaAs/GaAlAs heterostructure designed specially to facilitate membrane fabrication. As shown in Figure 3.1, the heterostructure consisted of GaAs/GaAlAs etch stop layers and a top active GaAs layer grown on a semi-insulating GaAs substrate. Membranes were formed by removing the underlying etch stop layers from the back surface with selective GaAs/GaAlAs etches. The method is shown schematically in Figure 3.2. The main steps are:

1. Pattern and open etch windows into a NiCr/Au mask on the

back surface of the wafer.

2. Etch GaAs through the windows in a fast non selective etch to within 10  $\mu$ m from the top surface.

3. Etch remaining GaAs and the etch stop layers in selective etches until the top GaAs layer remains.

#### 3.2.2 Material

The starting wafers were grown by MOVPE at Sheffield University (3.2) and by MBE in this department (3.3). The main features of the heterostructure (Figure 3.1) are:

a) GaAs and  $Ga_{0.3}Al_{0.7}As$  etch stop layers: the Al concentration was selected in order to obtain high GaAs/GaAlAs etch selectivity.

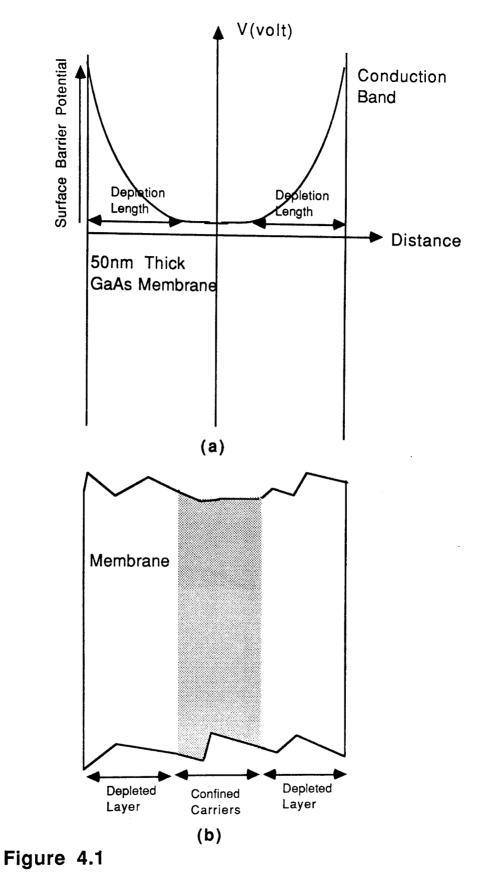

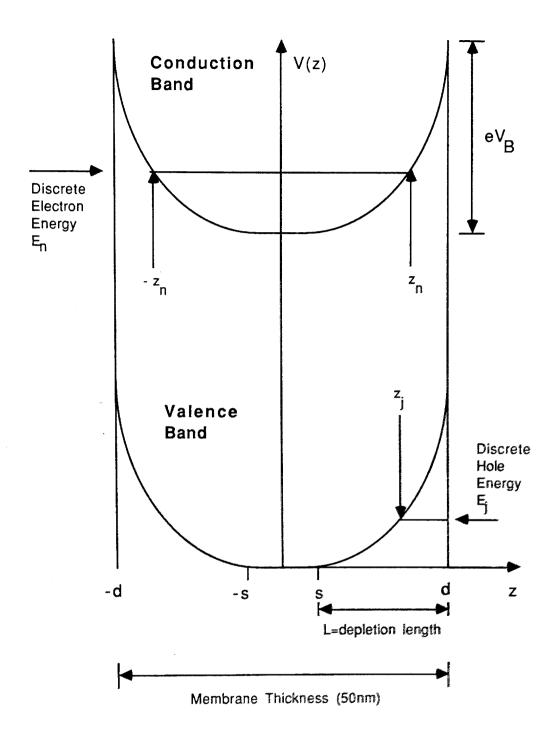

b) 50 nm thick GaAs active layer n-doped to a concentration of 3 X  $10^{18}$  cm<sup>-3</sup>. This layer formed the final membrane; very high doping density was therefore required to prevent total carrier depletion from both surfaces (3.4). At this doping density and assuming a surface barrier height of 0.7 eV (due to surface states), the calculated depletion width from each surface is 17nm (see Chapter 5).

All layers were grown on (100) semi-insulating GaAs wafers.

3.2.3 Etches (3.1)

The following etches were used:

#### 1) 1:8:1 H<sub>2</sub>SO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub>: H<sub>2</sub>O

This is a fast non selective anisotropic etch which etches GaAs at a rate of about 15  $\mu$ m/minute when freshly prepared. The etch rate drops to less than 10  $\mu$ m/minute as it cools.

This etches GaAs at a rate of about 2  $\mu$ m/minute and was used as the selective etch for GaAs. Its etch rate for Ga<sub>1-x</sub>Al<sub>x</sub>As drops exponentially with increase in x, becoming negligible for x greater than 0.3.

<u>3) 20% HF</u>

This does not etch GaAs but etches  $Ga_{1-x}Al_xAs$  at a rate which increases exponentially with x. It was used as the selective GaAlAs etch (20% HF etches  $Ga_{0.3}Al_{0.7}As$  at about 1  $\mu$ m/minute).

For each of the above etches, it was necessary first to wet the resist by immersing the samples into IPA followed by a water rinse. This measure ensures uniform etching especially for very small resist openings.

#### 3.2.4 Membrane Fabrication Procedure

#### Size of Membrane

Mackie had shown previously that, due to the properties of the 1:8:1 etch, the size of the final membrane is determined by the shape and the size of the etch windows and the wafer thickness (3.1). It was decided to make membranes with edges of between 100 and 200  $\mu$ m i.e. same size as the ones fabricated by Mackie. These can be formed by etching through 20 X 200  $\mu$ m windows on 100  $\mu$ m thick wafer with the length of the windows aligned parallel to the [011] crystal direction (3.1).

#### Polishing

The 2" wafers as received were about 450  $\mu$ m thick. It was therefore necessary to thin down the wafers in order to produce membranes of the required size. They were diced into quarters and sent for polishing. The back surface was first polished with coarse Aloxite 800 grit until the thickness of the wafer was about 200  $\mu$ m, then to 100  $\mu$ m using 0.3  $\mu$ m Alumina.

#### Crystal Orientation

The crystal orientation of a wafer was determined by observing the profiles of a cross that had been etched into the substrate with the 1:8:1 etch. The bottom of the etched grooves would appear rounded in one direction and flat in the other, corresponding to the [011] direction and the  $[01\overline{1}]$  direction respectively (3.1).

To carry out this test, a small piece of the material was broken off the polished wafer and its back surface masked with wax. Using the tip of a pair of tweezers, a cross was scratched into the wax and the exposed GaAs surface etched in the 1:8:1 mixture for 5 minutes. The wax was then dissolved in trichloroethylene to enable clearer examination of the etched cross under an optical microscope.

#### Diced wafers and Initial Cleaning

The polished material was diced into 6 X 7.5 mm wafers with the long edge of the wafers aligned parallel to the [011] crystal direction. This allowed identification of the crystal orientation at later process stages. Residual wax on the wafers from the polishing step was removed in trichloroethylene followed by a rinse in acetone and then in IPA.

A polyimide layer was spun on the front (membrane) surface of the wafers and baked at 180° C for at least one hour. The polyimide layer served only as a mechanical mask against dirt particles and scratches and was not intended as protection against wet chemical etches. It was, however, insoluble in acetone, trichloroethylene and IPA which were used extensively in the process for cleaning the wafers.

#### Evaporation of NiCr/Au Mask

The etch mask evaporated on the back surface of the wafers consisted of a 50 nm layer of Au on a 10 nm layer of NiCr. The metallisation step was preceded by a 30s surface oxide etch in 1:1 HCl:H<sub>2</sub>O which improved adhesion of the NiCr/Au mask on the wafers. The mask was adequate against all the etches used in the etching steps (3.1). After the metallisation, a 1  $\mu$ m thick PMMA layer was spun on the NiCr/Au surface and baked overnight at 180°C.

#### Etch Windows Patterning

20 X 200  $\mu$ m windows were written into the resist with a 0.25  $\mu$ m electron spot at 50 kV. Two such windows were patterned in each exposure frame of 1.5 x 1.2 mm. The length of the windows were aligned to the (011) crystal direction (i.e. parallel to the length of the chip). There were 5 by 4 exposure positions on each 7.5 by 6 mm wafer. Exposed resist was developed in 1:1 MIBK:IPA for 60s.

Windows were opened into the GaAs substrate by etching the

exposed NiCr/Au in  $I_2/KI$  solution (consisting of 4g/1g  $I_2/KI$  in 40ml of  $H_2O$  (3.5)) using the developed resist as the mask. But this etch also attacks GaAs and so it was necessary to protect the front surface of the wafers.

Each wafer was therefore waxed onto a glass cover slip after development. Care was taken to ensure that the entire front surface was covered with wax (Figure 3.3). This not only served to mask the surface during the subsequent etching in the NiCr/Au etch and then in the 1:8:1 etch but was also useful for handling the wafer. The etch time in the NiCr/Au etch was 2 minutes.

#### Etching Procedure

#### Fast Non Selective Etch

The GaAs substrate was first etched through the windows in the 1:8:1 mixture. The etching was stopped after 5 minutes by rinsing the wafer in deionised water. The undercutting action of the anisotropic etch formed an area of overhanging NiCr/Au/PMMA in the periphery of the etch windows. It was necessary to remove this to ensure that the etch was not prevented from diffusing into the etch well by trapped air bubbles during subsequent etching. To do this, the wafer was placed in IPA in an ultrasonic bath for 10s. Removal of the overhanging layer also enabled the bottom of the well to be viewed easily.

An optical microscope with calibrated vertical movement was used (as a vertical travelling microscope) to measure the depth of the etch wells. The depth after 5 minutes etching in the 1:8:1 mixture was typically about 50  $\mu$ m.

A further 3 minutes etch in the 1:8:1 solution was carried out

and the overhanging part of the mask removed afterwards as before. The etch well was usually about 70  $\mu$ m deep at this stage. From this point onwards the sample was etched at one minute intervals. In between, the etched depth was monitored using the optical microscope. The etching was stopped when the bottom of the well was within 10  $\mu$ m of the top surface.

#### Selective Etching of GaAs/GaAlAs Etch Stop Layers

The wafers were removed from the cover slips by melting the wax on a hot plate. Each wafer was then diced into twenty 1.5 X 1.5 mm samples, each containing 2 etched wells. Usually, twelve of the samples were then waxed onto a plastic strip, again making sure that the front surface of each sample was completely masked with wax.

The remaining GaAs to the first hetero-interface was removed in the 95:5 etch. The samples were immersed in the etch for no more than two minutes at a time. This was because prolonged etching in the solution caused the etch wells to be clotted up with brown precipitate which can be removed in HCl. At the end of each etch period, the wells were cleared by rinsing the samples in 1:1 HCl:H<sub>2</sub>O for 15s. The first hetero-interface was normally reached after about 4 to 8 minutes etching. Under an optical microscope, the GaAlAs surface appears white and mirror-like.

The 1  $\mu$ m thick GaAlAs layer was removed by etching in 20% HF for 2 minutes. Next, a 20s etch in the 95:5 solution to remove the last GaAs etch stop layer was carried out. This was followed by a 10s rinse in 1:1 HCI:H<sub>2</sub>O to clear the well of the brown precipitate. At this point the bottom of the well normally appears light green in colour. Finally, the last GaAlAs etch stop layer was removed by

etching in 20% HF for 15s. The 50 nm thick membranes should be reddish orange in colour.

#### Detach Membranes from Plastic Strip

The samples containing the membranes were detached from the plastic strip by dissolving the wax in trichloroethylene. This was done by floating the plastic strip on the solvent so that the samples were caused to slide off the strip eventually. Most of the breakages occurred at this stage due to the stress induced on the membranes by the detachment process. The yield of intact membranes was improved by accelerating the detachment process by heating the solvent. Previously, room temperature trichloroethylene had been used and the detachment process took about 5 minutes giving a yield of about 50% of intact membranes. The detachment was almost instantaneous in boiling trichloroethylene and the resultant yield was better than 90%.

The polyimide layer on the membrane surface of the samples was removed in acetophenone. Finally, the samples were cleaned individually by rinsing in acetone and then IPA.

#### 3.2.5 MBE vs MOVPE

Two out of three wafers grown by MOVPE were found to be unsuitable for making membranes. The etch stop layers of the "bad" wafers were found to be ineffectual due to the lack of GaAs/GaAlAs etch selectivity at the interfaces. This was attributed to fuzzy GaAs/GaAlAs interfaces.

Hyper-abrupt interfaces are more readily obtainable by MBE growth (3.6). Two wafers, nominally identical to the MOVPE wafers,

were grown by MBE in this department. Both gave excellent etch selectivity.

MBE material was used for all experiments on membranes and for fabricating membrane devices in this work.

#### 3.3 Electron Beam Lithography

Electron beam processing was carried out on 50 nm thick GaAs membranes with the following aims. Firstly, to see if the processing was destructive to the membranes; secondly, to determine the resolution limits of electron beam writing on the membranes and finally, to demonstrate high resolution re-alignment.

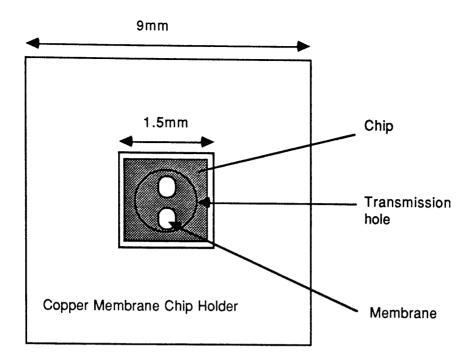

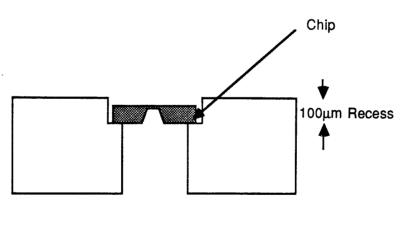

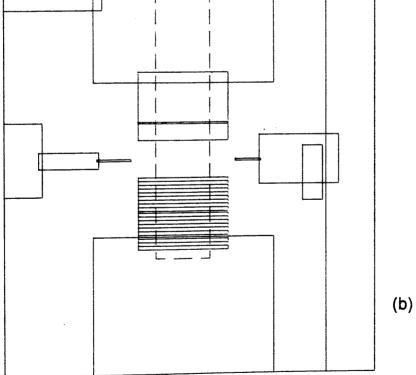

For ease of handling, the 1.5 X 1.5 mm chip containing two membranes was mounted on a specially designed holder shown in Figure 3.4. The chip was fitted in the recess and glued on with polyimide (10% in 35:65 xylene:acetophenone). The recessed structure prevented the resist from thickening near the corners during spinning so that a uniform resist layer was obtained. The transmission hole facilitated STEM and TEM microscopy.

#### 3.3.1. Resolution Tests

#### **Isolated** Lines

A high resolution bilayer resist system comprised of 40 nm of 350,000 molecular weight PMMA on 40 nm of 185,000 molecular weight PMMA was spin coated on the GaAs membranes and baked overnight at 180°C. Isolated single pixel lines were scanned in a 25 X 19  $\mu$ m frame with a 8 nm electron spot accelerated to 50 kV. The

exposed resist was developed in 1:3 MIBK:IPA for 20s followed by a 30s rinse in IPA. The sample was then coated with 10 nm of AuPd. Liftoff by shooting chlorobenzene on the sample in methanol (3.7) was found to be unsuitable as the process caused the membranes to break. Instead, liftoff was performed as follows. The sample was first soaked in acetone for at least half an hour. The metallisation was then caused to liftoff by gently squirting a jet of acetone on the sample from a squeezy bottle.

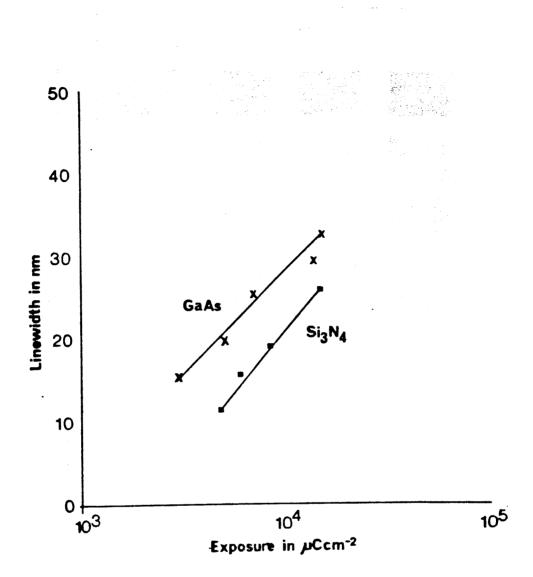

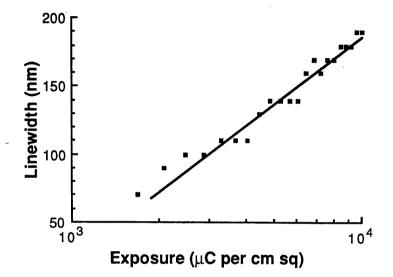

For comparisons, a similar experiment was carried out on 60 nm thick  $Si_3N_4$  membranes. The results are plotted in the graph in Figure 3.5. On GaAs membranes, the critical dose was lower and the lines were wider for a given exposure dose. The minimum linewidths achieved were 10 nm on nitride membrane and 17 nm on GaAs membrane.

#### **Closely Spaced Lines**

Using the above bilayer resist system (40 nm: 40 nm 185,000 MW: 350,000 MW PMMAs), Mackie had demonstrated that the smallest grating that could be fabricated on a 60 nm thick nitride membrane and on a 50 nm thick GaAs membrane had a centre-to-centre spacing of 40 nm and 70 nm respectively (3.1).

The aim here was to make device quality gratings on GaAs membranes which satisfied the following conditions. First, the fabrication of the gratings must be reliable and reproducible. Second, the lines of the gratings must be unbroken.

The thickness of the metallisation intended for device application was at least 60 nm. A bilayer resist consisting of 20 nm of 350,000 MW PMMA on 100 nm of 185,000 MW PMMA was used for the resolution tests. This was more than adequate to allow liftoff of a 60 nm thick metal layer.

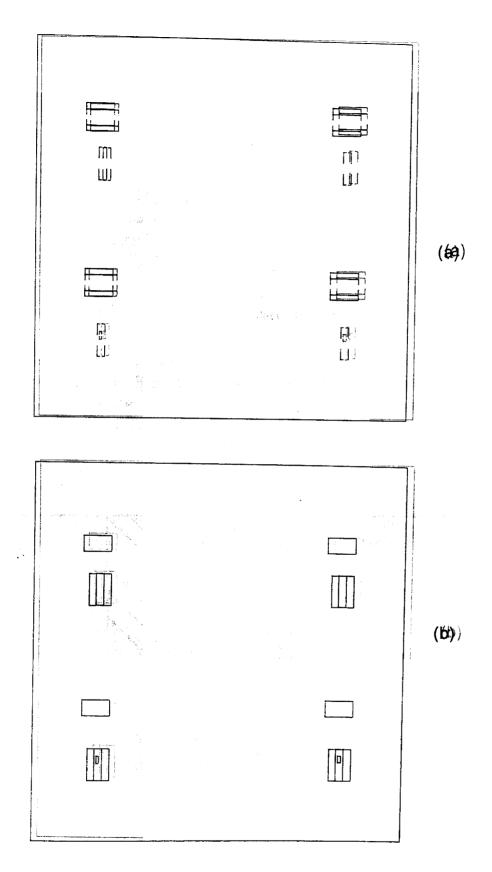

The pattern shown in Figure 3.6 was exposed in a 25 X 19  $\mu$ m frame. A 50 kV electron beam with 8 nm spot size was used. After exposure, the samples were developed in 1:3 MIBK:IPA for 30s and then rinsed in IPA for another 30s. The metallisation consisted of 10 nm of AuPd and liftoff was performed in acetone.

The pitch of the smallest grating was 70 nm. But the minimum pitch of the gratings which were reproducible and which satisfied the requirements for device purposes was 100 nm.

#### Very High Resolution Alignment

Two sets of gratings were interdigitated on 50 nm thick GaAs membrane using the very high resolution alignment technique described in Chapter 2. A bilayer resist consisting of 20 nm:100 nm of 350,000 MW: 185,000 MW PMMAs was used. The alignment was performed in a 25 X 19  $\mu$ m frame and the resist was developed in 1:3 MIBK:IPA for 30s after exposure. The alignment procedure was as described in Chapter 2 (Section 2.3.2). A STEM micrograph of a 50 nm pitch interdigital grating is shown in Figure 3.7. The pitch of the finest interdigital grating achieved was 35 nm.

#### Comments on the Resolution Tests

The above experiments show that the resolution of electron beam writing on 50 nm thick GaAs membrane is poorer than on 60 nm thick  $Si_3N_4$  membrane. This may be due to more pronounced backscattering effects in the GaAs membrane as GaAs is a denser material than silicon nitride.

The smallest gratings that can be fabricated reliably and with good reproducibility on the GaAs membrane is limited to about 100 nm. Gratings with smaller pitch, down to 70 nm, can be fabricated but at the expense of the quality of the gratings (more breaks in the lines) and the reliability and reproducibility of the process. Therefore, the best way to make device quality gratings with pitch smaller than 100 nm on the semiconductor membrane is by interdigitating two sets of gratings with a wider pitch.

#### 3.4 The Fabrication of FET devices on GaAs Membranes

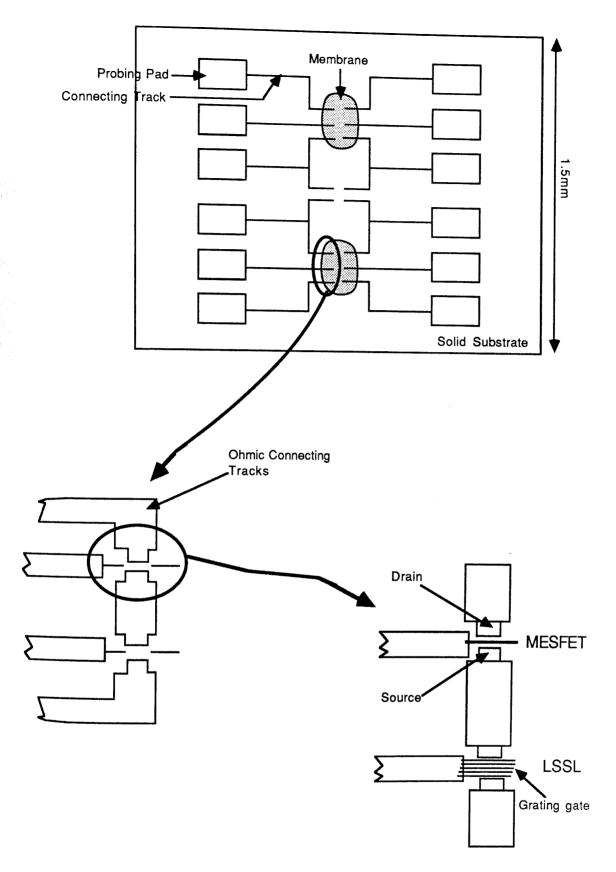

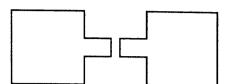

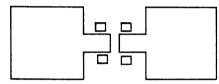

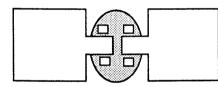

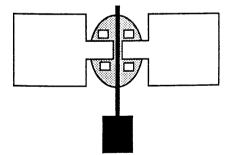

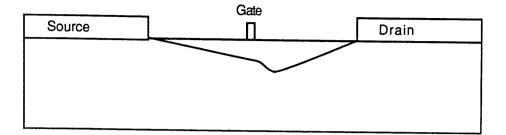

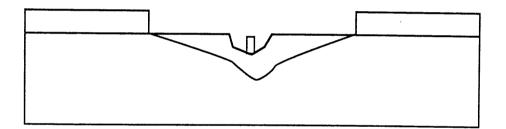

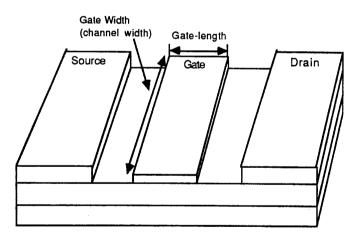

The target membrane FET devices were MESFETs and Lateral Surface Superlattices (LSSLs). The proposed structures of the devices are shown in Figure 3.8. The LSSL is similar to the membrane MESFET in structure but with a Schottky metal grating in place of the gate. The process requirements for both devices are common apart from the patterning of the gate level.

#### 3.4.1 Requirements for Membrane Device Fabrication

#### 3.4.1.1 Lithography

It was observed that the number of lithographic levels that could be performed on GaAs membranes was limited to 2 or 3 before the membranes started to break, usually during liftoff. To take account of this, the process for fabricating devices on GaAs membranes should involve minimal lithographic processing on the membranes. Conventional isolation technique by mesa isolation is clearly not suited to making membrane devices. A planar isolation method is required.

The bombardment of epitaxial GaAs with energetic ions causes formation of deep traps and renders it semi-insulating. Active channels can thus be defined using a suitable masking system to protect against the implant. Isolation by ion implantation became practicable when a MOP masks fabrication technique was developed in this Department (3.8). As the surface of the GaAs epilayer remains flat, this isolation technique is suitable for membrane devices.

Electrical isolation of all the GaAs FET devices fabricated was achieved by boron isolation. The standard process consisted of implantation of boron ions with dosages of  $2 \times 10^{13}$  cm<sup>-3</sup> at 40 and 80 kV. The effect of the implantation on the crystalline structure of GaAs had been studied in this Department by McMeekin (3.9). This was done by comparing TEM electron diffraction patterns of two 50 nm thick GaAs membranes, one was implanted with the standard dose of boron ions while the other was protected against the implantation (the implantation is more than sufficient to passivate 50 nm thick layer of epitaxial GaAs). The results indicated that the crystalline structure of the implanted membrane was strained. Thus, deep traps caused by ion implantation which render active GaAs semi-insulating may be linked to strain of the GaAs crystal structure. Alloyed  $Au_{0.88}Ge_{0.12}/Ni$  contacts (3.10–11) were used to make ohmic connections on the GaAs membranes. The contacts are Schottky-type as deposited and have to be annealed at a temperature commonly between 300°C and 400°C.

The approach to contact fabrication on membranes was as follows. First, the process for patterning ohmic contacts was demonstrated. Next, experiments on the alloying of the contacts to GaAs membranes were performed.

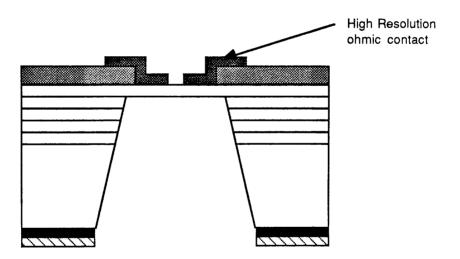

#### Ohmic Contact Patterning on GaAs membranes

Interproximity effects are less severe on thin substrates due to the reduced effect of backscattering. To exploit this, the drain and the source of the membrane MESFET were intended to be patterned on the membrane in order to obtain very narrow separation between the contacts.

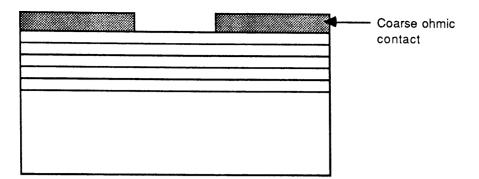

The first ohmic level containing the probing pads and connecting tracks were patterned on the solid substrate before forming the membranes. The method is shown schematically in Figure 3.9. A fuller account of this will be given in the next chapter. Next, a 1  $\mu$ m thick PMMA layer was coated on the 1.5 X 1.5 mm sample and baked at 180°C for 2 hours. The pattern containing a pair of closely spaced drain-source pads was exposed individually between the end of two connecting tracks on the membrane in a 25 X 19  $\mu$ m frame. A 50 kV electron beam with 16 nm spot size was used. After developing in 1:1 MIBK:IPA for 60s, ohmic metallisation consisting of 100 nm Au<sub>0.88</sub>Ge<sub>0.12</sub>, 15 nm of Ni and 50 nm of Au capping layer was

evaporated. Liftoff was performed in acetone as in the case for the high resolution processing.

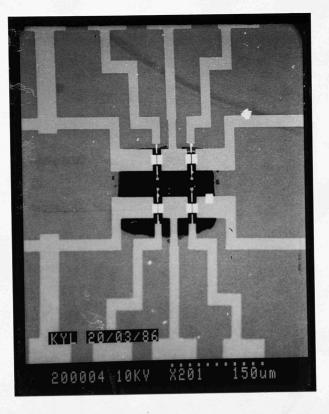

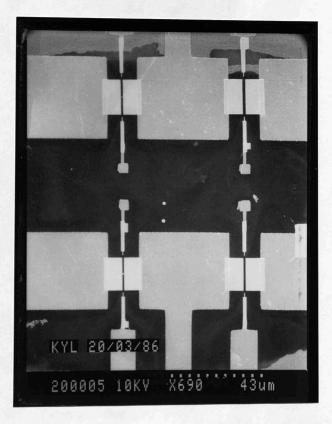

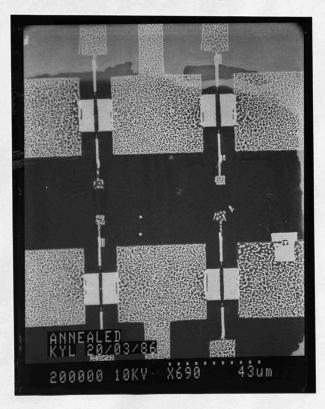

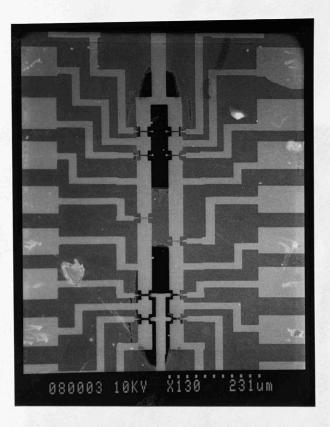

Micrographs of the metallisation on the membrane are shown in Figure 3.10. It can be seen that the edges of the drain and the source contacts are sharp and well defined. This was obtain without having to optimise the exposure conditions (i.e. no proximity correction). The smallest drain source gap achieved was 0.2  $\mu$ m.

#### Alloying

The ohmic contacts were alloyed at 350°C for 60s in a reducing atmosphere of 5:95 hydrogen:argon. The process was found to disintegrate all the membranes and was attributed to the stress induced on the membranes by the contacts during the alloying.

To avoid this problem, the ohmic contact was alloyed on the solid substrate before forming the membranes. But the process was found to cause the GaAs/GaAlAs etch selectivity required for forming membranes to be lost. This was attributed to the diffusion of the contact metallisation materials into the underlying GaAlAs layer during the annealing. Membranes must therefore be formed before alloying of the ohmic metallisation was carried out.

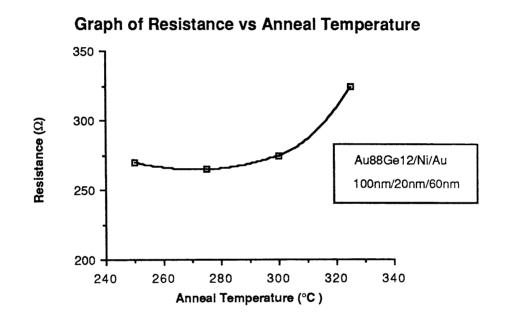

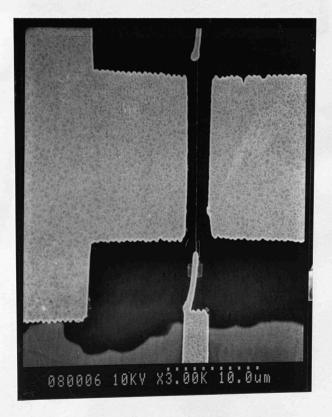

It was found that the damage to the membranes during the alloying process could be reduced by lowering the anneal temperature. By varying the thickness of the Ni layer in the composition of the ohmic contacts (3.12), it was possible to optimise contact resistance using a structure consisting of 100nm/20nm/50nm of  $Au_{0.88}Ge_{0.12}/Ni/Au$  when annealed at a temperature between 250 and 275°C. This can be deduced from Figure 3.11 in which the resistance between two ohmic contacts consisting of this composition is plotted

against the annealing temperature. This experiment was conducted on the solid heterostructure rather than the GaAs membranes because of the difficulty in making ohmic contacts to the membranes. Yield could be further improved by filling the etch wells with polyimide to give additional support to the membranes during annealing. The polyimide layer also acted as a heat sink giving better heat distribution across the membrane. Using low annealing temperatures and strengthening with polyimide, the damage was reduced to a hair line fracture (Figure 3.12) on each membrane, damaging, on average, one in four possible devices on each membrane.

The fracture incurred during the alloying weakened the membrane so much that further processing on the membrane was impossible. This meant that the annealing must be carried out last in the fabrication of an actual device.

#### 3.4.1.4 Schottky Contacts

High temperature treatment of a Schottky contact results in the lowering of the barrier height and reverse breakdown field and increases the ideality factor (3.13-16). The choice of gate metallisation for the membrane device must therefore be one that forms a thermally stable Schottky junction with n-GaAs.

Tests carried out by other workers have shown that Ti/n-GaAsSchottky contact is stable up to  $500^{\circ}C$  (3.15). Ti is therefore a suitable choice for the gate metallisation as the Schottky junction formed is stable over the temperature at which the alloying of the ohmic metallisation would be performed. Although there are alternatives other than Ti such as the combination of metals used in SAINTs (3.16), Ti is preferred because it is available and relatively

#### 3.4.2 Membrane FET Fabrication Strategy

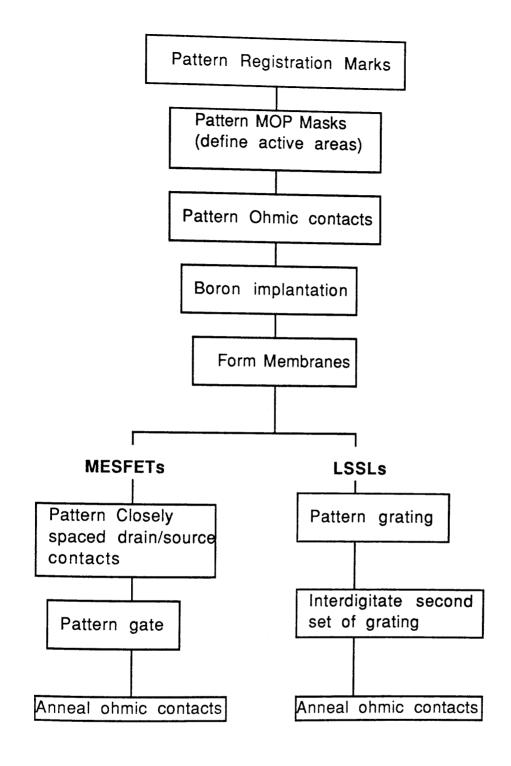

Based on the above work, the strategy for fabricating GaAs FET devices on membranes was devised:

a) Thin down wafer with GaAs/GaAlAs etch stop layers – this enables membranes of the required size to be produced

b) Perform all processes requiring low resolution on solid substrate - to minimise handling of the membranes (see Section 3.4.1.2)

c) Fabricate membranes

d) Perform high resolution patterning on membranes – for MESFETs, this would include the ohmic drain-source contacts and then the Ti gate. For LSSLs, Ti grating is patterned at this point, followed by, if desired, interdigitation.

e) Anneal ohmic contacts

f) test devices

#### 3.5 Discussions and Conclusions

It was demonstrated that the requirements for fabricating FET devices on 50 nm thick GaAs membranes can be fulfilled. Hence the fabrication of FET devices on the membranes is practicable.

Both high resolution and coarse electron beam patterning on the membranes have been demonstrated. It was shown that the smallest grating which was suitable for device application was 100 nm. Although such a resolution can be achieved on solid GaAs ( with 50 kV electron beam), on membranes gratings with narrower lines can be

fabricated and with better reliability. Further, if a smaller pitch grating is desired, it has been shown that this can be made by interdigitating two sets of gratings using the very high resolution alignment technique. The pitch of the smallest interdigital grating fabricated on GaAs membraness was 35 nm. Re-alignment at this resolution is difficult if not impossible on solid GaAs. On membranes, it was also shown that structures with thick metallisation can be spaced closely apart without the need for proximity correction. The smallest drain-source gap defined on the membrane was 0.2  $\mu$ m. The resolution capabilities demonstrate the potential of making ultrasmall devices on the GaAs membranes.

Abrupt interfaces are required for the heterostructure used for making membranes to ensure that the etch stop layers are effective. The growth of the heterostructure by MBE is preferred to that by MOVPE as the former growth method allows abrupt interfaces to be obtained more readily. It was also discovered that that interdiffusion between the ohmic metallisation materials and the GaAs/GaAlAs layers alters their chemical properties so that the GaAs/GaAlAs etch selectivity for the system of the selective etches used is destroyed.

#### **Chapter 3 References**

(3.1) W.S.Mackie, PhD Thesis, Glasgow University, 1984.

(3.2) W.S.Mackie, S.P.Beaumont, C.D.W.Wilkinson and J.S.Roberts, "High Resolution Lithography on Thin Active Semiconductor Membranes" in Proc. of the 10th International Conference on Electron and Ion Beam Technology (Electrochemical Society, Penington, NJ, 1083)).

(\$33) JIFröst, Internal Report, Glasgow University, 1987.

(3.4) A.Chandra, C.E.C.Wood, D.W.Woodward and L.F.Eastman, "Surface and Interface Depletion Corrections to Free Carrier-density Determination by Hall Measurements", Solid State Electron.,22, pp645-650, 1979.

(3.5) W.Kern and C.A.Deckert, "Etching Processes- Chemical Etching", in Thin Film Processes, pp401-481, Academic Press (London), 1978.

(3.6) C.R.Stanley, "III-V Semiconductor Growth Technique for Photonic Devices", Proc. Advanced Summer Institute on Electronic Structure of New Materials, Helsinki, ed. M.Leppihalme (Swedish Academy of Engineering Science in Finland) Report No. 42, pp81-114, 1986.

(3.7) S.P.Beaumont, P.G.Bower, T.Tamamura and C.D.W.Wilkinson, "Sub 20 nm wide metal lines by electron beam exposure of thin poly(methyl methacrylate) films and liftoff", Appl. Phys. Lett., 38, (6), pp.436-439, 1981.

(3.8) W.Patrick, W.S.Mackie, S.P.Beaumont and C.D.W.Wilkinson,

"Polyimide as a Negative Electron Resist and its application in Crossovers and Metal On Polymer mask Fabrication", J.Vac. Sci. Tech. B, Vol. 34 pp390-393, 1986.

(3.9) S.McMeekin, MSc Project Report, Glasgow University, 1987.

(3.10) V.L.Rideout,"A review of the theory and ohmic technology for ohmic contacts to Group III-V Compound Semiconductors", Solid State Electron., Vol. 18, pp541-550, 1975.

(3.11) N.Braslau, "Alloyed ohmic contacts to GaAs", J.Vac. Sci. and Technol., 19(3), pp803-806, 1981.

(3.12) W.Patrick, W.S.Mackie, S.P.Beaumont and C.D.W.Wilkinson,

"Low Temperature Annealed Contacts to very thin GaAs Epilayers",

Appl. Phys. Lett., Vol.48, pp986-988, 1986.

(3.13) A.K.Sinha and J.M.Poate, "Metal-Compound Semiconductor Reactions", in Thin Films-Interdiffusion and Reactions, edited by J.M.Poate, K.N.Tu and J.W.Mayer (Wiley, NY 1975), Chapter 9.

(3.14) S.S.Lau, W.X.Chen, E.D.Marshall and C.S.Pai, "Thermal and Chemical Stability of Schottky metallization on GaAs", Appl. Phys. Lett., 47, (12), pp1298-1300, 1985.

(3.15) A.K.Sinha, T.E.Smith, M.H.Read and J.M.Poate, "n-GaAs Schottky diodes metallised with Ti and Pt/Ti", Solid State Electron., Vol.19, pp489-492, 1976.

(3.16) D.A.Allan, "Stability of Schottky barriers at high temperatures for use in GaAs MESFET technology", IEE Proc. Vol. 133 Pt. 1 No.1, pp18-24, 1986.

The show have needed to the second of the

a ser a la comparte de la comparte d

| GaAs n-type                    | 50 nm    |  |

|--------------------------------|----------|--|

| Ga Al As<br>0.3 0.7            | 0.15 μm  |  |

| 0.3 0.7                        |          |  |

| GaAs                           | 0.3 µm   |  |

|                                | ·        |  |

|                                |          |  |

| Ga Al As<br>0.3 0.7            | 1.00     |  |

| 0.3 0.7                        | 1 µm     |  |

|                                |          |  |

|                                |          |  |

| GaAs Buffer                    | 0.05 µm  |  |

| Semi-insulating GaAs Substrate |          |  |

|                                | $\frown$ |  |

# Figure 3.1 Heterostructure used for Fabrication of GaAs membranes.

Layers were grown by MBE on a semi-insulating GaAs substrate.

Top GaAs Layer  $N_D = 3E+18 \text{ cm}^{-3}$

The other layers were nominally undoped

# Figure 3.2 Fabrication of GaAs Membrane

# Figure 3.3

The membrane chip is waxed onto a glass cover slip to mask the hetero-layers from the etches used to form membranes.

(a) a construction of a second s second s Second s Second seco

Plan View

Cross-section of the holder

# Figure 3.4 Special Copper Holder

The diagrams illustrate the design of the holder and the way a membrane chip is mounted. The holder consists of a 1  $\mu$ m hole which facilitates transmission microscopy. The recessed structure allows a uniform layer of resist to be spin coated on the chip.

#### Figure 3.5

Linewidth versus Exposure Dose Plot from Resolution tests on 50 nm thick GaAs and 60 nm thick Si  $_3Ni_4$ membranes. Isolated single lines were written on a 2-layer resist system (40nm:40nm 350,000MW:185,000MW PMMAs) with 8nm diameter electron beam accelerated to 50kV in 25X19µm frame. 10nm thick AuPd was deposited and liftoff process used.

increasing exposure dose

# Figure 3.6 Grating Test Pattern

The exposure dose and pitch are varied along rows and columns respectively.

# Figure 3.7

STEM micrograph of a interdigital grating with 50nm centre-to-centre spacing patterned on a 50nm thick GaAs membrane using two aligned lithographic steps. The light segment of the marker denotes 1µm.

1. Pattern low resolution ohmic contacts on solid heterostructure

2. Form Membrane

3. Pattern high resolution ohmic contacts on membrane

# Figure 3.9

Diagrams showing the fabrication of closely spaced ohmic contacts on 50nm thick GaAs membrane.

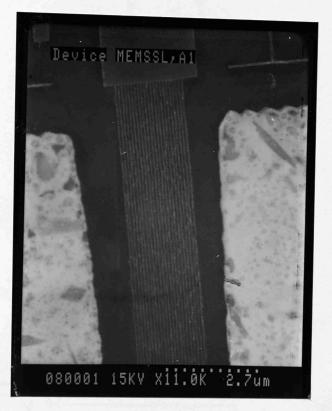

## Figure 3.10

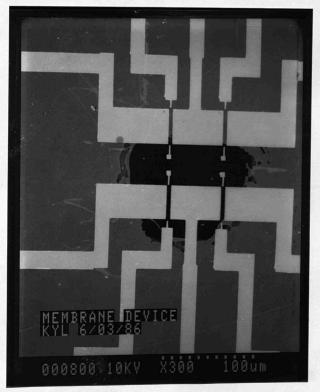

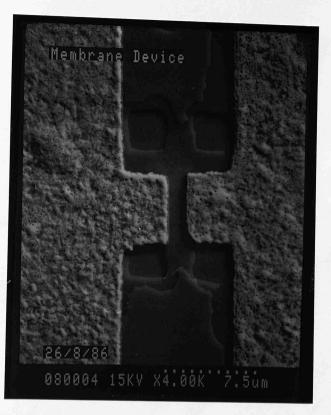

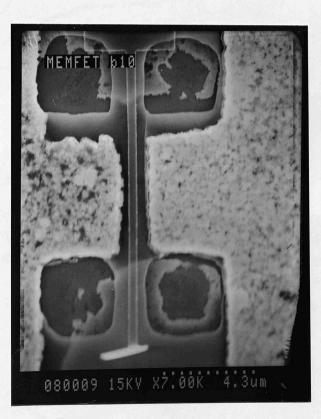

SEM micrographs of ungated MESFETs with closely spaced drain-source ohmic contacts patterned on 50nm thick GaAs membranes (dark areas)

## Figure 3.11

Graph showing the resistance between two ohmic contacts with  $1\mu m$  separation on the heterostucture at different anneal temperatures. The channel width was  $5\mu m$ .

# Figure 3.12

SEM micrograph showing hairline fracture on membrane caused by annealing of ohmic contacts.

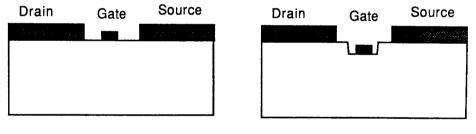

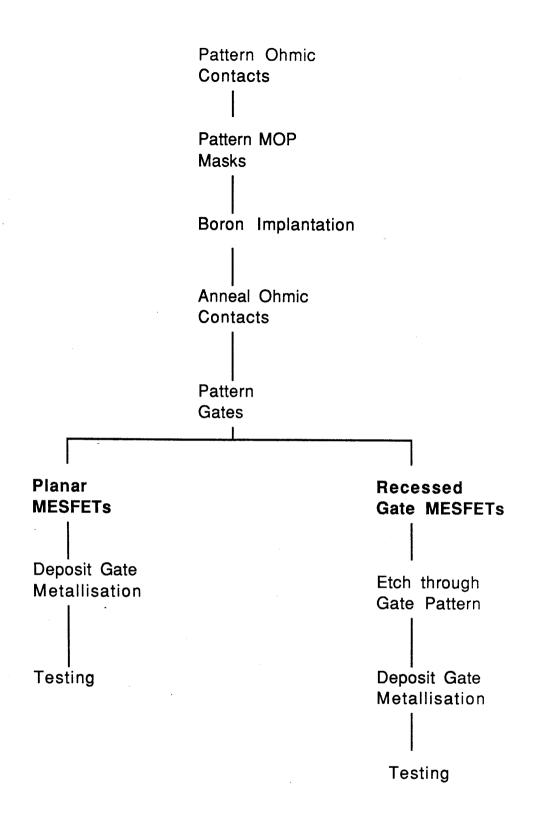

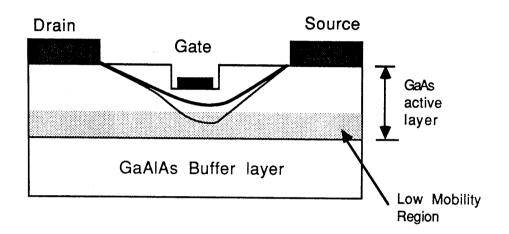

Chapter 4 The Fabrication of MESFETs and LSSLs on Thin Active GaAs Membranes

#### 4.1 Introduction

In this chapter, the process steps required for fabricating MESFETs (MEtal-Semiconductor Field Effect Transistors) and LSSLs (Lateral Surface SuperLattices) on 50 nm thick active GaAs ( $n^+ = 3 \times 10^{18}$  cm<sup>-3</sup>) membranes are described.

The fabrication process for making membrane MESFETs and LSSLs was based on the strategy developed in Chapter 3. An alternative method for fabricating membrane MESFETs has also been developed.

#### 4.1.1 Membrane MESFETs

Apart from the absence of a substrate, the structure of the membrane MESFET is similar to that on solid GaAs. A description of the device and the basis of its operation can be found in Chapter 6.

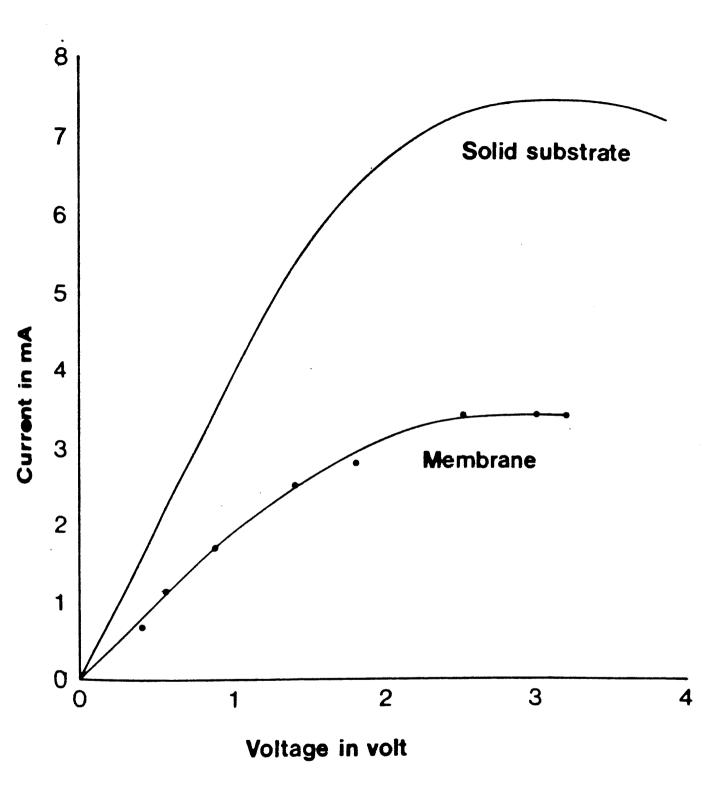

There are two reasons for making MESFETs on the thin substrates. Firstly, as was shown in chapter 3, the use of the membranes facilitates very high resolution electron beam lithography. The fabrication of 15 nm linewidths and ohmic drain-source contacts with separation as small as 0.2  $\mu$ m had been demonstrated on GaAs membranes. Secondly, membrane MESFETs can be compared with conventional devices on solid substrate to study the effect of the substrate on device operation. The basic idea of a superlattice, as first put forward by Esaki and Tsu (4.1), is to superimpose a one dimensional man made periodic potential on the atomic periodicity of the crystal structure. This additional periodicity splits the energy spectrum of the original crystal and produces minibands and minigaps which alter the physical properties of the original crystal (4.2).

The idea of a lateral superlattice was first put forward by Kastal'skii and Khusainov in 1970 (4.3), but the concept of an electrically controllable lateral surface superlattice (LSSL) was first proposed by Bate in 1977 (4.4). In order to form an LSSL, one must a) form a two-dimensional electron gas (2DEG) (the carriers can also be holes), and b) impose on it a periodic modulation in one or two dimensions (4.4-4.8).

A 2-DEG refers to an ensemble of electrons which are confined to a thin layer such that the number of degrees of spatial freedom of an electron is reduced from three to two. The criterion for observing superlattice effect is that the period of the external modulation has to be comparable to or less than the scattering length  $\lambda$  of an electron. Earlier analysis had assumed  $\lambda$  to be the shortest scattering length i.e. the elastic scattering length (4.2). But recent work by Warren et. al. (4.5) indicates that  $\lambda$  is associated with the longer inelastic scattering length.

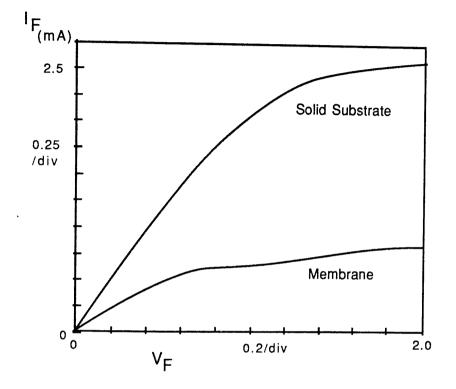

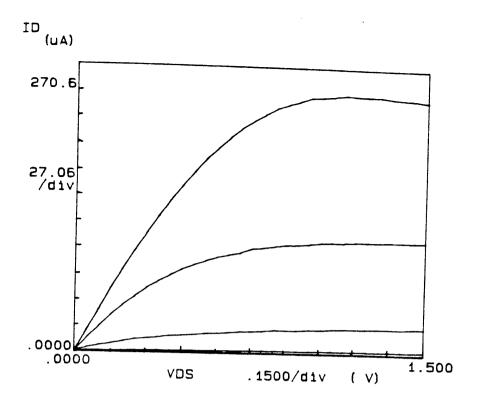

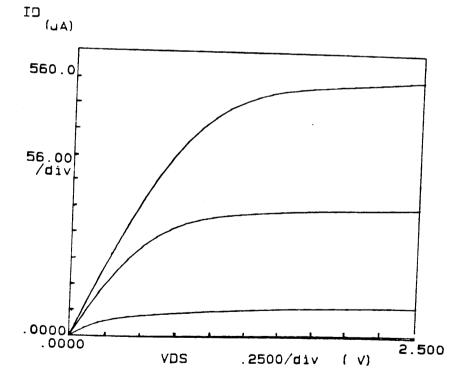

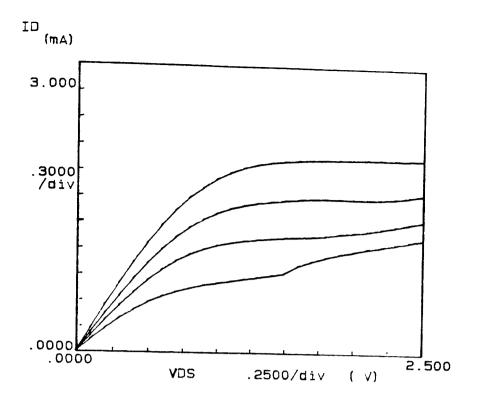

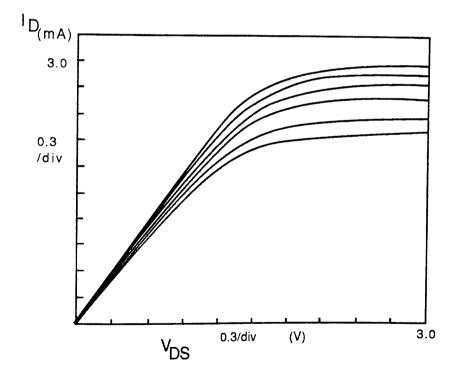

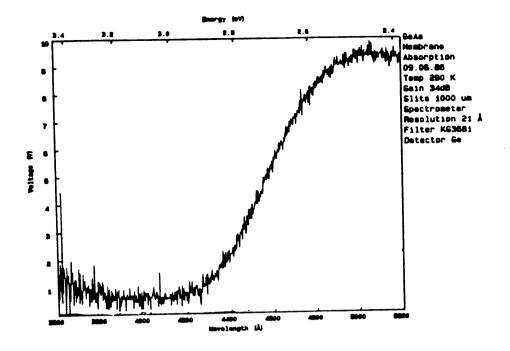

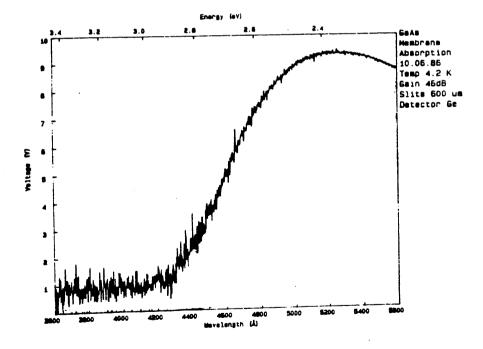

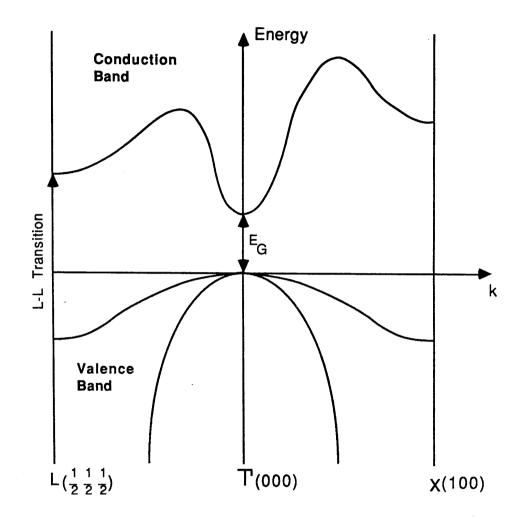

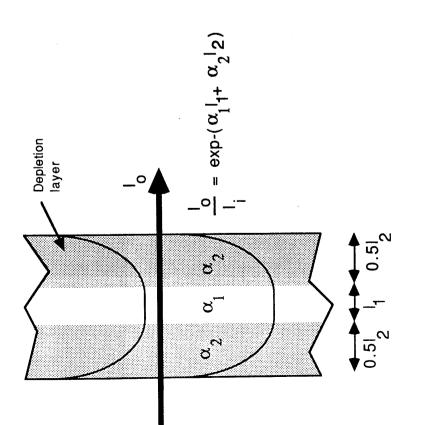

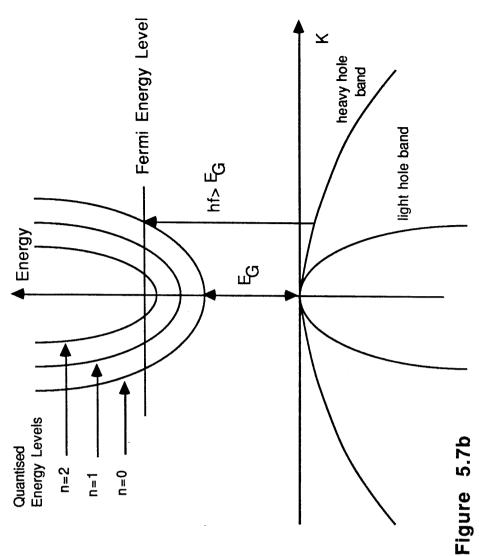

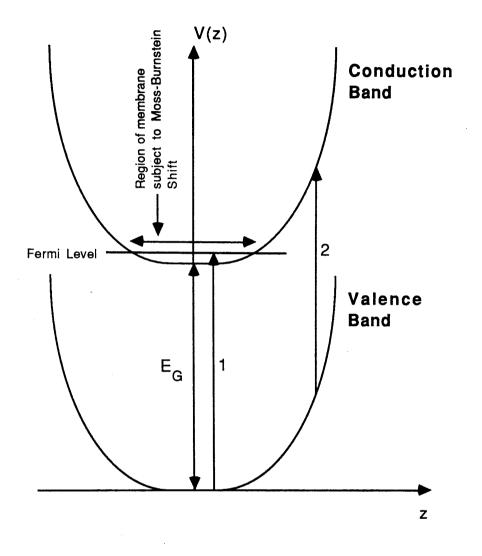

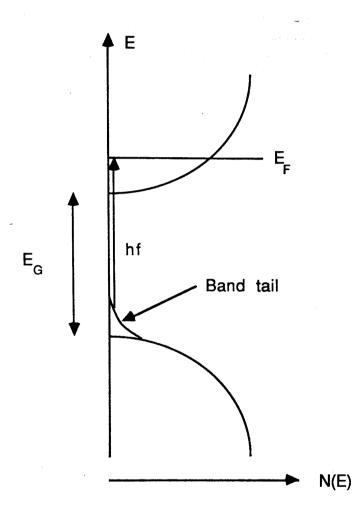

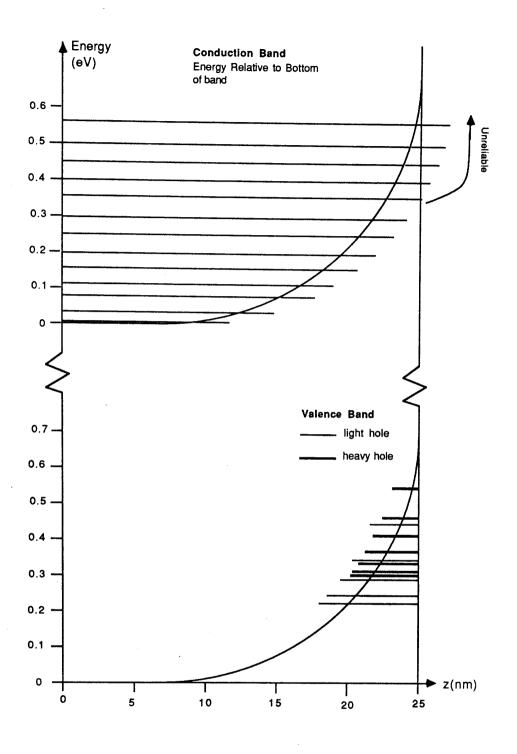

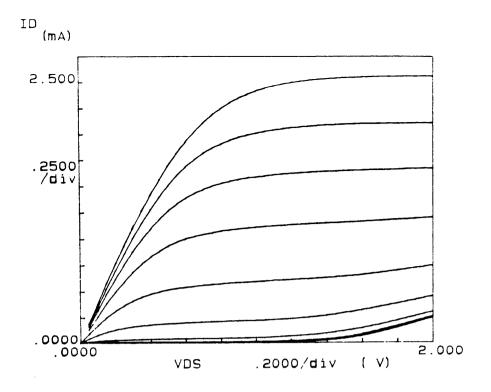

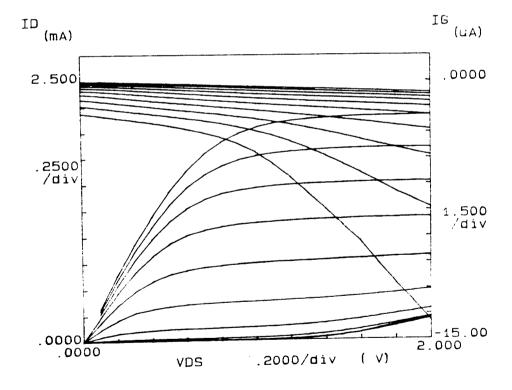

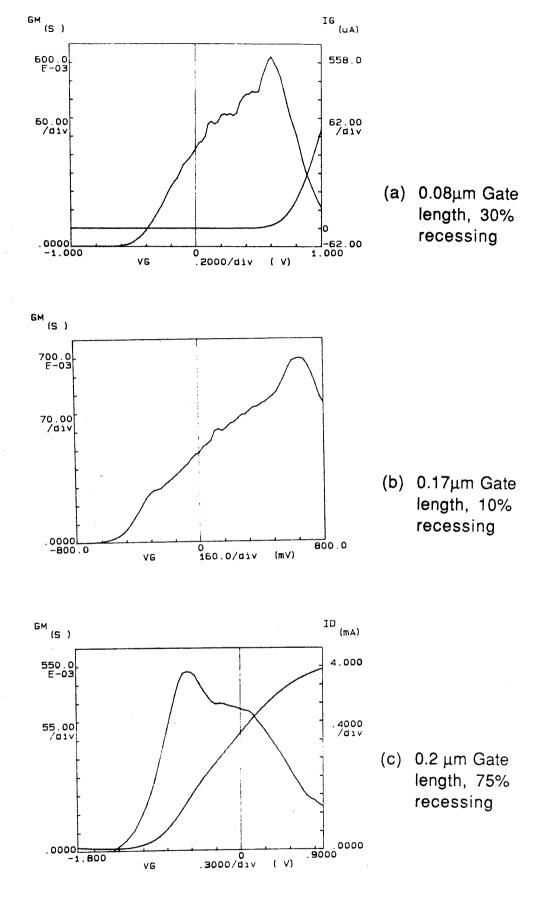

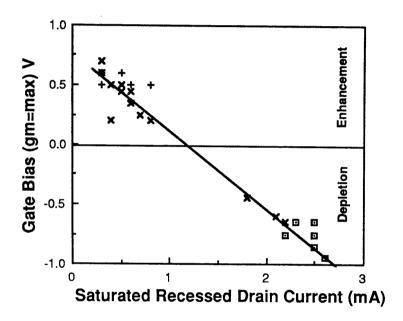

The proposed structure of the LSSL is shown in Figure 3.8. The device is similar to the membrane MESFET but with a grating in place of the gate. This induces a periodic Schottky potential which can be controlled externally. The inelastic scattering length of an electron in n-GaAs doped to 3 X  $10^{18}$  cm<sup>-3</sup> had been measured by