Liu, Fengyuan (2020) *Layer by layer printing of nanomaterials for largearea, flexible electronics.* PhD thesis.

https://theses.gla.ac.uk/77874/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses <u>https://theses.gla.ac.uk/</u> research-enlighten@glasgow.ac.uk

# Layer by Layer Printing of Nanomaterials for Large-Area, Flexible Electronics

### Fengyuan Liu

A thesis submitted in fulfilment of the requirements for the degree of

Doctor of Philosophy

The University of Glasgow

James Watt School of Engineering, College of Science and Engineering

September 2019

### Abstract

Large-area electronics, including printable and flexible electronics, is an emerging concept which aims to develop electronic components in a cheaper and faster manner, especially on those non-conventional substrates. Being flexible and deformable, this new form of electronics is regarded to hold great promises for various futuristic applications including the internet of things, virtual reality, healthcare monitoring, prosthetics and robotics. However, at present, large-area electronics is still nowhere near the commercialisation stage, which is due to several problems associated with performance, uniformity and reliability, etc. Moreover, although the device's density is not the major concern in printed electronics, there is still a merit in further increasing the total number of devices in a limited area, in order to achieve more electronic blocks, higher performance and multiple functionalities.

In this context, this Ph.D. thesis focuses on the printing of various nanomaterials for the realisation of high-performance, flexible and large-area electronics. Several aspects have been covered in this thesis, including the printing dynamics of quasi-1D NWs, the contact problem in device realisation and the strategy to achieve sequential integration (3D integration) of the as-printed devices, both on rigid and flexible substrates. Promisingly, some of the devices based on the printed nanomaterial show a comparable performance to the state-of-the-art technology. With the demonstrated 3D integration strategy, a highly dense array of electronic devices can be potentially achieved by printing method.

This thesis also touches on the problem associated with the circuit and system realisation. Specifically, graphene-based logic gates and NW based UV sensing circuit has been discussed, which shows the promising applications of nanomaterial-based electronics. Future work will be focusing on extending the UV sensing circuit to an active matrix sensor array.

## List of Publication

Selected portions of work discussed in this thesis are published or under preparation for publication as listed below.

### Journal Articles

- van der Waals Contact Engineering of Graphene Field-Effect Transistors for Large-Area Flexible Electronics

F. Liu, W. T. Navaraj, N. Yogeswaran, D. H. Gregory, R. Dahiya

ACS Nano, 13 (3), 3257-3268 (2019)

- Heterogeneous Integration of Contact-Printed Semiconductor Nanowires for High-Performance Devices on Large Areas

C. G. Núñez, F. Liu, W. T. Navaraj, A. Christou, D. Shakthivel, R Dahiya

Microsystems & Nanoengineering 4 (1), 22 (2018)

- 3) Ultra-Flexible, Printed Active Matrix for Wearable UV Sensor Array (under preparation)

### **Conference Proceedings**

Flexible Logic Circuits by using Van Der Waals Contacted Graphene Field-Effect Transistors

F. Liu, N. Yogeswaran, W. Navaraj, R. Dahiya

In IEEE International Symposium on Circuits and Systems (ISCAS), 1-5 (2019)

2) 3D Integrated Electronics with Layer by Layer Printing of NWs

F. Liu, A. Christou, R. Dahiya

In IEEE International Conference on Flexible and Printable Sensors and Systems (FLEPS) (2019)

### Book and Monograph

Integration Techniques for Micro/Nanostructure-Based Large-Area Electronics

C. G. Núñez, F. Liu, S. Xu, R. Dahiya

*Cambridge University Press* (2018)

Papers which are linked to the overall project but beyond the scope of this thesis are listed below:

#### Journal Articles

Large-Area Soft ESkin: The Challenges beyond Sensor Designs.

R. Dahiya, N. Yogeswaran, F. Liu, L. Manjakkal, E. Burdet, V. Hayward, H. Jörntell

#### Proceedings of the IEEE (in press)

2) Large-Area Self-Assembly of Silica Microspheres/Nanospheres by Temperature-Assisted Dip-Coating

C. G. Núñez, W. T. Navaraj, F. Liu, D. Shakthivel, R. Dahiya

- ACS Applied Materials & Interfaces 10 (3), 3058-3068 (2018)

- ZnO Nanowires-Based Flexible UV Photodetector System for Wearable Dosimetry C. G. Núñez, A. Vilouras, W. T. Navaraj, F. Liu, R Dahiya *IEEE Sensors Journal* 18 (19), 7881-7888 (2018)

- Piezoelectric Graphene Field Effect Transistor Pressure Sensors for Tactile Sensing N. Yogeswaran, W. T. Navaraj, S. Gupta, F. Liu, V. Vinciguerra, L. Lorenzelli, R. Dahiya

Applied Physics Letters 113 (1), 014102 (2018)

### **Conference Proceedings**

- Graphene-ZnO NWs Hybrid Film for Lrge-Area UV Photodetector

F. Liu, N. Yogeswaran, W. Navaraj, R. Dahiya

In *IEEE Sensors Conference* (2018)

- Contact-Printing of Zinc Oxide Nanowires for Chemical Sensing Applications

C. G. Núñez, L. Manjakkal, F. Liu, R Dahiya

In *IEEE Sensors Conference* (2018)

- Transforming the Short-Term Sensing Stimuli to Long-Term E-skin Memory

F. Liu, W. Taube, N. Yogeswaran, D. Gregory, R. Dahiya

In *IEEE Sensors Conference* (2017)

- 4) ZnO Nanowires based Flexible UV Photodetectors for Wearable Dosimetry

C. G. Nunez, W. Taube, F. Liu, R. Dahiya

In *IEEE Sensors Conference* (2017)

- 5) Nanomaterials Processing for Flexible Electronics

D Shakthivel, F Liu, CG Núñez, W Taube, R Dahiya

In IEEE 26th International Symposium on Industrial Electronics (ISIE) (2017)

- 6) Towards Flexible Magnetoelectronics for Robotic Applications

H. Heidari, F. Liu, R Dahiya

In 2nd Asia-Pacific Conference on Intelligent Robot Systems (ACIRS), 295-298 (2017)

- Modelling of Nanowire FETs based Neural Network for Tactile Pattern Recognition in E-Skin

W. Taube, **F. Liu**, A. Vilouras, D. Shaktivel, C. G. Nunez, H. Heidari, F. Labeau, D. Gregory, R. Dahiya

In IEEE Biomedical Circuits and Systems Conference (BioCAS), 572-575 (2016)

This dissertation is dedicated to my family, friends and those

people who have helped and supported me in the past.

### Acknowledgement

First, I would like to acknowledge the Lord Kelvin and Adam Smith (LKAS) Ph.D. Scholarship from University of Glasgow, without which this study would not have started.

I would like to express my deepest gratitude to my supervisor Professor Ravinder Dahiya, with whom I have privileged to work together for four years. His guidance and support are one of the most valuable treasures in my life. I am also greatly thankful to my second supervisor, Professor Duncan Gregory, for providing valuable guidance to this project from an excellent chemist point of view.

I would like to specially thank Dr. Carlos Garcia Nunez, Dr. William Navaraj and Dr. Dhayalan Shakthivel, the old "Nanowire team". We have together been through a tough time, starting all the researches from scratch. All of you are excellent researchers and have inspired me a lot. Taking this opportunity, I wish you all the best for the future.

I would like to extend my appreciations to all my colleagues at BEST group, especially:

Dr. Nivasan Yogeswaran: For together working on graphene and nanowires, and helped me in many aspects.

Dr. Shoubhik Gupta: For arranging several wonderful trips as well as keeping us safe.

Dr. Wenting Dang: For being the only Chinese in the group (except myself) during the first two years. Also for saving our wonderful "northern light tour" in Iceland by negotiating with the irresponsible travel agency in a firm, polite but harsh manner.

Anastasios Vilouras: For together making the impressive leaflet and handling the group social media.

Habib: For being my roommate during the stay in India.

Adamos: For your great contribution to the project as an excellent mechanical engineer.

Fabiane and Saoirse: For kindly arranging several activities which have greatly released some of my pressure during the thesis writing stage.

I would like to thank the great support from "the Chinese community" in University of Glasgow, especially Dr. Song Tang, Dr. Chengzhi Xie, Dr. Jiaying Zhang and Dr. Jue Wang. All of you are so generous and friendly. Without your help, I would have suffered a lot.

I would also like to thank James Watt Nanofabrication Centre (JWNC) and the staff maintaining its operation. This is really a dream cleanroom to work in.

Last but not least, I want to thank my parents and my wife. Your love is the biggest motivation in my life.

# Table of Contents

| Abstract                                                                    | 2  |

|-----------------------------------------------------------------------------|----|

| List of Publication                                                         | 3  |

| Acknowledgement                                                             | 7  |

| Table of Contents                                                           | 8  |

| List of Tables                                                              | 10 |

| List of Figures                                                             | 11 |

| Author's Declaration                                                        |    |

| Definitions/Abbreviations                                                   | 19 |

| 1. Chapter 1. Introduction                                                  | 21 |

| 2. Chapter 2. The State of the art in printed and 3D integrated electronics |    |

| 2.1 Printing technologies                                                   | 25 |

| 2.1.1 Conductors                                                            |    |

| 2.1.2 Semiconductors                                                        |    |

| 2.1.3 Dielectrics                                                           |    |

| 2.1.4 All printed electronics                                               |    |

| 2.1.5 Methodologies in printable electronics                                |    |

| 2.2 3D integration technologies                                             | 45 |

| 2.2.1 Parallel integrated 3D electronics                                    |    |

| 2.2.2 Monolithic 3D electronics by printing techniques                      |    |

| 2.3 Summary                                                                 | 53 |

| 3. Chapter 3. Printing nanomaterials on rigid and flexible substrates       | 55 |

| 3.1 Printing of quasi-1D NWs for large-area, flexible electronics           | 55 |

| 3.1.1 Why and how NW is good for flexible electronics?                      | 56 |

| 3.1.2 A home-made, close-loop controlled contact printing set-up            | 57 |

| 3.1.3 An image analysis approach                                            |    |

| 3.1.4 The study of the NW printing mechanics                                | 61 |

| 3.2 Transfer printing graphene for large-area, flexible electronics         | 72 |

| 3.2.1 Why and how graphene is good for flexible electronics?                | 72 |

| 3.2.2 The graphene transfer process                                         | 74 |

| 3.3 Screen printing of conductive electrodes for interconnect application   | 77 |

| 3.3.1 The influence of the surface treatment of the receiver substrate      | 78 |

| 3.3.2 The influence of the curing temperature and duration                  | 78 |

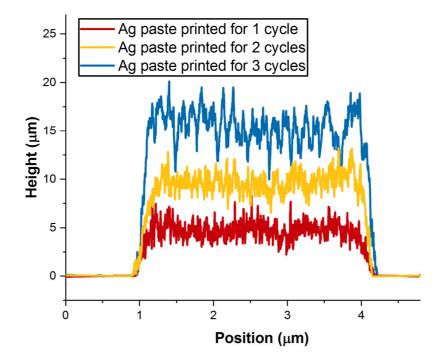

| 3.3.3 The influence of printing cycles                                      | 79 |

| 3.4 Summary                                                                 | 80  |

|-----------------------------------------------------------------------------|-----|

| 4. Chapter 4: Contact problem in printed and flexible electronics           | 81  |

| 4.1 The vdW contacted ZnO NW FET                                            | 82  |

| 4.2 Motivation for realising bottom contacted GFETs                         |     |

| 4.3 The experimental process to realise bottom contacted GFETs              |     |

| 4.4 The measurement of vdW contacted GFETs on rigid substrate               |     |

| 4.5 Analysis of graphene-Au separation in vdW and non-vdW contacted devices | 96  |

| 4.6 Carrier transport mechanism in graphene-Au vdW and non-vdW contact      | 99  |

| 4.7 Carrier transport mechanism in vdW contacted GFET                       | 102 |

| 4.8 Difference in graphene-Au vdW contact and ZnO-Au vdW contact            | 107 |

| 4.9 Summary                                                                 | 107 |

| 5. Chapter 5: Realising flexible electronics by printing approaches         | 108 |

| 5.1 Substrates in flexible electronics                                      | 108 |

| 5.2 Dielectrics in flexible electronics                                     | 111 |

| 5.3 Flexible ZnO NW based UV photodetector                                  | 115 |

| 5.4 vdW contact in flexible electronics                                     | 119 |

| 5.5 Flexible GFETs and logic circuits                                       | 122 |

| 5.6 Summary                                                                 | 126 |

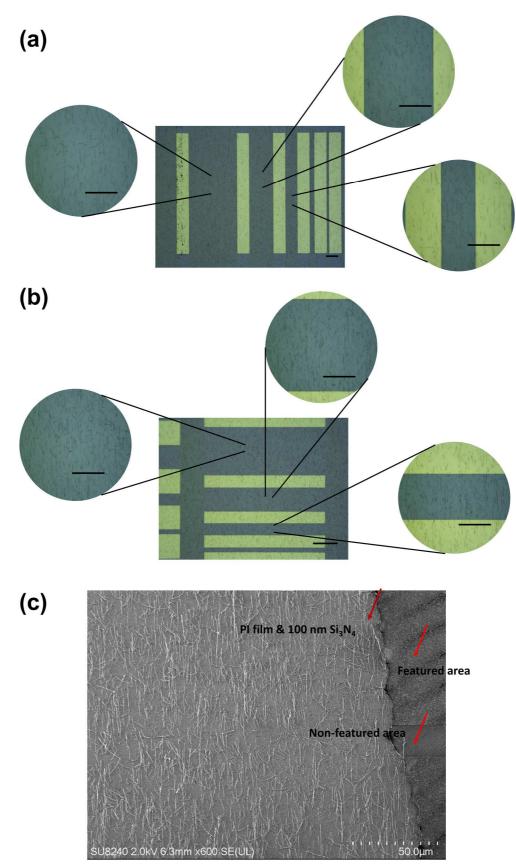

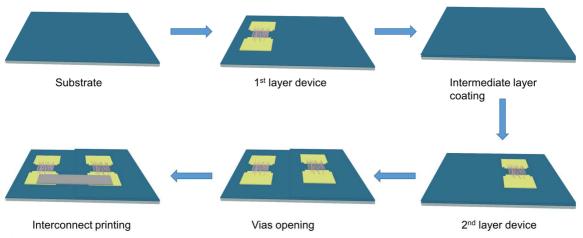

| 6. Chapter 6: 3D integration in printed electronics                         | 128 |

| 6.1 Technical challenges in 3D integration process                          | 128 |

| 6.1.1 Separation layer and planarisation problem                            | 128 |

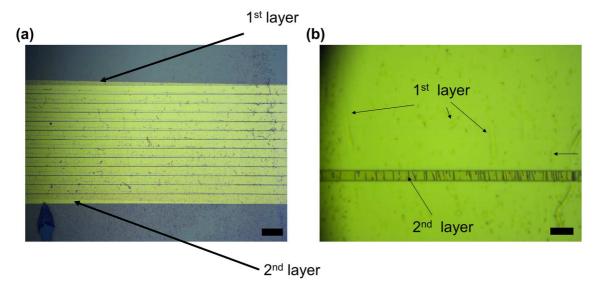

| 6.1.2 Vias opening                                                          | 131 |

| 6.1.3 Interconnects realisation                                             | 133 |

| 6.2 3D integrated Wheatstone bridge based on Si and ZnO NWs                 | 135 |

| 6.3 3D integrated FETs and sensors for large-area active matrix application | 138 |

| 7. Chapter 7. Conclusion and Future Perspective                             | 142 |

| 7.1 Conclusion                                                              | 142 |

| 7.2 Future perspective                                                      | 143 |

| Bibliography                                                                | 144 |

## List of Tables

| <b>Table 2.1:</b> Summary of printed conductive materials.                            | 29       |

|---------------------------------------------------------------------------------------|----------|

| <b>Table 2.2:</b> Summary of printable semiconducting materials.                      | 32       |

| Table 2.3: Dielectric properties of various materials.                                | 34       |

| <b>Table 2.4:</b> Comparison of the properties of various printing techniques.        | 44       |

| Table 2.5: Comparison of various parameters and strategies for 3D integrated electron | nics by  |

| printing techniques                                                                   | 53       |

| Table 3.1: Details for various receiver substrates used in the contact printing study | 65       |

| Table 4.1: Comparison of device performance with the state of art CVD graphene FE     | Τ.       |

| Copyright © American Chemical Society. Reprinted, with permission, from [12]          | 91       |

| Table 4.2: Comparison of monolayer graphene-metal contact properties at room temp     | erature. |

| Copyright © American Chemical Society. Reprinted, with permission, from [12]          | 94       |

| Table 5.1: Tested conditions for graphene-Au vdW contact.                             | 119      |

| Table 5.2: Comparison of monolayer graphene-metal contact properties on flexible su   | ıbstrate |

| at room temperature. Copyright © American Chemical Society. Reprinted, with permit    | ission,  |

| from [12].                                                                            | 122      |

|                                                                                       |          |

### List of Figures

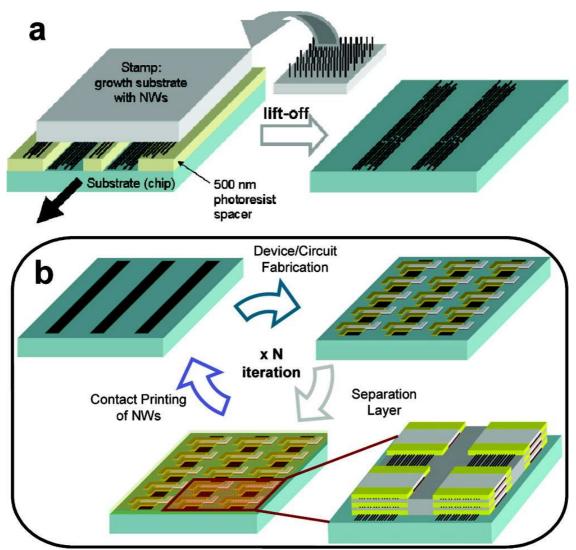

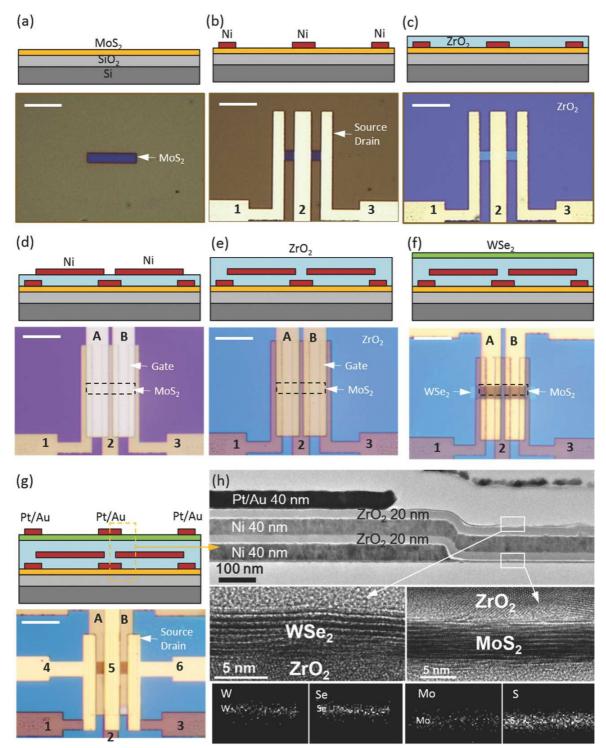

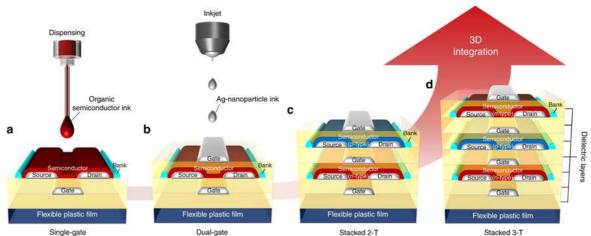

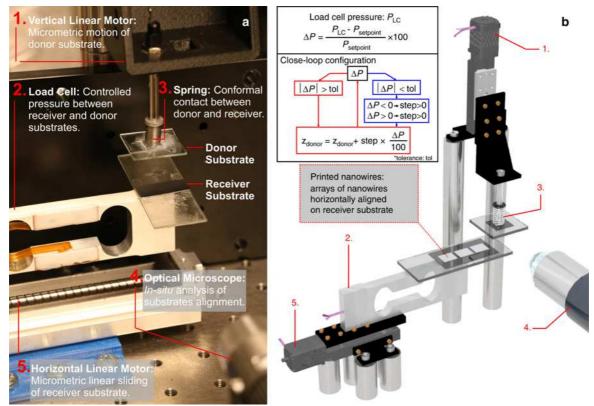

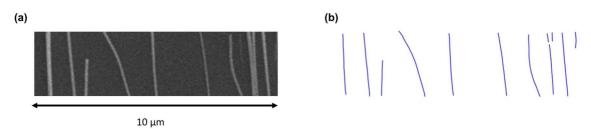

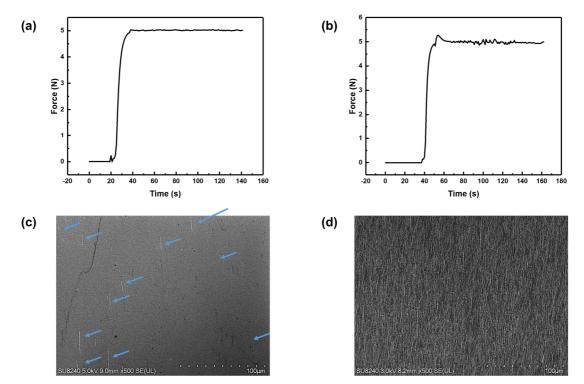

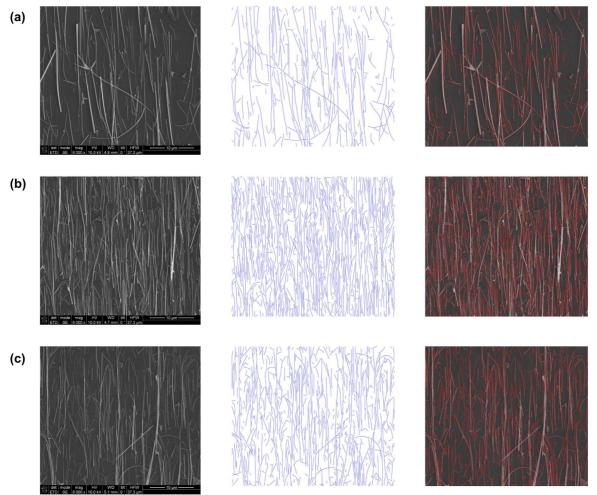

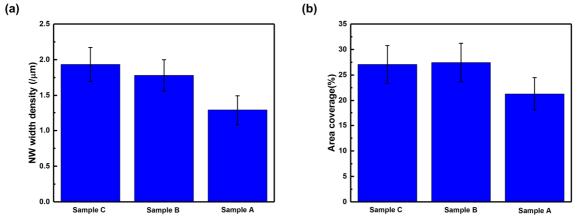

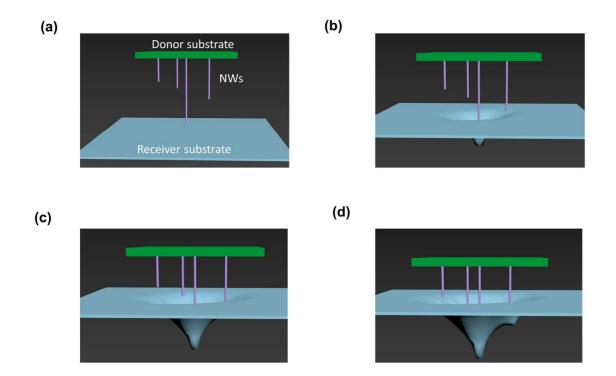

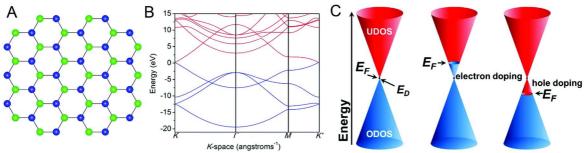

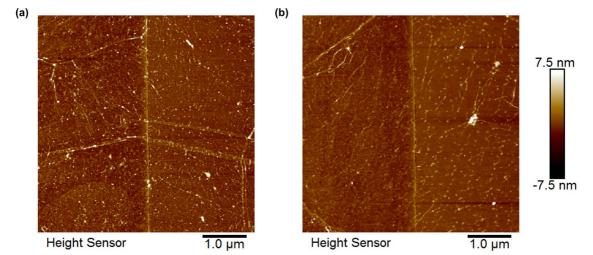

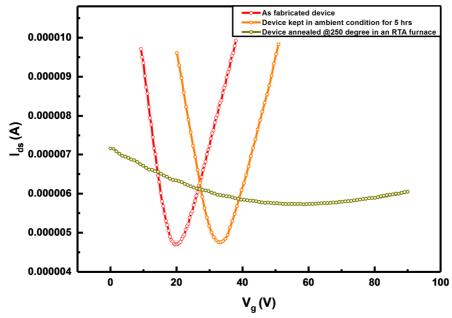

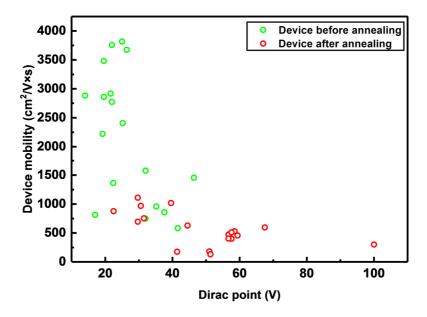

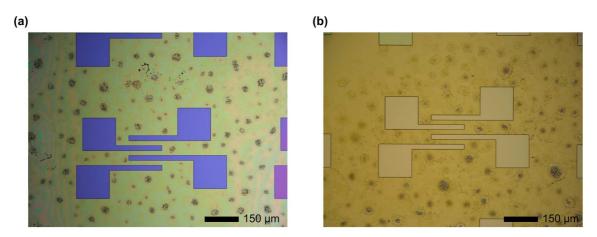

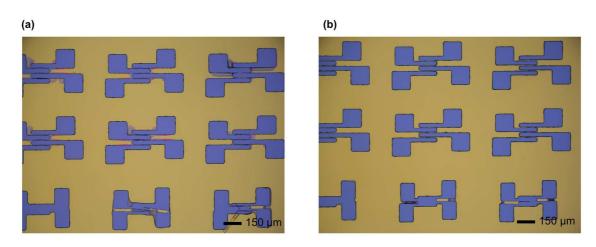

Figure 1.1: The schema showing the two possible roadmaps of electronics development, Figure 2.1: The Block diagram showing the classification of various printing techniques....26 Figure 2.2: The schema and examples for wet printed and dry printed contact pads. (a). (b) and (c) The typical schema and example of wet printed contacts. (d) and (e) The typical schema and example of dry printed contacts. (f) The example of metal contacts fabricated by conventional microfabrication process including photolithography and metal deposition on to the active material, leading to a contact with many defects and surface states Reprinted and adapted with permission. (a), (b) and (c) are from Ref [24]. Copyright © John Figure 2.3: Typical examples of printed semiconductors. (a) The inkjet printing of single crystal of C8-BTBT layer and its characterisations. The POM image shown on the bottom left indicates its crystallinity. (b) The inkjet printing of graphene based FET. (c) The wet printed CNT circuits with reasonable performance. (d) Printed quantum dots for XXX application. Reprinted and adapted with permission. (a) and (d) is from Ref [52].and [51], respectively. Copyright © Springer Nature. (b) and (c) are from Ref [98] and [58], respectively Copyright Figure 2.4: Typical examples of printed dielectrics. (a) The printing of solution based dielectric materials and corresponding characterisations. (b) The stamp printing of hBN for dielectric and encapsulation of GFET. Reprinted and adapted with permission. (a) is from Ref Figure 2.5: All printed electronic devices. (a) The solar cell fabricated by inkjet printing (b) The photodetectors realised by inkjet printing (c) All printed memory device (d) A all 2D material based transistor realised by transfer printing. Reprinted and adapted with permission. (a) is from Ref [90]. Copyright © John Wiley and Sons. (b) is from Ref [91]. Open access. (c) is from Ref [97]. Copyright © American Chemical Society. (d) is from [81]. Copyright © Figure 2.6: Schema of various printing technologies. (a) Inkiet printing (b) Screen printing (c) Transfer printing and (d) Contact printing. Reprinted and adapted with permission. (a) is from Ref [90]. Copyright © John Wiley and Sons. (b) is from Ref [107]. Copyright © American Scientific Publishers. (c) is from Ref [64]. Open access. (d) is from [123]. Figure 2.7: Roll-to-Roll printing technology. The Roll-to-Roll version of (a) inkjet printing, (b) screen printing, (c) contact printing, (d) polymer assisted transfer printing and (e) stamp assisted transfer printing. Reprinted and adapted with permission. (a) and (b) are from Ref [129]. Copyright © John Wiley and Sons. (c) is from Ref [133]. Copyright © AIP Publishing. (d) is from [131]. Copyright © Springer Nature. (e) is from Ref [130]. Copyright © John Figure 2.8: Contact printing NWs for the realisation of 3D electronics [127]. (a) The schema illustration of contact printing process. (b) The schema illustrating the method to achieve 3D integrated electronics. Reprinted and adapted with permission. (a) and (b) are from Ref [127]. Figure 2.9: The fabrication process flow for realisation of 3D integrated electronics from quasi-2D materials and corresponding characterisation images. (a) Transfer of MoS<sub>2</sub>. (b) Metallisation of the source and drain contacts for 1<sup>st</sup> layer device. (c) The deposition of dielectric material for 1<sup>st</sup> layer device. (d) The deposition of the shared gate electrodes. (e) The deposition of gate material for 2<sup>nd</sup> layer device (f) The transfer of WSe2 on the 2<sup>nd</sup> layer.

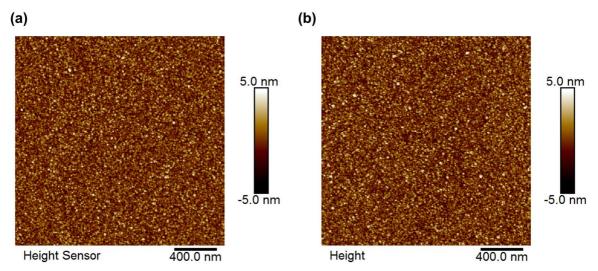

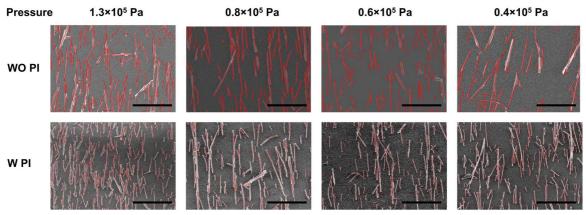

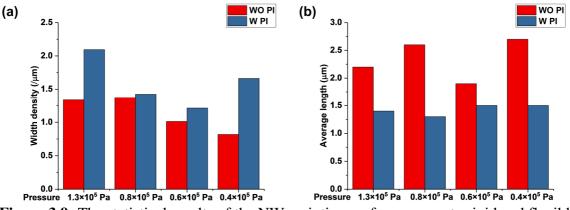

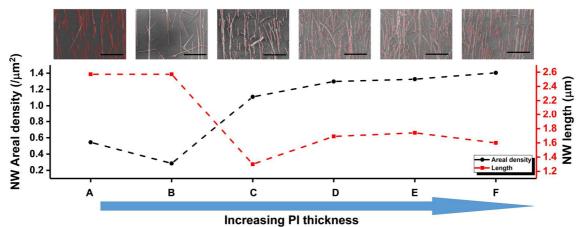

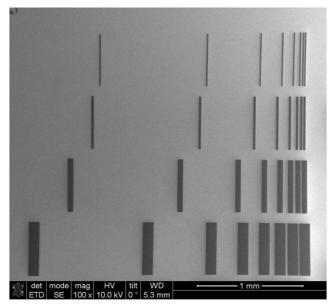

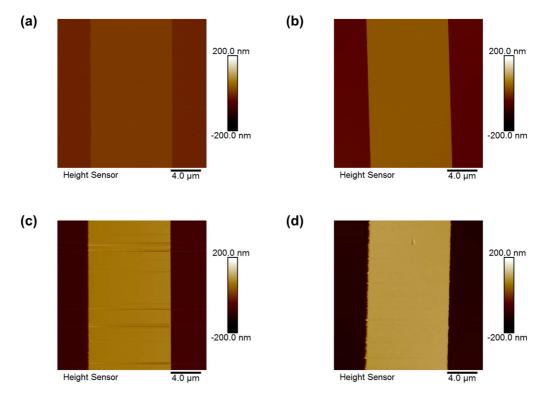

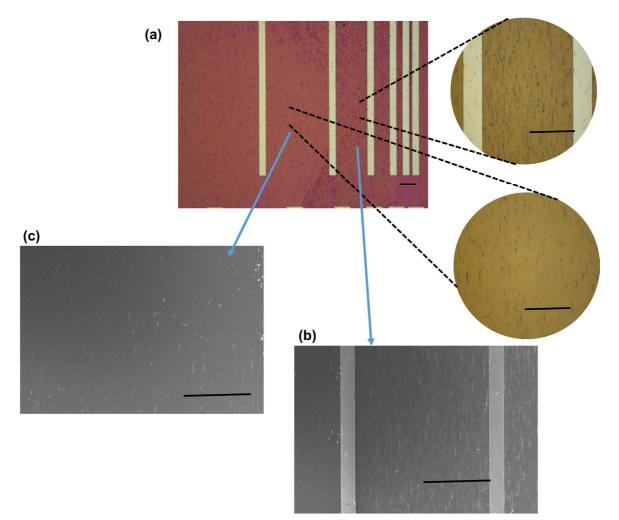

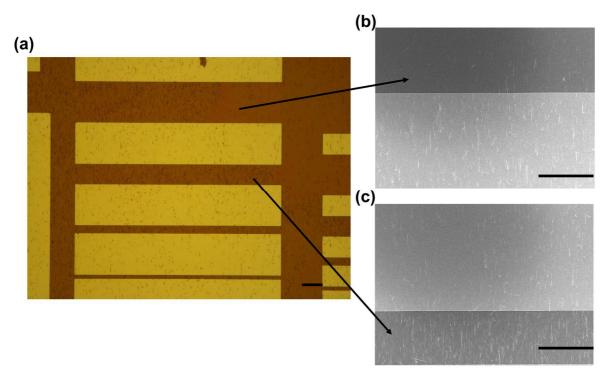

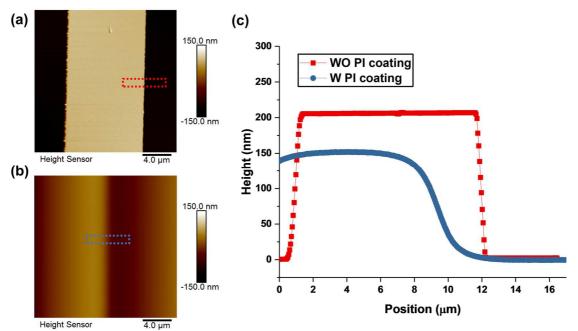

(g) Metallisation of the source and drain contacts for 2<sup>nd</sup> layer device. (h) The TEM characterisation of the cross section of the fabricated 3D device. Reprinted and adapted with Figure 2.10: The schema showing the fabrication process flow to realise the 3D integrated electronics based on organic material by inkjet printing. (a) The realisation of single gate device. (b) The realisation of dual gate device. (c) The realisation of the vertically stacked two transistors by inkjet printing. (d) The realisation of the vertically stacked 3 transistors by inkjet printing. Reprinted and adapted with permission. (a) to (c) are from Ref [158]. Open Figure 3.1: The photograph (a) and the schematic illustration (b) of the contact printing setup, version 1. Reprinted and adapted with permission. (a) and (b) are from Ref [176]. **Figure 3.2:** The self-adjustable platform used in the 2<sup>nd</sup> version of the contact printing Figure 3.3: Validation of the modified software to vectorise the NWs from the SEM image. (a) A specifically cropped SEM image, with the image width covering  $10 \mu m$ ; (b) the Figure 3.4: The comparison between the wet and dry printed NWs. (a) and (b) show the contact force applied in the wet and dry printing process, respectively. (c) and (d) show the SEM characterisation of the printed NWs from the wet and dry printing, respectively......60 Figure 3.5: The SEM image of NWs printed on Si/SiO<sub>2</sub> substrate (a) without plasma treatment; (b) and (c) with plasma treatment. The results shown in (b) was printed within 30mins after plasma treatment while in (c) the NWs were printed after 24hrs after plasma treatment. The images on left, middle and right represent the original, the vectorised, and the overlapped images, respectively. Copyright © 2019 IEEE. Reprinted, with permission, from [159].....61 Figure 3.6: Comparison of width density (a) and area coverage (b) for ZnO NWs printed onto Si/SiO<sub>2</sub> substrates treated under different conditions. Copyright © 2019 IEEE. Figure 3.7: The AFM characterisation of the (a) rigid substrate and (b) flexible substrate. The rigid substrate refers to the Si/SiO<sub>2</sub> wafer deposited with 100 nm Si<sub>3</sub>N<sub>4</sub>, while the flexible substrate refers to the spin-coated PI film deposited with 100 nm Si<sub>3</sub>N<sub>4</sub>. The carrier wafer for the spin-coated PI film is Si/SiO2. Copyright © 2019 IEEE. Reprinted, with permission, from [159].....63 Figure 3.8: The SEM characterisations of the NWs printed onto rigid and soft substrates Figure 3.9: The statistical results of the NWs printing performance onto rigid and flexible substrates. (a) and (b) shows the width density and average length of the printed NWs under Figure 3.11: The schemas showing NW printing on receiver substrates with different Figure 3.12: The SEM image showing the surface of the receiver substrate with various features on top......67 Figure 3.13: The AFM characterisation of the receiver substrates with features of various height......67 Figure 3.14: Images of NW printing onto uneven substrate. (a) The optical microscope image showing the NWs printed on the receiver substrate with features of 20 nm. All the

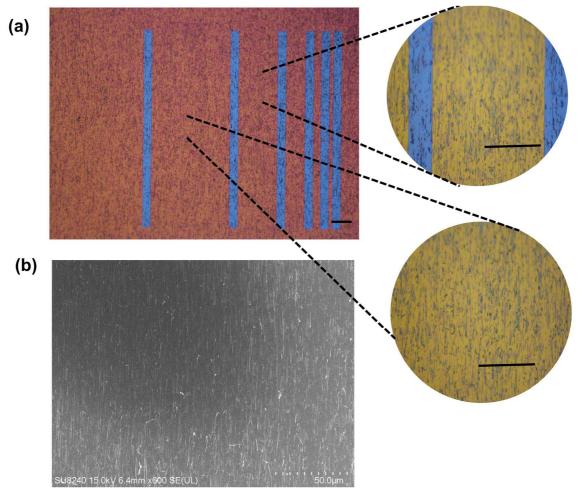

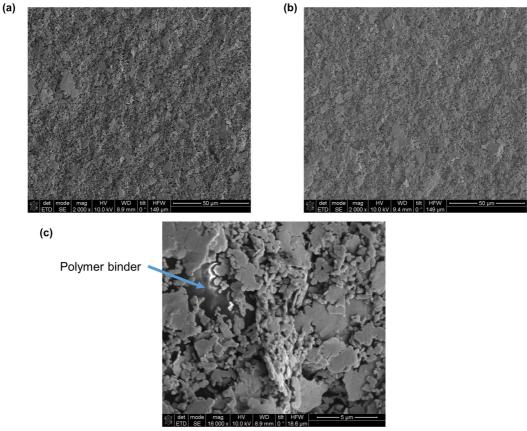

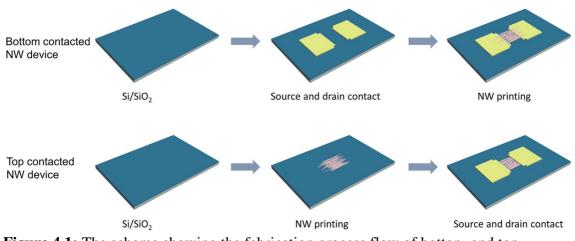

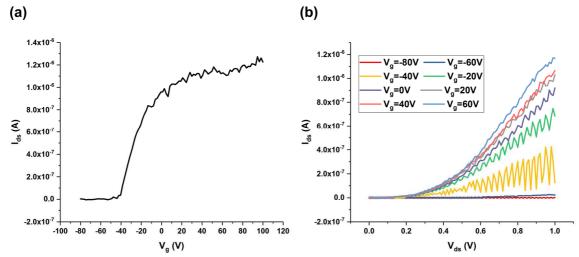

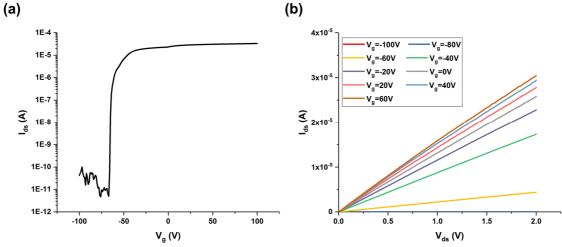

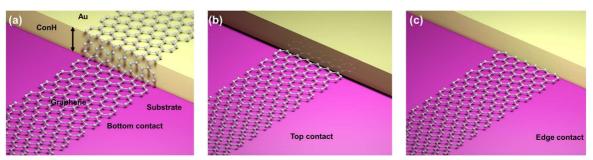

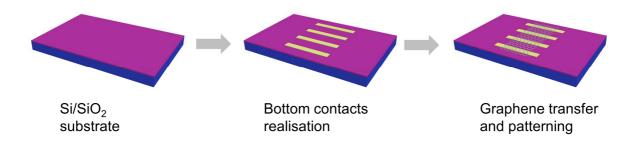

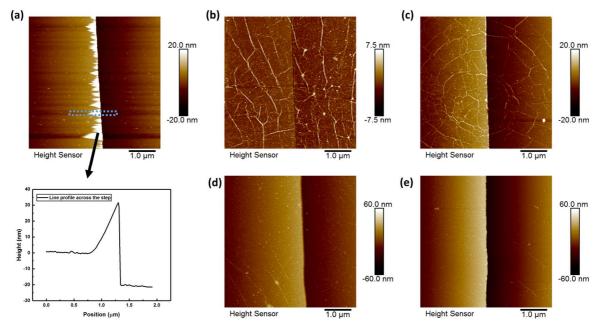

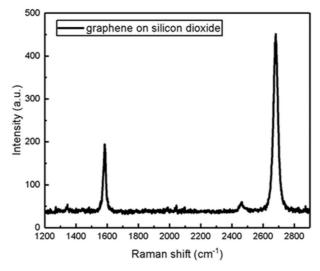

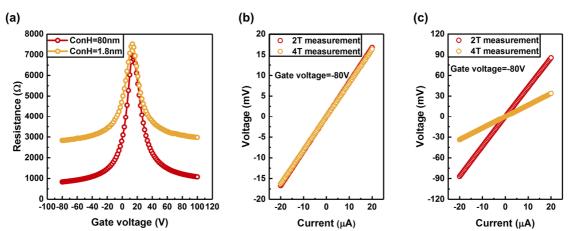

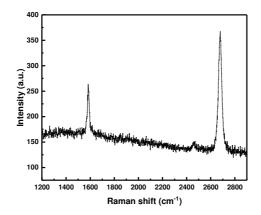

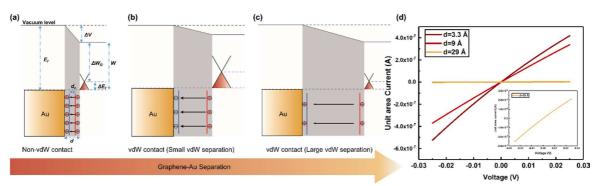

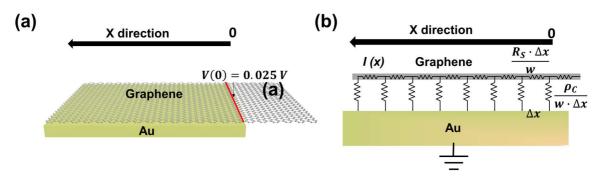

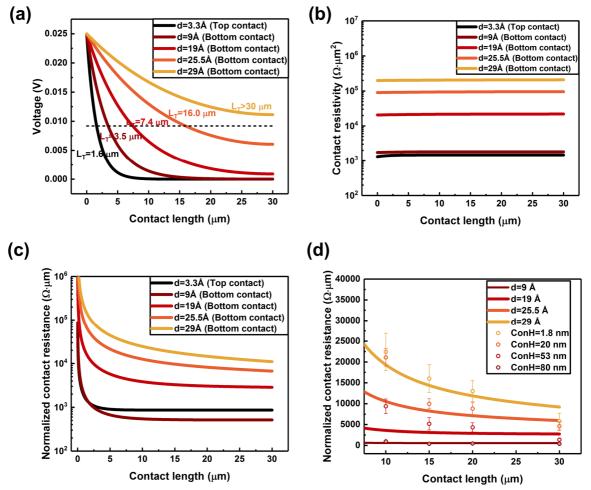

Figure 3.15: Images of NWs printed onto uneven substrates. Optical microscope (a) and SEM images (b and c) showing the results of NWs printed onto uneven substrates, with the Figure 3.16: Characterisation of NWs printed onto uneven substrates. Optical microscope (a) and SEM images (b and c) showing the results of NWs printed onto uneven substrates, with the printing direction perpendicular to the feature direction. All the scale bars are 50 µm. ...70 Figure 3.17: Images of NWs printed onto flattened substrates. (a) and (b) Optical microscopy images (c) SEM images. All the scale bars are 50 µm......70 Figure 3.18: The AFM characterisations of the features before and after flattening. (a) and (b) The AFM scans of the features before and after PI flattening. (c) The line profiles of the Figure 3.19: The lattice and band structure of graphene. A The honeycomb lattice structure of graphene. B The calculated band structure of graphene. C The schema showing the liner dispersion relationship near the Dirac cone. This figure is reused from Ref [166]. Copyright **Figure 3.20**: AFM characterisation of the transferred graphene. (a) as-transferred film (b) transferred film after a thermal annealing process in an RTA furnace The lattice and band structure of graphene. A The honevcomb lattice structure of graphene. B The calculated band structure of graphene. C The schema showing the liner dispersion relationship near the Dirac cone. This figure is reused from Ref [166]. Copyright © The Royal Society of Chemistry...74 Figure 3.22: Device performance of GFETs before and after the thermal annealing in an Figure 3.23: The SEM characterisations of the screen printed silver film. (a) Sample A (b) Sample B (c) The enlarged SEM image (from sample A), showing the polymer binder in the Figure 4.1: The schema showing the fabrication process flow of botton- and top- contacted Figure 4.2: The electrical characterisations of the vdW contacted ZnO NW FET. (a) transfer Figure 4.3: The electrical characterisations of the top-contacted ZnO NW FET. (a) transfer Figure 4.4: The schema showing the concept of bottom-, top- and edge- contacted GFETs. Copyright © American Chemical Society. Reprinted, with permission, from [12]......84 Figure 4.5: The schema showing the fabrication process flow of bottom-contacted GFET on Figure 4.6: The AFM characterisations of the surface of the metal contacts. (a) The metal contacts realised at high temperature and its line profile. (b), (c), (d) and (e), metal contacts realised at low temperature with various ConH. A monolayer graphene has been transferred on top. Copyright © American Chemical Society. Reprinted, with permission, from [12]....86 Figure 4.7: The Raman spectrum of the as-transferred graphene on Si/SiO<sub>2</sub> substrate. Copyright © American Chemical Society. Reprinted, with permission, from [12]......87 Figure 4.8: The Electrical characterisation of the bottom contacted GFETs. (a) The transfer curves obtained at ConH of 1.8 and 80 nm, respectively. (b) and (c) The output curves obtained at ConH of 80 and 1.8 nm, respectively. The ConL is 30 µm for the data shown in this figure. Copyright © American Chemical Society. Reprinted, with permission, from [12].

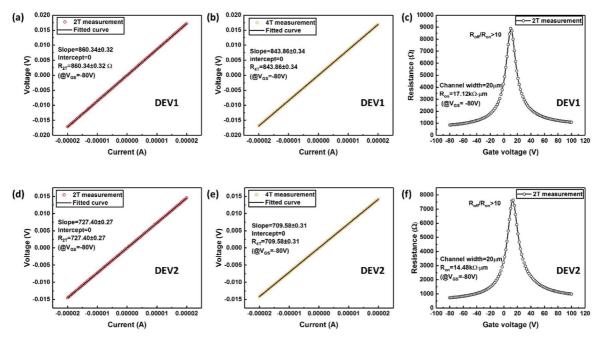

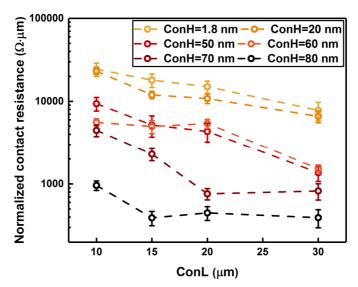

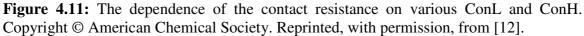

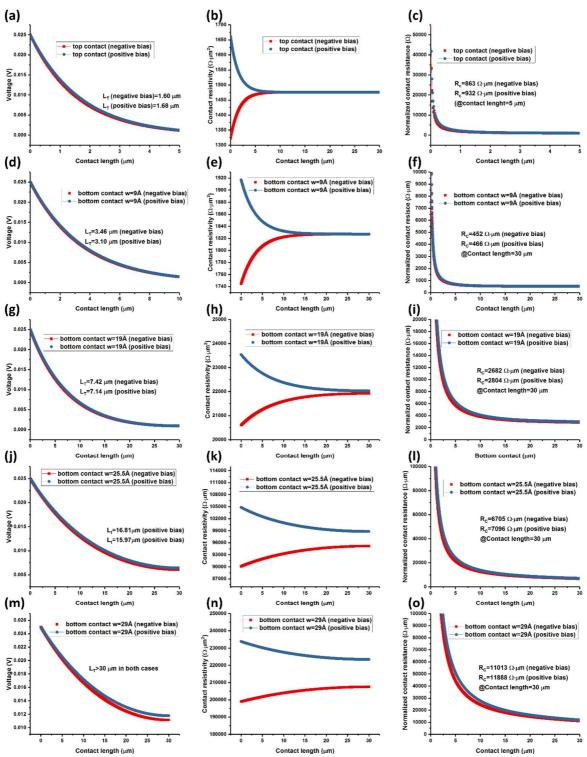

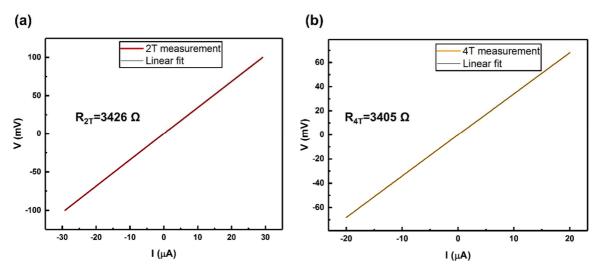

**Figure 4.9:** Bottom-contact GFETs with contact resistance lower than  $100\Omega \cdot \mu m$ . (a), (d) are the output curves from 2T measurements @VGS=-80V; (b), (e) are the output curves from

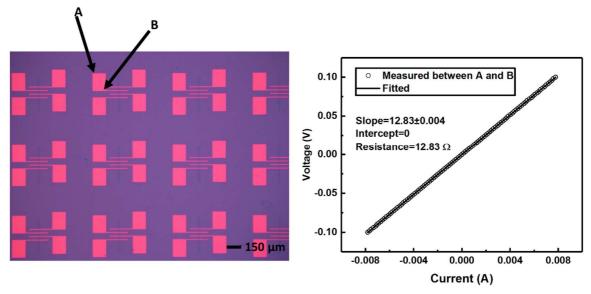

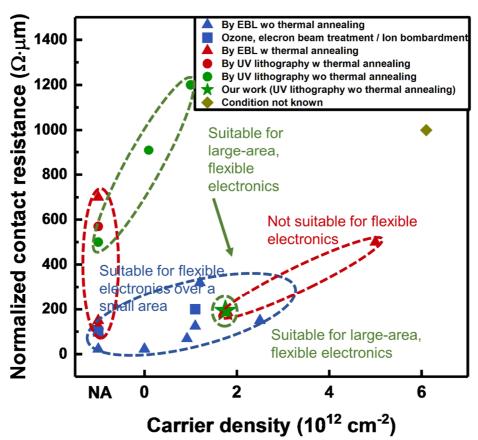

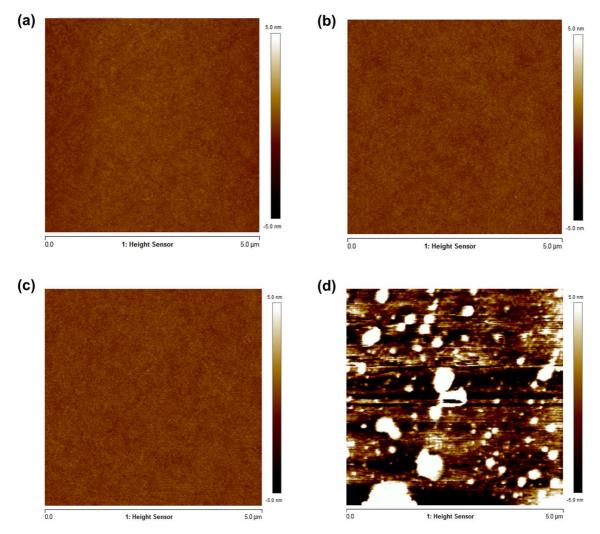

4T measurements @V<sub>GS</sub>=-80V; (c), (f) are the transfer curves from 2T measurements. Figure 4.10: (Left) A schematic of how the lead resistance was estimated by probing point A and point B in the same electrode. (Right) A plot of a voltage-current sweep showing the value of the lead resistance. Copyright © American Chemical Society. Reprinted, with permission, from [12]......90 Figure 4.11: The dependence of the contact resistance on various ConL and ConH. Copyright © American Chemical Society. Reprinted, with permission, from [12]......91 Figure 4.12: The comparison between the contact resistance versus carrier density from various work. Copyright © American Chemical Society. Reprinted, with permission, from Figure 4.13: The comparison between the field-effect mobility extracted by 2T and 4T Figure 4.14: (a) The schema showing the transfer process of graphene/PMMA bilayer onto substrates patterned with metal contacts. (b) and (c) The Raman mapping of 2D peak of graphene transferred onto metal/dielectric interface, with ConH of 1.8 nm and 80 nm, respectively. Copyright © American Chemical Society. Reprinted, with permission, from Figure 4.15: The typical Raman spectrum obtained from the graphene at the edge of the metal contact. Copyright © American Chemical Society. Reprinted, with permission, from Figure 4.16: The relationship between the fermi level shift of graphene and the graphenemetal separation d. Copyright © American Chemical Society. Reprinted, with permission, Figure 4.17: The fermi level of graphene under various graphene-Au separation and its influence on the current density. (a), (b) and (c) The schema showing the influence of graphene-metal separation d to the change of the fermi level of graphene. (d) The calculated unit area current under various graphene-Au separations. Copyright © American Chemical Figure 4.18: The illustration of the resistor network model. (a) The schema showing the graphene-metal bottom contact. (b) The schema showing the resistor network model for the graphene-metal bottom contact. Copyright © American Chemical Society. Reprinted, with Figure 4.19: The calculated contact parameter under various vdW gap. The voltage drop (a), contact resistivity (b) and normalised contact resistance (c) under various contact length. (d) The comparison between the calculation and the experimental data in terms of contact resistance. Copyright © American Chemical Society. Reprinted, with permission, from [12]. Figure 4.20: Comparisons of voltage drop, contact resistivity and width normalised contact resistance calculated at positive and negative bias. (a)-(c) show the scenario of a topcontacted GFET. (d) to (f), (g) to (i), (j) to (l) and (m) to (o) show the situations of a bottomcontacted GFET with vdW gap of 9, 19, 25.5 and 29 Å, respectively. Copyright © American Figure 5.1: The comparison of the surface roughness between spin-coated PI and commercial PI film. (a) PI2545 spin-coated at 2000 rpm for 1min with Primer, Ra~0.18 nm. (b) PI2545 spin-coated at 2000 rpm for 1min without Primer, Ra~0.22 nm. (c) PI2545 spincoated at 2000 rpm, 1 min for twice without Primer, Ra~0.23 nm. (d) A commercial PI film (Kapton film), Ra~1.5 nm. Copyright © 2019 IEEE. Reprinted, with permission, from [159]. 109

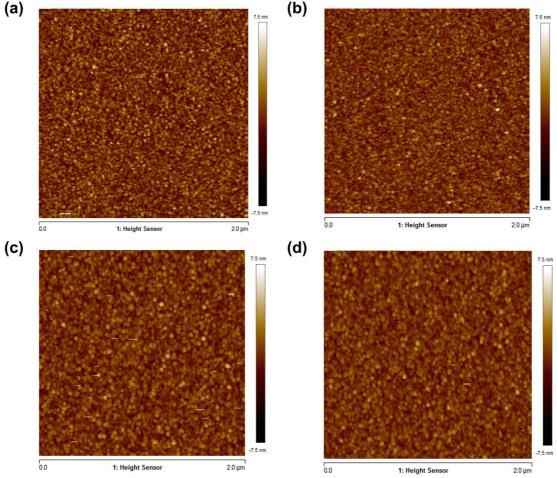

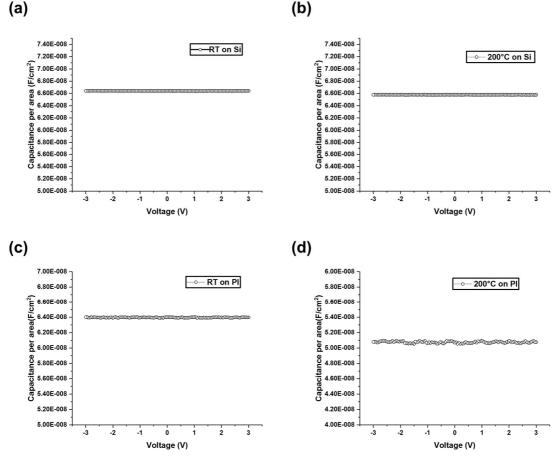

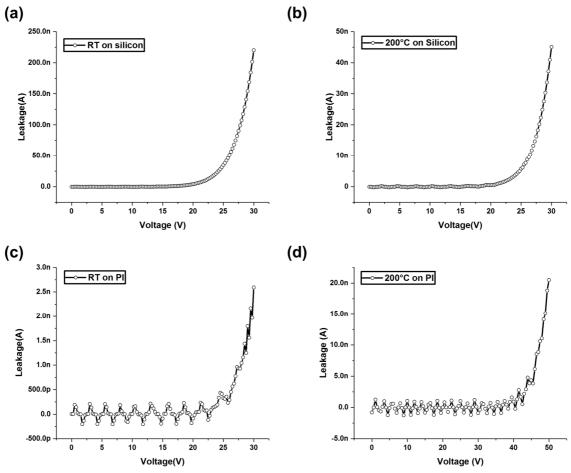

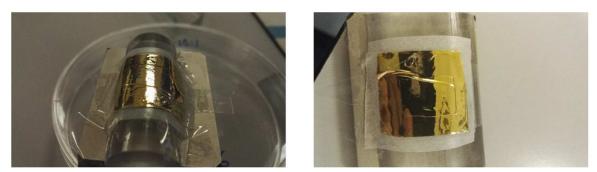

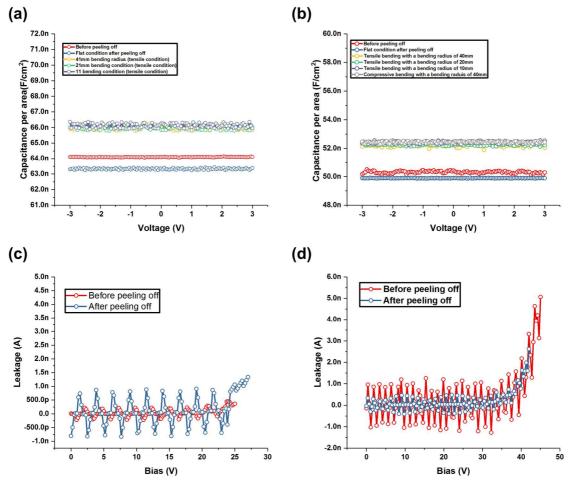

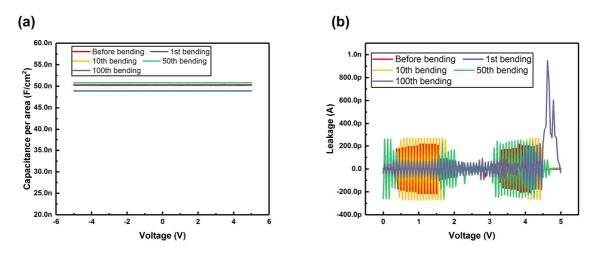

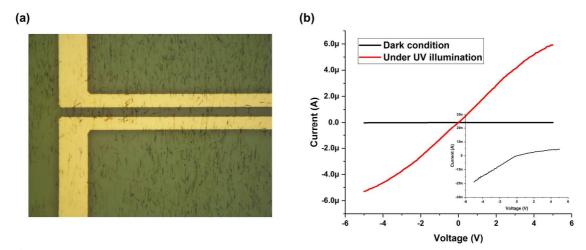

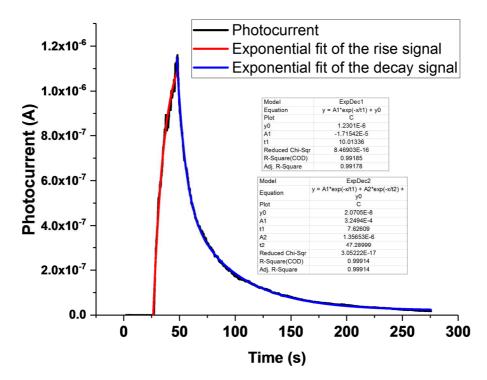

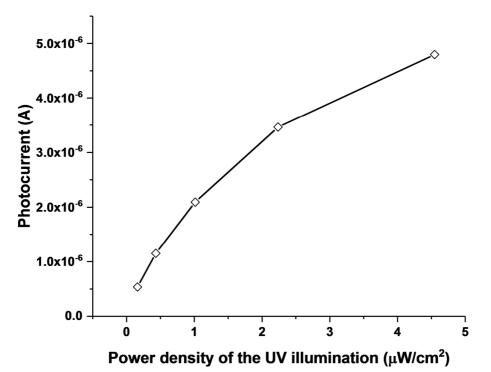

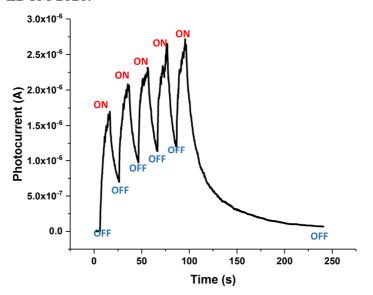

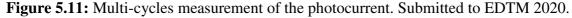

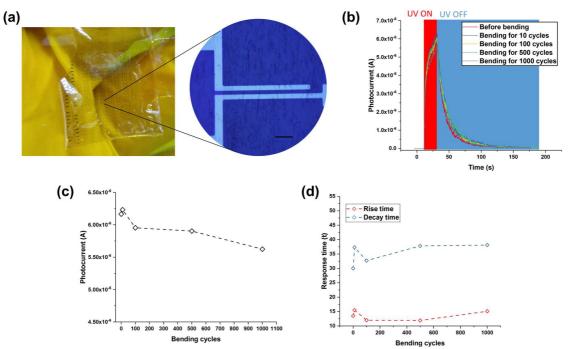

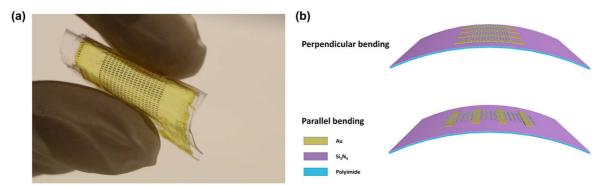

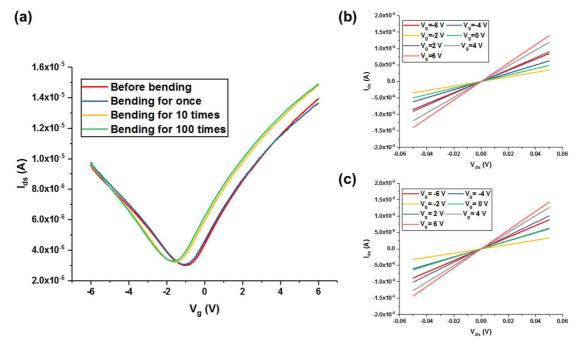

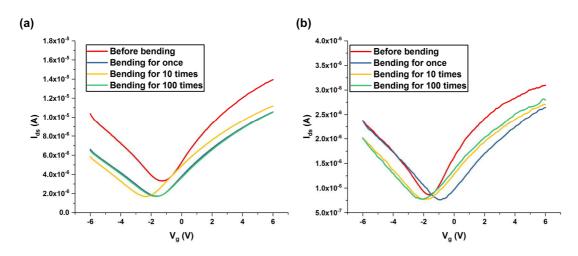

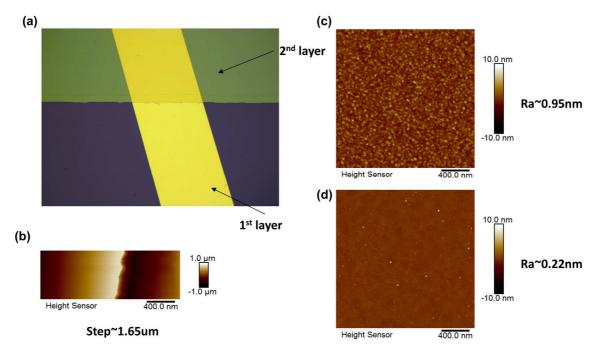

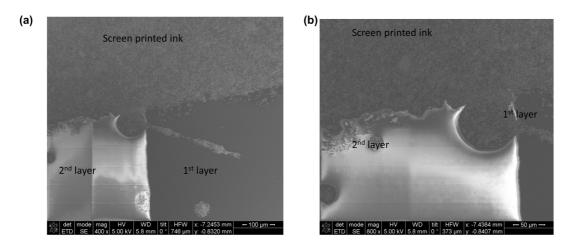

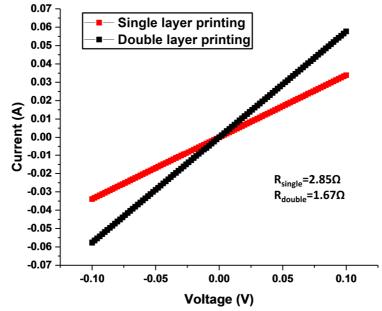

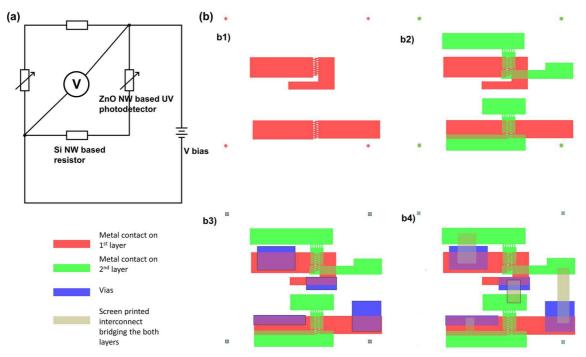

Figure 5.2: AFM characterisations of a 100 nm Si<sub>3</sub>N<sub>4</sub> deposited at (a) room temperature on silicon substrate, R<sub>a</sub> ~0.92 nm (b) 200 °C on silicon substrate, R<sub>a</sub> ~0.76 nm (c) room Figure 5.3: The CV characterisation of the  $Si_3N_4$  based capacitors. (a) The film was deposited at room temperature on silicon substrate (b) The film was deposited at 200 °C on silicon substrate (c) The film was deposited at room temperature on PI (d) The film was Figure 5.4: The leakage current of the Si<sub>3</sub>N<sub>4</sub> based capacitors. The film was deposited at (a) room temperature on silicon substrate (b) 200 °C on silicon substrate (c) room temperature on Figure 5.5: The photograph showing the test of flexible capacitors on a specific bending Figure 5.6: The CV and IV measurements under various conditions. (a) and (c): The CV and IV measurement of capacitor based on 100 nm Si<sub>3</sub>N<sub>4</sub> deposited at room temperature. (b) and (d): The CV and IV measurement of capacitors based on ~123 nm Si<sub>3</sub>N<sub>4</sub> deposited at 200  $^{\circ}$ C. Figure 5.7: Cyclic bending test of the flexible capacitor with a bending radius of 40 mm. (a) Figure 5.8: The printed ZnO NW UV photodetector. (a) The optical microscopy image of the flexible ZnO NW based UV photodetector on PI film. (b) The I-V characteristics of the device under dark condition and UV illumination (Inset: the enlarged plot of the dark current). The power density of the UV light is ~1 µW/cm<sup>2</sup>. Submitted to EDTM 2020......114 Figure 5.9: The time resolved measurement showing the rise and decay of the photocurrent. The power density of the UV light is ~0.43  $\mu$ W/cm<sup>2</sup>. Submitted to EDTM 2020. .....116 Figure 5.10: The relationship between the photocurrent and the power of the UV LED.....117 Figure 5.11: Multi-cycles measurement of the photocurrent. Submitted to EDTM 2020....117 Figure 5.12: The characterisations of the flexible UV photodetector. (a) The photograph and optical microscopy images of the flexible UV photodetectors based on printed ZnO NWs. (b) The relationship between the photocurrent and time. (c) and (d) The photocurrent, rise time and decay time under various bending cycles. The power density of the UV light is ~0.3 Figure 5.13: The photo and illustration of the graphene-Au vdW contact on flexible substrate. (a) The photograph of the graphene-Au vdW contact on PI substrate (b) The schema showing the definition of the perpendicular and parallel bending. Copyright © American Chemical Society. Reprinted, with permission, from [12]......119 Figure 5.14: The contact resistance under various bending conditions. The 2T and 4T output characteristics measured under high (|~80 nm, a) and low (~2 nm, b) ConH. The contact resistance extracted under various bending status under high (b) and low (e) ConH. The cyclic test of contact resistance under high (c) and low (f) ConH. Notably, the data in (b) and (c) are taken from different devices with the same ConH. The ConL is 30µm for all the cases. Copyright © American Chemical Society. Reprinted, with permission, from [12]. .....120 Figure 5.15: The 2T and 4T output characteristics measured under high ConH of ~80 nm at condition A. Copyright © American Chemical Society. Reprinted, with permission, from Figure 5.16: The electrical characterisation of flexible GFET. (a) The transfer curves measured at various conditions.  $V_{ds}$ =50 mV. (b) and (c) The output characteristics of the flexible GFETs before and after 100 cycles of bending at a bending radius of 40 mm. ......123 Figure 5.17: The change of transfer curves under various cycles of bending for another two

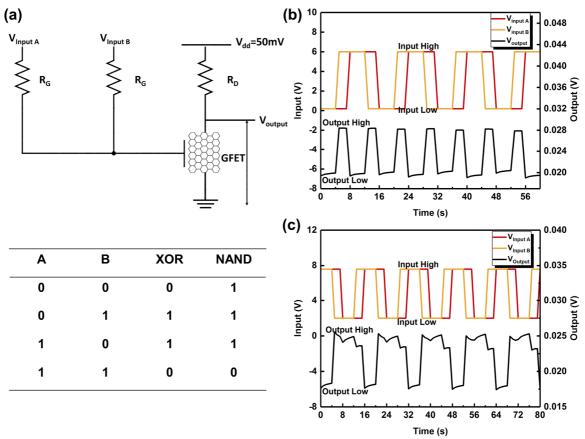

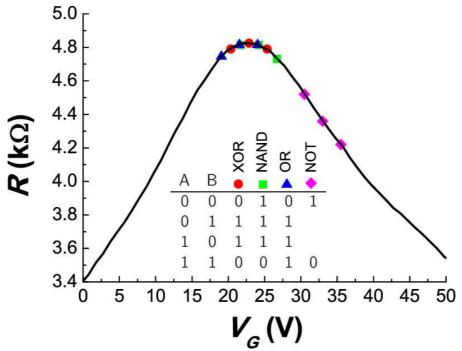

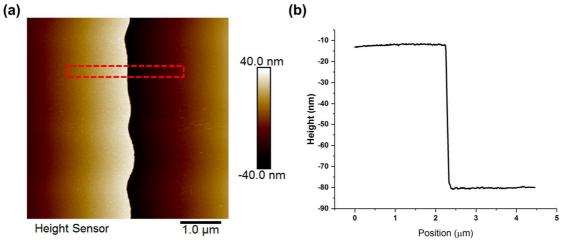

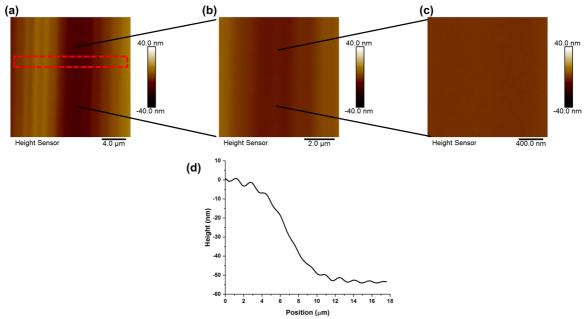

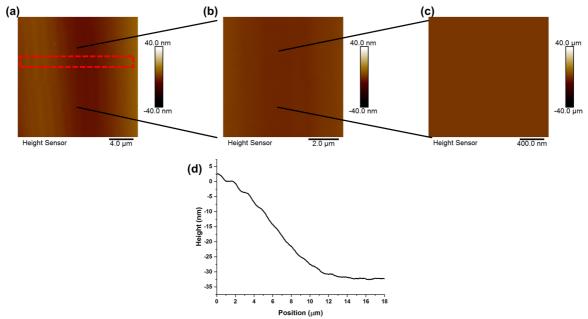

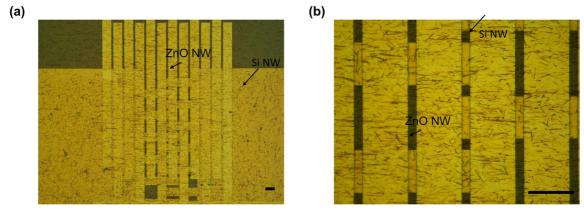

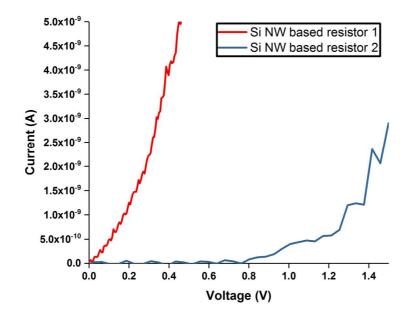

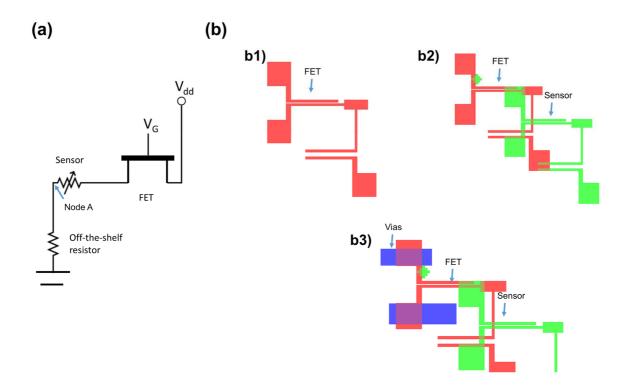

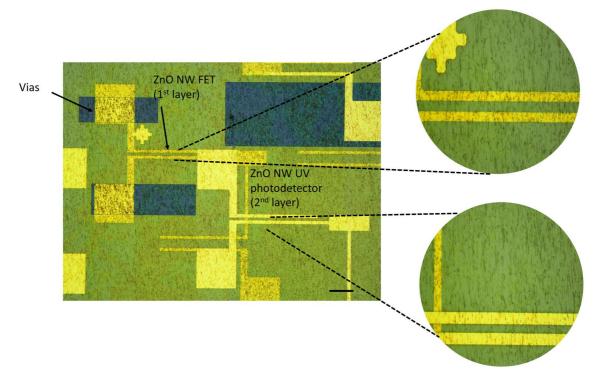

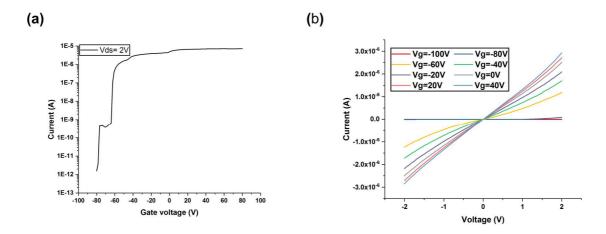

Figure 5.18: The electrical characterisation of flexible logic circuits. (a) The logic diagram and the truth table for the graphene based logic circuits. (b) and (c) The electrical characterisation of the XOR and NAND gate, respectively after 100 cycles of bending. Copyright © 2019 IEEE. Reprinted, with permission, from [173]......125 Figure 5.19: The figure illustrating the choice of the input voltage with respect to the Dirac point for various types of circuit. Inset: the truth table for various circuit. This figure is reused Figure 6.1: The characterisation of a step feature (a) The AFM scan (b) The line profile...128 Figure 6.2: The characterisation of the step feature after flattening. (a), (b) and (c) The AFM characterisations of the metal film after spin-coated with PI solution at 4000 rpm for twice. Figure 6.3: The characterisation of the step feature after flattening. (a), (b) and (c) The AFM characterisations of the metal film after spin-coated with PI solution at 4000 rpm for four times. (d) The line profile of the structure. Figure 6.4: The optical microscope images of the fully cured PI films after a dry etching. The film was spin-coated at 4000 rpm for 60s for once (a) and twice (b), respectively......130 Figure 6.5: The optical microscope images of the soft-cured PI film after a wet etching process. The PI film was soft cured at 140 °C for (a) 2.5 mins and (b) 5 mins, respectively. Figure 6.7: The optical microscope images of the as-fabricated 3D integrated devices. The scale bar in (a) and (b) are, 50 µm and 5 µm, respectively. Copyright © 2019 IEEE. Figure 6.8: The via opening process.(a) The optical microscope image showing the interface between 1<sup>st</sup> and 2<sup>nd</sup> layers. (b) The AFM characterisation of the step height between 1<sup>st</sup> and 2<sup>nd</sup> layers. (c) and (d) The AFM characterisation of the surface from 2<sup>nd</sup> and 1<sup>st</sup> layers......133 Figure 6.9: SEM characterisation of the screen printed Ag ink at the interface from the 1<sup>st</sup> Figure 6.11: The circuit diagram and layout of a 3D integrated Wheatstone bridge. (a) The circuit diagram of the Wheatstone bridge. (b) The layout for the 3D integrated Wheatstone bridge. b1) The mask for metal contacts on the first layer; b2) The mask for metal contacts on the first and second layer; b3) The mask showing the via opening process after the fabrication of both layers; b4) The mask showing the location of the screen printed silver ink, aiming to Figure 6.12: The optical microscopy images showing the as-fabricated 3D integrated Figure 6.15: The circuit diagram and layout of a 3D integrated 1T1S struture. (a) The circuit diagram of the 1T1S structure. (b) The layout for the 3D integrated transistors and sensors. b1) The mask for the source and drain contact for ZnO NW based transistors on the first layer; b2) The mask for the metal contacts for the UV photodetector on the second layer; b3) The mask showing the via opening process after the fabrication of both layers. The mask has Figure 6.16: Optical microscopy image showing the 3D integration of UV photodetectors on Figure 6.17: The electrical characterisations of the printed ZnO NW FET after 3D integration. The ZnO NW FET is on the first layer. (a) The transfer curve (b) The output

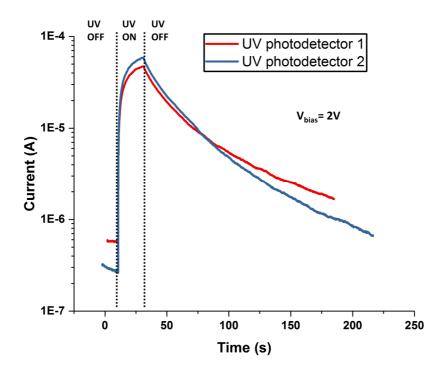

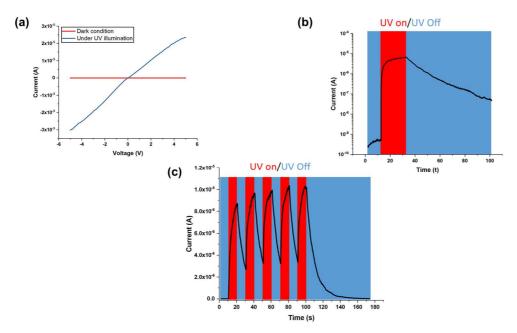

**Figure 6.18:** The UV electrical characterisations of the UV photodetector. (a) The I-t relationship under dark condition and UV illumination. The power density of the UV light used here is ~1  $\mu$ W/cm<sup>2</sup>. (b) The time resolved measurement showing the rise and decay of the current under UV and dark conditions. (c) The cyclic test of the sensor with and without UV illumination. The power density of the UV light used in (b) and (c) are ~0.43  $\mu$ W/cm<sup>2</sup>. 140

### Author's Declaration

I, Fengyuan Liu, hereby declare that except where explicitly reference is made to the contribution of others, this thesis is the result of the work of the named and has not been submitted for any other degree at the University of Glasgow or any other institution.

# Definitions/Abbreviations

1D: one-dimensional 1T1S: one transistor-one sensor 2D: two-dimensional 2T: two-terminal 3D: three-dimensional 3D WLP: 3D wafer-level packaging **3D-SICs: 3D stacked ICs** 3D SIP: 3D system in package 4T: four-terminal AFM: atomic-force microscope ALD: atomic layer deposition CMOS: Complementary-Metal-Oxide-Semiconductor CMP: chemical mechanical polishing CNT: carbon nanotube ConH: contact height ConL: contact length CV: capacitance-voltage CVD: chemical vapour deposition CVT: chemical vapour transport DTBDT-C6: dithieno[2,3-d;2',3'-d']benzo[1,2-b;4,5-b']dithiophene DOS: density of states Ebeam: electron-beam EBL: electron beam lithography FET: field-effect transistor GFET: graphene based field-effect transistor IC: integrated circuit IV: current-voltage LED: light-emitting diode NT: nanotube NW: nanowire OFET: organic field-effect transistor

PCDTBT:PCBM: poly[N-9-heptadecanyl-2,7-carbazole-alt-5,5-(4',7'-di-2-thieny-2',1',3'-

benzothiadiazole)]:[6,6]-phenyl-C71-butyric acid methyl ester

PECVD: plasma enhanced chemical vapour deposition

PEDOT:PSS: poly (3,4-ethylenedioxythiophene) polystyrene sulfonate

PI: polyimide

PMMA: Poly (methyl methacrylate)

P(NDI2OD-T2): poly{[N,N'-bis(2-octyldodecyl)naphthalene-1,4,5,8-bis(dicarboximide)-2,6-

diyl]-alt-5,5'-(2,2'-bithiophene)}

PS: polystyrene

PVP: Poly(4-vinyl-phenol)

PUA: poly (urethaneacrylate)

RIE: reactive ion etching

RTA: rapid thermal annealing

SEM: scanning electron microscope

SOA: State of the art

TRL: transistor resistor logic

TSV: through silicon vias

UV: ultraviolet

h-BN: hexagonal boron nitride

diF-TES-ADT: 2,8-Difluoro-5,11-bis-(triethylsilylethynyl)anthradithiophene. TU-3 denotes

benzobis(thiadiazole) derivative

vdW: van der Waals

### 1. Chapter 1. Introduction

The shrinking of the individual electronic device is expected to approach its physical limits in the very near future. The Moore's law, which provided a development roadmap for IC technology, is likely to lose its magic [1, 2]. In order to further advancing the development of IC technology, various solutions have been proposed including the use of 3D integration: a stack of electronic devices on different layers, unlike current CMOS technology, which arranges all the devices on the same plane, can further increases the device's density without tackling the barriers existing in the device miniaturisation. Another benefit of 3D integration of the devices is that the layout and interconnect of the circuit/system can be greatly simplified [3]. In general, the concept of realising electronics in a 3D manner is appealing and to meet this target various gaps need to be filled.

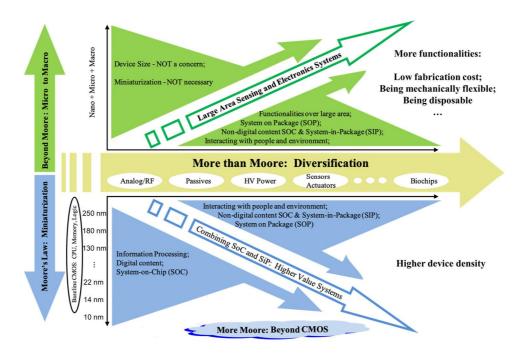

Meanwhile, large-area electronics, including flexible and printable electronics, is an emerging concept, which adopts a new way to make and use electronic devices and circuits [4]. Being flexible and printable, this can have applications in various aspects such as healthcare monitoring, the internet of things, robotics and prosthetics in a cost-effective manner, leading to a profound and revolutionary consequence to the daily life of people in the post-silicon era (see Figure 1.1) [5-8].

**Figure 1.1:** The schema showing the two possible roadmaps of electronics development, which can be classified as "More Moore" and "More than Moore".

While achieving a high device density is not the top priority in large-area electronics, merits still exist in utilizing the 3D integration strategy. For example, interconnects is studied to greatly limit the performance of an electronic system in terms of power consumption and signal delay [9]. And this aspect will become increasingly serious if various electronic systems with multiple functionalities are integrated together. The 3D integration, in the meanwhile, can greatly reduce the wiring length and increase the performance [3, 9]. Therefore, realising electronic components in a 3D manner by printing technology has its benefit and few studies have explored this direction.

This thesis aims to study the printing of various nanomaterials on flexible substrate and to further realising electronic devices and circuits in a 3D manner. Specifically, the objectives of this thesis can be summarised as follows:

- a) To study the printing of nanomaterials including quasi-1D NWs and quasi-2D graphene, on both rigid and flexible substrates.

- b) To realise functional devices and circuits from those printed nanomaterials, on both rigid and flexible substrates.

- c) To realise the 3D stacking of these devices and circuits.

This thesis covers these aspects and is arranged into seven chapters. Meanwhile, during the development of 3D integrated electronics, some other meaningful results, such as the study on contact problem in printed electronics, were also obtained and detailed research into them was carried out. These studies were included in this thesis as well. Here, a brief description of the content of each chapter is given to provide some more detail about this Ph.D. thesis.

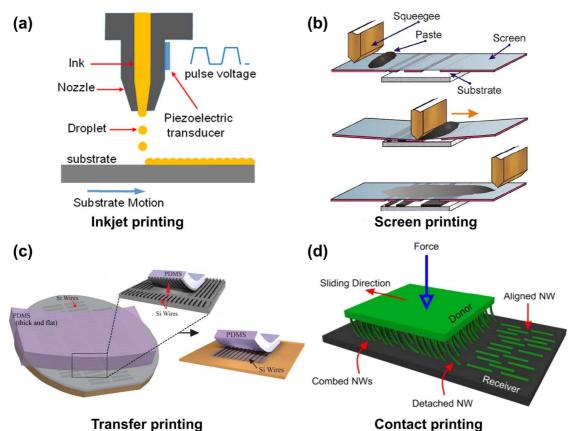

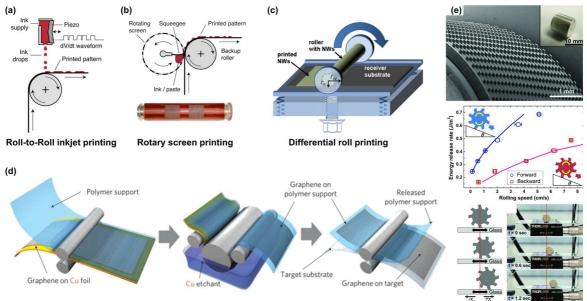

Chapter 2 presents an overview of the state of the art in printed and 3D integrated electronics. For this, various printing techniques are reviewed, including inkjet printing, screen printing, contact printing, transfer printing, and their roll-to-roll equivalents. A comparison between the listed printing techniques are made to highlight their advantages and disadvantages. Afterwards, the advances in 3D integration techniques are summarised, including a brief overview of 3D integration of chips and ultra-thin chips (parallel integration) and recently developed 3D printed devices and circuits (mainly sequential integration). A comparison between the listed works on 3D integrated electronics is made to highlight the advantages and disadvantages and disadvantages.

Based on the literature review in Chapter 2, Chapter 3 explores and further advances the printing technology used in this thesis. This chapter is arranged in 3 sections. The first section (3.1) provides an in-depth study of the NW printing process. For this, a home-made contact

printing setup was realised with a close-loop control system, which enables precise control of the printing parameters including the printing pressure, the sliding speed and the sliding distance over the entire process. Afterwards, a data analysing method, which could extract the important figure of merits from the SEM images of printed NWs, is described and verified. This was achieved by slightly modifying a software (GTFiber) proposed in a previous work on organic fibres [10]. With these prerequisites, the NW printing mechanism is studied, clarifying the NW printing mechanism on flexible and uneven substrates. Section 3.2 presents a brief process flow for graphene transfer. The impact of extrinsic factors, such as solvent cleaning and rapid thermal annealing process is investigated. In Section 3.3, a study on screen printed Ag ink is presented. The influence of the processing parameters has been investigated. The study described in this chapter lays the foundation for later work presented in this thesis, which aims to realise a 3D integrated, flexible electronic system in a printable manner.

Chapter 4 discusses the contact problems in printed electronics. Unlike traditional CMOS technology where the contact is achieved by high temperature annealing and silicide formation, the contact obtained by printing methods are often weakly bonded with a vdW interaction. Such contacts can be achieved at low temperature (<150 °C), which is compatible with flexible substrate, but its contact quality is a major concern. In this regard, this section presents an experimental study of the vdW contact for various materials including graphene and ZnO NW. The experimental results show a completely different contact quality for these two materials: while a low contact resistance can be achieved between graphene and Au, the vdW contact appears to be unreliable for ZnO NWs, showing a Schottky type contact. A qualitative explanation has been proposed for this significant contrast. Next, effort has been made to further understand the graphene-Au vdW contact. Raman characterisation has been performed to reveal the mechanical properties of graphene-Au contact. A model proposed in previous studies have been adopted to determine the change of fermi level of graphene with respect to the change of graphene-Au separation [11]. A direct tunnelling equation has been utilised to calculate the vertical current in a uniformly biased graphene-Au junction. And this was further extended into a FET by combining with a modified resistor network model. The calculated results have been compared with the experimental data. Finally, the limitation of this theory has been indicated and future work following this direction has been discussed.

Chapter 5 discusses the realisation of flexible devices and circuits. This is discussed in various aspects including substrate preparation, contact strategy validation, dielectric material examination, device fabrication and circuit realisation. Specifically, flexible GFETs and ZnO

NW based UV photodetectors have been realised and characterised. The GFET is also used to realise logic circuits, which could potentially lead to flexible circuits over large area.

Chapter 6 discusses the realisation of 3D integrated electronics. For this, technical challenges in realising 3D integration is discussed in Section 6.1. Afterwards, two kinds of layout, which are Wheatstone bridge and 1 transistor-1 sensor (1T1S) structure based on printed NWs, have been discussed and realised in Section 6.2 and 6.3, respectively.

Chapter 7 concludes this thesis and indicated some future work which may be worth pursuing. The key findings in this thesis are summarised as follows:

- a) A systematic study of NW printing mechanism on soft and uneven substrates has been carried out, which provides a preliminary guideline for NW printing on flexible substrates in a 3D manner.

- b) In order to realise the study described in a), a user-friendly, home-made contact printing setup with close-loop control has been built, enabling the controllable and uniform NW printing over large-area.

- c) Regarding the vdW contact between graphene and Au, before the study carried out in this thesis [12], no systematic investigation is available, and its nature is not clearly understood. The mainstream of the research in this field focuses on strategies of top-contact and edge contact. However, these two approaches have their benefits as well as drawbacks and they may not be so suitable for flexible electronics under the limitation of the thermal sensitive flexible substrate. For these reasons, a bottom contact method with a vdW graphene-Au interaction was adopted and systematically studied. An excellent contact performance has been achieved by engineering the graphene-Au vdW contact without the use of harsh thermal annealing. In addition, the vdW contact was realised on flexible substrate and its stability upon mechanical deformation was examined. Because of these benefits, a promising future is revealed to the long underestimated vdW contact.

- d) A 3D integrated electronic system with a stack of transistors and sensors has been realised by using a layer-by-layer printing method.

Considering the key achievements listed here, this Ph. D. thesis may be of interest to a wide range of readers, including the researchers who work on 1D and 2D materials, printed and flexible electronics, etc.

# 2. Chapter 2. The State of the art in printed and 3D integrated electronics

This chapter presents an overview of the current state of the art in printed and 3D integrated electronics. It starts with a review of various mainstream printing techniques from both material and equipment perspectives, covering the electronic devices and circuits realised by inkjet printing, screen printing, contact printing, transfer printing, and their roll-to-roll equivalents. Then, a comparison is made between the listed printing techniques to highlight their advantages and limitations. The mainstream 3D integration technologies are described and reviewed, including parallel integration and sequential integration. Finally, the recent advances in 3D integration realised by printing technologies for large-area, high density, flexible electronics.

### 2.1 Printing technologies

In the film "Minority Report", people are reading newspapers on the subway. It is the year 2054 and the newspapers are not only 'papery', but also electronic: they are composed of a flexible display on the paper substrate and they can be bent, flexed and disposed of after reading. This is one example given by Prof. Zhenan Bao, when answering why and where flexible and disposable electronics are needed [13]. Researchers are currently working towards these aims, in which electronics are not realised on rigid substrates, but on flexible, stretchable, biocompatible and even disposable platforms. The device size and density are not the primary concern for this new form of electronics. Instead those novel properties, such as bendability and disposability, take a greater priority. This innovation requires a change in fabrication technology. It should be cost-effective, realised under a low temperature and also capable of obtaining a high performance for various electronic applications.

One technology which potentially meets those requirements is printing. Unlike conventional micro-fabrication techniques which usually involve a high temperature process, printing can be realised at room temperature. Therefore, printing has been regarded as a promising approach to be used in flexible electronics, where most of the currently used deformable substrates are thermally sensitive. Various types of materials, including conductors, semiconductors and dielectrics, have been demonstrated to be achievable *via* printing [14], which has fostered the possibility of the realisation of all printed devices and circuits (see Subsection 2.1.4). This section aims to provide a general overview of printing technologies and is arranged as follows: first, typical donor materials of various bandgap have been summarised (Subsections 2.1.1 to

2.1.4). Then, several mainstream printing techniques for electronic applications have been reviewed with their advantages and challenges (Subsection 2.1.5). Finally, a comparison is made between the listed printing techniques (Subsection 2.1.5).

#### 2.1.1 Conductors

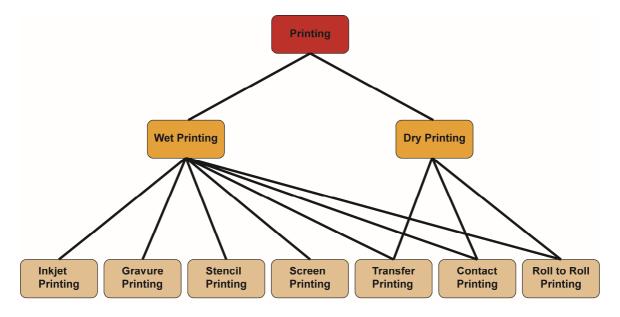

Figure 2.1: The block diagram showing the classification of various printing techniques.

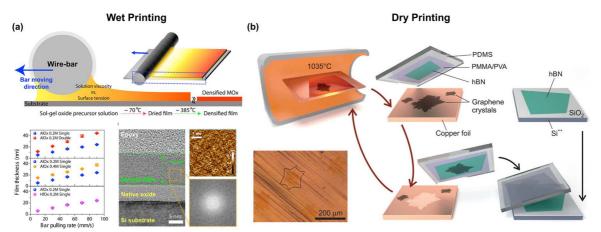

Generally, all printing techniques can be classified into two categories, which are wet printing and dry printing (See Figure 2.1). Wet printing refers to a printing process where liquid is involved, either in the form of "ink" or in the form of transfer medium. Dry printing refers to a process without involving any liquid. Some printing techniques can be classified into both categories, depending on the actual environment of the printing process. For example, transfer printing can be realised in a dry condition, where the contact interface between the donor and receiver does not involve any other materials [15]. It can also be achieved in a wet condition, where a liquid transfer medium is used to modify the interaction between the donor and the receiver [16]. A similar classification can be found in contact printing as well, where mineral oil is optionally used as a lubricant to improve the printing process [17]. Overall, this form of classification depends on specific printing techniques (Figure. 2.1) and detailed discussion can be found in Subsection 2.1.5.

With regard to the conductive film obtained by wet printing, the conductive ink needs to be prepared (see Figure 2.2 for wet printing). Therefore, three main types of ink have been developed and they are a) metal precursor ink, b) conductive polymers and c) carbon based ink

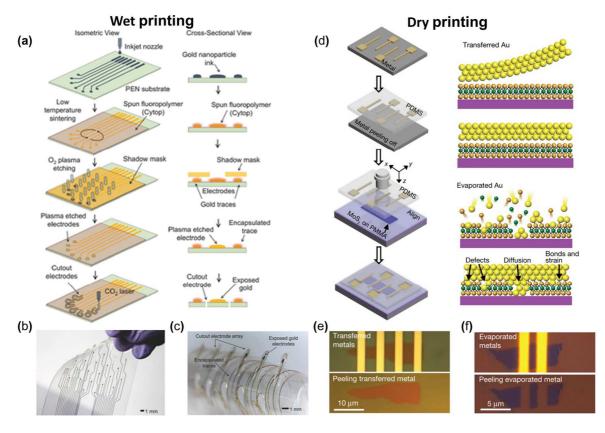

**Figure 2.2:** The schema and examples for wet printed and dry printed contact pads. (a). (b) and (c) The typical schema and example of wet printed contacts. (d) and (e) The typical schema and example of dry printed contacts. (f) The example of metal contacts fabricated by conventional microfabrication process including photolithography and metal deposition on to the active material, leading to a contact with many defects and surface states Reprinted and adapted with permission. (a), (b) and (c) are from Ref [24]. Copyright © John Wiley and Sons. (d), (e) and (f) are from Ref [46]. Copyright © Springer Nature.

[14, 18]. A typical example of the first type is an ink based on metal nanoparticles such as Ag [19, 20], Au [21], Pt [22], and Pd [23]. These varieties provide not only more freedom in controlling the band structure of the metal semi-conductor contact but also more functions for other applications. For example, Au nanoparticles show good bio-compatibilities. In this regard, they are widely used in various bio-medical applications [24] (Figure 2.2 a, b and c). Other considerations involve aspects such as the cost, the mechanical flexibility, the stretchability and the magnetic properties [25]. For various applications, different metal nanoparticles can be used accordingly as the variety of the metal nanoparticle inks facilitates various conductor applications in a printable manner.

Commercial metal nanoparticles based inks are dispersed in suspension. However, one of the biggest problems is the agglomeration between the nanoparticles, since they have large

Hamaker constants that make them strongly attractive to each other [26]. This is addressed by decorating the metal particles' surface with non-conductive ligands, which significantly increases their dispersibility and stability, leading to a long shelf life [27, 28]. Meanwhile, although this is crucial for the ink stability, it leads to a concern in electrical property as most of the ligands are insulating, forming a transport barrier between the metal nanoparticles. Therefore, the thickness of the ligands should be carefully controlled. Practically, a sintering step is adopted to partially remove the ligands after printing. This can be done by a thermal approach, which is the most common method [29]; or by other methods such as chemical sintering [30], electrical sintering [31], laser beam exposure [32] and microwave radiation [33]. In flexible electronics, additional concern is raised because of the use of mechanically flexible but thermally sensitive polymeric substrate. Therefore, the method of sintering should be chosen depending on the proposed use of the specific substrates. Another technical problem in this process is the adhesion between the printed materials and the substrate. This can be addressed by using a polymer-based binder following an increase in the surface energy [34]. Currently, three types of binder have been principally investigated, which are poly(4-vinylphenol) (PVP), poly (methyl methacrylate) (PMMA) and teflon. However, unlike the ligands which are necessary, the polymer binders are only adopted in certain cases as they further complicate the electrical transport because of their insulating nature.

The second type of commonly used conductive ink are conductive polymers such as polyacetylene and poly (3,4-ethylenedioxythiophene) polystyrene sulfonate (PEDOT:PSS). Compared to the metal nanoparticle based inks, the conductive polymers generally have greater flexibility as a result of the smaller Young's modulus from organic materials [35]. However, this would lead to concerns in terms of stability as some inks show vulnerability when exposed to various conditions such as UV light, heat stimuli, moist environment or even ambient conditions [36], and, to this end, suitable encapsulations are often necessary. Since this is not the major focus of this Ph.D. research, details in the recent advances for encapsulation are not included. Relative studies can be found in several previous reviews and books [37, 38].

Carbon based materials such as carbon nanotube (CNT), graphene and their derivatives have also been explored as good candidates for conductor applications. To that end, the preparation of their suspensions is a crucial step towards printing. Typical strategies include oxidation assisted dispersion [39], surfactant assisted dispersion [40] and distillation assisted dispersion [41]. The printed films show a high flexibility and good resistance to external environment, but their conductivity is a concern ( $\sim 10^3$  S/m for carbon based ink and  $\sim 10^7$  S/m for metal nanoparticle ink [18]). Therefore, the carbon based ink is usually used in applications where high conductivity is not required.

While these approaches are all based on a wet printing strategy, researchers have also developed dry printing methods for realising conducting films. This mainly refers to a physical transfer process (transfer printing or stamp printing) where an elastomer polymer is used to pick up and release the pre-fabricated metal films [42-45] (see Figure 2.2 for dry printing). The advantage of this approach is that it enables the merging of the traditional micro-fabrication process with the flexible electronics: the conventional micro-fabrication process which involves the high temperature treatment can be first realised on the rigid substrate and the as-fabricated materials and devices can be then transferred onto the flexible platform.

Unlike the conventional micro-fabrication process which inevitably introduces impurities (as a result of photoresist or solvent residues) and damages (as a result of physical bombardments on the material surface) the interface between donor and receiver, the dry printing method can achieve a pure and intrinsic interface as a result of a van der Waals (vdW) contact (see Figures 2.2 d, e and f) [46]. Recently, interesting results have been realised by exploring the vdW contact between metal film and MoS<sub>2</sub>, leading to the experimental validation of the long hypothesised Schottky-Mott relationship in the system of metal-MoS<sub>2</sub> vdW contact [46]. The vdW contact between metal and 2D material is another important part of this research which focuses on the exploration of graphene-Au vdW contact as realised by the transfer printing method and its applications in large-area flexible electronics. This will be discussed in Chapters 4 and 5.

Finally, a table has been included to compare the properties of the conducting materials printed by different methods.

| Material      | Fabrication method               | Minimum<br>thickness | Conductivit<br>y                         | Special requirement | Ref #       |

|---------------|----------------------------------|----------------------|------------------------------------------|---------------------|-------------|

| Ag ink        | Ink-jet or<br>screen<br>printing | Down to ~ 10<br>nm   | ~10 <sup>6</sup> S/m                     | Sintering required  | [19,20<br>] |

| Au ink        | Inkjet<br>printing               | Down to ~ 10<br>nm   | ~10 <sup>7</sup> S/m                     | Sintering required  | [21]        |

| PEDOT:<br>PSS | Inkjet<br>printing               | Down to ~10 nm       | 10 <sup>-1</sup> ~10 <sup>3</sup><br>S/m | Lack of stability   | [35]        |

Table 2.1: Summary of printed conductive materials.

| Carbon<br>based<br>ink | Inkjet<br>printing | Down to ~10<br>nm | ~10 <sup>3</sup> S/m                    | NA | [18] |

|------------------------|--------------------|-------------------|-----------------------------------------|----|------|

| Metal<br>film          | Transfer printing  | Down to ~1 nm     | 10 <sup>8</sup> ~10 <sup>9</sup><br>S/m | NA | [46] |

#### 2.1.2 Semiconductors

Various semiconducting materials including organic molecules and polymers [47, 48], inorganic nanowires (NWs)/nanotubes (NTs) [17, 49], thin films [50] and quantum dots [51], can be realised by a printing method over a large-area. As discussed earlier, the printing of semiconductors is categorised into dry and wet methods and promising results have been obtained using both approaches.

The mainstream of the wet printing for semiconductor applications include methods such as inkjet printing and screen printing. For this, suitable "inks" or "pastes" containing the desired semiconducting materials, both organic and inorganic, need to be prepared. Unlike the scenario for conductor applications where a binder can be used, the polymer binders are not favoured in preparing semiconducting inks, especially for printing organic films, since it introduces impurities to the device channel and reduces the performance. Instead, crystalline, high quality semiconductor film is regarded as indispensable for realising high carrier mobility of the FET and sustained efforts have been made to realise high crystalline organic film by using printing methods [52]. Although initial results of printed organic FET exhibit a low performance (~0.01 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) with bad crystallinity [53], significant advances have been made in this direction with single crystal up to several hundred micrometres achievable [52] (see Figure 2.3a). This leads to devices with a mean carrier mobility ~16.4 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [54]). Given the abundant material library for organic semiconductors, various functional electronic components with

high-performance can potentially be realised in a cost-effective manner over the large area, both on rigid and flexible substrates.

The wet printing approach can also be used to print inorganic semiconductors such as ZnO NWs, semiconducting CNTs and amorphous indium-gallium-zinc oxide (InGaZnO) nanofilms [55-58] (Figure 2.3 b and c). Often the printed inorganic semiconductor films are composed of randomly stacked inorganic crystals without any alignment preference, leading to complex and uncontrolled carrier transport properties [57, 59, 60]. In contrast, for inorganic semiconductors, because of their high stability and crystallinity, transfer or contact printing are more popular [61-64], since this provides greater freedom in material processing and alignment, and benefits the realisation of high-performance electronics (see Subsections 2.1.5.3 and 2.1.5.4). It should be noted that these two methods can be realised without the use of liquid, thus categorizing

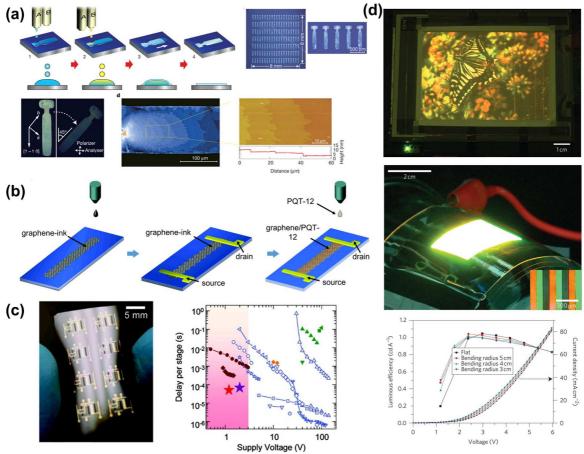

**Figure 2.3:** Typical examples of printed semiconductors. (a) The inkjet printing of single crystal of C8-BTBT layer and its characterisations. The POM image shown on the bottom left indicates its crystallinity. (b) The inkjet printing of graphene based FET. (c) The wet printed CNT circuits with reasonable performance. (d) Printed quantum dots for illuminating application. Reprinted and adapted with permission. (a) and (d) is from Ref [52].and [51], respectively. Copyright © Springer Nature. (b) and (c) are from Ref [98] and [58], respectively Copyright © American Chemical Society.

them as dry printing approaches. Compared to wet printing, dry printing of semiconductors leads to much cleaner interfaces. This is one crucial aspect towards the realisation of high-performance electronics based on nanomaterials, and has been demonstrated in many systems including organic and 2D materials [65-67].

Finally, a table has been included to summarize the properties of the printed semiconductors listed here for various applications.

|                               |                                               |                              | Applicati                    |          |

|-------------------------------|-----------------------------------------------|------------------------------|------------------------------|----------|

| Material                      | Printing                                      | U                            |                              | Ref #    |

|                               | method                                        | quality                      | on                           |          |

| Organic<br>semiconduct<br>ors | Inkjet or<br>screen<br>printing               | Comparab<br>le to the<br>SOA | FETs,<br>solar<br>cells, etc | [52]     |

| Inorganic<br>NWs/NTs          | Inkjet,<br>transfer or<br>contact<br>printing | Comparab<br>le to the<br>SOA | FETs,<br>sensors,<br>etc     | [60]     |

| 2D materials                  | Transfer printing                             | SOA                          | FETs,                        | [61, 67] |

| Quantum<br>dots               | Transfer printing                             | NA                           | LEDs, etc                    | [51]     |

Table 2.2: Summary of printable semiconducting materials.

#### 2.1.3 Dielectrics

Dielectrics are the final building blocks for electronic devices. However, in the development of printable electronics, such as FETs, many of the studies used a Si substrate with SiO<sub>2</sub> layer acting as a gate dielectric by a bottom gate strategy. This strategy avoids the fabrication of the gate terminal thus dramatically decreasing the process difficulties, but it is at the cost of high operation voltage as well as the inability to control the device individually. Therefore, for those circuit applications with an array of FETs, realising locally controlled gate terminals with low film thickness, high dielectric constant and strength, is desired. At present, two major types of materials have shown promising compatibilities with printing technologies and these are a) cross-linked polymer blend dielectrics and b) sol-gel based dielectrics [14]. The first type of materials are organic polymers, with typical examples of polystyrene (PS), and PMMA. Compared to conventional inorganic dielectrics such as SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>, the organic polymers show a better suitability with soft-electronics because of their higher flexibility [68]. Therefore, replacing the brittle insulator to these polymer-based dielectrics would potentially lead to a soft

electronic device with greater flexibility. However, various limitations exist for the organic polymers when compared to standard dielectrics from a conventional micro-fabrication process. To be more specific, one major drawback of polymer based dielectric materials is their low dielectric constant (<10) [69]: this value is usually >20 for those high- $\kappa$  materials. It should lead to a much higher requirement in thickness control, if the same level of areal capacitance is to be achieved. Other problems with the printed organic polymer dielectrics include low film quality with pinholes and uncontrolled film thickness via printing, which can be seen in the pioneering work during the initial stage [70-72]. Promisingly, all these concerns have been largely solved. This is because, thanks to the abundant material library for organic materials, organic polymers with high dielectric constant (>60), low surface roughness (~0.72 nm) and well controlled film thickness have been successfully found and achieved by printing technologies [69].

Meanwhile, inorganic dielectric layers, such as metal oxides, have also shown their printability with a sol-gel method. For example, highly smooth  $AlO_x$  film with low leakage current and high areal capacitance have been demonstrated by printing, with well-controlled thickness down to 10 nm (see Figure 2.4 a) [73]. The performance of the printed metal oxide layers has become comparable to those materials realised by conventional microfabrication technologies such as atomic layer deposition (ALD) and sputter, enabling the realisation of high-performance printed electronics.

**Figure 2.4:** Typical examples of printed dielectrics. (a) The printing of solution based dielectric materials and corresponding characterisations. (b) The stamp printing of hBN for dielectric and encapsulation of GFET. Reprinted and adapted with permission. (a) is from Ref [73]. Copyright © John Wiley and Sons. (b) is from Ref [82]. Open access article.

Apart from these wet printing approaches, dry printing has also been explored for the realisation of dielectrics. This mainly refers to those studies where hexagonal boron nitride (h-BN) is used as the dielectric layer and transferred onto the target location of the receiver substrate by a transfer printing method (Figure 2.4 b). The novelty of these studies is partly because of the material itself, since h-BN has been suggested as an ideal dielectric material with unique advantages of ultralow thickness (~0.33 nm for monolayer), ultra-flat surface, high breakdown voltage (>0.5 V/layer) and a perfect crystal plane without any dangling bonds [74-79]. In this regard, much research has explored the h-BN as a dielectric material in FETs, leading to the realisation of many novel devices with unprecedented performance [78, 80-82].

Despite these advantages, barriers exist in realising an ideal h-BN/semiconductor interface from a technical point of view. This includes the high-quality synthesis of h-BN and its subsequent clean, controllable and reproducible transfer. Specifically, how to achieve a uniform contact interface between the dielectric and semiconductor, by using the transfer printing method, is a critical problem. Although this aspect has seldom been mentioned in related research articles (possibly because of a different focus) [80, 81], the non-uniform vdW gap with bubble formations has been observed in the transfer printing process, and reported in other research from different groups [79, 83, 84]. In this regard, how to achieve a high-quality contact interface over large-area between h-BN and various semiconductors is a problem yet to be solved for near future printed electronics.

Finally, Table 2.3 directly compares all the dielectric materials mentioned in this section.

| Material              | Fabricatio<br>n method | Minimum<br>thickness | Dielectric constant | Dielectric strength        | Surface roughness                      | Young's<br>Modulus                       | Ref #       |

|-----------------------|------------------------|----------------------|---------------------|----------------------------|----------------------------------------|------------------------------------------|-------------|

| SiO <sub>2</sub>      | Thermally grown        | Down to 1<br>nm      | 3.9                 | 10 <sup>7</sup> V/cm       | $R_a \sim 0.2$ nm                      | 6.6×10 <sup>10</sup><br>N/m <sup>2</sup> | [85]        |

| BaTiO <sub>3</sub>    | Inkjet<br>printed      | NA                   | NA                  | NA                         | Particle<br>size of<br>100 ~ 200<br>nm | NA                                       | [71]        |

| Benzocy-<br>clobutene | Spin-<br>coated        | Down to 10 nm        | NA                  | >3×10 <sup>6</sup><br>V/cm | NA                                     | NA                                       | [72]        |

| PMMA                  | Spin-<br>coated        | Down to 100 nm       | 2.89~3.66           | >2×10 <sup>6</sup><br>V/cm | $R_a \sim 0.3$ nm                      | 1×10 <sup>9</sup><br>N/m <sup>2</sup>    | [86,<br>87] |

Table 2.3: Dielectric properties of various materials.

| AlO <sub>x</sub>    | Bar<br>pulling               | Down to 10 nm   | NA                                                           | >2×10 <sup>6</sup><br>V/cm                                  | $R_{RMS} \sim 0.08 \text{ nm}$ | NA                                        | [73]            |

|---------------------|------------------------------|-----------------|--------------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-------------------------------------------|-----------------|

| P(VDF-<br>TrFE-CFE) | spin-<br>coated              | ~160 nm         | >60                                                          | >2.5×10 <sup>6</sup><br>V/cm                                | R <sub>RMS</sub><br>~0.72 nm   | NA                                        | [69]            |

| h-BN                | Mechanic<br>al<br>exfoliated | Down to ~0.3 nm | 3.38 or<br>6.61<br>depending<br>on the<br>field<br>direction | $\sim 10^6$ or $10^7$ V/cm depending on the field direction | R <sub>a</sub> < 0.1<br>nm     | ~8.6×10 <sup>11</sup><br>N/m <sup>2</sup> | [76,<br>88, 89] |

#### 2.1.4 All printed electronics

In Subsections 2.1.1 to 2.1.3, the printing of materials with various bandgaps has been summarised and some of the preliminary device applications have been demonstrated. However, the examples listed above are only "partially printed": the devices are realised by combining the printing techniques with the standard microfabrication processes. One may wonder with the advances in printing technology described above, if it is possible to achieve an "all printed" device. This subsection explores this direction by reviewing the state of the art in various "all printed device", including solar cells, sensors, memories and FETs. Surprisingly, some of these prototype devices have shown a comparable performance to those state-of-the-art non-printed devices, which shows the great potential held by printing technology for the development of near future large-area electronics.

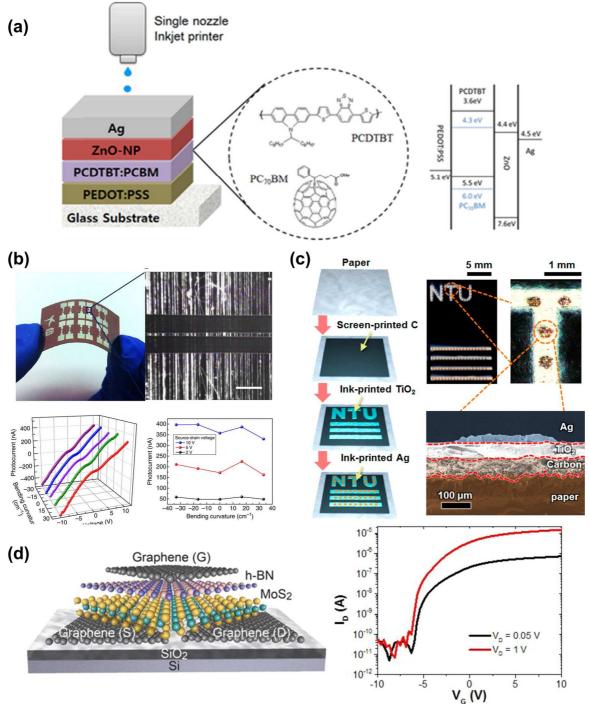

#### All printed solar cells

As previously highlighted, an inkjet printer is able to print various types of materials in a "drop on demand" manner. With suitable inks (semiconductors and conductors), a solar cell can be successfully realised in ambient condition by printing technology [90]. The printed device shows reasonable power conversion efficiency, with an average value of 2%. This is partially limited by the top contact (Ag electrode, as shown in Figure 2.5a), since the replacement of the printed Ag film by vacuum evaporated contacts would lead to a dramatic increase of the efficiency to 5%. Further study also indicates that the inkjet printed poly[N-9-heptadecanyl-2,7-carbazole-alt-5,5-(4′,7′-di-2-thieny-2′,1′,3′-benzothiadiazole)]:[6,6]-phenyl-C71-butyric acid methyl ester (PCDTBT:PCBM) layer shows similar behaviour to the spin-coated film, which has revealed the potential of the printing technologies in energy harvesting applications.

#### All printed sensors

A ZnO NW based UV photodetector is demonstrated by an inkjet printing method [91] (see Figure 2.5 b). ZnO is a wide-bandgap semiconductor and its allotropes, such as NWs and thin films, have been widely used for various sensing applications including UV detection [92, 93]. Unlike conventional NW based UV photodetectors where the channel is based on a single crystal material, this work adopted a thermal calcination method where the ZnO NW is converted from the printed zinc acetate (ZnAc) film and leads to a polycrystalline ZnO NW. Notably, such a change appears to reversely benefit the photodetector performance with a much lower dark current and ultra-high detectivity up to  $3.3 \times 10^{17}$  Jones. This enhancement is attributed to the band-edge modulation because of the existence of the grain boundaries. This study suggests that, although the printed film would be of low quality in the materials perspective (polycrystalline vs monocrystalline), such properties may reversely benefit the intended application and lead to a higher performance by the device.

#### All printed memory devices

Memristor is a device whose state (resistance) is dependent on its operational history of electrical stimuli. Because of its high endurance [94], high on/off ratio [95], long retention time [94, 96] and great potential for scaling down, memristor has been suggested as a promising candidate for next generation data storage device. Memristor usually has a metal-insulator-metal configuration, and is made by mature microfabrication techniques such as lithography, metal deposition, ALD and sputtering. With the development of printing technologies, there is a strong interest in developing electronics by printing method. For example, Lien *et al.* realised a C/TiO2/Ag based memory cell by using all printing methods (screen printing and inkjet printing, see Figure 2.5 c) [97]. The performance of the as-realised cell is still in its initial stage, with an endurance of ~100. However, the benefit of this method is in large scale processing on an arbitrary substrate, for example on a paper substrate which can be disposed after usage. This study, although quite preliminary, can encourage advances in future disposable electronics.

#### **All printed FETs**