Vilouras, Anastasios (2021) Ultra-thin and flexible CMOS technology: ISFETbased microsystem for biomedical applications. PhD thesis.

http://theses.gla.ac.uk/82122/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses <u>https://theses.gla.ac.uk/</u> research-enlighten@glasgow.ac.uk

# Ultra-thin CMOS Technology: ISFET-Based Sensing Microsystem for Wearable and Implantable Biomedical Applications

Anastasios Vilouras

A thesis submitted to the

Department of Electronics and Electrical Engineering

at the University of Glasgow

in fulfilment of the requirements for the

Degree of Doctor of Philosophy

December 2020

### Abstract

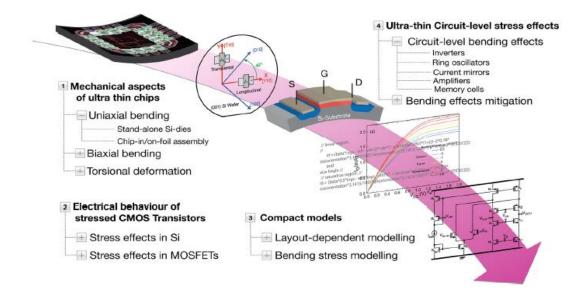

A new paradigm of silicon technology is the ultra-thin chip (UTC) technology and the emerging applications. Very thin integrated circuits (ICs) with through-silicon vias (TSVs) will allow the stacking and interconnection of multiple dies in a compact format allowing a migration towards three-dimensional ICs (3D-ICs). Also, extremely thin and therefore mechanically bendable silicon chips in conjunction with the emerging thin-film and organic semiconductor technologies will enhance the performance and functionality of large-area flexible electronic systems. However, UTC technology requires special attention related to the circuit design, fabrication, dicing and handling of ultra-thin chips as they have different physical properties compared to their bulky counterparts. Also, transistors and other active devices on UTCs experiencing variable bending stresses will suffer from the piezoresistive effect of silicon substrate which results in a shift of their operating point and therefore, an additional aspect should be considered during circuit design.

This thesis tries to address some of these challenges related to UTC technology by focusing initially on modelling of transistors on mechanically bendable Si-UTCs. The developed behavioural models are a combination of mathematical equations and extracted parameters from BSIM4 and BSIM6 modified by a set of equations describing the bending-induced stresses on silicon. The transistor models are written in Verilog-A and compiled in Cadence Virtuoso environment where they were simulated at different bending conditions.

To complement this, the verification of these models through experimental results is also presented. Two chips were designed using a 180 nm CMOS technology. The first chip includes nMOS and pMOS transistors with fixed channel width and two different channel lengths and two different channel orientations (0° and 90°) with respect to the wafer crystal orientation. The second chip includes inverter logic gates with different transistor sizes and orientations, as in the previous chip. Both chips were thinned down to ~20µm using dicing-before-grinding (DBG) prior to electrical characterisation at different bending conditions.

Furthermore, this thesis presents the first reported fully integrated CMOS-based ISFET microsystem on UTC technology. The design of the integrated CMOS-based ISFET chip with 512 integrated on-chip ISFET sensors along with their read-out and digitisation scheme is presented. The integrated circuits (ICs) are thinned down to  $\sim 30\mu$ m and the bulky as well as thinned ICs are electrically and electrochemically characterised. Also, the thesis presents the first reported mechanically bendable CMOS-based ISFET device demonstrating that mechanical deformation of the die can result in drift compensation through the exploitation of the piezoresistive nature of silicon. Finally, this thesis presents the studies towards the development of on-chip reference electrodes and biodegradable and ultra-thin biosensors for the detection of neurotransmitters such as dopamine and serotonin.

## Table of Contents

| Abstracti       |                                                                                                        |  |

|-----------------|--------------------------------------------------------------------------------------------------------|--|

| List of Tablesv |                                                                                                        |  |

| List of F       | iguresvi                                                                                               |  |

| List of P       | ublicationsxv                                                                                          |  |

| Acknowl         | edgementsxvii                                                                                          |  |

| Author's        | Declarationxviii                                                                                       |  |

| Glossary        | of Abbreviationsxix                                                                                    |  |

| Chapter         | 1. Introduction1                                                                                       |  |

| 1.1             | Motivation1                                                                                            |  |

| 1.2             | Research Objectives5                                                                                   |  |

| 1.3             | Research Contributions5                                                                                |  |

| 1.4             | Thesis organisation7                                                                                   |  |

| Chapter         | 2. Literature Review 10                                                                                |  |

| 2.1             | Introduction 10                                                                                        |  |

| 2.2             | Potentiometric Electrochemical Ion-Sensitive Electrodes 12                                             |  |

|                 | 1 Overview of Potentiometric Metal-Oxide Based Electrochemical pH Sensors<br>13                        |  |

| 2.2.            | 2 Sensing Mechanisms                                                                                   |  |

| 2.2.            | 3 Properties and Non-Ideal Characteristics of Potentiometric pH Sensors 19                             |  |

| 2.2.            | 4 Mechanically Flexible Potentiometric Ion-Sensitive Electrodes                                        |  |

| 2.3<br>On-Ch    | Ion-Sensitive Field-Effect Transistor: Operation, Sensor Interface and ip Signal Processing Techniques |  |

| 2.3.            | 1 Operation and Theory of pH Sensitivity                                                               |  |

| 2.3.            | 2 ISFET Read-Out Topologies                                                                            |  |

|                 | 3 Circuit-Level and Post-Processing Techniques for Mitigation of ISFET Non-                            |  |

| ldea            | al Effects                                                                                             |  |

| 2.4             | Ion-Sensitive Field-Effect Transistor: Applications and Advances                                       |  |

|                 | 1 Applications of ISFET-Based Sensing Systems                                                          |  |

|                 | 2 Mechanically Flexible ISFET-Based Sensors towards Wearable Healthcare<br>ices40                      |  |

| 2.5             | Summary 44                                                                                             |  |

| -               | 3. Modelling, Simulations and Validation of Mechanically Bendable<br>ed CMOS Devices                   |  |

| 3.1 In          | troduction                                                                                             |  |

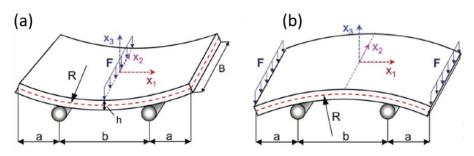

| 3.2             | Mechanical Characterisation of Ultra-Thin Silicon Chips                                                |  |

| 3.3             | Strain Effects: From Silicon Substrate to Integrated Devices and Circuits 50                           |  |

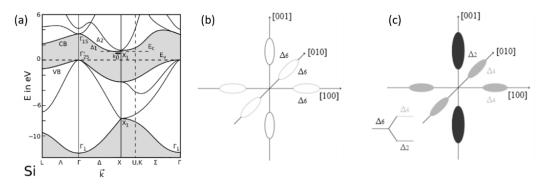

| 3.3.            | 1 Strain Effects on Bulk Silicon                                                                       |  |

|                 | ii                                                                                                     |  |

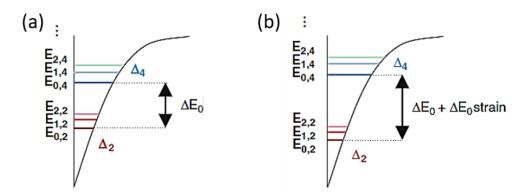

|      | 3.3.2 Strain Effects on MOSFETs and Ion-Sensitive Field-Effect Transistors 53                             | 3 |

|------|-----------------------------------------------------------------------------------------------------------|---|

|      | 3.3.3 Strain Effects on Basic CMOS Circuit Blocks58                                                       | 3 |

|      | 4 Compact Modelling of CMOS-Based Devices and Sensors on Bendable<br>tra-Thin Chips                       | 2 |

|      | 3.4.1 Modelling of Bending Stress Effect on Metal Oxide Semiconductor Field-<br>Effect Transistors        | 2 |

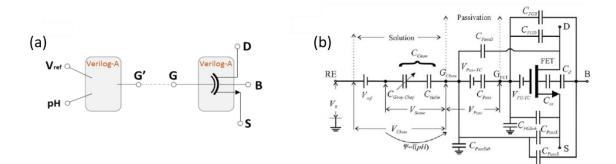

|      | 3.4.2 Modelling of Bending Stress Effect on Ion-Sensitive Field-Effect Transistors                        |   |

|      | 5 Electrical Characterisation and Model Evaluation of Transistors, Circuits and nsors on Ultra-Thin Chips | 4 |

|      | 3.5.1 Experimental Evaluation of MOSFET Model on Ultra-Thin Chips                                         | 5 |

|      | 3.5.2 Experimental Evaluation of ISFET Model on Ultra-Thin Chips                                          | Э |

| 3.   | 5 Summary                                                                                                 | 5 |

|      | ter 4. Fabrication and Characterisation of Thick-Film Reference Electrodes and<br>Flexible Biosensors     | 7 |

| 4.   | 1 Introduction                                                                                            | 7 |

| 4.   | 2 Screen Printed Thick Film Reference Electrode for Electrochemical Sensing<br>87                         |   |

|      | 4.2.1 Fabrication of Reference Electrode                                                                  | 3 |

|      | 4.2.2 Fabrication of $RuO_2$ Based Ion-Sensitive Electrode                                                | C |

|      | 4.2.3 Electrochemical Characterisation, Results and Discussion                                            | 1 |

| 4.   | Chitosan - Graphene Oxide Based Ultra-Thin and Biodegradable Biosensors97                                 | 7 |

|      | 4.3.1 Chitosan-Graphene Oxide-based ultra-thin conformable sensing patch for cell-health monitoring       | 3 |

|      | 4.3.2 Mesoporous Chitosan Based Conformable and Resorbable Biostrip for<br>Dopamine Detection             | 2 |

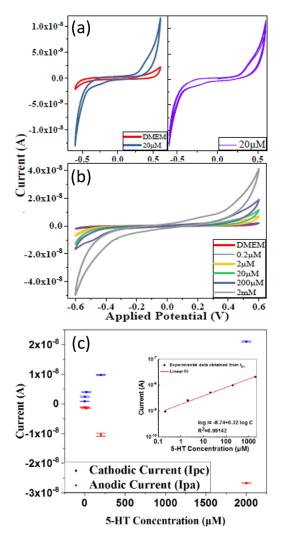

|      | 4.3.3 Graphene Oxide-Chitosan Based Ultra-Flexible Electrochemical Sensor for Detection of Serotonin      | 1 |

| 4.   | 4 Summary                                                                                                 | 5 |

| Chap | ter 5. ISFET Readout IC System Architecture118                                                            | 3 |

| 5.   | 1 Introduction                                                                                            | 3 |

| 5.2  | 2 System Design                                                                                           | 3 |

| 5.   | 3 System Requirements 119                                                                                 | Э |

| 5.4  | 4 Chip Architecture                                                                                       | C |

|      | 5.4.1 Standard Pixel Readout Topology 12:                                                                 | 1 |

|      | 5.4.2 Standard Pixel Readout Topology with Improved Fill-Factor                                           | 5 |

|      | 5.4.3 Current-Mode Pixel Readout Topology129                                                              | Э |

|      | 5.4.4 Pixel Selection                                                                                     | 2 |

|      | 5.4.5 Unity Gain Amplifier                                                                                | 1 |

| 5.   | 5 Summary                                                                                                 | 5 |

|      |                                                                                                           |   |

| Chapter 6. Post-Processed Ultra-Thin CMOS Chips 139                         |     |  |

|-----------------------------------------------------------------------------|-----|--|

| 6.1 Introduction                                                            | 139 |  |

| 6.2 Protection of Front Active Side during Back-Etching                     | 140 |  |

| 6.3 Fabrication of Ultra-Thin CMOS Chips                                    | 142 |  |

| 6.3.1 Chemical Wet Etching using PDMS as Protective Layer                   | 142 |  |

| 6.3.2 Back-Lapping                                                          | 149 |  |

| 6.4 Transfer and Bonding of Ultra-Thin Chips on Flexible Substrates         | 154 |  |

| 6.4.1 Design and Fabrication of Flexible Printed Circuit Boards             | 154 |  |

| 6.4.2 Transfer and Bonding of Ultra-Thin Chips                              | 155 |  |

| 6.5 Summary                                                                 | 156 |  |

| Chapter 7. Characterisation of CMOS ISFETs and Circuits on Ultra-Thin Chips | 158 |  |

| 7.1 Introduction                                                            | 158 |  |

| 7.2 Characterisation of Bulky and Ultra-Thin CMOS-based ISFET Chips         | 159 |  |

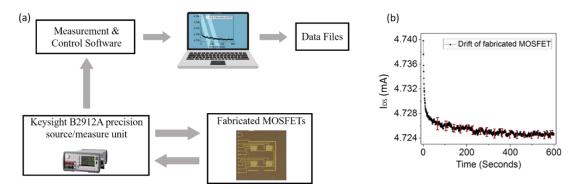

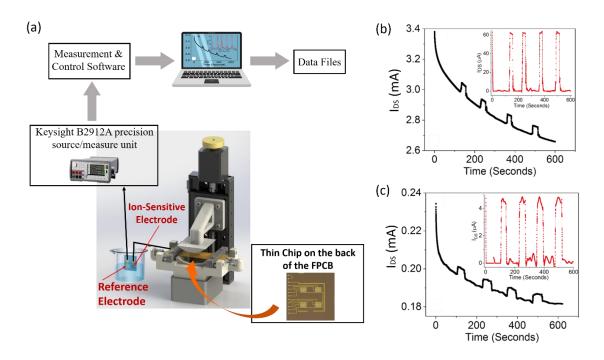

| 7.2.1 Hardware Setup                                                        | 159 |  |

| 7.2.2 Software Setup                                                        | 161 |  |

| 7.2.3 On-Chip Active Pixel Circuits                                         | 163 |  |

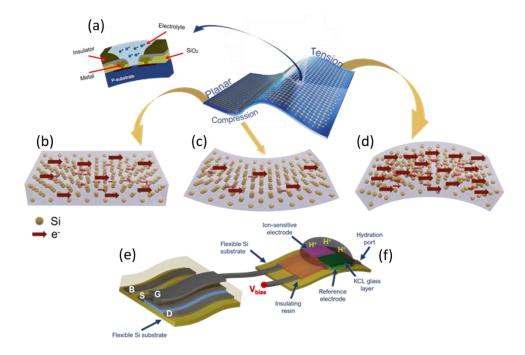

| 7.3 Ultra-Thin ISFET with Bending Induced Performance Enhancement           | 171 |  |

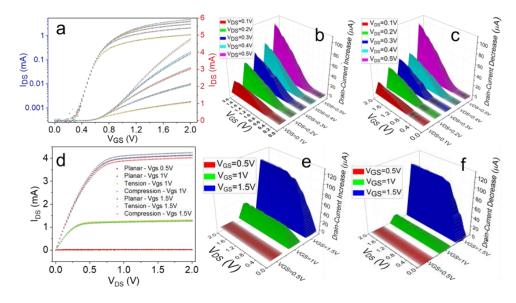

| 7.3.1 Characterisation of Drift in Fabricated MOSFETs                       | 173 |  |

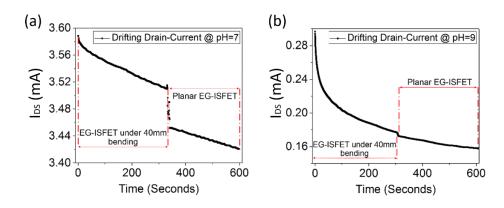

| 7.3.2 Behavior of Drift in Bendable EG-ISFETs                               | 173 |  |

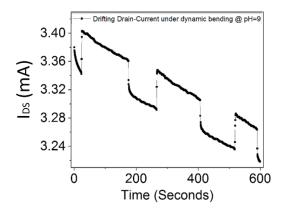

| 7.3.3 Compensation of Drift by Bending the EG-ISFETs on Si-UTCs             | 175 |  |

| 7.4 Summary                                                                 | 179 |  |

| Chapter 8. Conclusion and Future Work                                       | 182 |  |

| 8.1 Conclusion                                                              | 182 |  |

| 8.2 Future Work                                                             | 184 |  |

| References                                                                  | 188 |  |

## List of Tables

| Table 2.1: Values of dissociation constants, the density of sites and pH at the point of zero charges of different oxides [187]                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2: ISFET gate ion-sensitive materials, properties and deposition method.       29                                                                                                             |

| Table 2.3: Analytes found in sweat, tears and blood along with their diagnostic significance [286, 287].                                                                                              |

| Table 3.4: List of Young's modulus and Poisson ratio of some of the materials of interest                                                                                                             |

| Table 3.5: List of measured fundamental coefficients ( $\times 10 - 12Pa - 1$ ) at 298K along with their linear combinations [317, 371]                                                               |

| Table 3.6: Piezoresistive coefficients ( $\times 10 - 12Pa - 1$ ) of NMOS devices on (100) silicon [378] 56                                                                                           |

| Table 3.7: Piezoresistive coefficients of PMOS devices on (100) silicon ( $\times 10 - 12Pa - 1$ ) [378] 57                                                                                           |

| Table 3.8: Comparison table of inverters fabricated on ultra-thin chips.       59                                                                                                                     |

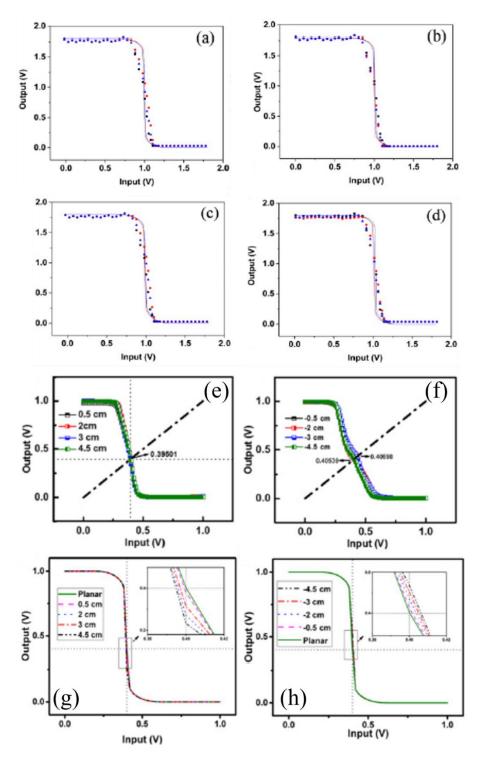

| Table 3.9: Measured values of switching threshold, input-high and input-low voltage of the inverters on the ultra-thin chip with channel-length of 0.18µm at different bending conditions [316]       |

| Table 3.10: Measured values of switching threshold, input-high and input-low voltage of the inverters on the ultra-thin chip with channel-length of $0.35\mu m$ at different bending conditions [316] |

| Table 3.11: Summary table of the formulas and parameters used in the model of MOST devices which include the effect of bending stress.       68                                                       |

| Table 3.12: The measured values used to model the drifting behaviour of the drain-current of EG-ISFETat different pH conditions.73                                                                    |

| Table 3.13: The measured values of carriers' mobility under planar and different bent conditions                                                                                                      |

| Table 4.14: Design specifications.    115                                                                                                                                                             |

| Table 5.15: Design specifications.    120                                                                                                                                                             |

| Table 5.16: Dimensions of transistors of unity-gain folded cascode amplifier                                                                                                                          |

| Table 6.17: Comparison table between different materials used as etch mask or front-side protection         during wet-etching of silicon [333]                                                       |

| Table 7.18: List of measured performance parameters of the folded-cascode unity-gain amplifier 171                                                                                                    |

## List of Figures

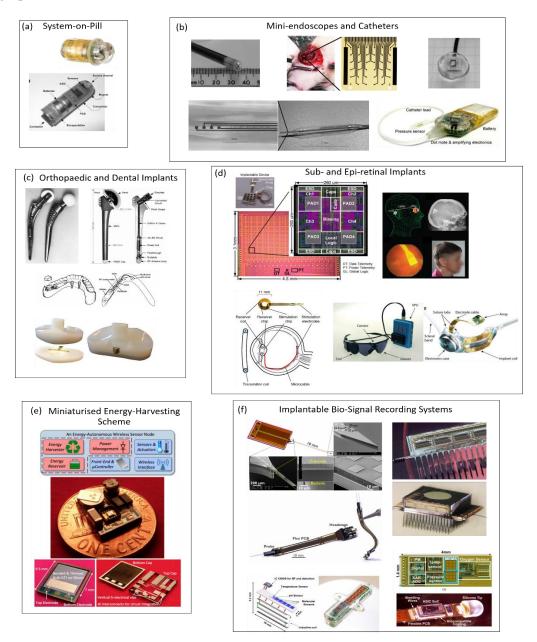

| Figure 1.1: (a) Implantable telemetry platform systems with ASIC for in vivo monitoring of gastrointestinal physiological information [59, 61], (b) Implantable bio-signal recording microsystems on endoscopes and catheters [62-68], (c) Temperature, load and strain sensing microsystems embedded in orthopaedic and dental implants [69-72], (d) High-density self-calibrating and wirelessly powered sub-retinal and epi-retinal artificial vision prosthesis [73-76], (e) Energy harvesting microsystems with self-supplied power-management circuitry [81] and (f) Implantable bio-signal recording microsystems on ultra-thin probes [25, 77-80].                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

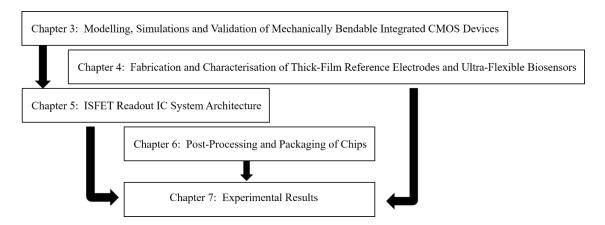

| Figure 1.2: Flowchart showing the connection between the chapters of the thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

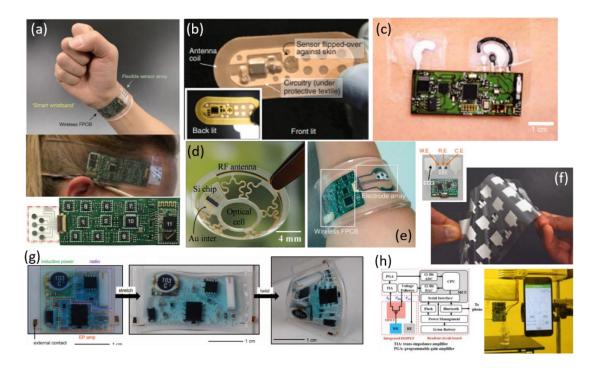

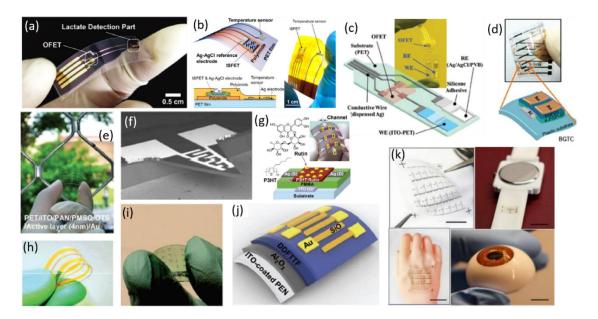

| Figure 2.3: (a) A multiplexed flexible sensing array integrated with a flexible PCB with capabilities for wireless transmission of data on a subject's wrist [86], (b) A Band-aid patch for continuous detection of ions in sweat, with RFID antenna for wireless signal transmission [87], (c) Iontophoretic-based tattoo sensors integrated with a flexible PCB on a human subject [88], (d) Stretchable electronic platform including the Si-chip and the RF-antenna integrated into a soft smart contact lens [89], (e) Wearable system capable of performing sweat extraction and sensing on a human subject [90], (f) Array of printed chemico-physical patches on a flexible substrate integrated with a PCB with capabilities for wireless transmission of data [91], (g) Wearable, soft, stretchable and twistable electronic system capable of electrophysiological measurements [92] and (h) A flexible organic ion-sensitive field-effect transistor integrated with a read-out circuit board [93] |

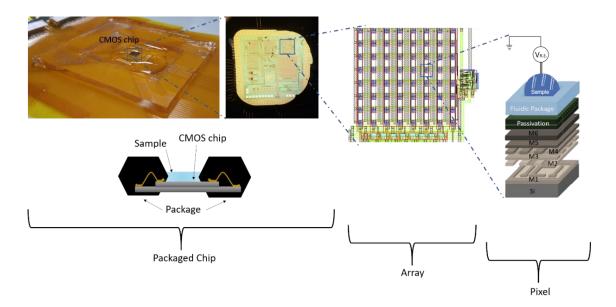

| Figure 2.4: The ultra-thin CMOS based miniaturised lab-on-chip for pH monitoring presented in this thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

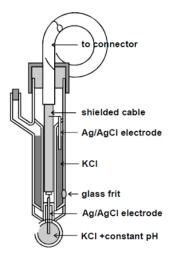

| Figure 2.5: Cross-section of a glass pH electrode [136]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

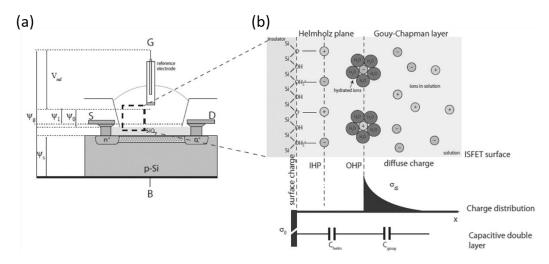

| Figure 2.6: (a) Schematic of the ion-sensitive field-effect transistor (ISFET) and (b) Schematic representation of the site-binding theory and the formation of the electrical double-layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

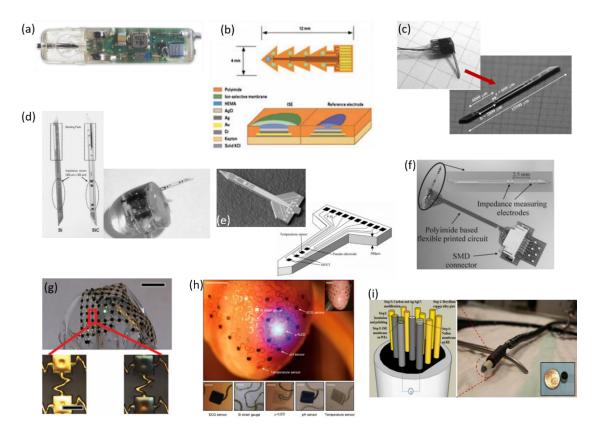

| Figure 2.7: (a) Medtronic Bravo <sup>™</sup> pH monitoring system [167], (b) Flexible multi-electrode array for pH and potassium ion measurements in in-vivo applications [168, 169], (c - f) A few examples of the of first-generation flexible potentiometric sensing probes for in-vivo monitoring of heart ischemia [170-173], (g) A flexible and stretchable IrO <sub>x</sub> -based pH sensing array for heart ischemia monitoring [174], (h) Multi-sensing array with for electrical, chemical and optical measurements capabilities for monitoring of the epicardium for ischemia applications [175] and (i) An endoscopic sensor array used in conjunction with a laparoscopic teleoperated robot gastro-endoscope for the detection of ischemia in the gastrointestinal tract [176-178]                                                                                                                                                                                                              |

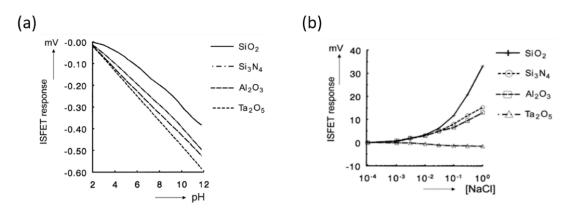

| Figure 2.8: (a) ISFET sensitivity and (b) ISFET response using different metal oxides as a sensitive layer to NaCl electrolyte concentration at constant pH [53]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

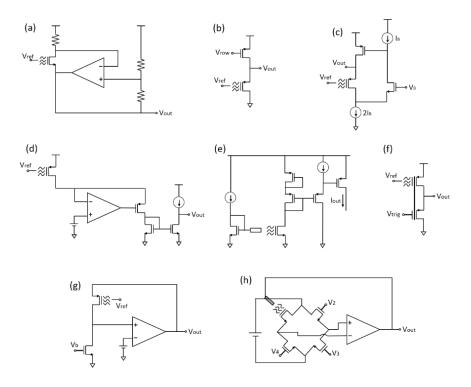

| Figure 2.9: (a) The source and drain follower read-out [53], (b) Standard source-follower in-pixel read-<br>out [201], (c) Modified flipped voltage follower read-out [202], (d) Current conveyor based ISFET read-<br>out [208], (e) Current-mode architecture based on translinear principle [209], (f) ISFET inverter topology<br>[204], (g) Complementary ISFET/MOSFET pair with source feedback [212] and (h) Wheatstone bridge<br>based read-out [213]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

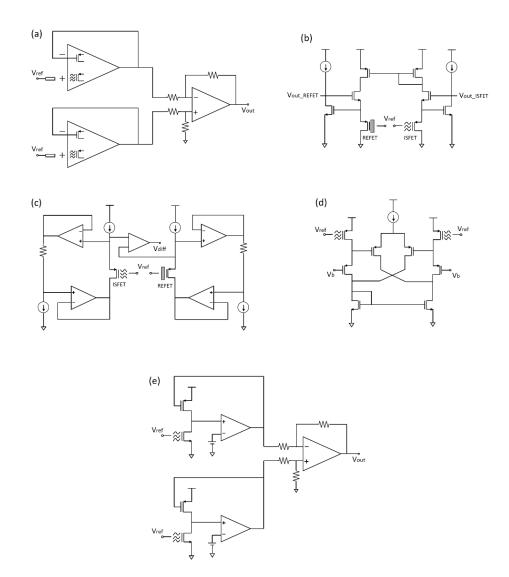

| Figure 2.10: (a) The ISFET/ISFET differential amplifier configuration [214] also reported as ISFET/REFET differentia amplifier in [53], (b) ISFET/REFET voltage clamped topology [215], (c) ISFET/REFET differential measurement configuration [216] also reported as ISFET/ISFET differential measurement configuration in [221], (d) ISFET/ISFET chemical Gilbert cell [218] and (e) ISFET/ISFET differential read-out architecture [220]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

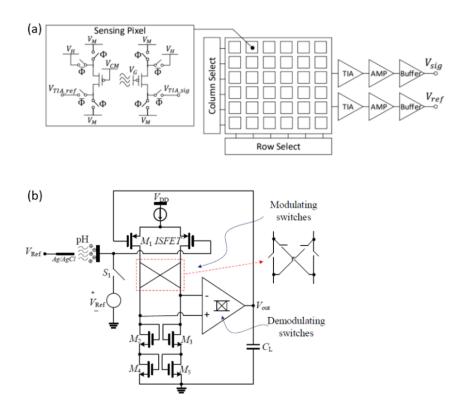

| Figure 2.11: (a) ISFET/MOSFET pair with in-pixel chopping scheme [222] and (b) Chopper-stabilised ISFET/MOSFET differential amplifier [225]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 2.12: (a) Block diagram of the ISFET front-end and microcontroller-based measurement system [232], (b) Switched-capacitor correlated double sampling topology [233] and (c) PWM ISFET interface circuit for vertical electric field cycling [224]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

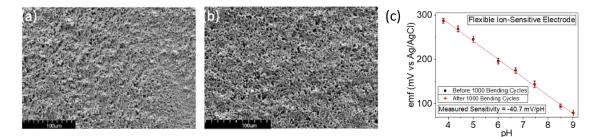

Figure 3.19: (a) SEM image of the surface morphology of the RuO<sub>2</sub> based ion-sensitive material on a  $45\mu$ m thick silicon substrate before 1000 bending cycles, (b) SEM image of the surface morphology of the RuO<sub>2</sub> based ion-sensitive material on a  $45\mu$ m thick silicon substrate after 1000 bending cycles and (c) Sensitivity measurement (Open circuit potential vs. pH value) of the RuO<sub>2</sub> based ion-sensitive electrode on a  $45\mu$ m thick silicon substrate before and after 1000 bending cycles at a maximum nominal strain of  $\pm 21 \times 10^{-4}$  [194].

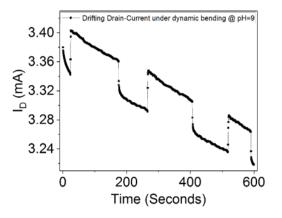

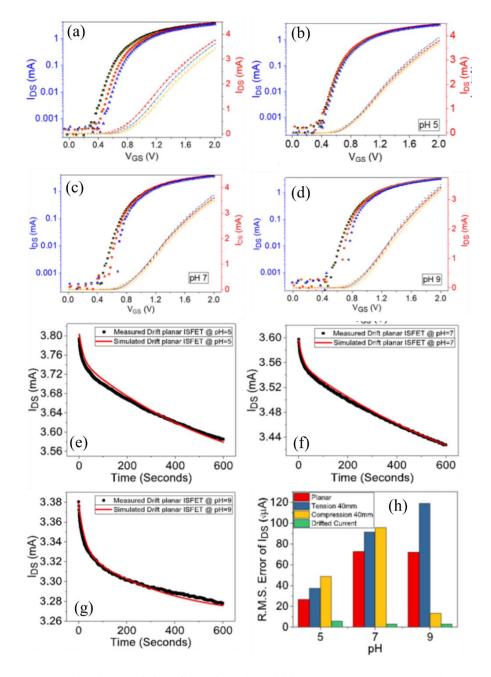

Figure 3.22: Behaviour of drift in bendable EG-ISFETs under dynamic bending showing that the driftrate does not change. These results were obtained after 1000 bending cycles of the EG-ISFETs. Drifting current of EG-ISFET biased at VR. E. = VGS = 2V and VDS = 0.4V at pH 9 [194]......74

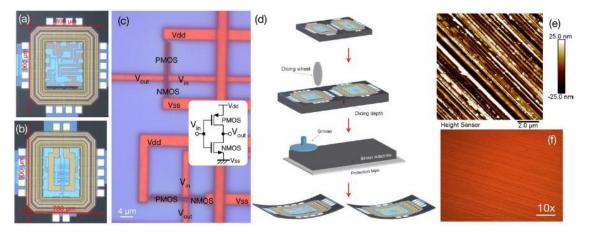

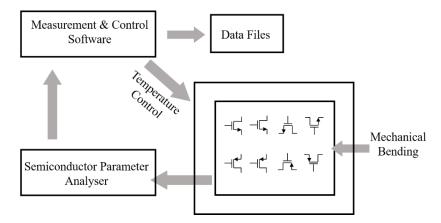

Figure 3.25: Simplified block diagram of the measurement setup......77

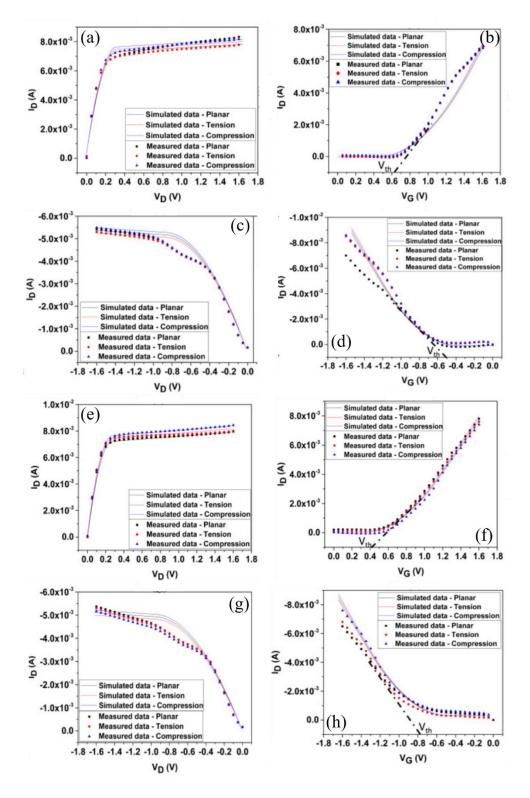

Figure 3.26: Measured (symbols) and simulated (lines) transfer and output characteristic curves of nMOS and pMOS transistors under planar, tensile, and compressive bending conditions. (a) Output characteristic (IDS - VDS). And (b) Transfer characteristics (IDS - VGS) of nMOS transistors with a channel length of 0.18  $\mu$ m. (c) Output characteristic (IDS - VDS) and (d) Transfer characteristics (IDS - VDS)

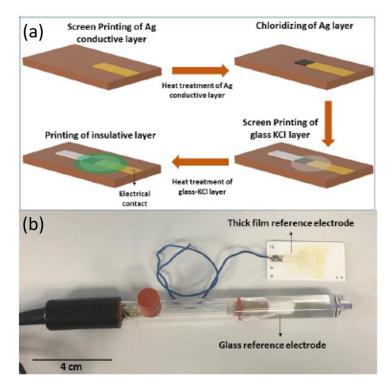

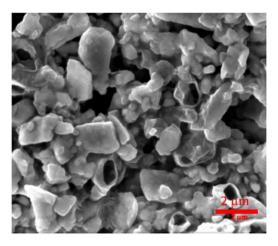

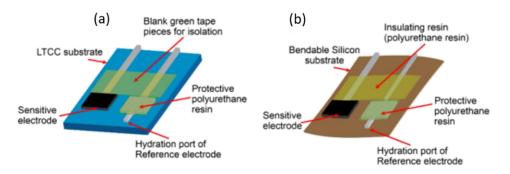

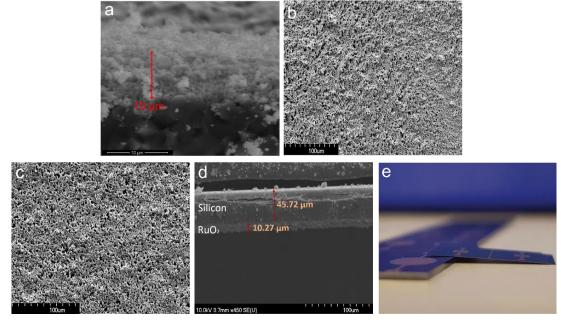

| Figure 4.34: (a) Scanning electron microscopic (SEM) image of surface morphology of the $RuO_2$ -based ion-sensitive oxide on rigid LTCC substrate, (b) Scanning electron microscopic (SEM) image of surface morphology of the $RuO_2$ -based ion-sensitive oxide on flexible silicon substrate before 1000 bending cycles, (c) Scanning electron microscopic (SEM) image of surface morphology of the $RuO_2$ -based ion-sensitive oxide on the flexible silicon substrate after 1000 bending cycles at maximum 40 mm bending radius, (d) Cross-section of the screen-printed $RuO_2$ layer showing thickness of 10µm and (e) Photograph of a thin silicon substrate compared with a brittle silicon piece with deposited electrodes [194]. Courtesy to Dr Libu Manjakkal who synthesised the RuO <sub>2</sub> paste |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

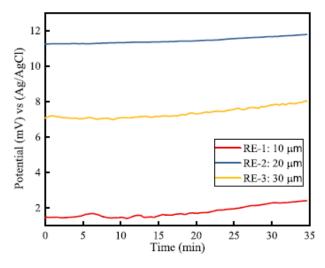

| Figure 4.35: Potential (emf) between the fabricated thick-film RE with various thickness of the KCl layer versus a commercially available standard glass-RE [131]. Courtesy to Dr Libu Manjakkal who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

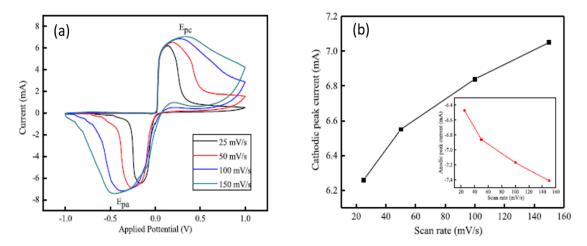

| Figure 4.36: (a) CV response of the fabricated thick-film RE under different scanning rates and (b) The variation of the cathodic and anodic (inset) peak current with scan rate [131]. Courtesy to Dr Libu Manjakkal who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

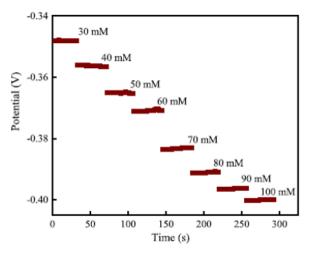

| Figure 4.37: Response of the fabricated thick-film reference electrode against a commercially available glass Ag/AgCl reference electrode in different concentrations of NaCl [131]. Courtesy to Dr Libu Manjakkal who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

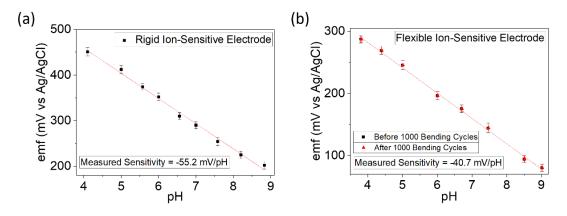

| Figure 4.38: (a) Open circuit potential as a function of pH for $RuO_2$ -based ion-sensitive electrode on rigid LTCC substrate and (b) Open circuit potential as a function of pH for $RuO_2$ -based ion-sensitive electrode on flexible silicon substrate before and after 1000 bending cycles at maximum 40mm bending radius [194]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

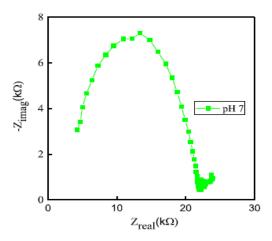

| Figure 4.39: Nyquist plot for the two-electrode system in pH 7 solution [131]. Courtesy to Dr Libu Manjakkal who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

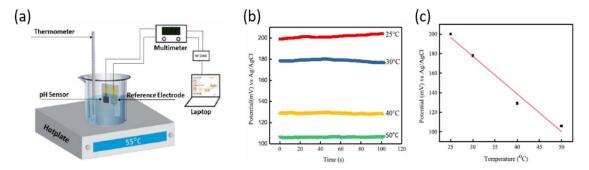

| Figure 4.40: (a) The experimental setup with a temperature regulated system connected to the digital-<br>multimeter and the LabVIEW interface, (b) Stability of potential at buffer solution of pH value 5 on<br>different temperature and (c) Potential value vs Temperature plot [131]. Courtesy to Dr Libu Manjakkal<br>who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

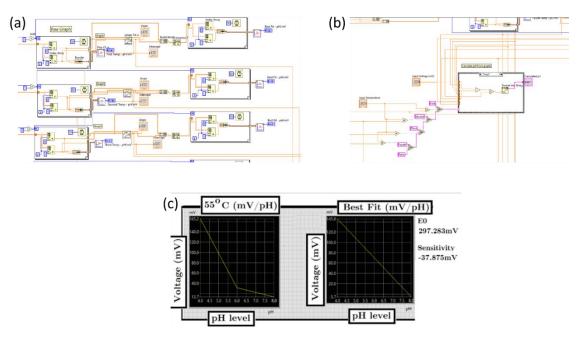

| Figure 4.41: (a) Part of the LabVIEW program which calculates the sensitivities by the slope of the accurate best fit, (b) Part of the LabVIEW program which calculates the levels of pH of an unknown solution and (c) Obtained and fitted graph respectively for sensor's sensitivity at 55°C [131]. Courtesy to Dr Libu Manjakkal who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

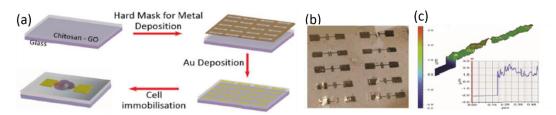

| Figure 4.42: (a) Schematics representing the fabrication process of the GO-Chit sensing patch for cell-<br>health monitoring, (b) Photograph of the fabricated GO-Chit sensing patch and (c) Surface morphology<br>of the fabricated GO-Chit sensing patch also showing the thickness of the patch obtained using the<br>Dektak XT profilometer [413]. Courtesy to Prof. Md Abdul Kafi and Dr Ambarish Paul who led this<br>work                                                                                                                                                                                                                                                                                                                                                                                      |

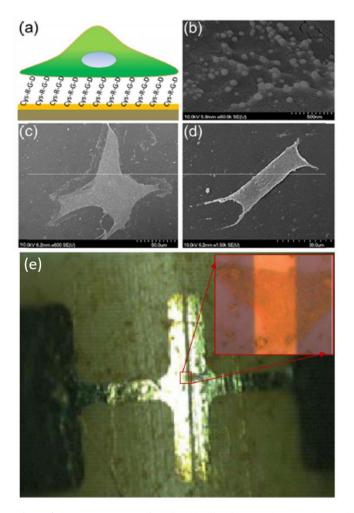

| Figure 4.43: (a) Illustration of the Cys-RGD assisted cell adhesion on the Au electrode, (b) SEM image of the self-assembled RGD nano-dots on the electrode, (c) Focal adhesion formation on RGD functionalised sensor-patch, (d) SEM image of the immobilised cell on non-RGD functionalised sensor patch and (e) Optical image of the immobilised cell on the Au electrode's micro-gap and paraformaldehyde-fixed dehydrated sample in the inset [413]. Courtesy to Prof. Md Abdul Kafi and Dr Ambarish Paul who led this work                                                                                                                                                                                                                                                                                      |

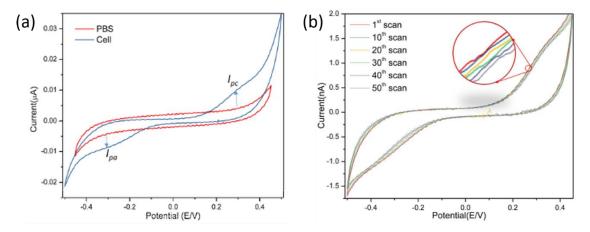

| Figure 4.44: (a) Cyclic voltammetry graph obtained from a GO-Chit substrate with HDF cells immobilised and (b) Cyclic voltammetry graph obtained from a GO-Chit substrate with HDF cells immobilised run for 50 cycles [413]. Courtesy to Prof. Md Abdul Kafi and Dr Ambarish Paul who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

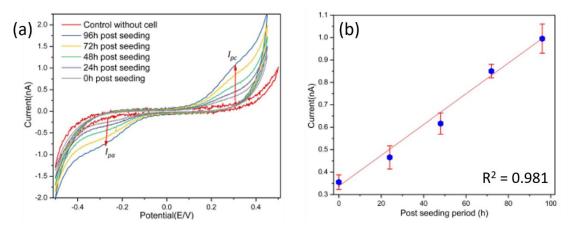

| Figure 4.45: (a) Cyclic voltammetry graph of HDF immobilized GO-Chit substrate at various period of post-seeding and (b) Changes in the <i>Ipc</i> peak intensities at different periods of cell growth on the GO-Chit substrate [413]. Courtesy to Prof. Md Abdul Kafi and Dr Ambarish Paul who led this work 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

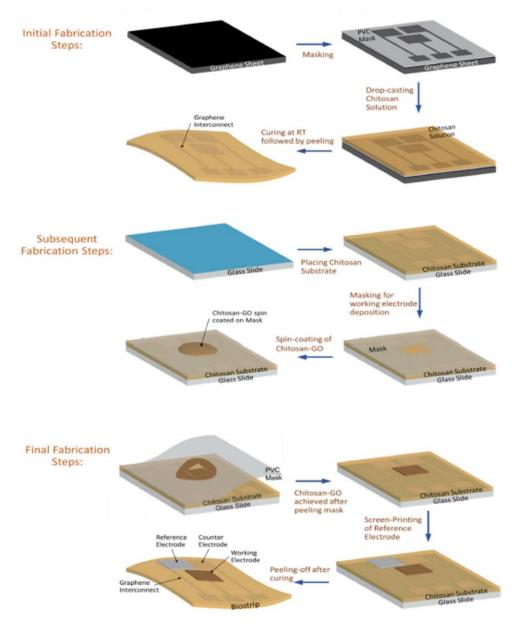

| Figure 4.46: Design and dimensions of the laser-cut PVC hard mask [410]. Courtesy to Prof. Md Abdul Kafi and Dr Ambarish Paul who led this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

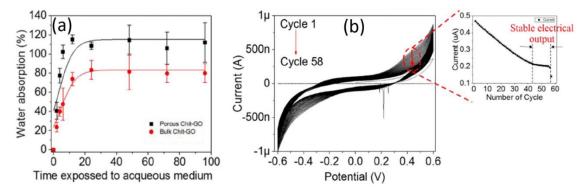

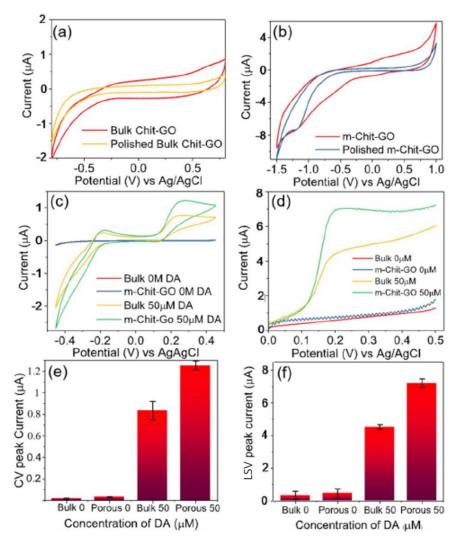

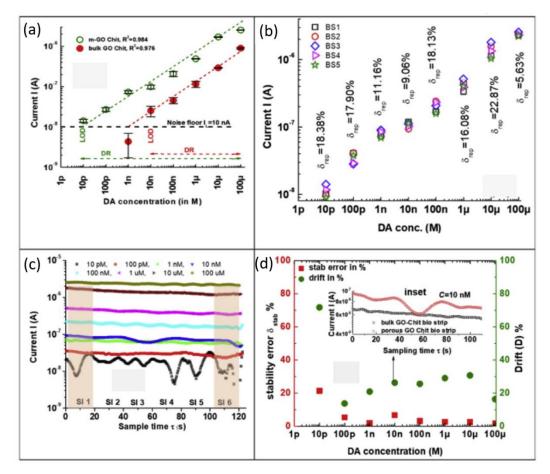

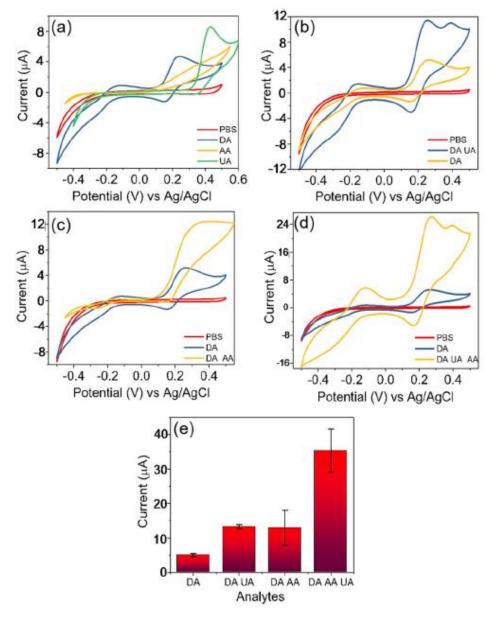

Figure 4.51: (a) Calibration plot for non-porous sand m-GO-Chit based bio-strip in the DA concentration range of 10 pM to  $100\mu$ M, (b) Characterisation of five different m-GO-Chit based sensors showing the reproducibility error for different DA concentrations, (c) Chrono-amperometric plot for different DA concentrations recorded for a total sampling time of 120 seconds showing the electrical stability and drift in sensor performance over time and (d) Stability error and drift vs. DA concentration plot for m-GO-Chit based sensors, inset: Comparative current vs. Time plot for non-porous and m-Chit-GO based bio-strips for DA concentration of 10nM [410]. Courtesy to Prof. Md Abdul Kafi and Dr Ambarish Paul who led this work.

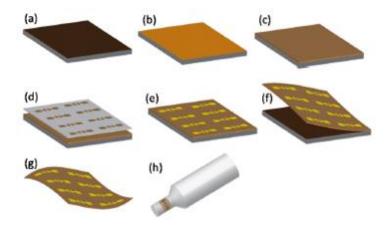

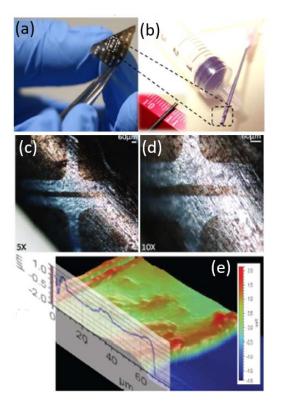

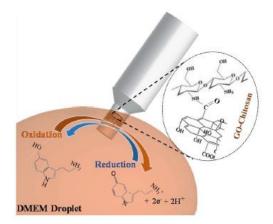

Figure 4.53: Fabrication steps of the SoP: (a) Si wafer, (b) Spin-coated cellulose acetate butyrate (CAB), (c) Drop-casted and cured GO/Chitosan, (d) Hard-mask for metal deposition, (e) Deposited platinum (Pt) electrodes on GO/Chitosan film, (f) Peeling off the CAB and GO/Chitosan layers, (g) Electrodes on GO/Chitosan film after dissolving CAB in acetone and (h) Mounting of the sensor on probe [411]. Courtesy to Prof. Md Abdul Kafi and Dr Ambarish Paul who synthesised the GO-Chit composite...... 112

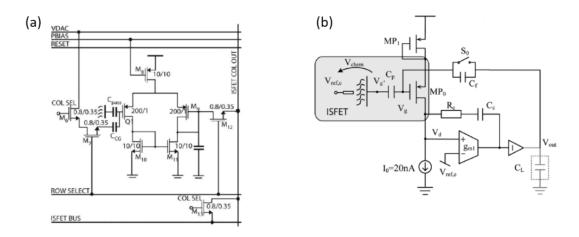

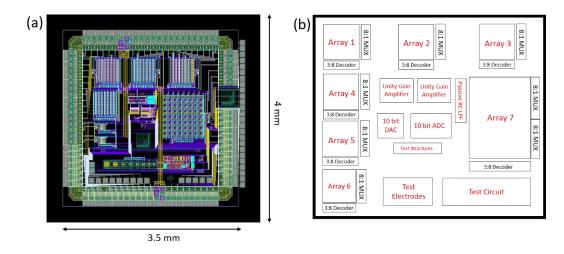

| Figure 5.57: (a) Finished chip layout and (b) Block diagram of the chip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

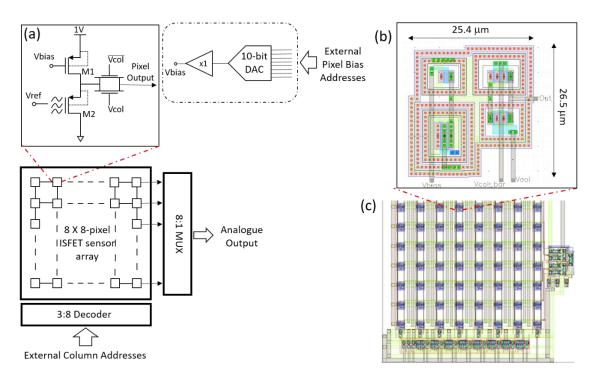

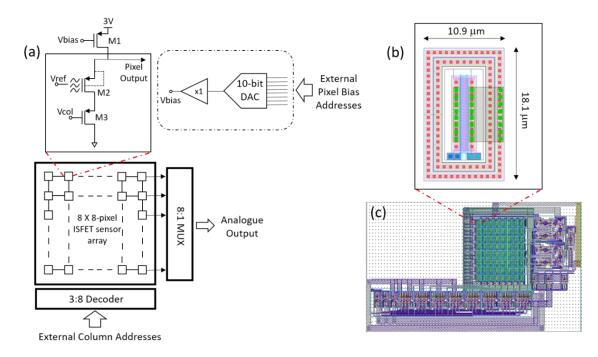

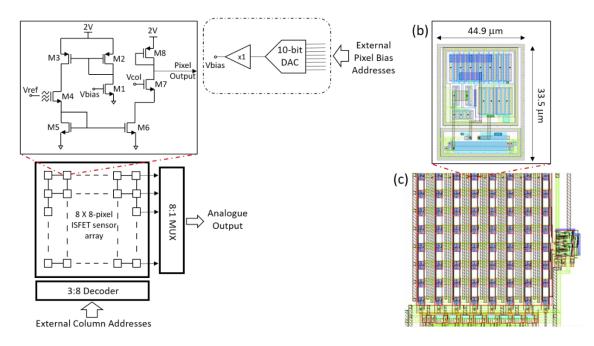

| Figure 5.58: (a) Schematic of the 8×8 array and of the in-pixel standard readout topology, (b) Layout of the in-pixel standard readout topology (poly-layer together with the first two metal-layers) and (c) Layout of the 8×8 array including the decoder and the analogue multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

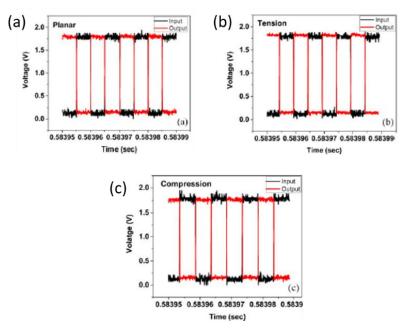

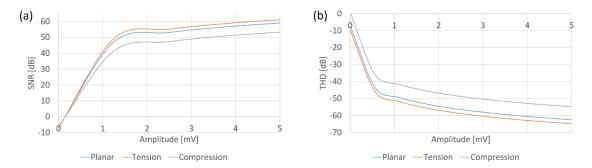

| Figure 5.59: (a) Simulated SNR vs. Input signal amplitude and (b) THD vs. Input signal amplitude of the standard readout topology at different strain condition (i.e. planar, tension and compression)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

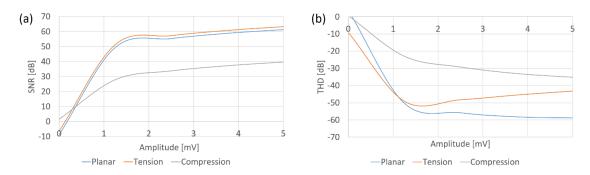

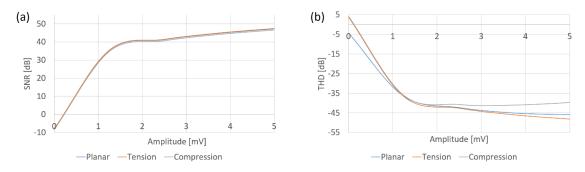

| Figure 5.60: (a) Schematic of the 8×8 array and of the in-pixel standard readout topology with improved fill-factor, (b) Layout of the in-pixel readout topology (poly-layer together with the first two metal-layers) and (c) Layout of the 8×8 array including the decoder and the analogue multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 5.61: (a) Simulated SNR vs. Input signal amplitude, (b) THD vs. Input signal amplitude of the standard readout topology with improved fill-factor at different strain condition (i.e. planar, tension and compression)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 5.62: (a) Schematic of the 8×8 array and of the in-pixel current-mode readout topology, (b) Layout of the in-pixel readout topology (poly-layer together with the first two metal-layers) and (c) Layout of the 8×8 array including the decoder and the analogue multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 5.63: (a) Simulated SNR vs. Input signal amplitude, (b) THD vs. Input signal amplitude of the current-mode readout topology at different strain condition (i.e. planar, tension and compression) 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

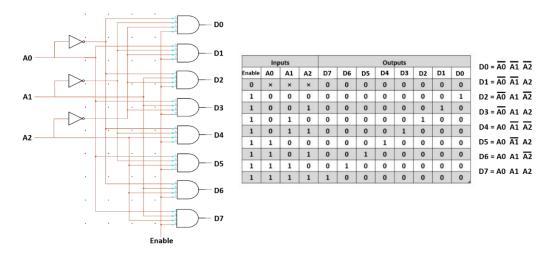

| Figure 5.64: Schematic and truth table of the decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

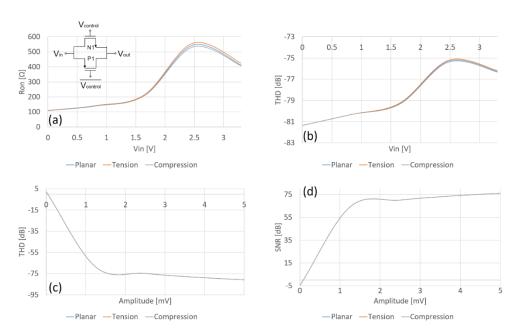

| Figure 5.65: Simulated (a) on-resistance, (b), THD vs. DC level at the input of the transmission gate, (c) THD vs. input signal amplitude and (d) SNR vs. input signal amplitude of the transmission gate at different strain conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

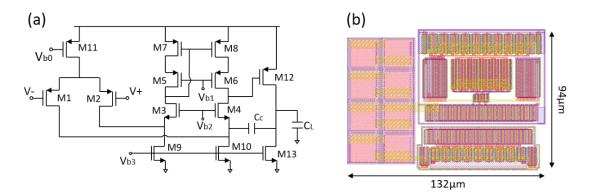

| Figure 5.66: (a) Schematic and (b) Layout of the two-stage folded-cascode amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

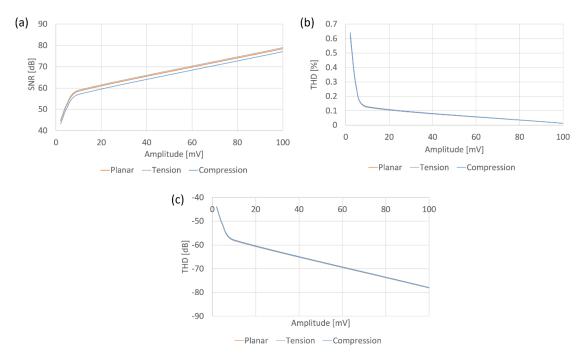

| Figure 5.67: (a) Simulated SNR vs. Input signal amplitude, (b) THD [%] and (c) THD [dB] vs. Input signal amplitude of the unity-gain folded cascode amplifier at different strain condition (i.e. planar, tension and compression)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

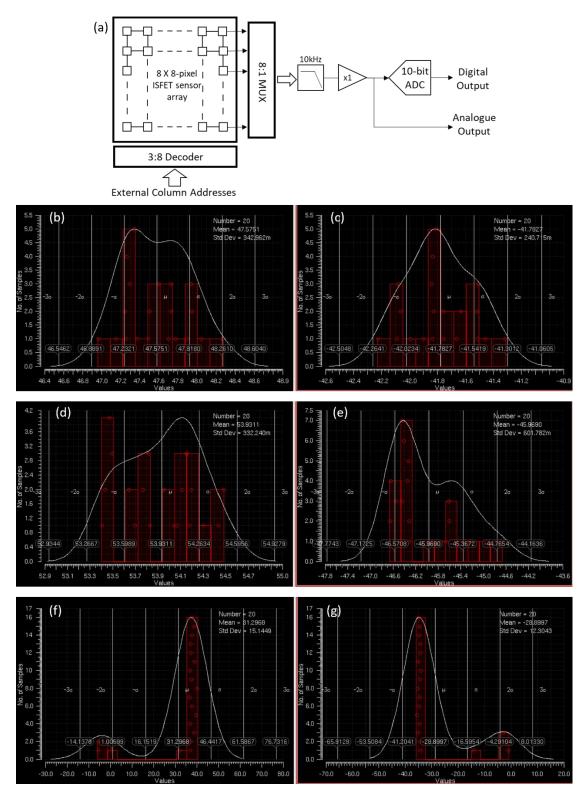

| Figure 5.68: (a) The architecture of the complete signal chain from an $8 \times 8$ ISFET array. (b, d, f)<br>Monte-Carlo simulations of the SNR of the complete signal chain using an input signal amplitude of $1.2 \text{mV}_{\text{p-p}}$ and the standard pixel readout, standard pixel readout with improved fill-factor and current-mode topologies, respectively. (c, e, g) Monte-Carlo simulations of the THD of the complete signal chain using an input signal amplitude of $1.2 \text{mV}_{\text{p-p}}$ and the standard pixel readout, standard pixel readout with improved fill-factor and current-mode topologies, respectively. (c, e, g) Monte-Carlo simulations of the THD of the complete signal chain using an input signal amplitude of $1.2 \text{mV}_{\text{p-p}}$ and the standard pixel readout, standard pixel readout with improved fill-factor and current-mode topologies, respectively |

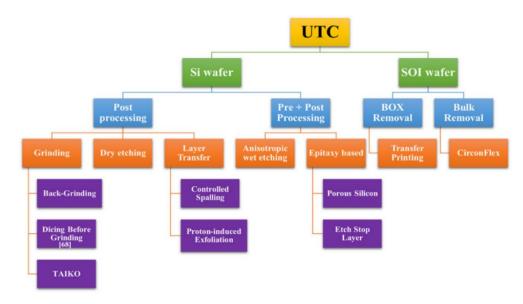

| Figure 6.69: Classification of various silicon thinning techniques for realising ultra-thin silicon wafers and chips [58]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

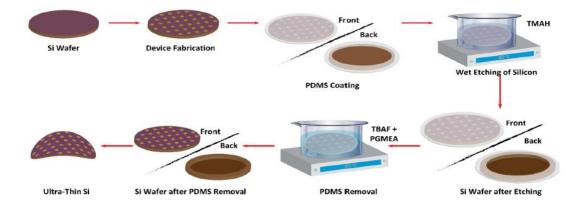

| Figure 6.70: Illustration of the process followed to realise ultra-thin silicon using a PDMS as protective layer [333]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

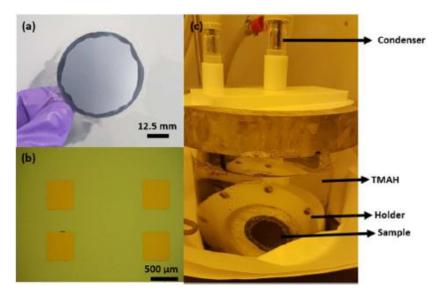

| Figure 6.71: Image of (a) wafer backside showing the etching window defined using PDMS, (b) optical image of the capacitive device on front-side and (c) the etching setup [333]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

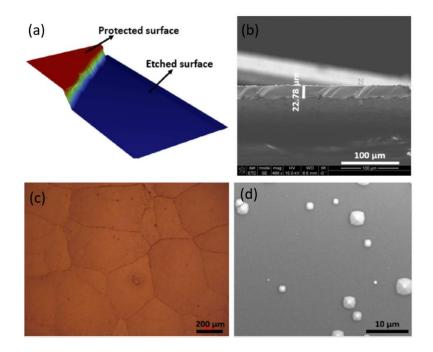

| Figure 6.72: (a) 3D scan of etched step showing the masking property of PDMS. The red area was masked with PDMS and the blue area shows the silicon region, (b) SEM image of the 22.78 $\mu$ m thick silicon obtained after 6 hours of etching, (c) Optical image of the etched backside showing the etch pits created during etching due to preferential etching of different crystallographic planes and (d) SEM image of hillocks formed on the silicon surface due to micro-masking effect due to hydrogen formed as a by-product of the chemical reaction between silicon and TMAH [333]                                                                                                                                                                                                                                                                                                                        |

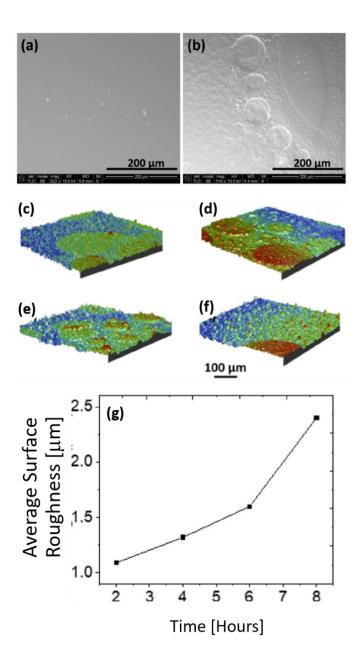

| Figure 6.73: SEM image of PDMS surface (a) Before etching and (b) After 2 hours of etching in TMAH. 3D profile scan of PDMS surface at the end of (c) 2 hours, (d) 4 hours, (e) 6 hours and (f) 8 hours of etching in TMAH and (g) Plot of the surface of PDMS vs etching time showing an almost linear increase in the roughness with time [333]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 6.74: (a) Reaction mechanism between TBAF and PDMS based on the nucleophilic attack of fluoride ion on the siloxane bond leading to the dissolution of the PDMS chain in the solvent. SEM image of silicon sample during (b) midway of PDMS etching and (c) after PDMS etching [333] 148 xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

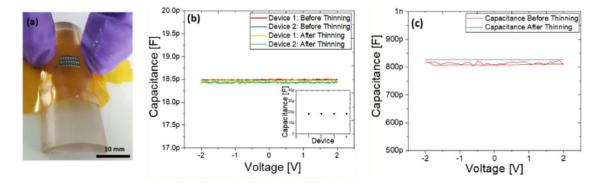

| Figure 6.75: (a) Image of thinned sample integrated into polyimide foil and placed over a 3D printed bending structure with bending radius of 10mm, (b) C-V plot of capacitive structures before and after thinning obtained using PDMS as a protective coating and (c) C-V plot of a sample capacitive device before and after thinning using ProTEK as protection coating [333].                                                                                                                                                                                                                                                                                     | 48 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

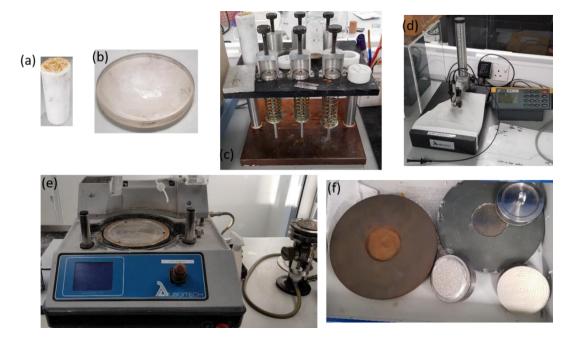

| Figure 6.76: Image of (a) Bonding wax, (b) Glass circular carrier with a diameter of 106mm, (c) Pressir system used to ensure uniformly spread bonding wax at the interface between glass-carrier and silicon sample, (d) Thickness measuring tool, (e) PM5 Logitech precision lapping and polishing machine (left) and jig (right) and (f) Lapping plates.                                                                                                                                                                                                                                                                                                            |    |

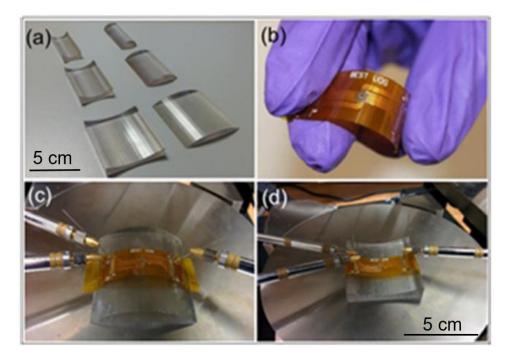

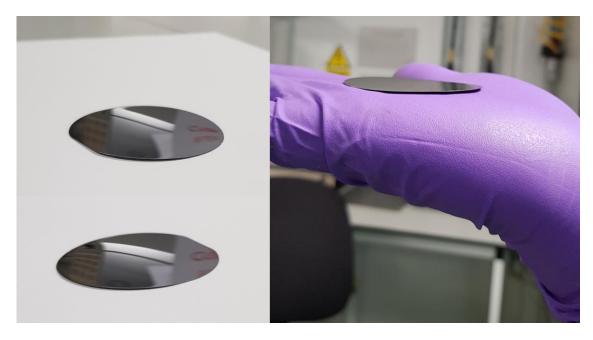

| Figure 6.77: Photographs of the two 2-inch wafers thinned down to the ultra-thin regime to optimise the thinning process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

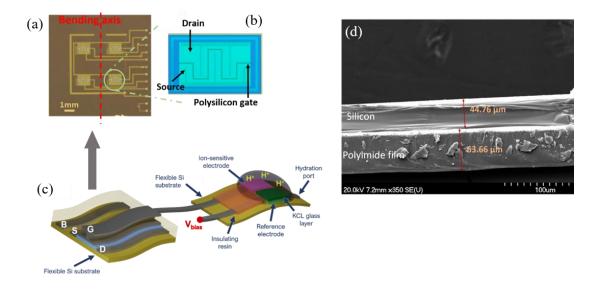

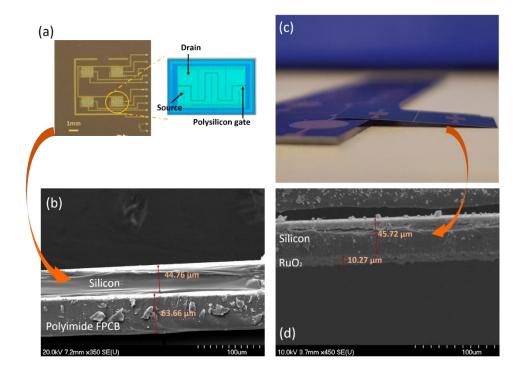

| Figure 6.78: (a) The fabricated chip $(1 \times 1 \text{ cm}^2)$ with four n-channel transistors and (b) the SEM image<br>the cross-section of the thin chip on a polyimide-based flexible PCB showing the thickness of the chip<br>and FPCB. (c) Photograph of thin silicon compared the bulky silicon dies with deposited ion-sensitive<br>electrodes and (d) the SEM image of the cross-section of the RuO <sub>2</sub> -based ion-sensitive electrode [194].<br>Courtesy to Dr Shoubhik Gupta who designed the photolithography masks used for the fabrication of the<br>four n-channel transistors which was done in the Fondazione Bruno Kessler (FBK) institute | ne |

| Figure 6.79: Time-lapse of the fabricated RuO <sub>2</sub> -based ion-sensitive electrode on the ultra-thin and mechanically flexible silicon substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53 |

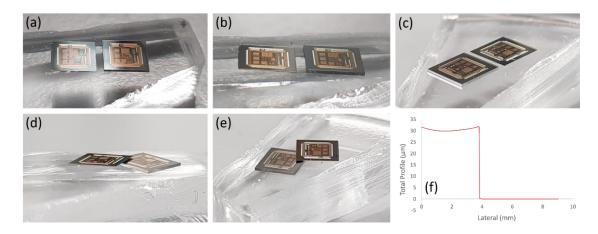

| Figure 6.80: (a - e) Photographs of the ultra-thin ICs compared with the bulky counterpart and (f) Surface profile of the ultra-thin chip measured using the DektakXT Stylus Surface Profiling System                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

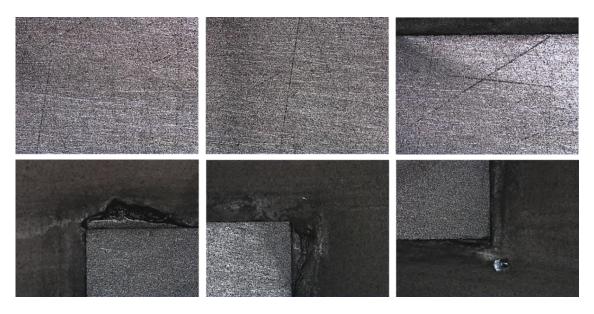

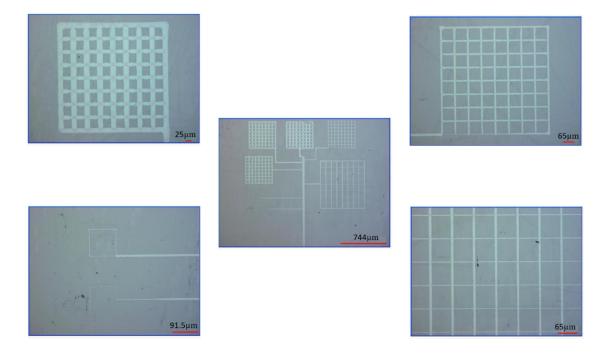

| Figure 6.81: Microscopic images of the backside after back-lapping of the dies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54 |

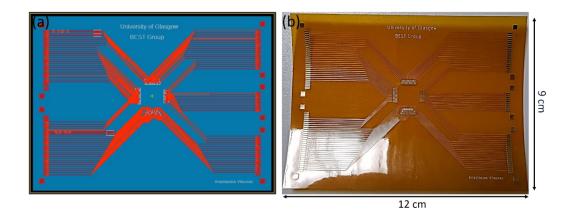

| Figure 6.82: (a) Designed and (b) Fabricated flexible PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54 |

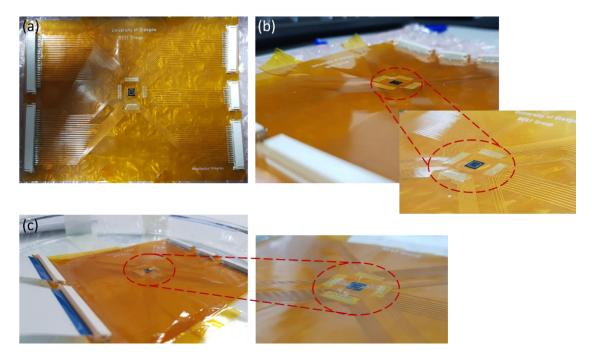

| Figure 6.83: Photographs of the (a, b) Glued ultra-thin IC and (c) Wire-bonded ultra-thin IC on the FPCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55 |

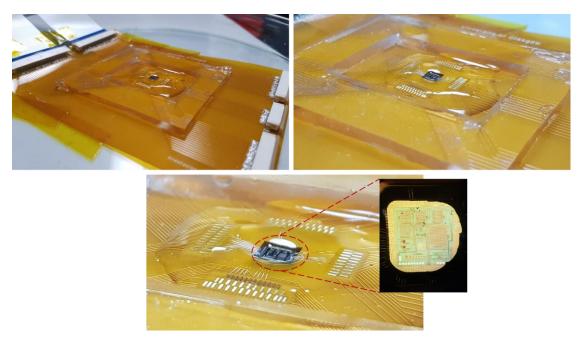

| Figure 6.84: Photographs of the encapsulated ICs on the FPCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56 |

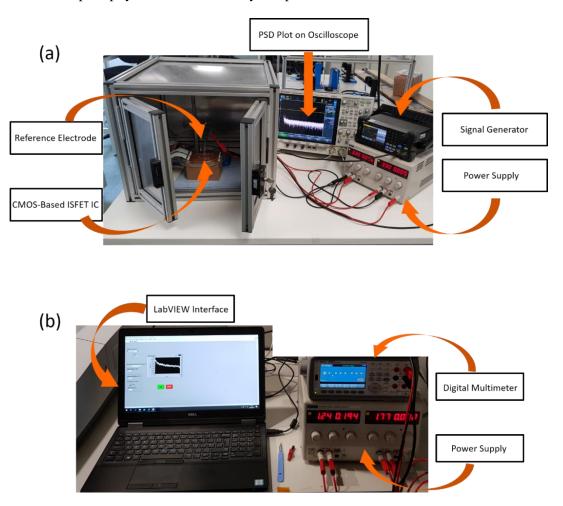

| Figure 7.85: Experimental setup for the characterisation of signal-to-noise ratio (SNR), input-referred noise, total harmonic distortion (THD) and noise spectral density of each ISFET active-pixel. (b) Experimental setup for the characterisation of pH sensitivity, drift and hysteresis                                                                                                                                                                                                                                                                                                                                                                          | 60 |

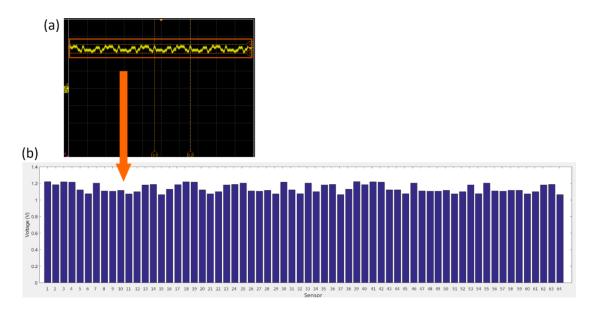

| Figure 7.86: (a) Analogue recording of the output voltage of an 8×8 ISFET array with improved fill-<br>factor captured in an oscilloscope and (b) The same recording captured by a Mbed LPC1768<br>microcontroller and visualised in real-time using Matlab                                                                                                                                                                                                                                                                                                                                                                                                            | 62 |

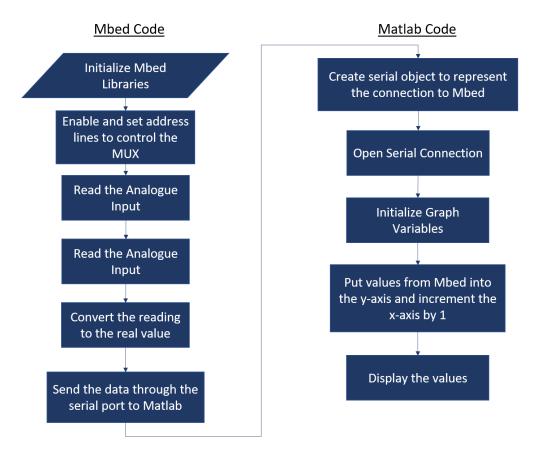

| Figure 7.87: Flowcharts of Mbed and Matlab programs to acquire and visualise the data acquired from the chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62 |

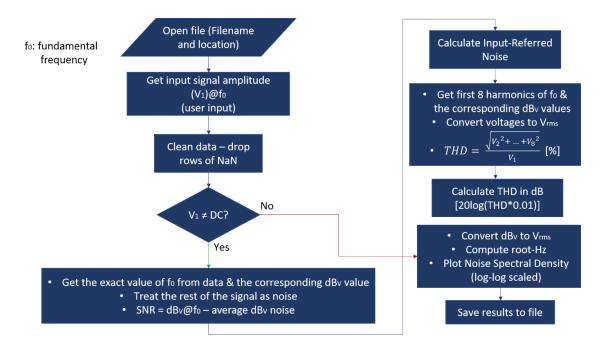

| Figure 7.88: Flowchart of the data analysis script in Python for the extraction of SNR, input-referred noise, THD and noise spectral density from the obtained PSD plots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63 |

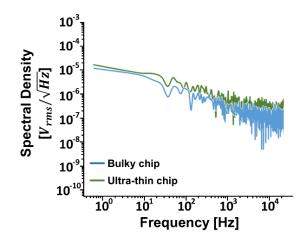

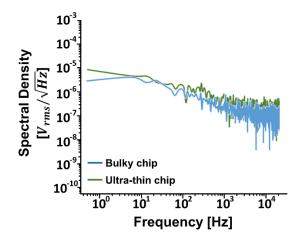

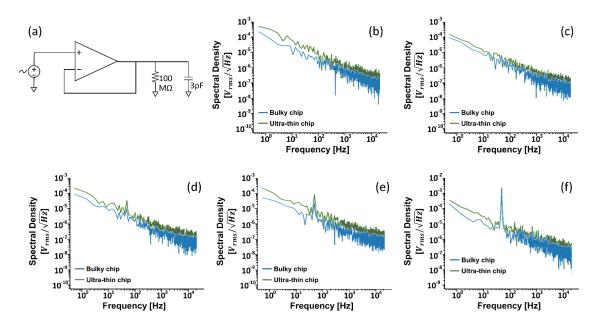

| Figure 7.89: Measured average noise spectral density of the standard pixel readout topology on bulky and ultra-tin ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64 |

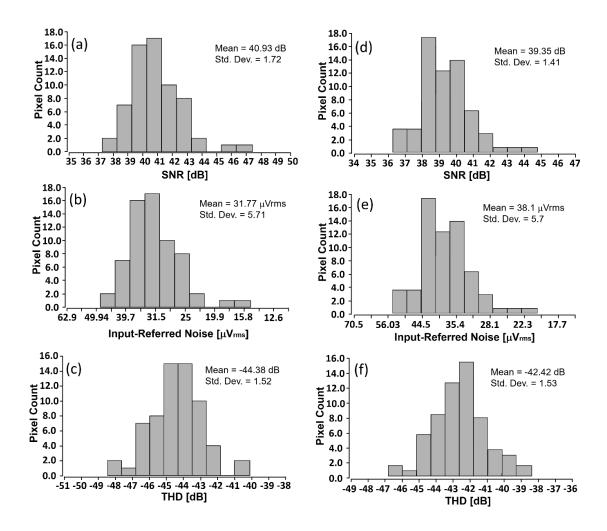

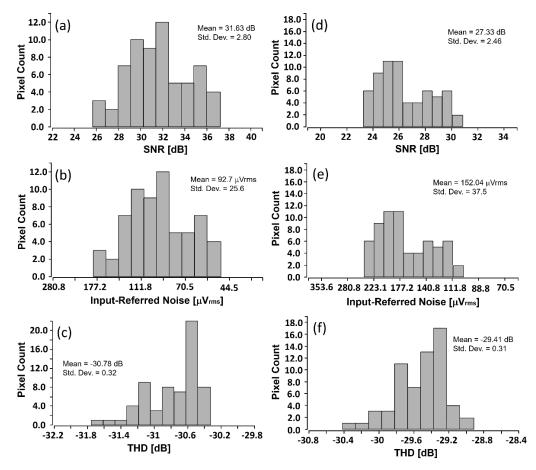

| Figure 7.90: (a - c) Histograms of the measured performance parameters of the 8×8 standard pixel readout ISFET array on the bulky (~250 µm thick) IC, (d - f) Histograms of the measured performance parameters of the 8×8 standard pixel readout ISFET array on the ultra-thin (30 µm thick) IC                                                                                                                                                                                                                                                                                                                                                                       | 65 |

| Figure 7.91: Measured average noise spectral density of the standard pixel with improved fill-factor readout topology on bulky and ultra-tin ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66 |

| Figure 7.92: (a - c) Histograms of the measured performance parameters of the 8×8 standard pixel with improved fill-factor readout ISFET array with improved fill-factor on the bulky (~250 µm thick) IC, (d f) Histograms of the measured performance parameters of the 8×8 standard pixel with improved fill-factor readout ISFET array on the ultra-thin (30 µm thick) IC.                                                                                                                                                                                                                                                                                          | -  |

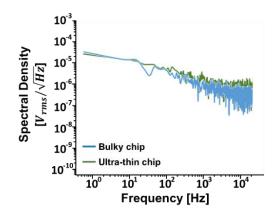

| Figure 7.93: Measured average noise spectral density of the current-mode pixel readout topology on bulky and ultra-thin ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

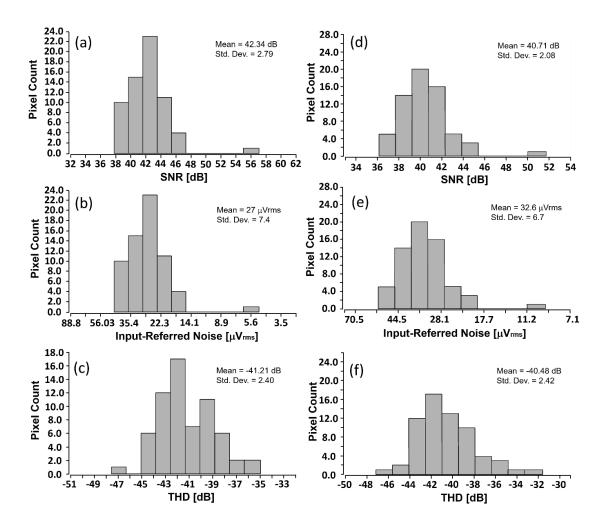

Figure 7.94: (a - c) Histograms of the measured performance parameters of the  $8\times8$  current-mode pixel readout ISFET array on the bulky (~250 µm thick) IC, (d - f) Histograms of the measured performance parameters of the  $8\times8$  current-mode pixel readout ISFET array on the ultra-thin (30 µm thick) IC. ..... 168

Figure 7.96: (a) Test configuration of the folded-cascode amplifier connected in a unity-gain configuration driving the loads which resemble the on-chip SAR ADC input impedance and capacitance. The obtained noise spectral density when was the applied signal at the input of the unity-gain amplifier was (b) DC, (c)  $2mV_{p-p}$  @ 50Hz, (d)  $5mV_{p-p}$  @ 50Hz, (e)  $10mV_{p-p}$  @ 50Hz and (f)  $100mV_{p-p}$  @ 50Hz.

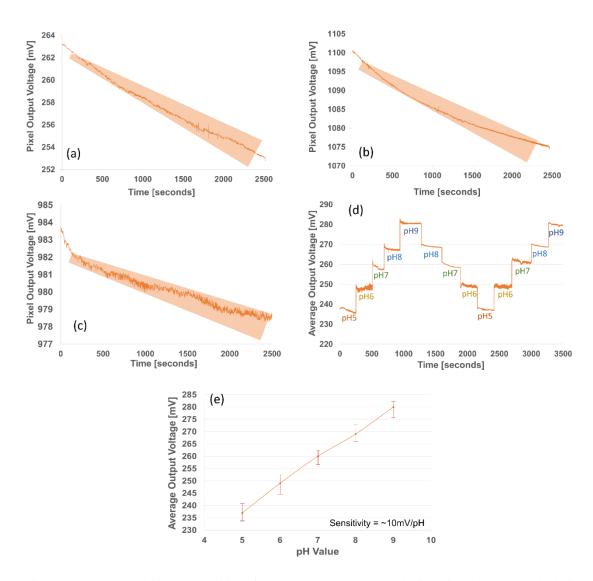

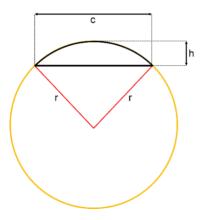

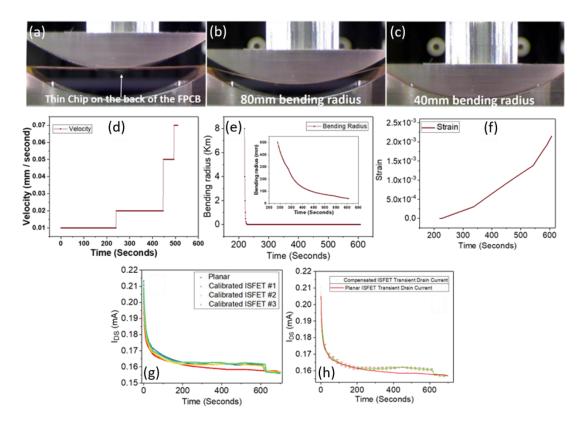

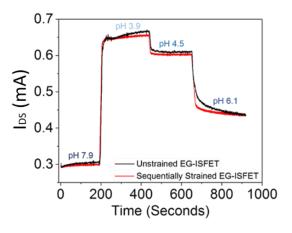

Figure 7.103: (a) Photograph of the motorized press at the moment of contact with the flexible printedcircuit-board (FPCB), (b) Photograph of the motorized press when it has reached the mid-point of the overall travelled distance and the chip is bent under 80mm bending radius, (c) Photograph of the motorized press when it has reached maximum travelled distance and the chip is bent at 40mm bending radius, (d) Velocity vs. Time plot describing the movement of the motorized press, (e) Calculated Bending Radius vs. Time diagram plot used to achieve drift-free ISFET response, (f) Calculated Strain vs. Time diagram plot used to achieve drift-free ISFET response, (g) Transient response of ISFET under planar condition compared with the drift-free response achieved by applying sequentially increased