Dhongde, Aniket (2023) *Advanced GaN HEMT technology for millimetrewave amplifiers*. PhD thesis.

https://theses.gla.ac.uk/83812/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses <u>https://theses.gla.ac.uk/</u> research-enlighten@glasgow.ac.uk

# Advanced GaN HEMT Technology for Millimetre-wave Amplifiers

by

Aniket Dhongde

# A thesis submitted in fulfilment for the degree of **Doctor of Philosophy**

in the

Electronics and Nanoscale Engineering Division of

School of Engineering

Copyright © May 2023, Aniket Dhongde

The thesis is dedicated to my family and Dr. Babasaheb Ambedkar, who was a remarkable social reformer and the chief architect of the Indian Constitution.

## Abstract

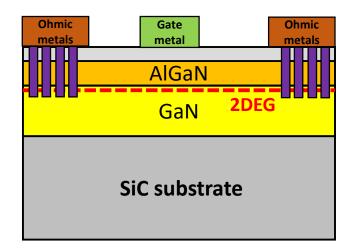

Gallium Nitride (GaN)-based High-Electron-Mobility Transistor (HEMT) technology is a breakthrough innovation in the semiconductor industry, offering high-frequency and high-power performance capabilities. GaN HEMTs are widely used in power electronics, wireless communication systems, and radar applications over the past two decades.

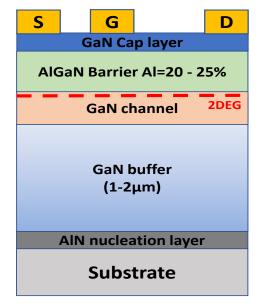

The key advantages of GaN HEMTs to produce heterojunctions to larger bandgap materials Aluminium Gallium Nitride (AlGaN) and the heterostructure results in the formation of the 2- dimensional electron gas (2DEG) which exhibits high electron mobilities of upto 2000 cm<sup>2</sup>/V.s and high saturation velocity of  $2 \times 10^7$  cm/s, resulting in high switching speeds and power densities. Due to its wide bandgap of 3.4 eV, it also allows exceptionally high breakdown fields of 3.3 MV/cm. In this thesis, the focus is on the major challenges in the development of GaN HEMT technology including achieving a low resistance ohmic contact, reducing self-heating, and improving device high frequency performance.

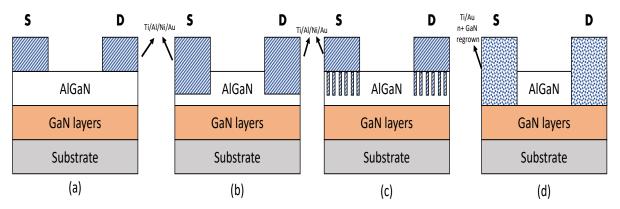

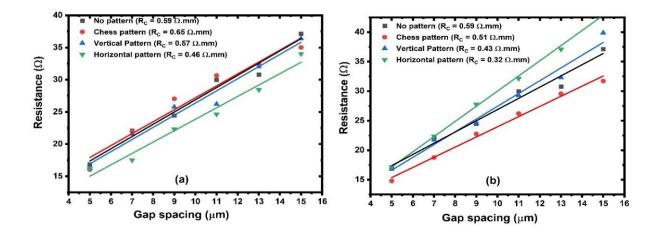

Due to the wide bandgap of III-nitride semiconductors, achieving low-resistance Ohmic contact resistance is difficult. Recessing the Ohmic region prior to metallization is a typical approach to lowering the contact resistance. The contact resistance is often minimised by optimising factors such as recess depth, anneal temperature, and metal stack design. In this work, the three approaches involving the recessing of the ohmic region were evaluated. The Ohmic contact area was recessed in patterns similar to a chess board, vertical recessed stripes, and horizontal recessed strips. The two different recess etch depths, shallow and deep etch depths of 9 nm and 30 nm, respectively, were investigate. The lowest contact resistance of  $0.32 \ \Omega$ .mm (compared to  $0.59 \ \Omega$ .mm for a conventional non-recessed Ohmic contact) was observed for a deep horizontal patterned structure. The results also indicate that a highly reproducible process.

The other major issue to address was to reduce the impact of device self-heating by effective heat distribution and dissipation. A novel thermal management technique was proposed, and the preliminary results are promising. It exploits the very thin epitaxial layer stack of a buffer-less GaN-on-SiC HEMT structure. III-V nitride material is etched and removed from around the active device area and the Au bond pad electrodes sit directly on the SiC substrate, providing a route for

thermal dissipation from the active device to the substrate. This approach was demonstrated to reduce device self-heating and to improve the current density of the device.

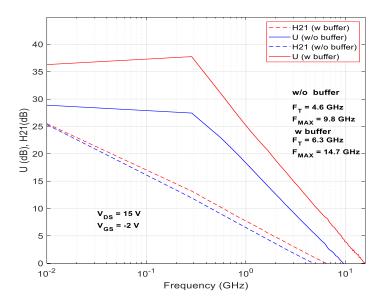

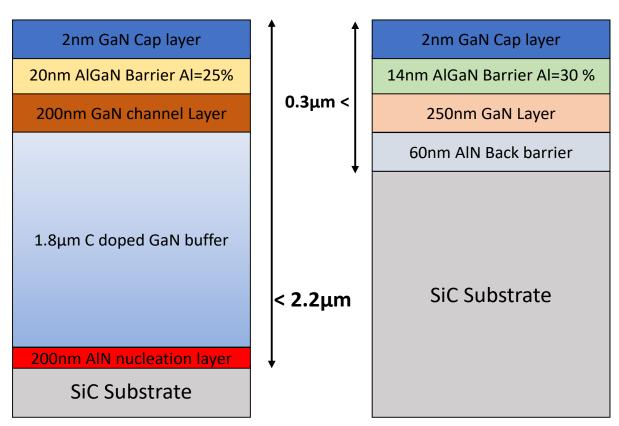

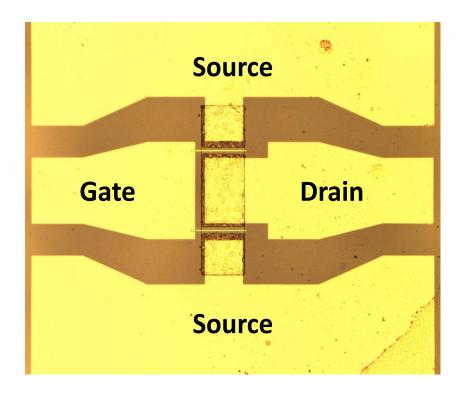

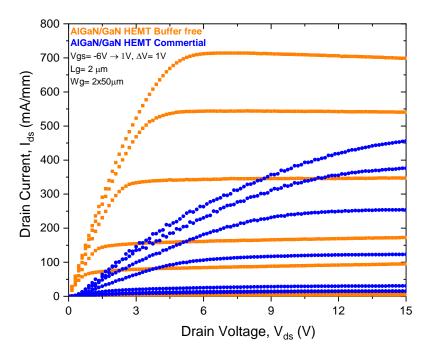

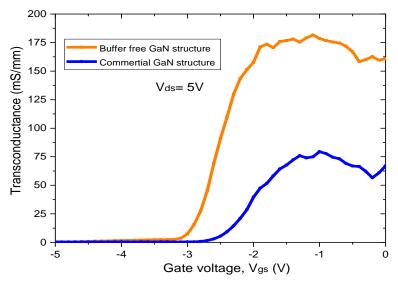

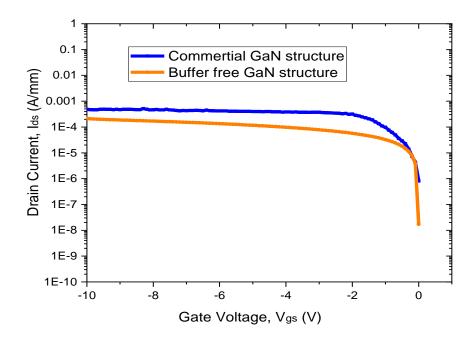

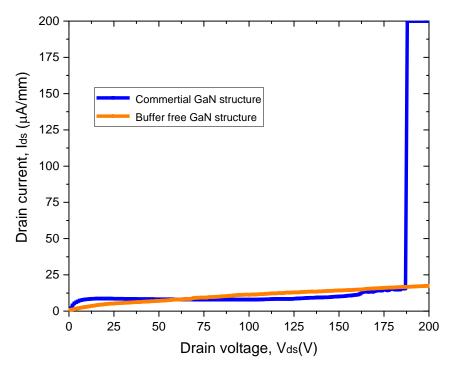

We fabricated and compared the performance of devices fabricated on the buffer-free and conventional GaN HEMTs. For identically sized 2- $\mu$ m gate long, two-finger 2 × 50  $\mu$ m gate width device with a gate to drain spacing of 3 µm, the conventional devices broke down at 186 V while for the buffer-free structure, it was over 200 V (above the measurement capability of our equipment). The maximum drain current density of  $\sim 631$  mA/mm and  $\sim 686$  mA/mm biased at  $V_{GS} = 1$  V for the two-finger 2  $\times$  50  $\mu$ m gate wide for buffer free and conventional GaN structure, respectively. The buffer free and conventional GaN structure devices were measured to determine their maximum cut-off frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$  when biased at  $V_{DS}$  = 15V. The lower gate leakage currents were observed for the fabricated buffer-free AlGaN/GaN HEMT device as compared to conventional GaN HEMTs 197µA and 260µA, respectively. Also, the buffer free device, which had two fingers each measuring 2x200 µm, yielded measurements of 4.6 GHz for f<sub>T</sub> and 9.8 GHz for f<sub>max</sub>. The conventional GaN device, also with two fingers each measuring  $2x200 \,\mu\text{m}$ , was tested and resulted in measurements of 6.3 GHz for  $f_T$ and 14.7 GHz for fmax. These results demonstrate the high quality of the buffer-free GaN heterostructure despite the absence of thick transition layers as currently used in the conventional GaN HEMTs. This indicates that the "buffer-free" design has the potential to be useful for millimetre wave applications in the future.

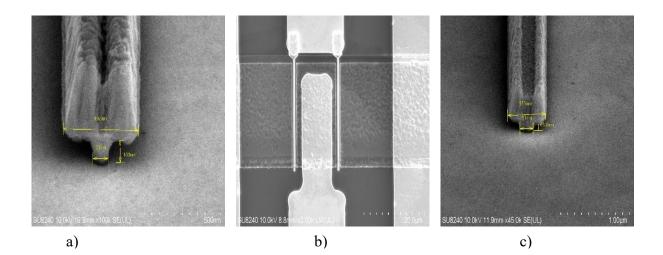

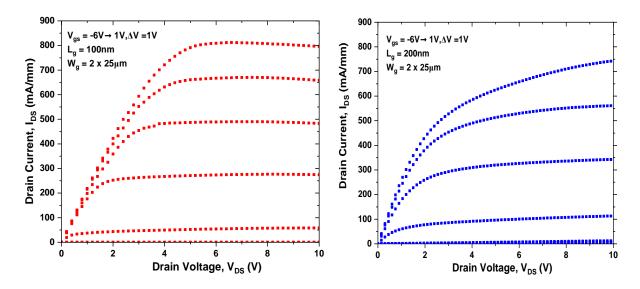

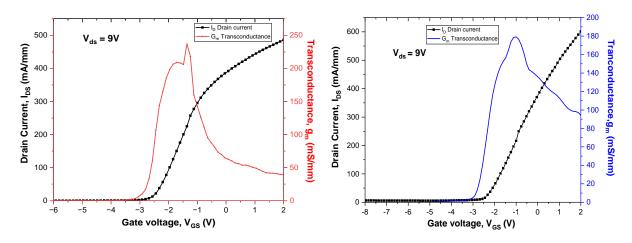

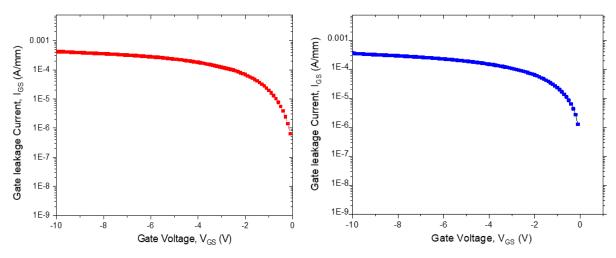

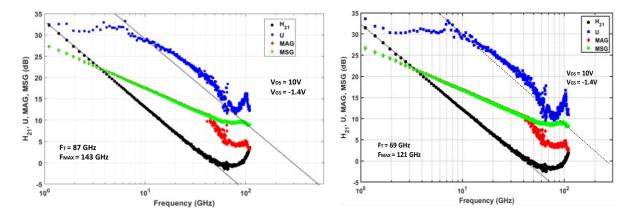

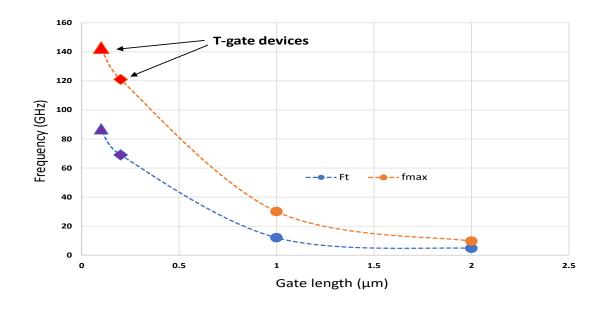

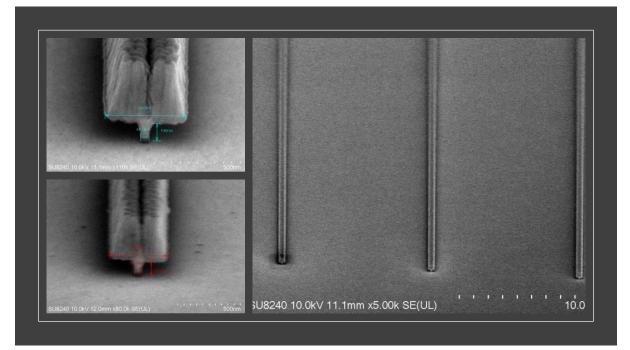

This thesis also describes the fabrication and characterisation of a 100 nm footprint Ni/Au-based T-gate HEMT,  $2x25 \mu m$  gate width, 1.5  $\mu m$  drain source spacing, 100nm Si<sub>3</sub>N<sub>4</sub> passivation layer thickness and device exhibit quite high peak currents of 805mA/mm and peak transconductance value of 246 mS/mm due to the low thermal boundary resistance on this buffer free epilayer wafer. The breakdown voltage was measured 47 Volts. Yielding a cut-off frequency  $f_T$  of 87 GHz and maximum oscillation frequency  $f_{max}$  of 143 GHz. We have developed a method for fabricating a T-shaped gate for sub 100nm gate foot length. The 100 nm length results in robustness, repeatable and has a high yield. Our findings indicate that this gate design could be beneficial for AlGaN/GaN buffer-free HEMTs used in millimetre wave frequency applications.

## Acknowledgements

First of all, I must express my sincere thanks to my supervisor, Dr Edward Wasige, who introduced me to the complex and beautiful world of semiconductors material. Now, I am more in love with semiconductor devices. This work could not have been initiated and completed in a short time without the constant support, encouragement, guidance, and selfless dedication from my supervisor. I am lucky to have you. I feel incredibly pleased and honoured to express my deep gratitude and indebtedness to Dr Chong li, who has helped me comprehensively understand high frequency device optimization and guidance. Thank you so much. The government of Maharashtra, India, funded the research outcome presented in this thesis. I sincerely thank the government of Maharashtra for providing financial support.

I would like to thank the James Watt Nanofabrication Centre (JWNC) staff for maintaining the facility in excellent condition, for instructing and guiding me as I used different fabrication equipment, and for the daily conversation.

Thanks to Dr Maira Elksne and Dr Sanna Taking for all the help in the cleanroom and outside, encouragement, fruitful discussion. Big thanks to Dr Afesomeh Ofiare for his continuous help with discussions, RF measurement system set up and all the help with measurements.

I would like to thank my group mates, office mates, lab mates and friends for encouragement, support, discussions, dinners, hugs and lunchtime fun. Big thanks to my friends Dr. Takshak Shande, Sachin Bahade, Kaivan Karami and Dr. Abdullah Al-Khalidi, for all the encouraging postcards that came from all around the world. Special thanks to Tania, Maira and Swagata for being there for me and of course, for all those sweets and chats.

Personally, this journey would not have been possible without my wife Shikha's generous love and support. Words are not enough to express it. And the biggest thanks to my little beautiful daughter Xiyana for choosing me to be her father and bringing us all the joy. Finally, I must thank my beloved parents, sister Neha and Samiksha, for their selfless love and motivation.

I am very thankful to every single person who has helped me through this journey.

# List of publications

- <u>Dhongde, A</u>. Ofiare, A., Karami, K. and Wasige, E. (2023) Buffer-Free GaN-on-SiC HEMTs with Bond Pad Heat Sinks. UK Semiconductors 2023, Sheffield, UK, 12-13 July 2023.

- <u>Dhongde, A.</u>, Taking, S., Karami, K., Elksne, M., Dwidar, M., Al-Khalidi, A. and Wasige, E. (2022) DC and RF Characteristics of Buffer-Free AlGaN/GaN HEMT and MIS-HEMTs Using Si<sub>3</sub>N<sub>4</sub> Passivated Mesa-Sidewall. In: International Conference on Electronic and Photonic Integrated Circuits (EPIC- 2022), Andhra Pradesh, India, 15-17 Dec 2022.

- <u>Dhongde, A.</u>, Elksne, M., Karami, K. and Wasige, E. (2022) Comparative Study of AlGaN/GaN HEMTs with and without the Buffer on SiC Substrates. UK Semiconductors 2022, Sheffield, UK, 6-7 July 2022.

- <u>Dhongde, A.</u>, Taking, S., Elksne, M., Ofiare, A., Karami, K., Dwidar, M., Al-Khalidi, A. and Wasige, E. (2022) High Performance of AlGaN/GaN HEMTs using Buffer-Free GaN on SiC Structure. 45th WOCSDICE Workshop on Compound Semiconductor Devices and Integrated Circuits, Ponta Delgada (São Miguel island Azores), Portugal, 3-6 May 2022.

- <u>Dhongde, A.</u>, Taking, S., Elksne, M., Samanta, S., Ofiare, A., Karami, K., Al-Khalidi, A. and Wasige, E. (2021) The role of selective pattern etching to improve the Ohmic contact resistance and device performance of AlGaN/GaN HEMTs. *International Journal of Nanoelectronics and Materials*, 14, pp. 21-28.

- Karami, K. <u>, Dhongde, A.</u>, Cheng, H., Reynolds, P. M., Thoms, S., Reddy, B. A., Ritter, D., Li, C. and Wasige, E. (2022) "Robust sub-100 nm T-gate fabrication process using multi-step development.", MNE EUROSENSORS 2022, Leuven, Belgium, 19-23 September 2022.

- Cheng, H., <u>Dhongde, A.</u>, Karami, K., Reynolds, P., Thoms, S., Wasige, E. and Li, C. (2022) Reliable T-gate Process for THz HEMTs. UK Semiconductors 2022, Sheffield, UK, 6-7 July 2022.

- Karami, K., Taking, S., Ofiare, A., Elksne, M., <u>Dhongde, A.</u>, Al-Khalidi,

A. and Wasige, E. (2022) Investigation of Al<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> Used for Surface

Passivation and Gate Dielectric on AlGaN/GaN Metal-Oxide-Semiconductor High Electron Mobility Transistors. WOCSDICE EXMATEC 2022, Ponta Delgada (São Miguel island–Azores), 3-6 May 2022.

- Karami, K., Hassan, S., Taking, S., Ofiare, <u>A.</u>, <u>Dhongde</u>, A., Al-Khalidi, A. and Wasige,

E. (2023) Comparative Study of Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> as gate dielectric on AlGaN/GaN MOSHEMTs. *International Journal of Electronics and Communication Engineering*, 17(2), pp. 47-50.

- Ofiare, A., Taking, S., Karami, K., <u>Dhongde, A.</u>, Al-Khalidi, A. and Wasige, E. (2021) Investigation of plasma induced etch damage/changes in AlGaN/GaN HEMTs. *International Journal of Nanoelectronics and Materials*, 14, pp. 29-36.

- Karami, K., Taking, S., <u>Dhongde, A</u>., Ofiare, A., Al-Khalidi, A. and Wasige, E. (2021) Heavily doped n++ GaN cap layer AlN/GaN metal oxide semiconductor high electron mobility transistor. *International Journal of Nanoelectronics and Materials*, 14, pp. 45-51.

- Karami, K., Taking, S., Ofiare, <u>A., Dhongde</u>, A., Al-Khalidi, A. and Wasige, E. (2021) High performance of n++GaN/AlN/GaN high electron mobility transistor. 44th Workshop on Compound Semiconductor Devices and Integrated Circuits held in Europe (WOCSDICE), Bristol, UK, 14-17 June 2021.

| Abstract   | t                   |                                                   | i     |  |

|------------|---------------------|---------------------------------------------------|-------|--|

| Acknow     | Acknowledgementsiii |                                                   |       |  |

| List of p  | ublic               | ations                                            | iv    |  |

| List of F  | igure               | S                                                 | ix    |  |

| List of Ta | able .              |                                                   | xv    |  |

| Definitio  | ons                 |                                                   | kviii |  |

| 1 Intr     | oduc                | tion                                              | 2     |  |

| 1.1        | Ove                 | rview                                             | 2     |  |

| 1.2        | GaN                 | I Applications                                    | 5     |  |

| 1.3        | Res                 | earch challenges                                  | 5     |  |

| 1.3        | .1                  | Ohmic contacts to AlGaN/GaN HEMTs                 | 5     |  |

| 1.3        | .2                  | Self-heating                                      | 7     |  |

| 1.3        | .3                  | Thermal Boundary Resistance                       | 8     |  |

| 1.4        | Res                 | earch aim                                         | 9     |  |

| 1.5        | The                 | sis structure                                     | 9     |  |

| 2 Gal      |                     | VIT Basic Theory                                  | . 12  |  |

| 2.1        | Intr                | oduction                                          | . 12  |  |

| 2.2        | III-N               | litride crystal structure                         | . 12  |  |

| 2.3        | Pola                | arization in III-N semiconductors                 | . 13  |  |

| 2.3        | .1                  | Spontaneous Polarization                          | . 13  |  |

| 2.3        | .2                  | Piezoelectric Polarization                        | . 14  |  |

| 2.3        | .3                  | 2-Dimension electron gas (2DEG) formation         | . 15  |  |

| 2.4        | GaN                 | I HEMT device structure                           | . 17  |  |

| 2.4        | .1                  | Substrate                                         | . 17  |  |

| 2.5        | GaN                 | I-based HEMT epitaxial layer structure            | . 19  |  |

| 2.6        | Dep                 | eletion mode GaN HEMT device: operation principle | . 20  |  |

| 2.7        | Enh                 | ancement mode GaN HEMTs                           | . 24  |  |

| 2.8        | HEN                 | /IT RF Behaviour                                  | . 25  |  |

| 2.8        | .1                  | Small signal Equivalent Circuit Model             | . 28  |  |

| 2.9        | Sum                 | nmary                                             | . 29  |  |

| 3 Gal      |                     | MT Device Fabrication Techniques                  | . 31  |  |

#### Table of Contents

|   | 3.1  |       | oduction                                  |    |

|---|------|-------|-------------------------------------------|----|

|   | 3.2  | -     | axial material growth                     |    |

|   | 3.2. |       | Metal Organic Chemical Vapor Deposition   |    |

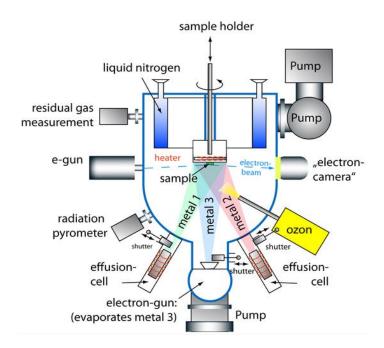

|   | 3.2. | _     | Molecular beam epitaxy (MBE)              |    |

|   | 3.3  |       | ography                                   |    |

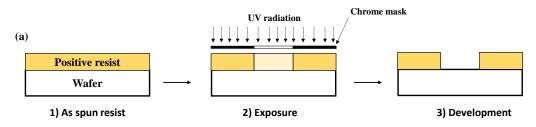

|   | 3.3. |       | Photolithography                          |    |

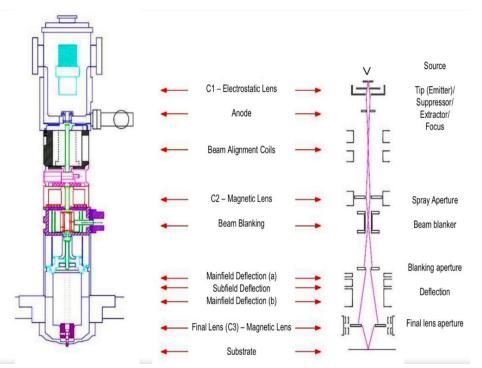

|   | 3.3. | 2     | Electron beam lithography                 |    |

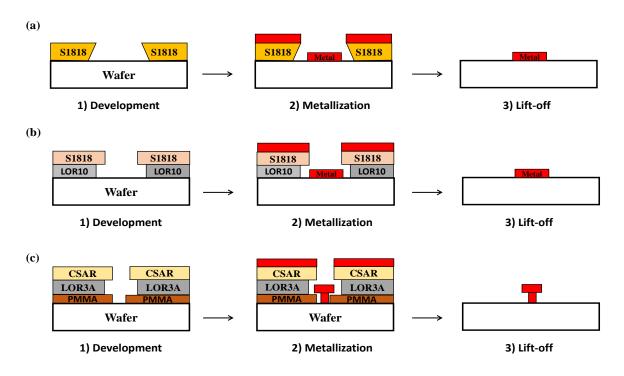

|   | 3.3. | 3     | Photoresists                              | 37 |

|   | 3.4  | Met   | tallization                               | 38 |

|   | 3.4. |       | Electron beam metal evaporation           |    |

|   | 3.5  |       | nealing                                   |    |

|   | 3.6  |       | ning                                      |    |

|   | 3.6. | 1     | Wet etching                               |    |

|   | 3.6. | 2     | Dry etching                               | 41 |

|   | 3.7  |       | lectric material deposition               |    |

|   | 3.8  | 0     | ate fabrication                           |    |

|   | 3.9  |       | ٨T fabrication process flow               |    |

|   | 3.9. |       | Mask plate design                         |    |

|   | 3.9. |       | Mesa isolation                            |    |

|   | 3.9. | 3     | DC and RF devices                         | 49 |

|   | 3.9. | 4     | Gate metallisation                        | 50 |

|   | 3.9. | 5     | Bondpad metallisation                     | 50 |

|   | 3.10 | Sum   | nmary                                     | 50 |

| 4 | Ohr  | nic C | Contacts in GaN HEMTs                     | 52 |

|   | 4.1  | Intr  | oduction                                  | 52 |

|   | 4.2  | Met   | tal-semiconductor Contact                 |    |

|   | 4.2. | 1     | Schottky Gate contact                     | 55 |

|   | 4.2. | 2     | Ohmic contact formation                   | 55 |

|   | 4.3  | Trar  | nsmission line model                      | 56 |

|   | 4.3. | 1     | Linear Transmission Line Model (LTLM)     | 56 |

|   | 4.3. | 2     | Circular Transmission Line Model (CTLM)   | 58 |

|   | 4.4  | Lite  | rature review on GaN based Ohmic contacts | 59 |

|   | 4.5  | Fab   | rication and evaluation of patterned Ohmic contacts                  | 61  |

|---|------|-------|----------------------------------------------------------------------|-----|

|   | 4.5. | 1     | Patterned TLMs and device fabrication.                               | 61  |

|   | 4.5. | 2     | Experimental results and discussion                                  | 64  |

|   | 4.6  | Cor   | nclusion                                                             | 67  |

| 5 | Con  | npar  | ative study of buffer thickness in AlGaN/GaN HEMTs on SiC substrates | 69  |

|   | 5.1  | Intr  | oduction                                                             | 69  |

|   | 5.1. | 1     | Buffer-free GaN heterostructure                                      | 71  |

|   | 5.2  | Ехр   | erimental results                                                    | 72  |

|   | 5.2. | 1     | Device structure and fabrication                                     | 72  |

|   | 5.2. | 2     | Result and discussion                                                | 74  |

|   | 5.3  | Cor   | nventional and buffer-free MOCVD-grown GaN HEMTs                     | 80  |

|   | 5.3. | 1     | Device measurement results                                           | 81  |

|   | 5.4  | Cor   | nclusion                                                             | 84  |

| 6 | The  | rma   | lly Efficient GaN HEMT Devices                                       | 86  |

|   | 6.1  | Intr  | oduction                                                             | 86  |

|   | 6.2  | The   | ermal management of GaN HEMTs                                        | 86  |

|   | 6.3  | Rev   | view of thermal management techniques for GaN HEMTs                  | 89  |

|   | 6.4  | Р     | roposed thermally efficient GaN-on-SiC HEMT device                   | 92  |

|   | 6.4. | 1     | Experimental results                                                 | 94  |

|   | 6.4. | 2     | Mesa-passivated thermally-efficient GaN MIS-HEMTs                    | 99  |

|   | 6.5  | Cor   | nclusion                                                             | 106 |

| 7 | Higl | h Fre | equency GaN HEMT Devices                                             | 108 |

|   | 7.1  | Intr  | oduction                                                             | 108 |

|   | 7.2  | Stat  | te of the art                                                        | 108 |

|   | 7.3  | Gal   | N HEMT devices with T-gates                                          | 114 |

|   | 7.3. | 1     | The importance and fabrication of T-gates                            | 114 |

|   | 7.3. | 2     | RF measurements                                                      | 119 |

|   | 7.4  | Sun   | nmary                                                                | 120 |

| 8 | Con  | lus   | ions and Future work                                                 | 122 |

|   | 8.1  | Cor   | nclusion                                                             | 122 |

|   | 8.1. | 1     | Ohmic contacts to AlGaN/GaN HEMTs                                    | 122 |

|   | 8.1. | 2     | Thermal management on AlGaN/GaN HEMTs                                | 122 |

| 8.1.     | 3    | T-Gate fabrication                          | 123 |

|----------|------|---------------------------------------------|-----|

| 8.2      | Futu | ire work                                    | 123 |

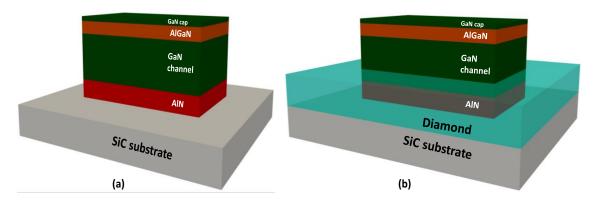

| 8.2.     | 1    | Proposed GaN/diamond-on-SiC                 | 123 |

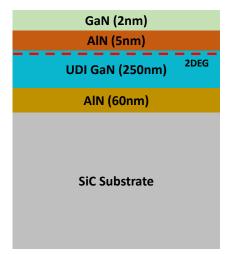

| 8.2.2    | 2    | Proposed buffer-free AIN/GaN HEMT structure | 124 |

| Appendi  | ix A |                                             | 125 |

| Referenc | ces  |                                             | 130 |

# **List of Figures**

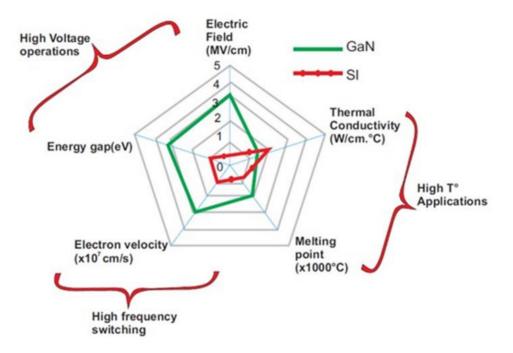

| Figure 1.1: A summary of the important properties of Si and GaN                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

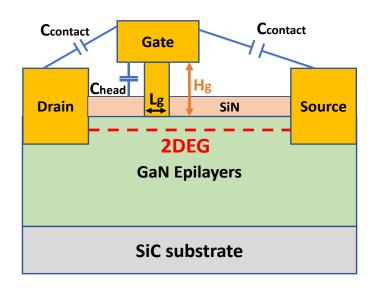

| Figure 1.2: Cross section of typical GaN HEMT device                                                                                                                                                          |

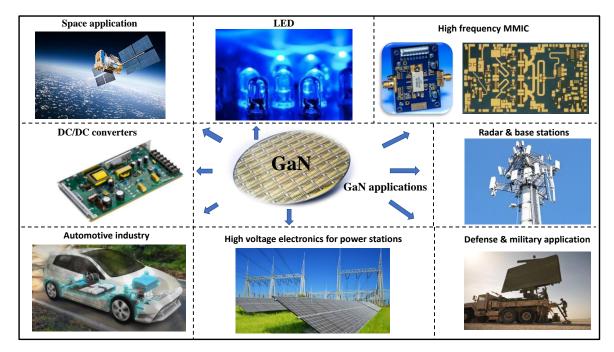

| Figure 1.3 : Applications of GaN technology5                                                                                                                                                                  |

| Figure 1.4: Ohmic contacts for AlGaN/GaN HEMTs (a) planar Ohmic contact (b) recess Ohmic contact (c) patterned Ohmic contact (d) regrown Ohmic contact                                                        |

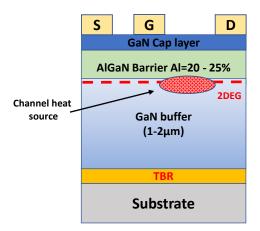

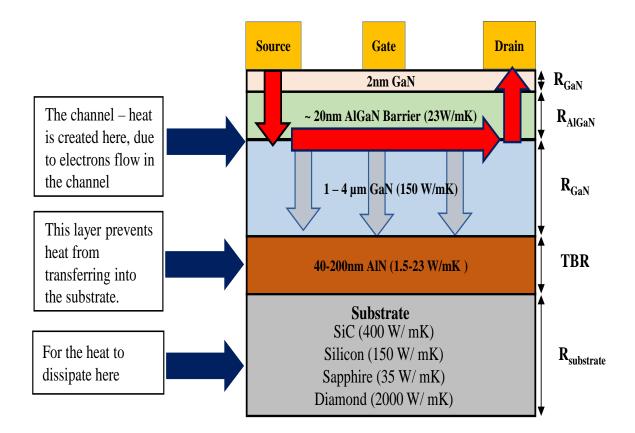

| Figure 1.5: Illustration of the standard AlGaN/GaN HEMT the channel heat source and TBR 8                                                                                                                     |

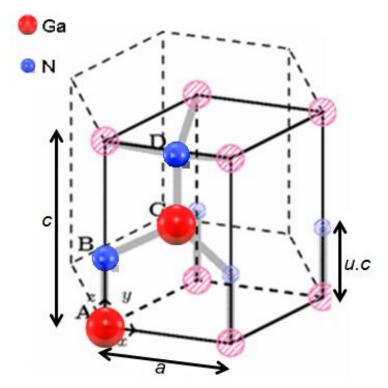

| Figure 2.1: Hexagonal Wurtzite structure13                                                                                                                                                                    |

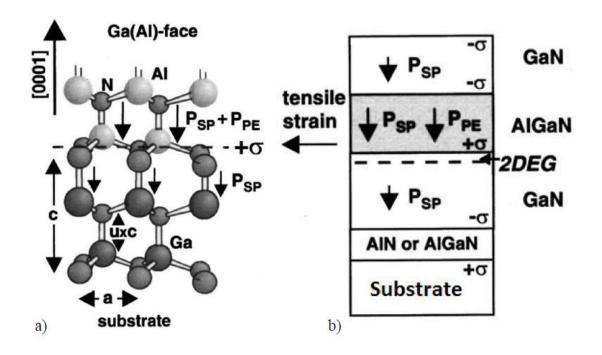

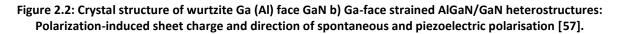

| Figure 2.2: Crystal structure of wurtzite Ga (Al) face GaN b) Ga-face strained AlGaN/GaN heterostructures: Polarization-induced sheet charge and direction of spontaneous and piezoelectric polarisation [57] |

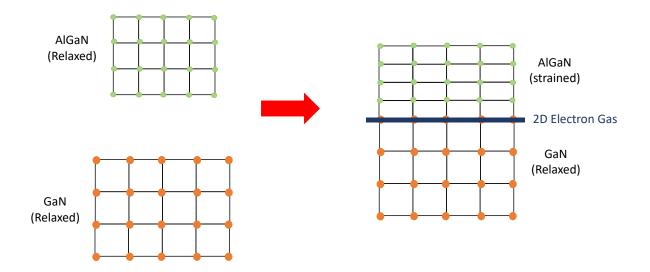

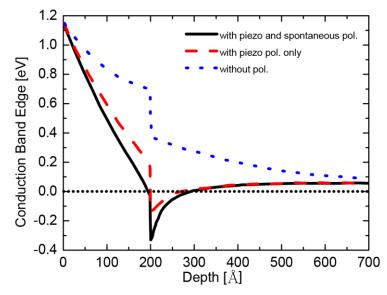

| Figure 2.3: Illustration of how AlGaN is strained during the formation of 2DEG on GaN                                                                                                                         |

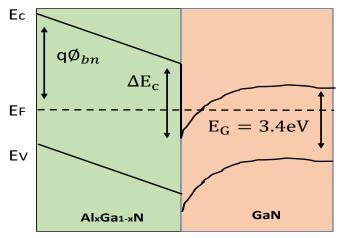

| Figure 2.4: AlGaN/GaN energy band diagram illustrating the impacts of PSP and PPE on the conduction band [60]                                                                                                 |

| Figure 2.5: AlxGa1-xN/GaN heterostructure's band structure demonstrating 2DEG development at the heterojunction as a result of quantum well formation [60]                                                    |

| Figure 2.6: Cross section of HEMT device structure                                                                                                                                                            |

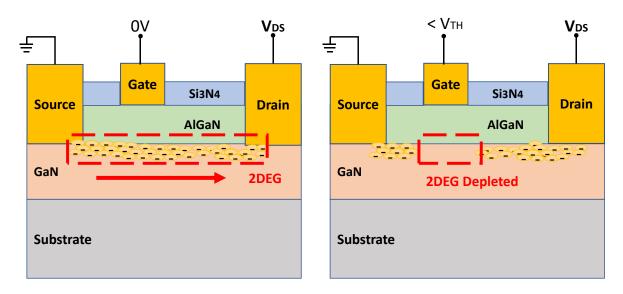

| Figure 2.7: Illustration of a HEMT operation principle and biasing (a) ON-state and (b) OFF-state with an AlGaN/GaN heterostructure and $Si_3N_4$ passivation                                                 |

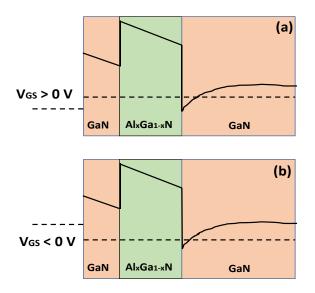

| Figure 2.8: Gate voltage effects on the energy band structure: a) $V_{GS} > V_{TH}$ and b) $V_{GS} < V_{TH}$ 22                                                                                               |

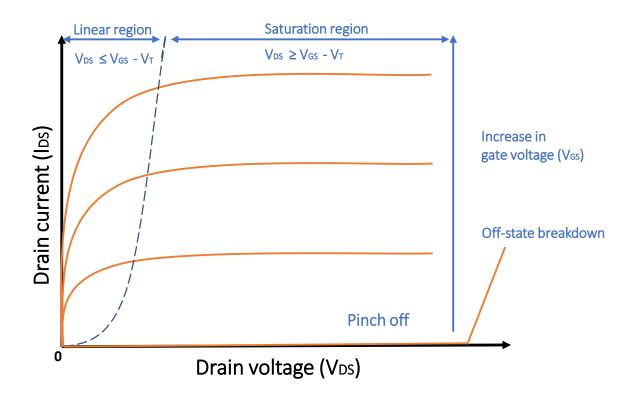

| Figure 2.9: Output DC- IV characteristic of a typical GaN HEMT                                                                                                                                                |

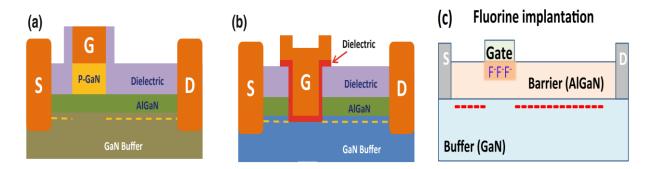

| Figure 2.10 Illustration of the three types of e-mode GaN HEMTs a) with p doped layer under the gate, b) deep recessed gate with insulator under the gate and c) fluoride treated region under the gate [76]                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

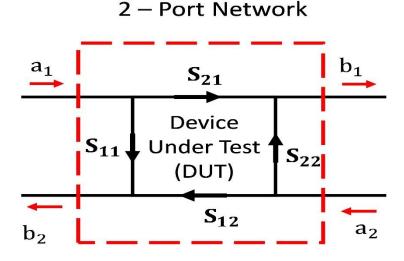

| Figure 2.11: Diagram of the two-port idea for device characterisation                                                                                                                                                                                                                                                                                                                                                                  |

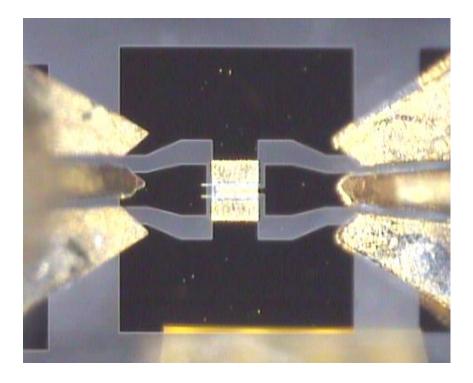

| Figure 2.12: Micrograph of a fabricated GaN HEMT with landed RF ground-signal-ground probes on device RF ports                                                                                                                                                                                                                                                                                                                         |

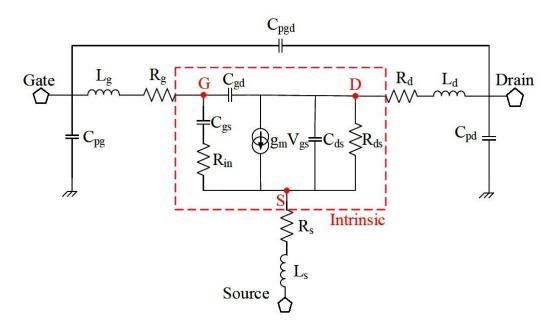

| Figure 2.13: Small-signal equivalent circuit model of HEMT                                                                                                                                                                                                                                                                                                                                                                             |

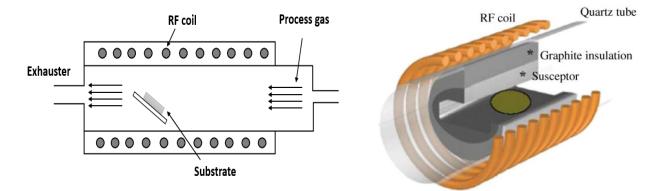

| Figure 3.1: Schematic illustrations (a) MOCVD growth chamber (b) In the hot-wall MOCVD growth chamber setup, the substrate is placed in the hot zone. Before entering the growth chamber, all precursors (TMAI/TMGa+NH3) and carrier gases (H2/N2) are mixed together                                                                                                                                                                  |

| Figure 3.2: Schematic illustration of an MBE growth chamber                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 3.3: Photo of the Karl Suss Mask Aligner (MA6)                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 3.4: Photo of the electron beam lithography tool Raith EBPG5200 HS                                                                                                                                                                                                                                                                                                                                                              |

| Figure 3.5: Schematic illustration of the column of an electron beam lithography tool                                                                                                                                                                                                                                                                                                                                                  |

| Figure 3.6: Positive photoresist spinning, exposure and development                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 3.7: The metal lift-off process flow using (a) a single layer photoresist (b) a bi-layer od photoresist (c) a tri-layer of photoresist                                                                                                                                                                                                                                                                                          |

| Figure 3.8: Image of the Plassys IV metal evaporation tool 40                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.9: Photo of the Jipelec JetFirst 200 rapid thermal annealing (RTA) machine                                                                                                                                                                                                                                                                                                                                                    |

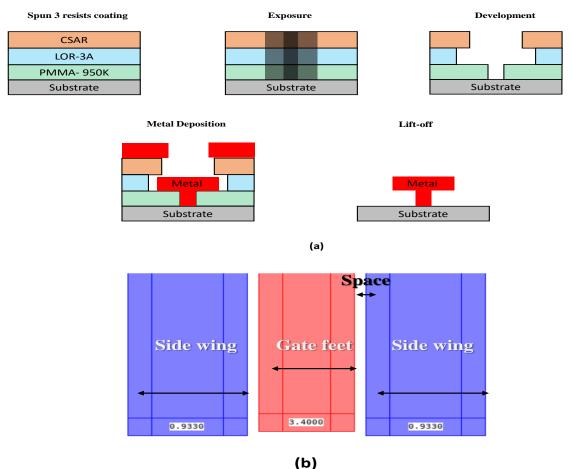

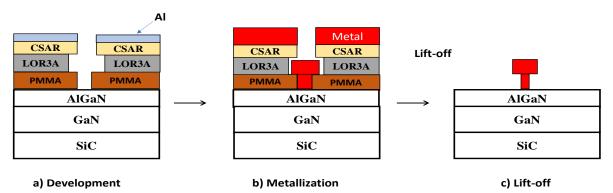

| Figure 3.10: Schematic of the process flow for the fabrication of T shape gate using tri-layer (a) and (b) exposed gate region                                                                                                                                                                                                                                                                                                         |

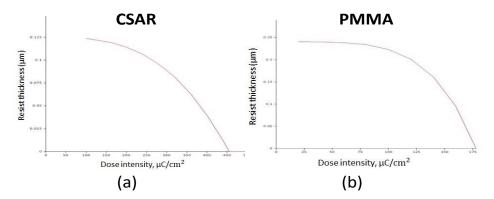

| Figure 3.11: The measured beam spread effect by forward scattering in the top CSAR (a) and PMMA-950K (b) at 100 keV. The layer structure is 120 and 250 nm thick PMMA and CSAR, respectively                                                                                                                                                                                                                                           |

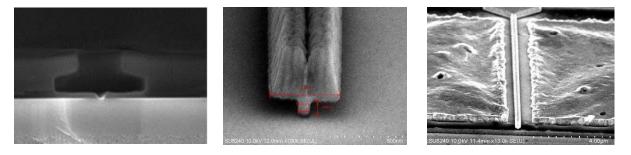

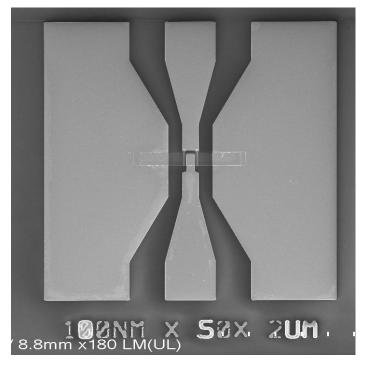

| Figure 3.12: SEM images of the developed three-layer photoresist profile of the T gate (a), the T-<br>gate, image after metallization on SiC (b) and T-gate in between source and drain on SiC substrate<br>(c)                                                                                                                                                                                                                        |

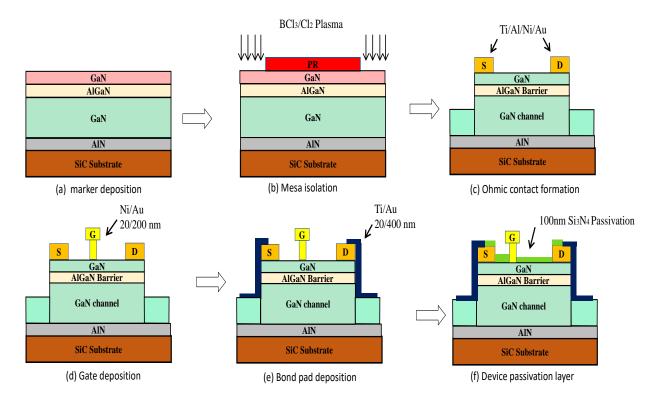

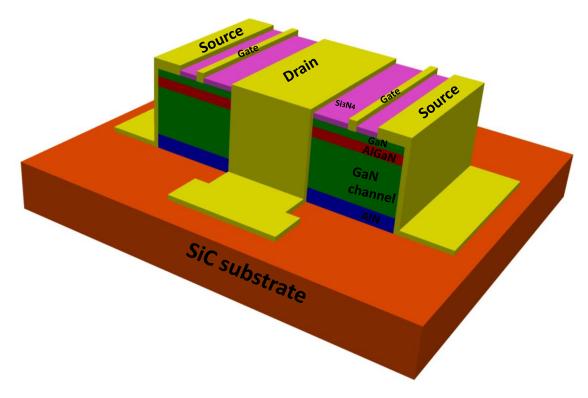

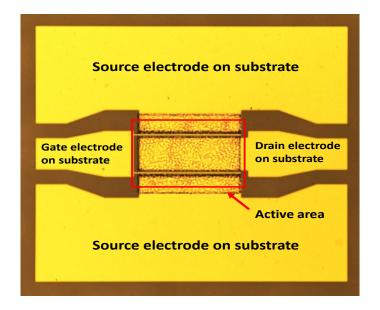

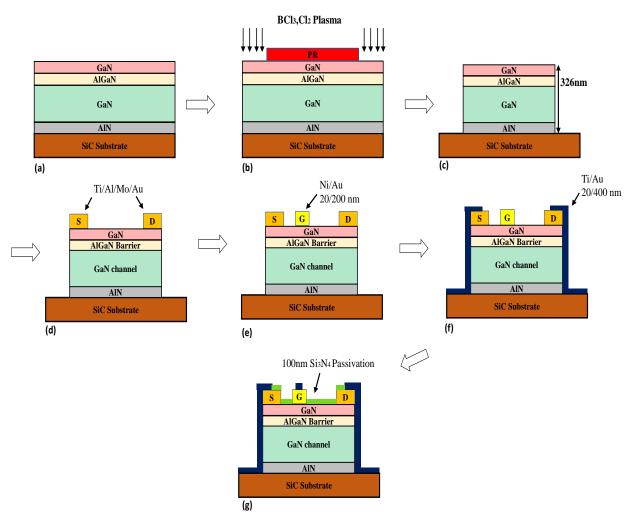

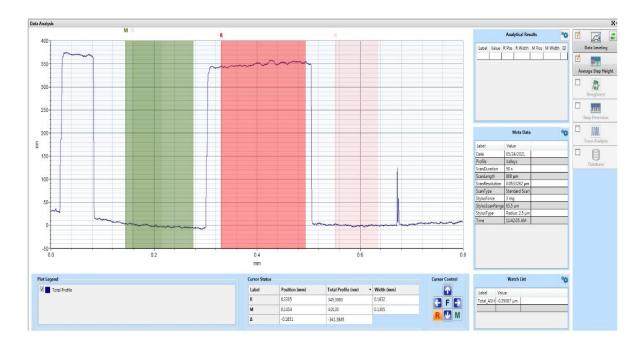

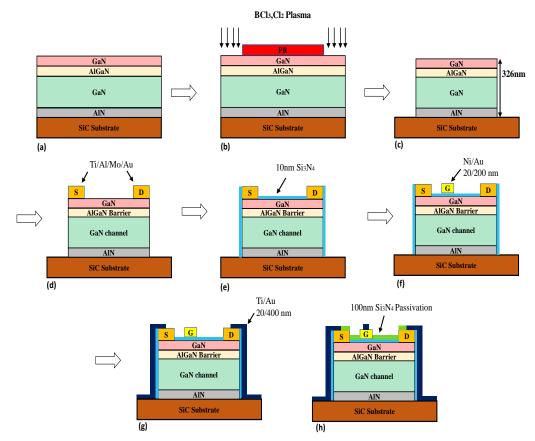

| Figure 3.13: Schematic views of the process flow for to substrate fabrication in AlGaN/GaN HEMT device processing steps (a)Clean wafer; markers (b) Photolithography and deep mesa-etch pattern using BCl <sub>3</sub> /Cl <sub>2</sub> plasma (c) Deposition of Ti/Al/Ni/Au metal stack Ohmic contacts (d) Ni/Au based gate metallization (e) Bond pads contacts (f) Device passivation using 100nm Si <sub>3</sub> N <sub>4</sub> 46 |

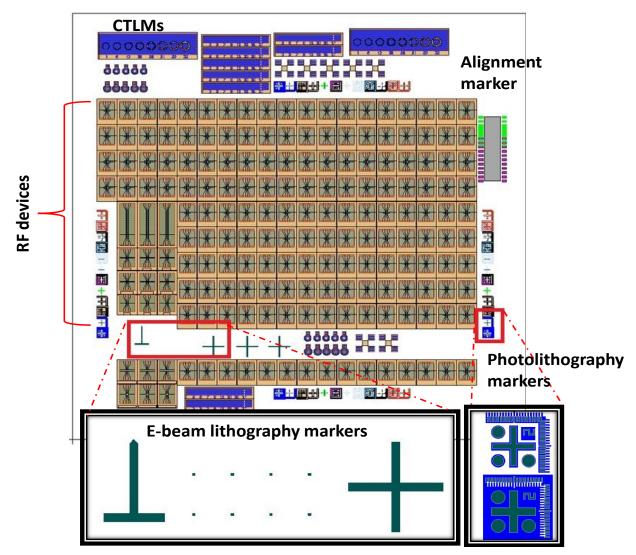

| Figure 3.14: Screenshot of layout of a design in L-edit                                                                                                                                                                                                                                                                                                                                                                                |

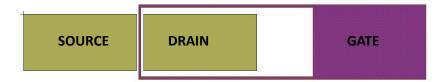

| Figure 3.15: Layout design of a DC device                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 3.16: Layout of fabricated design of a RF device                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

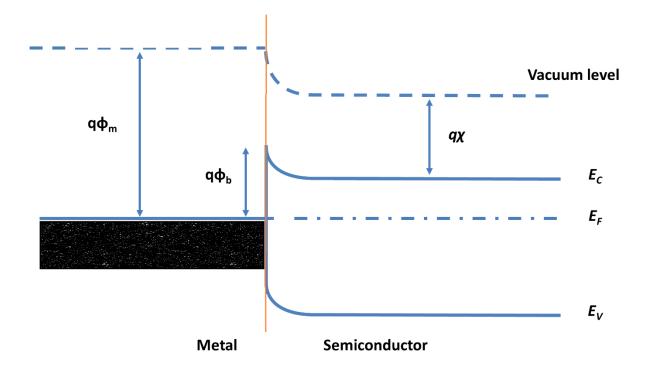

| Figure 4.1: Energy band diagram for a metal (n-type) semiconductor contact in thermal equilibrium                                                                                                                            |

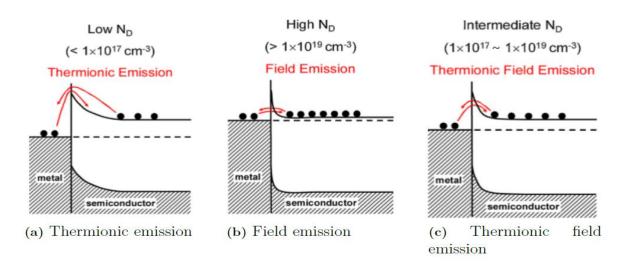

| Figure 4.2: The three types of carrier transport mechanism at metal and semiconductor, a) thermionic emission, b) Field emission and c) Thermionic field emission [101]                                                      |

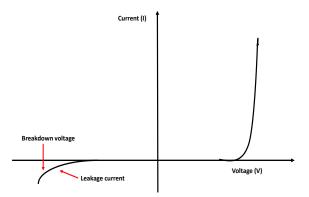

| Figure 4.3: IV characteristics for a Schottky gate contact                                                                                                                                                                   |

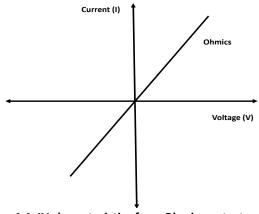

| Figure 4.4: IV characteristics for a Ohmic contact                                                                                                                                                                           |

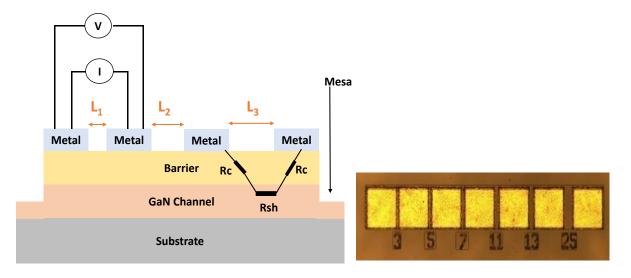

| Figure 4.5: (a) A semiconductor material with Ohmic contact pads for LTLM characterization (b) LTLM on after annealed                                                                                                        |

| Figure 4.6: An illustration of a plot of total resistance measurements versus various gap spacing                                                                                                                            |

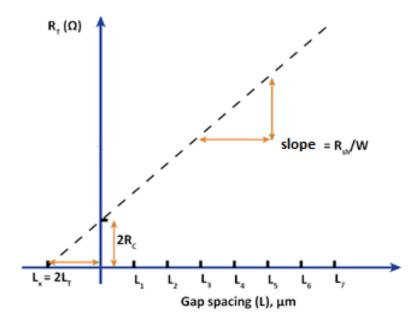

| Figure 4.7: Current flow in LTLM structures (a) non-isolated and (b) isolated                                                                                                                                                |

| Figure 4.8: Illustration of Reeves concentric circular contacts                                                                                                                                                              |

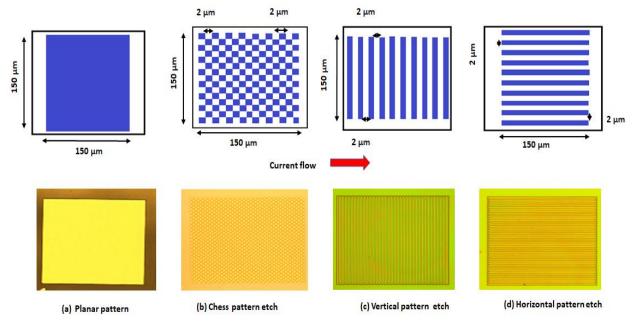

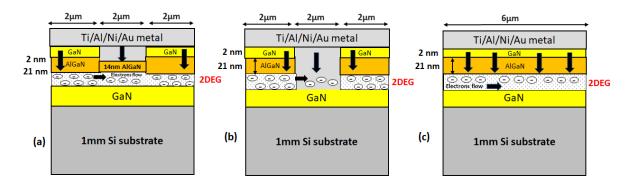

| Figure 4.9: Top-view illustrations of the patterned surface of Ohmic contact using (a) conventional or planar (b) chess pattern etch (c) vertical pattern etch, and (d) horizontal pattern etch of AlGaN/GaN HEMT structures |

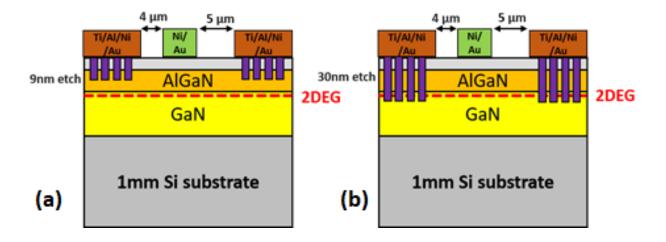

| Figure 4.10: The cross-section schematic illustration of the fabricated AlGaN/GaN HEMT structures with (a) shallow (~ 9 nm of etch depth) (b) deep (~ 30 nm of etch depth) Ohmic recess etching                              |

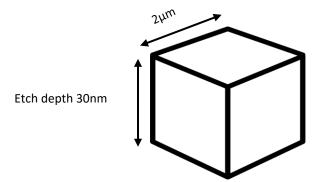

| Figure 4.11: The single etches chess pattern area                                                                                                                                                                            |

| Figure 4.12: Measured contact resistances, R <sub>c</sub> , of (a) shallow and (b) deep Ohmic recess etching on 4 different TLM pattern structures                                                                           |

| Figure 4.13. The cross-section schematic illustration of (a) shallow patterned etching (b) deep patterned etching (c) conventional or planar structure of Ohmic metal contact to AlGaN/GaN HEMT structures                   |

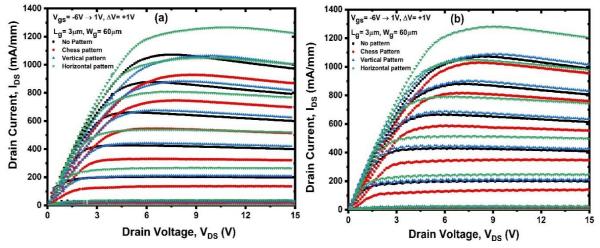

| Figure 4.14: The measured output characteristics of the fabricated AlGaN/GaN HEMTs with a (a) shallow (b) deep patterned etching of 4 different TLM structure                                                                |

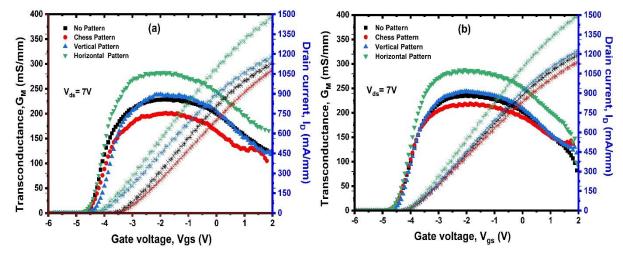

| Figure 4.15. The measured transconductance of the fabricated AlGaN/GaN HEMTs with (a) shallow Ohmic recess etching (b) deep Ohmic recess etching with 4 different TLM pattern structures                                     |

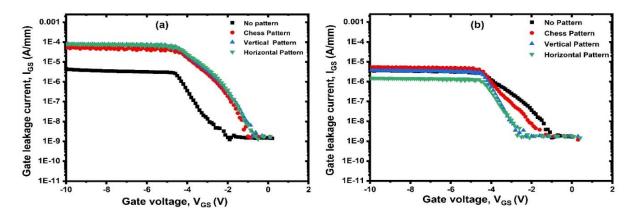

| Figure 4.16: The gate leakage current characteristics of the fabricated AlGaN/GaN HEMTs with a (a) shallow Ohmic recess etching (b) deep Ohmic recess etching with 4 different TLM pattern structures                        |

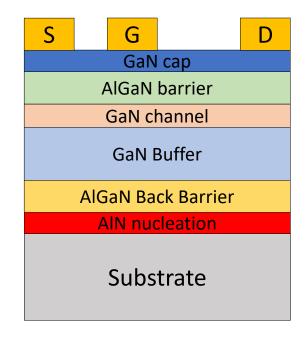

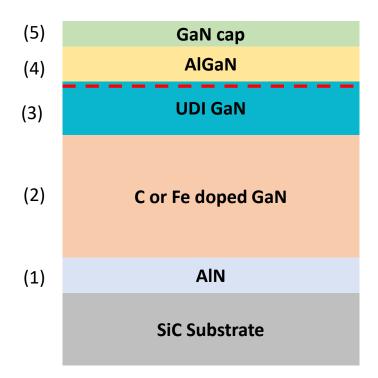

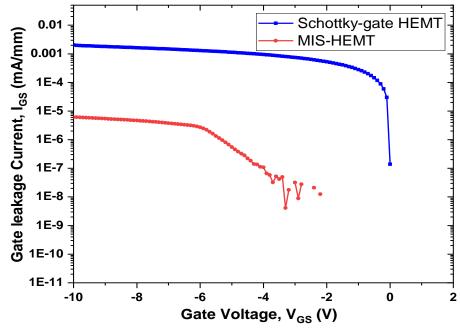

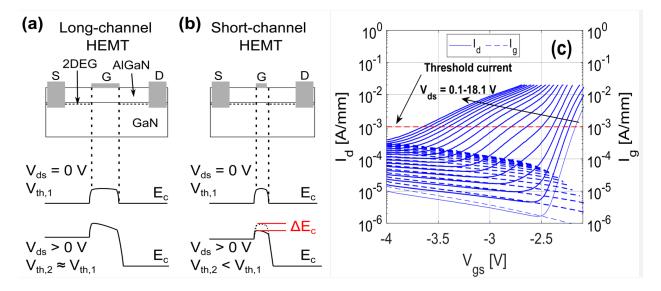

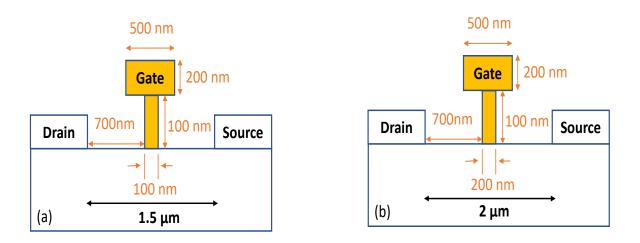

| buffer layer.    71      Figure 5.2: A buffer-less AlGaN/GaN heterostructure.    72      Figure 5.3: Epitaxial wafer structure of fabricated AlGaN/GaN heterostructure devices using (a) a thick GaN layer and (b) a buffer-free (c) Micrograph of fabricated 200µm wide device.    74      Figure 5.4: Measured contact resistance versus gap spacing of thick GaN buffer and buffer-free GaN wafers.    75      Figure 5.5: The los-Vos characteristics for 50 and 200 µm wide devices on buffer-free GaN wafer.    75      Figure 5.7: The los-Vos characteristics for 50 and 200 µm wide devices on buffer-free GaN wafer.    76      Figure 5.7: The los-Vos characteristics of 2 x 50 µm wide devices at V <sub>GS</sub> = 0V to -5V and V <sub>DS</sub> up to 40V on buffer free wafer and thick GaN buffer wafer.    76      Figure 5.8: Measured transfer characteristics of (a) buffer-free (b) thick GaN buffer devices biased at V <sub>DS</sub> = 5 V.    77      Figure 5.9: Measured gate leakage currents of (a) buffer-free (b) thick GaN buffer devices with a 2-µm gate long, two-finger 2 x 50 µm wide biased at V <sub>DS</sub> = 0 V.    78      Figure 5.11: Measured H21 and Maximum signal gain for 2x200µm device sizes for buffer and buffer free devices.    79      Figure 5.12: Standard GaN-on-SiC epitaxial layer wafer structures for comparison in terms of the device thermal performance.    80      Figure 5.13: Micrograph of the fabricated 2×50 µm wide devices on Wafer 1 (commercial) and wafer 2 (buffer free) devices.    82      Figure 5.14: Ios-Vos characteristics for 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 5.1: A conventional AlGaN/GaN heterostructure with a significant C or Fe doping in the                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

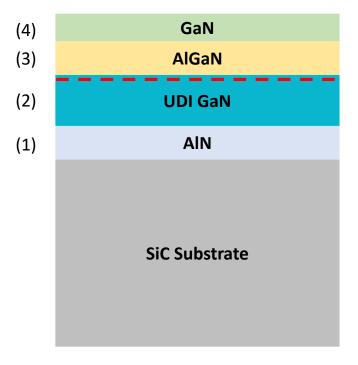

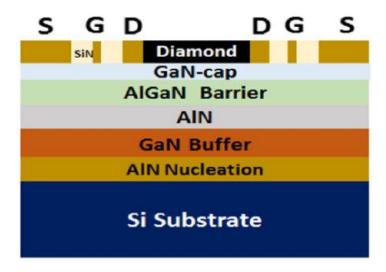

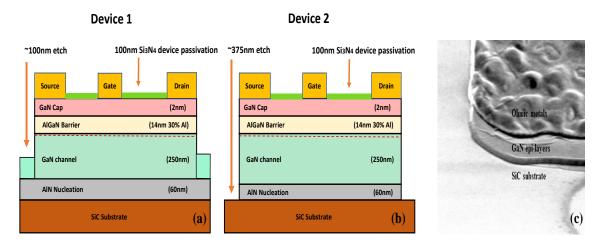

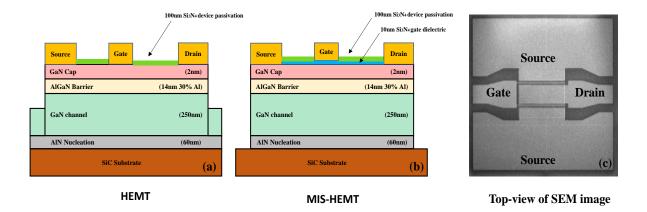

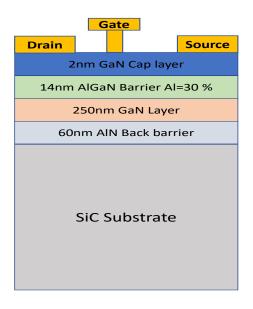

| Figure 5.3: Epitaxial wafer structure of fabricated AlGaN/GaN heterostructure devices using (a) a thick GaN layer and (b) a buffer-free (c) Micrograph of fabricated 200µm wide device.    74      Figure 5.4: Measured contact resistance versus gap spacing of thick GaN buffer and buffer-free GaN wafers.    75      Figure 5.5: The los-Vos characteristics for 50 and 200 µm wide devices on buffer-free GaN wafer.    75      Figure 5.6: The los-Vos characteristics for 50 and 200 µm wide devices on thick- GaN buffer wafer.    76      Figure 5.7: The los-Vos characteristics of 2 x 50 µm wide devices at V <sub>GS</sub> = 0V to -5V and V <sub>DS</sub> up to 40V on buffer free wafer and thick GaN buffer wafer.    76      Figure 5.8: Measured transfer characteristics of (a) buffer-free (b) thick GaN buffer devices biased at V <sub>DS</sub> = 5 V.    77      Figure 5.9: Measured gate leakage currents of (a) buffer-free (b) thick GaN buffer devices with a 2-µm gate long, two-finger 2 x 50 µm wide biased at V <sub>DS</sub> = 0 V.    78      Figure 5.11: Measured off-state breakdown voltage of (a) buffer-free (b) thick GaN buffer devices with a 2-µm gate long, two-finger 2 x 50 µm wide biased at V <sub>DS</sub> = -10 V.    78      Figure 5.11: Measured H21 and Maximum signal gain for 2x200µm device sizes for buffer and buffer free devices.    79      Figure 5.13: Micrograph of the fabricated 2×50 µm wide devices with gate-length of 2 µm.    81      Figure 5.14: Ios-Vos characteristics for 50 µm wide devices on Wafer 1 (commercial) and 2 (buffer-free from SweGaN).    82      Figure 5.16: Gate leakage comp                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

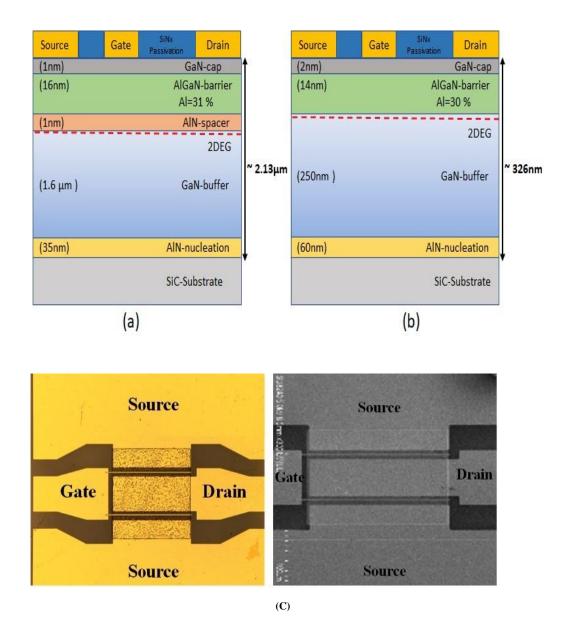

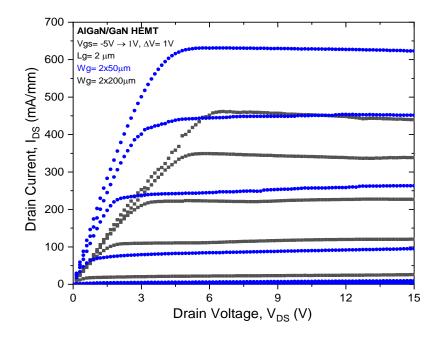

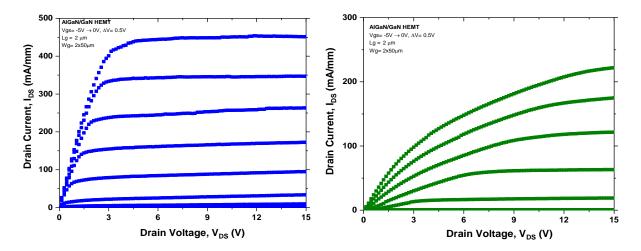

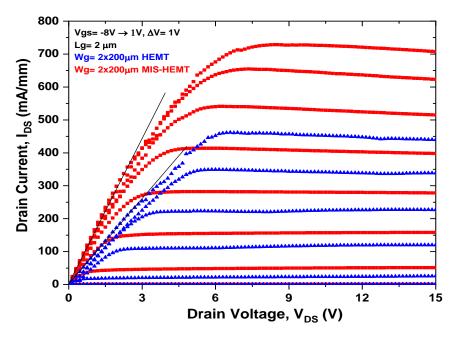

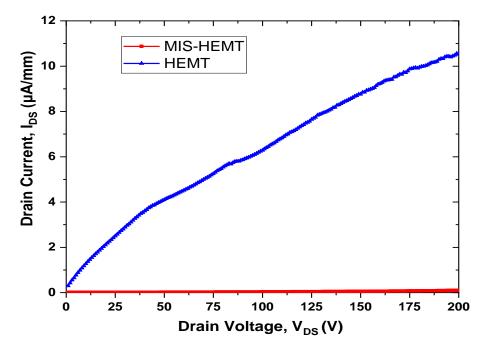

| GaN wafers.75Figure 5.5: The l <sub>DS</sub> -V <sub>DS</sub> characteristics for 50 and 200 μm wide devices on buffer-free GaN wafer.75Figure 5.6: The l <sub>DS</sub> -V <sub>DS</sub> characteristics for 50 and 200 μm wide devices on thick- GaN buffer wafer.76Figure 5.7: The l <sub>DS</sub> -V <sub>DS</sub> characteristics of 2 x 50 μm wide devices at V <sub>GS</sub> = 0V to -5V and V <sub>DS</sub> up to40V on buffer free wafer and thick GaN buffer wafer.76Figure 5.8: Measured transfer characteristics of (a) buffer-free (b) thick GaN buffer devices biasedat V <sub>DS</sub> = 5 V.77Figure 5.9: Measured gate leakage currents of (a) buffer-free (b) thick GaN buffer devices with a2-μm gate long, two-finger 2 x 50 μm wide biased at V <sub>DS</sub> = 0 V78Figure 5.10: Measured off-state breakdown voltage of (a) buffer-free (b) thick GaN buffer devices78Figure 5.11: Measured H21 and Maximum signal gain for 2x200μm device sizes for buffer andbuffer free devices.79Figure 5.12: Standard GaN-on-SiC epitaxial layer wafer structures for comparison in terms of thedevice thermal performance.80Figure 5.13: Micrograph of the fabricated 2×50 μm wide devices on Wafer 1 (commercial) and vafer 2(buffer free) devices.82Figure 5.15: Transconductance (gm) characteristics of the wafer 1 (commercial) and wafer 2(buffer free) devices.83Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer free) devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 5.3: Epitaxial wafer structure of fabricated AlGaN/GaN heterostructure devices using (a) a                             |

| 75Figure 5.6: The IDS-VDS characteristics for 50 and 200 μm wide devices on thick- GaN buffer wafer.76Figure 5.7: The IDS-VDS characteristics of 2 x 50 μm wide devices at VGS = 0V to -5V and VDS up to40V on buffer free wafer and thick GaN buffer wafer.76Figure 5.8: Measured transfer characteristics of (a) buffer-free (b) thick GaN buffer devices biasedat VDS = 5 V.77Figure 5.9: Measured gate leakage currents of (a) buffer-free (b) thick GaN buffer devices with a2-μm gate long, two-finger 2 x 50 μm wide biased at VDS = 0 V.78Figure 5.10: Measured off-state breakdown voltage of (a) buffer-free (b) thick GaN buffer deviceswith a 2 - μm gate long, two-finger 2 x 50 μm wide biased at VGS = -10 V.78Figure 5.11: Measured H21 and Maximum signal gain for 2x200μm device sizes for buffer andbuffer free devices.79Figure 5.13: Micrograph of the fabricated 2×50 μm wide device with gate-length of 2 μm.81Figure 5.14: IDS-VDS characteristics for 50 μm wide devices on Wafer 1 (commercial) and 2 (buffer-free from SweGaN).82Figure 5.15: Transconductance (gm) characteristics of the wafer 1 (commercial) and wafer 2 (buffer free) devices.82Figure 5.16: Gate leakage comparison of devices on wafer 1 (commercial) and wafer 2 (buffer free) devices.83Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer free) devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

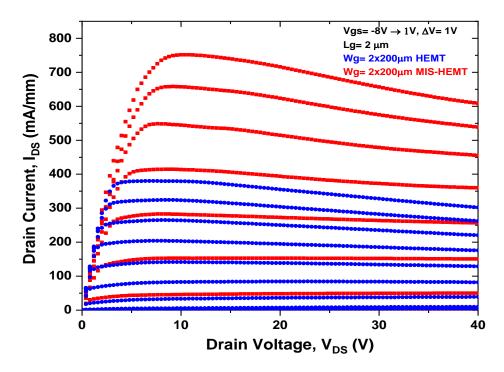

| Figure 5.6: The I <sub>DS</sub> -V <sub>DS</sub> characteristics for 50 and 200 µm wide devices on thick- GaN buffer wafer.<br>76<br>Figure 5.7: The I <sub>DS</sub> -V <sub>DS</sub> characteristics of 2 x 50 µm wide devices at V <sub>GS</sub> = 0V to -5V and V <sub>DS</sub> up to<br>40V on buffer free wafer and thick GaN buffer wafer.<br>76<br>Figure 5.8: Measured transfer characteristics of (a) buffer-free (b) thick GaN buffer devices biased<br>at V <sub>DS</sub> = 5 V.<br>77<br>Figure 5.9: Measured gate leakage currents of (a) buffer-free (b) thick GaN buffer devices with a<br>2-µm gate long, two-finger 2 x 50 µm wide biased at V <sub>DS</sub> = 0 V.<br>78<br>Figure 5.10: Measured off-state breakdown voltage of (a) buffer-free (b) thick GaN buffer devices<br>with a 2- µm gate long, two-finger 2 x 50 µm wide biased at V <sub>GS</sub> = -10 V.<br>78<br>Figure 5.11: Measured H21 and Maximum signal gain for 2x200µm device sizes for buffer and<br>buffer free devices.<br>79<br>Figure 5.12: Standard GaN-on-SiC epitaxial layer wafer structures for comparison in terms of the<br>device thermal performance.<br>80<br>Figure 5.13: Micrograph of the fabricated 2×50 µm wide devices with gate-length of 2 µm.<br>81<br>Figure 5.14: I <sub>DS</sub> -V <sub>DS</sub> characteristics for 50 µm wide devices on Wafer 1 (commercial) and 2 (buffer-<br>free from SweGaN).<br>82<br>Figure 5.15: Transconductance (gm) characteristics of the wafer 1 (commercial) and wafer 2<br>(buffer free) devices.<br>83<br>Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.<br>83<br>Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.<br>83<br>Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.<br>83<br>Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.<br>83<br>Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.<br>83 | -                                                                                                                             |

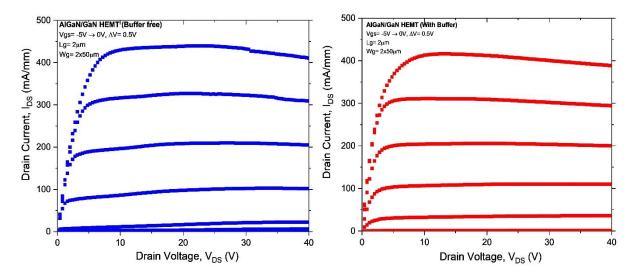

| Figure 5.7: The I <sub>D5</sub> -V <sub>D5</sub> characteristics of 2 x 50 μm wide devices at V <sub>G5</sub> = 0V to -5V and V <sub>D5</sub> up to<br>40V on buffer free wafer and thick GaN buffer wafer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 5.6: The $I_{DS}\text{-}V_{DS}$ characteristics for 50 and 200 $\mu m$ wide devices on thick- GaN buffer wafer.        |

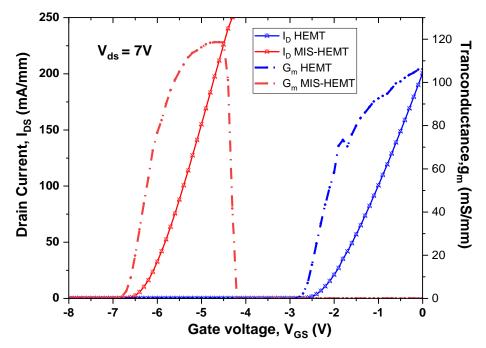

| at V <sub>Ds</sub> = 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 5.7: The $I_{DS}$ -V $_{DS}$ characteristics of 2 x 50 $\mu m$ wide devices at $V_{GS}$ = 0V to -5V and $V_{DS}$ up to |

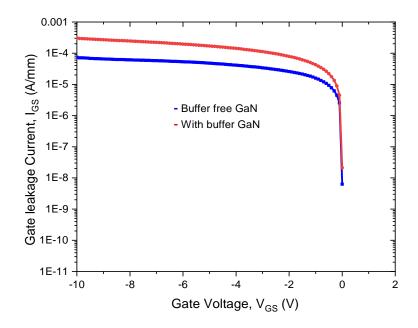

| 2-μm gate long, two-finger 2 x 50 μm wide biased at VDS = 0 V78Figure 5.10: Measured off-state breakdown voltage of (a) buffer-free (b) thick GaN buffer devices<br>with a 2- μm gate long, two-finger 2 x 50 μm wide biased at VGS = -10 V78Figure 5.11: Measured H21 and Maximum signal gain for 2x200μm device sizes for buffer and<br>buffer free devices.79Figure 5.12: Standard GaN-on-SiC epitaxial layer wafer structures for comparison in terms of the<br>device thermal performance.80Figure 5.13: Micrograph of the fabricated 2×50 μm wide device with gate-length of 2 μm.81Figure 5.14: IDS-VDS characteristics for 50 μm wide devices on Wafer 1 (commercial) and 2 (buffer-<br>free from SweGaN).82Figure 5.15: Transconductance (gm) characteristics of the wafer 1 (commercial) and wafer 2<br>(buffer free) devices.82Figure 5.16: Gate leakage comparison of devices on wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.83Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |

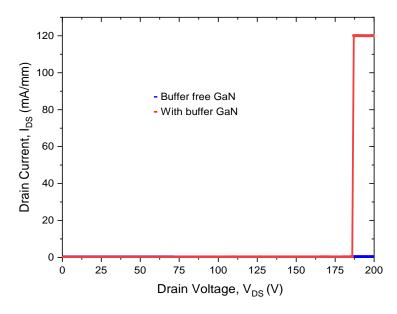

| with a 2- µm gate long, two-finger 2 x 50 µm wide biased at V <sub>GS</sub> = -10 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                               |

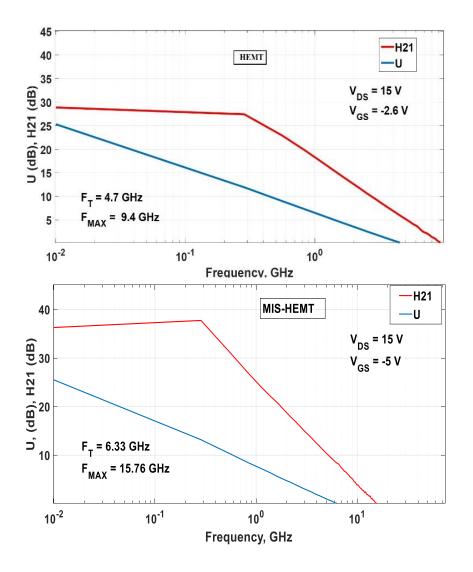

| buffer free devices.79Figure 5.12: Standard GaN-on-SiC epitaxial layer wafer structures for comparison in terms of the<br>device thermal performance.80Figure 5.13: Micrograph of the fabricated 2×50 µm wide device with gate-length of 2 µm.81Figure 5.14: Ips-Vps characteristics for 50 µm wide devices on Wafer 1 (commercial) and 2 (buffer-<br>free from SweGaN).82Figure 5.15: Transconductance (gm) characteristics of the wafer 1 (commercial) and wafer 2<br>(buffer free) devices.82Figure 5.16: Gate leakage comparison of devices on wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.83Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer free) devices.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                               |

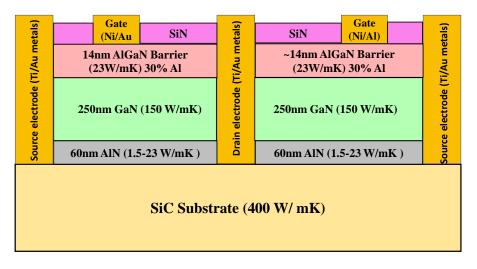

| device thermal performance.80Figure 5.13: Micrograph of the fabricated 2×50 μm wide device with gate-length of 2 μm.81Figure 5.14: IDS-VDS characteristics for 50 μm wide devices on Wafer 1 (commercial) and 2 (buffer-<br>free from SweGaN).82Figure 5.15: Transconductance (gm) characteristics of the wafer 1 (commercial) and wafer 2<br>(buffer free) devices.82Figure 5.16: Gate leakage comparison of devices on wafer 1 (commercial) and wafer 2 (buffer<br>free) devices.82Figure 5.17: Breakdown characteristics of wafer 1 (commercial) and wafer 2 (buffer free) devices.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                               |

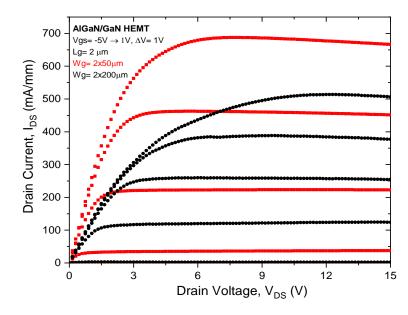

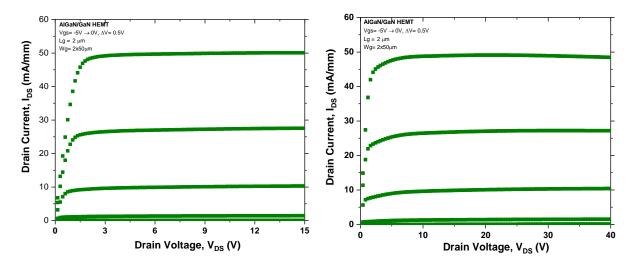

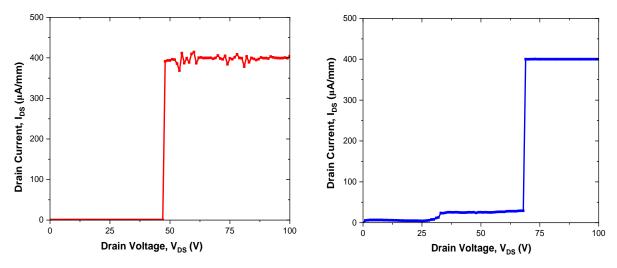

| Figure 5.14: I <sub>DS</sub> -V <sub>DS</sub> characteristics for 50 µm wide devices on Wafer 1 (commercial) and 2 (buffer-<br>free from SweGaN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                               |

| free from SweGaN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 5.13: Micrograph of the fabricated 2×50 $\mu m$ wide device with gate-length of 2 $\mu m.$ 81                          |

| (buffer free) devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                               |

| free) devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |

| Figure 6.1: A picture of a standard AlGaN/GaN HEMT with a three-arrow pointing from the channel to the substrate to show how heat flows. Also given are the thermal conductivities of the most common epi-layers and substrates                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

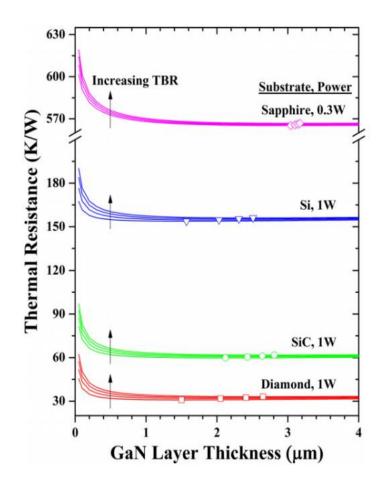

| Figure 6.2: The simulation on the effect of GaN buffer layer thickness on the thermal resistance for different substrate material [160]                                                                                                                             |

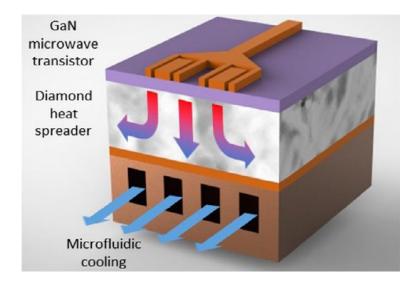

| Figure 6.3: Thermal management options illustrated schematically utilising diamond heat extractor using liquid cooling [167]                                                                                                                                        |

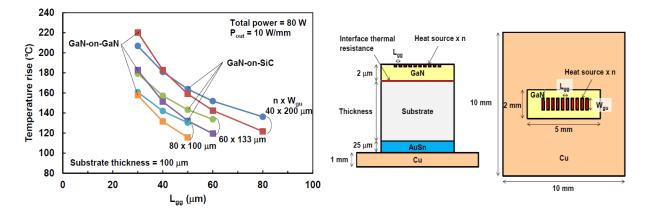

| Figure 6.4: A simulated comparison of heat source spacing distance dependence on temperature rise between GaN on GaN and GaN on SiC at different values of n × Wgu (left figure) and simulated structure with heat source placed on top of GaN epitaxial layer[169] |

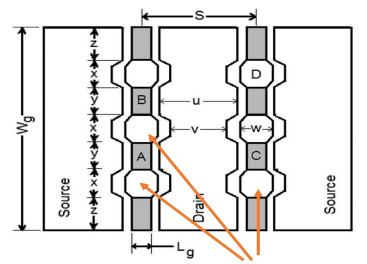

| Figure 6.5: Distributed gates design [172]                                                                                                                                                                                                                          |

| Figure 6.6: Diamond heat extractor using liquid cooling [174]                                                                                                                                                                                                       |

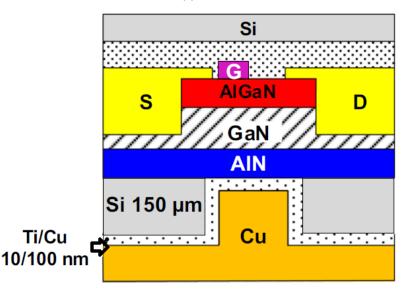

| Figure 6.7:Backside Silicon etched and filling micro-trench with copper electroplating [175] 92                                                                                                                                                                     |

| Figure 6.8: Layout of the new device with bond pads as heat sink                                                                                                                                                                                                    |