Nekoeian, Dayhim (2025) Advancing sensitivity and performance of Capacitive Micromachined Ultrasound Transducers (CMUTs) for medical imaging. MSc(R) thesis.

https://theses.gla.ac.uk/85257/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# Advancing Sensitivity and Performance of Capacitive Micromachined Ultrasound Transducers (CMUTs) for Medical Imaging

Dayhim Nekoeian

Submitted in fulfilment of the requirement for the

Degree of MSc in Mechanical Engineering (Research)

James Watt School of Engineering College of Science and Engineering University of Glasgow

April 2025

## Author's declaration

I hereby submit this thesis in fulfilment of the requirements for the degree of Master of Science in Mechanical Engineering (Research) at James Watt School of Engineering, University of Glasgow. This document is submitted solely for the purpose of this qualification.

I certify that this thesis is my original work, except where otherwise acknowledged or referenced. All information sources and literature used are properly referenced throughout the thesis.

This research was funded by the EU BRAINSTORM Project.

Signature: Dayhim Nekoeian Date: 14.04.2025

## Abstract

Ultrasound transducer technology has significantly contributed to advancements in medical imaging, continuously improving resolution, efficiency, and integration. Capacitive Micromachined Ultrasound Transducers (CMUTs) use electrostatic transduction to generate and detect sound waves, promise broader bandwidth, smaller size, and better integration with electronics than piezoelectric transducers, which improves Transduction efficiency and frequency response for next-generation imaging such as X-radiation (X-rays), Magnetic Resonance Imaging (MRIs), or standard photography.

This thesis focuses on improving CMUT sensitivity and performance for medical imaging through innovative design strategies, analytical modelling and optimized fabrication processes. The literature review covers ultrasound imaging principles, CMUT operation, and their use in diagnostics, therapy, biosensing, and airborne systems, while a comparison with PMUTs emphasizes CMUTs' improved electromechanical coupling and frequency response, supporting their role in advanced imaging. A fabrication process compatible with Complementary Metal Oxide Semiconductor (CMOS) is developed to support the integration of CMUTs with advanced electronic circuits, enabling the creation of compact and efficient imaging devices.

The research takes an experimental approach to improve a low-temperature sacrificial release method, enabling precise membrane formation with reduced stress. Various microfabrication techniques, including photolithography with photomask design using COMSOL, thin-film deposition, and etching, are refined to develop a scalable and reproducible fabrication process. To enhance CMUT sensitivity, the study uses analytical modelling with Hooke's Law and Euler-Bernoulli Beam Theory to analyse axial and bending stiffness in straight beams, then compares them to meander beams to assess their effect on CMUT sensitivity.

Experimental validation through capacitance-frequency (*C*-*F*) and capacitance-voltage (*C*-*V*) measurements confirms reliability, showing the Silicon Oxide (SiO<sub>2</sub>) sacrificial layer remained stable without causing capacitance loss. Additionally, the measured permittivity of the sputtered SiO<sub>2</sub> closely aligns with values reported in previous studies, demonstrating consistency in material properties and fabrication precision.

In summary, this research has established a CMOS-compatible fabrication process and refines the dry etching release method to reduce stiction, laying the groundwork for advancing CMUT technology with improved reliability and adaptability for medical imaging. Future work aims to improve CMUT fabrication by adjusting material choices and enhancing the sacrificial release process.

# Acknowledgment

I sincerely thank my supervisors, Professor Sandy Cochran and Professor Hadi Heidari, for their unwavering support and guidance throughout the past year. Their compassionate care and encouragement were invaluable in helping me navigate the challenges and obstacles I encountered during this journey.

I am also grateful to the Microelectronics Lab for their support and funding. A special note of appreciation goes to Dr. Mahdieh Shojaei Baghini, whose emotional and academic support inspired and motivated me throughout this work.

I would like to express my deepest gratitude to my parents, who have been the greatest source of strength and support. Their unconditional love and encouragement enabled me to overcome every difficulty along the way.

Lastly, I thank my brothers, Sahand and Alborz. No matter the distance, their constant love and support have always been with me and meant the world to me.

# **Table of Contents**

| List of T | Sables                                                  | VII  |

|-----------|---------------------------------------------------------|------|

| List of F | Figures                                                 | VIII |

| Table of  | of Abbreviations                                        | XI   |

| List of S | Symbols                                                 | XIII |

| Chapte    | r 1: Introduction                                       |      |

| 1.1       | Motivation                                              |      |

| 1.2       | Contributions to Knowledge                              | 2    |

| 1.3       | Thesis structure                                        |      |

| Chapte    | r 2: Literature Review                                  | 6    |

| 2.1       | Background on ultrasound                                | 6    |

| 2.2       | Micromachined Ultrasound Transducers                    | 7    |

| 2.2       | 2.1 Principle of operation                              | 8    |

| 2.2       | 2.2 Micro-machined ultrasound transducer                |      |

| 2.2       | 2.3 Capacitive micro-machined ultrasound transducer     | 11   |

| 2.2       | 2.4 CMUT working principle                              | 12   |

| 2.3       | Comparison between CMUT and PMUT                        | 14   |

| 2.4       | Applications of CMUTs                                   | 16   |

| 2.4       | I.1 Medical Imaging                                     | 17   |

| 2.5       | Fabrication process of CMUTs                            | 21   |

| 2.5       | 5.1 Wafer Bonding Method                                | 21   |

| Ι         | Direct wafer bonding                                    | 21   |

| I         | Anodic wafer bonding                                    | 23   |

| Ι         | Polymer adhesive wafer bonding                          | 24   |

| 2.5       | 5.2 Sacrificial Release Method                          | 25   |

| V         | Vias and 2D Arrays                                      |      |

| 2.6       | Chapter summary                                         |      |

| Chapte    | r 3: Modelling                                          |      |

| 3.1       | Modelling framework                                     |      |

| 3.2       | Analytical Modelling                                    |      |

| 3.3       | Axial Stiffness                                         |      |

| 3.4       | Bending Stiffness                                       |      |

| 3.5       | Axial and bending stiffness in straight Cantilever beam |      |

| 3.5       | 5.1 Axial Stiffness – Hooke's Law                       |      |

| 3.5       | 5.2 Bending Stiffness – Euler-Bernoulli Beam Theory     |      |

| Validati     | on of Analytical Modelling:                                                     |    |

|--------------|---------------------------------------------------------------------------------|----|

| 3.6 Th       | eory of meander design                                                          |    |

| 3.6.1        | Analytical Estimation of Axial Stiffness                                        |    |

| 3.6.2        | Analytical Estimation of Bending Stiffness                                      |    |

| Chapter 4: 0 | CMOS-Compatible Fabrication of CMUT                                             |    |

| 4.1 Me       | ethods                                                                          | 43 |

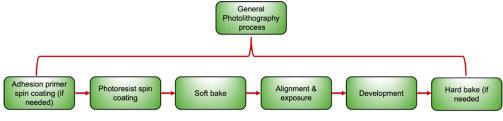

| 4.1.1        | Photolithography                                                                | 43 |

| 4.1.2        | Etching                                                                         | 46 |

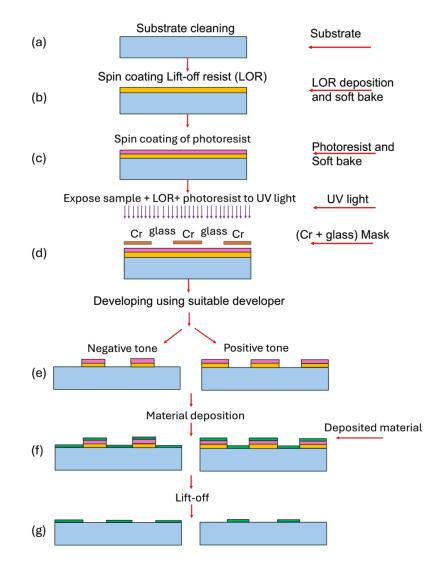

| 4.1.3        | Lift-off                                                                        | 47 |

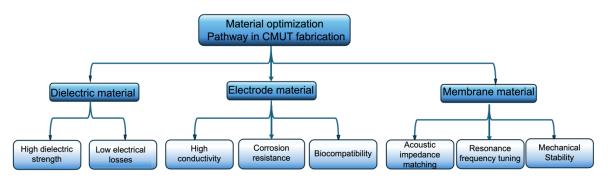

| 4.2 Ma       | terial Selection                                                                | 48 |

| 4.3 Fa       | prication of CMUTs                                                              | 50 |

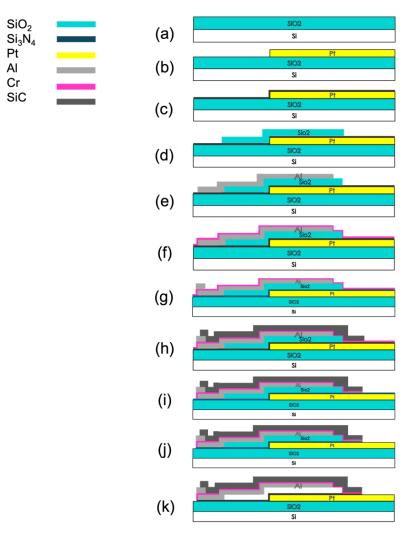

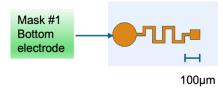

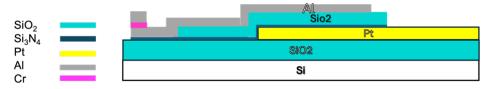

| 4.3.1        | Step 2 - deposition of Pt bottom electrode                                      | 51 |

| 4.3.2        | Step 3 - deposition of Si <sub>3</sub> N <sub>4</sub> dielectric layer          | 52 |

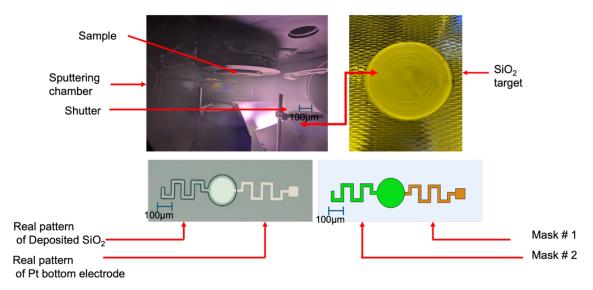

| 4.3.3        | Step 4 - deposition of SiO <sub>2</sub> Sacrificial layer                       |    |

| 4.3.4        | Step 5 - deposition of Al top electrode                                         | 54 |

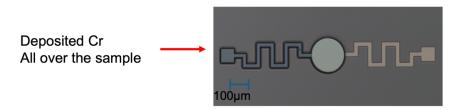

| 4.3.5        | Step 6 - deposition of Cr barrier layer                                         | 55 |

| 4.3.6        | Step 7 - deposition of Al bonding pad                                           |    |

| 4.3.7        | Step 8 - deposition of SiC membrane                                             |    |

| 4.3.8        | Step 9 - Wet etching of Cr barrier layer                                        | 57 |

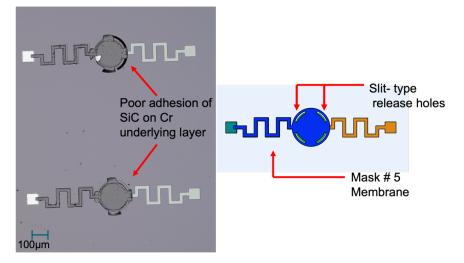

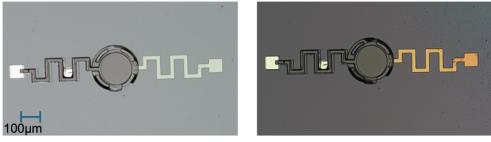

| 4.3.9        | Step 10 - Dry etching of Si <sub>3</sub> N <sub>4</sub> using RIE               |    |

| 4.3.10       | Step 11 - HF vapour dry release of sputtered SiO <sub>2</sub> sacrificial layer |    |

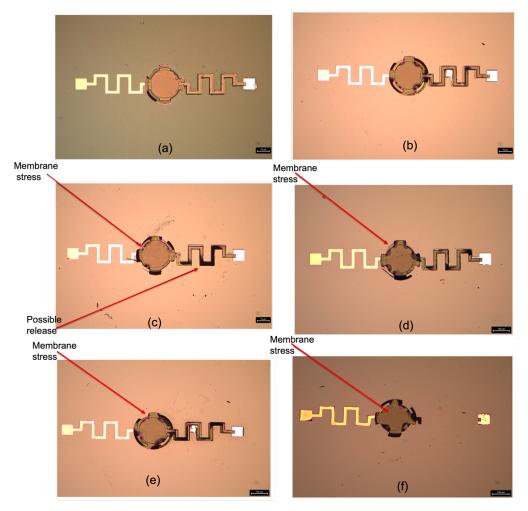

| First        | etch                                                                            | 60 |

| Etch         | cycle (2)                                                                       | 60 |

| Etch         | cycle (3)                                                                       | 60 |

| Etch         | cycle (4)                                                                       | 60 |

| Etch         | cycle (5)                                                                       | 60 |

| Chapter 5: 1 | Dynamic Measurement of Micromachined Capacitor                                  | 62 |

| 5.1 Str      | uctural characterization                                                        | 62 |

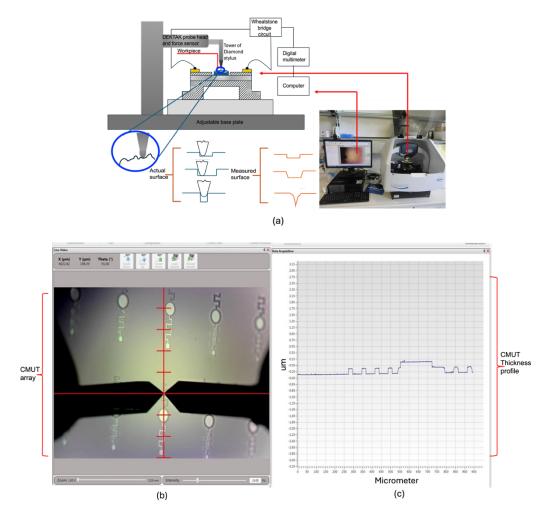

| 5.1.1        | Profilometry                                                                    | 62 |

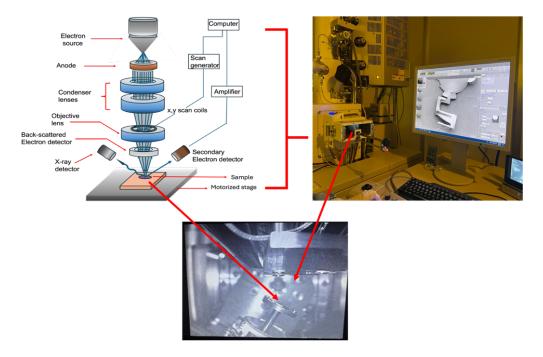

| 5.1.2        | Scanning Electron Microscopy                                                    | 64 |

| 5.2 Ele      | ectrical characterisation                                                       | 65 |

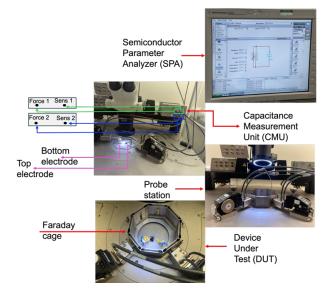

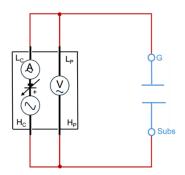

| 5.2.1        | Measurement setup                                                               | 66 |

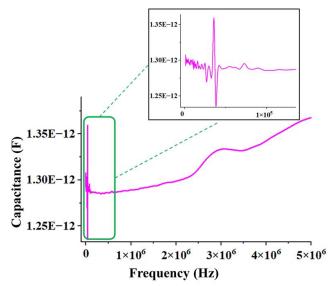

| 5.2.2        | C-F Analysis                                                                    | 67 |

| 5.2.3        | C-V Analysis                                                                    | 68 |

| Chapter 6: 0 | Conclusions & Future Work                                                       | 71 |

| Appendices   |                                                                                 | 73 |

| Appendix A   | : Clean room processes and tools                                                | 73 |

| A.1 Cleaning:                                      | 3 |

|----------------------------------------------------|---|

| A.1.1 Ultrasonic cleaning:                         | 3 |

| A.1.2 Asher                                        | 3 |

| A.2 Photolithography                               | 1 |

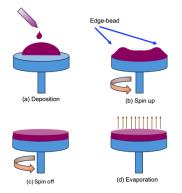

| A.2.1 Photoresist spin coating                     | 1 |

| A.2.2 Soft bake                                    | 5 |

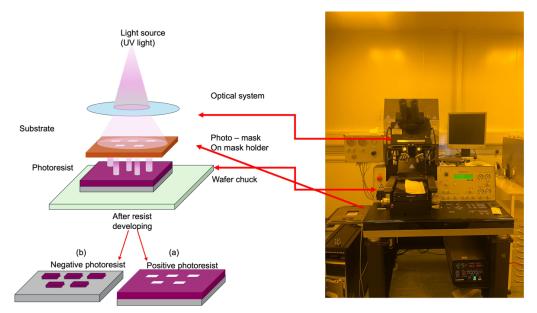

| A.2.3 Alignment and exposure                       | 5 |

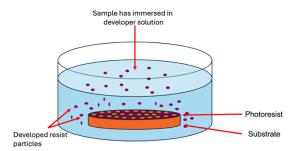

| A.2.4 Development                                  | 3 |

| A.3 Physical Vapour Deposition                     | 3 |

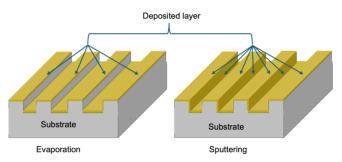

| A.3.1 Sputtering                                   | ) |

| A.3.2 Electron-beam evaporator                     | 1 |

| A.4 Chemical Vapour Deposition                     | 1 |

| A.4.1 Plasma - Enhanced Chemical Vapour Deposition | 2 |

| A.5 Etching methods and tools                      | 3 |

| A.5.1 Wet etching                                  | 1 |

| A.5.2 Dry etching                                  | 5 |

| Wet etch and Dry etch differences                  | 5 |

| A.6 HF vapour release tool                         | 5 |

| Bibliography                                       | 7 |

# List of Tables:

| Table 2-1: Comparison between CMUT and PMUT14                                      |  |

|------------------------------------------------------------------------------------|--|

| Table 3-1: Dimensions of straight beam ( $L_0$ ) and meander beams ( $L_0 - L_4$ ) |  |

#### **Table of Figures:**

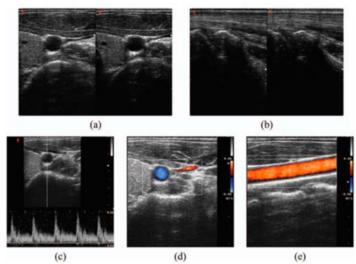

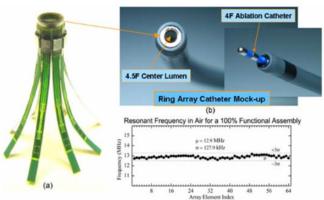

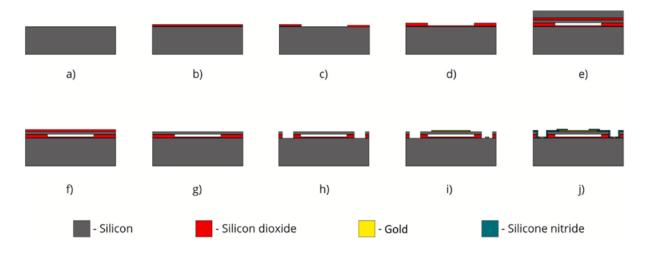

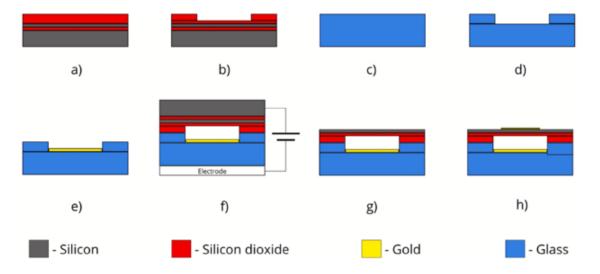

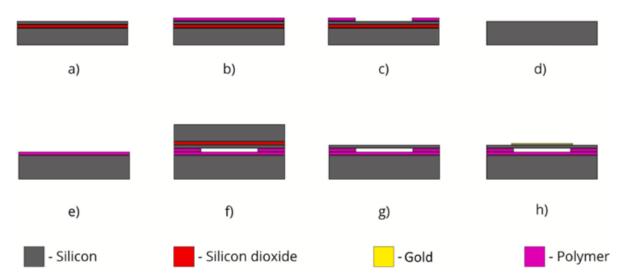

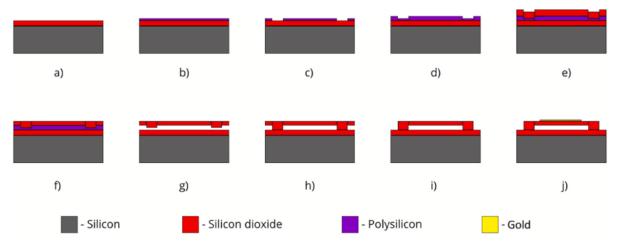

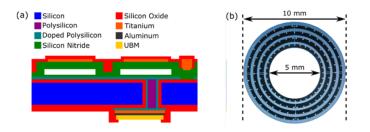

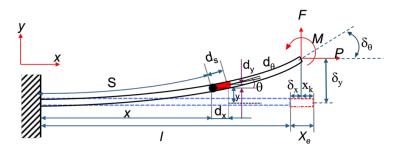

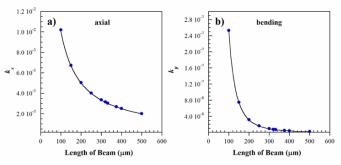

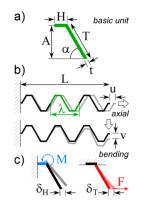

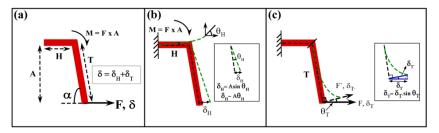

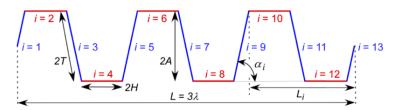

Figure 2-6: In vivo ultrasound images taken with an Esaote Technos imaging system set to a 13-MHz preset. (a) B-mode image of the carotid artery and (b) the forearm tendon, both shown with (left) a CMUT probe and (right) an Esaote LA435 piezoelectric thick-film transducer probe. (c) Pulsed wave (PW) Doppler and (d) and (e) color Doppler images of the same carotid artery. All images are displayed with a dynamic range of 55 dB. The imaging depth is 31 mm in (b) and 41 mm in (a), (c), (d), and (e) Figure 2-7:(a) A photo of a fully assembled ring, ready to be attached to a catheter. (b) An example of how the CMUT array is integrated with the catheter shaft. (c) Resonant frequencies of all 64 elements Figure 2-8: Steps of the direct wafer bonding: (a) preparing the prime wafer; (b) creating tiny support pillars through thermal oxidation; (c) etching to form a cavity; (d) adding an insulation layer using thermal oxidation; (e) bonding the wafers together; (f) handling wafer removal; (g) stripping away the oxide layer; (h) revealing the bottom wafer; (i) top electrode deposition; (j) applying a protective Figure 2-9: Steps of the anodic wafer bonding: (a) getting the prime wafer ready; (b) creating support pillars on the prime wafer using thermal oxidation; (c) preparing the glass wafer; (d) making pillars on the glass through thermal oxidation; (e) bottom electrode deposition; (f) bonding the wafers together using a high DC voltage: (g) handling layer removal: (h) top electrode deposition [97]. © 2024 Elsevier. Figure 2-10: Steps of the polymer adhesive wafer bonding: (a) getting the top wafer ready; (b) applying a polymer layer on the top wafer and letting it solidify; (c) etching to create a cavity; (d) getting the prime wafer ready; (e) applying and solidifying a polymer layer on the prime wafer; (f) bonding the wafers together using polymer adhesive; (g) handling layer removal; (h) top electrode deposition [97], Figure 2-11: Sacrificial Release Process: (a) An insulator layer is deposited. (b) A polysilicon sacrificial laver is added. (c) Insulator pillars are formed. (d) A membrane laver is deposited. (e) The pillar is etched to create a channel to the sacrificial layer. f) The sacrificial layer is etched away. (g) The cavity is sealed by depositing an insulator using LPCVD. (h) A top electrode layer is deposited. (i) The bottom wafer is exposed. (i) The final top electrode laver is deposited [97], © 2024 Elsevier. Used with Figure 2-12: a) A sacrificial release CMUT design that includes vias for electrical connections on the backside. (b) A four-ring 2D CMUT array created using the sacrificial release process and through-Figure 3-1: Deformation of a cantilever beam under the influence of both an applied end force (F) and Figure 3-2: Evaluation of stiffness as a function of cantilever length, with black lines depicting analytical solutions and blue symbols representing FEM results obtained using Eq. 3.5 and 3.8 for (a) axial stiffness and (b) bending stiffness [13], reproduced with permission from © 2012 IOP Publishing Figure 3-3: Parameters describing beam geometry. (b) A trapezoidal representation of the 3-period beams utilized in the Balakrisnan's study, showing the fixed-free boundary conditions along with the axial and bending displacements. (c) A schematic depiction of the main deformations occurring in the horizontal (blue) and inclined (red) segments of the basic unit during axial elongation [13], reproduced Figure 3-4: (a) The specific unit segment being analysed. (b) Rigid body rotation of the segment resulting from the deformation of segment H. The axial force generates a moment M on H, calculated as force multiplied by offset, M= F×A, leading to a rigid body rotation of T and causing a deflection,  $\delta_{\rm H}$ . (c) Segment T is modelled as a cantilever beam subjected to a point load at its tip, where the axial force

| induces a deflection $\delta_T$ . The overall deflection is determined by summing $\delta_H$ and $\delta_T$ [13], reproduced<br>with permission from © 2012 IOP Publishing Ltd |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

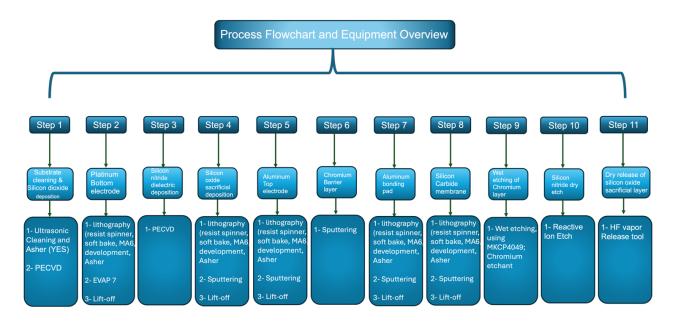

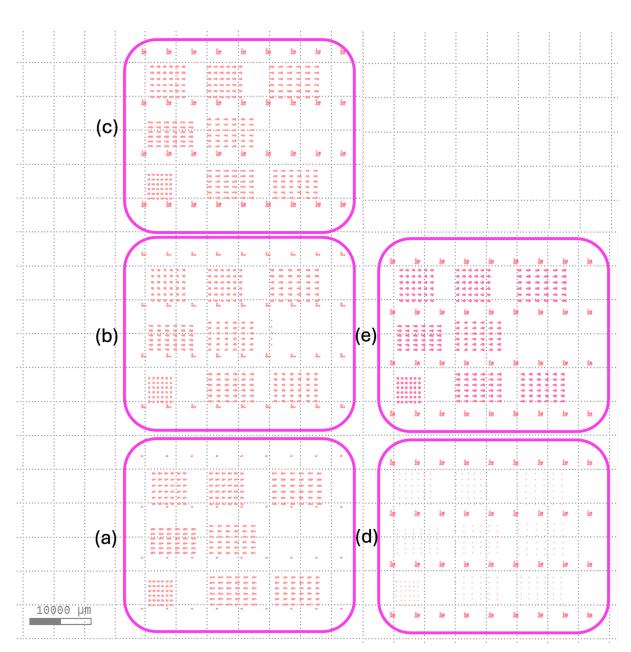

| Figure 4-1 : Process flowchart and equipment overview of CMUT fabrication                                                                                                      |

| Figure 4-6: Process flow for pattern transfer using photolithography and etching                                                                                               |

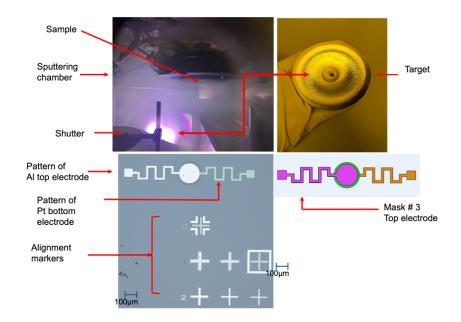

| Figure 4-11: Using Mask No.2 for the deposition of a sacrificial layer in the sputtering chamber with<br>an SiO <sub>2</sub> target to achieve the final pattern shown         |

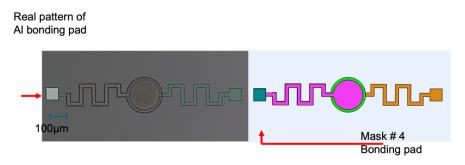

| Figure 4-15: Using Mask No.4 for the deposition of the Al bonding pad in the sputtering chamber to achieve the final pattern shown                                             |

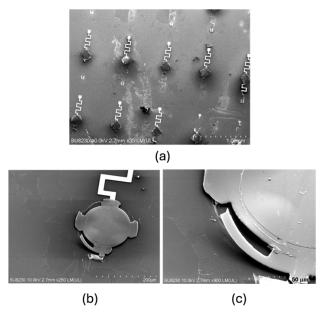

| Figure 5-4: SEM images showing detailed views of the device after the final (5th) HF vapour release      cycle of the sacrificial layer. (a) Overview of the CMUT array. (b) a single CMUT cell with partially      released membrane. (c) High-magnification image of the membrane edge, highlighting the undercut      region and released sacrificial layer. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure A-4: Hot plate used for the baking step in photolithography                                                                                                                                                                                                                                                                                              |

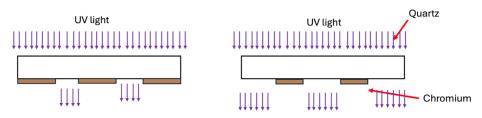

| Figure A-5: A schematic representation of the role of the Mask aligner (MA6, SUSS MicroTec,                                                                                                                                                                                                                                                                     |

| Germany) in the photolithography process                                                                                                                                                                                                                                                                                                                        |

| Figure A-6: Alignment markers used on the photomask for precise layer alignment in the lithography                                                                                                                                                                                                                                                              |

| process                                                                                                                                                                                                                                                                                                                                                         |

| Figure A-7: Schematic representation of the general photoresist developing process in                                                                                                                                                                                                                                                                           |

| photolithography                                                                                                                                                                                                                                                                                                                                                |

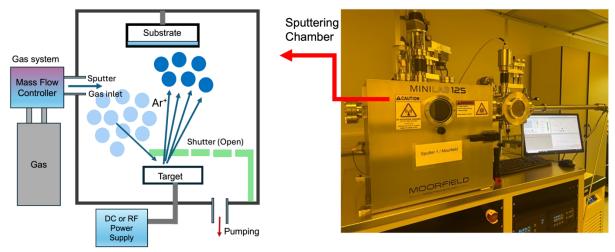

| Nanotechnology, UK) system for thin-film deposition                                                                                                                                                                                                                                                                                                             |

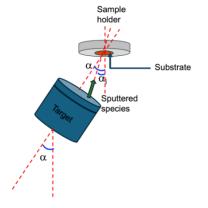

| Figure A-9: Schematic representation of the target and sample holder arrangement inside the deposition                                                                                                                                                                                                                                                          |

| chamber                                                                                                                                                                                                                                                                                                                                                         |

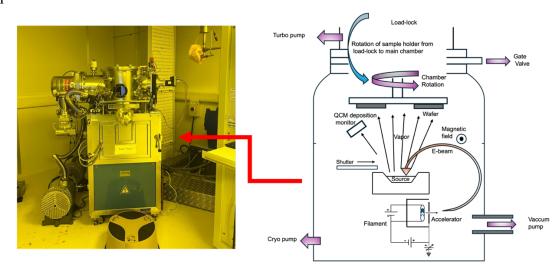

| Figure A-10: Schematic representation and setup of Electron beam evaporation (EVAP 7, Plassys,                                                                                                                                                                                                                                                                  |

| France)                                                                                                                                                                                                                                                                                                                                                         |

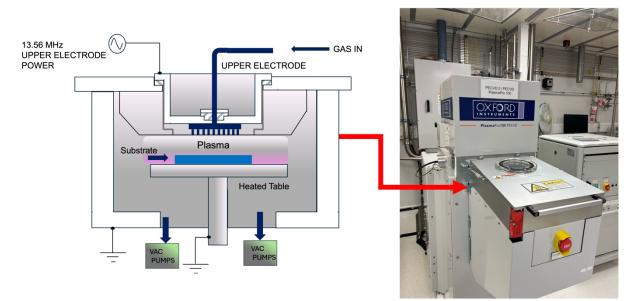

| Figure A-11: Schematic representation and setup of PECVD (PlasmaPro 100, OXFORD Instrument,                                                                                                                                                                                                                                                                     |

| UK)                                                                                                                                                                                                                                                                                                                                                             |

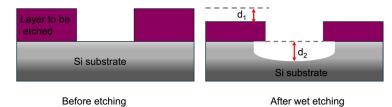

| Figure A-12: Schematic illustration of selectivity in the etching process, highlighting material removal                                                                                                                                                                                                                                                        |

| differences between the etched layer and the substrate                                                                                                                                                                                                                                                                                                          |

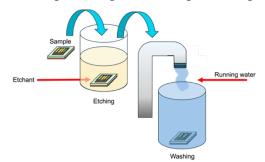

| Figure A-13: Schematic representation of the wet etching process in nanofabrication                                                                                                                                                                                                                                                                             |

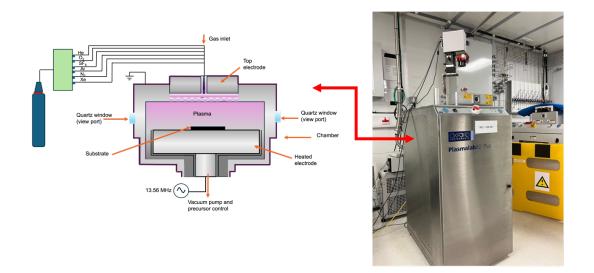

| Figure A-14: Schematic representation and actual setup of the RIE system (Plasmalab 80 Plus,                                                                                                                                                                                                                                                                    |

| OXFORD Instruments, UK), used for dry etching in nanofabrication                                                                                                                                                                                                                                                                                                |

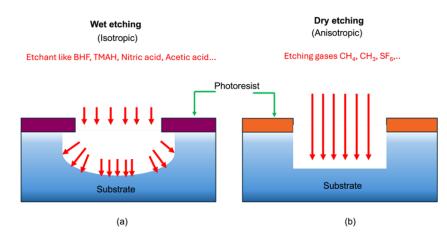

| Figure A-15: Schematic illustration comparing wet and dry etching processes, highlighting their                                                                                                                                                                                                                                                                 |

| different etchants, mechanisms, and effects on the substrate                                                                                                                                                                                                                                                                                                    |

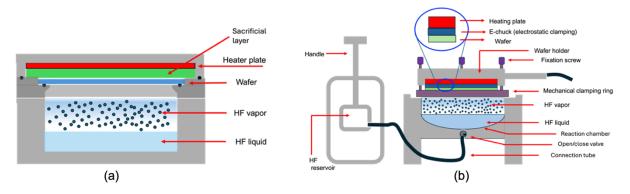

| Figure A-16: Schematic representation of (a) an HF vapour release tool and (b) a VPE system used for                                                                                                                                                                                                                                                            |

| dry etching in nanofabrication                                                                                                                                                                                                                                                                                                                                  |

# **Table of Abbreviations**

| 4TP   | Four-terminal pair                                 |

|-------|----------------------------------------------------|

| 2-D   | Two-dimensional                                    |

| 3-D   | Three-dimensional                                  |

| AC    | Alternating current                                |

| ALD   | Atomic layer deposition                            |

| BHF   | Buffered hydrofluoric acid                         |

| BOX   | Buried oxide                                       |

| BSA   | Bovine serum albumin                               |

| C-F   | Capacitance-frequency                              |

| C-V   | Capacitance-voltage                                |

| CMOS  | Complementary metal-oxide-semiconductor            |

| CMUT  | Capacitive Micro-machined Ultrasound Transducer    |

| CMP   | Chemical mechanical polishing                      |

| CVD   | Chemical vapour deposition                         |

| DC    | Direct current                                     |

| DEAs  | Dielectric elastomer actuators                     |

| DI    | Deionized                                          |

| DRIE  | deep reactive ion etching                          |

| EBE   | Electron Beam Evaporation                          |

| EBR   | Edge Bead Removal                                  |

| EMCC  | Electromechanical Coupling Coefficient             |

| EVAP  | Electron-beam evaporation                          |

| FEM   | Finite element method                              |

| H_C   | High current                                       |

| H_P   | High potential                                     |

| I-V   | Current-voltage                                    |

| IC    | Integrated Circuit                                 |

| ICP   | Inductively Coupled Plasma                         |

| JWNC  | James Watt Nano-Fabrication Centre                 |

| L_C   | Low- current                                       |

| L_P   | Low-protentional                                   |

| LOR   | Lift-off resist                                    |

| LPCVD | Low-pressure chemical vapour deposition            |

| MA6   | Mask aligner 6                                     |

| MEMS  | Micro-electromechanical systems                    |

| MRIs  | Magnetic Resonance Imaging                         |

| MUTs  | Micromachined Ultrasonic Transducers               |

| NEMS  | Nano-Electromechanical Systems                     |

| PECVD | Plasma - Enhanced Chemical Vapour Deposition       |

| PMUT  | Piezoelectric Micro-machined Ultrasonic Transducer |

| PW    | Pulsed wave                                        |

| PVD   | Physical vapour deposition                         |

| QCM   | Quartz crystal microbalance                        |

| RF    | Radio frequency                                    |

| RH    | Relative humidity                                  |

|       |                                                    |

| RIE   | Reactive ion etching               |

|-------|------------------------------------|

| RX    | Receiver mode                      |

| SAWs  | Surface acoustic waves             |

| SEM   | Scanning Electron Microscopy       |

| SNR   | Signal-to-noise ratio              |

| SOI   | Silicon on insulator               |

| SONAR | Sound Navigation and Ranging       |

| TOBE  | Top orthogonal to bottom electrode |

| TX    | Transmitter mode                   |

| UV    | Ultraviolet                        |

| VPE   | Vapour-phase etching               |

| X-Ray | X-radiation                        |

# List of Symbols

| A                              | Amplitude                                                    |

|--------------------------------|--------------------------------------------------------------|

| $A_C$                          | Cross-sectional area of the beam                             |

| $A_e$                          | Top electrode's area                                         |

| $A_{e\!f\!f}$                  | Effective area of the transducer membrane                    |

| Al                             | Aluminium                                                    |

| Al <sub>2</sub> O <sub>3</sub> | Aluminium oxide                                              |

| Ar                             | Argon                                                        |

| Au                             | Gold                                                         |

| α                              | Beam angle measured from the horizontal axis                 |

| $\alpha_i$                     | Incidence angle                                              |

| b                              | Damping coefficient                                          |

| BCB                            | Benzocyclo-butane                                            |

| BCl <sub>3</sub>               | Boron trichloride                                            |

| $C_{o}$                        | Transducer's static capacitance                              |

| CF <sub>4</sub>                | Carbon Tetrafluoride                                         |

| CHF3                           | Trifluoromethane                                             |

| Cl <sub>2</sub>                | Chlorine                                                     |

| Cr                             | Chromium                                                     |

| D                              | Charge density vector                                        |

| d                              | Diameter                                                     |

| $d_1$                          | Thickness of etched bottom layer                             |

| $d_2$                          | Thickness of etched higher layer                             |

| <i>d</i> 31                    | Sideways contraction and expansion                           |

| <i>d</i> 33                    | Movement perpendicular to the surface                        |

| dB                             | Decibel                                                      |

| $\delta_{\!H}$                 | Deflection of horizontal segment of meander                  |

| $\delta_T$                     | Deflection of the tilted segment of meander                  |

| $\delta_x$                     | Axial displacement                                           |

| $\delta_y$                     | Vertical displacement                                        |

| [d]                            | Piezoelectric coefficients                                   |

| $E_e$                          | Electric field                                               |

| E                              | Young's modulus                                              |

| $\mathcal{E}_{o}$              | Vacuum permittivity                                          |

| $\mathcal{E}_r$                | Relative permittivity                                        |

| [3]                            | Permittivity                                                 |

| F                              | Force                                                        |

| FBW                            | Fractional Bandwidth                                         |

| $F_e$                          | Electrostatic forces                                         |

| $F_y$                          | Force applied perpendicular to beam's length at the free end |

| $g_{\circ}$                    | Initial gap distance                                         |

| $g_{e\!f\!f}$                  | Effective gap height                                         |

| H                              | Length of the horizontal segment of meander                  |

| H <sub>2</sub>                 | Hydrogen                                                     |

| HF                             | Hydrofluoric acid                                            |

| Hz                             | Hertz                                                        |

| I<br>L.D.                      | Second moment of area                                        |

| InP                            | Indium phosphide                                             |

|                                |                                                              |

| IPA                            | Isopropyl alcohol                               |

|--------------------------------|-------------------------------------------------|

| $i_{th}$                       | Number of vertical or tilted segment            |

| КОН                            | Potassium hydroxide                             |

| k                              | Elastic coefficient                             |

| $k_p$                          | Spring constant                                 |

| $k_x^p$                        | Axial stiffness                                 |

| $k_y$                          | Bending stiffness                               |

| Ĺ                              | Length of beam                                  |

| λ                              | Wavelength                                      |

| М                              | External moment                                 |

| т                              | Mass                                            |

| MP 1165                        | Micro-posit Remover 1165                        |

| п                              | Number of periods                               |

| $O_2$                          | Oxygen                                          |

| Мо                             | Molybdenum                                      |

| $N_2$                          | Nitrogen                                        |

| NH <sub>3</sub>                | Ammonia                                         |

| N <sub>2</sub> O               | Nitrous oxide                                   |

| PDMS                           | Polydimethylsiloxane                            |

| PMMA                           | Polymethyl methacrylate                         |

| Pt                             | Platinum                                        |

| PZT                            | Lead Zirconate Titanate                         |

| $R_0$                          | Deposition rate at normal incidence             |

| S                              | Strain                                          |

| $S_e$                          | Selectivity                                     |

| SF <sub>6</sub>                | Sulphur hexafluoride                            |

| Si                             | Silicon                                         |

| SiC                            | Silicon Carbide                                 |

| SiH₄                           | Silane                                          |

| SiO <sub>2</sub>               | Silicon dioxide                                 |

| Si <sub>3</sub> N <sub>4</sub> | Silicon Nitride                                 |

| S                              | Distance between capacitance plate              |

| [ <i>s</i> ]                   | Compliance constants                            |

| $T_S$                          | Stress                                          |

| Т                              | Length of the tilted segment of meander         |

| Ti                             | Titanium                                        |

| TMAH                           | Tetramethylammonium hydroxide                   |

| t                              | Beam's thickness                                |

| $t_e$                          | Etching duration                                |

| $t_i$                          | Insulator thickness                             |

| $t_m$                          | Membrane thickness                              |

| $	heta_H$                      | Rotation angle of horizontal segment of meander |

| $\theta_T$                     | Rotation angle of horizontal segment of meander |

| V                              | Voltage                                         |

| Vac                            | Alternating voltage                             |

| V <sub>DC</sub>                | Direct current voltage (bias voltage)           |

| $V_{Collapse}$                 | Collapse voltage                                |

| W                              | Beam's width                                    |

| η                              | Electro-mechanical coupling                     |

|                                |                                                 |

## **Chapter 1: Introduction**

### 1.1 Motivation

Capacitive Micromachined Ultrasound Transducers (CMUTs) have found uses in some aspects of medical ultrasound imaging by providing notable advantages over traditional piezoelectric transducers. This study offers an in-depth analysis of CMUTs, their role in medical imaging, and the impact of the sacrificial release method in improving their sensitivity and overall performance, aligning with the thesis motivation. The discussion is based on recent research, highlighting fabrication techniques, associated challenges, and potential future developments. CMUTs are microelectromechanical systems (MEMS) that produce and sense ultrasonic waves, offering excellent performance that makes them useful in medical imaging. They can function at high frequencies and offer a wide bandwidth, both essential for high-resolution imaging applications such as intravascular ultrasound (IVUS) [1]. These characteristics make them well-suited for capturing fine details in medical diagnostics, giving good image quality and diagnostic precision [2].

The silicon-based fabrication of CMUTs enables direct integration with electronics, resulting in compact and efficient transducer arrays. This integration is especially advantageous for advanced imaging techniques, where there is a growing need for enhanced sensitivity and performance [3]. Sensitivity, which refers to the ability to detect weak ultrasonic signals, enhances the signal-to-noise ratio (SNR), improving clarity and detail in medical images, and can be optimized by reducing CMUT cell radius to increase mass sensitivity to 0.46 Hz/ag and 0.44 Hz/ag [4], decreasing the electrostatic air gap, using embedding metallic layers to reduce gap height and boost sensitivity by 10% while increasing membrane thickness, Young's modulus, and DC bias voltage [5], [6], applying parametric amplification with ac pumping voltage to raise receiving sensitivity by at least 7 dB [7], and fine-tuning membrane material, radius, thickness, electrode size, and bias voltage to maximize SNR [8].

The progress in medical imaging technologies, fuelled by the need for higher resolution and superior image clarity, necessitates the development of transducers with improved performance. It has been highlighted that increasing CMUT sensitivity is vital for detecting weaker signals, which is necessary for applications such as 3D imaging. The transducer's ability to support diverse imaging modalities depends on its performance, particularly in terms of bandwidth and efficiency [9]. The challenge lies in achieving these improvements while

maintaining cost-effectiveness and reliability, which is where fabrication techniques like the sacrificial release method are relevant.

Research suggests that the method's precision in controlling structural parameters can significantly enhance CMUT performance. The sacrificial release method, a surface micromachining technique, is responsible for creating the vacuum gap beneath the transducer membrane. This process involves depositing a sacrificial layer onto the substrate, which is later removed using a selective etchant that does not affect the membrane layer [3]. This gap allows the membrane to move freely in response to ultrasonic waves, directly contributing to the transducer's sensitivity and overall performance. This method provides precise control over membrane deflection, which is important for optimizing electroacoustic performance [10]. Adjusting the gap height and membrane thickness helps decrease parasitic capacitance, which in turn enhances the transducer's receiving capability [11]. Furthermore, innovations such as through-wafer via interconnections improve electrical connectivity in 2D arrays, contributing to enhanced overall performance [1]. The sacrificial release method offers several advantages, including improved control over uniformity and mechanical properties, which are vital for achieving consistent device performance.

This thesis seeks to enhance the sensitivity and performance of CMUTs for medical imaging by optimizing the sacrificial release method and incorporating a meandering beam design. The study focuses on refining the process to improve membrane deflection, minimize parasitic capacitance, and increase overall efficiency. By addressing these factors, the research aims to contribute to the development of advanced CMUTs that align with the demanding standards of modern medical ultrasound systems. Integrating these advancements could broaden the use of ultrasound, improving accessibility and patient care.

### **1.2** Contributions to Knowledge

In CMUT fabrication, design and material selection are key factors influencing performance, durability, and ease of manufacturing. This study explores innovative approaches, including the adoption of a meandering membrane structure, replacing polyimide which was used previously as a sacrificial layer [12] with sputtered silicon dioxide (SiO<sub>2</sub>), and utilizing Hydrofluoric acid (HF) vapour for sacrificial layer release. These advancements tackle persistent challenges while opening new opportunities in the field.

The meander design changes the way CMUT membranes manage mechanical stress and movement. Unlike a rigid, linear structure, this pattern enhances flexibility and distributes stress more evenly, minimizing the risk of fractures and extending the membrane's lifespan [13]. This is not just about making the membrane last longer—this design also helps it move more smoothly and efficiently. That means better sensitivity and a wider bandwidth, which are essential for producing sharper images and more accurate sensing. Switching to sputtered SiO<sub>2</sub> as a sacrificial layer in CMUT fabrication is a major upgrade, especially for low-temperature processes used in above- Integrated Circuit (IC) integration. Traditionally, polyimide has been the preferred option because it is easy to apply and remove [14]. However, it has some major drawbacks. It easily absorbs moisture, its dielectric properties can be unpredictable, and it gradually breaks down over time, which can affect the long-term reliability of CMUTs [15]. Replacing polyimide [12] using sputtered SiO<sub>2</sub> overcomes these challenges by offering greater mechanical stability, more consistent electrical properties, and improved resistance to environmental conditions, making it a significantly more reliable option. [16]

Sputtered SiO<sub>2</sub> provides a fully inorganic, thermally stable, and low-defect alternative with excellent step coverage, uniformity, and strong adhesion to Al-metallized circuits, making it highly beneficial for advanced semiconductor technologies. In contrast, removing polyimide through oxygen (O<sub>2</sub>) plasma ashing can introduce contamination and residual stress, compromising the accuracy of CMUT cavity formation [17] Meanwhile, sputtered SiO<sub>2</sub> deposition enables adjustable stress control and minimizes charge trapping, which is crucial for ensuring high performance and reliability.

A key benefit of sputtered SiO<sub>2</sub> is its excellent compatibility with Hydrofluoric acid (HF) vapour release. One of the biggest challenges with the conventional choice of wet etching, particularly when using polyimide, is stiction [18], where the CMUT membrane sticks and collapses due to surface tension as the liquid evaporates. This can result in defects, reduced fabrication yields, and inconsistent performance. HF vapour etching eliminates this issue by removing the sacrificial layer through a dry process, preserving membrane integrity and ensuring cleaner, more uniform cavity formation.

By combining sputtered SiO<sub>2</sub> with HF vapour etching, this work aims to create a CMOScompatible fabrication process to make CMUTs more scalable and high-performing, for modern ultrasound applications. These improvements will optimise CMUTs for medical imaging, therapeutic ultrasound, industrial non-destructive testing, and emerging tech like wearable ultrasound devices. Additionally, this approach helps bridge the gap between MEMS and semiconductor manufacturing, making it easier to integrate CMUTs with advanced electronics for more compact and efficient ultrasound imaging systems. In summary, this work brings together three improvements: a stress-optimized meander design, a stable sputtered SiO<sub>2</sub> sacrificial layer, and a carefully controlled HF vapour release process. By combining these elements, it aims to test and develop a more practical and scalable method for building more sensitive CMUTs. This approach moves beyond the limitations of traditional methods that rely on polyimide, making CMUT fabrication more efficient. With sputtered SiO<sub>2</sub> and HF vapour etching refining the sacrificial release process, this research opens the door for CMUTs to play a bigger role in medical imaging and other cutting-edge applications.

### 1.3 Thesis structure

This thesis is structured to provide a comprehensive exploration of CMUTs, covering their fundamental principles, fabrication processes, analytical modelling, performance evaluation, and future advancements. Each chapter builds upon the preceding one, offering a logical progression from theoretical background to practical implementation and optimization.

In Chapter 2, Literature Review, a comprehensive overview of ultrasound transducers is provided, focusing on micromachined ultrasound transducers (MUTs), their principles of operation, fabrication methods, and applications. The discussion begins with an introduction to ultrasound imaging, exploring its fundamental working principles and historical background. It then delves into MUTs, distinguishing between piezoelectric micromachined ultrasonic transducers (PMUTs) and CMUTs. A comparative analysis highlights their respective advantages and limitations, aiding in the selection of the most suitable transducer type for specific applications. The diverse applications of CMUTs are then examined, spanning medical imaging, therapeutic applications, chemical and biosensing, physical sensing, and airborne applications. Finally, the fabrication processes of CMUTs are explored, focusing on wafer bonding techniques, including direct, anodic, and polymer adhesive wafer bonding, as well as the sacrificial release method, providing insight into their role in achieving optimal device performance.

In Chapter 3, the analytical framework for understanding CMUT structures is discussed, beginning with an exploration of axial and bending stiffness. It utilises the fundamental concepts of stiffness in straight cantilever beams, employing Hooke's Law for axial stiffness and the Euler-Bernoulli Beam Theory for bending stiffness. The theory of meandering design is then introduced as a means of optimizing mechanical performance, followed by estimation of axial and bending stiffness. The chapter concludes with calculations that validate these

theoretical models, ensuring that the proposed design aligns with experimental and practical constraints.

In Chapter 4, the fabrication process is explored in detail, beginning with an overview of the cleanroom processes and tools for device manufacturing. Photolithography techniques, including photoresist spin coating, soft baking, alignment and exposure using an MA6 tool, and development processes, are thoroughly discussed, alongside the challenges associated with photolithography. The discussion then covers etching methods, lift-off techniques, and deposition methods such as physical vapour deposition (PVD) and chemical vapour deposition (CVD). Etching techniques, including wet and dry etching, and the HF vapour release tool are examined in depth, particularly focusing on their role in optimizing CMUT fabrication. Material selection criteria are outlined to ensure compatibility with the desired device performance. A step-by-step walkthrough of the CMUT fabrication process follows, detailing substrate cleaning, electrode deposition, sacrificial layer formation, membrane deposition, and final etching cycles required for device release. Emphasis is placed on the challenges and optimizations associated with the HF vapour etching process, aiming to enhance structural integrity and operational efficiency.

In Chapter 5, the measurement techniques used to evaluate the performance of capacitive part of CMUTs are presented. The setup for capacitance measurement is described in detail, including the analysis of capacitance-frequency (*C*-*F*) measurements from DC to 5 MHz and capacitance-voltage (*C*-*V*) measurements ranging from -2 V to 2 V. These measurements provide insights into the electrical behaviour and efficiency of the fabricated devices. Furthermore, the validation of the dielectric constant ( $\varepsilon_r$ ) (for SiO<sub>2</sub> sacrificial layer) using *C*-*V* measurements is discussed, ensuring that the fabricated CMUTs meet the expected performance criteria.

Chapter 6 provides conclusions and outlines future work, which includes material optimization, sacrificial release refinement, numerical modelling, etching improvements, electrode adjustments, and passivation layer enhancement. These refinements aim to improve CMUT performance, reliability, and applicability in medical imaging and diagnostics.

## **Chapter 2: Literature Review**

## 2.1 Background on ultrasound

After the sinking of the Titanic in 1912, Paul Langevin was commissioned to develop a device for discovering underwater items in the ocean. In 1915, motivated by the tragedy, he designed and constructed the first hydrophone, an invention that can claim to have been the first ultrasound transducer. It facilitated development of the first Sound Navigation and Ranging (SONAR) system, a technology that measures distance to an object through pulse-echo sending and returning sound [19].

The principles of pulse-echo technology, first developed for SONAR, became the basis for the medical application of ultrasound (frequency  $\geq 20$ kHz) during and following World War II. In 1942, neurologist and physicist Karl Dussik first used ultrasound for diagnosing brain tumours at the University of Vienna. In 1948, its application in gallstone diagnostics was first reported by George Ludwig. Ultrasound scanners have increasingly been used in a range of medical specialties over the years, with widespread use in abdominal imaging, and echocardiography, for visualization of the heart. Another milestone in this evolution was the contribution of Ian Donald, whose invention of diagnostic ultrasound revolutionized obstetrics and gynaecology in the mid-20th century [20]. In the post-war period, ceramic resonators were designed with barium titanate to exploit its high permittivity and piezoelectric coefficients and, in the 1950s, lead zirconate titanate (PZT) ceramic replaced barium titanate for use in generating and receiving sound waves [21].

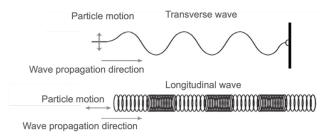

In solids, sound waves can travel in two ways: as longitudinal waves, where particles oscillate in the same plane as the wave, and as shear (or transverse) waves, where particles move perpendicular to the wave's path, as shown in Figure 2-1. For shear waves to exist, the material needs to be rigid enough for particles to "pull" on their neighbours. Fluids, like water or air, do not have this rigidity so they can support only longitudinal waves. Since the human body is mostly water, tissues are usually treated are usually treated as fluids in medical ultrasound and shear waves are often ignored. However, when designing ultrasound transducers, shear waves matter because the materials used in the transducer are solid and both types of waves can travel through them [19].

Figure 2-1: Illustration of Shear and Longitudinal Waves [19].

Human tissues like fat, muscle and blood each interact with sound waves in their own way which is the principle of ultrasound imaging. When an ultrasound machine sends a wave pulse into the body, part of the wave keeps traveling while the rest is reflected partially every time it is incident on a different layer of tissue. The transducer detects for these echoes and, by measuring when they return, the system calculates how deep each structure is. This process helps create the detailed images seen in an ultrasound scan [19].

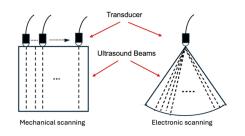

Figure 2-2: Steering the beam and creating an ultrasound image.

To create an ultrasound image, the transducer needs to send sound waves in different directions and capture the echoes that come back. This process, called beam steering, can be done in two ways: mechanically or electronically. As shown in Figure 2-2, mechanical beam steering moves the transducer using a motor to scan the area, but this method has drawbacks. In contrast, electronic beam scanning controls the timing of sound waves sent from different parts of the transducer, allowing for more precise imaging without needing moving parts. While this approach is more accurate, it also makes the device more complex [19].

#### 2.2 Micromachined Ultrasound Transducers

A notable development in ultrasound imaging was seen in the adoption of MEMS technologies. These offer possibilities as a viable alternative to traditional bulk transducers, improving manufacturing processes and sometimes overall performance, paving the way for alternative ultrasound technology [22].

MEMS-based ultrasound transducers have the advantage that they use technology similar to complementary metal-oxide-semiconductors (CMOS). This means they can theoretically

be manufactured at a lower cost, with greater design flexibility. Because MEMS and CMOS can be integrated into the same package, unwanted electrical interference can sometimes be reduced while making the system smaller, lighter, and more energy-efficient [23].

Among the different types of MUTs, the two most common are CMUTs and PMUTs. These may helped overcome many of the limitations found in traditional bulk ultrasound transducers. In particular, they may offer better control over operating frequency [24] and provide a closer acoustic impedance match with biological tissues, which improves imaging performance [25]. However, MUTs are not used only for medical applications. They have been proposed for fluid sensing to measure viscosity, density, and flow rate [26], [27], [28], [29], as well as in humidity sensors [30], eye-tracking systems [31], and particle manipulation [32]. They may also have a role in chemical and gas detection [33], monitoring structural health in buildings and materials [34], [35] and in airborne technologies like gesture recognition and haptic feedback [36]. With their versatility and efficiency, MUTs maybe useful beyond just ultrasound imaging, making them potential technology for the future. This will be elaborated in detail in the following sections.

#### 2.2.1 Principle of operation

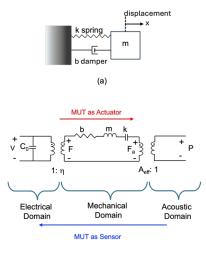

Medical ultrasound involves the use of electro-acoustic signals, typically in the MHz range, for diagnostic purposes. To convert electrical signals into sound waves and vice versa, transducers act as both transmitters and receivers. In this regard, CMUTs and PMUTs function as actuators and sensors, utilizing a vibrating membrane in a flexural mode. To better understand how these devices operate in the mechanical domain, they can be modelled using a mass-spring-damper system, as shown in Fig. 2-3(a).

(b)

Figure 2-3: (a) Model of mass-spring and damper system (b) simplified Mason model.

Here, the membrane's flexion is approximated as the piston-like motion of a rigid plate with mass m. When an external force is applied, the membrane bends and generates an opposing force to restore equilibrium. This restoring effect can be represented by a spring with an elastic coefficient k. Additionally, energy losses, including acoustic and mechanical coupling losses, can be accounted for using a damper with a damping coefficient b. By applying Newton's second law, the flexural motion of the MUT membrane can be described through a second-order differential equation as below:

$$m\frac{d^2x}{d^2t} + b\frac{dx}{dt} + kx = F$$

Eq. 2.1

Here, *x* represents the flexural displacement of the MUT membrane, while *F* denotes the total force acting on it, which includes contributions from acoustic and electrostatic forces, as well as forces generated by the piezoelectric effect (if present) and ambient pressure. From Eq. 2.1, the MUT's resonant frequency can be determined. While the mass-spring-damper model effectively captures the membrane's flexural motion, it does not account for the transducer's electrical characteristics, which are essential for analysing and designing its front-end electronics. To address this, the equivalent circuit model, known as the Mason model Figure 2-3 (b) can be used. This provides a linearized representation of the electromechanical-acoustic behaviour of the transducer around a bias point, without considering nonlinear distortion effects [37], [38].

Despite its simplifications, the Mason model provides a framework for approximating MUT performance, allowing for the prediction of electrical and mechanical losses, as well as interactions between the transducer and the surrounding medium. In this model, the equivalent inductor, capacitor, and resistor correspond to the mass, spring, and damper of the mechanical system, respectively. The same Mason model applies whether the transducer operates as an actuator (transmitter, TX mode) or as a sensor (receiver, RX mode). In the electrical domain, a voltage (V) is either applied to or sensed by the MUT, depending on whether it functions as a transmitter or receiver. The transducer's static capacitance is represented by  $C_{\theta}$ . To bridge the electrical and mechanical domains, an ideal transformer with a ratio of  $1:\eta$  is used, where  $\eta$  is the electromechanical coupling coefficient. Similarly, the mechanical domain is linked to the acoustic domain through another ideal transformer with a ratio of  $A_{df}$ :1, where  $A_{df}$  represents the effective area of the transducer membrane. This transformation process enables the conversion of voltage into force, which is then further translated into acoustic pressure [22].

The mass-spring-damper and Mason models effectively capture the fundamental working principles of MUTs; however, they involve significant simplifications and do not fully account for nonlinear behaviours and other non-idealities present in the device. To achieve more precise design and characterization of MUTs, the finite element method (FEM) - both static and dynamic - can be employed [26].

The next sections provide a more detailed explanation of the physics behind PMUTs and CMUTs, with a particular emphasis on their behaviour in biomedical applications.

#### 2.2.2 Micro-machined ultrasound transducer

Ultrasonic signals are usually created using one of four main methods: the piezoelectric effect, magnetostriction, the photo-acoustic effect or electrostatics [39]. The most common of these is the piezoelectric effect, which is widely used in PMUTs and traditional bulk PZT transducers. Piezoelectricity occurs in certain materials, like piezoceramics and crystals, which change shape when an electric field is applied. At the same time, if these materials are physically can pressed or stretched, they generate an electrical charge [33]. This phenomenon can be explained using the fundamental equations of piezoelectricity:

$$S = [s^{E_e}]T_s + [d^{T_s}]E_e$$

Eq. 2.2

and

$$D = [d^{E_e}]T_s + [\varepsilon^{T_s}]E_e$$

Eq. 2.3

In this context, *S* and *T<sub>S</sub>* represent strain and stress, while  $E_e$  stands for the electric field and *D* represents charge density. The behaviour of the material is determined by three key matrices: [*s*], which defines compliance constants (measured in m<sup>2</sup>/N); [*ε*], which describes permittivity (measured in F/m); and [*d*], which contains the piezoelectric coefficients (measured in C/N). The way PMUTs work is based on flexural vibrations triggered by either  $d_{31}$  or  $d_{33}$  mode excitation. The  $d_{31}$  mode refers to sideways contraction and expansion, while the  $d_{33}$  mode involves movement perpendicular to the surface when voltage is applied. These vibrations are what generate ultrasonic waves when electricity is supplied and, in turn, create an electrical signal when exposed to an incoming ultrasound wave. To measure how effectively a device converts electrical energy into mechanical motion (and vice versa), the electromechanical coupling coefficient (EMCC) is used. This metric gives a good indication of the device's overall performance [40], [41]. Figure 2-4 shows a basic diagram of a PMUT transducer. It consists of a thin piezoelectric film, typically a few hundred nanometres to a micrometer thick, placed between two electrodes (top and bottom). Beneath this, there is a SiO<sub>2</sub> layer that helps support the piezoelectric film while it operates. This layer also plays an important role in converting sideways stress (from the  $d_{31}$  mode) into perpendicular displacement, allowing the membrane to vibrate in its flexural modes. Underneath these layers, there is a small cavity that is key to how the PMUT resonates. Its size is carefully designed to match the natural vibration frequency of the membrane. The exact resonant frequency of a PMUT depends on several factors, including its shape, size, boundary conditions, internal stress, and mechanical stiffness [42].

Figure 2-4: Schematic of a PMUT cross section.

Enhancing the frequency response of transducers to further shorten their impulse response can significantly improve image resolution and expand the operational range of a given device. Recent advancements in composite materials and single-crystal transducers have been centred around achieving this goal.

#### 2.2.3 Capacitive micro-machined ultrasound transducer

Electrostatic transducers, such as CMUTs, initially were utilized in condenser microphones designed by Wente as early as 1917 [43]. Hunt later provided an in-depth analysis and design principles for electrostatic transducers, emphasizing their ability to achieve a flat and uniform frequency response [44]. In 1996, Ladabaum, Khuri-Yakub, and their team introduced a new way to make ultrasound transducers using surface micromachined technology. By using silicon nitride (Si<sub>3</sub>N<sub>4</sub>) membranes, they developed a more efficient method for creating transducers with a broad frequency response, making them suitable for immersion applications [45].

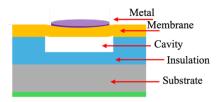

CMUTs operate based on electrostatic transduction, where a vibrating membrane plays a key role in generating and detecting sound waves. This membrane, which contains a conductive layer acting as the top electrode, moves in response to an applied voltage. The bottom electrode is typically part of the conductive substrate, and between them lies a cavity. When voltage is applied, an electric field forms within the cavity, allowing the device to convert electrical energy into mechanical vibrations and vice versa. [22] The membrane's shape—

which can be square, circular, or hexagonal—affects how it vibrates and how efficiently it transmits sound [46], [47], [48]. It is firmly attached at its edges, leaving the middle free to oscillate over the cavity. Depending on the design, the cavity can be vacuum-sealed or filled with air, with an electric field strength reaching several tens of volts per micron or even higher. This strong field contributes to efficient energy conversion [26]. To prevent short circuits, an insulating layer is added between the electrodes, ensuring the device operates safely and reliably. A schematic cross-section of a typical CMUT provides a view of this structure in Figure 2-5.

Figure 2-5: Schematic of a CMUT cross-section.

### 2.2.4 CMUT working principle

At a fundamental level, a CMUT functions similarly to a parallel-plate capacitor, where the top electrode is movable. To generate acoustic pressure waves, the diaphragm is actuated using electrostatic forces ( $F_e$ ), causing it to vibrate in response to an applied voltage,

$$F_e = \frac{-A_e \varepsilon_0 \varepsilon_r V^2}{2(g_{eff} - x)^2}$$

Eq. 2.4

In this setup, the top electrode's area is represented by  $A_e$ , while  $\varepsilon_o$  is the vacuum permittivity, and  $\varepsilon_r$  is the relative permittivity of the insulating and membrane materials, which are assumed to be the same. The applied voltage, V, controls the movement of the top electrode, with x representing its displacement. The effective gap height is calculated as:

$$g_{eff} = \frac{(t_i + t_m)}{\varepsilon_r} + g_0$$

Eq. 2.5

Where  $g_o$  is the initial gap distance when no voltage or external stress is applied,  $t_i$  is the insulator thickness, and  $t_m$  is the membrane thickness. By adjusting V, the electrostatic force changes dynamically, causing the diaphragm to vibrate and generate ultrasound waves [49]. When the CMUT operates as a sensor, external acoustic waves make the membrane oscillate, leading to capacitance variations. These variations are then converted into a changing voltage or current, allowing the device to detect sound waves [26].

Assuming the membrane moves by a displacement of x and the cavity is a vacuum, the CMUT can be modelled as an equivalent parallel-plate capacitor, with its capacitance determined by a standard equation [49].

$$C = \frac{A_e \varepsilon_0 \varepsilon_r}{g_{eff} - x}$$

Eq. 2.6

The operation of a CMUT, whether as an actuator or a sensor, follows the principles of Newton's second law and an electromechanical model, which results in a second-order differential equation describing its behaviour. This equation is non-linear in terms of the membrane's movement but, in most practical cases, the CMUT is operated with a large DC bias voltage ( $V_{DC}$ ), which is then modulated by a small ac voltage ( $V_{ac}$ ). This means the total applied voltage can be written as  $V = V_{DC} + V_{ac}$  in actuation mode. This voltage combination causes the membrane to vibrate and generate ultrasound waves, while in sensing mode, incoming acoustic pressure causes the membrane to oscillate, leading to variations in capacitance. To simplify analysis, the electrostatic force acting on the membrane is often linearized as a function of the DC bias voltage to make calculations more manageable [49].

When a DC bias voltage is applied to the top electrode, it creates an electric field that pulls the membrane downward, allowing it to move in a spring-like motion. However, if this voltage becomes too high, the membrane's displacement increases to the point where the electrostatic force exceeds the physical stiffness of the membrane, causing it to collapse onto the bottom electrode. This is known as the pull-in phenomenon, a condition where the membrane can no longer return to its original position because the attraction between the electrodes is too strong [50]. The voltage at which this collapse happens is called the collapse voltage, marking the limit beyond which stable operation is no longer possible:

$$V_{collapse} = \sqrt{\frac{8K_p g_{eff}^3}{27\varepsilon_0 \varepsilon_R A}}$$

Eq. 2.7

In this case,  $K_p$  represents the spring constant in the mass-spring model, which helps describe how the membrane moves [49]. While collapse mode is usually avoided because of its nonlinear behaviour, it has some advantages. When properly controlled, it can generate higher output pressure and improve electromechanical coupling, making it a useful alternative to conventional operation [50]. There are three main types of collapse mode, each working slightly differently: traditional collapse mode, collapse snap-back mode, and deep collapse mode [50]. In traditional collapse mode, the centre of the membrane touches the substrate, restricting its movement but still allowing controlled vibrations. Collapse snap-back mode starts by putting the CMUT into a collapsed state, but by carefully adjusting the voltage, the membrane is allowed to detach from the substrate, restoring some of its motion. Deep collapse mode happens when the applied ac voltage is higher than the collapse voltage, causing the membrane to push even further beyond its normal collapse point. The choice of which collapse mode to use depends on the specific application of the transducer. Since each mode affects things like sensitivity, efficiency, and operating range, selecting the right one helps ensure that the CMUT performs optimally for its intended application [22]. The equations for electrostatic force and capacitance assume ideal conditions such as perfectly parallel plates, vacuum-filled cavities, and uniform material properties. In practice, effects like dielectric charging, membrane curvature, and nonuniform electric fields can cause deviations, making advanced simulations and experimental validation necessary for accurate CMUT performance prediction.

## 2.3 Comparison between CMUT and PMUT

Compared to traditional piezoelectric transducers, CMUT arrays offer several advantages as well as certain challenges. A summary of these aspects is provided in Table 2-1.

| Feature               | CMUT                                                                            | РМИТ                                                           |

|-----------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------|

| Impedance<br>Matching | Highly efficient in both air and liquids, improving overall energy performance. | Less optimized, leading to lower energy efficiency.            |

| Bandwidth             | Wide bandwidth (over 100%), giving detailed and sharper images.                 | Moderate bandwidth (60-80%), slightly less detail.             |

| Image Quality         | Sharp images, good contrast, and an expanded field of view.                     | Acceptable images but missing CMUT's sharpness and contrast.   |

| Manufacturing         | Microfabrication allows for ultra-compact, high-frequency components.           | Traditional fabrication, resulting in<br>larger elements       |

| Cost                  | Cost-effective when mass-produced                                               | Can be more expensive due to<br>fabrication complexity         |

| Integration           | Easily integrates with modern circuits and 3D stacking                          | Limited integration with modern electronic circuits            |

| Sensitivity           | Low sensitivity, limiting deep imaging performance                              | Higher sensitivity, better for detecting weaker signals        |

| Penetration           | Struggles to reach deep tissues effectively                                     | More effective at penetrating deeper tissues                   |

| Reliability           | Can suffer from charging issues over time                                       | More stable and less affected by<br>charging issues            |

| Interference          | Highly prone to cross-talk and acoustic wave interference                       | Less cross-talk and interference,<br>providing clearer signals |

Table 2-1: Comparison between CMUT and PMUT.

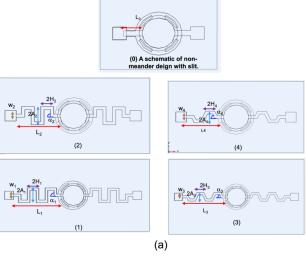

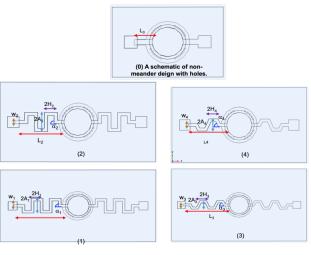

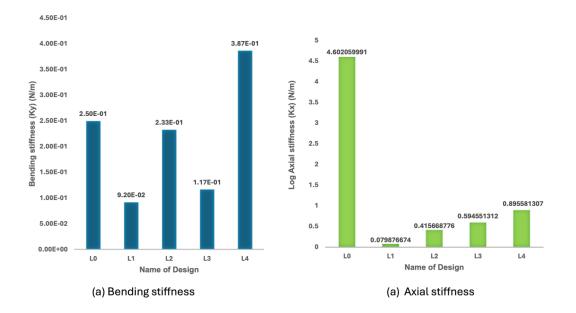

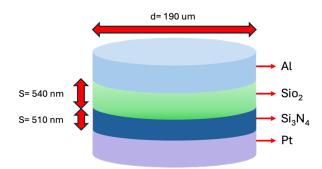

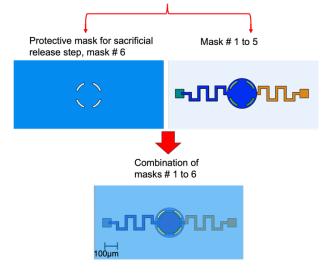

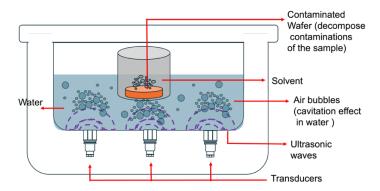

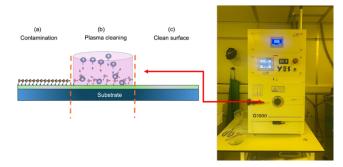

One key benefit is their improved impedance matching in both air and fluid environments [51], [52], which allows for wider bandwidths. While piezoelectric transducers typically have a fractional bandwidth (*FBW*) of 60%-80%, CMUTs can easily exceed 100%, significantly enhancing signal transmission and reception. Bandwidth plays a crucial role in image resolution, as a wider bandwidth leads to higher resolution images. Studies comparing CMUT arrays with piezoelectric transducers in in-vitro imaging have shown that CMUTs can provide better radial resolution, a notable improvement in contrast, and a wider field of view [53], [54], [55]. A great advantage of CMUT operation is that by adjusting the DC bias voltage, you can selectively activate specific elements in the CMUT array. This makes it easy to switch between different sub-apertures while using the same set of TX/RX electronics, adding more flexibility to the system. On top of that, recent advancements have improved sensitivity [56] and significantly reduced second harmonic distortion [57]. These advantages make CMUTs highly promising for ultrasound imaging applications, particularly in areas requiring high detail and accuracy.