Hao, Yijia (2025) *Analog integrated circuit design empowered by artificial intelligence techniques: from building blocks to small systems.* PhD thesis.

https://theses.gla.ac.uk/85613/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses

<a href="https://theses.gla.ac.uk/">https://theses.gla.ac.uk/</a>

research-enlighten@glasgow.ac.uk

# Analog Integrated Circuit Design Empowered by Artificial Intelligence Techniques: From Building Blocks to Small Systems

## Yijia Hao

# SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

JAMES WATT SCHOOL OF ENGINEERING

COLLEGE OF SCIENCE AND ENGINEERING

## Abstract

Analog integrated circuit (IC) design remains a major bottleneck in modern electronic systems due to its reliance on expertise-driven iteration and the growing complexity of performance, robustness, and variability requirements. This dissertation aims to advance artificial intelligence (AI)-driven analog IC design methodologies across three hierarchical levels: building blocks, subsystems, and systems.

At the block level, a design—insight—aware comparison is conducted across representative circuits including a StrongARM comparator, two Miller-compensated operational amplifiers, and an LC voltage-controlled oscillator (VCO) to benchmark AI-assisted optimization against conventional systematic flows. Post-layout and silicon measurement results demonstrate that AI-assisted frameworks can achieve superior performance and robustness while preserving design intent.

At the subsystem level, the first AI-driven co-design flow for VCO–LDO integration is introduced. By simultaneously optimizing both blocks under supply—noise coupling and frequency—pushing effects, the method improves phase noise, figure of merit (FoM), and runtime efficiency compared to sequential design, demonstrating the value of cross-block optimization.

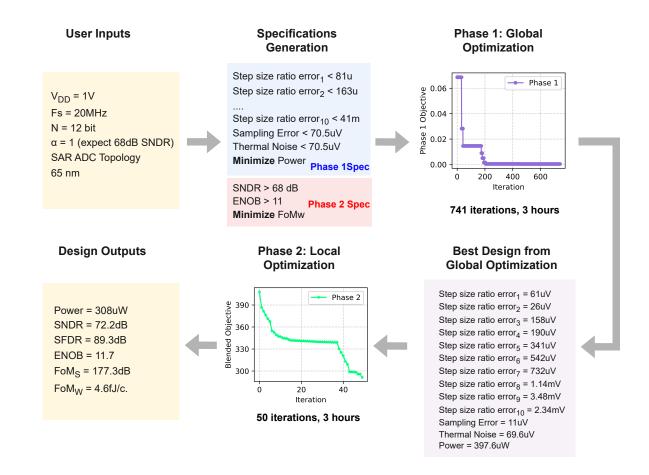

At the system level, a global–local optimization framework with multi-fidelity simulation is proposed for asynchronous successive-approximation register analog-to-digital converter. This methodology cascades surrogate model-based global exploration with parallel pattern search refinement, achieving competitive FoM across 12 design cases (7–12 bit, up to 250 MHz) with significantly reduced runtime and minimal manual effort.

Together, these contributions establish a practical pathway for AI-driven analog IC design automation. By combining black-box optimization, learning-based acceleration, and designer-in-the-loop validation, this work demonstrates measurable gains in design quality, robustness, and time efficiency, offering a foundation for future system-level EDA tools.

## Contents

| $\mathbf{A}$  | bstra                    | ct       |                                              | iii  |

|---------------|--------------------------|----------|----------------------------------------------|------|

| $\mathbf{Li}$ | List of Publications vii |          |                                              |      |

| $\mathbf{Li}$ | st of                    | Tables   |                                              | ix   |

| Li            | st of                    | Figures  | S                                            | xi   |

| A             | cknov                    | wledgen  | nents                                        | xii  |

| D             | eclar                    | ation    |                                              | xiv  |

| $\mathbf{A}$  | bbre                     | viations |                                              | xv   |

| 1             | Intr                     | oductio  | on                                           | 1    |

|               | 1.1                      | Analog   | Circuit Design Automation                    | . 1  |

|               | 1.2                      | Optimi   | zation-Based Analog IC Sizing                | . 2  |

|               | 1.3                      |          | nges and Research Objectives                 |      |

|               |                          | 1.3.1    | Block Level Sizing                           | . 4  |

|               |                          | 1.3.2    | Subsystem Co-Design                          | . 5  |

|               |                          | 1.3.3    | System Level Sizing                          |      |

|               | 1.4                      | Main C   | Contributions                                | . 8  |

|               | 1.5                      | Thesis   | Outline                                      | . 9  |

| 2             | Bac                      | kgroun   | d and Literature Review                      | 11   |

|               | 2.1                      | Backgr   | ound on Analog Circuits                      | . 11 |

|               | 2.2                      | Three (  | Generations of Analog Circuit Design Methods | . 14 |

|               |                          | 2.2.1    | Generation I: Quadratic Hand Analysis        | . 14 |

|               |                          | 2.2.2    | Generation II: The $g_m/I_D$ Method          | . 15 |

|               |                          | 2.2.3    | Generation III: Optimization-Centric Sizing  | . 16 |

|               |                          | 2.2.4    | Common Verification Loop                     | . 17 |

|               |                          | 2.2.5    | Comparison                                   | . 17 |

|               | 2.3                      | Local (  | Optimization Methods                         | . 17 |

|               |                          | 2.3.1    | Gradient-Based Methods                       | . 18 |

|               |                          | 2.3.2    | Nelder-Mead (Simplex)                        | . 18 |

|   |      | 2.3.3 Pattern Search Method                                   | )  |

|---|------|---------------------------------------------------------------|----|

|   |      | 2.3.4 Summary                                                 | L  |

|   | 2.4  | Global Optimization Methods                                   | 2  |

|   |      | 2.4.1 Evolutionary and Swarm-Based Heuristics                 | 2  |

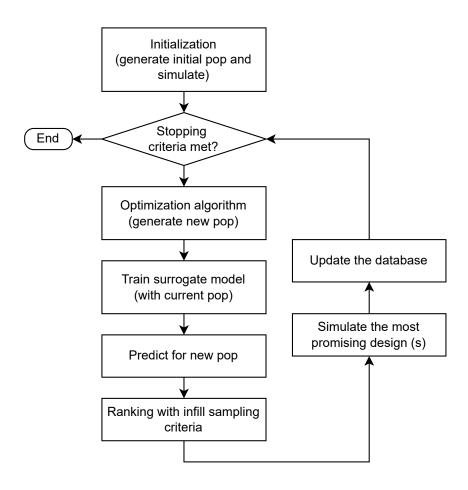

|   |      | 2.4.2 Surrogate Model-Assisted Optimization                   | 1  |

|   |      | 2.4.3 ANN vs. GPR                                             | )  |

|   | 2.5  | Summary                                                       | )  |

| 3 | Ass  | essing AI-Empowered Optimization Techniques for Analog Build- |    |

|   | ing  | Block Sizing 31                                               | Ĺ  |

|   | 3.1  | Introduction                                                  | L  |

|   | 3.2  | Contributions                                                 | }  |

|   | 3.3  | The AI-Empowered Analog Building Block Sizing Approach        | Į. |

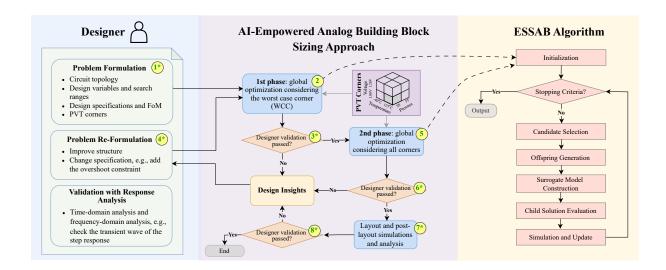

|   |      | 3.3.1 AI-Empowered Sizing Framework                           | 1  |

|   |      | 3.3.2 Global Optimization Engine                              | ;  |

|   | 3.4  | Comparative Study Using Four Design Cases                     | 7  |

|   |      | 3.4.1 StrongARM Latch Comparator                              | 3  |

|   |      | 3.4.2 Two-Stage Miller-Compensated Op-Amp (3.3 V)             | 1  |

|   |      | 3.4.3 Two-Stage Miller-Compensated Op-Amp (1.8 V)             | 2  |

|   |      | 3.4.4 LC Oscillator                                           | j  |

|   |      | 3.4.5 Discussion                                              | 3  |

|   | 3.5  | Summary                                                       | 2  |

| 4 | Sub  | osystem Design: VCO with LDO Integration 63                   | 3  |

|   | 4.1  | Introduction                                                  | }  |

|   | 4.2  | Literature Review                                             | j  |

|   | 4.3  | Contributions                                                 | j  |

|   | 4.4  | Problem Formulation                                           | j  |

|   |      | 4.4.1 Architecture of LDO-VCO                                 | j  |

|   |      | 4.4.2 Design Variables                                        | 7  |

|   |      | 4.4.3 Testbench and Measures                                  | )  |

|   |      | 4.4.4 Objective and Constraints                               | )  |

|   | 4.5  | AI-Driven Co-Design Method                                    | )  |

|   |      | 4.5.1 Sizing Flow and Considerations                          | )  |

|   |      | 4.5.2 Sizing Algorithm                                        | )  |

|   | 4.6  | Pre-layout Sizing Results and Analysis                        | l  |

|   | 4.7  | Post-Layout Results and Discussion                            | 1  |

|   | 4.8  | Summary                                                       | j  |

| 5 | Syst | tem-Level Design Automation for SAR ADCs 77                   | 7  |

|   | -    | Background                                                    | 7  |

|              | 5.2  | Litera | ture Review                                                     | 78  |

|--------------|------|--------|-----------------------------------------------------------------|-----|

|              | 5.3  | Contri | ibutions                                                        | 79  |

|              | 5.4  | Archit | ecture and Design Considerations of SAR ADC                     | 80  |

|              |      | 5.4.1  | Architecture and Operation                                      | 81  |

|              |      | 5.4.2  | Design Considerations and Trade-Offs                            | 86  |

|              | 5.5  | Metho  | odology                                                         | 88  |

|              |      | 5.5.1  | Overview                                                        | 88  |

|              |      | 5.5.2  | Automatic Specification Derivation                              | 89  |

|              |      | 5.5.3  | Low-Cost Simulation-Based Global Optimization                   | 92  |

|              |      | 5.5.4  | Fast Local Optimization Using Parallel Multi-Fidelity Transient |     |

|              |      |        | Simulation                                                      | 94  |

|              | 5.6  | Exper  | imental Results                                                 | 97  |

|              | 5.7  | Summ   | ary                                                             | 99  |

| 6            | Con  | clusio | ns and Future Work                                              | 101 |

|              | 6.1  | Analog | g Bulding Block Sizing                                          | 101 |

|              | 6.2  | LDO a  | and VCO Co-Design                                               | 103 |

|              | 6.3  | SAR A  | ADC Design                                                      | 104 |

| $\mathbf{A}$ | ppen | dices  |                                                                 | 105 |

|              | A    | Tables | 3                                                               | 105 |

## List of Publications

- 1. M. Chen, Y. Hao, et al., "Trade-off-Aware Analog Circuit Sizing Based on a Multitask Surrogate Model-Assisted Evolutionary Algorithm," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2025. (Under Review)

- 2. Y. Hao, et al., "A Global–Local Optimization Approach for Asynchronous SAR ADC Design," IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II), 2025. (Under Review)

- 3. Y. Hao, et al., "From Systematic to Intelligent: Assessing AI-Empowered Optimization Techniques for Analog Building Block Sizing," IEEE Access, 2025.

- 4. Y. Hao, et al., "An AI-Driven EDA Algorithm-Empowered VCO and LDO Co-Design Method," IEEE International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design (SMACD), 2025.

- 5. J. Wang, Y. Hao, et al., "Pose-Guided Focal Loss for Enhancing Vision Transformers in Continuous Sign Language Recognition," IEEE 35th International Workshop on Machine Learning for Signal Processing (MLSP), 2025.

- 6. Y. Hao, et al., "Integrating AI in Engineering Education: A Comprehensive Review and Student-Informed Module Design for UK Students," IEEE Transactions on Education, 2025.

- 7. A. Alexandrou, Y. Hao, et al., "Properties of Textured Piezoceramics Measured with Miniature Samples," IEEE International Ultrasonics, Ferroelectrics, and Frequency Control Symposium (UFFC), 2024.

- 8. Y. Hao, et al., "Design of a Two-Stage Miller-Compensated Operational Amplifier Using an EDA Tool-Centered Approach," IEEE International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design (SMACD), 2024.

## List of Tables

| 2.1 $2.2$  | A comparison between static and dynamic analog circuits                                                                                      | 12<br>30 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | Design variables and search ranges of StrongARM latch comparator Pre-layout performance values of the design obtained by AI-empowered method | 40       |

|            | and the reference design of StrongARM latch comparator                                                                                       | 41       |

| 3.3        | Post-layout performance values of the AI-empowered design (left) and the                                                                     |          |

|            | reference design of StrongARM latch comparator (right)                                                                                       | 43       |

| 3.4        | Design variables and search ranges of two-stage Miller-compensated op-amp                                                                    | 46       |

| 3.5        | Pre-layout performance values of the AI-empowered designs and the reference                                                                  |          |

|            | design of the two-stage Miller-compensated op-amp                                                                                            | 47       |

| 3.6        | Measured performance values of the AI-empowered design and the reference                                                                     |          |

|            | design of the two-stage Miller-compensated op-amp                                                                                            | 50       |

| 3.7        | Design variables and search ranges of low power design                                                                                       | 53       |

| 3.8        | Pre-layout performance values of the AI-empowered 3.3 V design and 1.8 V                                                                     |          |

|            | design                                                                                                                                       | 54       |

| 3.9        | Measured performance values of the AI-empowered 3.3 V design and 1.8 V                                                                       |          |

| 3.10       | design of the two-stage Miller-compensated op-amp                                                                                            | 54       |

|            | amplifier and the state-of-the-art                                                                                                           | 55       |

| 3.11       | Design variables and search ranges of the CMOS cross-coupled LC oscillator                                                                   | 58       |

|            | Performance values of the AI-empowered design and the reference design (pre-                                                                 |          |

|            | layout simulation results) of the CMOS cross-coupled LC oscillator                                                                           | 59       |

| 3.13       | Performance values of the AI-empowered design (measurement result) of the                                                                    |          |

|            | CMOS cross-coupled LC oscillator and the state-of-the-art                                                                                    | 60       |

| 3.14       | Summary of the comparison of typical contemporary AI-empowered and con-                                                                      |          |

|            | ventional systematic manual sizing methods based on the four case studies                                                                    | 61       |

| 4.1        | Design variables and search ranges of the CMOS cross-coupled LC oscillator                                                                   |          |

|            | and the LDO                                                                                                                                  | 68       |

| 4.2        | Specifications and pre-layout simulation results of the sequentially and co-                                                                 |          |

|            | designed LDO-VCO                                                                                                                             | 71       |

| 4.3        | Specifications and post-layout simulation results of the co-designed LDO-VCO.                                                                | 75       |

| 5.1        | Summary of specifications used in optimization                                                                                               | 92       |

| 5.2 | Simulation performance versus number of segments $M$ with a 12-bit 20 MHz   |

|-----|-----------------------------------------------------------------------------|

|     | SAR ADC                                                                     |

| 5.3 | Comparison with prior SAR ADC designs                                       |

| 1   | Pre-layout performance comparison of the AI-empowered design and the ref-   |

|     | erence design of the two-stage Miller-compensated op-amp with an additional |

|     | area constraint                                                             |

## List of Figures

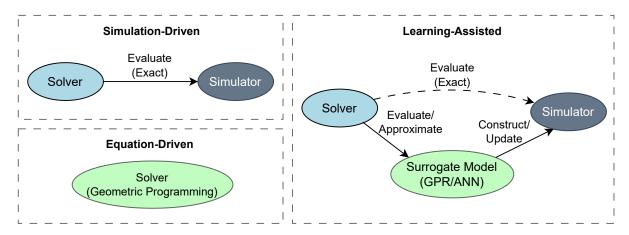

| 1.1  | The design optimization paradigms in analog circuit sizing                      | 3  |

|------|---------------------------------------------------------------------------------|----|

| 2.1  | The $g_m/I_D$ based method                                                      | 15 |

| 2.2  | Three generations of analog design methods                                      | 18 |

| 2.3  | The illustration of PS in a 2-D problem                                         | 20 |

| 2.4  | The surrogate model-assisted optimization flow                                  | 24 |

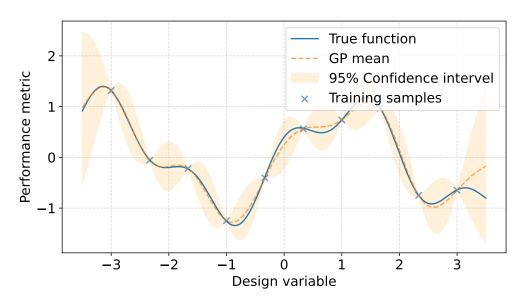

| 2.5  | An 1D GPR example                                                               | 26 |

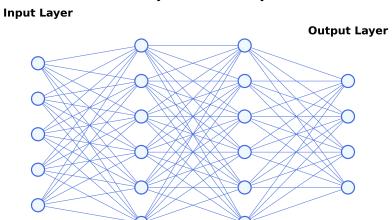

| 2.6  | An ANN with two hidden layers                                                   | 28 |

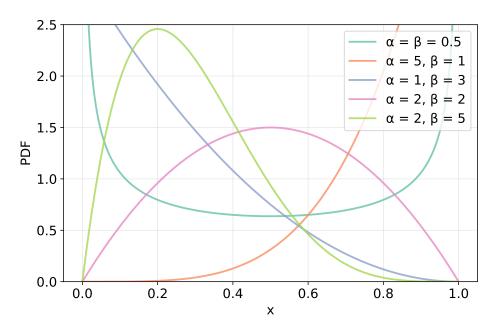

| 2.7  | The illustration of Beta distribution                                           | 29 |

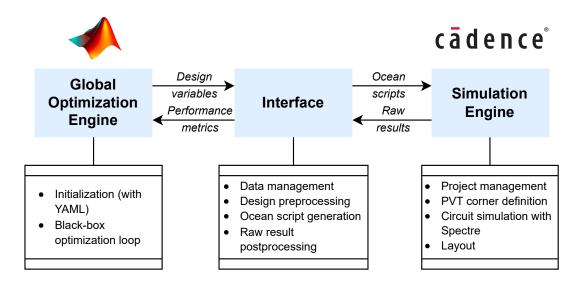

| 3.1  | The flow diagram of the AI-empowered analog building block sizing approach.     | 34 |

| 3.2  | Workflow of the experimental implementation                                     | 38 |

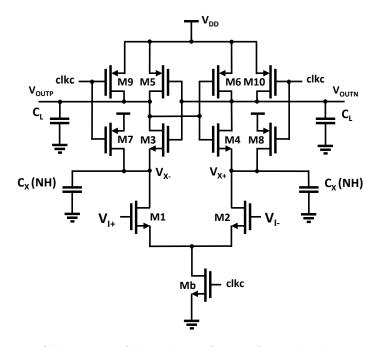

| 3.3  | Schematic of the classic StrongARM latch comparator                             | 39 |

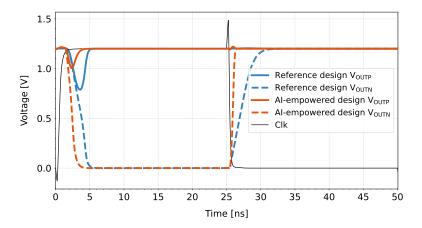

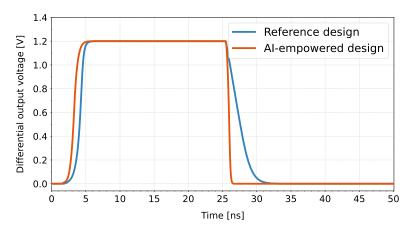

| 3.4  | Transient response of the AI-empowered design and the reference design [94]     |    |

|      | at output nodes $V_{OUTP}$ and $V_{OUTN}$                                       | 42 |

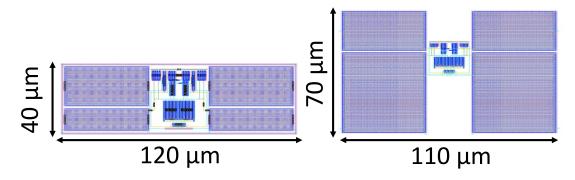

| 3.5  | Layouts for the AI-empowered design and the reference design [94] of the        |    |

|      | StrongARM latch comparator                                                      | 42 |

| 3.6  | Comparison of the post-layout responses of the AI-empowered design and the      |    |

|      | reference design [94] of the StrongARM latch comparator                         | 43 |

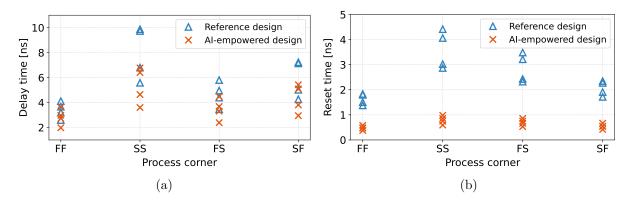

| 3.7  | Comparison of the speed of the AI-empowered design and the reference design     |    |

|      | [94] across 16 corners of the StrongARM latch comparator, with post-layout      |    |

|      | (a) delay time and (b) reset time grouped by four process corners               | 44 |

| 3.8  | Schematic of the two-stage Miller-compensated op-amp. The devices shown in      |    |

|      | gray (M12–M14) are auxiliary transistors used for startup and shutdown control. | 45 |

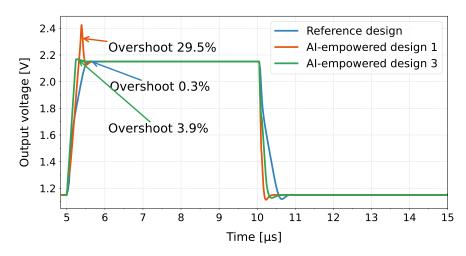

| 3.9  | A comparison of the op-amp unity-gain step responses. The input step size is    |    |

|      | 1 V                                                                             | 48 |

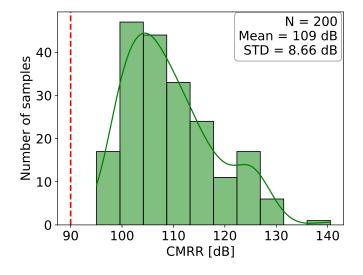

| 3.10 | CMRR of the AI-empowered design 3rd iteration                                   | 48 |

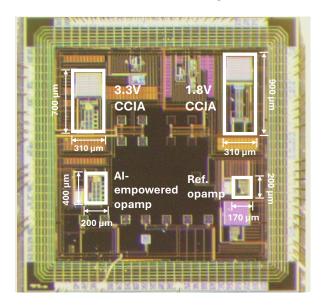

| 3.11 | Chip microphotograph of the reference design, the AI-empowered design, 3.3V     |    |

|      | CCIA, and 1.8V CCIA on the same die                                             | 50 |

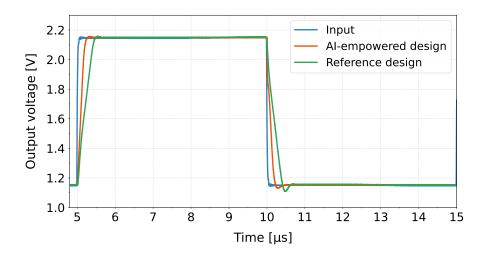

| 3.12 | Comparison of the measurement results of transient responses between the AI-    |    |

|      | empowered design and the reference design of the two-stage Miller-compensated   |    |

|      | op-amp                                                                          | 51 |

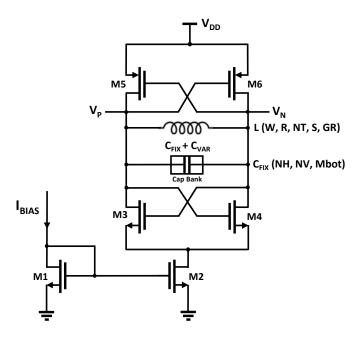

| 3.13 | Schematic of the CMOS cross-coupled LC oscillator. An 8-bit capacitor bank      |    |

|      | is used for frequency tuning                                                    | 57 |

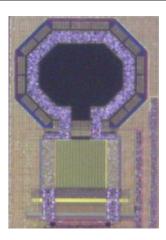

| 3.14 | Chip microphotograph of the AI-empowered oscillator design                            | 59 |

|------|---------------------------------------------------------------------------------------|----|

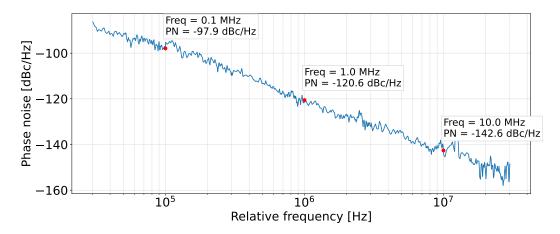

| 3.15 | The measured PN performance of the AI-empowered design of the oscillator              | 60 |

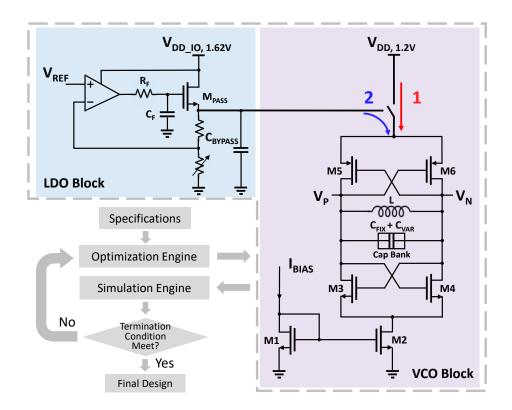

| 4.1  | The VCO and LDO co-design method including the schematic diagram of the               |    |

|      | LC-tank VCO with an integrated LDO. Two design approaches: the sequen-                |    |

|      | tial approach, which involves two distinct design phases, and the co-design           |    |

|      | approach, which optimizes both building blocks simultaneously                         | 67 |

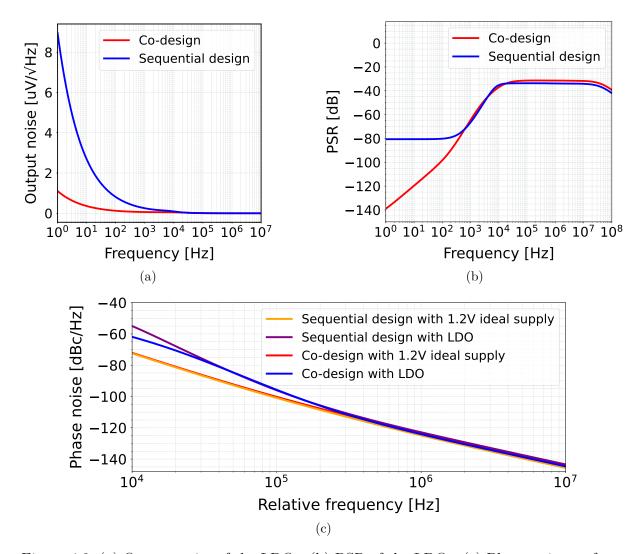

| 4.2  | (a) Output noise of the LDOs. (b) PSR of the LDOs. (c) Phase noise perform-           |    |

|      | ance of the VCO designs with 1.2 V ideal supply and with LDO                          | 72 |

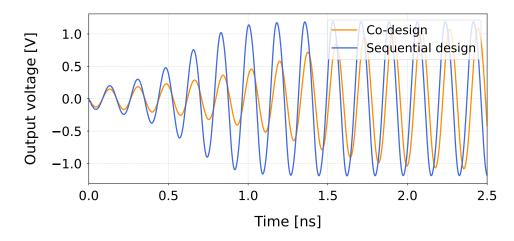

| 4.3  | Oscillation transients for LDO-VCO designs. The co-designed VCO has a                 |    |

|      | slower oscillation start-up and smaller oscillation amplitude                         | 73 |

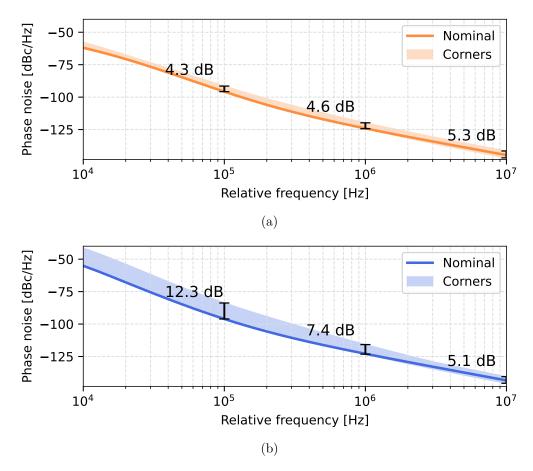

| 4.4  | (a) Corner spread of PN for the co-designed LDO-VCO. (b) Corner spread of             |    |

|      | PN for the sequentially designed LDO-VCO                                              | 74 |

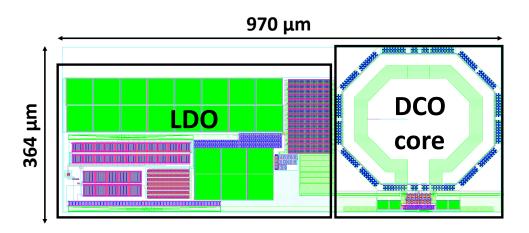

| 4.5  | Co-designed LDO-VCO layout                                                            | 75 |

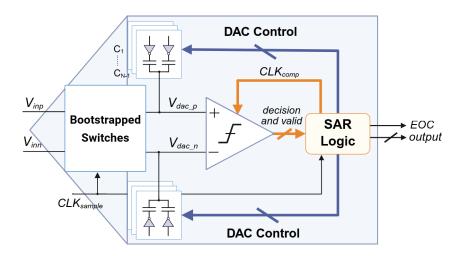

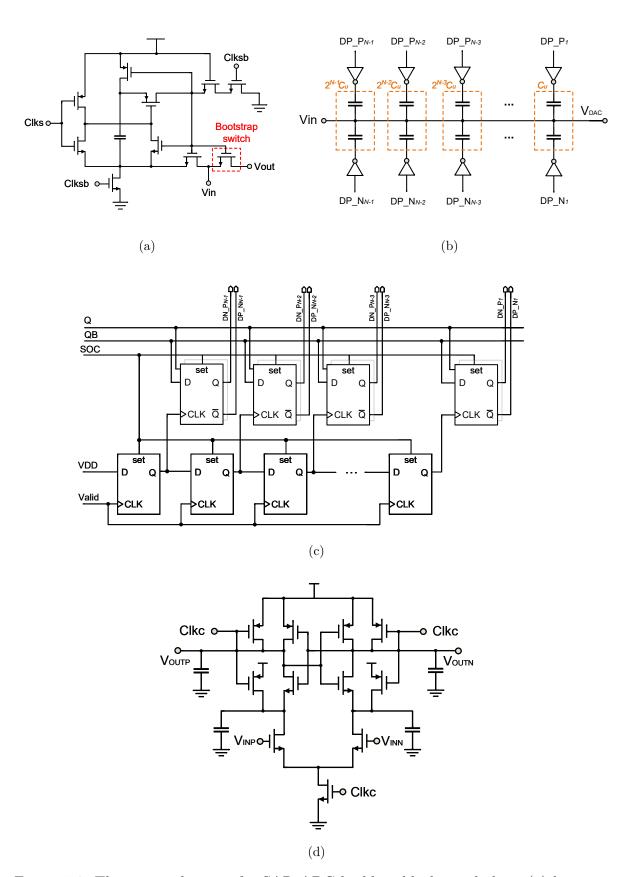

| 5.1  | The architecture of an N-bit asynchronous SAR ADC                                     | 81 |

| 5.2  | The circuit diagram for SAR ADC building blocks, including: (a) bootstrap             |    |

|      | switch, (b) CDAC, (c) SAR logic, and (d) dynamic comparator                           | 83 |

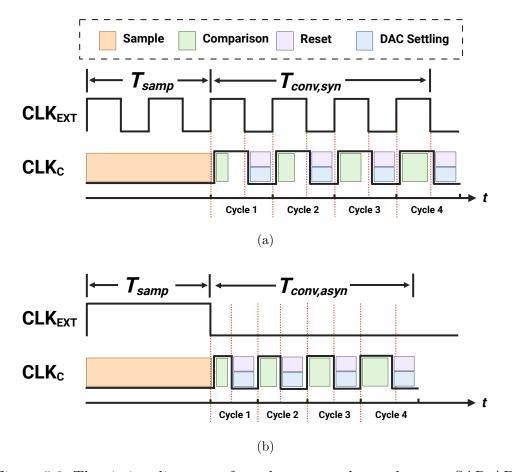

| 5.3  | The timing diagrams of synchronous and asynchronous SAR ADCs                          | 85 |

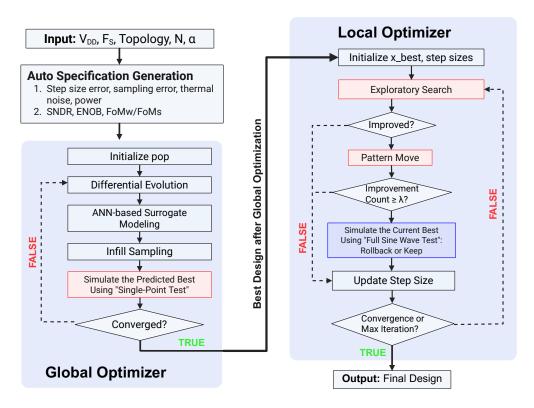

| 5.4  | The flow diagram of the proposed global-local sizing approach. The red blocks         |    |

|      | are based on the single-point test, while the blue block represents the full sine     |    |

|      | wave test                                                                             | 90 |

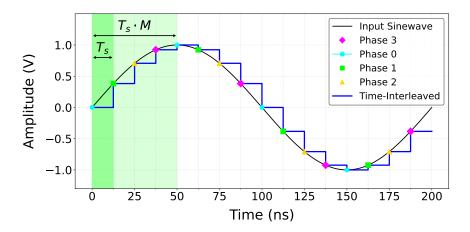

| 5.5  | Illustration of phase-shifted and time-interleaved parallel transient simulation:     |    |

|      | 16-point coverage via $4\times4$ samples                                              | 95 |

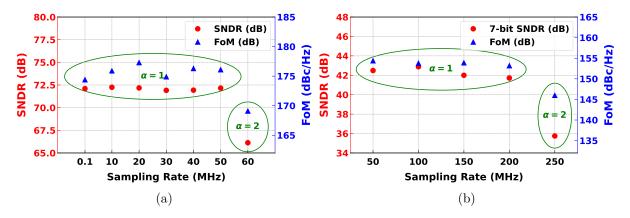

| 5.6  | SNDR and FoM of 12 design cases: (a) 12 bit (b) 7 bit. 10 design cases with           |    |

|      | $\alpha = 1$ and 2 design cases with $\alpha = 2$                                     | 98 |

| 5.7  | An example sizing process for the 12 bit SAR ADC, with the convergence plots $\alpha$ |    |

|      | of both the global and local optimization.                                            | 98 |

## Acknowledgements

This dissertation marks the culmination of several years of research, learning, and perseverance, and it would not have been possible without the guidance and support of many individuals to whom I am sincerely grateful.

First and foremost, I would like to express my heartfelt gratitude to my academic supervisors, Prof. Bo Liu and Prof. Sandy Cochran, as well as my industrial supervisor, Dr. Miguel Gandara, for their invaluable guidance, insightful feedback, and unwavering encouragement throughout this journey. Their patience, expertise, and dedication have been instrumental in shaping both this thesis and my growth as a researcher.

I would like to extend my gratitude to EPSRC for funding this research and supplying the resources that made it possible. This support played a vital role in enabling me to complete this thesis.

My heartfelt thanks go to my collaborators and colleagues, including Dr. Maarten Strackx (Magics Technologies), Dr. Srinjoy Mitra (University of Edinburgh), Prof. Francisco V. Fernandez (Universidad de Sevilla), Mr. Ken Li and Prof. Shaolan Li (Georgia Tech), Prof. Rami Ghannam, Mr. Minyang Chen, Mr. Yushi Liu, and Mr. Jingyan Wang (University of Glasgow). Their valuable input, thoughtful discussions, and generous sharing of expertise have been a constant source of inspiration, and I feel truly fortunate to have worked alongside them. I would also like to thank Dr. Alexandru Moldovan, Dr. Bartas Abaravicius, Dr. Meraj Ahmet and Mr. Huxi Wang for their training and help with my first tapeout and measurement.

I would also like to acknowledge the support of James Watt School of Engineering, whose facilities, resources, and administrative assistance have provided an excellent environment in which to conduct my studies. Special thanks go to FUSE CDT for their help behind the scenes.

Finally, I am deeply thankful to my family, friends, boyfriend for their love, patience, and encouragement during the most challenging times. Their constant support has sustained me through the challenges of this journey and made its completion possible. A special thanks to my cat, whose companionship and occasional distractions reminded me to take breaks and kept my spirits high.

To all who have contributed in ways big and small, I extend my deepest gratitude.

Declaration

Name: Yijia Hao

Registration Number: XXXXXXX

I certify that the thesis presented here for examination for a PhD degree of the University of Glasgow is solely my own work other than where I have clearly indicated that it is the work of others (in which case the extent of any work carried out jointly by me and any other person is clearly identified in it) and that the thesis has not been edited

by a third party beyond what is permitted by the University's PGR Code of Practice.

The copyright of this thesis rests with the author. No quotation from it is permitted

without full acknowledgement.

I declare that the thesis does not include work forming part of a thesis presented success-

fully for another degree.

I declare that this thesis has been produced in accordance with the University of Glasgow's

Code of Good Practice in Research.

I acknowledge that if any issues are raised regarding good research practice based on

review of the thesis, the examination may be postponed pending the outcome of any

investigation of the issues.

Yijia Hao

xiv

## Abbreviations

ABC Artificial Bee Colony AC Alternating Current

ACO Ant Colony Optimization

ADM Differential-Mode Gain

AI Artificial Intelligence

AMS Analog and Mixed-Signal

ANNs Artificial Neural Network

BGR Bandgap Reference

BO Bayesian Optimization

CCIA Capacitively Coupled Instrumentation Amplifier

CDF Cumulative Distribution Function

CMRR Common Mode Rejection Ratio

DACs Digital-to-Analog Converters

DFFs D Flip-Flops

DE Differential Evolution

DNL Differential Nonlinearity

EDA Electronic Design Automation

EI Expected Improvement

ESSAB Efficient Surrogate Model-Assisted Sizing Method for High-

Performance Analog Building Blocks

FFT Fast Fourier Transform FF Fast NMOS/Fast PMOS

FoM Figure of Merit

FS Fast NMOS/Slow PMOS

GA Genetic Algorithm GBW Gain Bandwidth

GPR Gaussian Process Regression

GWO Grey Wolf Optimizer

HT High Temperature

HV High Voltage

ICs Integrated Circuits

INL Integral Nonlinearity

IoT Internet of Things

IRN Input-Referred Noise

LDOs Low-Dropout Regulators

LNA Low-Noise Amplifier

LCB Lower Confidence Bound

LPTV Linear Periodically Time-Varying

LSB Least Significant Bit

LTE Long-Term Evolution

LTI Linear Time-Invariant

LT Low Temperature

LUTs Lookup Tables

LV Low Voltage

MC Monte Carlo

MSB Most Significant Bit NEF Noise Efficiency Factor

NM Nelder-Mead

op-amps Operational Amplifiers

PDF Probability Density Function

PDK Process Design Kit

PFI Probability of Further Improvement

PI Probability of Improvement

PLLs Phase-Locked Loops

PN Phase Noise

PNOISE Periodic Noise

PS Pattern Search

PSO Particle Swarm Optimization PSR Power Supply Rejection

PSRR Power Supply Rejection Ratio

PSS Periodic Steady-State

PVT Process, Voltage, Temperature

RF Radio Frequency

RL Reinforcement Learning

SAR ADCs Successive Approximation Register Analog-to-Digital Convert-

$\operatorname{ers}$

S/H Sample-and-Hold

SC Switched-Capacitor

SerDes Serializer/Deserializer

SF Slow NMOS/Fast PMOS

SNDR Signal-to-Noise and Distortion Ratio

SoC System on Chip

SPGP Sparse Pseudo-Input Gaussian Process

SQP Sequential Quadratic Programming

SS Slow NMOS/Slow PMOS

SSRE Step Size Ratio Error

THD Total Harmonic Distortion

TR Tuning Range

UGB Unity Gain Bandwidth

UCB Upper Confidence Bound

VCOs Voltage-Controlled Oscillators

WCC Worst Case Corner

## Chapter 1

## Introduction

## 1.1 Analog Circuit Design Automation

In modern integrated circuit (IC) design, analog circuit design remains one of the most complex and resource-intensive tasks. High-performance analog blocks, such as operational amplifiers (op-amps), low-dropout regulators (LDOs), comparators, and data converters, require delicate trade-offs among gain, bandwidth, noise, stability, power consumption, and robustness across process, voltage, and temperature (PVT) variations [1]–[3]. Traditional manual flows are based on designer expertise and heuristic iterations, which are increasingly inefficient and error-prone as circuit complexity continues to grow [4]. As a result, automated analog circuit design has become an indispensable research direction, offering the promise of reducing design turnaround time while improving performance, robustness and yield.

The field of electronic design automation (EDA) has a long history. Digital design automation matured rapidly beginning in the 1980s with the advent of logic synthesis, static timing analysis, and automated place-and-route [5], [6]. This maturity allowed digital ICs to scale in complexity and performance, while design cycles were kept manageable [7]. By contrast, analog design automation followed a slower trajectory. Early efforts in the 1980s and 1990s focused on symbolic analysis, sensitivity-based optimization, and quadratic law approximations for MOSFET behavior [8]–[10]. In the 2000s, geometric programming and convex optimization methods [11] provided new avenues, particularly for circuits where design constraints could be expressed as posynomials. However, many analog circuits (e.g., dynamic comparators, oscillators, switched-capacitor filters) exhibit strong nonlinearity, time-varying dynamics, and layout-dependent effects that defy simple convex formulations.

In the last decade, research has increasingly shifted toward simulation-driven optimization and machine learning-assisted frameworks. These approaches leverage SPICE-in-the-loop evaluation, surrogate models, and evolutionary search to explore large design spaces without relying exclusively on analytical equations [12]–[17]. This trend reflects a recognition that accurate modeling of modern CMOS circuits requires high-fidelity simulation data.

Commercial EDA platforms such as Cadence Virtuoso ADE and Synopsys Custom Compiler offer environments for schematic capture, simulation management, layout generation, and PVT verification. While these tools provide automation at the verification and layout levels, true automation at the circuit sizing level remains limited. Designers are still responsible for selecting architectures, biasing strategies, and device dimensions. Built-in optimizers (e.g., gradient descent and heuristic search) are often generic and do not scale effectively to the nonlinear, constraint-rich nature of analog design. Therefore, practical analog design continues to rely heavily on expertise-driven iteration, which is time-consuming, error-prone, and difficult to scale across increasing design complexity and variability. This gap motivates the development of artificial intelligence (AI)-driven optimization methodologies.

## 1.2 Optimization-Based Analog IC Sizing

Analog circuit optimization in this context refers to the systematic selection of design variables (e.g., transistor dimensions, biasing, passive component values) to maximize performance while satisfying constraints such as stability, noise, linearity, and PVT robustness. It is often called sizing in the domain. Unlike digital logic synthesis, analog circuit sizing problem is inherently nonlinear, nonconvex, and strongly affected by PVT variations.

Analog circuit sizing problems can be formulated either as single-objective or multiobjective optimization tasks depending on the design goals [18]. Single-objective optimization [19], [20] focuses on improving a dominant metric, such as minimizing power or maximizing bandwidth, while treating other specifications as constraints. This contrasts with multi-objective optimization [21]–[23], which explicitly formulates competing goals and generates Pareto-optimal trade-off fronts. While multi-objective approaches provide richer design insight, they also incur significantly higher computational cost. In this thesis, only single-objective optimization is considered, targeting one design goal while ensuring all other specifications are satisfied. Over the past two decades, optimization for analog circuit design has evolved from equation-driven formulations to simulation-based methods and, more recently, to learning-assisted approaches, as depicted in Fig. 1.1. Each generation reflects a different balance between interpretability, accuracy, and computational cost.

Figure 1.1: The design optimization paradigms in analog circuit sizing.

Equation-driven methods rely on analytical circuit models and first-order approximations, often cast into convex or geometric programming formulations [11]. These techniques offer high interpretability and computational efficiency, making them effective for early-stage design. However, their accuracy degrades in nanoscale technologies, where velocity saturation, mismatch, and layout parasitics dominate.

Simulation-driven methods embed SPICE simulations directly into optimization loops [15], [16], [24], ensuring high fidelity for dynamic and nonlinear circuits such as comparators, oscillators, and data converters. Their main drawback lies in inefficiency: repeated transient and noise simulations lead to prohibitive runtimes, particularly when PVT corners and Monte Carlo (MC) analyses are included.

To alleviate simulation cost, surrogate or learning-assisted methods approximate circuit responses using statistical or machine learning models. Gaussian process regression (GPR) [25], [26] and artificial neural networks (ANNs) [27] have been adopted within surrogate model-assisted frameworks to accelerate design space exploration. While these methods drastically reduce the number of expensive simulations, they introduce challenges in model fidelity, training overhead, and generalization across design spaces.

Overall, design optimization for analog circuits needs to handle complex performance trade-offs, nonconvex search spaces, and variability-aware robustness, while ensuring accuracy and efficiency. Recent trends move toward hybrid frameworks that combine global and local optimization, multi-fidelity simulations, and parallel computing to achieve both efficiency and accuracy.

## 1.3 Challenges and Research Objectives

Although EDA has evolved over several decades, its application in practical analog circuit design remains limited. Most EDA-driven approaches emphasize algorithm improvement but are often criticized for failing to capture design intent. Consequently, analog design continues to rely on manual iteration and expert intuition, particularly at the subsystem and system levels where strong cross-block interactions exist. Motivated by this gap, this research aims to bridge the divide between EDA methods and practical analog design by developing the next-generation design methodology based on AI-driven EDA tools. The thesis first validates an AI-empowered analog IC sizing framework with design insights and silicon results, and then extending it toward system-level sizing to account for cross-block effects. Specifically, this research focuses on the AI-empowered optimization for analog building blocks, the development of co-design method for interacting modules, and the implementation of system-level optimization. Given that these represent three specific research topics with unique challenges, the following subsections provide a brief analysis of each. A more detailed discussion of each topic can be found in the corresponding chapters outlined in Section 1.5.

## 1.3.1 Block Level Sizing

At the block level, analog circuit optimization represents the foundation of EDA-based analog IC design. While recent advances have significantly improved optimization algorithms and surrogate modeling techniques, two central challenges remain unresolved:

• Lack of Wide Silicon Validation. Most optimization approaches are evaluated only on limited analog building blocks through simulation results. Comprehensive silicon-based validation across multiple building blocks and technology nodes is scarce. Without such evidence, it is difficult to establish confidence in the wide applicability of proposed optimization frameworks.

• Lack of Design Insight—Based Comparison. Existing evaluations focus primarily on algorithmic outcomes such as convergence, runtime, or numerical performance metrics. Far less attention is given to whether the optimization results preserve meaningful design insights, such as power—speed—noise trade-offs. This gap limits the ability to judge whether automated techniques align with designer intent and can be seamlessly adopted in practice.

Motivated by these limitations, this study is structured around two key objectives:

- Systematic Comparison across Representative Case Studies. The objective is to perform a comprehensive comparison between manual and AI-empowered design approaches on key analog building blocks such as op-amps, comparators, and oscillators. The study aims to evaluate both design quality and efficiency, with silicon measurement incorporated to ensure practical relevance beyond simulation.

- Benchmarking with Design Insights. The objective is to move beyond numerical metrics to assess whether optimization outcomes align with established design knowledge and designer intent. By examining circuit sizings, trade-offs, and interpretability, the study seeks to determine the extent to which automated methods can complement or enhance human expertise.

## 1.3.2 Subsystem Co-Design

In conventional analog IC design, individual blocks such as LDOs or voltage-controlled oscillators (VCOs) are often optimized in isolation under fixed assumptions about their operating environment. While this block-level approach simplifies the design process, it overlooks important interactions between connected circuits, which can lead to suboptimal overall performance once the blocks are integrated. Considering a VCO integrated with an LDO as an example, several key challenges can be identified:

- Limitations of Sequential Design. Conventional practice treats the VCO and LDO as independent blocks: the VCO is optimized under an ideal supply and the LDO is later tuned around it. This separation neglects block interactions and often forces iterative redesign, reducing design efficiency.

- Noise Co-Optimization Challenges. Low phase noise (PN) depends on the joint treatment of multiple sources such as thermal, flicker, and regulator-induced supply noise, which interact in nontrivial ways during integration. These coupling effects are difficult to capture with manual design, and block-level optimizations often fail to hold at the subsystem level.

• Scalability Limits of Manual Tuning. With dozens of design variables across both circuits, manual optimization is labor-intensive and error-prone. Evaluating design corners under PVT variations further compounds the complexity, making a systematic automated approach essential.

Motivated by these challenges, this work is guided by two primary objectives:

- Subsystem-Level Co-Design of VCO and LDO. The first objective is to develop an AI-driven co-design methodology that simultaneously optimizes the VCO and LDO as an integrated subsystem. By jointly considering power consumption, frequency pushing effect, and LDO-induced noise, the method seeks to minimize overall PN while maintaining energy efficiency and robustness across corners.

- Efficiency and Robustness Demonstration. The second objective is to validate the proposed co-design flow by implementing it with a machine learning—assisted optimization engine and applying it to a 65 nm CMOS LC-tank VCO with integrated LDO. Its performance is benchmarked against a sequential design flow to demonstrate improvements in figure of merit (FoM), PVT robustness and runtime efficiency, thereby establishing the practical advantages of subsystem-level co-design.

While this work focus on LDO-VCO as a representative case study, it should be emphasized that the co-design framework is not restricted to this particular combination of building blocks. The same principles can be readily extended to other subsystem configurations, such as oscillator—mixer pairs.

## 1.3.3 System Level Sizing

Scaling sizing from block-level circuits to system-level architectures introduces new challenges. To tackle these challenges, this work focuses on asynchronous successive-approximation register analog-to-digital converters (SAR ADCs) as a representative case study. For asynchronous SAR ADCs, these challenges manifest as pressing constraints that restrict the applicability of current AI-driven sizing methods:

• Block-Level Optimization Limitations. Prior design sizing methods typically operate at the block level, where individual components such as the comparator, digital-to-analog converters (DACs), and sample-and-hold (S/H) are sized separately. This decomposition requires manual specification allocation and cannot fully capture inter-block interactions, leading to suboptimal system performance and iterative design loops. In some cases, it may fail to meet the requirements of high-resolution and high-speed ADCs.

• High Dimensionality and Long Simulation Time. System-level SAR ADC design involves dozens of design variables spanning transistor sizes, capacitor sizes, and timing parameters. As the number of variables increases, the design space grows exponentially, making exhaustive exploration impractical. Although global optimization methods are theoretically capable of addressing such complexity, their computational cost often results in prohibitively long runtime. In addition, accurate fast Fourier transform (FFT)-based signal-to-noise and distortion ratio (SNDR) characterization requires long simulation durations at Nyquist rate, which is impractical to embed in an iterative optimization loop.

To overcome these challenges, this piece of work is guided by two main objectives:

- Global—Local Optimization with Multi-Fidelity Simulation. To handle the high dimensionality and long simulation time, the first objective is to develop a hierarchical system-level optimization framework that integrates fast global search using ANN-based surrogate modeling with local refinement via parallel multi-fidelity pattern search (PS). The approach balances exploration and exploitation: the global optimizer efficiently scans the design space with low-cost approximations, while the local optimizer ensures convergence to high-quality solutions using accurate full sine-wave simulations.

- System-Level SAR ADC Sizing. The second objective is to validate the proposed framework across 12 design cases spanning 7- and 12-bit resolutions with sampling rates up to 250 MHz. The goal is to demonstrate competitive SNDR and FoM with reduced runtime and minimal manual effort, thereby advancing practical system-level sizing for SAR ADC design.

While the discussion here is centered on SAR ADCs, the underlying issues such as the limits of block-level optimization and the complexity of high-dimensional system-level search spaces, are common across many analog and mixed-signal (AMS) subsystems. Thus, while SAR ADCs serve as a representative example in this study, the proposed methodology is applicable to a broad range of system-level AMS design problems.

#### 1.4 Main Contributions

This dissertation advances next-generation AI-driven design methodology at the block, subsystem, and system levels through three distinct studies that combine black-box optimization with learning-based acceleration and designer-in-the-loop validation. The works demonstrate measurable gains in design quality, PVT robustness, and turnaround time with post-layout or silicon validation.

Block-Level Sizing: from Systematic to Intelligent. A rigorous, design insight-aware comparison was performed between contemporary AI-empowered sizing and conventional systematic (e.g.,  $g_m/I_D$ ) methods across four representative blocks: a StrongARM comparator, two Miller-compensated op-amps (standard- and low-power targets), and a crosscoupled LC VCO, spanning  $0.35 \,\mu\text{m} - 65 \,\text{nm}$ . The flow adopts an AI-driven global search in two phases (worst-case corner optimization followed by all-corner optimization), followed by MC analyses. Designers remain in the loop only to validate design intent and, if needed, adjust specifications, avoiding experience-heavy decisions. The optimizer is based on an online surrogate-assisted differential evolution (DE) framework that trains a light ANN surrogate on-the-fly and selects infill samples via beta distribution-based ranking. Quantitatively, the comparator case achieves a 62% reduction in the power–noise FoM (from 6.32 nW · V to 2.42 nW · V) while meeting all 16 corners, with delay and power both improved over the literature reference. Similar all-corner gains are observed post-layout. In the op-amp case, overshoot in unity-gain configuration is eliminated by constraint reformulation, obtaining lower power (476  $\mu$ W vs. 856  $\mu$ W), while sustaining other performance metrics. For the LC VCO, the measured design reaches a PN of -120.6 dBc/Hzat 1 MHz and a FoM of 187.9 dBc/Hz, competitive with state-of-the-arts. These results, including three silicon validations, show that AI-empowered sizing can match designer intent while improving both efficiency and design performance, with human focusing on encoding high-level objectives rather than device-level heuristics.

Subsystem Co-Design: LDO-VCO with AI-Driven EDA. The first AI-driven codesign flow was proposed that optimizes an LC-tank VCO and its integrated LDO simultaneously, explicitly capturing the trade-off between various noise sources. 32 PVT corners are considered using the same optimization engine for an apple-to-apple comparison with the sequential (first VCO then LDO) approach. On a 65 nm design targeting 5.5–5.6 GHz, co-design improves PN by 1.2 dB at 1 MHz offset, reduces dynamic power by 28.8%, and increases FoM by 2.4 dBc/Hz relative to the sequential flow. The runtime drops from 18 hours (7 hours VCO + 11 hours LDO) to 6 hours on a 32-core workstation, evidencing scalability of learning-assisted optimization beyond single blocks.

#### System-Level Sizing: Global-Local Framework for Asynchronous SAR ADCs.

A SAR-ADC sizing framework is developed that cascades a fast global explorer with a derivative-free local optimizer under multi-fidelity simulation. The global phase enforces automatically derived coarse constraints including step-size ratio error (SSRE), sampling error, thermal noise, and power, obtained analytically from top-level SNDR targets and it finishes within 3–4 hours. The local phase then applies a parallel, multi-fidelity PS that interleaves inexpensive checks with periodic full-cycle FFT analysis accelerated by time-interleaved transient runs, converging within another 3 hours. Across 12 cases (7–12 bit, 100 kHz–250 MHz, 65 nm), the framework achieves up to 72.2 dB SNDR and FoM of 177.3 dB, while automating specification allocation and inter-block co-optimization, which addressed the key limitations of block-level methods.

Overall Impact. Together, these studies (i) link the EDA and design communities, showing that designer-in-the-loop, AI-empowered sizing with silicon validation can surpass experience-driven flows while preserving design intent; (ii) demonstrate the effectiveness of the co-design approach using AI-driven EDA algorithms that remain beyond the reach of systematic manual design; and (iii) propose a holistic design methodology for analog small systems, bridging a gap previously unaddressed by both the EDA and design communities.

#### 1.5 Thesis Outline

This dissertation comprises six chapters. Chapter 1 introduces the motivation for analog design automation, reviews challenges of manual design, and outlines the role of EDA tools, research objectives, and contributions. Chapter 2 provides the background and literature review. It surveys common analog building blocks, reviews traditional and automated methodologies, and analyzes EDA sizing techniques, with emphasis on mathematical optimization, evolutionary algorithms, and surrogate-assisted methods. Chapter 3 addresses block-level sizing. An AI-empowered flow with designer interaction is developed for schematic sizing, and case studies on op-amps, comparators, and VCOs demonstrate improved efficiency and design performance over manual design with measurement results. Chapter 4 extends to subsystem-level design through a co-design framework integrating VCOs and LDOs for communication applications. Post-layout validation shows gains in PSRR, noise, and efficiency. Chapter 5 advances to system-level sizing with a hybrid framework combining surrogate model-assisted optimization and multi-fidelity PS. Twelve SAR ADC design cases are explored, with benchmarking against conventional block-level methods

highlighting improvements in quality and efficiency. Finally, Chapter 6 summarizes the contributions across block-, subsystem-, and system-level sizing, discusses practical impact, and outlines future directions including layout optimization and advanced machine learning methods for full analog synthesis.

## Chapter 2

## Background and Literature Review

## 2.1 Background on Analog Circuits

Analog ICs process signals that vary continuously in time and amplitude. They provide the indispensable interface between the physical world and digital world: amplifying microvolt-level sensor outputs, filtering noise, generating clocks, converting between analog and digital domains, and regulating on-chip supplies, etc.. This section classifies analog circuits by their time behavior (static vs. dynamic) and details the working principles of representative blocks that are widely found in modern applications.

As summarized in Table 2.1, static and dynamic analog circuits differ fundamentally in time behavior, design intent, and verification focus. Static analog circuits operate around a fixed bias point and can be approximated as linear time-invariant (LTI) systems under small-signal conditions. This enables accurate frequency domain analysis (e.g., gain, bandwidth, loop stability) within a limited operating region where device behavior remains approximately linear. Dynamic circuits are time-varying, either linear but periodically time-varying (LPTV) due to clocked switching, or strongly nonlinear due to regeneration, quantization, or oscillation. These distinctions determine the appropriate analysis techniques and dictate which performance metrics become most critical to meeting design specifications.

Static blocks draw a continuous quiescent current  $I_Q$  to establish transconductances and pole locations. Power is primarily static and can be calculated with  $P_{\rm static} \approx I_Q V_{DD}$ , with minimal dynamic components. LPTV blocks typically exhibit negligible static power consumption within their core switching networks, while consuming energy predominantly from capacitive charging and the overhead of clock or local oscillator drive circuits, exem-

Table 2.1: A comparison between static and dynamic analog circuits.

|                       | Static                                                                                   | Dynamic                                                                                          |

|-----------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Time behavior         | Continuous bias, steady operating point                                                  | Clocked, sampled, regenerative, or autonomous oscillation                                        |

| Linearity             | Small-signal linear around bias                                                          | Strongly nonlinear or LPTV                                                                       |

| Power profile         | Quiescent                                                                                | Often zero static power, dynamic charging/switching dominates                                    |

| Primary<br>analysis   | AC/noise models, loop gain and PM                                                        | Transient, PSS/PNOISE for periodic, timing and metastability                                     |

| Core specifications   | Power, DC gain, UGB, phase margin, PSRR, CMRR, noise, offset                             | Decision time, jitter/PN, SNDR, INL/DNL                                                          |

| Typical nonidealities | Limited swing, finite $r_o$ , flicker noise, stability margins                           | Kickback, metastability, limit cycles, reference drop                                            |

| Verification focus    | PVT corners, MC for offset/noise, stability                                              | Timing across PVT, metastability probability, jitter/PN, settling                                |

| Example blocks        | Op-amps (telescopic, folded-cascode, two-stage), active filters, bandgaps, LDOs, buffers | Dynamic comparators (StrongARM, double-tail), VCOs/PLLs (LC, ring), SC filters, mixers, SAR ADCs |

plified by

$$P_{\rm dyn} \approx \sum_{i} \left( C_i V_i^2 f_{\rm tog} \right) + P_{\rm clk} + P_{\rm ref},$$

(2.1)

where  $C_i$  is the capacitance being charged,  $V_i$  is the corresponding voltage swing,  $f_{\text{tog}}$  is the effective switching frequency (i.e., toggle rate),  $P_{\text{clk}}$  is the power required to drive clock, and  $P_{\text{ref}}$  accounts for additional reference or biasing circuitry. Oscillators and phase-locked loops (PLLs) are an important exception, which require a steady bias to sustain oscillations in addition to divider and loop switching.

Representative static blocks include op-amps such as telescopic [28], folded-cascode [29], and two-stage Miller compensated op-amps [30] together with active-RC/Gm-C filters [31], bandgap references (BGR) [32], LDOs [33], and unity gain buffers [34]. The design emphasis is small-signal gain, stability, and noise. First-order approximations can guide architecture selection and sizing, for example, the gain and unity gain bandwidth (UGB) can be estimated with:

$$A_{\nu} \approx g_m r_o,$$

(2.2)

$$f_u \approx \frac{g_m}{2\pi C_I},\tag{2.3}$$

where  $g_m$  is the transconductance,  $r_o$  is the output resistance, and  $C_L$  is the load capacitance.

Verification is primarily conducted in the frequency domain through alternating current (AC) and noise analyses. This is complemented by PVT corner and MC simulations to assess performance spread, mismatch, and offset distributions. Typical nonidealities include finite output resistance, flicker noise, headroom limits, and compensation trade-offs. Core specifications include power, DC gain, UGB, phase margin (PM), power supply rejection ratio (PSRR), common mode rejection ratio (CMRR), noise, and offset.

Dynamic circuits comprise two broad classes. The first is LPTV, exemplified by switched-capacitor (SC) networks [35] and passive mixers [36], where circuit parameters change with clock or local oscillator, and performance is captured by periodic steady-state (PSS) and periodic noise (PNOISE) analyses. Canonical behaviors include effective resistance in SC networks and frequency translation in mixers, for example:

$$R_{\rm eq} = \frac{1}{Cf_s},\tag{2.4}$$

where C is the switched capacitance and  $f_s$  is the switching frequency. The second category comprises strongly nonlinear circuits, such as dynamic comparators (e.g., StrongARM [37] and double-tail latches [38]), VCOs [39], PLLs [40], and SAR ADCs [41], where regenerative feedback, limit-cycle behavior, or quantization effects dominate [42]–[45]. Representative behavioral models aid in initial sizing and provide insight into dominant dynamic characteristics, such as decision time and oscillation frequency:

$$t_d \approx \tau \ln \left( \frac{V_{\text{swing}}}{V_0} \right),$$

(2.5)

$$\tau \approx \frac{C_L}{g_{m,\text{eff}}},\tag{2.6}$$

$$f_0 = \frac{1}{2\pi\sqrt{LC}},\tag{2.7}$$

where  $t_d$  is the decision time,  $\tau$  is the time constant,  $V_{\text{swing}}$  is the output voltage swing,  $V_0$  is the initial input differential voltage,  $C_L$  is the load capacitance,  $g_{m,\text{eff}}$  is the effective transconductance, L is the inductor value, and C is the capacitance in the resonant tank. Corresponding core specifications shift to decision time and metastability probability for comparators, PN and tuning range for VCOs/PLLs, and SNDR and integral nonlinearity (INL) and differential nonlinearity (DNL) for SAR ADCs.

# 2.2 Three Generations of Analog Circuit Design Methods

This section organizes analog circuit design practice into three methodological "generations" [1], [4]. Generation I relies on long-channel quadratic laws and closed-form hand analysis. Generation II centers on the transconductance efficiency  $g_m/I_D$  for navigating weak–moderate–strong inversion with process-portable sizing. Generation III formulates design as an optimization problem, either with analytic constraints or simulation-driven.

#### 2.2.1 Generation I: Quadratic Hand Analysis

Under long-channel, strong-inversion assumptions, MOS devices follow simple relations enabling paper-and-pencil sizing. For an NMOS,

$$I_D \approx \frac{1}{2}\mu C_{\text{ox}} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS}), \qquad g_m \approx \frac{2I_D}{V_{\text{ov}}}, \qquad r_o \approx \frac{1}{\lambda I_D},$$

(2.8)

where  $I_D$  is the drain current,  $\mu$  is the carrier mobility,  $C_{\rm ox}$  is the gate-oxide capacitance per unit area, W and L are the channel width and length,  $V_{GS}$  is the gate-source voltage,  $V_{TH}$  is the threshold voltage,  $\lambda$  is the channel-length modulation parameter,  $V_{DS}$  is the drain-source voltage,  $g_m$  is the transconductance,  $V_{\rm ov} = V_{GS} - V_{TH}$  is the overdrive voltage, and  $r_o$  is the output resistance. These lead to first-order block metrics such as

$$A_{\nu} \approx g_{m} r_{o}, \qquad \omega_{p} \approx \frac{1}{R_{\text{out}} C_{L}}, \qquad f_{u} \approx \frac{g_{m}}{2\pi C_{C}},$$

(2.9)

where  $A_v$  is the low-frequency gain,  $g_m$  is the effective transconductance,  $r_o$  is the output resistance,  $\omega_p$  is the dominant pole frequency,  $R_{\text{out}}$  is the output resistance seen at the node of interest,  $C_L$  is the load capacitance,  $f_u$  is the UGB, and  $C_C$  is the compensation capacitance.

A representative design flow based on the quadratic long-channel law proceeds as follows: (i) select the circuit topology and establish the bias point; (ii) choose the overdrive  $V_{ov}$  and bias currents from bandwidth and noise requirements; (iii) back-solve the device dimensions (W/L) from the targeted  $g_m$  and  $r_o$ ; (iv) select the compensation network (e.g.,  $C_C$  and zero placement) to satisfy the desired PM; and (v) validate the design and iterate using SPICE simulation. This approach offers high interpretability, enables rapid first-order sizing, and is effective for static, approximately LTI blocks. However, its accuracy degrades in deep-submicron technologies (e.g., modern CMOS nodes < 130 nm) due to

velocity saturation, mobility degradation, short-channel effects, and body effect. Moreover, weak/moderate inversion operation, device mismatch, and PSRR/CMRR constraints are captured only at a coarse level. Therefore, it is largely used in educational settings and for initial sizing of some low-frequency designs with legacy processes (> 180 nm).

#### 2.2.2 Generation II: The $g_m/I_D$ Method

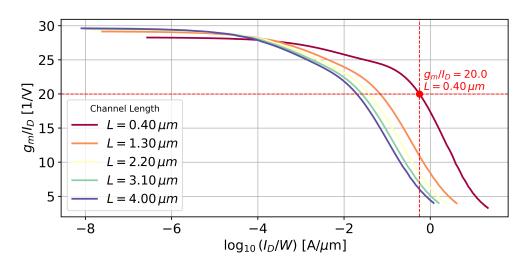

The transconductance efficiency  $g_m/I_D$  parameterizes the speed–noise–power trade-space via inversion level and maps directly to device sizing through EKV/BSIM lookup tables (LUTs) or process curves as shown in Fig. 2.1. Asymptotically,

$$\left. \frac{g_m}{I_D} \right|_{\text{weak}} \approx \frac{1}{nV_T} \text{ (typically } 20 \sim 30 \,\text{V}^{-1}\text{)},$$

(2.10)

$$\left. \frac{g_m}{I_D} \right|_{\text{strong}} \approx \frac{2}{V_{\text{ov}}},$$

(2.11)

where  $g_m$  is the transconductance,  $I_D$  is the drain current, n is the subthreshold slope factor,  $V_T$  is the thermal voltage, and  $V_{ov}$  is the overdrive voltage.

A typical  $g_m/I_D$ -based sizing flow proceeds as follows: (i) select a target  $g_m/I_D$  band from bandwidth, noise, and energy objectives; (ii) set  $g_m$  from the UGB  $f_u$  or from a noise budget, then compute  $I_D = g_m/(g_m/I_D)$ ; (iii) map to device dimensions (W/L), overdrive  $V_{\rm ov}$ , and operating region using process curves or LUTs; (iv) verify  $r_o$ , headroom, PM, PSRR/CMRR, and layout feasibility; and (v) refine.

Figure 2.1: The  $g_m/I_D$  based method.

The method is technology-portable, spans weak—moderate—strong inversion, and makes the power—speed—noise trade-offs explicit. It is most effective for quasi-LTI blocks, such as op-amps, gm—C filters, and LDOs, where performance metrics such as UGB and PSRR map directly to  $g_m$  and  $r_o$ . However, strongly time-varying or nonlinear behaviors (e.g., regeneration, limit cycles, quantization in dynamic circuits) are only indirectly captured. Furthermore, process curves are sampled at coarse intervals to reduce characterization time and memory cost, which limits its accuracy and may still require further tuning. In practice, the  $gm/I_D$ -based design methodology is widely adopted in both academia and industry, particularly for initial transistor sizing and early-stage performance estimation. It enables efficient exploration of power-constrained design spaces, such as those encountered in Internet of things (IoT) and biomedical applications. Supported by EKV models, LUT-based sizing environments, and some commercial EDA tools such as those from Synopsys and Mentor, this approach balances intuition and numerical accuracy. However, it is not fully automated and still relies on designer expertise for iterative refinement and results interpretation.

#### 2.2.3 Generation III: Optimization-Centric Sizing

Analog circuit sizing is formulated as an optimization problem with objective(s) and constraints, solved either from analytic models or via simulation-in-the-loop search with PVT considerations. Below is a single-objective example.

$$\begin{aligned} & \underset{x}{\min} \quad P(x) \\ & \text{s.t.} \quad A_0(x) \geq A_{\min}, \\ & f_u(x) \geq f_{\min}, \\ & \text{PM}(x) \geq \phi_{\min}, \\ & \text{PSRR}(x) \geq \rho_{\min}, \\ & x \in X. \end{aligned} \tag{2.12}$$

Equation-Driven/Convex Optimization. When specifications can be formulated as analytic, convex-like constraints (e.g., small-signal gain, UGB, PM and noise), geometric programming provides fast, globally optimal sizing, where global optimality is guaranteed [11]. However, the range of problems that can be addressed is limited by whether the underlying model can be transformed into a convex form. Many important behaviors, such as regeneration, sampling, and oscillation, cannot generally be expressed in convex terms, and therefore fall outside the scope of these methods. In addition, the accuracy of the equations is limited compared with BSIM models.

Simulation-Driven (Black-Box) Optimization. In this approach, SPICE analyses (AC, Transient, PSS, PNOISE) serve directly as evaluators within single- or multi-objective search frameworks, such as gradient-based, heuristic, or Bayesian methods. Surrogate models are often used to reduce the number of expensive simulations. This strategy is well suited for dynamic and nonlinear blocks, which supports capturing behaviors that are difficult to approximate analytically including comparator decision time and metastability, VCO PN, and SAR ADC SNDR. However, the computational cost is inevitably higher than that of quadratic law or  $g_m/I_D$ -based methods. Recent advances in surrogate modeling and efficient search algorithms have made the runtime increasingly manageable in practice, which will be discussed in Section 2.4.

#### 2.2.4 Common Verification Loop

Design verification follows a common procedure regardless of the methodology. Sign-off requires PVT analysis to guarantee functionality and stability margins, and MC simulations to quantify mismatch-induced variability such as input-referred offset and pole dispersion. For realistic yield assessment, MC should be performed at the identified worst-case corners.

#### 2.2.5 Comparison

In summary, Generation I enables rapid, first-order design via long-channel models and remains useful for early-stage estimation. Generation II introduces inversion-aware sizing through the  $g_m/I_D$  methodology, widely applied in power-constrained designs for its balance of efficiency and portability. Generation III formulates sizing as an optimization problem, supporting accurate and relatively efficient analog IC sizing. Fig. 2.2 summarizes the comparison across generations.

## 2.3 Local Optimization Methods

Local optimization techniques represent the earliest approaches adopted for analog circuit sizing. During the 1980s and early 1990s, gradient-based methods such as steepest descent, Newton methods, and sequential quadratic programming (SQP) were used, where circuit equations could be approximated in convex or near-convex form for efficient optimization.

## Gen I Quadratic law

#### Closed-form/intuition

- Closed-form sizing

- Fast, interpretable

- Degrades in deep submicron

## $\begin{array}{c} \textbf{Gen II} \\ \textbf{g}_{\textbf{m}}/\textbf{I}_{\textbf{D}} \text{ method} \end{array}$

#### Systematic sizing

- Process-portable flow

- Explicit power-speednoise trade-off

- LUTs (accuracy vs memory)

- Limited for dynamic blocks

## **Gen III**Optimization-based

#### Automated sizing

- Integrates

PVT/MC/parasitics

- Accurate and surrogate model reduces runtime

- Higher computation cost

Figure 2.2: Three generations of analog design methods.

Representative efforts, such as OPASYN [46], demonstrated the utility of convex and geometric programming frameworks for structured circuit classes. With the increasing reliance on simulation-based flows in the 1990s, derivative-free algorithms, including the Nelder–Mead (NM) simplex method and PS, were introduced to handle highly nonlinear behaviors where analytic gradients were unavailable.

#### 2.3.1 Gradient-Based Methods

When analytic or adjoint sensitivities are available, quasi-Newton or SQP [47], [48] provides fast refinement. While gradient-based methods (e.g., Newton/BFGS/SQP, interior-point) converges rapidly on smooth small-signal objectives, many analog performance metrics (e.g., transient settling, comparator decision time, SAR ADC SNDR) are noisy, nonsmooth, or even discontinuous, making gradient-free local methods more practical. Moreover, when reliable derivatives are unavailable, finite-difference approximations become both computationally expensive and brittle in the presence of SPICE noise, further motivating the adoption of derivative-free alternatives.

## 2.3.2 Nelder-Mead (Simplex)

The NM algorithm [49], [50] is a derivative-free local optimization technique that has been widely applied in engineering design problems, including analog circuit sizing. Unlike gradient-based methods, NM requires single objective function evaluations, making it suitable for noisy or nonsmooth responses often encountered in SPICE simulations.

The method maintains a simplex, i.e., a set of n+1 vertices in an n-dimensional design space. At each iteration, the vertices are ordered by their objective values, and the worst point is replaced by a new candidate generated through geometric operations relative to the centroid of the remaining vertices. The standard update rules include:

- Reflection:  $x_{\text{refl}} = c + \rho(c x_{\text{max}})$ , where c is the centroid,  $\rho > 0$  is the reflection coefficient and  $x_{\text{max}}$  is the worst vertex.

- Expansion:  $x_{\text{exp}} = c + \chi(x_{\text{refl}} c)$ , with  $\chi > 1$  promoting aggressive search when reflection improves the solution.

- Contraction:  $x_{\text{con}} = c + \gamma(x_{\text{max}} c)$ , with  $0 < \gamma < 1$  for conservative search if reflection fails.

- Shrink:  $x_i \leftarrow x_{\min} + \sigma(x_i x_{\min})$ , with  $0 < \sigma < 1$  contracting the simplex around the best vertex  $x_{\min}$ .

By iteratively applying these steps, NM adaptively explores the local design space without derivatives. Its strengths are simplicity, robustness to noise, and low overhead in low-to-moderate dimensions. In analog sizing, NM is typically used to fine-tune design parameters after global exploration, either in hybrid flows that interleave global and local updates or through simple concatenation where NM refines the best solution returned by a global search. Its limitations include potential stagnation in high dimensions and lack of convergence guarantees beyond low-dimensional smooth functions.

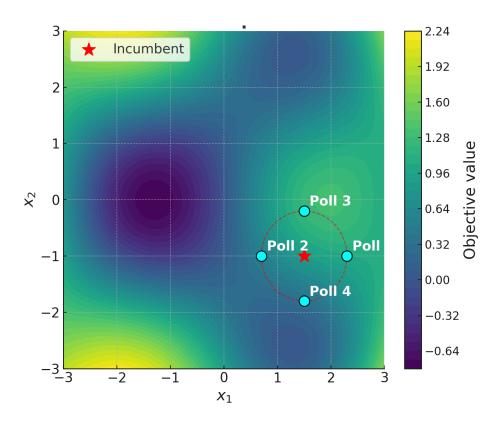

#### 2.3.3 Pattern Search Method

PS [51] is another derivative-free local optimization method designed for black-box and nonsmooth problems. Unlike simplex-based schemes, PS explores the design space by evaluating a set of candidate directions around the current solution and accepts a move if any candidate improves the objective.

At iteration t, given the incumbent  $x^{(t)}$  and mesh size  $\Delta^{(t)}$ , PS evaluates trial points of the form

$$x^{(t)} + \Delta^{(t)}d, \quad d \in D, \tag{2.13}$$

where D is a positive spanning set of directions (e.g., the coordinate basis  $\{\pm e_i\}_{i=1}^n$ ). In each iteration, the algorithm evaluates the objective at the poll points  $x^{(t)} + \Delta^{(t)}d$  for all  $d \in D$ , as shown in Fig. 2.3.

Figure 2.3: The illustration of PS in a 2-D problem.

If at least one poll point improves upon the incumbent, the best improving point is accepted as the new incumbent  $x^{(t+1)}$ , and the mesh size  $\Delta^{(t)}$  may be expanded to accelerate progress. If no poll point improves the objective, the incumbent is retained, the mesh size is reduced (typically by a constant factor such as 1/2), and a new poll step is attempted.

This poll-and-update cycle is repeated until a convergence criterion is satisfied, commonly when the mesh size  $\Delta^{(t)}$  falls below a prescribed threshold, or when successive iterations yield negligible improvement in the objective. In this way, PS adaptively balances global exploration (through larger mesh sizes) and local refinement (through progressively finer meshes).

The strengths of PS are its ability to handle nonsmooth, discontinuous, or noisy objective functions without requiring gradients. Its convergence is guaranteed under mild conditions to a Clarke stationary point [52]. In analog circuit sizing, PS is particularly useful for tuning mixed discrete—continuous parameters (e.g., unit capacitor counts, transistor fingers) and for refining post-layout designs where SPICE responses may be noisy or irregular. Compared to NM, PS scales more reliably in higher dimensions and supports parallel evaluation of the poll set, making it attractive in simulation-driven optimization flows. The pseudo code is shown in Algorithm 1.

#### Algorithm 1 PS for Analog Circuit Sizing

**Require:** Objective  $f(\cdot)$ , initial point  $x_0$ , initial mesh size  $\Delta_0$ , direction set D, bounds [l,u], integer mask isInt, expansion factor  $\alpha > 1$ , contraction factor  $0 < \beta < 1$ , tolerance  $\varepsilon$ , maximum iterations T.

```

1: x \leftarrow \text{ProjectAndRound}(x_0, l, u, \text{isInt})

2: f_x \leftarrow f(x), \Delta \leftarrow \Delta_0

3: for t = 1 \rightarrow T do

improved \leftarrow false

4:

x_{\text{best}} \leftarrow x, \quad f_{\text{best}} \leftarrow f_x,

for each d \in D do

5:

x_{\text{trial}} \leftarrow x + \Delta d

6:

x_{\text{trial}} \leftarrow \text{ProjectAndRound}(x_{\text{trial}}, l, u, \text{isInt})

7:

f_{\text{trial}} \leftarrow f(x_{\text{trial}})

8:

if f_{\text{trial}} + \varepsilon < f_{\text{best}} then

9:

x_{\text{best}} \leftarrow x_{\text{trial}}, \quad f_{\text{best}} \leftarrow f_{\text{trial}}

10:

11:

improved \leftarrow true

12:

end if

end for

13:

if improved then

14:

f_x \leftarrow f_{\text{best}}

15:

x \leftarrow x_{\text{best}},

\Delta \leftarrow \alpha \Delta

⊳ expand mesh

16:

17:

else

18:

\Delta \leftarrow \beta \Delta

▷ contract mesh

end if

19:

if \Delta < \Delta_{\min} then

20:

break

21:

22:

end if

23: end for

24: return x, f_x

```

As a rule of thumb, NM is lightweight and effective for  $n \le 15$  with moderate noise. PS scales better to mixed discrete and continuous variables and parallel evaluation. Both are robust and are now used frequently as second stages after global exploration.

# 2.3.4 Summary

Gradient-based local methods are ideal when small-signal, differentiable models exist. Otherwise, NM and PS provide practical, derivative-free refinement that respects search bounds and constraints, tolerates SPICE noise, and integrates cleanly after global optimizer.

# 2.4 Global Optimization Methods

Different from local methods, global optimization algorithms do not require an initial design and are capable of escaping local minima in highly nonlinear, multimodal analog design spaces. Evolutionary and swarm-based heuristics use population-based search strategies to explore the design space efficiently. More recently, surrogate model-assisted global optimization has been introduced to accelerate convergence by combining data-driven models with heuristic exploration, reducing the number of circuit simulations while maintaining global search capability.

#### 2.4.1 Evolutionary and Swarm-Based Heuristics