# Eblabla, Abdalla (2018) MM-wave frequencies GaN-on-Si HEMTs and MMIC technology development. PhD thesis.

http://theses.gla.ac.uk/8861/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten:Theses http://theses.gla.ac.uk/ theses@gla.ac.uk

# MM-Wave Frequencies GaN-on-Si HEMTs and MMIC Technology Development

by

## Abdalla Eblabla

A thesis submitted in fulfilment for the degree of Doctor of Philosophy

in the

Division of Electronics and Electrical Engineering

School of Engineering

Copyright © 2018, Abdalla Eblabla

## Abstract

Gallium Nitride (GaN)-based High Electron Mobility Transistors (HEMTs) grown on Silicon (Si) substrates technology is emerging as one of the most promising candidates for cost effective, high-power, high-frequency Integrated Circuit (IC) applications; operating at Microwave and Millimetre (mm)-wave frequencies. To capitalise on the advantages of RF GaN technology grown on Low resistivity (LR) Si substrates; RF losses due to the Si substrate must be eliminated at the active devices, passive devices and interconnect. Low resistivity Si substrates are intrinsic prone to RF losses and high resistivity (HR) Si substrates shown to exhibit RF losses as a result of operating substrate temperature at the system level. Therefore, obtaining a viable high-performance RF GaN-on both LR and HR Si device remains a challenge for this technology. In an attempt to overcome these issues, Microwave Monolithic Integrated Circuit (MMIC)-compatible technology was developed for the first time aiming to eliminate the substrate coupling effect for the realisation of high performance passive and active devices on GaN-on-Si substrates for mm-wave MMIC applications.

To validate the novel RF GaN-on-Si substrates developed technology in this work, several fabrication techniques approaches were investigated and developed in order to improve the DC and RF performance of developed AlGaN/GaN HEMTs. The electrical characteristics were analysed based on the extracted small-signal equivalent circuit model from the measured data using on-wafer probes. Device parasitic effects associated with input/output contact pads were minimised by optimising the layout of the device. Consequently, using a proper device layout design, downscaling the AlGaN Schottky barrier and inserting an AlN interlayer in the material structure were found to have effectively improve the RF performance, where a maximum cut-off frequency,  $f_{\rm T}$  of 79.75 GHz and maximum oscillation frequency,  $f_{\rm MAX}$  of 82.5 GHz were obtained. To our knowledge, these results were the best performance AlGaN/GaN HEMTs grown on LR Si, and comparable to AlGaN/GaN HEMTs grown on Semi Insulating (SI)-SiC and HR Si substrates with similar gate lengths.

Novel low-loss transmission media technology on GaN-on-LR Silicon was also developed and demonstrated in this work. Two design structures were successfully realised providing complete isolation of the conductive substrate by employing a ground plane, a 5 µm-thick

benzocyclobutene (BCB) and an additional elevation of elevated line traces supported by airbridges. Consequently, an attenuation constant,  $\alpha$ , of better than 0.06 Np/mm and 0.45 Np/mm were achieved at frequencies of up to 76 GHz and 750 GHz, respectively, with matching (S<sub>11</sub>) of better than -15 dB over the whole frequency range. These results for the passive components and transmission media interconnect performance exhibited a better performance than those currently used in MMICs' conventional transmission media technology, such as Microstrip and Coplanar waveguide (CPW) on a standard SI-GaAs substrates. To prove the capabilities and efficiency of the developed transmission media, low-loss in-line series and shunt Metal-Insulator-Metal (MIM) capacitors were presented. In addition, High-Q on-chip inductors employing elevated traces and a BCB interface layer were also realized. A peak Q-factor of 22 at 24 GHz and  $f_{SRF}$  of 59 GHz was achieved for 0.81 nH inductors. The realised MIM capacitors and spiral inductors were characterized based on the extracted small-signal equivalent circuit model. The developed transmission media and passive devices technology offered a promising platform for integrated RF GaN-HEMTs on Si for the realisation of high-performance monolithic integrated circuits for mm-wave applications.

## Acknowledgments

First of all, I would like to thank the almighty God (ALLAH) for giving me the knowledge, strength and patience to curry this research work.

I would like to take this opportunity to acknowledge the assistance and support provided by many people during the competition of this thesis.

I would like to express my genuine thanks to my supervisor, Dr. Khaled Elgaid for giving me the valuable chance to carry out this research work, and for his unique mentoring, useful feedbacks and guidance throughout this work, which would not have been completed without his great support, wide experience and frequent encouragements.

I would like to extend my sincerest gratitude to Dr. Xu Li for his prompt help and support with dry etch and the extremely useful discussions on fabrication related issues. Also, I should not forget to thank Dr. Afesomeh Ofiare for his continuous help with the RF measurement system set up and calibration.

I would like to acknowledge Mr. Hermann Massler, Microelectronics Group Manager, Fraunhofer Institute for Applied Solid State Physics IAF, Freiburg, Germany for conducting the THz on-wafer measurements.

I am grateful to the entire technical staff at the James Watt Nanofabrication Centre (JWNC) at the University of Glasgow for providing training on the required equipment and their technical support during this work. Special thanks to Susan Ferguson and Helen Mclelland for introducing me to the cleanroom and their supervision on the fabrication of the first devices in this thesis.

I also wish to recognise the financial support throughout this work provided by my sponsor, the Ministry of Higher Education of Libya. Also, special thanks to the Engineering and Physical Sciences Research Council (EPSRC) who partially supported this research work.

Last although not least, I would like to thank my beloved parents, family and friends for giving me the patience and endless moral support during my research. They were totally understanding about the demands of this work, providing unlimited encouragement when things are gloomy.

## **Associated Publications**

#### **Journal papers**

- <u>A. Eblabla</u>, X. Li, D. J. Wallis, I. Guiney and K. Elgaid, "High Performance MMIC Inductors for GaN-on-Low Resistivity Silicon for Microwave Applications," in *IEEE Microwave and Wireless Components Letters*, vol. 28, no. 2, pp. 99-101, 2018.

- <u>A. M. Eblabla</u>, X. Li, D. J. Wallis, I. Guiney and K. Elgaid, "GaN on Low-Resistivity Silicon THz High-Q Passive Device Technology," in *IEEE Transactions on Terahertz Science and Technology*, vol. 7, no. 1, pp. 93-97, Jan. 2017.

- <u>A. Eblabla</u>, B. Benakaprasad, X. Li, D. J. Wallis, I. Guiney and K. Elgaid, "Low-Loss MMICs Viable Transmission Media for GaN-on-Low Resistivity Silicon Technology," in *IEEE Microwave and Wireless Components Letters*, vol. 27, no. 1, pp. 10-12, Jan. 2017.

- <u>A. Eblabla</u>, X. Li, I. Thayne, D. J. Wallis, I. Guiney and K. Elgaid, "High Performance GaN High Electron Mobility Transistors on Low Resistivity Silicon for X-Band Applications," in *IEEE Electron Device Letters*, vol. 36, no. 9, pp. 899-901, Sept. 2015.

- <u>A. Eblabla</u>, D. J. Wallis, I. Guiney and K. Elgaid, "Novel Shielded Coplanar Waveguides on GaN-on-Low Resistivity Si Substrates for MMIC Applications," in *IEEE Microwave and Wireless Components Letters*, vol. 25, no. 7, pp. 427-429, July 2015.

#### **Conference** papers

- <u>A. Eblabla</u>, B. Benakaprasad, X. Li, D. J. Wallis, I. Guiney, C. Humphreys and K. Elgaid "Passive components technology for THz-Monolithic Integrated Circuits (THz-MIC)," 2017 18th International Radar Symposium (IRS), Prague, Czech Republic, 2017, pp. 1-7.

- <u>A. Eblabla</u>, X. Li, I. Thayne, D. J. Wallis, I. Guiney and K. Elgaid, "MMIC-Compatible Microstrip Technology for GaN-HEMTs on Low Resistivity Silicon Substrate" *the International Workshop on Nitride Semiconductors (IWN 2016)*, October 2-7, 2016, Orlando, Florida.

- <u>A. Eblabla</u>, X. Li, D. J. Wallis, I. Guiney & K. Elgaid, "GaN-based HEMTs on Low Resistivity Silicon Technology for Microwave Applications" *the 8<sup>th</sup> Wide Bandgap Semiconductor and Components Workshop*, ESA/ECSAT, Harwell, UK, 2016.

- <u>A. Eblabla</u>, B. Benakaprasad, X. Li, I. Thayne, D. J. Wallis, I. Guiney, C. Humphreys and K. Elgaid, "High Frequency Active and Passives Devices using GaN on Low Resistivity Silicon", *ARMMS RF & Microwave Society Conference*, The Oxford Belfry, UK 2016.

- <u>A. Eblabla</u>, B. Benakaprasad, X. Li, D. J. Wallis, I. Guiney, C. Humphreys and K. Elgaid, "Effect of AlN Spacer in the Layer Structure on High RF Performance GaN-Based HEMTs on Low Resistivity Silicon at K-Band Application", 11<sup>th</sup> International Conference on Nitride Semiconductors (ICNS-11), Beijing, China, 2015.

- B. Benakaprasad, <u>A. Eblabla</u>, X. Li, D. J. Wallis, I. Guiney and K. Elgaid, "Design and performance comparison of various terahertz microstrip antennas on GaN-on-low resistivity silicon substrates for TMIC," 2016 Asia-Pacific Microwave Conference (APMC), New Delhi, 2016, pp. 1-4.

- B. Benakaprasad, <u>A. Eblabla</u>, X. Li, D. J. Wallis, I. Guiney, C. Humphreys and K. Elgaid "Terahertz microstrip elevated stack antenna technology on GaN-on-low resistivity silicon substrates for TMIC," 2016 46th European Microwave Conference (EuMC), London, 2016, pp. 413-416.

- B. Benakaprasad, <u>A. Eblabla</u>, X. Li, D. J. Wallis, I. Guiney, C. Humphreys and K. Elgaid "Terahertz monolithic integrated circuits (TMICs) array antenna technology on GaN-on-Low resistivity silicon substrates," 2016, 41st International Conference on Infrared, Millimetre, and Terahertz waves (IRMMW-THz), Copenhagen, 2016, pp. 1-2.

## **Table of Contents**

| A | bstra  | nct    | I                                                                    |

|---|--------|--------|----------------------------------------------------------------------|

| A | ckno   | wledg  | gments III                                                           |

| A | ssoci  | ated l | Publications IV                                                      |

| L | ist of | Figu   | resX                                                                 |

| L | ist of | Tabl   | es XIV                                                               |

| L | ist of | Abbi   | reviationsXV                                                         |

| 1 | Ir     | ntrodu | action and the State of the Art1                                     |

|   | 1.1    | Der    | nand for High Output Power and High Frequency Transistors at mm-wave |

|   | Freq   | uenci  | es1                                                                  |

|   | 5.1    | Gal    | N-based High Electron Mobility Transistors (HEMTs) on Si Technology  |

|   | 5.2    | Tra    | nsmission Media Technology for GaN-on-LR Si Substrates6              |

|   | 5.3    | Res    | earch Goal and Objects6                                              |

|   | 5.4    | The    | esis Outline7                                                        |

| 2 | F      | abrica | ation Techniques9                                                    |

|   | 2.1    | Intr   | oduction9                                                            |

|   | 2.2    | Ma     | terial Structure10                                                   |

|   | 2.3    | Bar    | nd diagram11                                                         |

|   | 2.4    | San    | nple Preparation                                                     |

|   | 2.5    | Litl   | nography13                                                           |

|   | 2.     | 5.1    | Optical Lithography                                                  |

|   | 2.     | 5.2    | E-beam Lithography16                                                 |

|   | 2.     | 5.3    | Pattern Definition17                                                 |

|   | 2.     | 5.4    | Mask Plate                                                           |

|   | 2.6    | Dry    | <sup>7</sup> Etch                                                    |

|   | 2.     | 6.1    | Reactive Ion Etching                                                 |

|   | 2.     | 6.2    | Inductively-Coupled Plasma Reactive Ion Etching                      |

|   | 2.7        | Die | electric Deposition                                                  | 21 |

|---|------------|-----|----------------------------------------------------------------------|----|

|   | 2.7        | 7.1 | Inductively-Coupled Plasma Chemical Vapor Deposition                 | 21 |

|   | 2.8        | Me  | etallisation and Lift-off                                            | 23 |

|   | 2.9        | Ga  | N-based HEMT Process Flow                                            | 24 |

|   | 2.9        | 9.1 | Alignment Markers                                                    | 24 |

|   | 2.9        | 9.2 | Ohmic Contacts                                                       | 25 |

|   | 2.9        | 9.3 | Mesa Isolation                                                       | 26 |

|   | 2.9        | 9.4 | Passivation                                                          | 27 |

|   | 2.9        | 9.5 | Gates                                                                |    |

|   | 2.9        | 9.6 | Contact Pads                                                         | 29 |

|   | 2.10       | ł   | Passive Devices Fabrication Process                                  | 31 |

|   | 2.1        | 0.1 | Shielded Transmission Media Technology                               | 31 |

|   | 2.1        | 0.2 | Shielded-Elevated Transmission Media Technology                      | 35 |

|   | 2.11       | (   | Conclusion                                                           | 37 |

| 3 | Al         | GaN | //GaN HEMTs on Low Resistivity Si Substrates                         |    |

|   | 3.1        | Int | roduction                                                            |    |

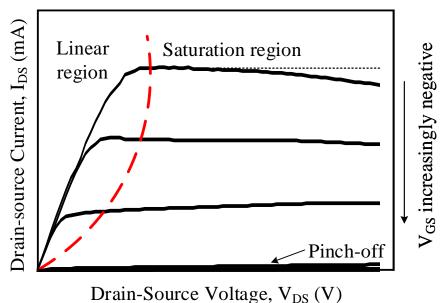

|   | 3.2        | Op  | eration of HEMT                                                      | 39 |

|   | 3.3        | Su  | mmary of Important HEMTs Parameters                                  | 40 |

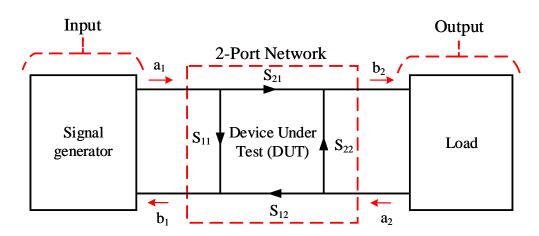

|   | 3.4        | HE  | EMT RF Behaviour                                                     | 42 |

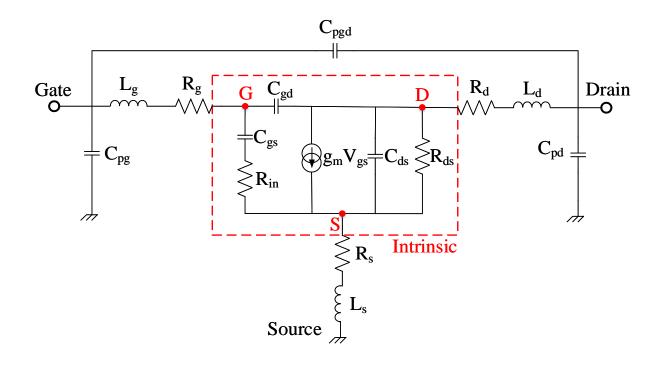

|   | 3.4        | 4.1 | Small-signal Equivalent Circuit Model                                | 44 |

|   | 3.5        | Me  | easurement Techniques                                                | 47 |

|   | 3.5        | 5.1 | On-wafer Small-signal Open-Short De-embedding                        | 47 |

|   | 3.6        | Fal | prication Process                                                    | 50 |

|   | 3.7        |     |                                                                      |    |

|   |            | Im  | pact of AlN Spacer on Device Characteristics                         | 52 |

|   | 3.7        |     | pact of AlN Spacer on Device Characteristics<br>Material and Devices |    |

|   | 3.7<br>3.7 | 7.1 |                                                                      | 52 |

|   | 3.8   | .1   | Material and Devices                                                      | 57   |

|---|-------|------|---------------------------------------------------------------------------|------|

|   | 3.8   | .2   | Results and Discussion                                                    | 58   |

|   | 3.9   | Imp  | pact of Source-to-drain Separation on Device Characterises.               | 62   |

|   | 3.9   | .1   | Results and Discussion                                                    | 63   |

|   | 3.10  | E    | Effect of GaN Buffer Thickness on Device Performance                      | 67   |

|   | 3.11  | C    | Conclusion                                                                | 69   |

| 4 | M     | MIC  | Transmission Media and Passive Devices Technology for GaN-on-LR Si.       | 70   |

|   | 4.1   | Intr | oduction                                                                  | 70   |

|   | 4.2   | Des  | sign of Passive Components                                                | 71   |

|   | 4.2   | .1   | Microstrip Lines                                                          | 71   |

|   | 4.2.2 |      | Metal-Insulator-Metal (MIM) Capacitor                                     | 74   |

|   | 4.2   | .3   | On-chip RF Spiral Inductors                                               | 77   |

|   | 4.3   | Mo   | delling and Measurements                                                  | 80   |

|   | 4.4   | Nov  | vel Transmission Media Technology                                         | 80   |

|   | 4.4   | .1   | Influence of Design Parameters                                            | 82   |

|   | 4.4   | .2   | Results and Discussion.                                                   | 86   |

|   | 4.5   | Lov  | w-loss MIM Capacitors                                                     | 90   |

|   | 4.5   | .1   | Results and Discussion                                                    | 91   |

|   | 4.6   | Hig  | h-Q Inductors                                                             | 94   |

|   | 4.6   | .1   | Results and Discussion                                                    | 94   |

|   | 4.7   | Via  | bility of the Developed Transmission Media Technology for THz Frequencies | s 98 |

|   | 4.7   | .1   | Results and Discussion                                                    | 100  |

|   | 4.7   | .2   | Short-circuited stub filters                                              | 102  |

|   | 4.8   | Cor  | nclusion                                                                  | 104  |

| 5 | Co    | nclu | sions and Future Work                                                     | 105  |

|   | 5.1   | Cor  | nclusions                                                                 | 105  |

|   | 5.1.2   | Demonstration of Low-loss Transmission Media for GaN-on-LR Si           |

|---|---------|-------------------------------------------------------------------------|

|   | Technol | ogy                                                                     |

| 5 | .2 Fut  | ure Work                                                                |

|   | 5.2.1   | Material Optimisation                                                   |

|   | 5.2.2   | Fabrication Technology                                                  |

|   | 5.2.3   | Thermal Management in GaN-based Heterostructures on LR Si Substrates109 |

| 6 | Bibliog | raphy                                                                   |

## List of Figures

| Figure 3.4: HEMT small-signal equivalent circuit model. Elements inside the dashed box                                   |

|--------------------------------------------------------------------------------------------------------------------------|

| show the intrinsic device, whereas the elements outside represent device Parasitics                                      |

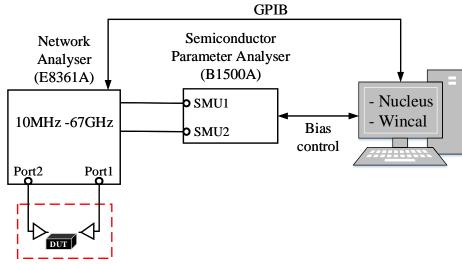

| Figure 3.5: DC and RF measurement system at the University of Glasgow                                                    |

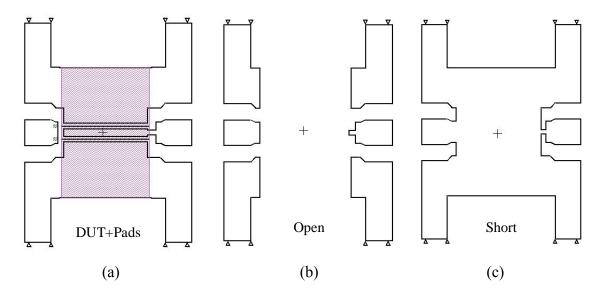

| Figure 3.6: Open-Short de-embedding structures. (a) DUT with the measurement pads. (b)                                   |

| Open dummy structure. And (c) short dummy structure                                                                      |

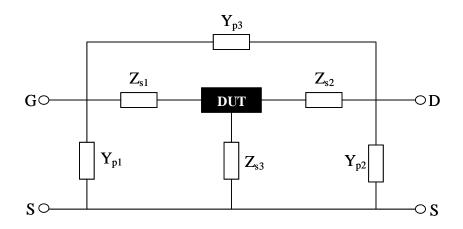

| Figure 3.7: Equivalent circuit used for two-step de-embedding of measured high-frequency                                 |

| data of HEMTs                                                                                                            |

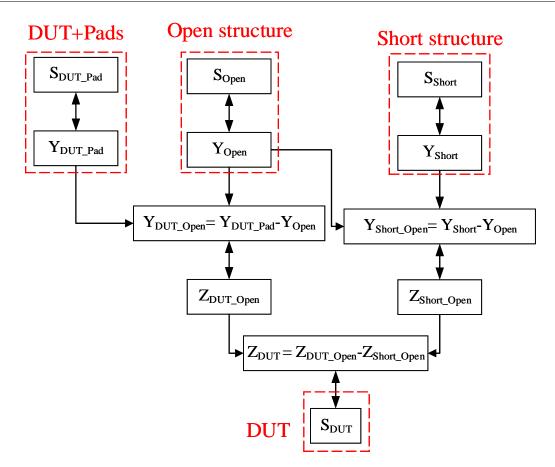

| Figure 3.8: Open-Short de-embedding procedure                                                                            |

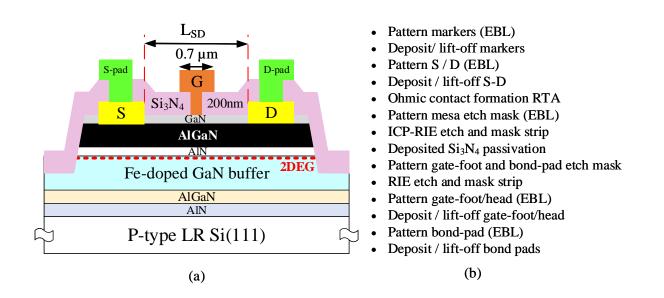

| Figure 3.9: (a) Cross-sectional schematic view. And (b) the process flow for the fabrication                             |

| of T-gate AlGaN/GaN HEMT on LR Si with $Si_3N_4$ passivation                                                             |

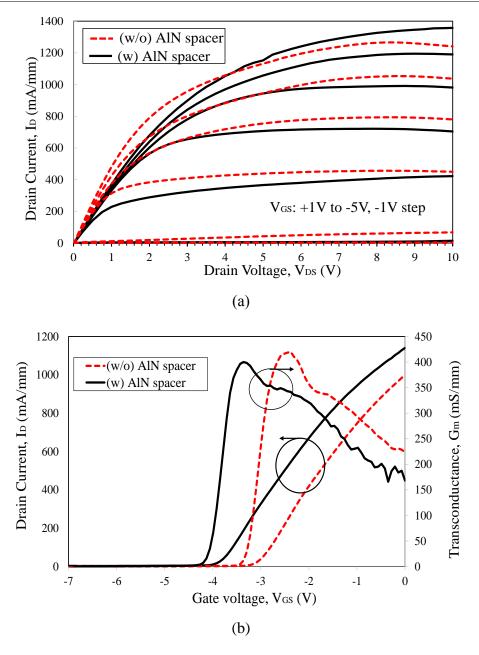

| Figure 3.10: (a) Output. And (b) Transfer characteristics at a fixed drain voltage, $V_{DS} = 5V$                        |

| of $2 \times (0.3 \times 100) \mu\text{m}^2$ AlGaN/GaN HEMTs on LR Si with (w) and without (w/o) the AlN                 |

| interlayer                                                                                                               |

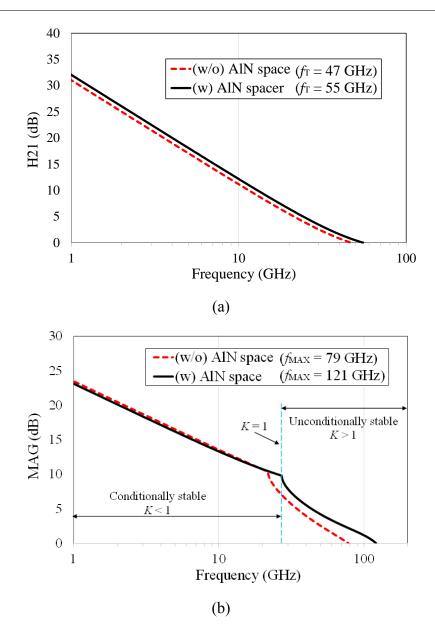

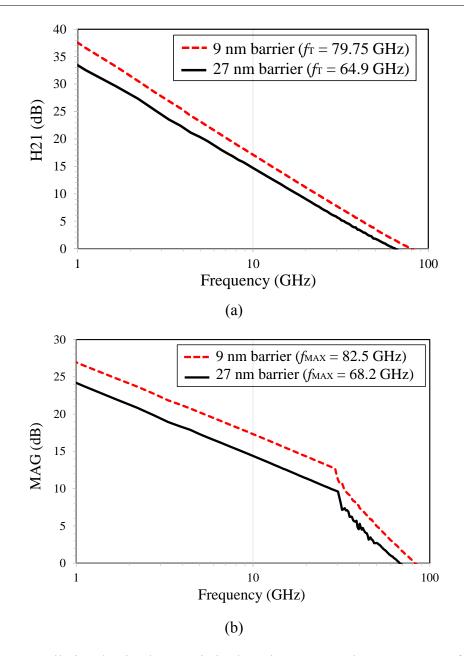

| Figure 3.11: Small-signal gain characteristics based on extracted S-parameters of a 0.3 $\mu$ m ×                        |

| 200 $\mu$ m AlGaN/GaN HEMTs on LR Si (111) substrate at $V_{DS} = 5$ V and $V_{GS} = -3.2$ V(with                        |

| AlN spacer), and $V_{GS} = -2.4$ V (without AlN spacer). (a) $H_{21}$ . And (b) MAG                                      |

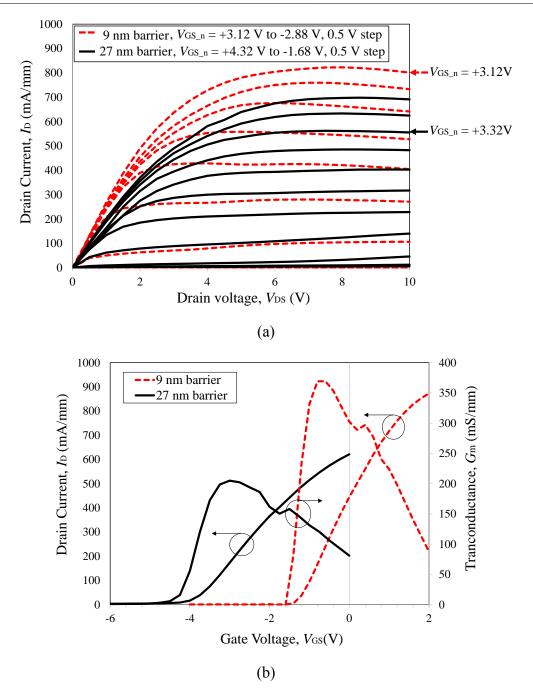

| Figure 3.12: (a) Output. And (b) Transfer characteristics of $2 \times (0.27 \times 100) \mu\text{m}^2$                  |

| AlGaN/GaN HEMTs on LR Si with two different top barriers; 27 nm $Al_{0.25}Ga_{0.75}N$ and 9 nm                           |

| Al <sub>0.35</sub> Ga <sub>0.65</sub> N. $V_{GS_n}$ is $V_{GS}$ normalised to $V_T$                                      |

| Figure 3.13: Small-signal gain characteristics based on extracted S-parameters of a 0.27 µm                              |

| × 200 $\mu$ m AlGaN/GaN HEMTs LR Si at $V_{DS} = 5.5$ V and $V_{GS} = -0.5$ V (9 nm barrier), and                        |

| $V_{\rm DS} = 3$ V and $V_{\rm GS} = -3$ V (27 nm barrier). (a) $H_{21}$ . And (b) MAG                                   |

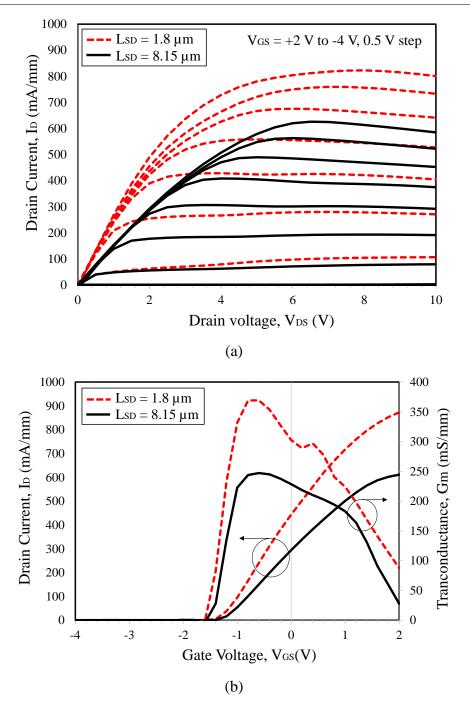

| Figure 3.14: (a) Output. And (b) Transfer characteristics of $2 \times (0.27 \times 100) \mu\text{m}^2$                  |

| AlGaN/GaN HEMTs on LR Si with $L_{SD} = 1.8 \mu\text{m}$ and $8.15 \mu\text{m}$                                          |

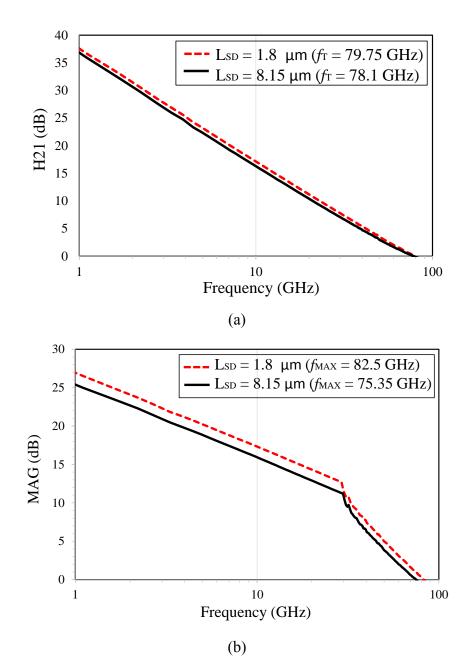

| Figure 3.15: Small-signal gain characteristics based on extracted S-parameters of a $2 \times (0.27)$                    |

| × 100) $\mu$ m <sup>2</sup> AlGaN/GaN HEMTs LR Si at $V_{GS} = -0.5$ V, and $V_{DS} = 5.5$ V ( $L_{SD} = 1.8 \mu$ m) and |

| $V_{\rm DS} = 6.5 \text{ V} (L_{\rm SD} = 8.15 \mu\text{m}).$ (a) $H_{21}$ . And (b) MAG                                 |

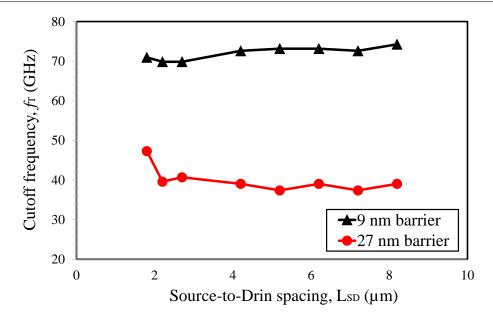

| Figure 3.16: Unity current gain frequency against source-to-drain spacing of a $2 \times (0.27 \times$                   |

| 100) $\mu$ m <sup>2</sup> AlGaN/GaN HEMTs LR Si                                                                          |

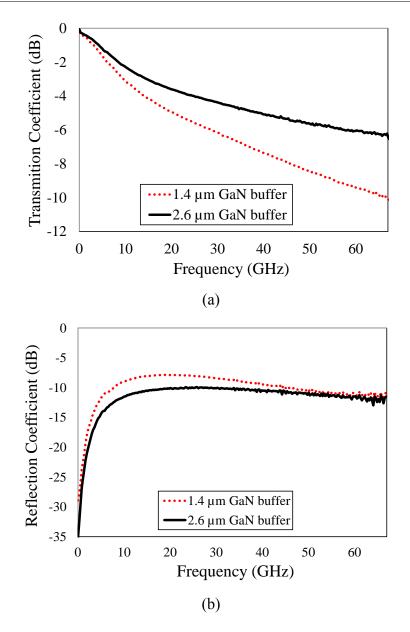

| Figure 3.17: Measured S-parameters (without de-embedding) results of 50 $\Omega$ transmission                            |

| media fabricated on GaN-on-LR Si with GaN buffer thicknesses of $1.4 \mu\text{m}$ and $2.6 \mu\text{m}$ on the           |

| mesa etched areas. (a) Transmission coefficient. And (b) Reflection coefficient                                          |

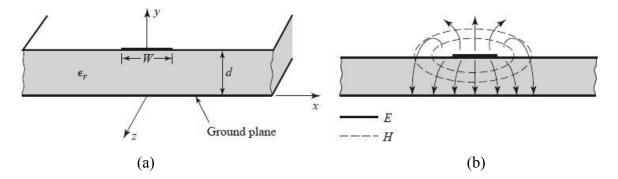

| Figure 4.1: Microstrip transmission line. (a) Structure. And (b) Electrical and magnetic field                           |

| lines [98]                                                                                                               |

| nnes [70].                                                                                                               |

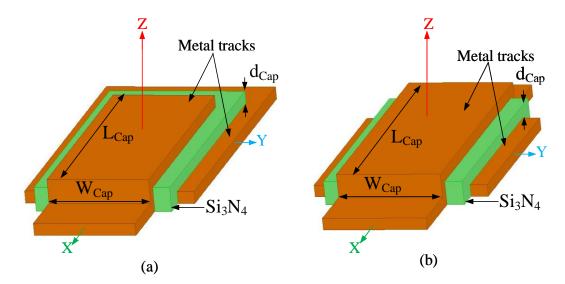

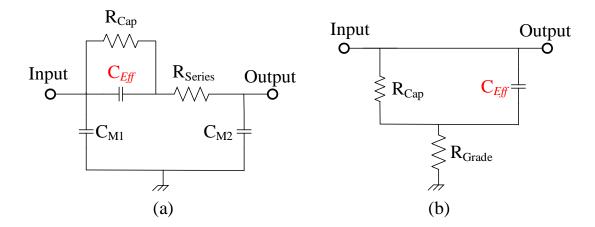

| Figure 4.2: Layout of in-line MIM capacitors. (a) Series. And (b) Shunt                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.3: Equivalent circuit model of (a) Series MIM capacitor. And (b) Shunt MIM                                                           |

| capacitor [58] [107]76                                                                                                                        |

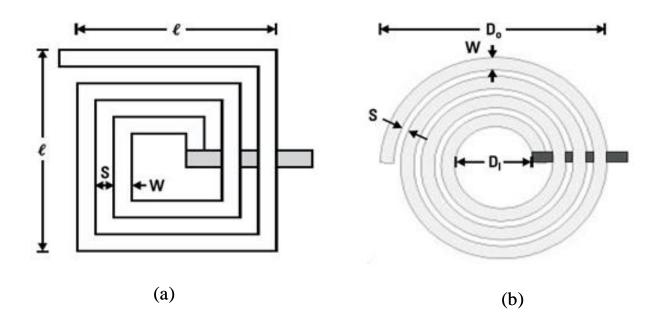

| Figure 4.4: Geometry of spiral inductors (a) Rectangular. And (b) Circular [12]77                                                             |

| Figure 4.5: Schematic of the equivalent circuit model for a spiral inductor                                                                   |

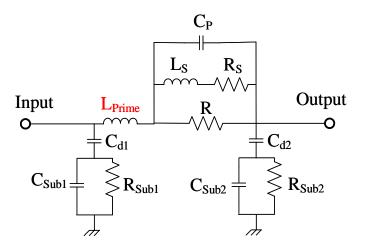

| Figure 4.6: Oblique projection of the fabricated 1 mm-length 50 $\Omega$ lines (a) S-Microstrip line                                          |

| with $S = 4.5 \ \mu\text{m}$ and $G = 13.2 \ \mu\text{m}$ . And (b) SE-Microstrip lines with $S = 9 \ \mu\text{m}$ , $G = 20 \ \mu\text{m}$ , |

| $Wg = 100 \mu m.$                                                                                                                             |

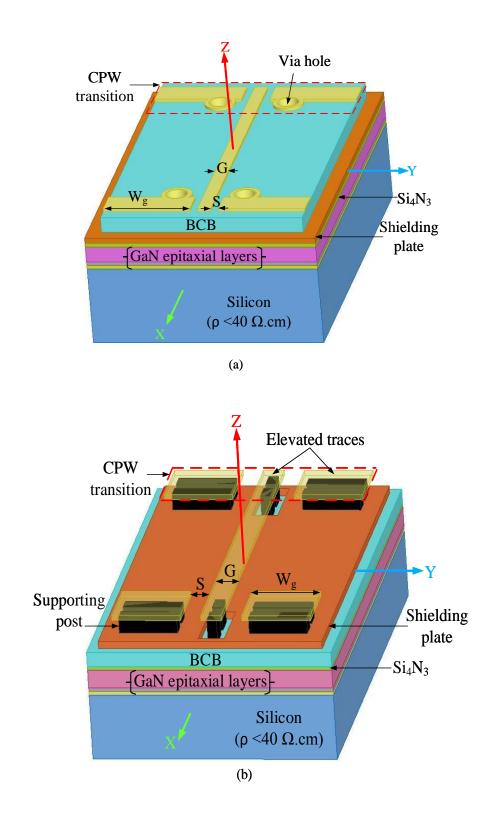

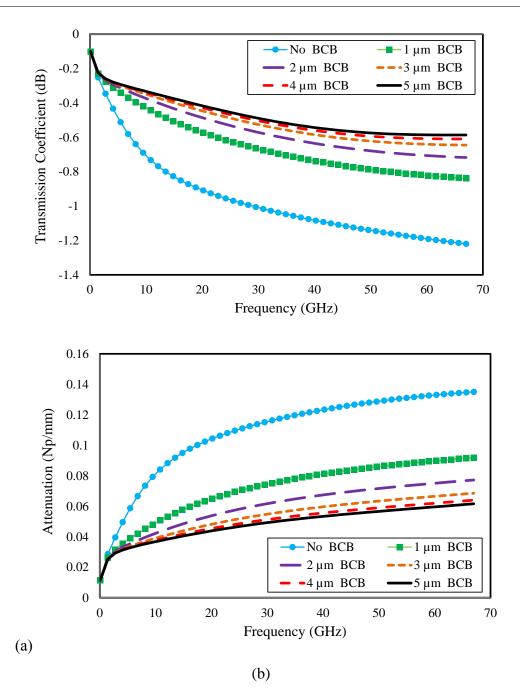

| Figure 4.7: Effect of BCB thickness on S-Microstrip lines (a) Transmission coefficient. And                                                   |

| (b) Attenuation                                                                                                                               |

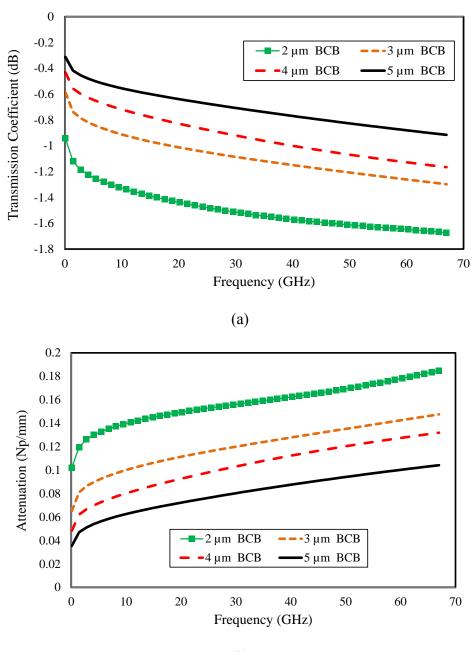

| Figure 4.8: Effect of BCB thickness on SE-Microstrip line (a) Transmission coefficient. And                                                   |

| (b) Attenuation                                                                                                                               |

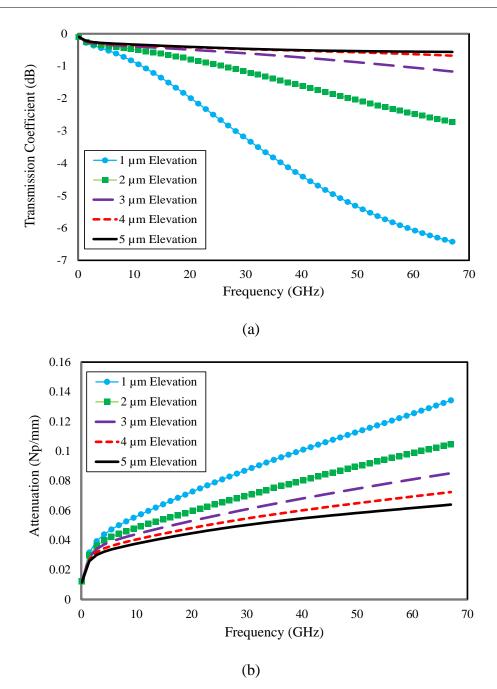

| Figure 4.9: Effect of elevation height on SE-Microstrip line (a) Transmission coefficient. And                                                |

| (b) Attenuation                                                                                                                               |

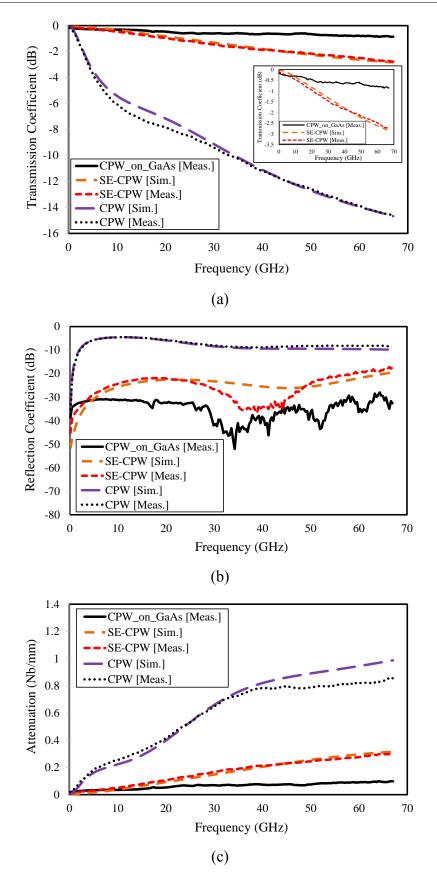

| Figure 4.10: Measured and simulated S-parameters results of conventional CPW and SE-                                                          |

| CPW lines. (a) Transmission coefficient, $S_{21}$ . (b) Reflection coefficient, $S_{11}$ . (c) Attenuation,                                   |

| α                                                                                                                                             |

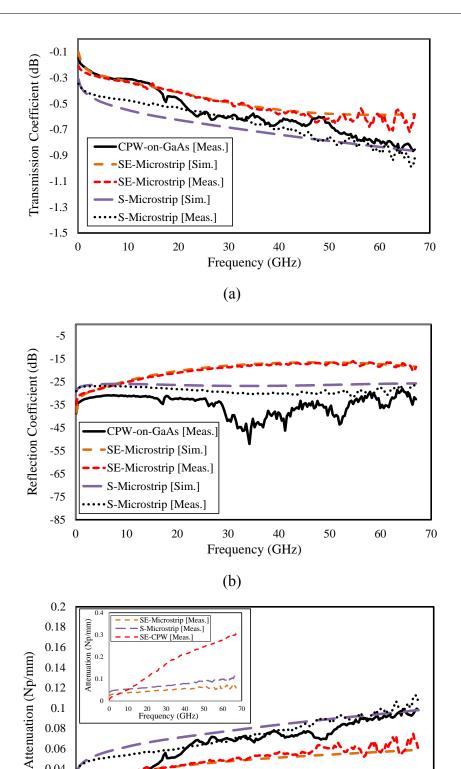

| Figure 4.11: Measured and simulated S-parameters results of SE-CPW, S-Microstrip, SE                                                          |

| Microstrip lines on GaN-on-LR Si and CPW-on-GaAs lines. (a) Transmission coefficient,                                                         |

| $S_{21}$ . (b) Reflection coefficient, $S_{11}$ . (c) Attenuation, $\alpha$                                                                   |

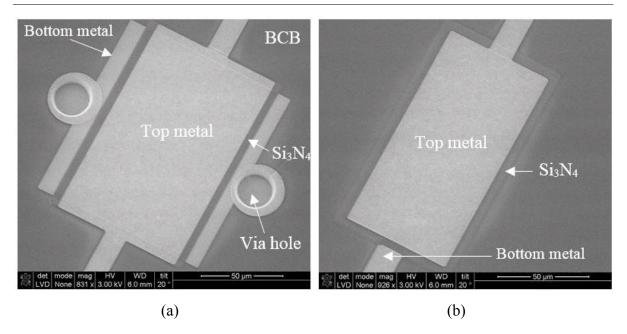

| Figure 4.12: SEM images of the fabricated in-line (a) Series. And (b) Shunt MIM capacitors                                                    |

| using S-Microstrip transmission media technology                                                                                              |

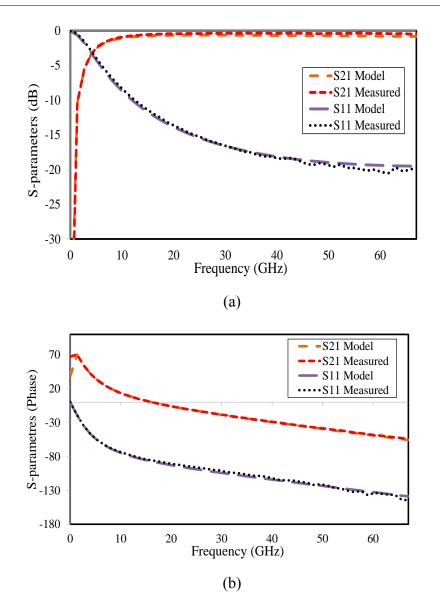

| Figure 4.13: Measured and modelled S-parameters results of a $60 \times 20 \ \mu m^2$ series capacitor                                        |

| integrated to 0.19 mm-length S-Microstrip lines, (a) Magnitude (dB). And (b) Phase                                                            |

| (degrees)                                                                                                                                     |

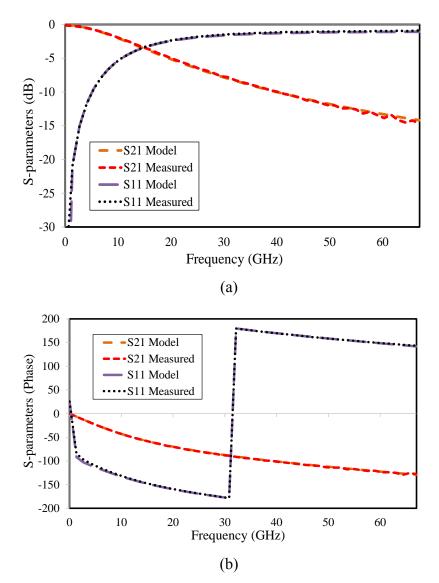

| Figure 4.14: Measured and modelled S-parameters results of a $60 \times 20 \mu\text{m}^2$ shunt capacitor                                     |

| integrated to 0.19 mm-length S-Microstrip lines, (a) Magnitude (dB). And (b) Phase                                                            |

| (degrees)                                                                                                                                     |

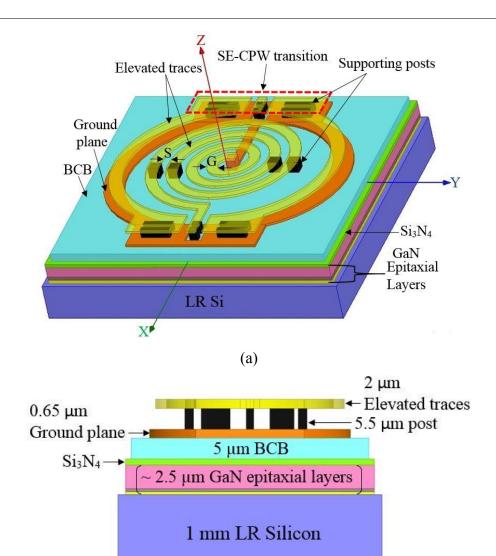

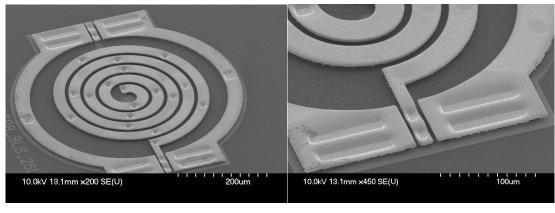

| Figure 4.15: (a) 3-dimentional view. (b) Cross-sectional view. And (c) SEM image of the                                                       |

| fabricated MMIC spiral elevated inductor integrated to 50 Ω SE-CPW on BCB95                                                                   |

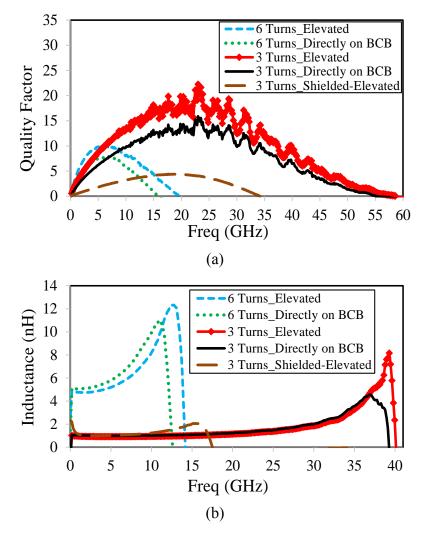

| Figure 4.16: Comparison of the measured results of the fabricated MMIC inductors versus                                                       |

| frequency: (a) Quality-factor and (b) Inductance                                                                                              |

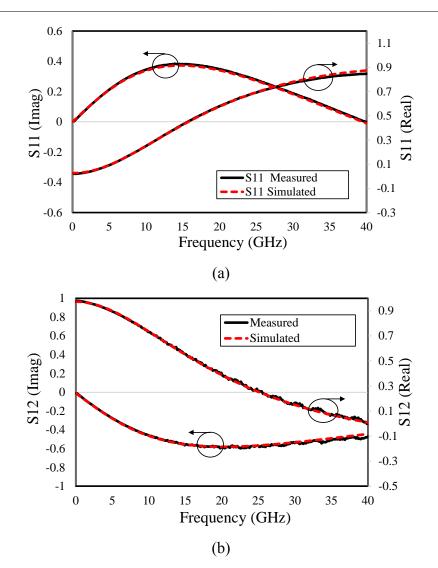

| Figure 4.17: Measured versus modelled (a) $S_{11}$ and (b) $S_{21}$ for a 3-turns spiral elevated                                             |

| inductor on BCB for model validation                                                                                                          |

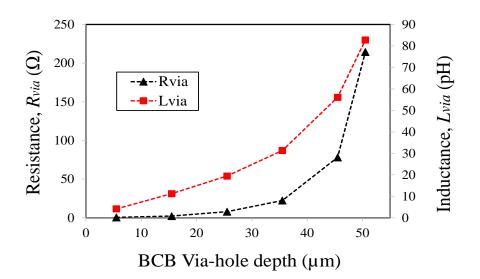

| Figure 4.18: Extracted parasitic resistance ( $R_{via}$ ) and inductance ( $L_{via}$ ) values versus via-hole |

|---------------------------------------------------------------------------------------------------------------|

| depth of the S-Microstrip line                                                                                |

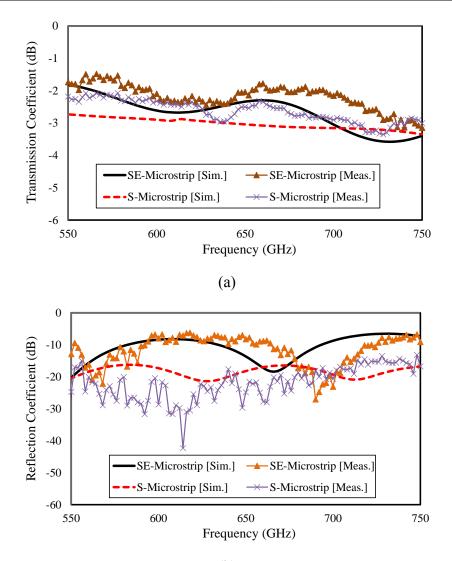

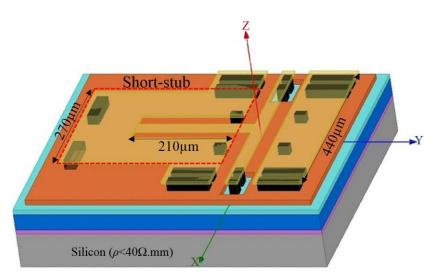

| Figure 4.19: Measured and simulated S-parameters results of 1mm-length 50 $\Omega$ S-Microstrip               |

| and SE-Microstrip lines on GaN-on-LR Si. (a) Transmission coefficient, $S_{21}$ . (b) Reflection              |

| coefficient, $S_{11}$ . (c) Attenuation, $\alpha$                                                             |

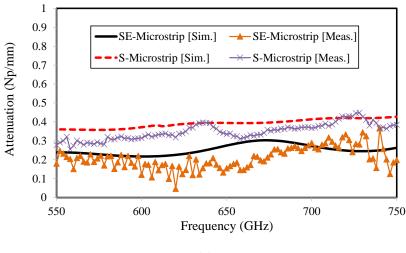

| Figure 4.20: Oblique projection of the fabricated SE-CPW short-circuited stub filter with the                 |

| fabricated dimensions                                                                                         |

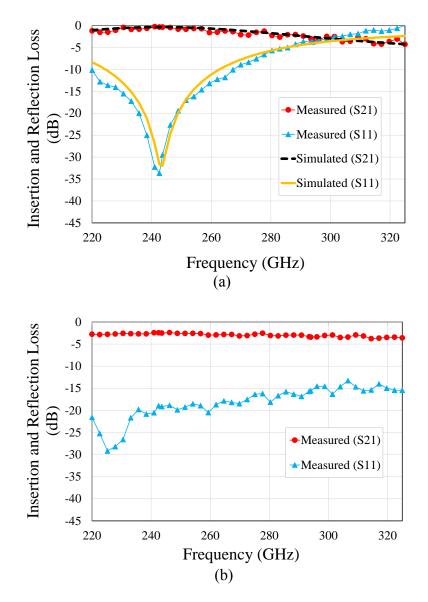

| Figure 4.21: S-parameters results of the fabricated SE-CPW short-circuited stub filter (a) with               |

| BCB insert, and (b) without BCB insert103                                                                     |

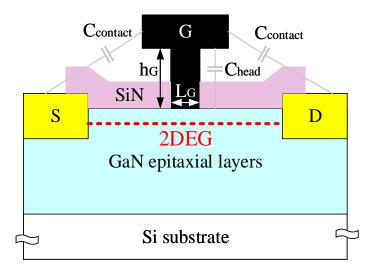

| Figure 5.1: Cross-sectional view of two-level T-shaped gate module and associated parasitic                   |

| capacitances                                                                                                  |

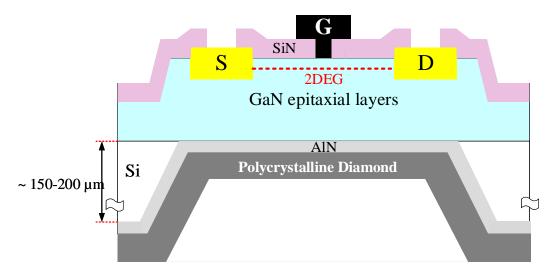

| Figure 5.2: Cross-sectional view of GaN-based heterostructure on Si with incorporated                         |

| backside diamond110                                                                                           |

### List of Tables

| Table 1.1: Physical properties for group III-Nitrides compared with other semiconductor of                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| interest                                                                                                                                                                         |

| Table 1.2: State of the art DC and RF performance of GaN-based heterostructures grown on                                                                                         |

| Si4                                                                                                                                                                              |

| Table 3.1: Epitaxial layer structure of the compared devices; with and without the AlN                                                                                           |

| interlayer53                                                                                                                                                                     |

| Table 3.2: Fitted values for all model parameters in the equivalent circuit for a $L_{\rm G} = 0.3 \mu m$                                                                        |

| and $W_{\rm G} = (2 \times 100) \mu\text{m}$ transistors at $V_{\rm DS} = 5 \text{V}$ and $V_{\rm GS} = -3.2 \text{V}$ (Sample A), and $V_{\rm GS} = -2.4$                       |

| V (Sample B)56                                                                                                                                                                   |

| Table 3.3: Epitaxial layer structure of the compared samples, with different AlGaN Schottky                                                                                      |

| barriers                                                                                                                                                                         |

| Table 3.4: Fitted values for all model parameters in the equivalent circuit for a $L_{\rm G} = 0.27 \mu m$                                                                       |

| and $W_{\rm G} = (2 \times 100) \mu\text{m}$ transistors at $V_{\rm DS} = 5.5 \text{V}$ and $V_{\rm GS} = -0.5 \text{V}$ (sample C), and $V_{\rm DS} = 3$                        |

| V and $V_{GS} = -3$ V (sample D)62                                                                                                                                               |

| Table 3.5: Fitted values for all model parameters in the equivalent circuit for a $L_{\rm G} = 0.27 \mu m$                                                                       |

| and $W_{\rm G} = (2 \times 100) \mu\text{m}$ transistors at $V_{\rm GS} = -0.5 \text{V}$ , and $V_{\rm DS} = 5.5 \text{V}$ ( $L_{\rm SD} = 1.8 \mu\text{m}$ ) and $V_{\rm DS} =$ |

| 6.5 V ( $L_{SD} = 8.15 \ \mu m$ )                                                                                                                                                |

| Table 4.1: Derived equivalent circuit model and its coefficients for MIM capacitors94                                                                                            |

| Table 4.2: Extracted parameters for the equivalent circuit model and measured Q-factor and                                                                                       |

| <i>f</i> <sub>SRF</sub> of spiral inductors                                                                                                                                      |

## List of Abbreviations

- 5G: Fifth Generation

- ABF: Ajinomoto Build-up Film

- ALD: Atomic Layer Deposition

- AlGaN: Aluminium Gallium Nitride

- AlN: Aluminium Nitride

- BCB: Benzocyclobutene

- BELL: Beam-writer Exposure for Lithography Engineers

- CAD: Computer Aided Design

- CVD: Chemical Vapour Deposition

- DC: Direct Current

- DHFET: Double-Heterostructures Field Effect Transistor

- DUT: Device Under Test

- EBL: Electron Beam Lithography

- GaN: Gallium Nitride

- GHz: Gigahertz

- HCL: Hydrochloric Acid

- HEMT: High Electron Mobility Transistor

- HF: Hydrofluoric Acid

- HFSS: High Frequency Structure Simulator

- HR: High Resistivity

- ICP-CVD: Inductively-Coupled Plasma Chemical Vapour Deposition

- ICP-RIE: Inductively-Coupled Plasma Reactive Ion Etching

**IP: Internet Provider**

ISS: Impedance Standard Substrate

LDMOS: Laterally Diffused Metal Oxide Semiconductor

LOR: Lift-Off Resist

LR: Low Resistivity

MAX: Maximum Available Gain

MESFET: Metal-Semiconductor Field Effect Transistor

MIM: Metal-Insulator-Metal

MMIC: Microwave Monolithic Integrated Circuit

MOCVD: Metal-Organic Chemical Vapor Deposition

PECVD: Plasma Enhanced Chemical Vapour Deposition

PMMA: Poly-Methyl Methacrylate

**RF:** Radio Frequency

**RIE: Reactive Ion Etching**

SCE: Short Channel Effect

SEM: Scanned Electron Microscopy

SI: Semi-Insulating

Si: Silicon

Si<sub>3</sub>N<sub>4</sub>: silicon nitride

SiC: silicon carbide

SiO<sub>2</sub>: silicon dioxide

SOLT: Short-Open-Load-Thru

SRF: Self-Resonance Frequency

TE: Transverse Electric

TEM: Transverse Electromagnetic

TM: Transverse Magnetic TMIC: THz Monolithic Integrated Circuits UV: Ultra-Violet VDP: Van-Der-Pauw WLAN: Wireless Local Networks

## Chapter 1

## Introduction and the State of the Art

## 1.1 Demand for High Output Power and High Frequency Transistors at mm-wave Frequencies

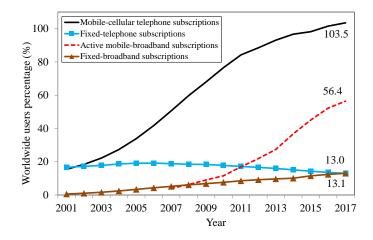

The demand for creating smaller chip sizes along with greater functionality has led to tremendous semiconductor technology development and the establishment of a new market for semiconductor devices. Silicon (Si)-based devices offer a cost-effective and promising performance technology for data processing applications. Recently, there has been significant research and development aiming to increase the frequency of operation in order to satisfy the requirements for high frequency and high power applications. The broadcasting of telecommunication signals is an example of the power amplifiers' market [1]. Figure 1.1 shows how rapidly the worldwide telecommunications sector has grown since 2001. The number of internet/mobile users has intensively increased as a result of the development of wireless local networks (WLAN) and the enhancement of mobile phone technologies. According to studies from CISCO, it is expected that by 2021 there will be nearly 4.6 billion global internet users, and consequently the Internet Provider (IP) traffic will reach an annual run rate of 3.3 zettabytes [2]. This will lead to a massive demand on bandwidths and high data rate requirements. Therefore, efficient power amplifiers operating in the mm-wave frequency range are essential for today's telecommunication market.

Figure 1.1: Wireless communications and internet access services growth over the last decades. Source: ITU World Telecommunications / ICT Indicator Database.

The availability of the 57-64 GHz licence-free frequency range has made high-power amplifiers operating at frequencies beyond 50 GHz attractive candidates for various applications, including short-range point-to-point wireless Gbit/s and inter-satellite communications. At V-band frequency range (50-57 GHz), the existence of atmospheric attenuation makes it possible to identify multiple users in a compact area with mitigated signal interference. This could be ultimately utilised for the next generation WLAN technologies. In addition to wireless communication applications, high power devices are commonly used at W-band frequency ranges (74-77 GHz) for automotive radar applications, which are essentially used for adaptive cruise and safety systems.

Gallium nitride (GaN)-based devices are emerging as promising solid-state microwave power devices because of their capabilities in enabling power-switching operations at high voltages/currents at high speed and greater efficiency at frequencies beyond 50 GHz [3]. This is attributed to their inherent material properties, such as a wide bandgap (> 3 eV), a high critical electrical field (2-4 MV/cm) and high saturation electron drift velocity (> 2 × 10<sup>7</sup> V/cm). Table 1.1 demonstrates the properties of the widely used semiconductor materials [4] [5]. For heat dissipation purposes and high frequency operation, GaN is typically grown on high thermal and Semi-Insulating (SI) substrates, such as silicon carbide (SiC) and Diamond) to allow high power and high frequency operation [6] [7]. SiC is more desirable for GaN-based devices since it has a close lattice match with III-nitrides [5]. Therefore, GaN-based transistors are considered as superior candidates that could be utilized in many of the above applications.

| Material | $\begin{array}{c} \text{Lattice} & \text{Energy} \\ \text{bandgap} \\ \text{constant} \\ (\text{\AA}) & E_{\text{G}} \\ \text{(eV)} \end{array}$ |     | Maximum<br>electrical<br>field<br>(MV/cm) | Dielectric<br>constant<br>(ɛ <sub>r</sub> ) | Thermal<br>conductivity<br>(w/cmK) | Carrier<br>mobility<br>(cm <sup>2</sup> /Vs) |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------|---------------------------------------------|------------------------------------|----------------------------------------------|--|

| GaN      | 3.189 3.4 2                                                                                                                                      |     | 7.8                                       | 1.4                                         | 2000                               |                                              |  |

| AlN      | 3.112                                                                                                                                            | 6.2 | -                                         | 8.5                                         | 1.8-5.5                            | 300                                          |  |

| SiC      | 3.081                                                                                                                                            | 3.3 | 2.5                                       | 9.8                                         | 4.9                                | 980                                          |  |

| Diamond  | 3.567                                                                                                                                            | 5.5 | 10                                        | 5.5                                         | 10-20                              | 1800                                         |  |

| Si       | 5.73                                                                                                                                             | 1.1 | 0.3                                       | 11.9                                        | 1.5                                | 1350                                         |  |

Table 1.1: Physical properties for group III-Nitrides compared with other semiconductor of interest.

#### 5.1 GaN-based High Electron Mobility Transistors (HEMTs) on Si Technology

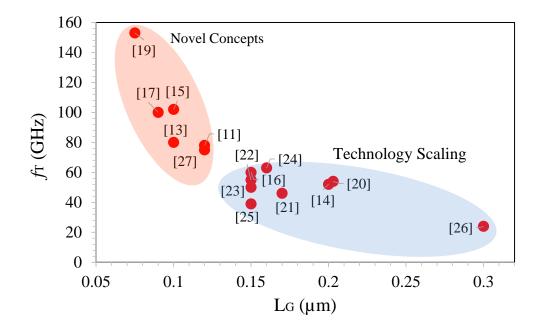

As a n example of utilising GaN-on-LR Si technology, recent work on the integration of GaN HEMT based gate driver and buck converters on SI-SiC substrates has achieved envelope tracking bandwidths of 20 MHz with power device switching frequencies up to 200 MHz [8]. The potential use of this circuit for 5G applications using GaN on Si substrates were both power and RF GaN on the same chip will offer the additional benefit of lower cost. Currently GaN grown on SI-SiC substrates are likely the best solution in terms of output power, thermal management and operation frequency. This technology have been rapidly developed over the last two decades, where current densities in excess of 3 A/mm and RF performance with cutoff frequency/maximum oscillation frequency ( $f_T/f_{MAX}$ ) 453/446 GHz have been demonstrated [9]. However, SI-SiC substrates are expensive and have limited availability in large substrate diameters, which is considered as a major concern for GaN-electronics. These factors coupled with the more demanding back side fabrication process for the realization of Microstrip Microwave Monolithic Integrated Circuits (MMICs) ultimately increase the cost of GaN-on-SiC electronics [10]. To leverage the economies of scale offered by large wafer diameters, GaN-based HEMT structures grown on high-resistivity (HR) Si substrates of diameters of up to 100 mm have been realized. Outstanding DC and RF performance have been achieved as a result of the advanced epitaxial material growth, where a current density of nearly 1 A/mm and an RF performance with  $f_T/f_{MAX}$  of 78/190 GHz respectively, have been demonstrated [11]. Table 1.2 summarises the most recent research and development of GaN-based heterostructures grown on Si substrates. It can clearly be seen that innovative fabrication technology and material structure optimisation are strongly required for high current densities (> 0.8 mA/mm) along with high RF characteristics ( $f_T > 60$  GHz), as indicated in Figure 1.2. The major breakthroughs can be summarised as follows:

- Development of regrowth based source/drain ohmic contacts (*R*<sub>C</sub>) for power loss reduction and RF characteristics enhancement [12].

- Adoption of in-situ Si<sub>3</sub>N<sub>4</sub> cap layer early passivation as part of the material growth process for device reliability enhancement and gate-leakage mitigation [13].

- Ultra-thin Schottky barrier layers which allow scaling the gate length and thus improving the DC and RF performance [11] [14].

• Insertion of an optimised AlN spacer layer and the use of AlGaN back barriers for better electron confinement and higher current densities [15].

|                                                                   | Schottky        | $L_{ m G}$       | 2DEG                  | DC                          |                                   |                                  |                               | RF                |                   |                           |      |

|-------------------------------------------------------------------|-----------------|------------------|-----------------------|-----------------------------|-----------------------------------|----------------------------------|-------------------------------|-------------------|-------------------|---------------------------|------|

| Technology                                                        | barrier<br>(nm) | $L_{\rm G}$ (nm) | $(\text{cm}^{-2})$    | μ<br>(cm <sup>2</sup> /V.s) | $R_{\rm SH}$<br>( $\Omega/\Box$ ) | $R_{\rm C}$ ( $\Omega/\rm{mm}$ ) | I <sub>DS_MAX</sub><br>(A/mm) | $G_{MAX}$ (mS/mm) | $f_{\rm T}$ (GHz) | f <sub>MAX</sub><br>(GHz) | Ref. |

| -                                                                 | AlGaN           | 150              | -                     | -                           | -                                 | -                                | -                             | -                 | 60                | 160                       | [16] |

| -                                                                 | 12.5<br>AlGaN   | 90               | 1.17×10 <sup>13</sup> | 2000                        | 314                               | 0.45                             | 0.82                          | 440               | 100               | 206                       | [17] |

| -                                                                 | AlGaN           | 500              | -                     | -                           | -                                 | 0.3                              | 0.75                          | 220               | 24.6              | 45.4                      | [18] |

| Regrowth contacts                                                 | 20<br>AlGaN     | 75               | 1.44×10 <sup>13</sup> | 1006                        |                                   | 0.11                             | 1.3                           | 290               | 153               | 22                        | [19] |

| In-situ AlN                                                       | 18<br>AlGaN     | 203              |                       |                             | 322                               | 0.6                              | 0.93                          | 335               | 54                | 182                       | [20] |

|                                                                   | 30<br>AlGaN     | 170              | 8×10 <sup>12</sup>    | 1600                        | 500                               | -                                | 0.55                          | 215               | 46                | 92                        | [21] |

| -AlN spacer<br>-Si-based<br>contacts                              | 20<br>AlGaN     | 150              | -                     | -                           | -                                 | -                                | 0.9                           | 320               | 55                | 130                       | [22] |

| BCB<br>encapsulation                                              | 25<br>AlGaN     | 150              | 8×10 <sup>12</sup>    | 1456                        |                                   | 0.2                              | 0.953                         | 300               | 50                | 47                        | [23] |

| AlGaN back barrier                                                | 17.5<br>AlGaN   | 160              | 9.4×10 <sup>12</sup>  | 1550                        | 430                               | 0.3                              | 0.8                           | 260               | 63                | 226                       | [24] |

| Ta/Si<br>contacts                                                 | 18<br>AlGaN     | 150              | 1.1×10 <sup>13</sup>  | 1450                        |                                   | 0.24                             | 0.83                          | 250               | 39                | 39                        | [25] |

| -In-situ Si <sub>3</sub> N <sub>4</sub><br>-AlGaN back<br>barrier | 25<br>AlGaN     | 300              | -                     | 1500                        | 530                               | -                                | 0.85                          | 220               | 24                | 47                        | [26] |

|                                                                   | 6<br>AlN        | 100              | 2×10 <sup>13</sup>    | 1400                        | 240                               | 0.35                             | 1.8                           | 500               | 80                | 192                       | [13] |

| -In-situ Si <sub>3</sub> N <sub>4</sub><br>-AlGaN back<br>barrier | 9<br>AlInN      | 100              | 2.6×10 <sup>13</sup>  | 400                         | 460                               | 0.54                             | 1.3                           | 330               | 102               | 89                        | [15] |

| -In-situ Si <sub>3</sub> N <sub>4</sub><br>-AlGaN back<br>barrier | 6<br>AlN        | 200              | 2×10 <sup>13</sup>    | 1400                        | 240                               | 0.35                             | 1.8                           | 470               | 52                | 91                        | [14] |

| -                                                                 | 6<br>AlN        | 120              | 2×10 <sup>13</sup>    | 1400                        | 240                               | 0.4                              | 1.5                           | 550               | 75                | 102                       | [27] |

| -                                                                 | 4<br>AlN        | 120              | 1.5×10 <sup>13</sup>  | 1250                        | 310                               | 0.35                             | 1                             | 390               | 78                | 190                       | [11] |

Table 1.2: State of the art DC and RF performance of GaN-based heterostructures grown on Si.

Figure 1.2: Summary of 'State of the Art' GaN-based heterostructures on Si performance  $(f_T)$  versus gate-length  $(L_G)$ , achieved by the international research laboratories.

One of the major issues associated with growing GaN epitaxial layers on HR Si substrates is RF losses, as a result of the formation of a thin conductive layer at the interface following the diffusion of Ga into the Si substrate. This can be classified as an epitaxial material growth issue and has been resolved by controlling the Ga discussion throughout the growth process [28] [29]. In addition to the outstanding DC and RF performance obtained by GaN-based HEMTs on HR Si, HR Si substrates are still relatively expensive compared to the more commonly used LR Si substrates and maintaining high resistivity through the high temperature GaN growth process is challenging. Several research teams have realized RF GaN HEMTs on LR Si. Despite the well-behaved DC performance, these devices have shown a lower RF performance than that achieved using SiC, Sapphire or HR Si [30] [31]. The lower RF performance is mainly because of the RF signal coupling to the conductive Si substrate.

The technology development for these applications initially aims to demonstrate MMICs. However, not only does the parasitic loss associated with LR Si substrate negatively affect the RF performance of transistors but also makes it impossible to realise standard transmission media technology for MMIC applications.

#### 5.2 Transmission Media Technology for GaN-on-LR Si Substrates.

Realization of low-loss waveguides, capacitors and inductors with high-quality factors at mmwave frequencies are of great importance for circuit application where interconnects and passive components are needed. Therefore, low-loss transmission media are necessarily required for cost-effective GaN-based MMIC technology.

Previously, a number of researchers have attempted to develop high quality transmission media on LR Si substrates. Some reports have shown a reduction in losses using thick insulators such as polyamide [32], Ajinomoto Build-up Film (ABF) and SU-8 [33] but these still have relatively high attenuation at mm-wave frequencies. On the other hand, reports have shown that attaching silicon dioxide (SiO<sub>2</sub>) to the surface of the Si substrate, induces a low-resistivity layer at the interface between the SiO<sub>2</sub> and the Si surface [34]. These phenomena cause degradation of the attenuation constant. Several approaches have been suggested to avoid such undesirable effects, such as introducing polysilicon at the Si-SiO<sub>2</sub> interface [35], removing the Si substrate from the backside substrate by micromachining [36] and using the floating shield technique [37]. However, each of these methods requires complex and lengthy fabrication processes. Insertion of a low-losses, low dielectric constant, k, layer of benzocyclobutene (BCB) as an insulator was proved to be another technique for substrate coupling reduction [38]. This approach, compared to other more complicated techniques [36] [37], has the advantage of accommodating active circuits underneath the passive components and interconnectors with no degradation of active device performance [39].

#### 5.3 Research Goal and Objects

The main focus of this project is to develop a viable MMIC technology for GaN-based HEMTs grown on LR and HR Si substrates for mm-wave frequencies applications. The challenge in this technology development is to decouple the substrate from both active, passive devices and transmission media interconnect. LR Si substrates are intrinsic lossy to the mm-wave signal. In addition, recent studies of AlGaN/GaN HEMTs grown on HR Si substrates have shown degradation of mm-wave performance at high temperature (i.e. telecommunication basestation applications where devices are operated at high power); this is due to the increase of the intrinsic carrier density in the HR Si substrate [40]. Despite that much lower temperature

dependence on mm-wave signal was observed on the AlGaN/GaN HEMTs grown on LR Si and exhibits better performance at high temperature than that of AlGaN/GaN HEMTs grown on HR Si, it remains not viable technology for mm-wave applications. This proves that the technology developed in this work can effectively be utilised independent of substrate technology with better performance at mm-wave and THz frequencies than that of conventional Microstrip and Coplanar waveguide (CPW). As mentioned earlier, the RF performance of GaN-on-LR Si substrates technology remains relatively poor, compared to those grown on SI-SiC and HR Si substrates at room temperatures. This is mainly because of the parasitic loss caused by the conductive substrate. Mitigating this issue is the first step towards the realisation of high performance MMIC circuits' technology at mm-wave frequencies. The main objectives of this work are to:

- develop a reliable, high yield, cost-effective and MMIC-compatible fabrication process for GaN-on-LR Si technology.

- demonstrate high DC and RF performance AlGaN/GaN HEMTs on LR Si for V-band and higher frequencies applications.

- realise a low-loss transmission media technology that can be integrated with the demonstrated active devices for future MMIC applications.

#### 5.4 Thesis Outline

This thesis consists of five chapters:

**Chapter 1** provides a brief overview of the state-of-the-art GaN-based heterostructures grown on Si substrates technology, followed by the introduction of GaN-on-LR Si technology as an alternative solution for cost-effective MMIC applications. The challenges associated with the realisation of both active and passive MMIC devices at mm-wave frequencies using this technology are also addressed.

**Chapter 2** describes the fabrication techniques required for the realisation of MMICcompatible active and passive devices using GaN-based on LR Si technology for mm-wave applications. It begins by introducing the material properties used in this work, followed by a brief description of the main fabrication processing techniques, such as sample preparation, lithography, metallisation and dry etch. Then, the detailed fabrication process of AlGaN/GaN HEMTs on LR Si is provided. Finally, the fabrication process of novel transmission media technology and various passive components is introduced.

**Chapter 3** focuses on the active devices, namely AlGaN/GaN HEMTs on LR Si. This includes a summary of the theory and operation of HEMTs in briefly and with special emphasis on the most critical figures of merit that influence the DC and RF performance of the devices. In addition, the RF performance of HEMTs fabricated is further analysed using the RF smallsignal equivalent circuit model. Next, the DC and RF characteristics of the AlGaN/GaN HEMTs developed on LR Si are systematically introduced; various material structures and device geometries are investigated aiming for performance enhancement.

**Chapter 4** is devoted to the development of a low-loss MMIC interconnect transmission media technology for GaN-on-LR Si technology. An overview of the basic operation of Microstrip lines and passive elements, such as Metal-Insulator-Metal (MIM) capacitors and spiral inductors, is provided. Novel transmission media interconnect for MMIC technology (Shielded-Microstrip and Shielded-Elevated Microstrip lines) is also presented. 3-D full wave electromagnetic simulations using Ansoft HFSS<sup>TM</sup> of the proposed transmission media are carried out as per fabrication requirements. In-line shunt and series MIM capacitors, and High-Q inductors are introduced, proving the viability of the new proposed transmission media for MMIC technology compatibility. The equivalent circuit models for the demonstrated passive components are also discussed.

**Chapter 5** concludes this research report by summarising its findings along with a discussion on the potential for future work.

## Chapter 2

## **Fabrication Techniques**

#### 2.1 Introduction

This chapter outlines the vertical material layer structures and the fabrication process required for the realisation of active and passive devices on GaN-based HEMTs grown on LR Si substrates. The fabrication process was carried out at the James Watt Nanofabrication Centre (JWNC) at the University of Glasgow. All levels of device definition utilised in this work are compatible with MMIC technology. The material vertical layer structures used in device fabrication are described. Next, the main fabrication process including sample preparation, Electron-beam (e-beam) lithography, photolithography, dry etch and deposition of dielectrics and metals are presented, followed by a detailed description of each step in the fabrication process of AlGaN/GaN HEMTs and transmission media on LR Si substrate. The limitations and challenges faced while carrying out the technology development are outlined. Finally, the conclusions are summaries.

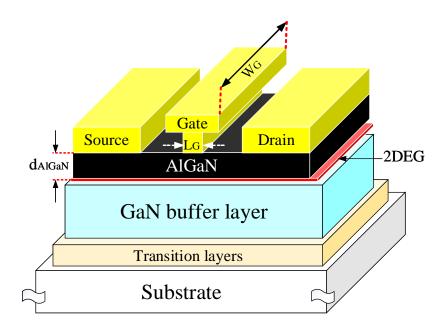

#### 2.2 Material Structure

GaN-based HEMT structures are based on the growth of stack layers with different bandgaps and polarisation fields, which enables the creation of discontinuity in the polarisation field and surface charges at the heterointerface. The two dimensional electron gas (2DEG) channel is formed by the electron compensation of the induced positive charge, where electrons are confined into a quantum well. Molecular Beam Epitaxy (MBE) and Metal-Organic Chemical Vapor Deposition (MOCVD) are among the most commonly used techniques for the epitaxial material growth. The following layers, from bottom to top, form the typical epitaxial layer structure of GaN-based HEMTs:

- *Nucleation buffer layers*: Thin intermediate layers of AlN, GaN, AlGaN or graded AlGaN are usually grown on the non-native substrate (e.g. Si) to compensate the lattice mismatch and stress between the GaN and substrate.

- Buffer layer: A lower bandgap material (e.g. GaN) is usually grown on the nucleation layers. High-quality buffer material with low defect density and high resistivity is essential for optimal device performance (e.g. full channel pinch-off, low gate leakage current, high drain-source current saturation and low microwave frequencies losses) [41].

- *Spacer layer*: A thin optimised AlN interlayer between the buffer layer and barrier layer plays an important role in decreasing electron scattering and hence improving the device 2DEG mobility [42].

- Barrier layer: A material with wider bandgap than the buffer layer is used as a barrier layer, e.g. Al<sub>x</sub>Ga<sub>1-x</sub>N and AlN. Device performance is strongly affected by the quality of this layer. The aluminium alloy concentration (x) and layer thickness determine the 2DEG density.

- *Cap layer*: A thin GaN cap layer (1-2 nm) is grown on the barrier layer to enhance gate current leakage as a result of increased effective Schottky barrier height, and to protect the epitaxial layer from oxidation [43].

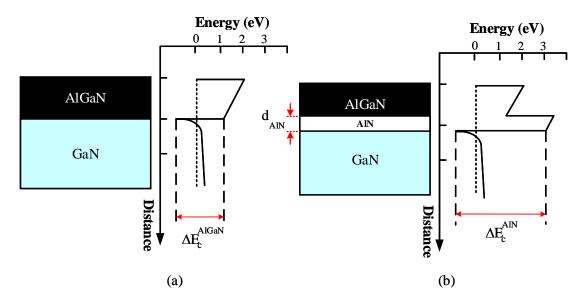

#### 2.3 Band diagram

Figure 2.1 illustrates the energy band diagram of AlGaN/GaN and AlGaN/AlN/GaN heterostructures. A conduction band offset is observed as a result of the conduction band energy variation at the material interfaces. This creates a triangular-like quantum well with lower energy levels, which attract electrons resulting in the formation of the 2DEG at the interface. The diagrams also show that a large effective conduction band offset is produced when inserting a thin AlN interlayer in the heterointerface of AlGaN/GaN. This is because of the potential drop across the spacer layer owing to large piezoelectric and spontaneous polarisation field. The conduction band offset increase in the presence of the AlN interlayer is evaluated by [42]:

$$\Delta E_c^{AlN} - \Delta E_c^{AlGaN} = \exp\left(\frac{\sigma_{AlN} - N_{2DEG}}{\varepsilon_{AlN}}\right) d_{AlN}$$

(2.1)

Where the offsets in the conduction bands between the AlGaN/AlN/GaN and AlGaN/GaN are indicated by  $\Delta E_c^{AlN}$  and  $\Delta E_c^{AlGaN}$ , respectively.  $N_{2DEG}$  represents the sheet carrier concentration of the structure with the AlN interlayer.  $\varepsilon_{AlN}$  is the AlN spacer dielectric constant,  $\sigma_{AlN}$  is the polarisation induced charge at the AlGaN/GaN interface and  $d_{AlN}$  is the AlN spacer thickness.

Figure 2.1: Illustration of the pattern of energy band diagram for the (a) AlGaN/GaN. And (b) AlGaN/AlN/GaN HEMTs [42]

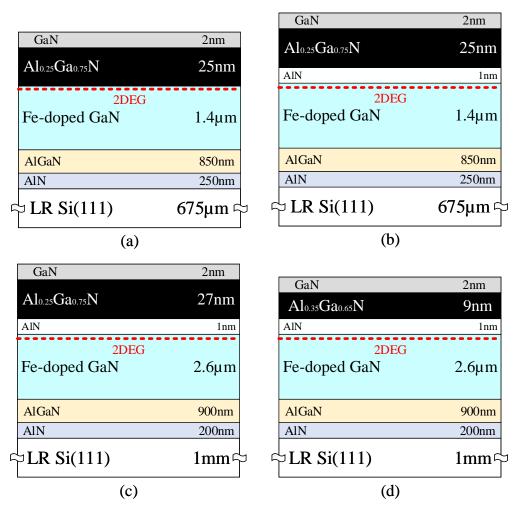

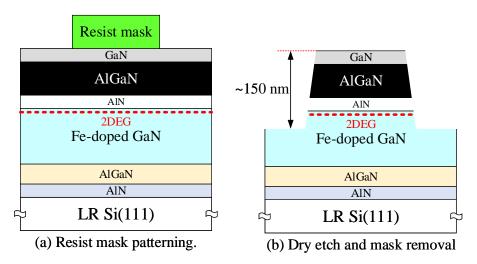

The study in this work was carried out on AlGaN/GaN HEMTs supplied by the Cambridge Centre for GaN at the University of Cambridge. The epitaxial structures were grown by MOCVD on a 150 mm diameter p-type LR Si ( $\sigma < 10 \ \Omega$ .cm) substrates. A number of material structures with identical layer stack order and slightly different thickness were used in this work, as shown in Figure 2.2. The layer stack, from the substrate up, consists of a 250/220 nm AlN nucleation layer followed by a 850/900 nm Fe-doped AlGaN graded buffer (to accommodate the lattice and thermal expansion miss-match), a 1.4/2.6 µm insulating Fe-doped GaN buffer layer and a GaN channel layer. The channel includes a 1 nm AlN spacer layer, a 27/9 nm Al<sub>0.25</sub>Ga<sub>0.75</sub>N/Al<sub>0.35</sub>Ga<sub>0.65</sub>N barrier and a 2 nm GaN cap. Fe-doping in the GaN buffer makes the fabricated devices suitable for high power switching operation [44].

Figure 2.2: Schematic cross-sections of GaN-based HEMT layer sequences grown on LR Si epitaxial wafer structures used in this work.

#### 2.4 Sample Preparation

Surface treatment and cleaning procedures are crucial prior to any fabrication process. There are two purposes in sample preparation; the removal of residues or debris resulting from cleaving the wafer and the removal of native oxide layers as a result of exposing the surface of a semiconductor to air. All samples used in this work were initially cleaned using standard cleaning procedures. The organic contamination of the sample surface was chemically and physically removed by soaking the sample in acetone, followed by isopropyl alcohol (IPA) in an ultrasonic water bath for five minutes. Finally, the sample was rinsed with de-ionised (DI) water and blown dry with a nitrogen N<sub>2</sub>, gun. Commonly used Hydrochloric (HCL): H<sub>2</sub>O and Hydrofluoric (HF): H<sub>2</sub>O diluted acids can effectively remove oxide layers and carbon/hydrocarbon contamination, respectively [45].

#### 2.5 Lithography

Lithography is one of the most critical processes required for the fabrication of modern microelectronic integrated circuits [46]. The process involves the transformation of designed patterns into the sample surface coated with a radiation-sensitive film (resist) using a masking layer. Optical and e-beam are the most commonly used lithography techniques, and can be chosen based on the required minimum feature size and alignment accuracy. E-beam lithography is preferable for the fabrication of sub-micron devices. On the other hand, optical lithography is faster and cheaper compared to e-beam but has limited resolution and registration because of diffraction [47]. In this report, optical lithography was employed for the fabrication of passive components; active devices were fabricated using e-beam.

#### 2.5.1 Optical Lithography

Optical lithography, also referred to as photolithography, can be defined as the process of transferring patterns from a mask plate to a wafer surface [47]. The process involves the ultraviolet (UV) light through an optical mask onto a substrate coated with photo-sensitive resist. In this work, the contact photolithography method was used for optimal pattern transfer from the mask. The optical mask (normally defined by e-beam or laser beam) was held in contact with the sample using a vacuum, while the UV light was focussed through a lens to ensure a

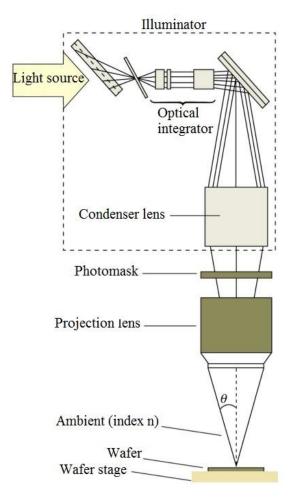

uniform and coherent exposure. Extra care was required during this process to reduce the risk of damaging the mask and contaminating the sample by a physical contact. This issue can be resolved by elevating the mask above the substrate. However, light diffraction around the mask features may consequently cause a slight deterioration in the achievable resolution. The optical system of a mask aligner used to replicate a mask pattern during photolithography is shown in Figure 2.3.

A resist image was obtained by replicating the mask pattern using a mask aligner, the UV light was collected from the source, and the mask pattern was illuminated by the condenser. Next, an aerial image was formed in order to provide a selective resist exposure. This was done by passing the illuminated light through the imaging lens. The patterned resist can be used for the subsequent fabrication process, e.g. dry etch, lift-off, plating, metallisation or implantation. Photoresists used for photolithography are generally classified into two types:

Figure 2.3: Illustration of the optical system of a mask aligner used to replicate a mask pattern during optical lithography [48].

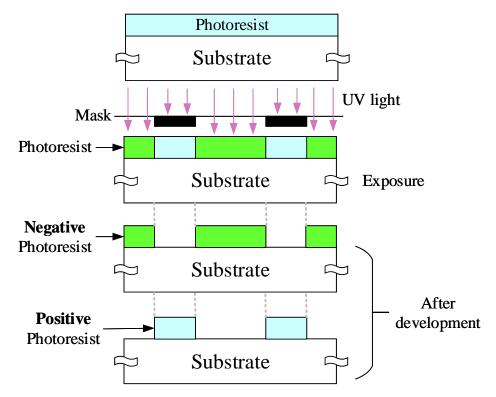

positive and negative. Figure 2.4 illustrates the outcome of a positive and negative resist once a mask pattern is exposed onto a resist-coated wafer and the pattern is etched after resist development of the mask pattern. The reaction of the photoresists to UV light or radiation determines the type of the resist. For example, the areas exposed to UV light of the positive photoresist become more soluble in developer solutions and are then removed during the development process. As a consequence, the pattern transferred on the resist-coated sample will be a replication of the pattern on the mask. On the other hand, negative photoresists react oppositely to UV light exposure, where the unexposed regions become more soluble in development process.

In this report, contact photolithography was carried out using a Karl Suss MA6 mask aligner, which has a light source of  $\lambda = 365$  nm [49]. This, however, limits the resolution to nearly 1 µm. Since a minimum feature size of 5 µm is required for passive component fabrication, the optical lithography technique was adequate to satisfy the resolution requirements. However, at frequencies beyond X-band, active device realisation required the use of gate technology of 0.3 µm or less along with good alignment accuracy, where several levels of lithography were needed. In this case, e-beam lithography had to be employed.

Figure 2.4: An image of a negative photoresist and positive photoresist after exposure.

#### 2.5.2 E-beam Lithography

In electron beam lithography, which is also known as "e-beam" or EBL, patterns are written directly onto the resist-coated sample using a focussed electron beam. Unlike photolithography, EBL does not need a mask plate for pattern transfer. The patterns are initially generated or designed in software and then transferred to a computer-controlled exposure system which controls the highly confined electron beam for pattern production.

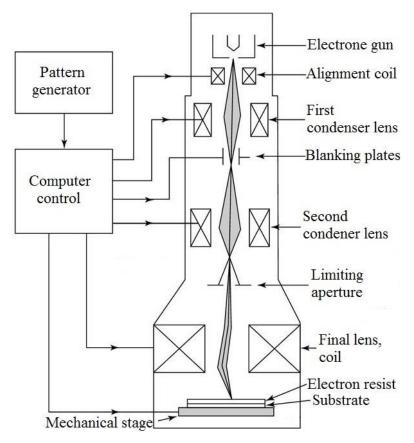

The principal components of a typical EBL machine are outlined in Figure 2.5. The pattern is written on the resist-coated substrate using a beam of electrons generated by the electron gun. Heating a tungsten filament results in electron emission, where the electrons gain sufficient energy to overcome their work function barrier. Moreover, the emission properties of the electron source are controlled by incorporating the electron gun with an electron or more. Electron optics within the column can accurately control the diameter, profile and direction of the electron beam, whereas, fine control of the stage positioning mechanism within the chamber can perform precise alignment. The vacuum system provides two main functions during operation; maintaining a constant pressure throughout the column and at the gun assembly, and controlling the pressure variation which is needed for loading and unloading samples. The supporting electronic system is used for power generation and signal transmission, which works as a system variation regulators throughout the e-beam machine. A master computer is used to drive the whole e-beam tool. In this work, electron beam lithography was carried out using a Vistec VB6-UHREWF, which has a maximum field size of 1.2 mm, minimum resolution of 0.5 nm and a minimum spot size of approximately 4 nm [50].

Figure 2.5: E-beam lithography system [51].

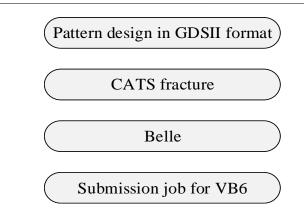

#### 2.5.3 Pattern Definition

Standard approaches using CAD packages are widely used to transfer patterns to the e-beam tool. The large structures on the pattern were initially divided into smaller shapes that can be achieved by the pattern generator, as large patterns were written from conjoined small fields in the e-beam tool. This can be realised using the fracture process where large shapes are broken into trapezoidal sub-shapes. Figure 2.6 summarises the general fracture process from design to lithography. The GDS layout file, which was generated using CAD package, is fractured by using commercial fracturing tools, e.g. the CATS package from Synopsys. The fractured patterns are then exposed using a computer-controlled system at given positions related to substrate corners at specific exposure. Belle (Beam-writer Exposure for Lithography Engineers) software, which was developed at the University of Glasgow, was used to create these files. Further layers can be aligned relative to the first metallization layer to produce multi-level devices. In this case, several lithography levels could be written and accurately aligned based on scanning the edges of alignment markers with a specific size. [50].

Figure 2.6: General data processing flow for e-beam submission job.

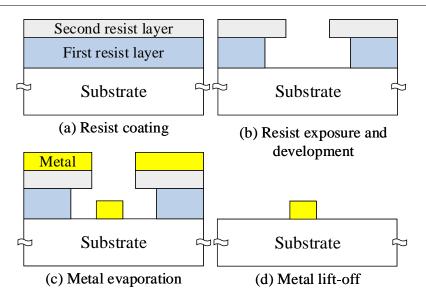

Polymers are used as e-beam resits for e-beam lithography. They behave in a similar way to those of photoresists where radiation can chemically or physically change the e-beam resist in order to pattern the resist. For positive tone e-beam resists, molecular fragments are generated by breaking the chemical bonds of resist exposed areas to electrons. This causes the exposed areas to be dissolved more quickly in the development process. On the other hand, irradiation can result in radiation-induced polymer linking when using negative tone e-beam resists, causing complexity in the three-dimensional structure. Hence, the exposed areas become harder to dissolve in the development solution.

The main benefit of the e-beam tool is that when using electrons instead of light to expose the radiation-sensitive resist, it overcomes the resolution restrictions by light diffraction. E-beam lithography resolution is limited by the minimum achievable beam spot size and the interactions of incident electrons with the resist and substrate during exposure [50].

Some advantages of using EBL include:

- Sub-micron features patterning

- Highly automated and precisely controlled operation

- Precise layer to layer alignment

- Fixable and no mask plate required as the designed patterns are directly transferred and written on the resit-coated sample

- Ease of editing layout design during the fabrication run

However, some disadvantages existed when comparing EBL to photolithography, including a long processing time and relatively higher operation costs and low throughput. In summary, photolithography is only preferred when a minimum feature size of 2  $\mu$ m and alignment accuracy of 1  $\mu$ m are required.

### 2.5.4 Mask Plate

The mask plate is needed for optical lithography pattern transfer. The GDS file pattern is initially generated in CAD package (L-Edit) prior to fracturing in CATS. Next, the fractured pattern is handled in BELL software using several given parameters, e.g. substrate size, dose and resolution, as described in Section 2.5.2. Having finished the CAD design and e-beam job submission, the mask plates are processed by the technical staff of JWNC where submitted pattern is written using e-beam tools. The mask plate substrate is quartz coated with chrome. The process starts by patterning the e-beam resist on the substrate which is used as a mask for the subsequent chemical wet etch process. The exposed areas of the chrome on the mask are then etched away using a chemical wet etch, prior to ashing, so that the original pattern is transferred into the chrome.

# 2.6 Dry Etch

As a result of the chemical stability of group III-Nitride semiconductors and the requirements of defining sub-microns trenches along with high alignment accuracy, dry etching (also called plasma-assisted etching) is considered the dominant etching technique in this project for both active and passive devices. Amongst all dry etching techniques, reactive ion etching (RIE) and inductively-coupled plasma reactive ion etching (ICP-RIE) have been commonly utilised in III-nitride materials etching process. This section is devoted to these dry etch process approaches.

### 2.6.1 Reactive Ion Etching

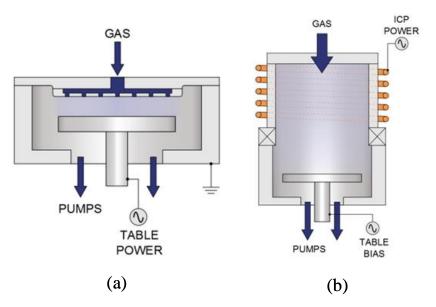

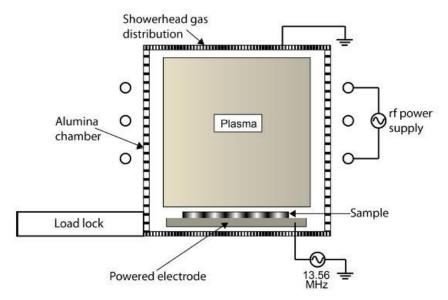

In Reactive Ion Etching (RIE), anisotropic profiles, fast etch rates and dimensional control are realised by the use of both chemical and physical components of an etch mechanism. A typical RIE system is schematically indicated in Figure 2.7a [52]. An RF power at 13.56 MHz applied between two parallel electrodes in a reactive gas is optimally used to generate RIE plasmas.

The substrate to be etched is located on the powered electrode, where a voltage is applied and ion energies, which are ideally a few hundred electron-volts, are defined as they pass the plasma sheath. Because of the low pressures (ranging from a few mTorr up to 200 mTorr) required to operate the RIE, anisotropic etching profiles result the rise in mean free paths and reduction in collisional scattering of ions during acceleration in the sheath [53]. However, difficulties are encountered in the achievement of independent control of both physical and chemical components during the etching process in traditional RIE tools. This will noticeably affect the etch profile shape, in particular for III-Nitride materials, where breaking the bonds between their forming atoms needs relatively high ion energy. The RIE process was carried out in this project using an Oxford Instruments Plasmalab RIE 80 Plus and System 100 (T-gate).

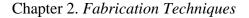

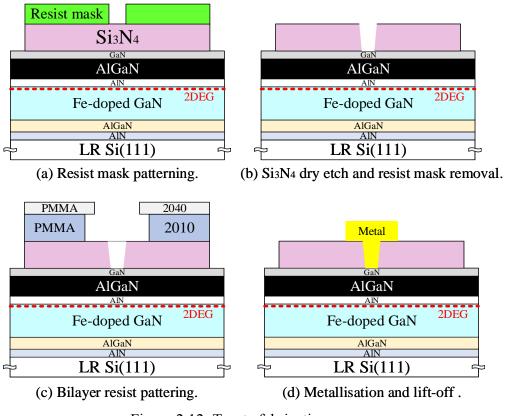

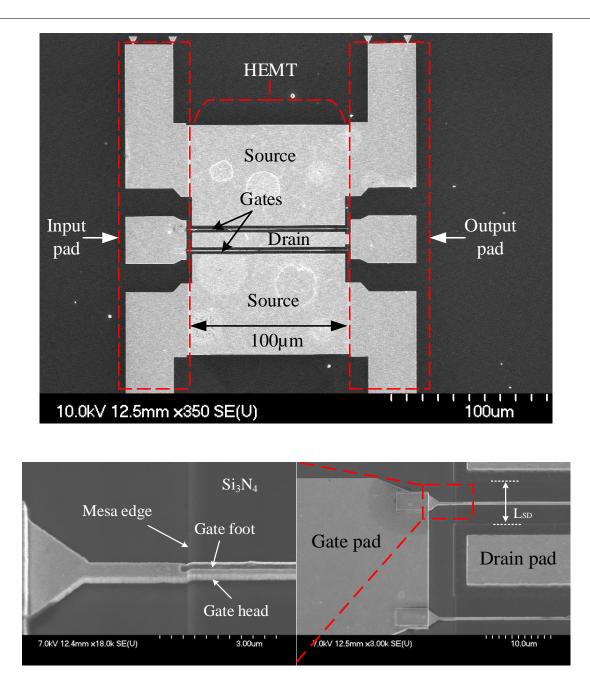

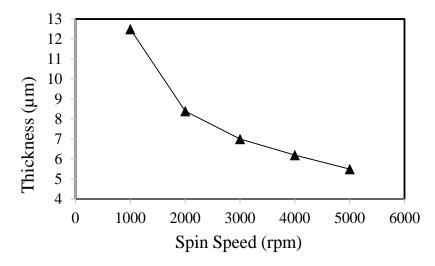

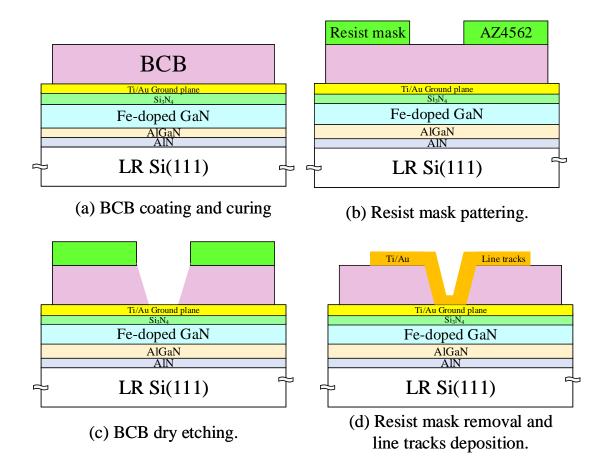

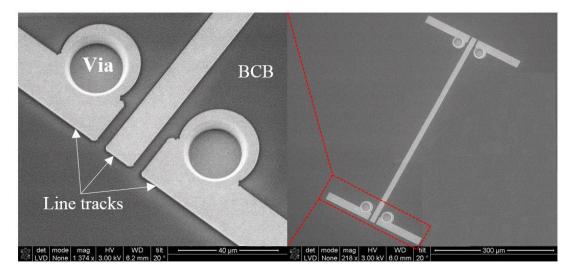

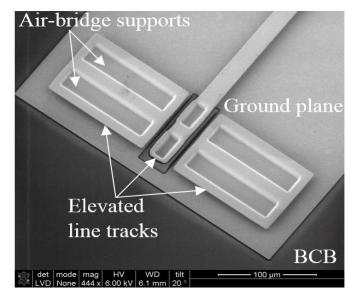

### 2.6.2 Inductively-Coupled Plasma Reactive Ion Etching